#### **General Description**

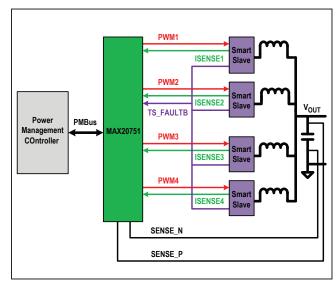

The MAX20751 PMBus™-compliant multiphase master IC, with extensive status and parameter monitoring, is capable of driving up to four smart-slave integrated power devices.

Utilizing Maxim's smart-slave ICs, the device provides a high-density and flexible solution that can be tailored to a range of power loads used in communication equipment. Proprietary-coupled inductors, recommended to reduce the effective inductor value without excessive ripple current, results in improved transient response and reduction in the number of output capacitors required.

The device incorporates current reporting, temperature monitoring, fault detection, and PMBus support. Overcurrent and overtemperature faults are detected by the individual smart slaves and faults communicated through the master IC. The highest junction temperature is reported, both before and after smart-slave regulation.

The device features an integrated switching regulator that can optionally be used to supply the  $V_{DD}$  rail for the master controller and smart-slave devices to reduce the power-rail requirements and simplify the regulator design.

#### **Applications**

- Communication, Networking, Servers, and Storage Equipment

- ASICs

- · Microprocessor Chipsets

- Memory V<sub>DDQ</sub>

- · Other High-Current Digital ICs

Ordering Information appears at end of data sheet.

PMBus is a trademark of SMIF, Inc.

#### **Benefits and Features**

- Increased Power Density with Fewer External Components Needed

- · Scalable, Multiphase Solution

- Compatibility with Coupled Inductors Enables Fast Transient Response and Reduced C<sub>OUT</sub>

- Integrated Internal Switching Regulator to Power Smart Slaves

- Optimized Component Performance and Efficiency with Reduced Design-In Time

- PMBus-Compliant Interface for Telemetry and Power Management

- Field-Programmable Memory to Allow Storage of Desired Configuration Parameters

- · Fault Logging

- Comprehensive System and IC Self-Protection

Features Promote Increased Power-Supply Reliability

- · Overcurrent and Overtemperature

- · Boost Voltage UVLO

- VX Short to Ground or V<sub>DDH</sub> Detection

- · Phase-Current Steering for Thermal Balancing

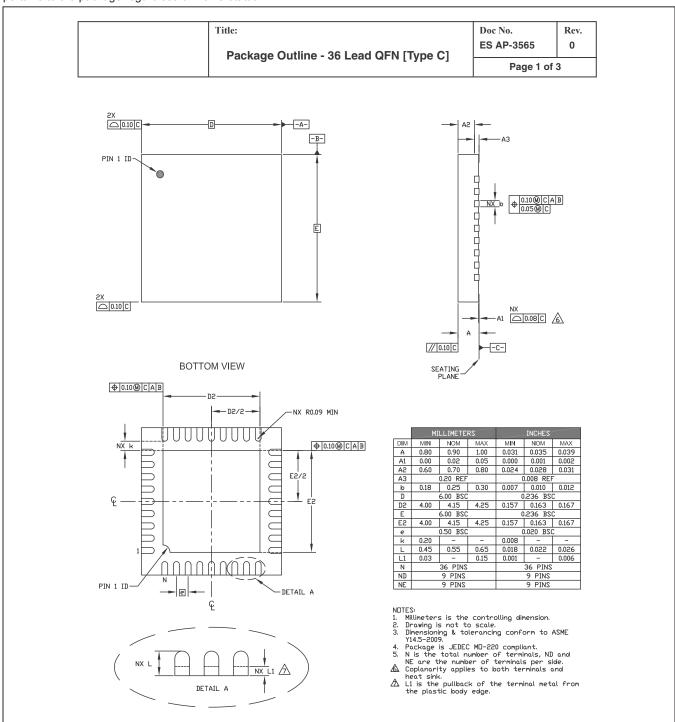

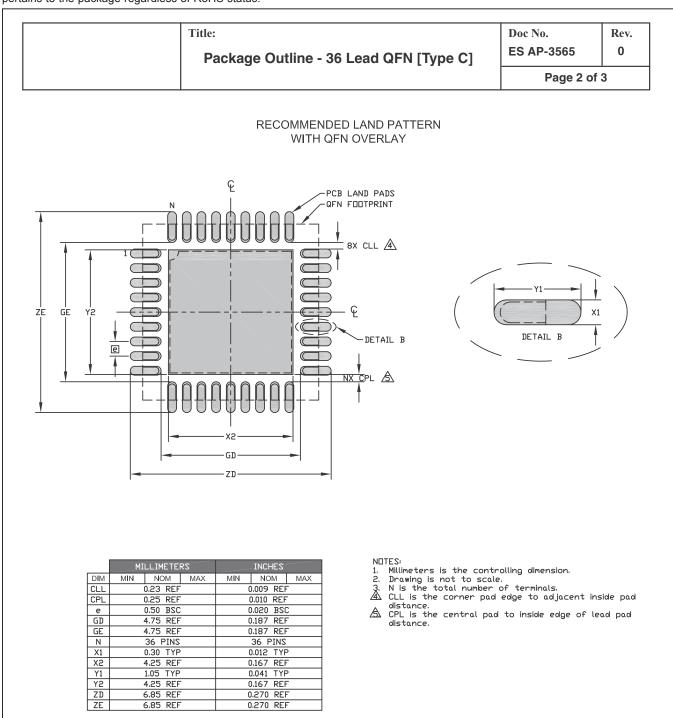

- 36-Pin (6mm x 6mm) QFN Package

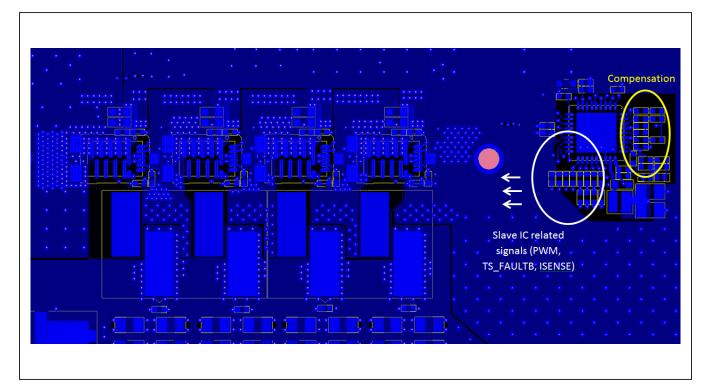

Figure 1. Basic Application Circuit

### **Absolute Maximum Ratings**

| V <sub>DD33</sub> Supply Voltage | 0.3V to +4V                      | SENSE_P                                | -0.3V to +4V                  |

|----------------------------------|----------------------------------|----------------------------------------|-------------------------------|

| VIN_UV, VR_ON and PWRGD Pins     | 0.3V to +4V                      | R_REF, MRAMP, R_SELx, PWMx             | , TS_FAULTB, ISENSEx,         |

| V <sub>DD</sub> Supply Voltage   | 0.3V to +2.5V                    | A1_OUT, A2_x, A2B_OUT, A3_x            | 0.3 to V <sub>DD</sub> + 0.3V |

| PVX to PGND                      | 0.6V to V <sub>DD33</sub> + 0.6V | Junction Temperature (T <sub>J</sub> ) | +150°C                        |

| PMBus Pins (PMD, PMC, ALERTB)    | 0.3V to +6V                      | Storage Temperature Range              | 65°C to +150°C                |

| SENSE_N                          | 0.3V to V <sub>DD</sub> +0.3V    | Peak Reflow Temperature                | +260°C                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Operating Ratings**

| V <sub>DD33</sub> Supply Voltage | +2.97V to +3.63V | SENSE N0.1V to +0.2V                                       |

|----------------------------------|------------------|------------------------------------------------------------|

| V <sub>DD</sub> Supply Voltage   |                  | SENSE P0.1V to +2.5V                                       |

| VIN UV, VR ON and PWRGD          |                  | Junction Temperature Range (T <sub>J</sub> )40°C to +125°C |

| PMRus Pins (PMD PMC ALERTR)      | -0.1\/ to +5.5\/ | 3 ( 0)                                                     |

### **Package Thermal Characteristics**

**TQFN**

Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......1.7°C/W

This product is completely Halogen-free and Pb-free, employing SnAgCu solder balls. The product is RoHS compliant with an -e1 termination finish and is compatible with both SnPb and Pb-free soldering operations. The product is MSL classified at peak reflow temperatures that meet JEDEC JSTD-020.

#### **Electrical Characteristics**

(V<sub>DD</sub> = 1.71V to 1.98V, V<sub>DD33</sub> = 3.3V  $\pm$ 10%, **T<sub>J</sub> = +25°C**, unless otherwise noted.)

| PARAMETER                                                      | SYMBOL                   | CONDITIONS                                                          | MIN  | TYP  | MAX  | UNITS |  |

|----------------------------------------------------------------|--------------------------|---------------------------------------------------------------------|------|------|------|-------|--|

| SUPPLY VOLTAGES AND CURRENTS                                   |                          |                                                                     |      |      |      |       |  |

| Supply Voltage Range                                           | V <sub>DD</sub>          | If external V <sub>DD</sub> supply is used                          | 1.71 | 1.86 | 1.98 | V     |  |

| Supply Current                                                 | I <sub>DD</sub>          | PWM not switching (Note 2)                                          | 14   | 17   | 20   | mA    |  |

| 3.3V Supply Voltage Range                                      | V <sub>DD33</sub>        |                                                                     | 2.97 | 3.30 | 3.63 | V     |  |

| 3.3V Supply Current                                            | I <sub>DD33</sub>        | No load, internal integrated switcher disabled, PMBus idle (Note 2) |      | 24   | 130  | μA    |  |

| V <sub>DD</sub> UVLO (UNDERVOLTAGE LOCKOUT)                    |                          |                                                                     |      |      |      |       |  |

| Supply Voltage Undervoltage-<br>Lockout Rising Threshold       | V <sub>DD_UVLO_RIS</sub> | (Note 2)                                                            |      | 1.62 | 1.66 | V     |  |

| Supply Voltage Undervoltage-<br>Lockout Falling Threshold      | V <sub>DD_UVLO_FAL</sub> | (Note 2)                                                            | 1.58 | 1.60 |      | V     |  |

| V <sub>DD33</sub> UVLO                                         |                          |                                                                     |      |      |      |       |  |

| 3.3V Supply Voltage Undervoltage-<br>Lockout Rising Threshold  | V <sub>DD33_UV_RIS</sub> | (Note 2)                                                            |      | 2.90 | 2.95 | V     |  |

| 3.3V Supply Voltage Undervoltage-<br>Lockout Falling Threshold | V <sub>DD33_UV_FAL</sub> | (Note 2)                                                            | 2.80 | 2.85 |      | V     |  |

Electrical Characteristics (continued) ( $V_{DD}$  = 1.71V to 1.98V,  $V_{DD33}$  = 3.3V ±10%,  $T_J$  = +25°C, unless otherwise noted.)

| PARAMETER                                                              | SYMBOL                | CONDITIONS                                                                           | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|-------|-------|-------|-------|

| VIN UVLO (USING VIN_UV PIN)                                            |                       |                                                                                      |       |       |       |       |

| VIN_UV Rising Threshold                                                | VIN_UV <sub>RIS</sub> | (Note 2)                                                                             |       | 0.380 | 0.390 | V     |

| VIN_UV Falling Threshold                                               | VIN_UV <sub>FAL</sub> | (Note 2)                                                                             | 0.318 | 0.328 |       | V     |

| Delay from VIN_UV UVLO to<br>System Shutdown                           | tdVIN_UV_UVLO         |                                                                                      | 125   |       | 275   | ns    |

| INTEGRATED INTERNAL SWITCH                                             | ER                    |                                                                                      |       |       |       | ,     |

| Output Valley Voltage                                                  | V <sub>OUT_IIS</sub>  |                                                                                      |       | 1.86  |       | V     |

| Current Driving Capability                                             | I <sub>OUT_IIS</sub>  | Tested at L = 2.2μH, t <sub>ON</sub> = 1.30μs                                        | 300   |       |       | mA    |

| Switcher Peak Inductor Current                                         | I <sub>LPK_IIS</sub>  |                                                                                      |       |       | 1.5   | Α     |

| High-Side Switch On-Time                                               |                       | Default 1.30µs (Notes 1, 2)                                                          | 0.52  | 0.65  | 0.78  |       |

|                                                                        |                       |                                                                                      | 1.04  | 1.30  | 1.56  | - µs  |

|                                                                        | ton_iis               |                                                                                      | 1.52  | 1.90  | 3.28  |       |

|                                                                        |                       |                                                                                      | 2.20  | 2.75  | 3.30  |       |

| V <sub>NOM</sub> (NOMINAL OUTPUT VOLTAGE AFTER STARTUP, WITHOUT DROOP) |                       |                                                                                      |       |       |       |       |

| Output Voltage Range                                                   | VNOM                  | Programmable through R_SEL or PMBus, direct feedback of VOUT to SENSE_P (Notes 1, 2) | 0.500 |       | 1.520 | V     |

| Resolution                                                             |                       | (Note 2)                                                                             |       | 5     |       | mV    |

| DO 4                                                                   |                       | 1V ≤ V <sub>NOM</sub> ≤ 1.52V (Note 2)                                               | -0.5  |       | +0.5  | %     |

| DC Accuracy                                                            |                       | 0.5V ≤ V <sub>NOM</sub> < 1V (Note 2)                                                | -5    |       | +5    | mV    |

| rajastmant valtago,                                                    |                       |                                                                                      | 3.25  | 3.75  | 4.25  | mV    |

|                                                                        |                       |                                                                                      | 2.00  | 2.50  | 3.00  |       |

|                                                                        |                       |                                                                                      | 0.75  | 1.25  | 1.75  |       |

|                                                                        | VOUT_FINE_ADJ         | Programmable with PMBus, default is 0.00mV. (Notes 1, 2)                             | -0.50 | 0.00  | +0.50 |       |

|                                                                        |                       |                                                                                      | -1.75 | -1.25 | -0.75 |       |

|                                                                        |                       |                                                                                      | -3.00 | -2.50 | -2.00 |       |

|                                                                        |                       |                                                                                      | -4.25 | -3.75 | -3.25 |       |

|                                                                        |                       |                                                                                      | -5.50 | -5.00 | -4.50 |       |

| SWITCHING FREQUENCY                                                    |                       |                                                                                      |       |       |       |       |

| Nominal Switching Frequency Range                                      | fsw                   | Programmable through R_SEL or PMBus (Note 1)                                         | 300   |       | 800   | kHz   |

| Switching Frequency Tolerance                                          | f <sub>SW_TOL</sub>   | (Note 2)                                                                             | -10   |       | +10   | %     |

| OUTPUT-VOLTAGE STARTUP SLE                                             |                       |                                                                                      |       |       |       |       |

|                                                                        |                       |                                                                                      |       | 0.5   |       |       |

| Output-Voltage Slew Rate After                                         |                       | Programmable through R_SEL or                                                        |       | 1.25  |       | m\//  |

| Output-Voltage Slew Rate After Initial Jump from 0V                    | S <sub>VOUT</sub>     | PMBus (Note 1)                                                                       |       | 2.5   |       | mV/μs |

|                                                                        |                       |                                                                                      |       | 5     |       |       |

Maxim Integrated | 3 www.maximintegrated.com

Electrical Characteristics (continued) ( $V_{DD}$  = 1.71V to 1.98V,  $V_{DD33}$  = 3.3V ±10%,  $T_J$  = +25°C, unless otherwise noted.).

|                                                                             |                      | T                                                                            |        |        |        |       |

|-----------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------|--------|--------|--------|-------|

| PARAMETER                                                                   | SYMBOL               | CONDITIONS                                                                   | MIN    | TYP    | MAX    | UNITS |

| R_REF                                                                       |                      |                                                                              |        |        |        |       |

| Reference Voltage for R_REF                                                 | V <sub>R_REF</sub>   | (Note 2)                                                                     | 0.79   | 0.80   | 0.81   | V     |

| AMPLIFIER A1                                                                |                      |                                                                              |        |        |        |       |

| A1 Amplifier Closed-Loop<br>Differential Gain                               | A <sub>1DM</sub>     | (Note 2)                                                                     | 2.17   | 2.19   | 2.23   | V/V   |

| Error-Amplifier Closed-Loop BW                                              | CLBW                 |                                                                              | 7      |        | 15     | MHz   |

| Positive Sense Line Current                                                 | I <sub>SENSE_P</sub> | VSENSE_N grounded (Note 2)                                                   |        |        | 90     | μA    |

| Negative Sense Line Current                                                 | I <sub>SENSE_N</sub> | VSENSE_P grounded (Note 2)                                                   | -90    |        |        | μA    |

| AMPLIFIER A2                                                                |                      |                                                                              |        |        |        |       |

| Amplifier Closed-Loop Gain of A2 with feedback capacitor C2 shorted         | A <sub>V2</sub>      | Set through external R (Note 1)                                              | 1      |        | 4      | V/V   |

| A2 Amplifier Open-Loop Gain                                                 | A <sub>OL2</sub>     |                                                                              | 60     |        |        | dB    |

| Closed-Loop Bandwidth                                                       | CLBW_A2              | Gain = 2                                                                     | 10     |        |        | MHz   |

| AMPLIFIER A2B                                                               |                      |                                                                              |        |        |        |       |

| A2B Amplifier Closed-Loop Gain                                              | A <sub>DM</sub>      |                                                                              |        | 1      |        | V/V   |

| Closed-Loop Bandwidth                                                       | CLBW_A2B             |                                                                              | 11     |        |        | MHz   |

| AMPLIFIER A3                                                                |                      |                                                                              |        |        |        |       |

| A3 Amplifier Open-Loop Gain                                                 | A <sub>OL3</sub>     |                                                                              | 60     |        |        | dB    |

| Closed-Loop Bandwidth                                                       | CLBW_A3              | Gain = 2                                                                     | 10     |        |        | MHz   |

| MODULATOR RAMP RATE                                                         |                      |                                                                              |        |        |        |       |

| Ramp-Rate Programming Range                                                 | M <sub>RAMP</sub>    | Program through R at MRAMP pin (Note 1)                                      | 0.4    |        | 2      | V/µs  |

| OVERCURRENT PROTECTION (OC                                                  | P)                   |                                                                              |        |        |        |       |

| Positive Current Limit (Sustaining),<br>Programmed Through R <sub>DES</sub> | Pocp                 | Voltage across R <sub>DES</sub> referred to VCM, 4-phase system (Notes 1, 2) | -0.658 | -0.598 | -0.538 | V     |

| Negative Current Limit (Sustaining)                                         | N <sub>OCP</sub>     | Voltage across R <sub>DES</sub> referred to VCM, 4-phase system (Note 2)     | 0.157  | 0.183  | 0.209  | V     |

| Positive Current-Limit Tolerance                                            | ILIM_TOL             | Not including the external resistor tolerance (1%) (Note 2)                  | -10    |        | +10    | %     |

| OVERVOLTAGE PROTECTION (OV                                                  | P)                   |                                                                              |        |        |        | ,     |

| Tracking OVP Threshold Voltage<br>Above V <sub>NOM</sub> (Rising)           |                      | (Note 2)                                                                     |        | 205    | 217    | >/    |

| Tracking OVP Threshold Voltage (Falling)                                    | V_TRA_OVP            | (Note 2)                                                                     | 187    | 199    |        | mV    |

| Tracking OVP Blanking Time from the End of an I <sub>DAC</sub> Transition   | t_BL_OVP             |                                                                              |        | 90     |        | μs    |

Maxim Integrated | 4 www.maximintegrated.com

Electrical Characteristics (continued) ( $V_{DD}$  = 1.71V to 1.98V,  $V_{DD33}$  = 3.3V ±10%,  $T_J$  = +25°C, unless otherwise noted.)

| DADAMETED                                                            | OVMDOL                    | CONDITIONS                                                                                   | BAINI | TVD  | MAY             | LINUTO |

|----------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------|-------|------|-----------------|--------|

| PARAMETER                                                            | SYMBOL                    | CONDITIONS                                                                                   | MIN   | TYP  | MAX             | UNITS  |

| Umbrella OVP Threshold Voltage (Rising)                              | V_UMB_OVP                 | (Note 2)                                                                                     |       | 2.52 | 2.59            | V      |

| Umbrella OVP Threshold Voltage (Falling)                             | v_OMB_OVP                 | (Note 2)                                                                                     | 2.38  | 2.45 |                 | V      |

| Delay Time to Respond to OVP                                         | t <sub>d_OVP</sub>        |                                                                                              |       | 1    |                 | μs     |

| VR_ON (ENABLE) PIN                                                   | _                         |                                                                                              |       |      |                 |        |

| VR_ON <sub>IH</sub>                                                  | V/D ON                    | (Note 2)                                                                                     | 0.9   |      |                 | V      |

| VR_ON <sub>IL</sub>                                                  | VR_ON                     | (Note 2)                                                                                     |       |      | 0.2             | V      |

| VR_ON Deglitch Filter Time                                           | t <sub>FLT_VRON</sub>     |                                                                                              |       | 2    |                 | μs     |

| PWRGD (Note 3)                                                       |                           |                                                                                              |       |      |                 |        |

| PWRGD Assert Threshold (Rising)                                      |                           | Referenced to V <sub>NOM</sub> (Note 2)                                                      |       | -225 | -216            | mV     |

| PWRGD Deassert Threshold (Falling)                                   | V <sub>THR PG</sub>       | Referenced to V <sub>NOM</sub> (Note 2)                                                      | -234  | -227 |                 | mV     |

| PWRGD Deassert Threshold<br>Deglitch Filter Time                     | _                         |                                                                                              |       |      | 8               | μs     |

| PWRGD High-Deglitch<br>Filter Time                                   | t <sub>d_PG</sub>         | PWRGD remains deasserted until 90µs after the end of the startup I <sub>DAC</sub> transition |       | 90   |                 | μs     |

| Output Low Voltage                                                   | V <sub>PG_OL</sub>        | I <sub>OL</sub> = -4mA (Note 2)                                                              |       |      | 0.3             | V      |

| ORTHOGONAL CURRENT REBAL                                             | <del></del>               |                                                                                              |       |      |                 |        |

|                                                                      | OCR                       | Programmable through PMBus (Note 1)                                                          |       | 0    |                 |        |

| 0.                                                                   |                           |                                                                                              |       | 1.8  |                 |        |

| Gain                                                                 |                           |                                                                                              |       | 3.5  |                 |        |

|                                                                      |                           |                                                                                              |       | 4.4  |                 |        |

| PMBus (PMC, PMD, ALERTB PINS                                         | )                         |                                                                                              |       |      |                 |        |

| Input High Voltage (PMC, PMD)                                        | V <sub>IH</sub>           | (Note 2)                                                                                     | 1.5   |      | V <sub>PM</sub> | V      |

| Input Low Voltage (PMC, PMD)                                         | V <sub>IL</sub>           | (Note 2)                                                                                     | -0.1  |      | +0.8            | V      |

| Output Low Voltage (PMD, ALERTB)                                     | V <sub>OL</sub>           | I <sub>OL</sub> = -4mA (Note 2)                                                              |       |      | 0.4             | V      |

| PMBus Resistor Pullup Voltage (PMC, PMD, ALERTB)                     | V <sub>PM</sub>           |                                                                                              | 1.71  |      | 5.5             | V      |

| PMBus Clock Frequency                                                | f <sub>PMC</sub>          |                                                                                              |       | 100  | 400             | kHz    |

| NONVOLATILE MEMORY PROGRA                                            |                           |                                                                                              | •     |      |                 |        |

| Temperature Range for<br>Programming Data into Nonvolatile<br>Memory | TEMP <sub>NVM</sub> _PROG | Applies only to STORE_USER_<br>ALL PMBus command                                             | -40   |      | +85             | °C     |

Maxim Integrated | 5 www.maximintegrated.com

Electrical Characteristics (continued) ( $V_{DD}$  = 1.71V to 1.98V,  $V_{DD33}$  = 3.3V ±10%,  $T_J$  = +25°C, unless otherwise noted.).

| PARAMETER                                                           | SYMBOL                 | CONDITIONS                                                                      | MIN   | TYP   | MAX   | UNITS |

|---------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------|-------|-------|-------|-------|

| PMBus MONITORING AND TELEMI                                         | ETRY                   |                                                                                 |       |       |       |       |

| Range of Reported Output Current as a Percentage of Positive Output |                        | 1, 2, or 3 slaves                                                               | -30   |       | +100  |       |

| Current-Limit IPLIM                                                 |                        | 4 slaves                                                                        | -30   |       | +88   | %     |

| Error of Reported Output Current                                    |                        | 4-phase system at 100A, 1.0V, not including R <sub>DES</sub> tolerance (Note 2) | -6    |       | +6    |       |

| Resolution of Reported Output Current                               | IOUT <sub>REPORT</sub> |                                                                                 |       | 0.5   |       | Α     |

| Update Rate of Reported Output Current                              |                        |                                                                                 |       | 512   |       | μs    |

| Overcurrent Warning Response<br>Time Delay After Update             |                        |                                                                                 |       | 1     |       | ms    |

| Range of Reported Highest Slave<br>Temperature                      |                        |                                                                                 | -40   |       | +127  | °C    |

| Error of Reported Highest Slave<br>Temperature                      |                        | 4-phase system at 70A, 1.0V (Note 2)                                            | -6    |       | +6    | °C    |

| Resolution of Reported Slave<br>Temperature                         | TEMP <sub>REPORT</sub> |                                                                                 |       | 1     |       | °C    |

| Update Rate of Reported Slave<br>Temperature                        |                        |                                                                                 |       | 3     |       | ms    |

| Temperature Warning or Fault-<br>Response Time Delay After Update   |                        |                                                                                 |       | 1     |       | ms    |

| Scaled Voltage Range of Input<br>Voltage at VIN_UV Pin              | VIN <sub>SCALE</sub>   |                                                                                 | 0.317 |       | 1.383 | V     |

| Range of Reported Input Voltage                                     |                        | 140/2048 for VIN_UV/VIN voltage ratio, no offset added                          | 4.625 |       | 20.25 | V     |

| Error of Reported Input Voltage                                     |                        | Not including tolerance of resistor voltage-divider (Note 2)                    | -2    |       | +2    | %     |

| Resolution of Reported Input<br>Voltage                             | VIN <sub>REPORT</sub>  |                                                                                 |       | 31.25 |       | mV    |

| Update Rate of Reported Input Voltage                               |                        |                                                                                 |       | 3     |       | ms    |

| Input-Voltage Warning or Fault-<br>Response Time Delay After Update |                        |                                                                                 |       | 1     |       | ms    |

Maxim Integrated | 6 www.maximintegrated.com

### **Electrical Characteristics (continued)**

( $V_{DD}$  = 1.71V to 1.98V,  $V_{DD33}$  = 3.3V ±10%,  $T_J$  = +25°C, unless otherwise noted.)

| PARAMETER                                                            | SYMBOL                 | CONDITIONS                                                          | MIN   | TYP | MAX   | UNITS |

|----------------------------------------------------------------------|------------------------|---------------------------------------------------------------------|-------|-----|-------|-------|

| Range of Reported Output Voltage                                     |                        |                                                                     | 0.500 |     | 1.520 | V     |

| Error of Reported Output Voltage                                     |                        | 1.000V ≤ V <sub>OUT</sub> ≤ 1.520V (Note 2)                         | -1    |     | +1    | %     |

| Enor of Reported Output Voltage                                      |                        | $0.500V \le V_{OUT} < 1.000V \text{ (Note 2)}$                      | -10   |     | +10   | mV    |

| Resolution of Reported Output Voltage                                | VOUT <sub>REPORT</sub> |                                                                     |       | 5   |       | mV    |

| Update Rate of Reported Output Voltage                               |                        |                                                                     |       | 3   |       | ms    |

| Output Voltage Warning or Fault-<br>Response Time Delay After Update |                        |                                                                     |       | 1   |       | ms    |

| Range of Reported Output                                             |                        | 1, 2, or 3 slaves                                                   | 0     |     | 100   |       |

| Power as a Percentage of (V <sub>OUT</sub> ) x (IPLIM)               |                        | 4 slaves                                                            | 0     |     | 88    | %     |

| Error of Reported Output Power                                       | POUT <sub>REPORT</sub> | 4-phase system at 100A, 1.0V, not including RDES tolerance (Note 2) | -7    |     | +7    | %     |

| Resolution of Reported Output<br>Power                               | . SO'KEPURI            |                                                                     |       | 2   |       | W     |

| Update Rate of Reported Output Power                                 |                        |                                                                     |       | 3   |       | ms    |

**Note 1:** Parameters are programmable.

**Note 2**: Specifications apply over the  $TJ = -40^{\circ}C$  to  $+105^{\circ}C$  temperature range.

Note 3: PWRGD output signal is different from the PMBus POWER\_GOOD signal.

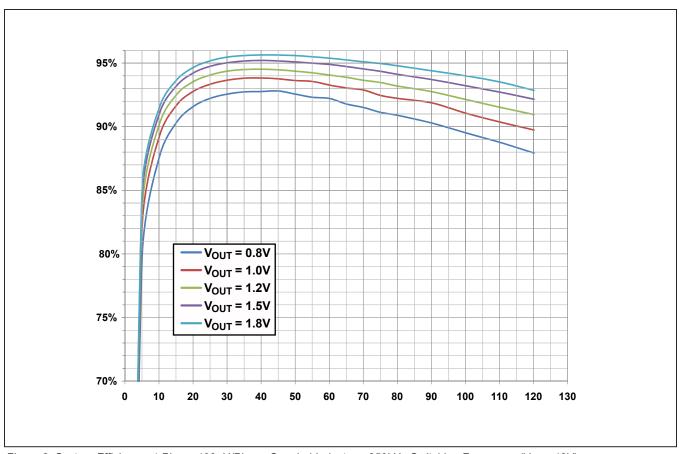

### **Typical Operating Characteristics**

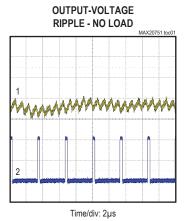

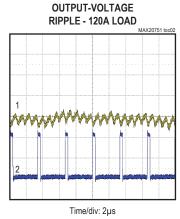

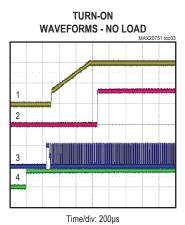

$(V_{IN}$  = 12V,  $V_{OUT}$  = 1.00V,  $f_{SW}$  = 300kHz, Four Phases,  $C_{OUT}$  = 32 x 47 $\mu$ F Multilayer Ceramic Capacitors,  $L_{OUT}$  = 100nH/Phase Two Winding-Coupled Inductor for Each Pair of Phases.)

CONDITIONS: TRIGGER ON PWM2, POSITIVE-GOING EDGE

- 1. V<sub>OUT</sub>: 5mV/div, 20MHz BANDWIDTH

- 2. PWM2: 1.00V/div, 20MHz BANDWIDTH

CONDITIONS: TRIGGER ON PWM2, POSITIVE-GOING EDGE

- 1. V<sub>OUT</sub>: 5mV/div, 20MHz BANDWIDTH

- 2. PWM2: 1.00V/div, 20MHz BANDWIDTH

CONDITIONS: TRIGGER ON VR\_ON, POSITIVE-GOING EDGE

- 1. V<sub>OUT</sub>: 500mV/div, 20MHz BANDWIDTH

- 2. PWRGD: 2.00V/div, 20MHz BANDWIDTH

- 3. PWM2: 2.00V/div, 20MHz BANDWIDTH

- 4. VR\_ON: 2.00V/div, 20MHz BANDWIDTH

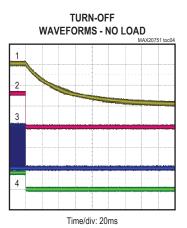

CONDITIONS: TRIGGER ON VR\_ON, NEGATIVE-GOING EDGE

- 1.  $V_{OUT}$ : 500mV/div, 20MHz BANDWIDTH

- 2. PWRGD: 2.00V/div, 20MHz BANDWIDTH

- 3. PWM2: 1.00V/div, 20MHz BANDWIDTH

- 4. VR ON: 2.00V/div, 20MHz BANDWIDTH

Time/div: 20µs

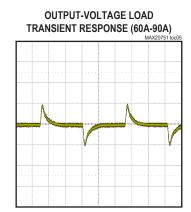

CONDITIONS: TRIGGER ON VOUT, POSITIVE-GOING EDGE 1. VOUT: 50mV/div, 20MHz BANDWIDTH

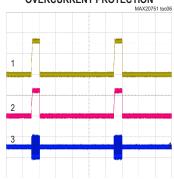

#### **OUTPUT VOLTAGE IN HICCUP-MODE OVERCURRENT PROTECTION**

Time/div: 10ms

CONDITIONS: TRIGGER ON VOUT, NEGATIVE-GOING EDGE

- 1. VOUT: 500mV/div, 20MHz BANDWIDTH

- 2. I<sub>OUT</sub>: 133.3A/div, 20MHz BANDWIDTH

- 3. PWM2: 2.00V/div, 20MHz BANDWIDTH

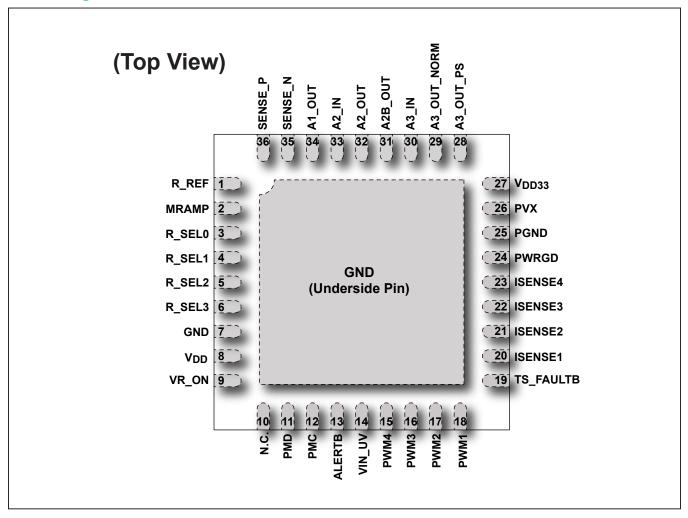

### **Pin Configuration**

### **Pin Description**

| PIN | NAME          | FUNCTION                                                                                                                                                                                       |

|-----|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | R_REF         | Connect the $20k\Omega$ reference resistor R_REF from this pin to ground. The resistor should have $\pm 0.5\%$ tolerance or lower, with a temperature coefficient of $\pm 25$ ppm/°C or lower. |

| 2   | MRAMP         | Connect this node to ground through a resistor to program the PWM regulator modulator ramp rate.                                                                                               |

| 3–6 | R_SEL0-R_SEL3 | Programming Input. Connect these nodes to ground through a configuration resistor with ±1% tolerance or lower and a temperature coefficient of ±100ppm/°C or lower.                            |

| 7   | GND           | Ground                                                                                                                                                                                         |

| 8   | $V_{DD}$      | V <sub>DD</sub> Supply Voltage Connection                                                                                                                                                      |

| 9   | VR_ON         | Input for Regulator to Enable Regulation                                                                                                                                                       |

| 10  | N.C.          | No Connection. This node should not be connected to any other devices or components. It is connected internally.                                                                               |

### **Pin Description (continued)**

| PIN   | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                        |

|-------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11    | PMD               | PMBus Data I/O                                                                                                                                                                                                                                                                                                                  |

| 12    | PMC               | PMBus Clock                                                                                                                                                                                                                                                                                                                     |

| 13    | ALERTB            | Open-Drain, Active-Low PMBus Alert Output                                                                                                                                                                                                                                                                                       |

| 14    | VIN_UV            | Scaled Version of Slave V <sub>DDH</sub> Voltage. A resistor-divider on this input is used to program the input undervoltage lockout (UVLO) threshold for the slave V <sub>DDH</sub> supply.                                                                                                                                    |

| 15–18 | PWM4–PWM1         | Pulse-Width-Modulation Phase-Control Outputs for the Regulator. Connect these nodes to the input pins of the slave devices selected for the application. Connect pins for phases not populated to ground. Do not leave any PWM pin unconnected.                                                                                 |

| 19    | TS_FAULTB         | Temperature Sensor and Slave Fault Flag. Connect this node to the TSENSE outputs of the slave ICs. This node is an analog representation of the junction temperature for the hottest slave of the regulator during normal operation and is also used by the slave devices to report faults (a fault condition is asserted low). |

| 20–23 | ISENSE1-ISENSE4   | Phase Current-Sense Inputs. Connect these nodes to the ISENSE outputs of the slave devices. Ground the pin if not in use (the corresponding RPH resistor should not be connected to ISENSE when ISENSE is connected to ground) to minimize noise into the device.                                                               |

| 24    | PWRGD             | Power-Good Output for the Regulator. This node indicates whether the output voltage is within regulation. This open-drain output should be pulled high externally with a resistor of approximately $10k\Omega$ .                                                                                                                |

| 25    | PGND              | Power Ground. Connect this node to power ground.                                                                                                                                                                                                                                                                                |

| 26    | PVX               | Internal Switcher Switching Node. This node should be connected to an inductor for correct operation.                                                                                                                                                                                                                           |

| 27    | V <sub>DD33</sub> | 3.3V Supply for the IC and Internal Switcher                                                                                                                                                                                                                                                                                    |

| 28    | A3_OUT_PS         | Phase-Shedding Feature (disabled in the MAX20751). This pin must be connected to A3_OUT_ NORM with a short trace or a $0\Omega$ resistor.                                                                                                                                                                                       |

| 29    | A3_OUT_NORM       | Phase Current-Loop Amplifier Output for the Regulator. Must be connected to A3_OUT_PS with a short trace or a $0\Omega$ resistor.                                                                                                                                                                                               |

| 30    | A3_IN             | Phase Current-Loop Amplifier Negative Input                                                                                                                                                                                                                                                                                     |

| 31    | A2B_OUT           | This node has the same value as A2_OUT during normal operation, but has programmable positive and negative voltage clamps that limit the maximum positive and negative output current.                                                                                                                                          |

| 32    | A2_OUT            | Voltage-Loop Amplifier Output                                                                                                                                                                                                                                                                                                   |

| 33    | A2_IN             | Voltage-Loop Amplifier Negative Input                                                                                                                                                                                                                                                                                           |

| 34    | A1_OUT            | Differential Error-Amplifier Output                                                                                                                                                                                                                                                                                             |

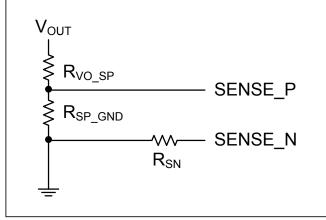

| 35    | SENSE_N           | Negative Remote-Voltage Sense                                                                                                                                                                                                                                                                                                   |

| 36    | SENSE_P           | Positive Remote-Voltage Sense                                                                                                                                                                                                                                                                                                   |

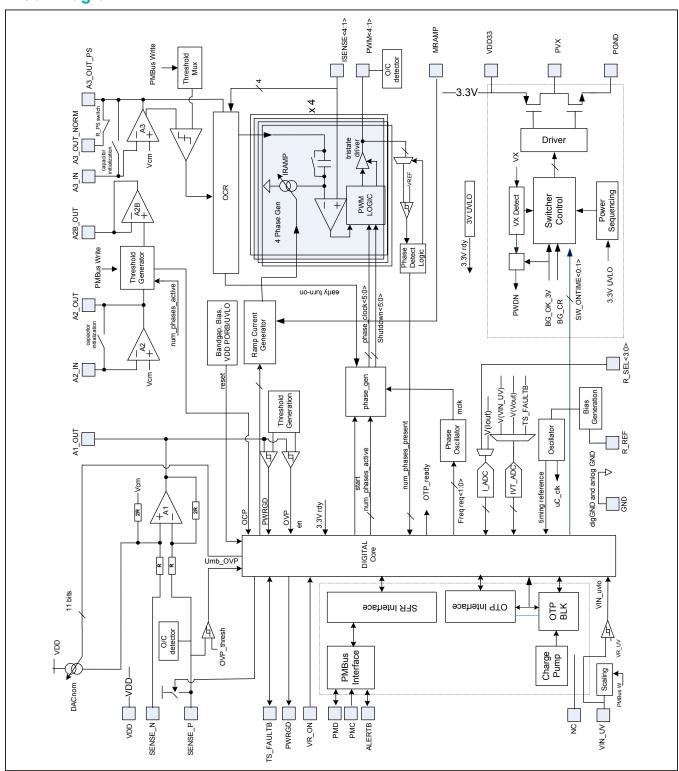

### **Block Diagram**

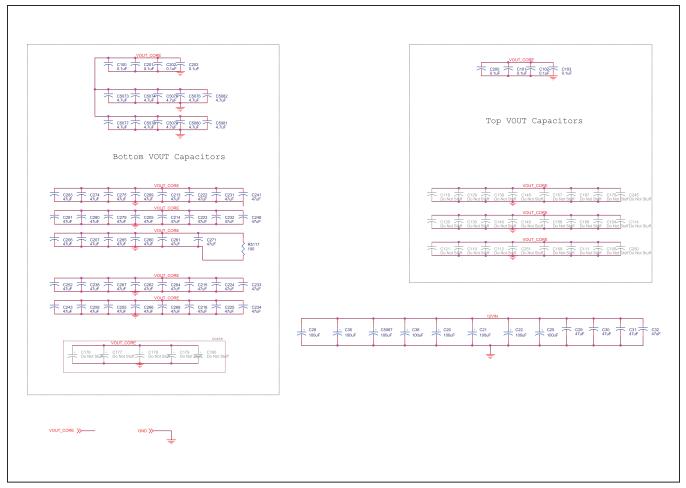

Figure 2. System Efficiency: 4-Phase, 100nH/Phase-Coupled Inductors, 350kHz Switching Frequency ( $V_{IN} = 12V$ )

#### **Theory of Operation**

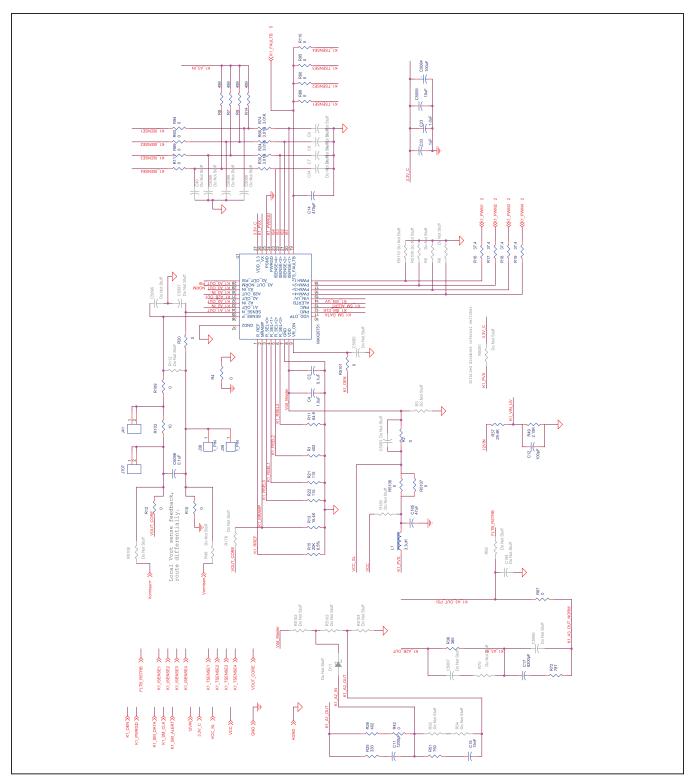

The MAX20751 master IC provides a high-frequency, highly integrated compact solution for high-performance, low-voltage power conversion (with PMBus interface). The basic system architecture consists of a single-rail master controller and up to four smart-slave devices. These ICs, along with a small number of external components, provide a complete solution for single-rail voltage regulation.

The master IC contains a pulse-width-modulation (PWM) control circuit, PMBus interface, and multiphase control circuits for low-loss operation over a wide range of load currents. The applicable smart-slave ICs utilize the full benefits of a synchronous rectification topology. Both the top and bottom power FETs are integrated on-chip, with no external power components (MOSFETs or Schottky diodes) required. Each smart-slave device contains temperature and current monitoring. PWM signals are generated in the master IC and sent to the slaves. Current-sense and temperature feedback signals are generated in the slaves and sent to the master.

The smart-slave ICs have integrated lossless currentsense technology. This current-sense technology provides accurate current information that is not affected by temperature, process variation, or tolerances of passive elements such as the output inductor, resistors and capacitors, and NTCs used in other systems to extract current information. With this approach, a currentsense signal is fed back to the master as a current instead of a voltage, as is the case with DCR and other forms of current sensing. This allows very robust system feedback of current, with better noise immunity than other methods. The current information can be used to control the load line precisely and in the calculation of real output-power measurements. Highly precise current information removes the challenges of meeting load-line specifications, especially at light load, an area known to challenge DCR current sensing due to the low signal levels and tolerances involved.

The output voltage, output-voltage turn-on slew rate, PMBus address, and PMBus output-current gain are hardware programmable using configuration resistors, as discussed in the *Configuration* section.

An internal integrated switching regulator allows creation of the  $V_{DD}$  supply from the  $V_{DD33}$  supply, with the addition of an LC filter.

#### **Control Architecture**

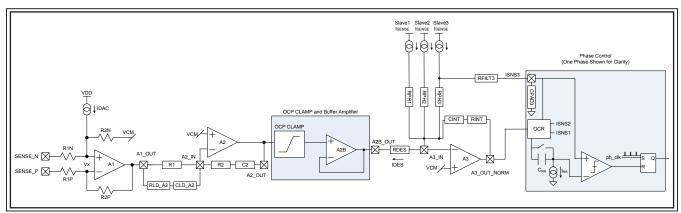

<u>Figure 3</u> shows the internal amplifier stages of the master and how phase-current information is used to generate the phase-control signals, as well as provide accurate current reporting. The master IC contains multiple amplifier stages and one duty-cycle modulator for each phase, to allow independent control of the high-side MOSFET on-time according to each individual phase current.

The first amplifier stage (A1) in Figure 3 is a differential amplifier, the output being the error between the DAC reference voltage and the differential voltage-sense lines multiplied by a factor of 2.19. This stage enables true remote voltage sensing, and its differential structure provides high common-mode rejection ratio to protect from any noise present at the processor ground. The second amplifier stage (A2) provides voltage-loop compensation, with its DC gain used to set the load line of the voltage regulator. The A2 amplifier is followed by a clamping circuit and buffer amplifier (A2B) to provide overcurrent protection (OCP). The output of amplifier A2B is converted to a current through the resistor (RDES) and represents the desired total system current (IDES), which sets the target for the current loop. The third amplifier (A3) acts as a current-error amplifier, as it receives the current command (through RDES) and each individual sensed current from the smart-slave ICs (through resistors RPH1, RPH2, and RPH3, as shown in Figure 3. This stage has an integrator connection. The very large DC gain of the A3 stage guarantees that the total load current equals the current command (IDES) in steady state. As a result, the load line of the voltage regulator is set by the gain of the voltageloop amplifier (A2). Zero load line can be achieved by configuring the amplifier as an integrator by placing capacitor C2 in series with R2, as shown in Figure 3.

The system also offers programmable modulator ramprate stability and noise immunity, set by connecting a resistor between the MRAMP pin and ground. This ramp determines the duty-cycle modulator gain and is used to tune the current-loop compensation.

Loop compensation is implemented by adding series or parallel RC networks across the voltage-loop and current-loop amplifiers (A2 and A3), respectively. For the voltage loop, lead compensation can be added by using a series RC network across the R1 resistor, as shown in Figure 3 (RLD\_A2 and CLD\_A2). Lag compensation can be added by adding a series RC network across the R2-C2 network resistor.

Compensation for the current loop is achieved by placing a series RC network across the current-loop amplifier feedback (R<sub>INT</sub>-C<sub>INT</sub>, in <u>Figure 3</u>). This network provides extremely high gain at low frequency, which guarantees tight current regulation (i.e., the output current is very close to the current command).

### Multiphase Master with PMBus Interface and Internal Buck Converter

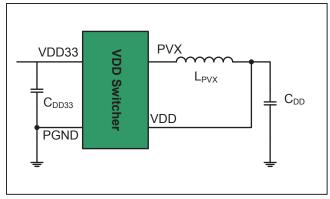

#### Integrated 1.8V Switching Regulator

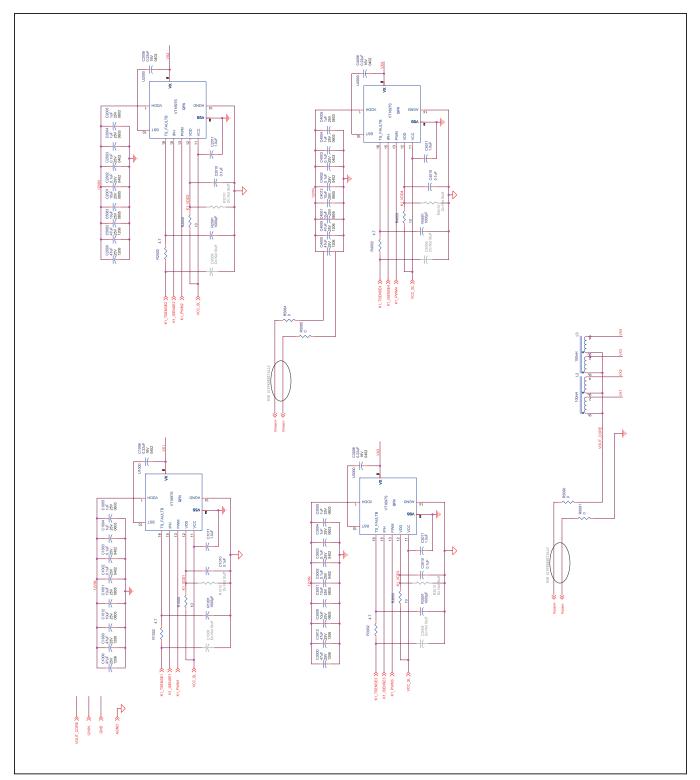

The MAX20751 master IC features an integrated switching regulator that provides the bias current to the master controller and to the smart-slave ICs (both core analog/ digital circuits and gate drive).

This regulator enables efficient power conversion from the 3.3V supply at both light load and heavy load using a pulse-frequency-modulation (PFM) mode of operation. The external LC filter for this regulator is extremely small and inexpensive, as it only requires a chip inductor and small case-size ceramic capacitors. The control scheme adopted here is voltage mode constant on-time with the inductor always operated in the discontinuous-conduction mode (DCM) of operation, providing an inherent currentlimiting protection as well as soft-start capability. Details of the integrated regulator can be seen in the Block Diagram. The PGND pin should connect to the GND pins through a single wide trace or via.

In order to achieve simple average-output current-limiting protection, this converter is forced to stay in DCM mode by only allowing high-side turn-on when the current reaches zero. The peak current in the inductor is given in Equation 1.

#### **Equation 1:**

$$I_{P} = \frac{V_{DD33} - V_{DD}}{L_{PVX}} t_{ON}$$

where:

L<sub>PVX</sub> is the switcher inductor

The maximum average current is given by Equation 2.

#### **Equation 2:**

$$I_{MAX\_AVE} = \frac{V_{DD33} - V_{DD}}{2L_{PVX}} t_{ON}$$

If load current is higher than IMAX\_AVE, the V<sub>DD</sub> voltage drops. If V<sub>DD</sub> drops below the falling UVLO threshold, the device resets.

The on-time (t<sub>ON</sub>) is programmable using the PMBus. Table 1 shows the programmable on-times. Before V<sub>DD</sub> has risen above the rising undervoltagelockout (UVLO) threshold, the lowest on-time of 0.64µs is used. When V<sub>DD</sub> has risen above both the rising and falling UVLO thresholds, the switcher uses the programmed on-time. The default value is 1.30µs.

The switcher becomes active when V<sub>DD33</sub> voltage has risen above its rising UVLO threshold.

The inductor (L<sub>PVX</sub>) must be able to support the maximum peak current without saturating significantly, since the inductor impedance is what provides the current limit. The maximum peak current occurs at startup from zero output voltage.

The output-voltage peak-to-peak ripple depends on the capacitor (C<sub>VDD</sub>). The worst-case ripple occurs at light load and is given in Equation 3.

#### Equation 3:

$$\Delta V_{P-P} = \frac{I_P}{2C_{VDD}} \times \frac{V_{DD33}}{V_{DD}} t_{ON}$$

ΔV<sub>P-P</sub> should be 30mV or less

**Table 1. On-Time Selection Table**

|--|

Figure 3. Control Architecture

Figure 4. Integrated Switcher Circuit

The control method regulates the valley voltage. The peak voltage is the valley voltage plus the peak-to-peak ripple voltage.

The current from the  $V_{DD33}$  supply occurs in pulses of charge given by Equation 4.

#### Equation 4:

$$Q_{VDD33} = \frac{I_P}{2} t_{ON}$$

where:

Ip is the peak current

Capacitor  $C_{DD33}$  at the  $V_{DD33}$  pin should be chosen to supply the peak current and charge without too much voltage change. A ceramic capacitor of at least 10µF is recommended.

To estimate the  $V_{DD33}$  current using the integrated switching regulator, assume a minimum efficiency of 80% for the integrated switching regulator. For example, if the maximum total master and slave IC current from  $V_{DD}$  is 175mA,  $V_{DD}$  = 1.9V, and  $V_{DD33}$  = 3.3V, then the  $V_{DD33}$  current for the integrated switching regulator is (175mA x 1.9V)/(3.3V x 0.80) = 126mA.

To estimate the total  $V_{DD33}$  current, also include the PMBus resistor pulldown current if operated from  $V_{DD33}$ . For example, if 2.15k $\Omega$  pulldown resistors are used from the PMC, PMD, and ALERTB pins to  $V_{DD33}$ , then the maximum PMBus current is 3 x 3.3V/2.15k $\Omega$  = 4.6mA. Therefore, the total  $V_{DD33}$  current for the integrated switching regulator and PMBus is, approximately, 131mA.

The integrated switching regulator can be disabled by removing LPVX and connecting a  $10\Omega$  resistor from PVX to  $V_{DD33}$ . An external supply is then applied to  $V_{DD}$ .

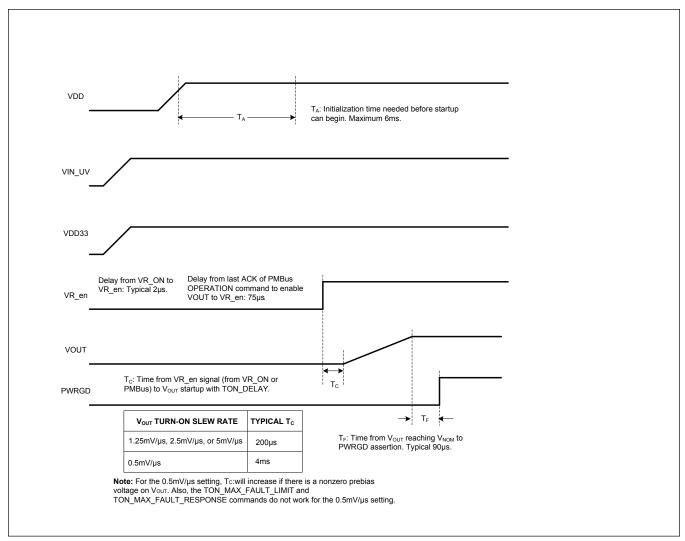

#### **Startup and Shutdown Operation**

When VDD and VDD33 are above their rising UVLO thresholds, the device is enabled and goes through an initialization and phase-detection procedure. Configuration resistors are read and external resistors checked for valid values. Any faults will prevent the output voltage from turning on.

The PMBus communication and telemetry are then enabled. The VIN\_UV voltage must be above its rising UVLO threshold for the output voltage to turn on.

If the output voltage is programmed to below 0.25V through the PMBus VOUT\_COMMAND, the output is disabled. Programming the output voltage to any other allowable voltage using the PMBus VOUT\_COMMAND allows the output voltage to turn on.

Depending on how the voltage-regulation enable is configured, a VR\_en signal from VR\_ON and/or the PMBus OPERATION command may also be required for the output voltage to turn on. The default configuration for the VR\_en signal is the VR\_ON signal at the high logic level, with no PMBus command needed.

When the VIN\_UV voltage is above its rising UVLO threshold and the proper VR\_en signal, if required, has occurred, the output voltage turns on after the PMBus programmable TON\_DELAY time. The default TON DELAY time is 0ms.

After the output voltage has reached its nominal value, the PWRGD signal is asserted.

The startup sequence caused by VR\_ON going high is shown in Figure 5.

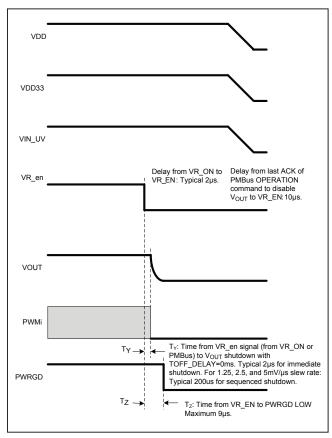

When shutdown occurs, the master IC causes the VX nodes of the slaves to stop switching, which then causes the output voltage to turn off. The PWRGD signal is deasserted and is actively pulled low.

Depending on how the voltage-regulation enable is configured, the output voltage can be turned off using the VR\_en signal from VR\_ON and/or the PMBus OPERATION command. Depending on the PMBus configuration, the output turns off immediately or with sequencing. When the output turns off with sequencing, there is a delay time determined by the PMBus programmable TOFF\_DELAY command and then  $V_{OUT}$  ramps down with a turn-off slew rate that is the same as the turn-on slew rate for turn-on slew rates of  $1.25 \text{mV/}\mu\text{s}$ ,  $2.5 \text{mV/}\mu\text{s}$ , and  $5 \text{mv/}\mu\text{s}$ . For turn-on slew rate  $0.5 \text{mV/}\mu\text{s}$ , if sequencing is used, the delay time is followed by an immediate turn-off (no slew rate-controlled  $V_{OUT}$  ramp-down). The default TOFF\_DELAY time is 0ms. Note that when  $V_{OUT}$  ramps down, energy

Figure 5. Startup Sequence

may be delivered from  $V_{OUT}$  to  $V_{IN}$ . The  $V_{IN}$  capacitors should be sized to absorb this energy to prevent a large increase in the  $V_{IN}$  voltage.

The output voltage can be turned off by programming the output voltage below 0.25V using the PMBus VOUT\_COMMAND. The turn-off in this case is also determined by the PMBus configuration.

If the  $V_{DD}$  or  $V_{DD33}$  supplies go below their falling UVLO thresholds, the output voltage is turned off and the system is reset.

The output voltage can be turned off by the VIN\_UV voltage going below the VIN\_UV falling UVLO threshold. This is logged as a hardware fault.

The VIN\_UV UVLO thresholds should be higher than the corresponding smart-slave IC's  $V_{DDH}$  UVLO thresholds to prevent a slave fault from occurring, which could potentially prevent the output voltage from turning back on. If this occurs, the system may need to be reset by bringing the  $V_{DD}$  or  $V_{DD33}$  supplies below their falling UVLO thresholds.

The shutdown sequence caused by VR\_ON going low is shown in Figure 6.

Figure 6. Shutdown Sequence

#### **Droop and Load-Line Regulation**

If the A2 amplifier series R2-C2 network is replaced by resistor R2 only, the MAX20751 provides accurate output load line over the entire range of output currents. The load line is set by the combination of the R1, R2, and  $R_{\mbox{\scriptsize DES}}$  resistors.

#### Switching Frequency and Output-Voltage Turn-On Slew Rate

The switching frequency and output voltage turn-on slew rate are programmable using configuration resistors. See the <u>Configuration</u> section. They are also programmable using the PMBus.

#### **Orthogonal Current Rebalancing (OCR)**

Phase-current imbalance can occur due to high-frequency loading transients. The purpose of the OCR circuit is to reduce phase-current imbalance.

This is accomplished by modifying the output of the A3 amplifier for each individual phase (k). Instead of the A3 amplifier output voltage being fed directly to the PWM comparator of a phase, a control voltage ( $V_{Ck}$ ) is used. The equation for  $V_{Ck}$  is given in Equation 5.

#### Equation 5:

$$V_{Ck} = V_{O3} - G_{OCR} \left( V_{RPHk} - \frac{1}{N} \sum_{i=1}^{N} V_{RPHi} \right)$$

where:

V<sub>RPHk</sub> = Voltage on resistor RPHk (a voltage proportional to the current in phase k)

$V_{O3} = A3_OUT_NORM$  voltage

N = Total number of phases

G<sub>OCR</sub> = Gain of the OCR circuit

$V_{Ck}$  = Voltage fed to the phase k PWM comparator instead of the A3 amplifier output voltage

The difference between the current of a phase k from the average current (with some gain  $G_{OCR}$ ) is subtracted from  $V_{O3}$  to determine the control voltage ( $V_{Ck}$ ). If the current in any phase is greater than the average of all the phases, then the corresponding  $V_{Ck}$  voltage will be less than  $V_{O3}$  and the subsequent PWM pulse for that phase shorter, thus preventing further phase-current imbalance.

The default gain (GOCR) is 1.8.

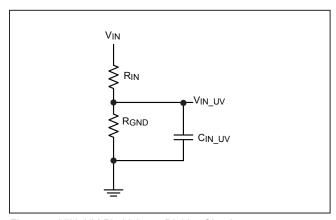

## Input Voltage Undervoltage Lockout (UVLO) Using the VIN\_UV Pin

The VIN\_UV pin on the master IC is connected to the middle point of a voltage-divider from the slave  $V_{DDH}$  (power input rail) to ground. This pin provides an externally programmable input supply UVLO and sensing for the PMBus  $V_{IN}$  telemetry.

The UVLO function is provided by comparing the VIN\_UV voltage to internal references with a comparator. When the  $V_{IN\_UVLO}$  voltage exceeds the rising threshold, the system is allowed to operate and the falling reference voltage is then used as a disable point for built-in hysteresis. See the *Electrical Characteristics* table for more details.

<u>Figure 7</u> shows the VIN\_UV circuit. Resistors  $R_{IN}$  and  $R_{GND}$  form a voltage-divider that scales the  $V_{IN}$  voltage to the VIN\_UV pin. The scale factor (VIN\_RATIO) is given by Equation 6. VIN\_RATIO is programmable using the PMBus. The default value is (140/2048) = 0.06836.

#### Equation 6:

$$VIN\_RATIO = \frac{R_{GND}}{R_{GND} + R_{IN}}$$

$R_{GND}||R_{IN}|$  should be approximately  $2k\Omega$  with capacitor  $C_{IN\_UV}$  = 100pF. It is suggested to use 1% tolerance resistors with the values  $R_{GND}$  = 2.15k $\Omega$  and  $R_{IN}$  = 29.4k $\Omega$ . The value for VIN\_RATIO should be less than or equal to 140/2048.

#### **Phase Population Order**

Depending on the total number of phases in the system, specific phase positions must be populated, while the others must be deactivated by connecting a  $0\Omega$  resistor between the MAX20751's phase-control pins (PWMk) of the inactive phases and ground (Table 2).

The phase number is defined by the PWMx pin name (e.g., phase 2 is driven by PWM2).

Figure 7. VIN\_UV Pin Voltage-Divider Circuit

#### **Table 2. Phase Population Positions**

| NUMBER OF POPULATED PHASES | POSITIONS TO BE POPULATED (BY FIRING SEQUENCE) |

|----------------------------|------------------------------------------------|

| 1                          | 2                                              |

| 2                          | 2, 1                                           |

| 3                          | 2, 1, 3                                        |

| 4                          | 2, 4, 1, 3                                     |

For example, for 2-phase operation, only phases 2 and 1 are used; therefore, pins PWM4 and PWM3 should each be connected to GND with  $0\Omega$  resistors.

For 3-phase operation, PWM4 should be connected to GND with a  $0\Omega$  resistor. For single-phase operation PWM4, PWM3, and PWM1 should each be connected to GND with  $0\Omega$  resistors.

If the wrong PWMk pins are connected to GND with  $0\Omega$  resistors, a configuration fault occurs in the fault-checking procedure (occurring prior to  $V_{OUT}$  startup) and operation is halted.

#### **Protection And Monitoring**

The master IC includes multiple protection circuits to protect the regulator and load, and to monitor the output voltage, as described in the following sections.

## Fault Detection when V<sub>DD</sub> and V<sub>DD33</sub> are Initially Applied

When  $V_{DD}$  and  $V_{DD33}$  are initially applied and at their proper levels, the master IC checks the following resistor values and connections and if detected as being outside the correct range or open, an error is flagged and the regulator will not start regulation:

- RMRAMP

- RRFF

- SENSE P Open

#### **PWRGD (Power-Good) Pin**

The PWRGD output (different from the PMBus POWER\_GOOD signal) is an active-high, open-drain output used to show that the output is settled at its commanded voltage. The output goes high after a fixed delay, after the end of the output-voltage startup transition, assuming the output voltage is above the PWRGD threshold. It is deasserted when any of the following occurs:

- The output voltage drops below the threshold, relative to the nominal voltage, for any reason.

- An OVP fault is detected.

- An OCP fault is detected when the mode is set to hiccup mode and the regulator shuts down the output voltage during the shutdown part of the hiccup cycle. In constant current-limit mode, the PWRGD signal is based on the PWRGD voltage threshold only.

- The output is disabled.

#### **Overcurrent Protection (OCP)**

System OCP is based on a fixed voltage threshold for the voltage across the  $R_{DES}$  resistor. The overcurrent threshold is therefore set by selecting an appropriate value of  $R_{DES}$  for the design. The voltage threshold is scaled internally, depending on the number of active phases (i.e., the voltage threshold is a fixed per-phase value).

The OCP trips when the peak voltage over RDES reaches the inception value and remains tripped down to the nominal/sustaining value (i.e., the values shown are the sustaining currents and not the inception point, which is 5% higher). Negative (sinking) OCP is automatically set to 30% of the positive value.

The OCP is based on the instantaneous voltage over RDES, and a small ripple voltage reflecting the output-voltage ripple may be present. If the instantaneous commanded current (output of amplifier A2) reaches the inception voltage, the commanded current is immediately clamped to the sustaining value. If the commanded current drops below the sustaining value, it must once again reach the inception point before clamping commences.

An overcurrent fault is logged in the fault log if clamping continues for 5ms, to ensure that only periods of continuous overloads are recorded as faults.

**Table 3. Master Faults**

| MAX20751<br>PROTECTION                       | MAX20751 OUTPUT<br>SIGNAL(S) SHOWING FAULT  | SYSTEM<br>SHUTDOWN    | SYSTEM<br>LATCHED OFF?  | LOGGED IN FAULT LOG? |

|----------------------------------------------|---------------------------------------------|-----------------------|-------------------------|----------------------|

| Resistor Out-of-Range<br>Detected at Startup | PWRGD low                                   | System does not start | Yes                     | Yes                  |

| OCP: Hiccup or CCM                           | PWRGD low (if output drops below threshold) | No                    | No                      | Yes<br>(after 5ms)   |

| Fixed (Umbrella) or<br>Tracking OVP          | PWRGD low                                   | Yes                   | Yes                     | Yes                  |

| VIN_UV UVLO                                  | PWRGD low (if output drops below threshold) | Yes                   | No                      | Yes                  |

| Output Undervoltage                          | PWRGD low                                   | No                    | No                      | No                   |

| V <sub>DD</sub> UVLO                         | PWRGD low                                   | Yes                   | No<br>(system in reset) | No                   |

| V <sub>DD33</sub> UVLO                       | PWRGD low                                   | Yes                   | No (system in reset)    | No                   |

#### **Table 4. Effects of Slave Faults**

| SLAVE FAULT                                                           | MAX20751 OUTPUT SIGNAL<br>SHOWING FAULT | SYSTEM<br>SHUTDOWN | SYSTEM<br>LATCHED OFF* | LOGGED IN<br>FAULT LOG |

|-----------------------------------------------------------------------|-----------------------------------------|--------------------|------------------------|------------------------|

| Slave Cycle-by-Cycle OCP<br>(Sinking or Sourcing Current)             | None                                    | No                 | No                     | Yes                    |

| Slave Sourcing OCP<br>Current Shutdown                                | PWRGD low                               | Yes                | Yes<br>(through slave) | Yes                    |

| Slave OTP Shutdown (Sent to<br>Master through Slave TS_FAULTB<br>Low) | PWRGD low                               | Yes                | Yes<br>(through slave) | Yes                    |

| Slave Boost UVLO (Undervoltage Lockout on Boost Supply)               | PWRGD low                               | Yes                | No                     | Yes                    |

| Slave VX Short-to-Ground or V <sub>DDH</sub>                          | PWRGD low                               | Yes                | Yes (through slave)    | Yes                    |

\*Note: "Yes (through slave)" refers to the fact that the slave latches in this condition and therefore the system latches. Once the slave fault is cleared by cycling its power, the system can restart. This table shows the effect on the system.

Three modes of operation are provided for positive (sourcing) OCP: shutdown, constant current, and hiccup (default); negative OCP is always constant current. The mode can be changed using PMBus commands. If hiccup OCP mode is selected, when the OCP is exceeded, the system will deliver the maximum programmed sustaining current for 5ms before shutting down and waiting 45ms before restarting. This cycling continues until the commanded current falls below the programmed value. Should constant-current mode be selected, the system tries to regulate at the OCP sustaining current until the commanded current falls below the sustaining value. The upper threshold of current delivery is the OCP inception point and, once this level is reached, the system folds back to the sustaining level (the programmed value) to deliver constant current indefinitely. The shutdown mode is similar to the constant-current mode but shuts down VOUT after 5ms. The VOUT voltage can be enabled again by using the VR ON signal and/or the OPERATION PMBus command.

#### Overvoltage Protection (OVP)

Two separate OVP circuits are included, one based on the programmed nominal output voltage, the other on an "umbrella" fixed value. If either is tripped, an OVP fault is recorded, PWRGD is deasserted, and the system stops regulating. OVP faults can only be cleared by toggling the  $V_{DD}$  or  $V_{DD33}$  supply rail.

#### **Undervoltage Lockout**

The master IC includes three UVLO circuits,  $V_{DD}$  rail,  $V_{DD33}$  rail and  $V_{DDH}$  (i.e.,  $V_{IN}$ ).  $V_{IN}$  is monitored through an external resistor-divider to bring the voltage down to within the operating range of the VIN\_UV pin. If a  $V_{IN}$  UVLO is detected, the system stops regulating and indicates an input-voltage fault. Once the input voltage rises above the rising threshold, the IC reinitiates and follows the same startup procedure as if enabled by VR ON.

### Configuration

## **Determining the Optimum Number of Phases, IOUTMAX**, and **Overcurrent Protection**

The typical starting point for a voltage-regulator design is to choose a value of maximum output current (I<sub>OUTMAX</sub>). The value of I<sub>OUTMAX</sub> is determined by the MAX20751 system overcurrent-protection (OCP) setting and is set to 85% of this setting. Therefore, a target minimum system OCP rating can easily be determined based on I<sub>OUTMAX</sub>. Once this value is known, the area available, smart-slave part numbers to be used, and the desired performance

Table 5. Selection of R<sub>DES</sub> for Overcurrent Limit and Maximum Output Current I<sub>OUTMAX</sub> = 0.85 I<sub>OCP</sub>

| 1-PHASE OCP (A) | 2-PHASE OCP (A) | 3-PHASE OCP (A) | 4-PHASE OCP (A) | R <sub>DES</sub> (Ω) |

|-----------------|-----------------|-----------------|-----------------|----------------------|

| 25              | 50              | 75              | 100             | 604                  |

| 27.3            | 54.7            | 82              | 109.3           | 549                  |

| 29.7            | 59.3            | 89              | 118.6           | 511                  |

| 32              | 64              | 96              | 128             | 464                  |

| 34.3            | 68.6            | 103             | 137.3           | 432                  |

| 36.7            | 73.3            | 110             | 146.6           | 412                  |

| 39              | 78              | 116.9           | 155.9           | 383                  |

| 41.3            | 82.6            | 123.9           | 165.2           | 365                  |

| 43.6            | 87.3            | 130.9           | 174.6           | 340                  |

| 46              | 91.9            | 137.9           | 183.9           | 324                  |

| 48.3            | 96.6            | 144.9           | 193.2           | 309                  |

| 50.6            | 101.3           | 151.9           | 202.5           | 294                  |

| 53              | 105.9           | 158.9           | 211.8           | 280                  |

| 55.3            | 110.6           | 165.9           | 221.2           | 274                  |

| 57.6            | 115.2           | 172.9           | 230.5           | 261                  |

| 60              | 119.9           | 179.9           | 239.8           | 249                  |

versus cost should all be considered, with the number of phases and smart-slave devices determined. Efficiency curves and ratings shown on the respective smart-slave data sheets can be used for this purpose. If any phases aren't used, their corresponding PWMx pins should be connected to GND with  $0\Omega$  resistors, as discussed in the  $Phase\ Population\ Order\ section.$

#### Selecting R<sub>DES</sub>

With the number of phases and part numbers known,  $R_{DES}$  should be selected to give the correct overcurrent-protection (OCP) value. The OCP value is set by  $R_{DES}$ , in that the master IC uses a fixed value of 150mV per phase. Since  $R_{DES}$  is also used by

Table 6. Using R\_SEL3 to Set the V<sub>OUT</sub> Slew Rate and Switching Frequency

| V <sub>OUT</sub> SLEW RATE (V/ms) | f <sub>SW</sub> (kHz) | R_SEL3 (Ω) |

|-----------------------------------|-----------------------|------------|

|                                   | 300                   | 0          |

|                                   | 350                   | 17.8       |

|                                   | 400                   | 33.2       |

| 1.25                              | 450                   | 48.7       |

| 1.25                              | 500                   | 64.9       |

|                                   | 600                   | 80.6       |

|                                   | 700                   | 95.3       |

|                                   | 800                   | 115        |

|                                   | 300                   | 133        |

|                                   | 350                   | 154        |

|                                   | 400                   | 178        |