### NXP Semiconductors

Data sheet: Technical data

## Programmable solenoid controller

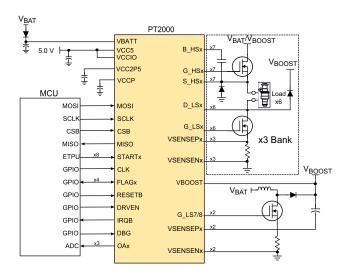

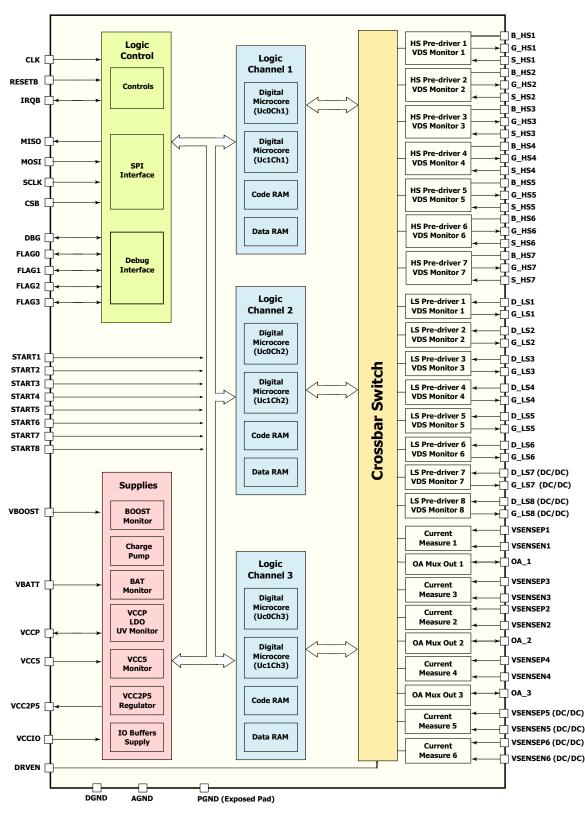

The PT2000 is a SMARTMOS programmable gate driver IC for precision solenoid control applications, which makes the component very flexible and relieves the main microcontroller from the heavy task of the actuator control. The chip integrates six microcores used to control, seven external MOSFET high-side pre-drivers, eight external MOSFET low-side pre-drivers (two of them with higher switching frequency can be used for DC/DC converters), an integrated end of injection detection, six current measurements, and diagnostics for both the high-side and low-side.

PT2000 includes two internal regulators with overvoltage and undervoltage monitoring and protection, V<sub>CCP</sub> fed from the battery line supplying the pre-driver section and V<sub>CC2P5</sub> fed from an external 5.0 V generating supply for the digital block.

Interface with the MCU is achieved via serial peripheral interface (SPI) and 16 configurable I/O signals. I/O are supplied by an external 3.3 V or 5.0 V regulator connected to  $V_{CCIO}$ .

These features along with cost effective packaging, make the PT2000 ideal for power train engine control applications.

#### Features

- Battery voltage range, 5.0 V < V<sub>BATT</sub> < 72 V</li>

- · Battery and boost voltage monitoring

- Pre-drive operating voltage up to 72 V

- · Seven high-side/ eight low-side pre-drive PWM capability up to 100 kHz-30 nC

- All pre-drivers have four selectable slew rates

- Eight selectable, pre-defined V<sub>DS</sub> monitoring thresholds

- · Measurement function for end of injection detection

- Encryption for microcode protection

- Integrated 1.0 MHz back-up clock

## PT2000

#### PROGRAMMABLE SOLENOID CONTROLLER

#### Applications

- Automotive (12 V), truck and industrial (24 V) power train

- Diesel and gasoline direct injection (three banks)

- Transmission

- Valve control

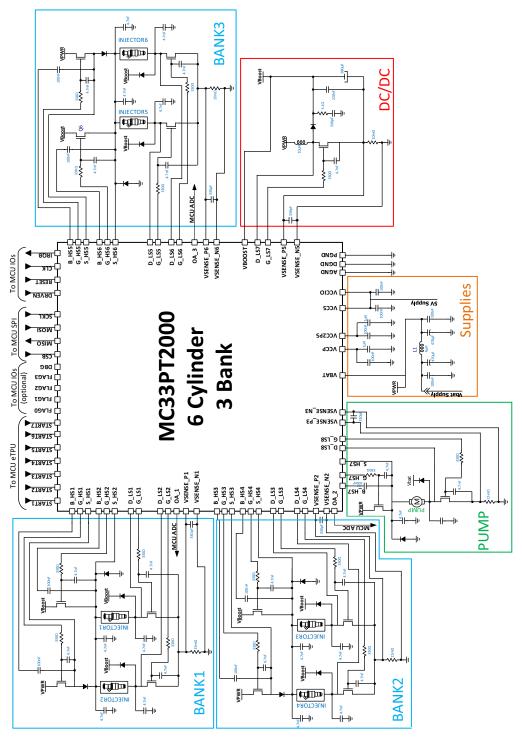

Figure 1. PT2000 simplified application diagram

# **Table of Contents**

| 1 | Orde  | able parts      |                                                         | 4  |

|---|-------|-----------------|---------------------------------------------------------|----|

|   | 1.1   | Cipher key .    |                                                         | 4  |

| 2 | Inter | al block diagr  | am                                                      | 5  |

| 3 | Pin o | onnections      |                                                         | 6  |

| 4 | Fund  | ional descript  | ion                                                     | 10 |

|   | 4.1   | Introduction    | ······································                  | 10 |

|   | 4.2   | Features        | ······································                  | 10 |

| 5 | Elec  | rical character | istics                                                  | 11 |

|   | 5.1   | Maximum rat     | tings                                                   | 11 |

|   | 5.2   | Power supply    | y electrical characteristics                            | 13 |

|   | 5.3   | High-side pre   | e-driver electrical characteristics                     | 16 |

|   | 5.4   | Low-side (LS    | 31-LS6) pre-driver electrical characteristics           | 17 |

|   | 5.5   | Low-side hig    | h-speed (LS7-LS8) pre-driver electrical characteristics | 19 |

|   | 5.6   | High-side VD    | OS VSRC monitoring electrical characteristics           | 20 |

|   | 5.7   | Low-side VD     | S VSRC monitoring electrical characteristics            | 22 |

|   | 5.8   | Load bias ele   | ectrical characteristics                                | 23 |

|   | 5.9   | Current measure | surement electrical characteristics                     | 24 |

|   |       | 5.9.1 Current   | t measurement for positive current                      | 24 |

|   |       | 5.9.2 Current   | t measurement for negative currents                     | 26 |

|   | 5.10  | Analog outpu    | It (OAx) electrical characteristics                     | 28 |

|   | 5.11  | Clock / PLL e   | electrical characteristics                              | 29 |

|   | 5.12  |                 | output electrical characteristics                       |    |

|   | 5.13  |                 | eral interface electrical characteristics               |    |

| 6 | Fund  |                 | scription                                               |    |

|   | 6.1   |                 | ies                                                     |    |

|   |       |                 |                                                         |    |

|   |       |                 | • • • • • • • • • • • • • • • • • • • •                 |    |

|   |       |                 | 25 regulator                                            |    |

|   |       |                 | 25 regulator                                            |    |

|   |       |                 | regulator                                               |    |

|   |       | -               | voltage monitor                                         |    |

|   |       |                 | roltage monitor                                         |    |

|   |       | •               | pump                                                    |    |

|   | 6.2   | •               | stem                                                    |    |

|   | 6.3   | •               | e-driver                                                |    |

|   |       | •               | de pre-driver slew rate control                         |    |

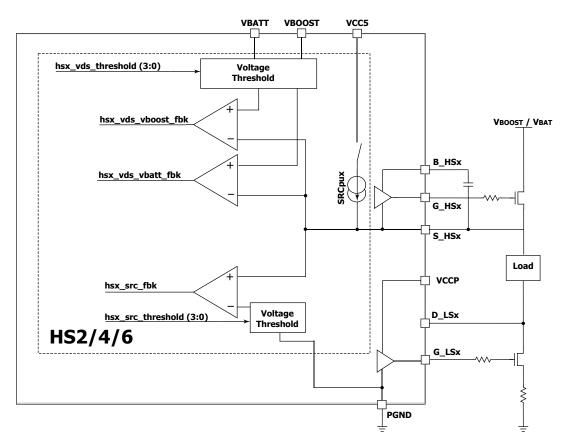

|   |       |                 | ate of high-side pre-driver                             |    |

|   | 6.4   | •               | OS and VSRC monitor                                     |    |

|   |       |                 | , 5, 7 VDS monitoring                                   |    |

|   |       |                 | , 6 VDS monitoring                                      |    |

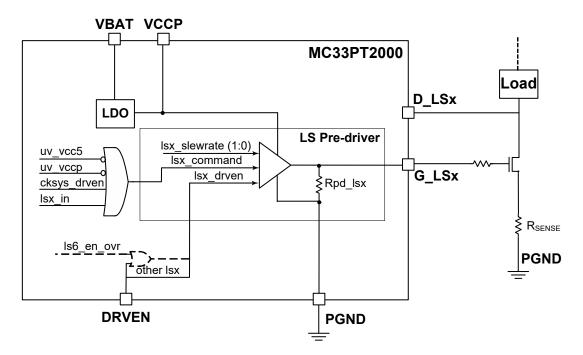

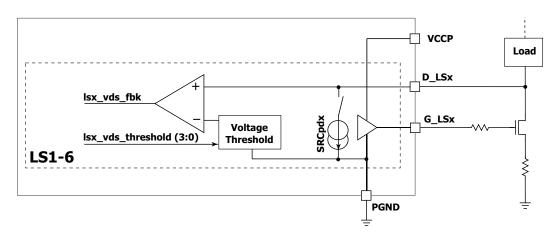

|   | 6.5   |                 | -driver (LS1-6)                                         |    |

|   |       |                 | de pre-driver slew rate control                         |    |

|   |       |                 | S6 VDS monitor                                          |    |

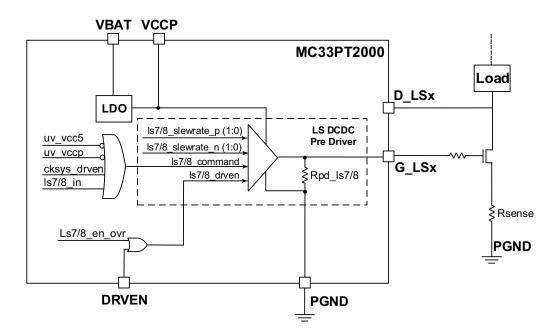

|   | 6.6   |                 | -driver for DC/DC converter (LS7 and LS8)               |    |

|   |       |                 | de pre-driver slew rate control (LS7 and LS8)           |    |

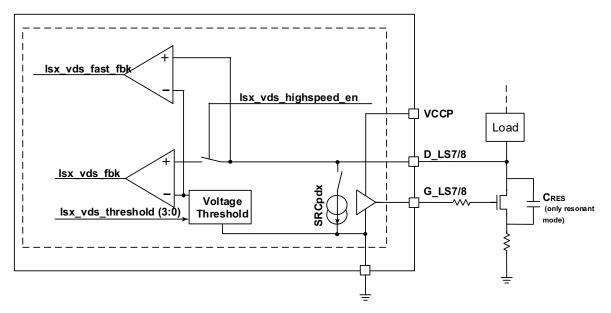

|   |       | 6.2 Low-sid     | de VDS monitor D_Is7/D_Is8 for DC/DC                    | 48 |

|    | 6.7   | Current measurement                                                  | -9         |

|----|-------|----------------------------------------------------------------------|------------|

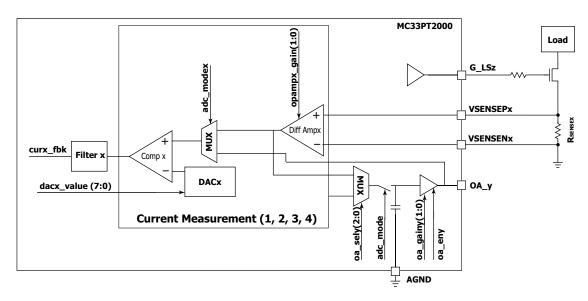

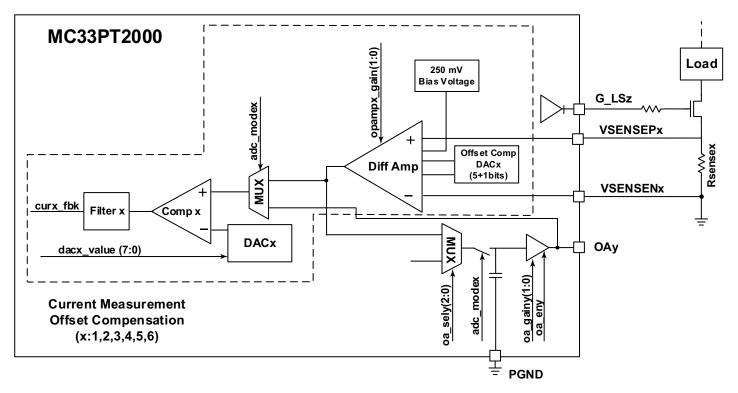

|    |       | 6.7.1 General purpose current measurement block 4                    | 9          |

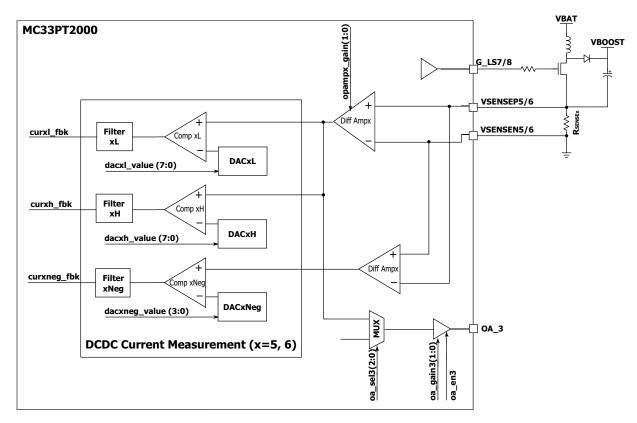

|    |       | 6.7.2 Current measurement for DC/DC 5                                | 52         |

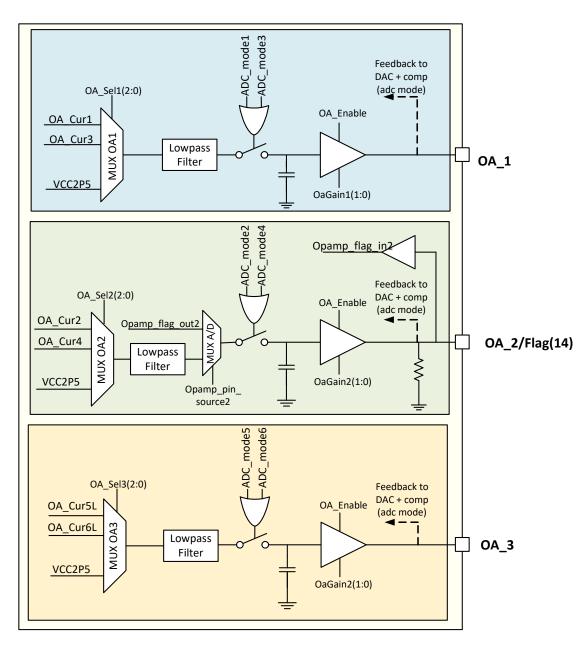

|    | 6.8   | OA_x output pins, multiplexer and T & H 5                            | 3          |

|    |       | 6.8.1 General features                                               | ;3         |

|    |       | 6.8.2 OA_2 Pin digital I/O function                                  | 5          |

|    |       | 6.8.3 OAx output offset and offset error 5                           | 6          |

| 7  | Fund  | tional device operation                                              | 57         |

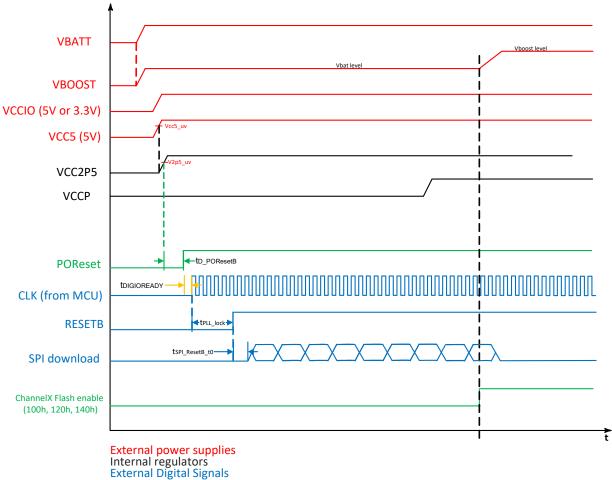

|    | 7.1   | Power-up/down sequence                                               | 57         |

|    |       | 7.1.1 Power-up sequence of VCC5, VCC2P5, and reset 5                 | 57         |

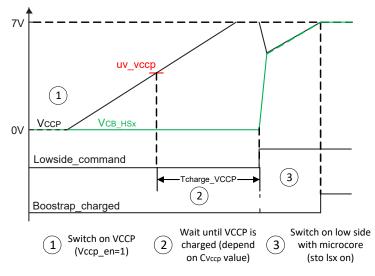

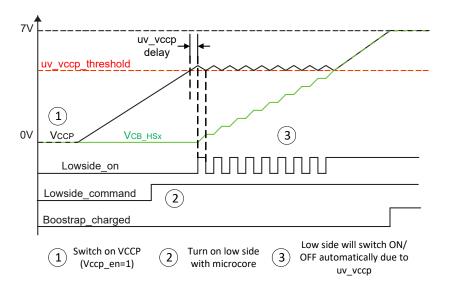

|    |       | 7.1.2 Power-up sequence VCCP and bootstrap capacitors 5              | 8          |

|    | 7.2   | DC/DC converter control (LS7/8) 6                                    | <b>i</b> 1 |

|    |       | 7.2.1 General description                                            | <b>i1</b>  |

|    | 7.3   | Device clock manager and PLL init                                    | 3          |

|    | 7.4   | SW initialization flow                                               | 63         |

|    |       | 7.4.1 Power supply, reset, and clock                                 | 3          |

|    |       | 7.4.2 SPI configuration                                              | <b>j</b> 4 |

|    |       | 7.4.3 Clock monitor, flash enable, and DrvEn                         | <b>54</b>  |

|    | 7.5   | BIST                                                                 | <b>j</b> 4 |

|    |       | 7.5.1 MBIST                                                          | i5         |

|    |       | 7.5.2 LBIST                                                          | i5         |

|    | 7.6   | Reset sources                                                        | 5          |

|    | 7.7   | Cipher unit                                                          | 6          |

|    | 7.8   | Ground connections                                                   | 6          |

|    | 7.9   | Shutoff path via the DrvEn pin                                       | 6          |

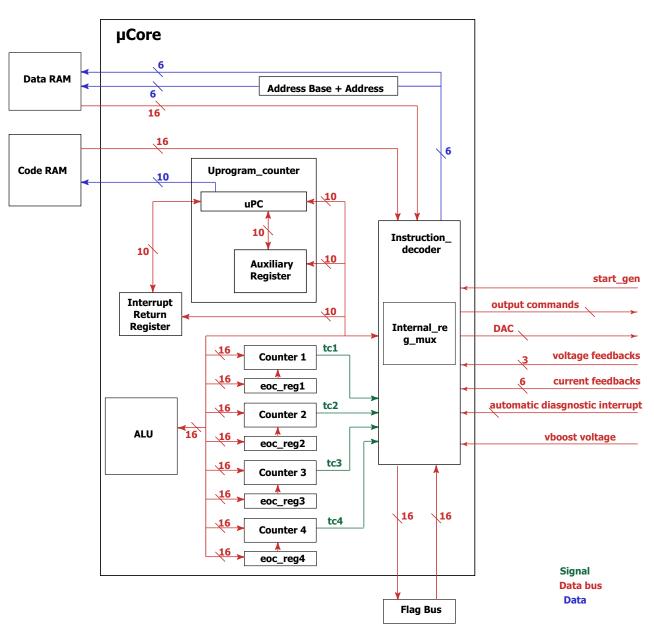

| 8  | Digit | al core                                                              | 8          |

|    | 8.1   | Logic channels description                                           | 8          |

|    |       | 8.1.1 Microcores                                                     | ;9         |

|    |       | 8.1.2 Dual microcore arbiter                                         | 0'         |

|    |       | 8.1.3 Signature unit                                                 | '2         |

|    |       | 8.1.4 SPI backdoor                                                   | '2         |

|    |       | 8.1.5 CRAM                                                           | '3         |

|    |       | 8.1.6 DRAM                                                           | '3         |

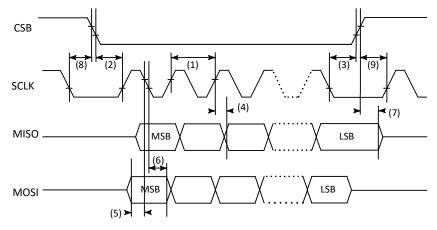

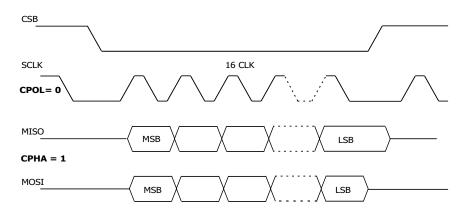

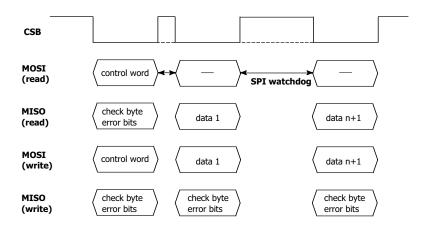

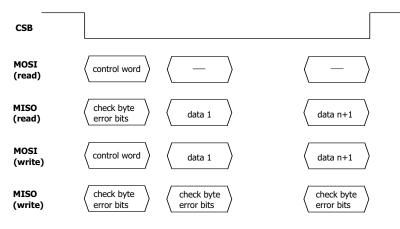

|    | 8.2   | Serial peripheral interface                                          | '4         |

|    |       | 8.2.1 SPI read access                                                | '5         |

|    |       | 8.2.2 SPI write access                                               | '6         |

|    |       | 8.2.3 SPI protocol                                                   | '7         |

|    | 8.3   | SPI address map                                                      | '9         |

|    |       | 8.3.1 Selection register (3FFh) 8                                    | 9          |

|    |       | 8.3.2 Configuration register 9                                       | 90         |

|    |       | 8.3.3 IO configuration registers                                     | 0          |

|    |       | 8.3.4 Main configuration registers                                   | 7          |

|    |       | 8.3.5 Diagnostics configuration registers                            | 2          |

| 9  | Турі  | cal applications                                                     | 9          |

|    | 9.1   | Application diagram: 3 bank, 6 cylinder with DC/DC 13                | 9          |

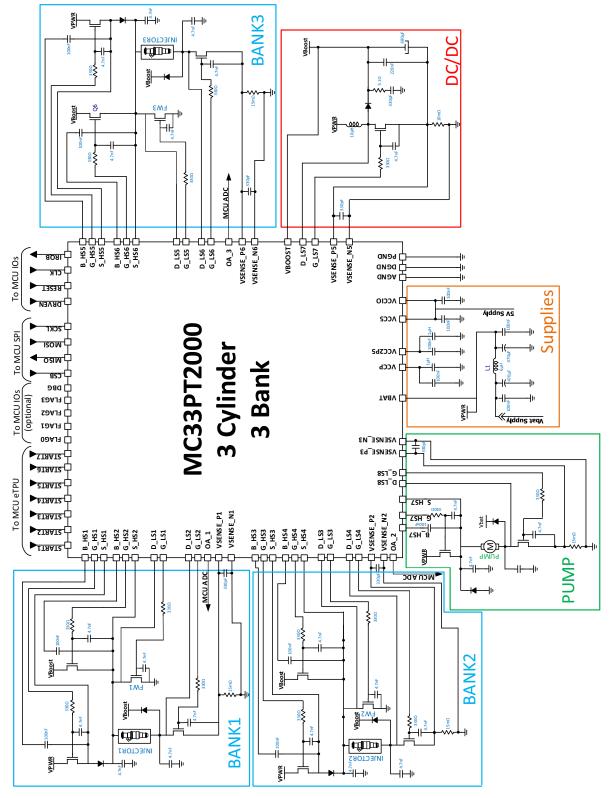

|    | 9.2   | Application diagram: 3 bank, 3 cylinder (full overlap) with DC/DC 14 | 0          |

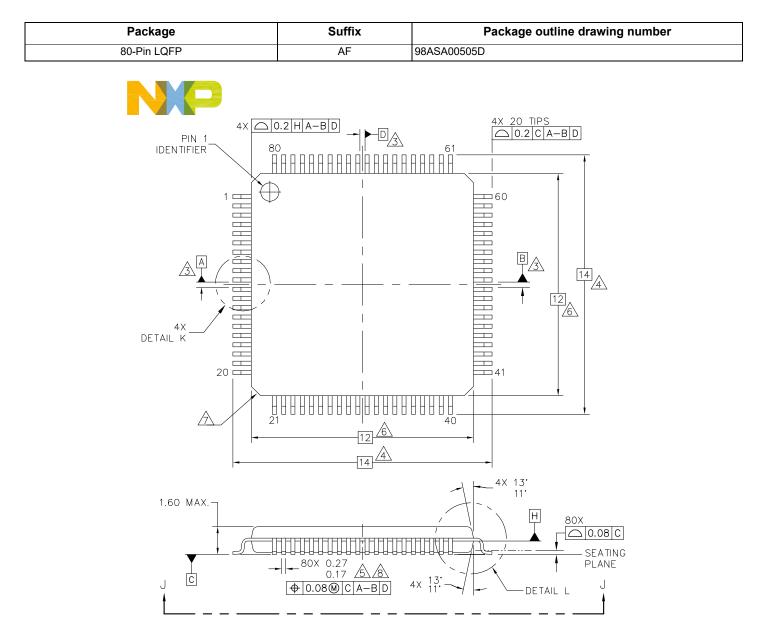

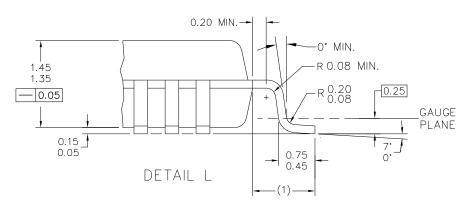

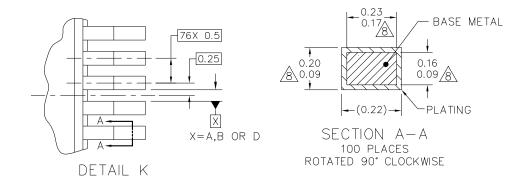

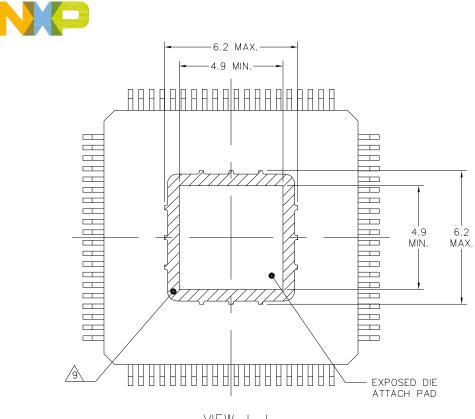

| 10 | Pac   | xaging                                                               | 1          |

|    | 10.1  | Package mechanical dimensions                                        | 1          |

| 11 | Refe  | rence section                                                        | -5         |

| 10 | Revi  | sion history                                                         | 6          |

# 1 Orderable parts

#### Table 1. Orderable part variations

| Part number                 | Temperature (T <sub>A</sub> ) | Package                      |

|-----------------------------|-------------------------------|------------------------------|

| MC33PT2000AF <sup>(1)</sup> | -40 °C to 125 °C              | 80-pin LQFP with exposed pad |

Notes

1. To order parts in tape and reel, add the R2 suffix to the part number.

## 1.1 Cipher key

Contact a NXP sales representative to obtain devices with a specific encryption key and the associated code encryptor.

## 2 Internal block diagram

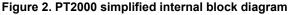

## 3 Pin connections

Figure 3. PT2000 pin connections

Functional descriptions of many of these pins can be found in the Functional block description section beginning on page 34.

| Table 2. | PT2000 | pin definitions | (2), (3), (4) |

|----------|--------|-----------------|---------------|

|----------|--------|-----------------|---------------|

| Pin | Pin name | Pin function | Pull configuration    | Definition                           |

|-----|----------|--------------|-----------------------|--------------------------------------|

| 1   | DRVEN    | Input        | Weak PD               | Driver enable input                  |

| 2   | RESETB   | Input        | Weak PU               | Reset pin                            |

| 3   | START1   | Input/output | PU/PD<br>Configurable | Trigger pin actuator 1 / Flag_bus(5) |

| 4   | START2   | Input/output | PU/PD<br>Configurable | Trigger pin actuator 2 / Flag_bus(6) |

| 5   | START3   | Input/output | PU/PD<br>Configurable | Trigger pin actuator 3 / Flag_bus(7) |

| 6   | START4   | Input/output | PU/PD<br>Configurable | Trigger pin actuator 4 / Flag_bus(8) |

| 7   | START5   | Input/output | PU/PD<br>Configurable | Trigger pin actuator 5 / Flag_bus(9) |

### Table 2. PT2000 pin definitions <sup>(2), (3), (4)</sup>(continued)

| Pin | Pin name | Pin function | Pull configuration    | Definition                                                                                |

|-----|----------|--------------|-----------------------|-------------------------------------------------------------------------------------------|

| 8   | START6   | Input/output | PU/PD<br>Configurable | Trigger pin actuator 6 / Flag_bus(10)                                                     |

| 9   | START7   | Input/output | PU/PD<br>Configurable | Trigger pin actuator 7 / Flag_bus(11)                                                     |

| 10  | FLAG 0   | Input/output | Weak PD               | Flag_bus(0) (general purpose I/O)/command for external free-wheeling MOSFTET pre-driver 1 |

| 11  | FLAG 1   | Input/output | Weak PD               | Flag_bus(1) (general purpose I/O)/command for external free-wheeling MOSFTET pre-driver 2 |

| 12  | FLAG 2   | Input/output | Weak PD               | Flag_bus(2) (general purpose I/O)/command for external free-wheeling MOSFTET pre-driver 3 |

| 13  | FLAG 3   | Input/output | Weak PD               | Flag_bus(3) (general purpose I/O)/command for external free-wheeling MOSFTET pre-driver 4 |

| 14  | CSB      | Input        | PU                    | SPI chip select                                                                           |

| 15  | MOSI     | Input        | Weak PU               | SPI slave input                                                                           |

| 16  | MISO     | Output       | _                     | SPI slave output                                                                          |

| 17  | SCLK     | Input        | Weak PU               | SPI clock                                                                                 |

| 18  | VCCIO    | Input        | _                     | Digital I/O voltage supply 3.3 V or 5.0 V (supplied externally)                           |

| 19  | DBG      | Input/output | Weak PU               | Debug port / Flag_bus (15)                                                                |

| 20  | DGND     | Ground       | _                     | Digital ground                                                                            |

| 21  | VCC2P5   | Output       | _                     | Internal 2.5 V voltage regulator decoupling                                               |

| 22  | VCC5     | Input        | _                     | Power supply 5.0 V (supplied externally)                                                  |

| 23  | AGND     | Ground       | _                     | Analog ground                                                                             |

| 24  | VSENSEN4 | Input/output | PU/PD<br>Configurable | Current sense input comparator - / Start8 / Flag(12)                                      |

| 25  | VSENSEP4 | Input/output | Weak PD               | Current sense input comparator + /Flag(4) (general purpose I/O)                           |

| 26  | VSENSEN1 | Input        | _                     | Current sense input comparator 1 -                                                        |

| 27  | VSENSEP1 | Input        | _                     | Current sense input comparator 1 +                                                        |

| 28  | VSENSEN2 | Input        | _                     | Current sense input comparator 2 -                                                        |

| 29  | VSENSEP2 | Input        | _                     | Current sense input comparator 2 +                                                        |

| 30  | VSENSEN3 | Input        | _                     | Current sense input comparator 3 -                                                        |

| 31  | VSENSEP3 | Input        | _                     | Current sense input comparator 3 +                                                        |

| 32  | VSENSEN5 | Input        | _                     | DC-DC current sense input comparator -                                                    |

| 33  | VSENSEP5 | Input        |                       | DC-DC current sense input comparator +                                                    |

| 34  | VSENSEN6 | Input        | _                     | DC-DC current sense input comparator -                                                    |

| 35  | VSENSEP6 | Input        | _                     | DC-DC current sense input comparator +                                                    |

| 36  | OA_1     | Output       | -                     | Analog output 1                                                                           |

| 37  | OA_2     | Input/output | Weak PD               | Analog output 2/Flag_bus (14)                                                             |

| 38  | OA_3     | Output       | _                     | Analog output 3                                                                           |

| 39  | D_LS8    | Input        | _                     | Drain pin low-side MOSFET for DC/DC converter                                             |

| 40  | D_LS7    | Input        | _                     | Drain pin low-side MOSFET for DC/DC converter                                             |

| 41  | D_LS6    | Input        | _                     | Drain pin low-side MOSFET actuator 6                                                      |

| 42  | D_LS5    | Input        | _                     | Drain pin low-side MOSFET actuator 5                                                      |

### Table 2. PT2000 pin definitions <sup>(2), (3), (4)</sup>(continued)

| Pin | Pin name | Pin function | Pull configuration | Definition                                                                                                |

|-----|----------|--------------|--------------------|-----------------------------------------------------------------------------------------------------------|

| 43  | D_LS4    | Input        | _                  | Drain pin low-side MOSFET actuator 4                                                                      |

| 44  | D_LS3    | Input        | _                  | Drain pin low-side MOSFET actuator 3                                                                      |

| 45  | D_LS2    | Input        | _                  | Drain pin low-side MOSFET actuator 2                                                                      |

| 46  | D_LS1    | Input        | _                  | Drain pin low-side MOSFET actuator 1                                                                      |

| 47  | VBATT    | Input        | _                  | Battery voltage input                                                                                     |

| 48  | VCCP     | Input/output | _                  | Output: Internal 7.0 V voltage regulator<br>Input: External 7.0 V voltage regulator (supplied externally) |

| 49  | G_LS8    | Output       | —                  | Gate pin low-side high speed MOSFET can be used for DC/DC converter                                       |

| 50  | G_LS7    | Output       | —                  | Gate pin low-side high speed MOSFET can be used for DC/DC converter                                       |

| 51  | G_LS6    | Output       | —                  | Gate pin low-side MOSFET actuator 6                                                                       |

| 52  | G_LS5    | Output       | —                  | Gate pin low-side MOSFET actuator 5                                                                       |

| 53  | G_LS4    | Output       | _                  | Gate pin low-side MOSFET actuator 4                                                                       |

| 54  | G_LS3    | Output       | -                  | Gate pin low-side MOSFET actuator 3                                                                       |

| 55  | G_LS2    | Output       | _                  | Gate pin low-side MOSFET actuator 2                                                                       |

| 56  | G_LS1    | Output       | _                  | Gate pin low-side MOSFET actuator 1                                                                       |

| 57  | VBOOST   | Input        |                    | Boost voltage and drain pin for boost pre-drivers                                                         |

| 58  | B_HS7    | -            | _                  | Bootstrap pin high-side MOSFET 7                                                                          |

| 59  | G_HS7    | Output       | _                  | Gate pin high-side MOSFET 7                                                                               |

| 60  | S_HS7    | Input        | _                  | Source pin high side MOSFET 7                                                                             |

| 61  | B_HS6    | -            | _                  | Bootstrap pin Boost MOSFET 6                                                                              |

| 62  | G_HS6    | Output       | _                  | Gate pin Boost MOSFET 6                                                                                   |

| 63  | S_HS6    | Input        | _                  | Source pin Boost MOSFET 6                                                                                 |

| 64  | B_HS5    | -            | _                  | Bootstrap pin high-side MOSFET 5                                                                          |

| 65  | G_HS5    | Output       | _                  | Gate pin high-side MOSFET 5                                                                               |

| 66  | S_HS5    | Input        | _                  | Source pin high side MOSFET 5                                                                             |

| 67  | B_HS4    | -            |                    | Bootstrap pin boost MOSFET 4                                                                              |

| 68  | G_HS4    | Output       | _                  | Gate pin boost MOSFET 4                                                                                   |

| 69  | S_HS4    | Input        | _                  | Source pin boost MOSFET 4                                                                                 |

| 70  | B_HS3    | -            | _                  | Bootstrap pin high-side MOSFET 3                                                                          |

| 71  | G_HS3    | Output       | _                  | Gate pin high-side MOSFET 3                                                                               |

| 72  | S_HS3    | Input        | _                  | Source pin high-side MOSFET 3                                                                             |

| 73  | B_HS2    | -            | _                  | Bootstrap pin boost MOSFET 2                                                                              |

| 74  | G_HS2    | Output       |                    | Gate pin boost MOSFET 2                                                                                   |

| 75  | S_HS2    | Input        | _                  | Source pin boost MOSFET 2                                                                                 |

| 76  | B_HS1    | -            |                    | Bootstrap pin high-side MOSFET 1                                                                          |

| 77  | G_HS1    | Output       | _                  | Gate pin high-side MOSFET 1                                                                               |

| 78  | S_HS1    | Input        | _                  | Source pin high-side MOSFET 1                                                                             |

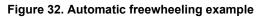

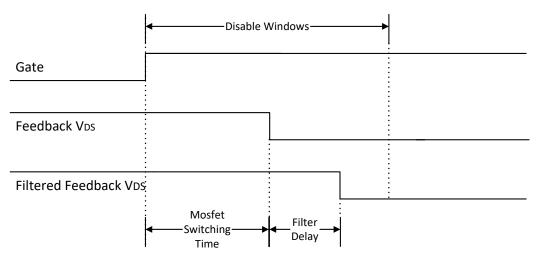

| 79  | IRQB     | Input/output | Weak PD            | Interrupt output/Flag_bus (13)                                                                            |

| 80  | CLK      | Input        | Weak PU            | Clock pin (low-frequency reference for internal PLL)                                                      |

### Table 2. PT2000 pin definitions <sup>(2), (3), (4)</sup>(continued)

| Pin  | Pin name | Pin function | Pull configuration | Definition                               |

|------|----------|--------------|--------------------|------------------------------------------|

| ePAD | PGND     | Ground       | —                  | Power ground (to be soldered on GND PCB) |

Notes

- 2. External 7.0 V is required in case the typical battery voltage is 24 V (See External VCCP (vccp\_ext\_en='1') on page <u>35</u>).

- 3. Except for supply and ground, it is guaranteed by design unused pins can be kept open without any impact on the device.

- 4. Unused VSENSEPx and VSENSENx pins can both be connected to GND.

#### Table 3. Resistor types

| Pin type | Description                                            |

|----------|--------------------------------------------------------|

| PU       | Pull-up to VCCIO (nominal value: 120 k $\Omega$ )      |

| Weak PU  | Weak pull-up to VCCIO (nominal value: 480 k $\Omega$ ) |

| PD       | Pull-down to AGND (nominal value: 120 k $\Omega$ )     |

| Weak PD  | Weak pull-down to AGND (nominal value: 480 k $\Omega)$ |

# 4 Functional description

## 4.1 Introduction

The PT2000 is a mixed signal IC for engine injector and electrical valve control, which provides a cost effective, flexible, and smart, highside and low-side MOSFET gate driver. The device includes both individual charge pump outputs for each high-side pre-driver and highvoltage DC/DC converter pre-driver. Gate drive, diagnostics, and protection against external faults, are managed through six independent and concurrent digital microcores. Each of the three logic channels including two microcores and their own code RAM and data RAM. The internal microcode is protected against theft via encryption and corruption via check sums. Those microcores are optimized to control power MOSFET with a small latency time. The PT2000 can control three banks of two injectors each or three banks with one injector per bank for full overlap,

### 4.2 Features

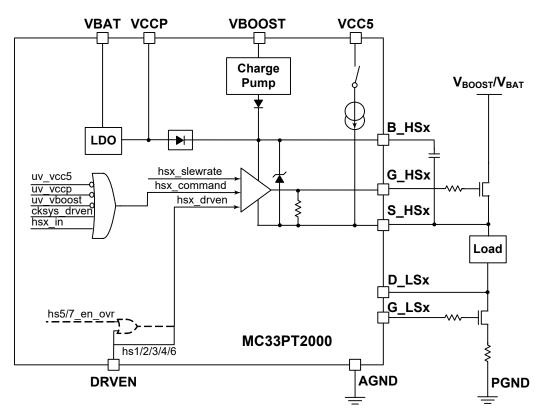

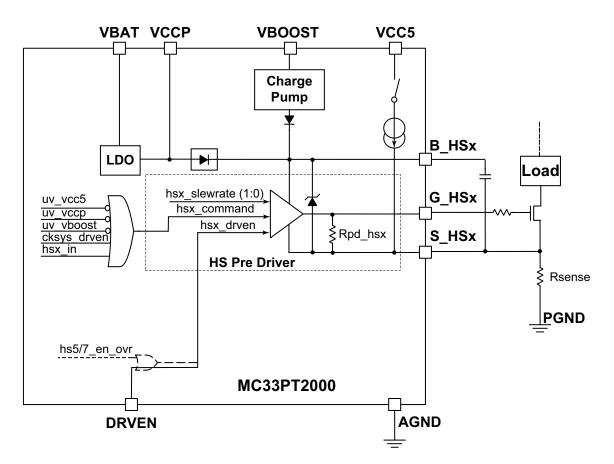

High-side and low-side pre-drivers

- · Seven high-side pre-drivers for logic level N-channel MOSFETs using four programmable slew rates

- · Six low-side pre-drivers for logic level N-channel MOSFETs using four programmable slew rates

- · Integrated bootstrap circuitry for each high-side pre-driver

- Integrated charge pump circuitry for each high-side pre-driver with 100% duty cycle capability

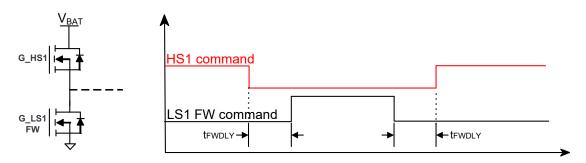

- · Configurable automatic freewheeling capability between high-side and low-side

#### DC/DC converter

- Two low-side pre-driver, for a logic level N-channel MOSFET, can be optionally dedicated to providing a boost DC-DC converter with four programmable slew rates

- · Three different control modes to reduce power dissipation (manual, hysteretic, resonant)

#### Current measurement

- · Four independent current measurement blocks

- Two current measurements (channel 5 and 6) are optionally configurable to support DC/DC converters

#### Diagnostics and monitoring

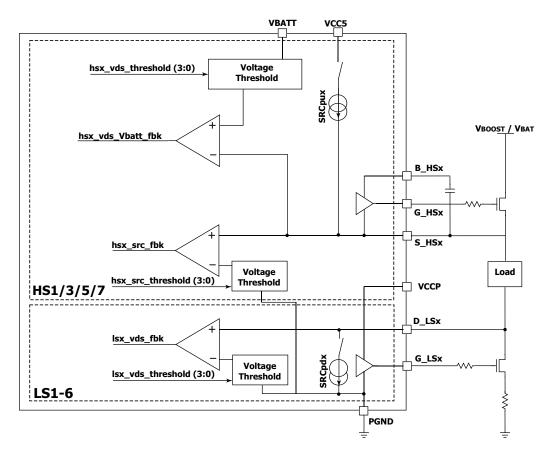

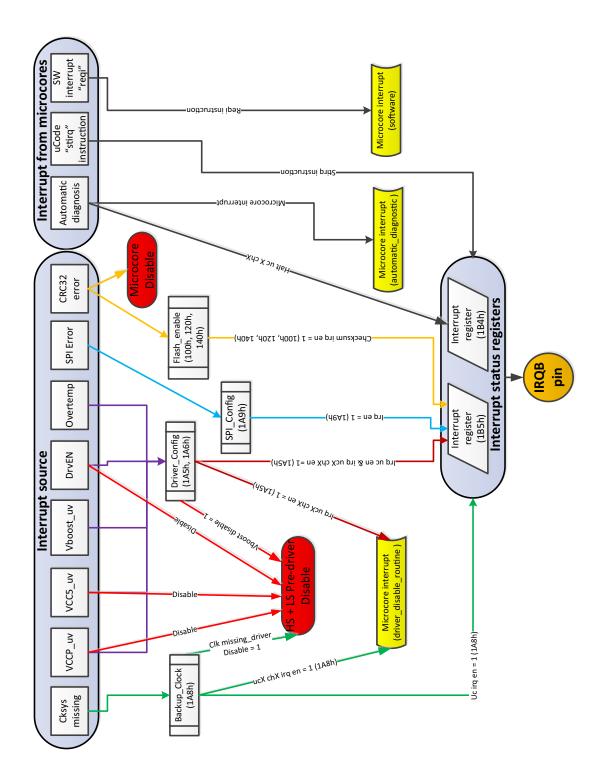

- V<sub>DS</sub> and V<sub>SRC</sub> monitoring (programmable values) for fault protection and diagnostics

- V<sub>BOOST</sub> monitoring

- V<sub>BAT</sub> monitoring

- Temperature monitoring

#### Integrated end of injection detection

· Accurate detection of end of injection for each high-side source and low-side drain without any external component needed.

#### Power supplies

- Integrated 7.0 V linear regulator (VCCP) for the HS/LS gate power supply <sup>(2)</sup>

- Integrated 2.5 V linear regulator (VCC2P5) for the digital core supply based on the VCC5 input supply

- External 5.0 V supply (VCC5)

- Selectable VCCIO external supply (5.0 V or 3.3 V) for digital I/O

#### Digital block

- · Six digital microcores, each with their own ALU, and full access to the system crossbar switch

- Three memory banks: 1024 x 16-bit of code RAM with built-in error detection and 64 x 16-bit of data RAM

- · Memory BIST and Logic BIST activated by the SPI, with pass/fail status

#### Control interface

- 16-bit slave SPI up to 10 MHz two protocols programmable slew rate

- 16 general purpose digital IOs able to sustain up to 36 V

- · Independent direct pre-driver inhibition input for safety purposes

# 5 Electrical characteristics

## 5.1 Maximum ratings

#### Table 4. Maximum ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                  | Ratings                                                                                                                                                                         | Min.                     | Max.                                                                    | Unit | Notes      |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------|------|------------|

| Electrical ratings                      |                                                                                                                                                                                 |                          |                                                                         |      | I          |

| V <sub>BOOSTMAX</sub>                   | DC voltage at VBOOST                                                                                                                                                            | 0                        | 72                                                                      | V    |            |

| V <sub>BATT</sub>                       | DC voltage at VBATT                                                                                                                                                             | -0.3                     | 72                                                                      | V    |            |

| V <sub>CC5</sub>                        | DC voltage at VCC5                                                                                                                                                              | -0.3                     | 36                                                                      | V    |            |

| V <sub>CCIO</sub>                       | DC voltage at VCCIO                                                                                                                                                             | -0.3                     | 36                                                                      | V    |            |

| V <sub>CC2P5</sub>                      | DC voltage at VCC2P5                                                                                                                                                            | -0.3                     | 3.0                                                                     | V    |            |

| V <sub>DIG</sub>                        | DC voltage at CLK, MISO, MOSI, SCLK, CSB, IRQB, RESETB                                                                                                                          | -0.3                     | 36                                                                      | V    |            |

| V <sub>DRV_EN</sub>                     | DC voltage at DRVEN                                                                                                                                                             | -0.3                     | 36                                                                      | V    |            |

| V <sub>STARTX</sub>                     | DC voltage at STARTx                                                                                                                                                            | -0.3                     | 36                                                                      | V    |            |

| V <sub>FLAGX</sub>                      | DC voltage at FLAGx                                                                                                                                                             | -0.3                     | 36                                                                      | V    |            |

| V <sub>START8</sub> _V <sub>SENSE</sub> | Start8 voltage of pins multiplexed with V <sub>SENSEN4</sub>                                                                                                                    | -1.0<br>-1.0             | 18<br>36                                                                | V    | (5)        |

| V <sub>FLAG4</sub> _V <sub>SENSE</sub>  | Flag4 voltage of pins multiplexed with V <sub>SENSEP4</sub>                                                                                                                     | -2.5<br>-2.5             | 18<br>36                                                                | V    | (5)        |

| V <sub>DBG</sub>                        | DC voltage at DBG                                                                                                                                                               | -0.3                     | 36                                                                      | V    |            |

| V <sub>OA_OUTX</sub>                    | DC voltage at OA_1, OA_2, OA_3                                                                                                                                                  | -0.3                     | 36                                                                      | V    |            |

| V <sub>DGND</sub>                       | DC voltage at DGND                                                                                                                                                              | -0.3                     | 0.3                                                                     | V    |            |

| V <sub>AGND</sub>                       | DC voltage at AGND                                                                                                                                                              | -0.3                     | 0.3                                                                     | V    |            |

| V <sub>CCP</sub>                        | DC voltage at VCCP                                                                                                                                                              | -0.3                     | 9.0                                                                     | V    |            |

| V <sub>S_HSX</sub>                      | S_HSx<br>• DC voltage<br>• Transients t <800 ns<br>• Transients t <400 ns                                                                                                       | -3.0<br>-6.0<br>-8.0     | V <sub>BOOSTMAX</sub><br>V <sub>BOOSTMAX</sub><br>V <sub>BOOSTMAX</sub> | V    | (6)<br>(6) |

| V <sub>B_HSX</sub>                      | B_HSx<br>• V <sub>BATT</sub> -V <sub>B_HSx</sub> must not exceed 40 V<br>• Transients t <800 ns<br>• Transients t <400 ns                                                       | -0.3<br>-2.0<br>-4.0     | V <sub>S_HSX</sub> +<br>V <sub>BS_HSX_CL</sub>                          | V    | (6)<br>(6) |

| V <sub>G_HSX</sub>                      | DC voltage at G_HSx                                                                                                                                                             | V <sub>S_HSx</sub> - 0.3 | V <sub>B_HSx</sub> +0.3                                                 | V    |            |

| V <sub>G_LSX</sub>                      | G_LSx<br>• DC voltage<br>• Transients t < 5.0 μs; V <sub>CCP_MAX</sub> = 8.0 V; energy of pulses < 0 V or > V <sub>CCP</sub> is<br>limited to 2.0 μJ due to capacitive coupling | -0.3<br>-1.5             | V <sub>CCP</sub> + 0.3<br>V <sub>CCP</sub> + 1.5                        | V    | (6)        |

| V <sub>D_LSX</sub>                      | D_LSx<br>• DC voltage<br>• Transients t < 400 ns                                                                                                                                | -3.0<br>-8.0             | 75<br>75                                                                | V    | (6)        |

#### Table 4. Maximum ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                    | Ratings                                                                                                                                                                                                               | Min.                | Max.             | Unit | Notes      |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|------|------------|

| V <sub>VSENSEN1/2/3</sub> | DC voltage at VSENSEN1/2/3<br>• Static at VCC5 < 10 V<br>• Dynamic for max 5.0 μs, 1.0 kHz repetition rate at VCC5, 5.25 V<br>• Dynamic for max 1.0 μs at VCC5 < 5.25 V                                               | -1.0<br>-5.0<br>-15 | 1.0<br>5.0<br>15 | V    | (6)<br>(6) |

| V <sub>VSENSEP1/2/3</sub> | <ul> <li>DC voltage at VSENSEP1/2/3</li> <li>DC voltage at VCC5 &lt; 10 V</li> <li>Dynamic for max 5.0 μs, 1.0 kHz repetition rate at VCC5 &lt; 5.25 V</li> <li>Dynamic for max 1.0 μs at VCC5 &lt; 5.25 V</li> </ul> | -2.5<br>-5.0<br>-15 | 2.5<br>5.0<br>15 | V    | (6)<br>(6) |

| Vvsensen5/6               | <ul> <li>DC voltage at VSENSEN5/6</li> <li>DC voltage at VCC5 &lt; 10 V</li> <li>Dynamic for max 5.0 μs, 1.0 kHz repetition rate at VCC5 &lt; 5.25 V</li> <li>Dynamic for max 1.0 μs at VCC5 &lt; 5.25 V</li> </ul>   | -3.0<br>-5.0<br>-15 | 1.0<br>5.0<br>15 | V    | (6)<br>(6) |

| Vvsensep5/6               | DC voltage at VSENSEP5/6<br>• DC voltage at VCC5 < 10 V<br>• Dynamic for max 5.0 μs, 1.0 kHz repetition rate at VCC5 < 5.25 V<br>• Dynamic for max 1.0 μs at VCC5 < 5.25 V                                            | -4.2<br>-5.0<br>-15 | 2.5<br>5.0<br>15 | V    | (6)<br>(6) |

ESD voltage

| Vesd-hbm1<br>Vesd-hbm2<br>Vesd-hbm3<br>Vesd-cdm1 | ESD voltage<br>• Human body model (HBM)<br>VBOOST, VBATT, S_HSx<br>D_LSx<br>All other pins<br>• Machine model<br>Corner pins | -4000<br>-8000<br>-2000<br>-750 | 4000<br>8000<br>2000<br>750 | V | (7), (8) |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------|---|----------|

|                                                  |                                                                                                                              |                                 |                             |   |          |

| V <sub>ESD-CDM2</sub>                            | All other pins                                                                                                               | -500                            | 500                         |   |          |

**Thermal ratings**

| T <sub>A</sub><br>T <sub>J</sub> | Operating temperature <ul> <li>Ambient</li> <li>Junction</li> </ul> | -40<br>-40 | 125<br>150 | °C |  |

|----------------------------------|---------------------------------------------------------------------|------------|------------|----|--|

| T <sub>THRESHOLD</sub>           | Temperature monitoring threshold                                    | 167        | 187        | °C |  |

| T <sub>STG</sub>                 | Storage ambient temperature                                         | -55        | 150        | °C |  |

Thermal resistance

| R <sub>θJA</sub>       | Thermal resistance junction to ambient     | _ | 25.3 | °C/W | (9)  |

|------------------------|--------------------------------------------|---|------|------|------|

| R <sub>0JCTOP</sub>    | Thermal resistance junction to case top    | - | 13.2 | °C/W | (10) |

| R <sub>0JCBOTTOM</sub> | Thermal resistance junction to case bottom | _ | 0.8  | °C/W | (11) |

Notes

5. With series resistor of 3.3 k $\Omega \pm 20\%$  at the pin

6. Guaranteed by design.

7. Human body model (HBM) per JESD22-A114 - 100 pF, 1.5 k $\Omega$

8. Charge device model (CDM) per JESD22-C101.

9. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal

10. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC - 883 Method 1012.1).

11. Thermal resistance between the die and the solder pad on the bottom of the package based on the simulation without internal resistance

## 5.2 **Power supply electrical characteristics**

#### Table 5. PT2000 static electrical characteristics

Characteristics noted under conditions -40  $^{\circ}C < T_A < +125 ^{\circ}C$ , referenced to ground, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25 ^{\circ}C$  under nominal conditions, unless otherwise noted.

| Symbol                     | Characteristic                                                                                                                                                                                                                                                                                    | Min.             | Тур.                | Max.               | Unit | Notes |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|--------------------|------|-------|

| /BATT input supp           | ly                                                                                                                                                                                                                                                                                                |                  |                     |                    |      |       |

| V <sub>BATT</sub>          | <ul><li>VBATT power supply input voltage, normal operation</li><li>Internal VCCP regulator</li><li>External VCCP regulator</li></ul>                                                                                                                                                              | 5.0<br>5.0       | 13.5<br>—           | 16<br>72           | v    | (12)  |

| V <sub>BATT_LOADDUMP</sub> | VBATT power supply input voltage during load dump duration < 500 ms <ul> <li>Internal VCCP regulator</li> </ul>                                                                                                                                                                                   | 18               | _                   | 40                 | v    |       |

| I <sub>VBATT_LEAK</sub>    | VBATT power supply current in reset state, $V_{CC5} = V_{CCIO} = 0.0 V$<br>• $V_{BATT} = 13.5 V$<br>• $V_{BATT} = 40 V$                                                                                                                                                                           |                  | 150<br>600          | 180<br>800         | μA   |       |

| IVBATT_OPER                | <ul> <li>VBATT power supply current in normal operation V<sub>BATT</sub> = 16 V</li> <li>DRVEN low, internal VCCP reg. off</li> <li>DRVEN low, Internal VCCP reg. on</li> <li>DRVEN high, VCCP max. load 100 mA</li> </ul>                                                                        |                  | 0.9<br>4.5<br>104.5 | 2.5<br>6.0<br>106  | mA   |       |

| I <sub>VBATT_LEAK</sub>    | VBATT power supply current in reset state, $V_{CC5} = V_{CCIO} = 0.0 V$<br>• $V_{BATT} = 13.5 V$<br>• $V_{BATT} = 40 V$                                                                                                                                                                           |                  | 150<br>600          | 180<br>800         | μA   |       |

| /BOOST input sup           | oply                                                                                                                                                                                                                                                                                              |                  |                     |                    |      |       |

| I <sub>VBOOST_LEAK</sub>   | Leakage current from V <sub>BOOST</sub> , during reset state with<br>$V_{CC5} = V_{CCIO} = 5.0 \text{ V}$<br>• $V_{BOOST} = V_{BAT} = 13.5 \text{ V}$<br>• $V_{BOOST} = V_{BAT} = 40 \text{ V}$<br>• $V_{BOOST} = V_{BAT} = 65 \text{ V}$<br>Contributors (13.5 V): $V_{BOOST}$ volt. div.: 65 µA | 65<br>240<br>400 |                     | 90<br>370<br>600   | μΑ   |       |

| I <sub>VBOOST_OPER</sub>   | Operating current from V <sub>BOOST</sub> = 65 V                                                                                                                                                                                                                                                  |                  | 3.9                 | 5.75               | mA   |       |

| /CC5 input supply          |                                                                                                                                                                                                                                                                                                   |                  |                     |                    |      | 1     |

| V <sub>CC5</sub>           | VCC5 supply input voltage                                                                                                                                                                                                                                                                         | 4.75             | 5.0                 | 5.25               | V    |       |

| V <sub>CC5_DIGITAL</sub>   | VCC5 supply input voltage for digital part functional only                                                                                                                                                                                                                                        | 4.0              | 5.0                 | 5.25               | V    | (12)  |

| I <sub>VCC5</sub>          | <ul> <li>VCC5 supply current</li> <li>f<sub>SYS</sub> = 24 MHz, 7 HS load biasing enabled, no microcore running</li> <li>f<sub>SYS</sub> = 24 MHz, 7 HS load biasing enabled, all microcores running</li> <li>LBIST running, bias disabled</li> </ul>                                             |                  | 53<br>65<br>40      | 66.4<br>81.4<br>50 | mA   | (12)  |

| V <sub>OVVCC5</sub>        | VCC5 overvoltage threshold                                                                                                                                                                                                                                                                        | 7.5              | 8.5                 | 10                 | V    |       |

| V <sub>OVVCC5_VCCP</sub>   | VCC5 overvoltage threshold for VCCP shutdown                                                                                                                                                                                                                                                      | 6.2              | 6.9                 | 7.5                | V    |       |

| V <sub>UVVCC5-</sub>       | VCC5 undervoltage low-voltage threshold                                                                                                                                                                                                                                                           | 4.3              | 4.45                | 4.7                | V    |       |

| V <sub>UVVCC5+</sub>       | VCC5 undervoltage high-voltage threshold                                                                                                                                                                                                                                                          | 4.35             | 4.5                 | 4.75               | V    |       |

| V <sub>UVVCC5_HYST</sub>   | VCC5 undervoltage hysteresis                                                                                                                                                                                                                                                                      | 30               | 50                  | 85                 | mV   |       |

Notes

12. Guaranteed by design.

#### Table 5. PT2000 static electrical characteristics (continued)

Characteristics noted under conditions -40  $^{\circ}C < T_A < +125 ^{\circ}C$ , referenced to ground, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25 ^{\circ}C$  under nominal conditions, unless otherwise noted.

| Symbol                     | Characteristic                                                                                                                                                                                                                                                                                  | Min.  | Тур.      | Max.                    | Unit     | Notes |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|-------------------------|----------|-------|

| VCC5 input supply          | / (continued)                                                                                                                                                                                                                                                                                   | I     | I         | I                       | I        | 1     |

| T <sub>FILTER_UVVCC5</sub> | VCC5 UV anti-glitch filter delay time                                                                                                                                                                                                                                                           | 0.8   | 1.3       | 2.0                     | μs       |       |

| VCCIO INPUT SUP            | PLY                                                                                                                                                                                                                                                                                             |       |           |                         |          |       |

| V <sub>CCIO</sub>          | VCCIO supply input voltage                                                                                                                                                                                                                                                                      | 3.0   | —         | 5.25                    | V        |       |

| Ivccio                     | <ul> <li>VCCIO supply current</li> <li>f<sub>SYS</sub> = 24 MHz, no microcore running</li> <li>f<sub>SYS</sub> = 24 MHz, all microcores running</li> </ul>                                                                                                                                      |       | 38<br>1.5 | 70<br>—                 | μA<br>mA | (13)  |

| VCCP input supply          | y                                                                                                                                                                                                                                                                                               |       | I         |                         | 1        | -     |

| V <sub>CCP</sub>           | VCCP output voltage, 0.0 mA < I <sub>VCCP</sub> < 100 mA                                                                                                                                                                                                                                        | 6.5   | 7.0       | 7.5                     | V        |       |

| V <sub>CCP_EXT</sub>       | V <sub>CCP</sub> input voltage range (V <sub>CCP</sub> externally supplied)                                                                                                                                                                                                                     | 5.0   | _         | 9.0                     | V        |       |

| C <sub>VCCP</sub>          | V <sub>CCP</sub> external output capacitor                                                                                                                                                                                                                                                      | 1.0   | 4.7       | 14                      | μF       | (14)  |

| $\Delta V_{VCCP}$          | $V_{BATT} \text{ to } V_{CCP} \text{ voltage dropout}$ $V_{BATT} = 5.0 \text{ V and } I_{VCCP} = -50 \text{ mA}$ $V_{BATT} = 5.0 \text{ V and } I_{VCCP} = -30 \text{ mA}$ $V_{BATT} = 5.0 \text{ V and } I_{VCCP} = -10 \text{ mA}$ $V_{BATT} = 5.0 \text{ V and } I_{VCCP} = -100 \text{ mA}$ |       | <br><br>  | 180<br>110<br>40<br>350 | mV       |       |

| V <sub>UVVCCP-</sub>       | VCCP undervoltage low-voltage threshold                                                                                                                                                                                                                                                         | 4.3   | 4.5       | 4.68                    | V        |       |

| V <sub>UVVCCP+</sub>       | VCCP undervoltage high-voltage threshold                                                                                                                                                                                                                                                        | 4.4   | 4.55      | 4.73                    | V        |       |

| V <sub>UVVCCP_HYST</sub>   | VCCP undervoltage hysteresis                                                                                                                                                                                                                                                                    | 30    | 50        | 70                      | mV       |       |

| IVCCP                      | $V_{CCP}$ output current (average during PWM operation)<br>9.0 V < V <sub>BATT</sub> < 18 V                                                                                                                                                                                                     | _     | _         | 100                     | mA       |       |

| I <sub>VCCP_MAX</sub>      | VCCP output current limitation                                                                                                                                                                                                                                                                  | 150   | 200       | 250                     | mA       |       |

| t <sub>FILTER_UVVCCP</sub> | VCCP UV anti-glitch filter delay time                                                                                                                                                                                                                                                           | 0.8   | 1.3       | 2.0                     | μs       |       |

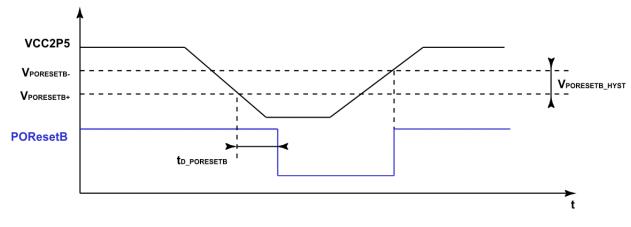

| VCC2P5 internal re         | egulator                                                                                                                                                                                                                                                                                        |       |           |                         |          |       |

| V <sub>CC2P5</sub>         | VCC2P5 supply output voltage                                                                                                                                                                                                                                                                    | 2.375 | 2.5       | 2.625                   | V        |       |

| V <sub>cc5_BGmin</sub>     | Voltage required on VCC5 to start VCC2P5                                                                                                                                                                                                                                                        | _     | —         | 3.8                     | V        |       |

| C <sub>VCC2P5</sub>        | VCC2P5 external output capacitor                                                                                                                                                                                                                                                                | 0.5   | 1.0       | 3.0                     | μF       | (15)  |

| I <sub>VCC2P5</sub>        | VCC2P5 supply output current<br>• f <sub>SYS</sub> = 24 MHz, all microcores running                                                                                                                                                                                                             | _     | -15       | -50                     | mA       |       |

| IVCC2P5_LIM                | VCC2P5 supply output current limit                                                                                                                                                                                                                                                              | -50   | 93        | 140                     | mA       |       |

| V <sub>PORESETB-</sub>     | VCC2P5 voltage threshold for asserting PORESETB                                                                                                                                                                                                                                                 | 2.0   | 2.11      | 2.21                    | V        |       |

| V <sub>PORESETB+</sub>     | VCC2P5 voltage threshold for deasserting PORSETB                                                                                                                                                                                                                                                | 2.07  | 2.19      | 2.3                     | V        |       |

| V <sub>PORESETB_HYST</sub> | PORESETB voltage hysteresis                                                                                                                                                                                                                                                                     | 50    | 75        | 100                     | mV       |       |

| t <sub>D_PORESETB</sub>    | PORESETB switching time                                                                                                                                                                                                                                                                         |       | 0.7       | 1.5                     | μs       | 1     |

Notes

13. Guaranteed by design.

14. For VCCP: "For EMC purpose adding 1.0  $\mu$ F + 100 nF caps in parallel connected to PGND is recommended

15. For VCC2P5: "For EMC purpose adding 1.0 µF + 100 nF caps in parallel connected to DGND is recommended

#### Table 5. PT2000 static electrical characteristics (continued)

Characteristics noted under conditions -40  $^{\circ}C < T_A < +125 ^{\circ}C$ , referenced to ground, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25 ^{\circ}C$  under nominal conditions, unless otherwise noted.

| Symbol                      | Characteristic                                                        | Min.  | Тур.  | Max.  | Unit | Notes |

|-----------------------------|-----------------------------------------------------------------------|-------|-------|-------|------|-------|

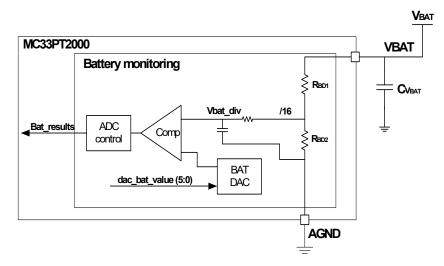

| Battery voltage mo          | pnitor                                                                |       |       |       |      |       |

| V <sub>BATT_MONITOR</sub>   | Input voltage range                                                   | 5.0   | —     | 36    | V    | (16)  |

| R <sub>VBATT_IN</sub>       | Input impedance                                                       | 350   | 500   | —     | kΩ   |       |

| G <sub>VBATT_DIV</sub>      | V <sub>BATT</sub> voltage divider ratio                               | —     | 1/16  | —     |      |       |

| f <sub>CVBATT_DIV</sub>     | V <sub>BATT</sub> analog filter cutoff frequency                      | 10    | 15.5  | 20    | kHz  |       |

| V <sub>VBATT_REF</sub>      | DAC reference voltage                                                 | 2.475 | 2.5   | 2.525 | V    |       |

| V <sub>VBATT_DAC_LSB</sub>  | DAC LSB                                                               | —     | 39.06 | —     | mV   |       |

| V <sub>VBATT_DAC_OUT_</sub> | DAC minimum output voltage <ul> <li>DAC code = 0h</li> </ul>          | _     | 0.0   | _     | V    |       |

| V <sub>VBATT_DAC_OUT_</sub> | DAC maximum output voltage <ul> <li>DAC code = 3Fh</li> </ul>         | _     | 2.461 | _     | V    |       |

| <sup>€</sup> VBATT          | V <sub>BATT</sub> measurement total error (V <sub>BATT</sub> > 5.0 V) | -5.0  | 1.0   | 5.0   | %    |       |

| t <sub>VBATT_DAC</sub>      | V <sub>BATT</sub> DAC settling time                                   | —     | —     | 0.9   | μs   |       |

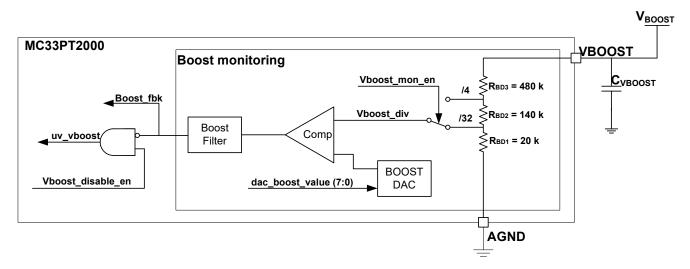

| Boost voltage mor           | litor                                                                 | •     |       |       |      |       |

| V <sub>BOOSTMAX</sub>       | Input voltage range                                                   | 0.0   |       | 72    | V    |       |

| R <sub>VBOOST IN</sub>      | Input impedance                                                       | 400   | 640   | _     | kΩ   |       |

| R <sub>VBOOST_IN</sub>     | Input impedance                                               | 400         | 640  | -           | kΩ |  |

|----------------------------|---------------------------------------------------------------|-------------|------|-------------|----|--|

| G <sub>VBOOST_DIV</sub>    | V <sub>BOOST</sub> voltage divider ratio (boost monitor mode) | 1/32* 0.996 | 1/32 | 1/32* 1.004 |    |  |

| G <sub>UV_VBOOST_DIV</sub> | $V_{BOOST}$ voltage divider ratio (UV $V_{BOOST}$ mode)       | 1/4* 0.996  | 1/4  | 1/4* 1.004  |    |  |

| $V_{VBOOST\_DAC\_LSB}$     | DAC LSB                                                       | _           | 9.77 | -           | mV |  |

| <sup>€</sup> ∨BOOST        | V <sub>BOOST</sub> measurement total error (4.85 V to 72 V)   | -2.0        |      | 2.0         | %  |  |

Notes

This limitation is only for the V<sub>BAT</sub> ADC, if V<sub>BAT</sub> is > 36 V, then V<sub>BAT</sub> monitoring results will saturate. It means in case V<sub>BAT</sub> > 36 V, the V<sub>BAT</sub> monitoring feature will not work but device will be 100 % functional until V<sub>BAT</sub> = 72 V.

## 5.3 High-side pre-driver electrical characteristics

#### Table 6. High-side pre-driver electrical characteristics

Characteristics noted under conditions -40  $^{\circ}C < T_A < +125 ^{\circ}C$ , referenced to ground, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25 ^{\circ}C$  under nominal conditions, unless otherwise noted.

| Symbol                     | Characteristic                                                                                                                                                                                                | Min.                        | Тур.        | Max.                            | Unit | Notes    |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------|---------------------------------|------|----------|

| ligh-side pre-driv         | er                                                                                                                                                                                                            |                             |             |                                 |      |          |

| V <sub>S_HSX</sub>         | S_HSx pin operating voltage<br>Transients t <400 ns<br>Transients t <800 ns                                                                                                                                   | -3.0<br>-6.0<br>-8.0        | _<br>_<br>_ | V <sub>BOOSTMAX</sub><br>—<br>— | V    | (17)     |

| V <sub>B_HSX</sub>         | B_HSx pin operating voltage                                                                                                                                                                                   | V <sub>S_HSX</sub> +<br>4.0 | _           | V <sub>S_HSX</sub> +<br>8.0     | V    | (17)     |

| V <sub>BS_HSX_CL</sub>     | B_HSx-S_HSx clamp voltage                                                                                                                                                                                     | 6.5                         | 7.3         | 8.0                             | V    | (18)     |

| V <sub>G_HSX</sub>         | G_HSx operating voltage                                                                                                                                                                                       | V <sub>S_HSX</sub>          | _           | V <sub>B_HSX</sub>              | V    | (17)     |

| IS_HSX_SINK_OFF            | $\begin{split} &S\_HSx \text{ leakage current biasing switched Off:} \\ &V_{S\_HSX} = V_{BOOSTMAX} \\ &V_{S\_HSX} = 13.5 \text{ V} \\ &V_{S\_HSX} = 7.0 \text{ V} \\ &V_{S\_HSX} = 4.0 \text{ V} \end{split}$ | <br><br>                    | <br><br>    | 1000<br>250<br>120<br>100       | μΑ   |          |

| I <sub>S_HSX_SINK_ON</sub> | S_HSx leakage current when pre-driver on (biasing switched Off)<br>• $V_{S_{HSX}} = 7.0 V$                                                                                                                    | _                           | _           | 220                             | μΑ   |          |

| <sup>f</sup> g_hsx_pwm     | PWM frequencyInternal $V_{CCP}$ and $V_{BATT} \ge 9.0 V$ Internal $V_{CCP}$ and $5.0 V \le V_{BATT} \le 9.0 V$ External $V_{CCP}$ and $9.0 V \le V_{BATT}$                                                    | 0.0<br>0.0<br>0.0           |             | 100<br>50<br>100                | kHz  | (17)     |

| $DC_{G_{HSX}}$             | Duty cycle                                                                                                                                                                                                    | 0.0                         | _           | 100                             | %    |          |

| t <sub>ON_HSX_MIN</sub>    | High-side driver minimum PWM on time                                                                                                                                                                          | _                           |             | 1.0                             | μs   | (17)     |

| $Q_{G_{HSX}}$              | External high-side MOSFET effective gate charge<br>• $f_{PWM} \le f_{G_HSx_PWM}$<br>• $f_{PWM} \le 67 \text{ kHz}$                                                                                            |                             | 40<br>55    | 50<br>75                        | nC   |          |

| I <sub>G_HSX_PWM</sub>     | G_HSx current (average during PWM operation) $\rm Q_{G}$ = $\rm Q_{G_HSX},$ $\rm f_{PWM}$ = 100 kHz                                                                                                           | —                           | 4.0         | 5.0                             | mA   | (17)     |

| I <sub>G_HSx_SRC</sub>     | Peak source gate drive current                                                                                                                                                                                | —                           | 230         | —                               | mA   | (17)     |

| I <sub>G_HSx_SINK</sub>    | Peak sink gate drive current                                                                                                                                                                                  | —                           | 440         | —                               | mA   | (17)     |

| ligh-side pre-driv         | er dynamic                                                                                                                                                                                                    |                             |             | •                               |      | •        |

| t <sub>R_G_HSX</sub>       | Turn on rise time, 10%-90% of out voltage, $V_{CCP}$ = 7.0 V, at open pin                                                                                                                                     | 4.5                         |             | 25                              | ns   | (17)     |

| t <sub>F_G_HSX</sub>       | Turn off fall time, 90%-10% of out voltage, $V_{CCP}$ = 7.0 V, at open pin                                                                                                                                    | 5.0                         |             | 25                              | ns   | (17)     |

| $SR_{S_{HSX}}$             | Max permissible slew rate at the S_HSX pin                                                                                                                                                                    | -125                        |             | 600                             | V/µs | (17)     |

| t <sub>DON_G_HSX_300</sub> | Turn on propagation delay at 300 V/ $\mu$ s slew rate                                                                                                                                                         | 40                          | —           | 100                             | ns   | (17)(19) |

| tDOFF_G_HSX_300            | Turn off propagation delay at 300 V/ $\mu$ s slew rate                                                                                                                                                        | 40                          | _           | 100                             | ns   | (17)(19) |

| t <sub>DON_G_HSX_50</sub>  | Turn on propagation delay at 50 V/µs slew rate                                                                                                                                                                | 65                          | _           | 125                             | ns   | (17)(19) |

| t <sub>DOFF_G_HSX_50</sub> | Turn off propagation delay at 50 V/µs slew rate                                                                                                                                                               | 50                          |             | 100                             | ns   | (17)(19) |

Notes

17. Guaranteed by design.

18. VB\_HSx has to be 2.0 V above PGND for full function (switch on) of the pre-driver

19. 10% of output voltage change,  $C_{LOAD}$  = 4.7 nF;  $R_G$  = 40.2  $\Omega$ ,  $V_{CCP}$  = 7.0 V

#### Table 6. High-side pre-driver electrical characteristics (continued)

Characteristics noted under conditions -40  $^{\circ}$ C < T<sub>A</sub> < +125  $^{\circ}$ C, referenced to ground, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25  $^{\circ}$ C under nominal conditions, unless otherwise noted.

| Symbol                      | Characteristic                                        | Min. | Тур. | Max. | Unit | Notes    |

|-----------------------------|-------------------------------------------------------|------|------|------|------|----------|

| High-side pre-drive         | er dynamic (continued)                                |      |      |      |      |          |

| t <sub>DON_G_HSX_25</sub>   | Turn on propagation delay at 25 V/ $\mu$ s slew rate  | 100  | —    | 200  | ns   | (20)(21) |

| tDOFF_G_HSX_25              | Turn off propagation delay at 25 V/ $\mu$ s slew rate | 70   | —    | 150  | ns   | (20)(21) |

| t <sub>DON_G_HSX_12.5</sub> | Turn on propagation delay at 12.5 V/µs slew rate,     | 160  | —    | 310  | ns   | (20)(21) |

| tDOFF_G_HSX_12.5            | Turn off propagation delay at 12.5 V/µs slew rate     | 90   | _    | 170  | ns   | (20)(21) |

| HS pre-driver safe          | off                                                   |      |      |      |      |          |

| R <sub>PD_HSX</sub>         | G_HSX to S_HSX pull-down resistor                     | 500  |      | 2000 | kΩ   |          |

| Slew rate control           | -                                                     |      |      |      |      |          |

| R <sub>DS_HSX_P (00)</sub>  | G_HSx pMOS R <sub>DS(on)</sub> (00) 300 V/µs          | 7.5  | 14.6 | 31.4 | Ω    |          |

| R <sub>DS_HSX_N (00)</sub>  | G_HSx nMOS R <sub>DS(on)</sub> (00) 300 V/µs          | 2.5  | 5.9  | 16.5 | Ω    |          |

| R <sub>DS_HSX_P (01)</sub>  | G_HSx pMOS R <sub>DS(on)</sub> (01) 50 V/µs           | 61   | 85   | 115  | Ω    |          |

| R <sub>DS_HSX_N (01)</sub>  | G_HSx nMOS R <sub>DS(on)</sub> (01) 50 V/µs           | 23   | 35   | 50   | Ω    |          |

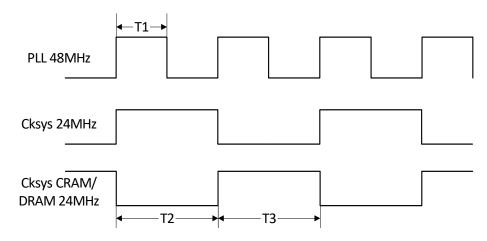

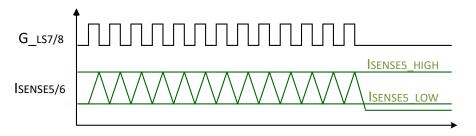

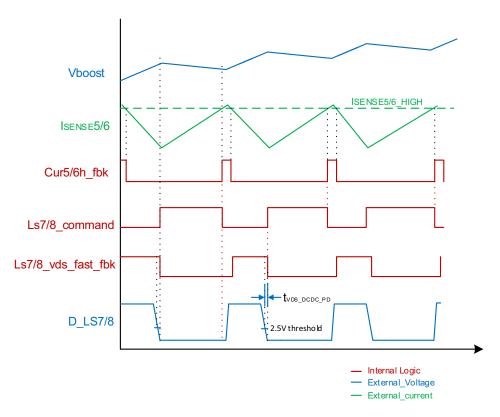

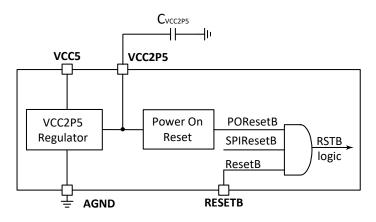

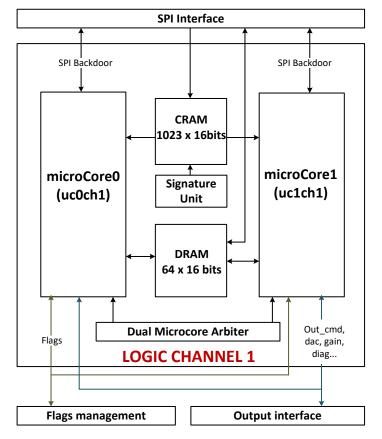

| R <sub>DS_HSX_P (10)</sub>  | G_HSx pMOS R <sub>DS(on)</sub> (10) 25 V/µs           | 122  | 169  | 230  | Ω    |          |