# 5V ECL 6-Bit Universal Up/Down Counter

#### Description

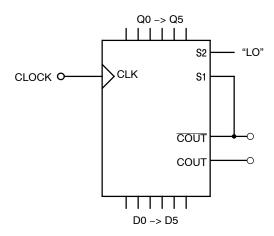

The MC10E/100E136 is a 6-bit synchronous, presettable, cascadable universal counter. The device generates a look-ahead-carry output and accepts a look-ahead-carry input. These two features allow for the cascading of multiple E136's for wider bit width counters that operate at very nearly the same frequency as the stand alone counter.

The CLOUT output will pulse LOW for one clock cycle one count before the E136 reaches terminal count. The COUT output will pulse LOW for one clock cycle when the counter reaches terminal count. For more information on utilizing the look-ahead-carry features of the device please refer to the applications section of this data sheet. The differential COUT output facilitates the E136's use in programmable divider and self-stopping counter applications.

Unlike the H136 and other similar universal counter designs, the E136 carry—out and look-ahead-carry—out signals are registered on chip.

This design alleviates the glitch problem seen on many counters where the carry out signals are merely gated. Because of this architecture there are some minor functional differences between the E136 and H136 counters. The user, regardless of familiarity with the H136, should read this data sheet carefully. Note specifically (see logic diagram) the operation of the carry out outputs and the look-ahead-carry in input when utilizing the master reset.

When left open all of the input pins will be pulled LOW via an input pull-down resistor. The master reset is an asynchronous signal which when asserted will force the Q outputs LOW.

The Q outputs need not be terminated for the E136 to function properly, in fact if these outputs will not be used in a system it is recommended to save power and minimize noise that they be left open. This practice will minimize switching noise which can reduce the maximum count frequency of the device or significantly reduce margins against other noise in the system.

The 100 Series contains temperature compensation.

#### **Features**

- 550 MHz Count Frequency

- Fully Synchronous Up and Down Counting

- Look-Ahead-Carry Input and Output

- Asynchronous Master Reset

- PECL Mode Operating Range: V<sub>CC</sub> = 4.2 V to 5.7 V with V<sub>EE</sub> = 0 V

- NECL Mode Operating Range: V<sub>CC</sub> = 0 V with V<sub>EE</sub> = -4.2 V to -5.7 V

- Internal Input 50 kΩ Pulldown Resistors

- ESD Protection: Human Body Model: > 2 kV, Machine Model: > 200 V

# ON Semiconductor®

http://onsemi.com

PLCC-28 FN SUFFIX CASE 776

#### MARKING DIAGRAM\*

xxx = 10 or 100

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

\*For additional marking information, refer to Application Note AND8002/D.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.

- Meets or Exceeds JEDEC Standard EIA/JESD78 IC Latchup Test

- Moisture Sensitivity Level: Pb = 1; Pb-Free = 3

For Additional Information, see Application Note AND8003/D

- Flammability Rating: UL 94 V-0 @ 0.125 in, Oxygen Index: 28 to 34

- Transistor Count = 506 devices

1

• Pb-Free Packages are Available\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Warning: All V<sub>CC</sub>, V<sub>CCO</sub>, and V<sub>EE</sub> pins must be externally connected to Power Supply to guarantee proper operation.

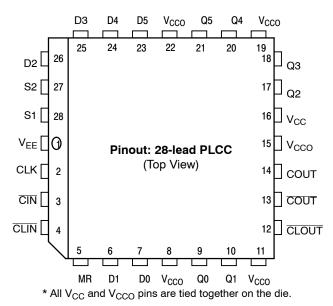

Figure 1. 28-Lead Pinout

**Table 1. PIN DESCRIPTION**

| PIN                                | FUNCTION                                       |

|------------------------------------|------------------------------------------------|

| D <sub>0</sub> – D <sub>5</sub>    | ECL Preset Data Inputs                         |

| $Q_0 - Q_5$                        | ECL Data Outputs                               |

| S1, S2                             | Mode Control Pins                              |

| MR                                 | Master Reset                                   |

| CLK                                | ECL Clock Input                                |

| COUT,<br>COUT                      | ECL Differential Carry-Out Output (Active LOW) |

| CLOUT                              | ECL Look-Ahead-Carry Out (Active LOW)          |

| CIN                                | ECL Carry-In Input (Active LOW)                |

| CLIN                               | ECL Look-Ahead-Carry In Input (Active LOW)     |

| V <sub>CC</sub> , V <sub>CCO</sub> | Positive Supply                                |

| V <sub>EE</sub>                    | Negative Supply                                |

**Table 2. FUNCTION TABLE**

(Expanded Truth Table on page 3)

| S1                    | S2               | CIN                        | MR               | CLK                             | FUNCTION                                                                                                                             |

|-----------------------|------------------|----------------------------|------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| L<br>L<br>H<br>H<br>X | L<br>H<br>L<br>L | X<br>L<br>H<br>L<br>H<br>X | L<br>L<br>L<br>L | Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>X | Preset Parallel Data<br>Increment (Count Up)<br>Hold Count<br>Decrement (Count Down)<br>Hold Count<br>Hold Count<br>Reset (Qn = LOW) |

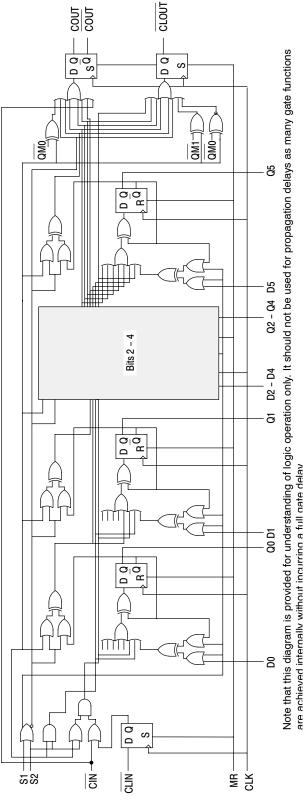

Figure 2. E136 Universal Up/Down Counter Logic Diagram

Table 3. EXPANDED TRUTH TABLE

| Function                                           | S1            | S2               | MR               | CIN                             | CLIN                       | CLK                                  | D5                                   | D4                              | D3                              | D2                              | D1                         | D0                                   | Q5     | Q4                              | Qз                | Q2                                   | Q1                              | Q0                              | COUT                            | CLOUT  |

|----------------------------------------------------|---------------|------------------|------------------|---------------------------------|----------------------------|--------------------------------------|--------------------------------------|---------------------------------|---------------------------------|---------------------------------|----------------------------|--------------------------------------|--------|---------------------------------|-------------------|--------------------------------------|---------------------------------|---------------------------------|---------------------------------|--------|

| Preset                                             | L             | L                | L                | Х                               | Х                          | Z                                    | L                                    | L                               | L                               | L                               | Н                          | Н                                    | L      | L                               | L                 | L                                    | Н                               | Н                               | Н                               | Н      |

| Down                                               | H<br>H<br>H   | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>L                     | L<br>L<br>L                | Z<br>Z<br>Z<br>Z                     | X<br>X<br>X                          | X<br>X<br>X                     | X<br>X<br>X                     | X<br>X<br>X                     | X<br>X<br>X                | X<br>X<br>X                          | LLLH   | L<br>L<br>L                     | L<br>L<br>H       | L<br>L<br>L                          | H<br>L<br>L                     | L<br>H<br>L<br>H                | H<br>L<br>H                     | HH     |

| Preset                                             | L             | L                | L                | Х                               | Х                          | Z                                    | Н                                    | Н                               | Н                               | Н                               | L                          | L                                    | Н      | Н                               | Н                 | Н                                    | L                               | L                               | Н                               | Н      |

| Up                                                 |               | H<br>H<br>H<br>H | L<br>L<br>L<br>L |                                 | L<br>L<br>L<br>L           | Z<br>Z<br>Z<br>Z<br>Z<br>Z           | X<br>X<br>X<br>X                     | X<br>X<br>X<br>X<br>X           | X<br>X<br>X<br>X                | X<br>X<br>X<br>X                | X<br>X<br>X<br>X           | X<br>X<br>X<br>X<br>X                | HHLLL  | H<br>H<br>L<br>L                | H<br>H<br>L<br>L  | H<br>H<br>L<br>L                     | L<br>H<br>L<br>L                | H<br>H<br>L<br>H<br>L           | H<br>H<br>H<br>H                | H      |

| Hold                                               | H<br>H        | H<br>H           | L<br>L           | X<br>X                          | X<br>X                     | Z<br>Z                               | X                                    | X<br>X                          | X                               | X<br>X                          | X<br>X                     | X<br>X                               | L<br>L | L<br>L                          | L<br>L            | L<br>L                               | H<br>H                          | L<br>L                          | H<br>H                          | H<br>H |

| Down<br>Hold<br>Down<br>Hold                       | H H H H H H H | L<br>L<br>L<br>L |                  | L<br>H<br>L<br>H<br>H<br>L<br>L | L<br>L<br>L<br>H<br>H<br>L | Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z | ×<br>×<br>×<br>×<br>×<br>×           | ×<br>×<br>×<br>×<br>×<br>×      | X<br>X<br>X<br>X<br>X<br>X      | ×<br>×<br>×<br>×<br>×<br>×      | ×<br>×<br>×<br>×<br>×<br>× | X<br>X<br>X<br>X<br>X<br>X           |        |                                 |                   |                                      | L<br>L<br>L<br>L                | HLLLLL                          | H<br>H<br>H<br>H<br>L           |        |

| Hold<br>Preset<br>Up<br>Hold<br>Up<br>Hold<br>Hold | H             | H                |                  | LXLLHLHHL                       | L<br>X<br>L<br>L<br>L<br>L | Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z | X<br>H<br>X<br>X<br>X<br>X<br>X<br>X | X<br>H<br>X<br>X<br>X<br>X<br>X | X<br>H<br>X<br>X<br>X<br>X<br>X | X<br>H<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X<br>X | X<br>L<br>X<br>X<br>X<br>X<br>X<br>X |        | L<br>H<br>H<br>H<br>H<br>H<br>H | L H H H H H H H H | L<br>H<br>H<br>H<br>H<br>H<br>H<br>H | L<br>L<br>H<br>H<br>H<br>H<br>H | L<br>H<br>L<br>H<br>H<br>H<br>H | L<br>H<br>H<br>H<br>L<br>H<br>L |        |

| Up                                                 |               | H<br>H<br>H      | L<br>L<br>L      | L<br>L<br>L                     | L<br>L<br>L                | Z<br>Z<br>Z<br>Z                     | X<br>X<br>X                          | X<br>X<br>X                     | X<br>X<br>X                     | X<br>X<br>X                     | X<br>X<br>X                | X<br>X<br>X                          | LLL    | L<br>L<br>L                     | L<br>L<br>L       | L<br>L<br>L                          | L<br>L<br>H                     | L<br>H<br>L<br>H                | H<br>H<br>H                     | HHH    |

| Reset                                              | Х             | Χ                | Н                | Χ                               | Χ                          | Χ                                    | Х                                    | Χ                               | Χ                               | Χ                               | Χ                          | Χ                                    | L      | L                               | L                 | L                                    | L                               | L                               | Н                               | Н      |

Z = Low to High Transition

**Table 4. MAXIMUM RATINGS**

| Symbol            | Parameter                                          | Condition 1                                    | Condition 2                                | Rating                     | Unit     |

|-------------------|----------------------------------------------------|------------------------------------------------|--------------------------------------------|----------------------------|----------|

| V <sub>CC</sub>   | PECL Mode Power Supply                             | V <sub>EE</sub> = 0 V                          |                                            | 8                          | V        |

| V <sub>EE</sub>   | NECL Mode Power Supply                             | V <sub>CC</sub> = 0 V                          |                                            | -8                         | V        |

| VI                | PECL Mode Input Voltage<br>NECL Mode Input Voltage | V <sub>EE</sub> = 0 V<br>V <sub>CC</sub> = 0 V | $V_{I} \leq V_{CC}$<br>$V_{I} \geq V_{EE}$ | 6<br>-6                    | V<br>V   |

| l <sub>out</sub>  | Output Current                                     | Continuous<br>Surge                            |                                            | 50<br>100                  | mA<br>mA |

| T <sub>A</sub>    | Operating Temperature Range                        |                                                |                                            | 0 to +85                   | °C       |

| T <sub>stg</sub>  | Storage Temperature Range                          |                                                |                                            | -65 to +150                | °C       |

| θЈА               | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | PLCC-28<br>PLCC-28                         | 63.5<br>43.5               | °C/W     |

| $\theta_{\sf JC}$ | Thermal Resistance (Junction-to-Case)              | Standard Board                                 | PLCC-28                                    | 22 to 26                   | °C/W     |

| V <sub>EE</sub>   | PECL Operating Range<br>NECL Operating Range       |                                                |                                            | 4.2 to 5.7<br>-5.7 to -4.2 | V<br>V   |

| T <sub>sol</sub>  | Wave Solder Pb Pb-Free                             |                                                |                                            | 265<br>265                 | °C       |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Table 5. 10E SERIES PECL DC CHARACTERISTICS  $V_{CCx} = 5.0 \text{ V}$ ;  $V_{EE} = 0.0 \text{ V}$  (Note 1)

|                 |                              | 0°C  |      |      | 25°C |      |      | 85°C |      |      |      |

|-----------------|------------------------------|------|------|------|------|------|------|------|------|------|------|

| Symbol          | Characteristic               | Min  | Тур  | Max  | Min  | Тур  | Max  | Min  | Тур  | Max  | Unit |

| I <sub>EE</sub> | Power Supply Current         |      | 125  | 150  |      | 125  | 150  |      | 125  | 150  | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 2) | 3980 | 4070 | 4160 | 4020 | 4105 | 4190 | 4090 | 4185 | 4280 | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 2)  | 3050 | 3210 | 3370 | 3050 | 3210 | 3370 | 3050 | 3227 | 3405 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage           | 3830 | 3995 | 4160 | 3870 | 4030 | 4190 | 3940 | 4110 | 4280 | mV   |

| V <sub>IL</sub> | Input LOW Voltage            | 3050 | 3285 | 3520 | 3050 | 3285 | 3520 | 3050 | 3302 | 3555 | mV   |

| I <sub>IH</sub> | Input HIGH Current           |      |      | 150  |      |      | 150  |      |      | 150  | μΑ   |

| I <sub>IL</sub> | Input LOW Current            | 0.5  | 0.3  |      | 0.5  | 0.25 |      | 0.3  | 0.2  |      | μΑ   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

- 1. Input and output parameters vary 1:1 with  $V_{CC}$ .  $V_{EE}$  can vary -0.46~V / +0.06~V.

- 2. Outputs are terminated through a 50  $\Omega$  resistor to  $V_{CC}$  2.0 V.

Table 6. 10E SERIES NECL DC CHARACTERISTICS V<sub>CCx</sub> = 0.0 V; V<sub>EE</sub> = -5.0 V (Note 3)

|                 |                              | 0°C   |       |       |       | 25°C  |       |       |       |       |      |

|-----------------|------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol          | Characteristic               | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EE</sub> | Power Supply Current         |       | 125   | 150   |       | 125   | 150   |       | 125   | 150   | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 4) | -1020 | -930  | -840  | -980  | -895  | -810  | -910  | -815  | -720  | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 4)  | -1950 | -1790 | -1630 | -1950 | -1790 | -1630 | -1950 | -1773 | -1595 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage           | -1170 | -1005 | -840  | -1130 | -970  | -810  | -1060 | -890  | -720  | mV   |

| V <sub>IL</sub> | Input LOW Voltage            | -1950 | -1715 | -1480 | -1950 | -1715 | -1480 | -1950 | -1698 | -1445 | mV   |

| I <sub>IH</sub> | Input HIGH Current           |       |       | 150   |       |       | 150   |       |       | 150   | μΑ   |

| I <sub>IL</sub> | Input LOW Current            | 0.5   | 0.3   |       | 0.5   | 0.065 |       | 0.3   | 0.2   |       | μΑ   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

- 3. Input and output parameters vary 1:1 with V<sub>CC</sub>. V<sub>EE</sub> can vary –0.46 V / +0.06 V.

- 4. Outputs are terminated through a 50  $\Omega$  resistor to V<sub>CC</sub> 2.0 V.

Table 7. 100E SERIES PECL DC CHARACTERISTICS  $V_{CCx} = 5.0 \text{ V}$ ;  $V_{EE} = 0.0 \text{ V}$  (Note 5)

|                 |                              | 0°C  |      | 25°C |      |      | 85°C |      |      |      |      |

|-----------------|------------------------------|------|------|------|------|------|------|------|------|------|------|

| Symbol          | Characteristic               | Min  | Тур  | Max  | Min  | Тур  | Max  | Min  | Тур  | Max  | Unit |

| I <sub>EE</sub> | Power Supply Current         |      | 125  | 150  |      | 125  | 150  |      | 140  | 170  | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 6) | 3975 | 4050 | 4120 | 3975 | 4050 | 4120 | 3975 | 4050 | 4120 | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 6)  | 3190 | 3295 | 3380 | 3190 | 3255 | 3380 | 3190 | 3260 | 3380 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage           | 3835 | 3975 | 4120 | 3835 | 3975 | 4120 | 3835 | 3975 | 4120 | mV   |

| V <sub>IL</sub> | Input LOW Voltage            | 3190 | 3355 | 3525 | 3190 | 3355 | 3525 | 3190 | 3355 | 3525 | mV   |

| I <sub>IH</sub> | Input HIGH Current           |      |      | 150  |      |      | 150  |      |      | 150  | μΑ   |

| I <sub>IL</sub> | Input LOW Current            | 0.5  | 0.3  |      | 0.5  | 0.25 |      | 0.5  | 0.2  |      | μΑ   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

- 5. Input and output parameters vary 1:1 with  $V_{CC}$ .  $V_{EE}$  can vary -0.46~V / +0.8~V.

- 6. Outputs are terminated through a 50  $\Omega$  resistor to VCC 2.0 V.

Table 8. 100E SERIES NECL DC CHARACTERISTICS  $V_{CCx} = 0.0 \text{ V}$ ;  $V_{EE} = -5.0 \text{ V}$  (Note 7)

|                  |                              |       | 0°C   |       |       | 25°C  |       |       | 85°C  |       |      |

|------------------|------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol           | Characteristic               | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EEf</sub> | Power Supply Current         |       | 125   | 150   |       | 125   | 150   |       | 140   | 170   | mA   |

| V <sub>OH</sub>  | Output HIGH Voltage (Note 8) | -1025 | -950  | -880  | -1025 | -950  | -880  | -1025 | -950  | -880  | mV   |

| V <sub>OL</sub>  | Output LOW Voltage (Note 8)  | -1810 | -1705 | -1620 | -1810 | -1745 | -1620 | -1810 | -1740 | -1620 | mV   |

| V <sub>IH</sub>  | Input HIGH Voltage           | -1165 | -1025 | -880  | -1165 | -1025 | -880  | -1165 | -1025 | -880  | mV   |

| V <sub>IL</sub>  | Input LOW Voltage            | -1810 | -1645 | -1475 | -1810 | -1645 | -1475 | -1810 | -1645 | -1475 | mV   |

| I <sub>IH</sub>  | Input HIGH Current           |       |       | 150   |       |       | 150   |       |       | 150   | μΑ   |

| I <sub>IL</sub>  | Input LOW Current            | 0.5   | 0.3   |       | 0.5   | 0.25  |       | 0.5   | 0.2   |       | μΑ   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

- 7. Input and output parameters vary 1:1 with  $V_{CC}$ .  $V_{EE}$  can vary -0.46 V / +0.8 V.

- 8. Outputs are terminated through a 50  $\Omega$  resistor to  $V_{CC}$  2.0 V.

Table 9. AC CHARACTERISTICS  $V_{CCx} = 5.0 \text{ V}$ ;  $V_{EE} = 0.0 \text{ V}$  or  $V_{CCx} = 0.0 \text{ V}$ ;  $V_{EE} = -5.0 \text{ V}$  (Note 9)

|                                      |                                                                           |                           | 0°C                          |                              |                           | 25°C                         |                              |                           | 85°C                         |                              |      |

|--------------------------------------|---------------------------------------------------------------------------|---------------------------|------------------------------|------------------------------|---------------------------|------------------------------|------------------------------|---------------------------|------------------------------|------------------------------|------|

| Symbol                               | Characteristic                                                            | Min                       | Тур                          | Max                          | Min                       | Тур                          | Max                          | Min                       | Тур                          | Max                          | Unit |

| f <sub>COUNT</sub>                   | Maximum Count Frequency                                                   | 550                       | 650                          | -                            | 550                       | 650                          | -                            | 550                       | 650                          | -                            | MHz  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay to Output  CLK to Q  MR to Q  CLK to COUT  CLK to CLOUT | 850<br>850<br>800<br>825  | 1150<br>1150<br>1150<br>1150 | 1450<br>1450<br>1300<br>1400 | 850<br>850<br>800<br>825  | 1150<br>1150<br>1150<br>1150 | 1450<br>1450<br>1300<br>1400 | 850<br>850<br>800<br>825  | 1150<br>1150<br>1150<br>1150 | 1450<br>1450<br>1300<br>1400 | ps   |

| t <sub>s</sub>                       | Setup Time S1, S2 D CLIN CIN                                              | 1000<br>800<br>150<br>800 | 650<br>400<br>0<br>400       | -<br>-<br>-<br>-             | 1000<br>800<br>150<br>800 | 650<br>400<br>0<br>400       | -<br>-<br>-                  | 1000<br>800<br>150<br>800 | 650<br>400<br>0<br>400       | -<br>-<br>-                  | ps   |

| t <sub>h</sub>                       | Hold Time S1, S2 D CLIN CIN                                               | 150<br>150<br>300<br>150  | -200<br>-250<br>0<br>-250    | -<br>-<br>-<br>-             | 150<br>150<br>300<br>150  | -200<br>-250<br>0<br>-250    | -<br>-<br>-                  | 150<br>150<br>300<br>150  | -200<br>-250<br>0<br>-250    | -<br>-<br>-<br>-             | ps   |

| t <sub>RR</sub>                      | Reset Recovery Time                                                       | 1000                      | 700                          | -                            | 1000                      | 700                          | -                            | 1000                      | 700                          | _                            | ps   |

| t <sub>JITTER</sub>                  | Random Clock Jitter                                                       |                           | < 1                          |                              |                           | < 1                          |                              |                           | < 1                          |                              | ps   |

| t <sub>PW</sub>                      | Minimum Pulse Width CLK, MR                                               | 700                       | 400                          | _                            | 700                       | 400                          | -                            | 700                       | 400                          | -                            | ps   |

| t <sub>r</sub><br>t <sub>f</sub>     | Rise/Fall Times 20% - 80%                                                 | 250                       | 425                          | 600                          | 250                       | 425                          | 600                          | 250                       | 425                          | 600                          | ps   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

<sup>9. 10</sup> Series:  $V_{EE}$  can vary -0.46 V / +0.06 V. 100 Series:  $V_{EE}$  can vary -0.46 V / +0.8 V.

#### **APPLICATIONS INFORMATION**

#### Overview

The MC10E/100E136 is a 6-bit synchronous, presettable, cascadable universal counter. Using the S1 and S2 control pins the user can select between preset, count up, count down and hold count. The master reset pin will reset the internal counter, and set the  $\overline{\text{COUT}}$ ,  $\overline{\text{CLOUT}}$ , and  $\overline{\text{CLIN}}$  flip-flops. Unlike previous 136 type counters the carry out outputs will go to a high state during the preset operation. In addition since the carry out outputs are registered they will not go low if terminal count is loaded into the register. The look-ahead-carry out output functions similarly.

Note from the schematic the use of the master information from the least significant bits for control of the two carry out functions. This architecture not only reduces the carry out delay, but is essential to incorporate the registered carry out functions. In addition to being faster, because these functions are registered the resulting carry out signals are stable and glitch free.

### **Cascading Multiple E136 Devices**

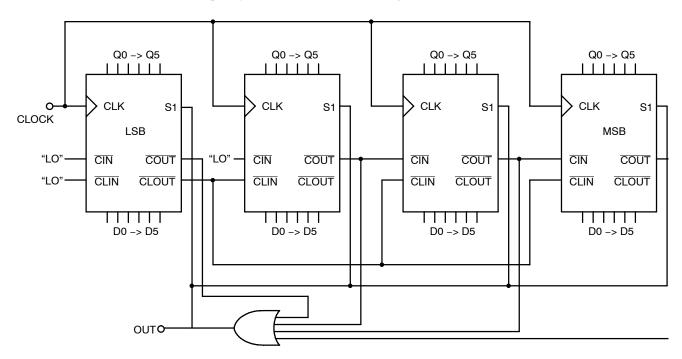

Many applications require counters significantly larger than the 6 bits available with the E136. For these applications several E136 devices can be cascaded to increase the bit width of the counter to meet the needs of the application.

In the past cascading several 136 type universal counters necessarily impacted the maximum count frequency of the resulting counter chain. This performance impact was the result of the terminal count signal of the lower order counters having to ripple through the entire counter chain. As a result past counters of this type were not widely used in large bit counter applications.

An alternative counter architecture similar to the E016 binary counter was implemented to alleviate the need to ripple propagate the terminal count signal. Unfortunately these types of counters require external gating for cascading designs of more than two devices. In addition to requiring additional components, these external gates limit the cascaded count frequency to a value less than the free running count frequency of a single counter. Although there is a performance impact with this type of architecture it is minor compared to the impact of the ripple propagate designs. As a result the E016 type counters have been used extensively in applications requiring very high speed, wide bit width synchronous counters.

ON Semiconductor has incorporated several improvements to past universal counter designs in the E136 universal counter. These enhancements make the E136 the unparalleled leader in its class. With the addition of look-ahead-carry features on the terminal count signal, very large counter chains can be designed which function at very nearly the same clock frequency as a single free running device. More importantly these counter chains require no external gating. Figure 1 below illustrates the interconnect scheme for using the look-ahead-carry features of the E136 counter.

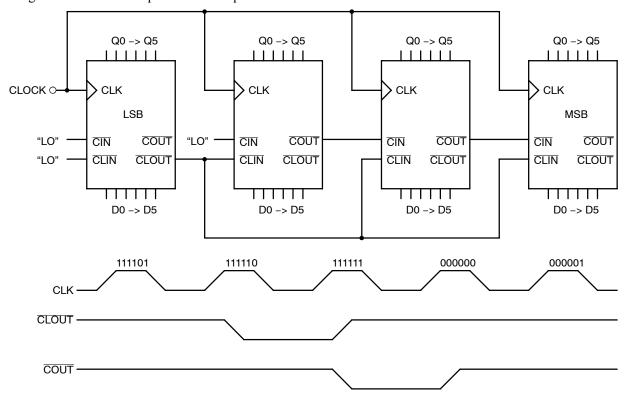

Figure 3. 24-bit Cascaded E136 Counter

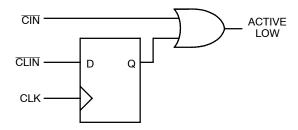

Figure 4. Look-Ahead-Carry Input Structure

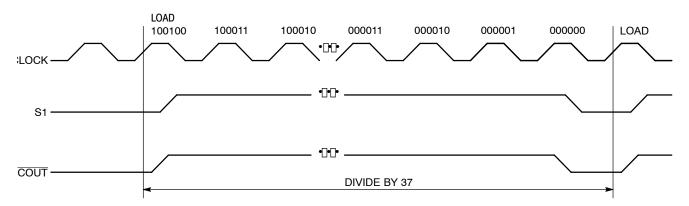

Note from the waveforms that the look-ahead-carry output ( $\overline{\text{CLOUT}}$ ) pulses low one clock pulse before the counter reaches terminal count. Also note that both  $\overline{\text{CLOUT}}$  and the carry out pin ( $\overline{\text{COUT}}$ ) of the device pulse low for only one clock period. The input structure for look-ahead-carry in ( $\overline{\text{CLIN}}$ ) and carry in ( $\overline{\text{CIN}}$ ) is pictured in Figure 2.

The  $\overline{\text{CLIN}}$  input is registered and then ORed with the  $\overline{\text{CIN}}$  input. From the truth table one can see that both the  $\overline{\text{CIN}}$  and the  $\overline{\text{CLIN}}$  inputs must be in a LOW state for the E136 to be enabled to count (either count up or count down). The  $\overline{\text{CLIN}}$  inputs are driven by the  $\overline{\text{CLOUT}}$  output of the lowest order E136 and therefore are only asserted for a single clock period. Since the  $\overline{\text{CLIN}}$  input is registered it must be asserted one clock period prior to the  $\overline{\text{CIN}}$  input.

If the counter previous to a given counter is at terminal count its  $\overline{\text{COUT}}$  output and thus the  $\overline{\text{CIN}}$  input of the given counter will be in the "LOW" state. This signals the given counter that it will need to count one upon the next terminal count of the least significant counter (LSC). The  $\overline{\text{CLOUT}}$  output of the LSC will pulse low one clock period before it reaches terminal count. This  $\overline{\text{CLOUT}}$  signal will be clocked into the  $\overline{\text{CLIN}}$  input of the higher order counters on the following positive clock transition. Since both  $\overline{\text{CIN}}$  and  $\overline{\text{CLIN}}$  are in the LOW state the next clock pulse will cause the least significant counter to roll over and all higher order counters, if signaled by their  $\overline{\text{CIN}}$  inputs, to count by one.

Figure 5. 6-bit Programmable Divider

During the clock pulse in which the higher order counter is counting by one the  $\overline{\text{CLIN}}$  is clocking in the high signal

presented by the  $\overline{\text{CLOUT}}$  of the LSC. The  $\overline{\text{CIN}}$ 's in the higher order counter will ripple propagate through the chain to update the count status for the next occurrence of terminal count on the LSC. This ripple propagation will not affect the count frequency as it has  $2^6-1$  or 63 clock pulses to ripple through without affecting the count operation of the chain.

The only limiting factor which could reduce the count frequency of the chain as compared to a free running single device will be the setup time of the  $\overline{\text{CLIN}}$  input. This limit will consist of the CLK to  $\overline{\text{CLOUT}}$  delay of the E136 plus the  $\overline{\text{CLIN}}$  setup time plus any path length differences between the  $\overline{\text{CLOUT}}$  output and the clock.

# **Programmable Divider**

Using external feedback of the  $\overline{\text{COUT}}$  pin, the E136 can be configured as a programmable divider. Figure 3 illustrates the configuration for a 6-bit count down programmable divider. If for some reason a count up divider is preferred the  $\overline{\text{COUT}}$  signal is simply fed back to S2 rather than S1. Examination of the truth table for the E136 shows that when both S1 and S2 are LOW the counter will parallel load on the next positive transition of the clock. If the S2 input is low and the S1 input is high the counter will be in the count down mode and will count towards an all zero state upon successive clock pulses. Knowing this and the operation of the  $\overline{\text{COUT}}$  output it becomes a trivial matter to build programmable dividers.

For a programmable divider one wants to load a predesignated number into the counter and count to terminal count. Upon terminal count the counter should automatically reload the divide number. With the architecture shown in Figure 3 when the counter reaches terminal count the  $\overline{\text{COUT}}$  output and thus the S1 input will go LOW, this combined with the low on S2 will cause the counter to load the inputs present on D0-D5. Upon loading the divide value into the counter  $\overline{\text{COUT}}$  will go HIGH as the counter is no longer at terminal count thereby placing the counter back into the count mode.

**Table 10. Preset Inputs Versus Divide Ratio**

| Divide                                                              |    | Preset Data Inputs |    |    |               |         |  |  |  |

|---------------------------------------------------------------------|----|--------------------|----|----|---------------|---------|--|--|--|

| Ratio                                                               | D5 | D4                 | D3 | D2 | D1            | D0      |  |  |  |

| 2<br>3<br>4<br>5<br>•<br>36<br>37<br>38<br>•<br>•<br>62<br>63<br>64 |    |                    |    |    | L H H L L H H | ILIILI. |  |  |  |

Figure 6. Programmable Divider Waveforms

The exercise of building a programmable divider then becomes simply determining what value to load into the counter to accomplish the desired division. Since the load operation requires a clock pulse, to divide by N, N-1 must be loaded into the counter. A single E136 device is capable of divide ratios of 2 to 64 inclusive, Table 1 outlines the load values for the various divide ratios. Figure 4 presents the waveforms resulting from a divide by 37 operation. Note that the availability of the COUT complementary output  $\overline{\text{COUT}}$  allows the user to choose the polarity of the divide by output.

For single device programmable counters the E016 counter is probably a better choice than the E136. The E016 has an internal feedback to control the reloading of the counter, this not only simplifies board design but also will result in a faster maximum count frequency.

For programmable dividers of larger than 8 bits the superiority of the E016 diminishes, and in fact for very wide dividers the E136 will provide the capability of a faster count frequency. This potential is a result of the cascading features mentioned previously in this document. Figure 5 shows the architecture of a 24-bit programmable divider implemented using E136 counters. Note the need for one external gate to control the loading of the entire counter chain. An ideal device for the external gating of this architecture would be the 4-input OR function in the 8-lead SOIC ECLinPS Lite™ family. However the final decision as to what device to use for the external gating requires a balancing of performance needs, cost and available board space. Note that because of the need for external gating the maximum count frequency of a given sized programmable divider will be less than that of a single cascaded counter.

Figure 7. 24-bit Programmable Divider Architecture

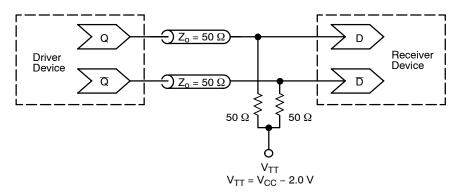

Figure 8. Typical Termination for Output Driver and Device Evaluation (See Application Note AND8020/D – Termination of ECL Logic Devices.)

### **ORDERING INFORMATION**

| Device         | Package              | Shipping <sup>†</sup> |

|----------------|----------------------|-----------------------|

| MC10E136FN     | PLCC-28              | 37 Units / Rail       |

| MC10E136FNG    | PLCC-28<br>(Pb-Free) | 37 Units / Rail       |

| MC10E136FNR2   | PLCC-28              | 500 / Tape & Reel     |

| MC10E136FNR2G  | PLCC-28<br>(Pb-Free) | 500 / Tape & Reel     |

| MC100E136FN    | PLCC-28              | 37 Units / Rail       |

| MC100E136FNG   | PLCC-28<br>(Pb-Free) | 37 Units / Rail       |

| MC100E136FNR2  | PLCC-28              | 500 / Tape & Reel     |

| MC100E136FNR2G | PLCC-28<br>(Pb-Free) | 500 / Tape & Reel     |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# **Resource Reference of Application Notes**

AN1405/D - ECL Clock Distribution Techniques

AN1406/D - Designing with PECL (ECL at +5.0 V)

AN1503/D - ECLinPS™ I/O SPiCE Modeling Kit

AN1504/D - Metastability and the ECLinPS Family

AN1568/D - Interfacing Between LVDS and ECL

AN1672/D - The ECL Translator Guide

AND8001/D - Odd Number Counters Design

AND8002/D - Marking and Date Codes

AND8020/D - Termination of ECL Logic Devices

AND8066/D - Interfacing with ECLinPS

AND8090/D - AC Characteristics of ECL Devices

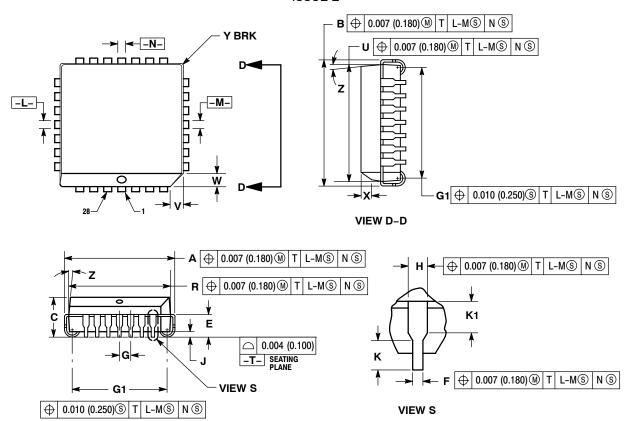

#### PACKAGE DIMENSIONS

#### PLCC-28 **FN SUFFIX**

PLASTIC PLCC PACKAGE CASE 776-02 ISSUE E

- DATUMS -L-, -M-, AND -N- DETERMINED

WHERE TOP OF LEAD SHOULDER EXITS

- PLASTIC BODY AT MOLD PARTING LINE.

2. DIMENSION G1, TRUE POSITION TO BE MEASURED AT DATUM -T-, SEATING PLANE.

3. DIMENSIONS R AND U DO NOT INCLUDE

- MOLD FLASH. ALLOWABLE MOLD FLASH IS 0.010 (0.250) PER SIDE.

- 0.010 (0.250) PER SIDE.

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

5. CONTROLLING DIMENSION: INCH.

6. THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM BY UP TO 0.012 (0.300). DIMENSIONS R AND U ARE DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BUIRDS, GATE BUIRDS, AND INTERLIFAD. BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

- 7. DIMENSION H DOES NOT INCLUDE DAMBAR PROTRUSION OR INTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE GREATER THAN 0.037 (0.940). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE SMALLER THAN 0.025 (0.635).

|     | INC   | HES   | MILLIN | IETERS |

|-----|-------|-------|--------|--------|

| DIM | MIN   | MAX   | MIN    | MAX    |

| Α   | 0.485 | 0.495 | 12.32  | 12.57  |

| В   | 0.485 | 0.495 | 12.32  | 12.57  |

| C   | 0.165 | 0.180 | 4.20   | 4.57   |

| Е   | 0.090 | 0.110 | 2.29   | 2.79   |

| F   | 0.013 | 0.019 | 0.33   | 0.48   |

| G   | 0.050 | BSC   | 1.27   | BSC    |

| Н   | 0.026 | 0.032 | 0.66   | 0.81   |

| 7   | 0.020 |       | 0.51   |        |

| K   | 0.025 |       | 0.64   |        |

| R   | 0.450 | 0.456 | 11.43  | 11.58  |

| 5   | 0.450 | 0.456 | 11.43  | 11.58  |

| ٧   | 0.042 | 0.048 | 1.07   | 1.21   |

| W   | 0.042 | 0.048 | 1.07   | 1.21   |

| Х   | 0.042 | 0.056 | 1.07   | 1.42   |

| Υ   |       | 0.020 |        | 0.50   |

| Z   | 2 °   | 10°   | 2°     | 10°    |

| G1  | 0.410 | 0.430 | 10.42  | 10.92  |

| K1  | 0.040 |       | 1.02   |        |

ECLinPS and ECLinPS Lite are trademarks of Semiconductor Components Industries, LLC (SCILLC).

ON Semiconductor and the registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

# Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.