# Isolated Precision Half-Bridge Driver, 4 A Output

# **Data Sheet**

## FEATURES

4 A peak output current Working voltage High-side or low-side relative to input: 537 V peak High frequency operation: 1 MHz maximum 3.3 V to 5 V CMOS input logic 4.5 V to 18 V output drive Secondary UVLO ADuM3224A/ADuM4224A UVLO at 4.1 V VDDA/VDDB ADuM3224B/ADuM4224B UVLO at 6.9 V VDDA/VDDB ADuM3224C/ADuM4224C UVLO at 10.5 V VDDA/VDDB **Precise timing characteristics** 59 ns maximum isolator and driver propagation delay 5 ns maximum channel-to-channel matching **CMOS input logic levels** High common-mode transient immunity: >25 kV/µs Enhanced system-level ESD performance per IEC 61000-4-x High junction temperature operation: 125°C **Default low output** Safety and regulatory approvals ADuM3224 narrow-body, 16-lead SOIC UL recognition per UL 1577 3000 V rms for 1 minute SOIC long package **CSA Component Acceptance Notice 5A** VDE certificate of conformity (pending) DIN V VDE V 0884-10 (VDE V 0884-10):2006-12  $V_{IORM} = 560 V peak$ ADuM4224 wide-body, 16-lead SOIC UL recognition per UL 1577 5000 V rms for 1 minute SOIC long package **CSA Component Acceptance Notice 5A** VDE certificate of conformity (pending) DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 **V**<sub>IORM</sub> = **849 V peak Qualified for automotive applications APPLICATIONS** Switching power supplies

Switching power supplies Isolated IGBT/MOSFET gate drives Industrial inverters

# ADuM3224/ADuM4224

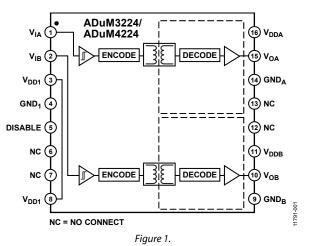

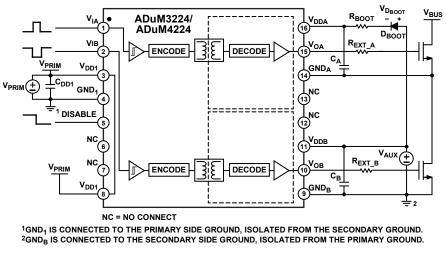

# FUNCTIONAL BLOCK DIAGRAM

### **GENERAL DESCRIPTION**

TheADuM3224/ADuM4224<sup>1</sup> are 4 A isolated, half-bridge gate drivers that employ the Analog Devices, Inc., *i*Coupler\* technology to provide independent and isolated high-side and low-side outputs. The ADuM3224 provides 3000 V rms isolation in the narrow-body, 16-lead SOIC package, and the ADuM4224 provides 5000 V rms isolation in the wide-body, 16-lead SOIC package. Combining high speed CMOS and monolithic transformer technology, these isolation components provide outstanding performance characteristics superior to the alternatives, such as the combination of pulse transformers and gate drivers.

The ADuM3224/ADuM4224 isolators each provide two independent isolated channels. They operate with an input supply ranging from 3.0 V to 5.5 V, providing compatibility with lower voltage systems. In comparison to gate drivers employing high voltage level translation methodologies, the ADuM3224/ADuM4224 offer the benefit of true, galvanic isolation between the input and each output. Each output can be continuously operated up to 537 V peak relative to the input, thereby supporting low-side switching to negative voltages. The differential voltage between the high-side and low-side can be as high as 800 V peak.

As a result, the ADuM3224/ADuM4224 provide reliable control over the switching characteristics of IGBT/MOSFET configurations over a wide range of positive or negative switching voltages.

<sup>1</sup> Protected by U.S. Patents 5,952,849; 6,873,065; and 7,075,239. Other patents pending.

Rev. B

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013–2015 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features                                                          | 1 |

|-------------------------------------------------------------------|---|

| Applications                                                      | 1 |

| Functional Block Diagram                                          | 1 |

| General Description                                               | 1 |

| Revision History                                                  | 2 |

| Specifications                                                    | 3 |

| Electrical Characteristics—5 V Operation                          | 3 |

| Electrical Characteristics—3.3 V Operation                        | 4 |

| Package Characteristics                                           | 5 |

| Insulation and Safety Related Specifications                      | 5 |

| Regulatory Information                                            | 6 |

| DIN V VDE V 0884-10 (VDE V 0884-10) Insulation<br>Characteristics | 7 |

| Recommended Operating Conditions                                  | 8 |

| Absolute Maximum Ratings                                          | 9 |

| ESD Caution                                                       | 9 |

### **REVISION HISTORY**

| 11/15—Rev. A to Rev. B               |

|--------------------------------------|

| Changes to Power Consumption Section |

#### 11/14—Rev. 0 to Rev. A

| Changes to Features Section and General Description     |   |

|---------------------------------------------------------|---|

| Section                                                 | 1 |

| Changes to Table 5                                      | 5 |

| Changes to Regulatory Information Section, Table 6, and |   |

| Table 7                                                 | 6 |

| Changes to Table 8 and Table 9                          | 7 |

12/13—Revision 0: Initial Version

# SPECIFICATIONS

# **ELECTRICAL CHARACTERISTICS—5 V OPERATION**

All voltages are relative to their respective ground. 4.5 V  $\leq$  V<sub>DD1</sub>  $\leq$  5.5 V, 4.5 V  $\leq$  V<sub>DDA</sub>  $\leq$  18 V, 4.5 V  $\leq$  V<sub>DDB</sub>  $\leq$  18 V, unless stated otherwise. All minimum/maximum specifications apply over T<sub>J</sub> = -40°C to +125°C. All typical specifications are at T<sub>J</sub> = 25°C, V<sub>DD1</sub> = 5 V, V<sub>DDA</sub> = V<sub>DDB</sub> = 12 V. Switching specifications are tested with CMOS signal levels.

| Parameter                                                                        | Symbol                                    | Min                                          | Тур                                    | Max                  | Unit    | Test Conditions/Comments                                                     |

|----------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------|----------------------------------------|----------------------|---------|------------------------------------------------------------------------------|

| DC SPECIFICATIONS                                                                | Symbol                                    | MIII                                         | тур                                    | IVIAX                | Unit    | Test conditions/comments                                                     |

|                                                                                  | la a vas                                  |                                              | 1.4                                    | 2.4                  | mA      |                                                                              |

| Input Supply Current, Quiescent<br>Output Supply Current, Per Channel, Quiescent |                                           |                                              | 2.3                                    | 2.4<br>3.2           | mA      |                                                                              |

|                                                                                  | IDDO(Q)                                   |                                              | 2.5                                    | 5.2                  | IIIA    |                                                                              |

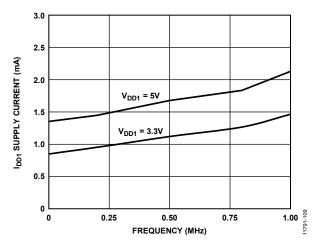

| Supply Current at 1 MHz                                                          | 1                                         |                                              | 1.6                                    | 2.5                  | mA      | Up to 1 MHz, no load                                                         |

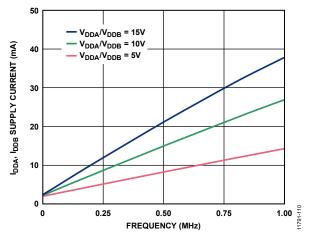

| V <sub>DD1</sub> Supply Current                                                  |                                           |                                              | 5.6                                    | 2.5<br>8.0           |         | •                                                                            |

|                                                                                  | Idda(q)/Iddb(q)<br>Iia, Iib               | -1                                           | 5.0<br>+0.01                           |                      | mA<br>A | Up to 1 MHz, no load                                                         |

| Input Currents                                                                   | VIH                                       |                                              | +0.01                                  | +1                   | μA<br>V | $0 V \leq V_{\text{IA}}, V_{\text{IB}} \leq V_{\text{DD1}}$                  |

| Logic High Input Threshold                                                       |                                           | $0.7 \times V_{DD1}$                         |                                        | 0.2                  | -       |                                                                              |

| Logic Low Input Threshold                                                        | VIL                                       | N/ /                                         |                                        | $0.3 \times V_{DD1}$ | V       |                                                                              |

| Logic High Output Voltages                                                       | V <sub>oah</sub> , V <sub>obh</sub>       | V <sub>DDA</sub> /<br>V <sub>DDB</sub> – 0.1 | V <sub>DDA</sub> /<br>V <sub>DDB</sub> |                      | V       | $I_{Ox} = -20 \text{ mA}, V_{Ix} = V_{IxH}$                                  |

| Logic Low Output Voltages                                                        | Voal, Vobl                                |                                              | 0.0                                    | 0.15                 | V       | $I_{Ox} = +20 \text{ mA}, V_{Ix} = V_{IxL}$                                  |

| Undervoltage Lockout, V <sub>DDA</sub> /V <sub>DDB</sub> Supply                  |                                           |                                              |                                        |                      |         |                                                                              |

| A Grade                                                                          |                                           |                                              |                                        |                      |         |                                                                              |

| Positive Going Threshold                                                         | V <sub>DDAUV+</sub> , V <sub>DDBUV+</sub> |                                              | 4.1                                    | 4.4                  | V       |                                                                              |

| Negative Going Threshold                                                         | VDDAUV-, VDDBUV-                          | 3.2                                          | 3.6                                    |                      | V       |                                                                              |

| Hysteresis                                                                       | V <sub>DDAUVH</sub> , V <sub>DDBUVH</sub> |                                              | 0.5                                    |                      | V       |                                                                              |

| B Grade                                                                          |                                           |                                              |                                        |                      |         |                                                                              |

| Positive Going Threshold                                                         | VDDAUV+, VDDBUV+                          |                                              | 6.9                                    | 7.4                  | V       |                                                                              |

| Negative Going Threshold                                                         | VDDAUV-, VDDBUV-                          | 5.7                                          | 6.2                                    |                      | V       |                                                                              |

| Hysteresis                                                                       | VDDAUVH, VDDBUVH                          |                                              | 0.7                                    |                      | V       |                                                                              |

| C Grade                                                                          |                                           |                                              |                                        |                      |         |                                                                              |

| Positive Going Threshold                                                         | VDDAUV+, VDDBUV+                          |                                              | 10.5                                   | 11.1                 | V       |                                                                              |

| Negative Going Threshold                                                         | V <sub>DDAUV-</sub> , V <sub>DDBUV-</sub> | 8.9                                          | 9.6                                    |                      | V       |                                                                              |

| Hysteresis                                                                       | VDDAUVH, VDDBUVH                          |                                              | 0.9                                    |                      | V       |                                                                              |

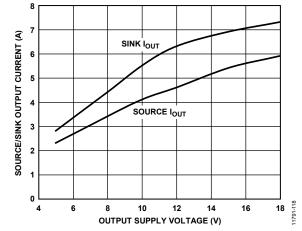

| Output Short-Circuit Pulsed Current <sup>1</sup>                                 | I <sub>OA(SC)</sub> , I <sub>OB(SC)</sub> | 2.0                                          | 4.0                                    |                      | А       | $V_{DDA}/V_{DDB} = 12 V$                                                     |

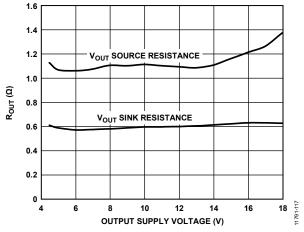

| Output Pulsed Source Resistance                                                  | Roa, Rob                                  | 0.3                                          | 1.1                                    | 3.0                  | Ω       | $V_{DDA}/V_{DDB} = 12 V$                                                     |

| Output Pulsed Sink Resistance                                                    | R <sub>OA</sub> , R <sub>OB</sub>         | 0.3                                          | 0.6                                    | 3.0                  | Ω       | $V_{DDA}/V_{DDB} = 12 V$                                                     |

| SWITCHING SPECIFICATIONS                                                         |                                           |                                              |                                        |                      |         |                                                                              |

| Pulse Width <sup>2</sup>                                                         | PW                                        | 50                                           |                                        |                      | ns      | $C_L = 2 nF, V_{DDA}/V_{DDB} = 12 V$                                         |

| Maximum Data Rate <sup>3</sup>                                                   |                                           | 1                                            |                                        |                      | MHz     | $C_L = 2 nF$ , $V_{DDA}/V_{DDB} = 12 V$                                      |

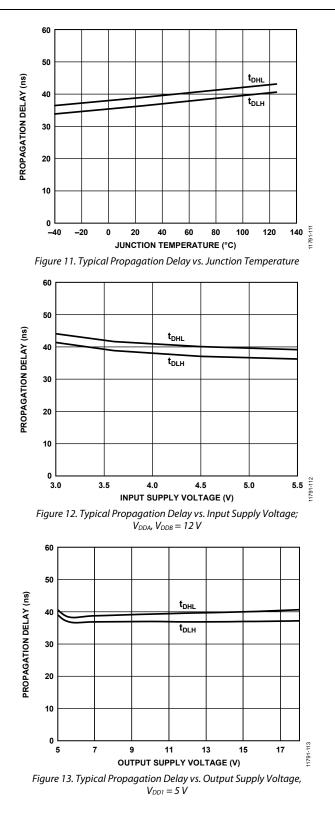

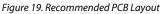

| Propagation Delay <sup>4</sup>                                                   | t <sub>DHL</sub> , t <sub>DLH</sub>       | 31                                           | 43                                     | 54                   | ns      | $C_L = 2 \text{ nF}$ , $V_{DDA}/V_{DDB} = 12 \text{ V}$ ; see Figure 20      |

| ADuM3224A/ADuM4224A                                                              | t <sub>DHL</sub> , t <sub>DLH</sub>       | 35                                           | 47                                     | 59                   | ns      | $C_L = 2 \text{ nF}, V_{DDA}/V_{DDB} = 4.5 \text{ V}; \text{ see Figure 20}$ |

| Propagation Delay Skew <sup>5</sup>                                              | t <sub>PSK</sub>                          |                                              |                                        | 12                   | ns      | $C_L = 2 \text{ nF}, V_{DDA}/V_{DDB} = 12 \text{ V}; \text{ see Figure 20}$  |

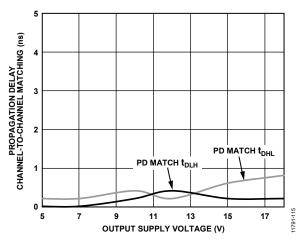

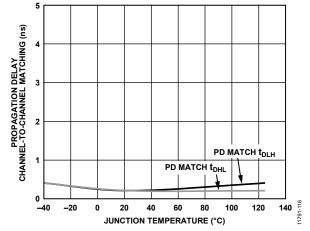

| Channel-to-Channel Matching <sup>6</sup>                                         | <b>t</b> <sub>PSKCD</sub>                 |                                              | 1                                      | 5                    | ns      | $C_L = 2 \text{ nF}, V_{DDA}/V_{DDB} = 12 \text{ V}; \text{ see Figure 20}$  |

| -                                                                                | t <sub>PSKCD</sub>                        |                                              | 1                                      | 7                    | ns      | $C_L = 2 \text{ nF}, V_{DDA}/V_{DDB} = 4.5 \text{ V}; \text{ see Figure 2C}$ |

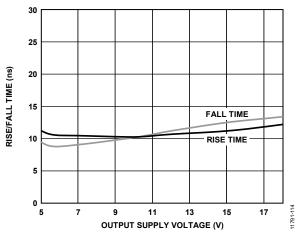

| Output Rise/Fall Time (10% to 90%)                                               | t <sub>R</sub> /t <sub>F</sub>            | 6                                            | 12                                     | 18                   | ns      | $C_L = 2 \text{ nF}, V_{DDA}/V_{DDB} = 12 \text{ V}; \text{ see Figure 20}$  |

| Dynamic Input Supply Current Per Channel                                         | I <sub>DDI(D)</sub>                       |                                              | 0.05                                   |                      | mA/Mbps | $V_{DDA}/V_{DDB} = 12 V$                                                     |

| Dynamic Output Supply Current Per Channel                                        | IDDO(D)                                   |                                              | 1.65                                   |                      | mA/Mbps | $V_{DDA}/V_{DDB} = 12 V$                                                     |

| Refresh Rate                                                                     | fr                                        |                                              | 1.2                                    |                      | Mbps    |                                                                              |

<sup>1</sup> Short-circuit duration less than 1 µs. Average power must conform to the limit shown in the Absolute Maximum Ratings section.

<sup>2</sup> The minimum pulse width is the shortest pulse width at which the specified timing parameter is guaranteed.

<sup>3</sup> The maximum data rate is the fastest data rate at which the specified timing parameter is guaranteed.

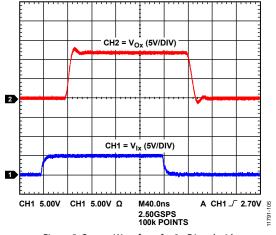

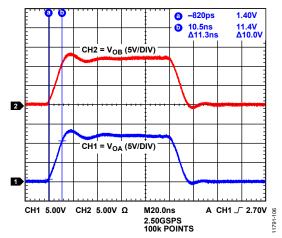

<sup>4</sup> The t<sub>DLH</sub> propagation delay is measured from the time of the input rising logic high threshold, V<sub>H</sub>, to the output rising 10% level of the V<sub>ox</sub> signal. The t<sub>DHL</sub> propagation delay is measured from the input falling logic low threshold, V<sub>IL</sub>, to the output falling 90% threshold of the V<sub>ox</sub> signal. See Figure 20 for waveforms of propagation delay parameters.

<sup>5</sup> t<sub>PSK</sub> is the magnitude of the worst-case difference in t<sub>DLH</sub> and/or t<sub>DHL</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions. See Figure 20 for waveforms of propagation delay parameters.

<sup>6</sup> Channel-to-channel matching is the absolute value of the difference in propagation delays between the two channels.

### **ELECTRICAL CHARACTERISTICS—3.3 V OPERATION**

All voltages are relative to their respective ground. 3.0 V  $\leq$  V<sub>DD1</sub>  $\leq$  3.6 V, 4.5 V  $\leq$  V<sub>DDA</sub>  $\leq$  18 V, 4.5 V  $\leq$  V<sub>DDB</sub>  $\leq$  18 V, unless stated otherwise. All minimum/maximum specifications apply over T<sub>J</sub> = -40°C to +125°C. All typical specifications are at T<sub>J</sub> = 25°C, V<sub>DD1</sub> = 3.3 V, V<sub>DDA</sub> = V<sub>DDB</sub> = 12 V. Switching specifications are tested with CMOS signal levels.

| Parameter                                        | Symbol                                     | Min                                          | Тур                                    | Max                  | Unit    | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------|--------------------------------------------|----------------------------------------------|----------------------------------------|----------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC SPECIFICATIONS                                |                                            |                                              |                                        |                      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Input Supply Current, Quiescent                  | I <sub>DDI(Q)</sub>                        |                                              | 0.87                                   | 1.4                  | mA      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Output Supply Current, Per Channel, Quiescent    | I <sub>DDO(Q)</sub>                        |                                              | 2.3                                    | 3.2                  | mA      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Supply Current at 1 MHz                          |                                            |                                              |                                        |                      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>DD1</sub> Supply Current                  | I <sub>DD1(Q)</sub>                        |                                              | 1.1                                    | 1.5                  | mA      | Up to 1 MHz, no load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VDDA/VDDB Supply Current                         | IDDA(Q)/IDDB(Q)                            |                                              | 5.6                                    | 8.0                  | mA      | Up to 1 MHz, no load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input Currents                                   | I <sub>IA</sub> , I <sub>IB</sub>          | -10                                          | +0.01                                  | +10                  | μΑ      | $0 \text{ V} \leq V_{IA}, V_{IB} \leq V_{DD1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Logic High Input Threshold                       | VIH                                        | $0.7 \times V_{DD1}$                         |                                        |                      | V       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Logic Low Input Threshold                        | VIL                                        |                                              |                                        | $0.3 \times V_{DD1}$ | V       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Logic High Output Voltages                       | Vоан, Vовн                                 | V <sub>DDA</sub> /<br>V <sub>DDB</sub> – 0.1 | V <sub>DDA</sub> /<br>V <sub>DDB</sub> |                      | v       | $I_{\text{Ox}} = -20 \text{ mA}, V_{\text{Ix}} = V_{\text{IxH}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Logic Low Output Voltages                        | VOAL, VOBL                                 |                                              | 0.0                                    | 0.15                 | V       | $I_{Ox} = +20 \text{ mA}, V_{Ix} = V_{IxL}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Undervoltage Lockout, VDDA/VDDB Supply           |                                            |                                              |                                        |                      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A Grade                                          |                                            |                                              |                                        |                      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Positive Going Threshold                         | VDDAUV+, VDDBUV+                           |                                              | 4.1                                    | 4.4                  | V       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Negative Going Threshold                         | V <sub>DDAUV</sub> -, V <sub>DDBUV</sub> - | 3.2                                          | 3.6                                    |                      | V       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Hysteresis                                       | Vddauvh, Vddbuvh                           |                                              | 0.5                                    |                      | V       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| B Grade                                          |                                            |                                              |                                        |                      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Positive Going Threshold                         | V <sub>DDAUV+</sub> , V <sub>DDBUV+</sub>  |                                              | 6.9                                    | 7.4                  | V       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

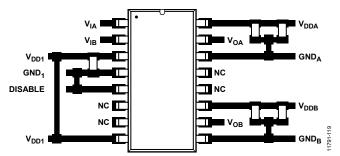

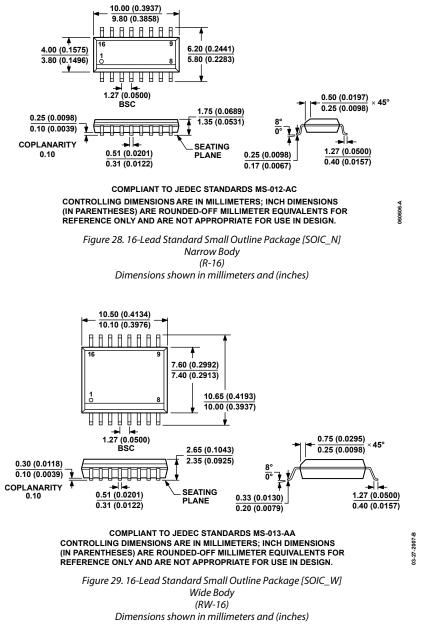

| Negative Going Threshold                         | VDDAUV-, VDDBUV-                           | 5.7                                          | 6.2                                    |                      | V       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |