#### **MAX11312**

## PIXI, 12-Port Programmable Mixed-Signal I/O with 12-Bit ADC, 12-Bit DAC, Analog Switches, and GPIO

#### **General Description**

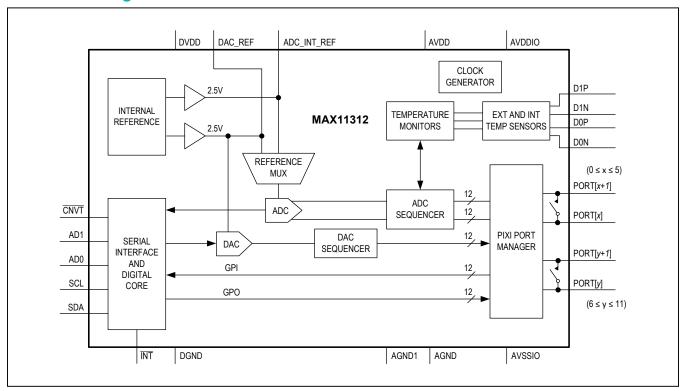

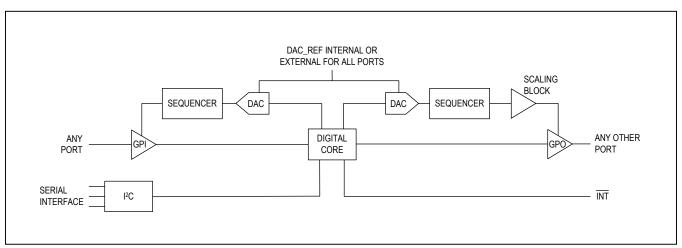

The MAX11312 integrates a PIXI™, 12-bit, multichannel, analog-to-digital converter (ADC) and a 12-bit, multichannel, buffered digital-to-analog converter (DAC) in a single integrated circuit. This device offers 12 mixed-signal high-voltage, bipolar ports, which are configurable as an ADC analog input, a DAC analog output, a general purpose input (GPI), a general-purpose output (GPO), or an analog switch terminal. One internal and two external temperature sensors track junction and environmental temperature. Adjacent pairs of ports are configurable as a logic-level translator for open-drain devices or an analog switch.

PIXI ports provide highly flexible hardware configuration for 12-bit mixed-signal applications. The MAX11312 is best suited for applications that demand a mixture of analog and digital functions. Each port is individually configurable with up to four selectable voltage ranges within the -10V to +10V range.

The device allows for the averaging of 2, 4, 8, 16, 32, 64, or 128 ADC samples from each ADC-configured port to improve noise performance. A DAC-configured output port can drive up to 25mA. The GPIO ports can be programmed to user-defined logic levels, and a GPI coupled with a GPO forms a logic-level translator.

Internal and external temperature measurements monitor programmable conditions of minimum and maximum temperature limits, using the interrupt to notify the host if one or more conditions occur. The temperature measurement results are made available through the serial interface.

The device features an internal, low-noise 2.5V voltage reference and provides the option to use external voltage references with separate inputs for the DAC and ADC. The MAX11312 uses a 400kHz I<sup>2</sup>C-compatible serial interface, operating from a 5V analog supply and a 1.8V to 5.0V digital supply. The PIXI port supply voltages operate from a wide -12.0V to +12.0V.

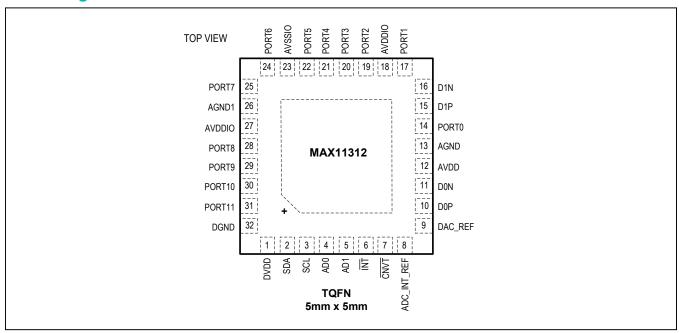

The MAX11312 is available in a 32-pin TQFN, 5mm x 5mm package specified over the -40°C to +105°C temperature range.

#### **Applications**

- Base-Station RF Power Device Bias Controllers

- System Supervision and Control

- Power-Supply Monitoring

- Industrial Control and Automation

- · Control for Optical Components

PIXI is a trademark of Maxim Integrated Products, Inc..

#### **Benefits and Features**

- 12 Configurable Mixed-Signal Ports Maximize Design Flexibility Across Platforms

- Up to 12 12-Bit ADC Inputs

- Single-Ended, Differential, or Pseudo-Differential

- Range Options: 0 to 2.5V, ±5V, 0 to +10V, -10V to 0V

- Programmable Sample Averaging Per ADC Port

- Unique Voltage Reference for Each ADC PIXI Port

- · Up to 12 12-Bit DAC Outputs

- Range Options: ±5V, 0 to +10V, -10V to 0V

- 25mA Current Drive Capability with Overcurrent Protection

- Up to 12 General-Purpose Digital I/Os

- 0 to +5V GPI Input Range

- 0 to +2.5V GPI Programmable Threshold Range

- 0 to +10V GPO Programmable Output Range

- Logic-Level-Shifting Between Any Two Pins

- 60Ω Analog Switch Between Adjacent PIXI Ports

- Internal/External Temperature Sensors, ±1°C Accuracy

- Adapts to Specific Application Requirements and Allows for Easy Reconfiguration as System Needs Change

- Configurability of Functions Enables Optimized PCB Layout

- Reduces BOM Cost with Fewer Components in a Small Footprint

- 25mm<sup>2</sup> 32-Pin TQFN

Ordering Information appears at end of data sheet.

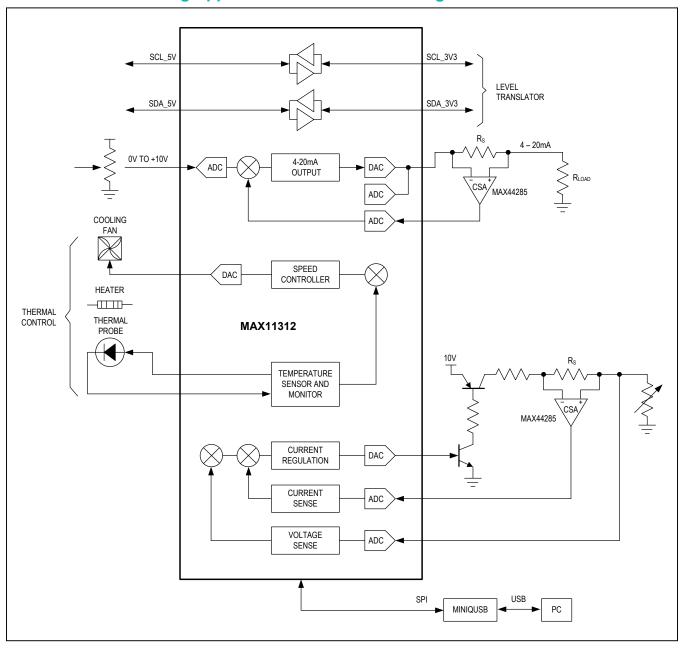

### **Functional Diagram**

#### **Absolute Maximum Ratings**

| DVDD to DGND0.3V to +6V                                           | (AD0, AD1) to DGND0.3V to min of $(V_{DVDD} + 0.3V)$ or +6V              |

|-------------------------------------------------------------------|--------------------------------------------------------------------------|

| AVDD to AGND0.3V to +6V                                           | DAC and ADC Reference Pins to AGND (DAC_REF,                             |

| AVDDIO to AVSSIO0.3V to +25V                                      | ADC_INT_REF,)0.3V to min of (V <sub>AVDD</sub> +0.3V) or +4V             |

| AVDDIO to AGND0.3V to +17V                                        | Temperature Sensor Pins                                                  |

| AVSSIO to AGND14V to +0.3V                                        | (D0N, D0P, D1N, D1P) to AGND0.3V to min of                               |

| AGND to AGND10.3V to +0.3V                                        | (V <sub>AVDD</sub> + 0.3V) or +6V                                        |

| AGND to DGND0.3V to +0.3V                                         | Current into Any PORT Pin100mA                                           |

| AGND1 to DGND0.3V to +0.3V                                        | Current into Any Other Pin Except Supplies                               |

| (PORT0 to PORT11) to AGNDmax of (V <sub>AVSSIO</sub> - 0.3V)      | and Ground50mA                                                           |

| or -14V to min of $(V_{AVDDIO} + 0.3V)$ or +17V                   | Continuous Power Dissipation (T <sub>A</sub> = +70°C) (Multilayer board) |

| (PORT0 to PORT11) to AGND (GPI and Bidirectional Level            | TQFN (derate 34.5mW/°C above +70°C)2758.6mW                              |

| Translator Modes)0.3V to min of (V <sub>AVDD</sub> + 0.3V) or +6V | Operating Temperature Range40°C to +105°C                                |

| CNVT to DGND0.3V to min of (V <sub>DVDD</sub> + 0.3V) or +6V      | Storage Temperature Range65°C to +150°C                                  |

| INT to DGND0.3V to +6V                                            | Lead Temperature (soldering, 10s)+300°C                                  |

| (SDA, SCL) to DGND0.3V to +6V                                     | Soldering Temperature (reflow)+260°C                                     |

|                                                                   |                                                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 1)**

**TQFN**

$\label{eq:continuous} \mbox{Junction-to-Case Thermal Resistance } (\theta_{\mbox{\scriptsize JC}})......1.7^{\circ}\mbox{C/W} \qquad \mbox{Junction-to-Ambient Thermal Resistance } (\theta_{\mbox{\scriptsize JA}})........29^{\circ}\mbox{C/W}$

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

#### **ADC Electrical Specifications**

$(V_{AVDD}$  = 4.75V to 5.25V,  $V_{DVDD}$  = 3.3V,  $V_{AVDDIO}$  = +12.0V,  $V_{AGND}$  =  $V_{DGND}$  = 0V,  $V_{AVSSIO}$  = -2.0V,  $V_{DACREF}$  = 2.5V,  $V_{ADCREF}$  = 2.5V (Internal),  $V_{ADCREF}$  = 4.0°C to +105°C, unless otherwise noted. Typical values are at  $V_{ADCREF}$  = 2.5V. (Note 2)

| PARAMETER                           | SYMBOL | CONDITIONS                        | MIN | TYP    | MAX  | UNITS  |  |

|-------------------------------------|--------|-----------------------------------|-----|--------|------|--------|--|

| DC ACCURACY (Note 3)                |        |                                   |     |        |      |        |  |

| Resolution                          |        |                                   | 12  |        |      | Bits   |  |

| Integral Nonlinearity               | INL    |                                   |     |        | ±2.5 | LSB    |  |

| Differential Nonlinearity           | DNL    | No missing codes over temperature |     |        | ±1   | LSB    |  |

| Offset Error                        |        |                                   |     | ±0.5   | ±8   | LSB    |  |

| Offset Error Drift                  |        |                                   |     | ±0.002 |      | LSB/°C |  |

| Gain Error                          |        |                                   |     |        | ±11  | LSB    |  |

| Gain Error Drift                    |        |                                   |     | ±0.01  |      | LSB/°C |  |

| Channel-to-Channel Offset Matching  |        |                                   |     | 1      |      | LSB    |  |

| Channel-to-Channel Gain<br>Matching |        |                                   |     | 2      |      | LSB    |  |

### **Electrical Characteristics (continued)**

#### **ADC Electrical Specifications**

$(V_{AVDD}$  = 4.75V to 5.25V,  $V_{DVDD}$  = 3.3V,  $V_{AVDDIO}$  = +12.0V,  $V_{AGND}$  =  $V_{DGND}$  = 0V,  $V_{AVSSIO}$  = -2.0V,  $V_{DACREF}$  = 2.5V,  $V_{ADCREF}$  = 2.5V (Internal),  $V_{ADCREF}$  = 4.00ksps, 10V analog input range set to range 1 (0 to +10V).  $V_{ADCREF}$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $V_{ADCREF}$  = -2.5V. (Note 2)

| PARAMETER                       | SYMBOL            | CONDITIONS                                        | MIN | TYP | MAX | UNITS |  |

|---------------------------------|-------------------|---------------------------------------------------|-----|-----|-----|-------|--|

| DYNAMIC PERFORMANCE (SIN        | IGLE-ENDED        | INPUTS)                                           |     |     |     |       |  |

| Signal-to-Noise Plus Distortion | SINAD             | f <sub>S</sub> = 400ksps, f <sub>IN</sub> = 10kHz |     | 70  |     | dB    |  |

| Signal to Noise                 | SNR               | f <sub>S</sub> = 400ksps, f <sub>IN</sub> = 10kHz |     | 71  |     | dB    |  |

| Total Harmonic Distortion       | THD               | f <sub>S</sub> = 400ksps, f <sub>IN</sub> = 10kHz |     | -75 |     | dB    |  |

| Spurious-Free Dynamic Range     | SFDR              | f <sub>S</sub> = 400ksps, f <sub>IN</sub> = 10kHz |     | 75  |     | dB    |  |

| Crosstalk                       |                   |                                                   |     | -85 |     | dB    |  |

| DYNAMIC PERFORMANCE (DIF        | FERENTIAL I       | NPUTS)                                            | •   |     |     |       |  |

| Signal-to-Noise Plus Distortion | SINAD             | f <sub>S</sub> = 400ksps, f <sub>IN</sub> = 10kHz |     | 71  |     | dB    |  |

| Signal to Noise                 | SNR               | f <sub>S</sub> = 400ksps, f <sub>IN</sub> = 10kHz |     | 72  |     | dB    |  |

| Total Harmonic Distortion       | THD               | f <sub>S</sub> = 400ksps, f <sub>IN</sub> = 10kHz |     | -82 |     | dB    |  |

| Spurious-Free Dynamic Range     | SFDR              | f <sub>S</sub> = 400ksps, f <sub>IN</sub> = 10kHz |     | 82  |     | dB    |  |

| Crosstalk                       |                   |                                                   |     | -85 |     | dB    |  |

| CONVERSION RATE                 |                   |                                                   |     |     |     |       |  |

|                                 |                   | ADCCONV[1:0] = 00                                 |     | 200 |     |       |  |

| Throughput (Note 4)             |                   | ADCCONV[1:0] = 01                                 |     | 250 |     | ksps  |  |

| Throughput (Note 4)             |                   | ADCCONV[1:0] = 10                                 |     | 333 |     |       |  |

|                                 |                   | ADCCONV[1:0] = 11                                 |     | 400 |     |       |  |

|                                 |                   | ADCCONV[1:0] = 00                                 |     | 3.5 |     |       |  |

| Acquisition Time                |                   | ADCCONV[1:0] = 01                                 |     | 2.5 |     |       |  |

| Acquisition Time                | tACQ              | ADCCONV[1:0] = 10                                 |     | 1.5 |     | μs    |  |

|                                 |                   | ADCCONV[1:0] = 11                                 |     | 1.0 |     |       |  |

| ANALOG INPUT (All Ports)        |                   |                                                   | •   |     |     |       |  |

|                                 |                   | Range 1                                           | 0   |     | 10  |       |  |

| Absolute Input Voltage (Nata E) |                   | Range 2                                           | -5  |     | +5  | V     |  |

| Absolute Input Voltage (Note 5) | V <sub>PORT</sub> | Range 3                                           | -10 |     | 0   | V     |  |

|                                 |                   | Range 4                                           | 0   |     | 2.5 | 1     |  |

| Input Desistance                |                   | Range 1, 2, 3                                     | 70  | 100 | 130 | kΩ    |  |

| Input Resistance                |                   | Range 4                                           | 50  | 75  | 100 | kΩ    |  |

#### **REF Electrical Characteristics**

$(V_{AVDD} = 4.75V \text{ to } 5.25V, V_{DVDD} = 3.3V, V_{AVDDIO} = +12.0V, V_{AGND} = V_{DGND} = 0V, V_{AVSSIO} = -2.0V, V_{DACREF} = 2.5V, V_{ADCREF} = 2.5V \text{ (Internal)}, f_S = 400 \text{ksps}, 10V \text{ analog input range set to range 1 (0 to +10V)}. T_A = -40 ^{\circ}\text{C} \text{ to +105 ^{\circ}C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25 ^{\circ}\text{C}$ .) (Note 2)

| PARAMETER                       | SYMBOL              | CONDITIONS                                    | MIN   | TYP | MAX   | UNITS  |

|---------------------------------|---------------------|-----------------------------------------------|-------|-----|-------|--------|

| ADC INTERNAL REFERENCE          |                     |                                               |       |     |       |        |

| Reference Output Voltage        |                     | Internal references at T <sub>A</sub> = +25°C | 2.494 | 2.5 | 2.506 | V      |

| REF Output Tempco (Note 6)      | T <sub>C-VREF</sub> |                                               |       | ±10 | ±25   | ppm/°C |

| Capacitor Bypass at ADC_INT_REF |                     |                                               | 4.7   |     | 10    | μF     |

| DAC INTERNAL REFERENCE          |                     |                                               |       |     |       |        |

| Reference Output Voltage        |                     | Internal references at T <sub>A</sub> = +25°C | 2.494 | 2.5 | 2.506 | V      |

| REF Output Tempco (Note 6)      | T <sub>C-VREF</sub> |                                               |       | ±10 | ±25   | ppm/°C |

| Capacitor Bypass at DAC_REF     |                     |                                               | 4.7   |     | 10    | μF     |

| DAC EXTERNAL REFERENCE          |                     |                                               |       |     |       |        |

| Reference Input Range           |                     |                                               | 1.25  |     | 2.5   | V      |

### **GPIO Electrical Specifications**

$(V_{AVDD} = 5.0V, V_{DVDD} = 3.3V, V_{AVDDIO} = +12.0V, V_{AGND} = V_{DGND} = 0V, V_{AVSSIO} = -2.0V, V_{DACREF} = 2.5V, V_{ADCREF} = 2.5V$  (Internal),  $f_S = 400$ ksps, 10V analog input range set to range 1 (0 to +10V).  $T_A = -40$ °C to +105°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 2)

| PARAMETER                                                                                     | SYMBOL            | CONDITIONS                                                                                                   | MIN                    | TYP | MAX                        | UNITS |

|-----------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------|------------------------|-----|----------------------------|-------|

| GPIO EXCEPT IN BIDIRECTIONA                                                                   | L LEVEL TF        | RANSLATION MODE                                                                                              |                        |     |                            |       |

| Programmable Input Logic Threshold                                                            | V <sub>ITH</sub>  |                                                                                                              | 0.3                    |     | V <sub>DACREF</sub>        | V     |

| Input High Voltage                                                                            | V <sub>IH</sub>   |                                                                                                              | V <sub>ITH</sub> + 0.3 |     |                            | V     |

| Input Low Voltage                                                                             | V <sub>IL</sub>   |                                                                                                              |                        |     | V <sub>ITH</sub> - 0.3     | V     |

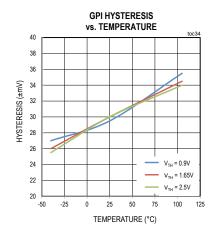

| Hysteresis                                                                                    |                   |                                                                                                              |                        | ±30 |                            | mV    |

| Programmable Output Logic Level                                                               | V <sub>OLVL</sub> |                                                                                                              | 0                      |     | 4 x<br>V <sub>DACREF</sub> | V     |

| Propagation Delay from GPI Input<br>to GPO Output in Unidirectional<br>Level Translating Mode |                   | Midscale threshold-5V logic swing                                                                            |                        | 2   |                            | μs    |

| BIDIRECTIONAL LEVEL TRANSL                                                                    | ATION PATH        | I AND ANALOG SWITCH                                                                                          |                        |     |                            |       |

| Input High Voltage                                                                            | V <sub>IH</sub>   |                                                                                                              | 1                      |     |                            | V     |

| Input Low Voltage                                                                             | V <sub>IL</sub>   |                                                                                                              |                        |     | 0.2                        | V     |

| On-Resistance                                                                                 |                   | From V <sub>AVSSIO</sub> + 2.50V to V <sub>AVDDIO</sub> -2.50V                                               |                        |     | 60                         | Ω     |

| Propagation Delay                                                                             |                   | 10kΩ pullup resistors to rail in each side. Midvoltage to midvoltage when driving side goes from high to low |                        |     | 1                          | μs    |

#### **GPIO Electrical Specifications (continued)**

$(V_{AVDD} = 5.0V, V_{DVDD} = 3.3V, V_{AVDDIO} = +12.0V, V_{AGND} = V_{DGND} = 0V, V_{AVSSIO} = -2.0V, V_{DACREF} = 2.5V, V_{ADCREF} = 2.5V$  (Internal), f<sub>S</sub> = 400ksps, 10V analog input range set to range 1 (0 to +10V). T<sub>A</sub> = -40°C to +105°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER         | SYMBOL | CONDITIONS                                                      | MIN | TYP | MAX | UNITS |

|-------------------|--------|-----------------------------------------------------------------|-----|-----|-----|-------|

| ANALOG SWITCH     | '      |                                                                 |     |     |     |       |

| Turn-On Delay     |        | (Note 7)                                                        |     |     | 400 | ns    |

| Turn-Off Delay    |        | (Note 7)                                                        |     |     | 400 | ns    |

| On-Time Duration  |        | (Note 7)                                                        | 1   |     |     | μs    |

| Off-Time Duration |        | (Note 7)                                                        | 1   |     |     | μs    |

| On-Resistance     |        | From V <sub>AVSSIO</sub> + 2.50V to V <sub>AVDDIO</sub> - 2.50V |     |     | 60  | Ω     |

### **DAC Electrical Specifications**

$(V_{AVDD} = 4.75V \text{ to } 5.25V, V_{DVDD} = 3.3V, V_{AVDDIO} = +12.0V, V_{AGND} = V_{DGND} = 0V, V_{AVSSIO} = -2.0V, V_{DACREF} = 2.5V, V_{ADCREF} = 2.5V \text{ (Internal)}, f_S = 400ksps, 10V \text{ analog input range set to range 1 (0 to +10V)}. T_A = -40^{\circ}\text{C} \text{ to +105}^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 2)

| PARAMETER                                       | SYMBOL            | CONDITIONS                                                                 | MIN  | TYP  | MAX  | UNITS             |

|-------------------------------------------------|-------------------|----------------------------------------------------------------------------|------|------|------|-------------------|

| DC ACCURACY                                     | •                 |                                                                            |      |      |      |                   |

| Resolution                                      | N                 |                                                                            | 12   |      |      | Bits              |

|                                                 |                   | Range 1                                                                    | 0    |      | +10  |                   |

| Output Range (Note 5)                           | V <sub>PORT</sub> | Range 2                                                                    | -5   |      | +5   | V                 |

|                                                 |                   | Range 3                                                                    | -10  |      | 0    |                   |

| Integral Linearity Error                        | INL               | From code 100 to code 3996                                                 |      | ±0.5 | ±1.5 | LSB               |

| Differential Linearity Error                    | DNL               |                                                                            |      | ±0.5 | ±1   | LSB               |

| Offset Voltage                                  |                   | At code 100                                                                |      |      | ±20  | LSB               |

| Offset Voltage Tempco                           |                   |                                                                            |      | 15   |      | ppm/°C            |

| Gain Error                                      |                   | From code 100 to code 3996                                                 | -0.6 |      | +0.6 | % of FS           |

| Gain Error Tempco                               |                   | From code 100 to code 3996                                                 |      | 4    |      | ppm of<br>FS/°C   |

| Power-Supply Rejection<br>Ratio                 | PSRR              |                                                                            |      | 0.4  |      | mV/V              |

| DYNAMIC CHARACTERIST                            | ics               |                                                                            |      |      |      |                   |

| Output Voltage Slew Rate                        | SR                |                                                                            |      | 1.6  |      | V/µs              |

| Output Settling Time                            |                   | To ±1 LSB, from 0 to full scale, output load capacitance of 250pF (Note 8) |      | 40   |      | μs                |

| Settling Time After Current-<br>Limit Condition |                   |                                                                            |      | 6    |      | μs                |

| Noise                                           |                   | f = 0.1Hz to 300kHz                                                        |      | 3.8  |      | mV <sub>P-P</sub> |

### **DAC Electrical Specifications (continued)**

$(V_{AVDD}$  = 4.75V to 5.25V,  $V_{DVDD}$  = 3.3V,  $V_{AVDDIO}$  = +12.0V,  $V_{AGND}$  =  $V_{DGND}$  = 0V,  $V_{AVSSIO}$  = -2.0V,  $V_{DACREF}$  = 2.5V,  $V_{ADCREF}$  = 2.5V (Internal),  $f_S$  = 400ksps, 10V analog input range set to range 1 (0 to +10V).  $T_A$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER           | SYMBOL | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------|--------|------------|-----|-----|-----|-------|

| TRACK-AND-HOLD      |        |            |     |     |     |       |

| Digital Feedthrough |        |            |     | 5   |     | nV∙s  |

| Hold Step           |        | (Note 6)   |     | 1   | 6   | mV    |

| Droop Rate          |        | (Note 6)   |     | 0.3 | 15  | mV/s  |

### **Interface Digital IO Electrical Specifications**

$(V_{AVDD} = 5.0V, V_{DVDD} = 1.62V \text{ to } 5.50V, V_{AVDDIO} = +12.0V, V_{AGND} = V_{DGND} = 0V, V_{AVSSIO} = -2.0V, V_{DACREF} = 2.5V, V_{ADCREF} = 2.5V (Internal), f_S = 400ksps, 10V analog input range set to range 1 (0 to +10V). T_A = -40°C to +105°C, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 2)$

| PARAMETER                                                         | SYMBOL              | CONDITIONS                                                | MIN                         | TYP | MAX                         | UNITS |

|-------------------------------------------------------------------|---------------------|-----------------------------------------------------------|-----------------------------|-----|-----------------------------|-------|

| I <sup>2</sup> C IO DC SPECIFICATION                              |                     |                                                           |                             |     |                             |       |

| Input Logic-High Voltage                                          |                     | V <sub>DVDD</sub> = 2.5V to 5.5V                          | 0.7 x<br>V <sub>DVDD</sub>  |     |                             | V     |

| (SDA, SCL, AD0, AD1, CNVT)                                        |                     | V <sub>DVDD</sub> = 1.62V to 2.5V                         | 0.85 x<br>V <sub>DVDD</sub> |     |                             | V     |

| Input Logic-Low Voltage                                           |                     | V <sub>DVDD</sub> = 2.5V to 5.5V                          |                             |     | 0.3 x<br>V <sub>DVDD</sub>  | V     |

| SDA, SCL, AD0, AD1, CNVT)                                         |                     | V <sub>DVDD</sub> = 1.62V to 2.5V                         |                             |     | 0.15 x<br>V <sub>DVDD</sub> | V     |

| Input Leakage Current (SDA, SCL, AD0, AD1, CNVT)                  |                     |                                                           | -10                         |     | +10                         | μΑ    |

| Input Capacitance (SDA, SCL, AD0, AD1, $\overline{\text{CNVT}}$ ) |                     |                                                           |                             | 10  |                             | pF    |

| Output Logic-Low Voltage (SDA)                                    |                     | I <sub>SNK</sub> = 3mA                                    |                             |     | 0.4                         | V     |

| Outside the size house Vallages (INIT)                            |                     | I <sub>SNK</sub> = 5mA, V <sub>DVDD</sub> = 2.5V to 5.5V  |                             |     | 0.4                         | V     |

| Output Logic-Low Voltage (INT)                                    |                     | I <sub>SNK</sub> = 2mA, V <sub>DVDD</sub> = 1.62V to 2.5V |                             |     | 0.2                         | V     |

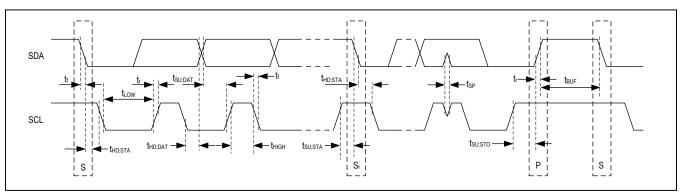

| I <sup>2</sup> C TIMING REQUIREMENTS (F                           | ast Mode) (S        | ee Figure 1)                                              |                             |     |                             |       |

| Serial Clock Frequency                                            | f <sub>SCL</sub>    |                                                           | 0                           |     | 400                         | kHz   |

| Bus Free Time Between STOP and START Condition                    | t <sub>BUF</sub>    |                                                           | 1.3                         |     |                             | μs    |

| Hold Time (Repeated) START Condition                              | t <sub>HD;STA</sub> | After this period, first clock pulse is generated         | 0.6                         |     |                             | μs    |

| SCL Pulse-Width Low                                               | t <sub>LOW</sub>    |                                                           | 1.3                         |     |                             | μs    |

| SCL Pulse-Width High                                              | tHIGH               |                                                           | 0.6                         |     |                             | μs    |

### **Interface Digital IO Electrical Specifications (continued)**

$(V_{AVDD}$  = 4.75V to 5.25V,  $V_{DVDD}$  = 3.3V,  $V_{AVDDIO}$  = +12.0V,  $V_{AGND}$  =  $V_{DGND}$  = 0V,  $V_{AVSSIO}$  = -2.0V,  $V_{DACREF}$  = 2.5V,  $V_{ADCREF}$  = 2.5V (Internal),  $f_S$  = 400ksps, 10V analog input range set to range 1 (0 to +10V).  $T_A$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                               | SYMBOL              | CONDITIONS                       | MIN                                  | TYP | MAX | UNITS |

|-----------------------------------------|---------------------|----------------------------------|--------------------------------------|-----|-----|-------|

| Setup Time for Repeated START Condition | t <sub>SU;STA</sub> |                                  | 0.6                                  |     |     | μs    |

| Data Hold Time                          | t <sub>HD;DAT</sub> |                                  | 0                                    |     | 900 | ns    |

| Data Setup Time                         | t <sub>SU;DAT</sub> |                                  | 100                                  |     |     | ns    |

| SDA and SCL Receiving Rise<br>Time      | t <sub>r</sub>      | (Note 6)                         | 12 x<br>(V <sub>DVDD</sub><br>/5.5V) |     | 300 | ns    |

| SDA and SCL Receiving Fall<br>Time      | t <sub>f</sub>      | (Note 6)                         | 12 x<br>(V <sub>DVDD</sub><br>/5.5V) |     | 300 | ns    |

| SDA Transmitting Fall Time              | t <sub>of</sub>     |                                  | 12 x<br>(V <sub>DVDD</sub><br>/5.5V) |     | 250 | ns    |

| Setup Time for STOP Condition           | tsu;sto             |                                  | 0.6                                  |     |     | μs    |

| Bus Capacitance Allowed                 | C <sub>b</sub>      | V <sub>DVDD</sub> = 2.5V to 5.5V |                                      |     | 400 | pF    |

| Pulse Width of Suppressed<br>Spike      | tsp                 |                                  |                                      | 50  |     | ns    |

Figure 1. I<sup>2</sup>C Timing

#### **Electrical Characteristics**

### **Internal and External Temperature Sensor Specifications**

$(V_{AVDD}$  = 4.75V to 5.25V,  $V_{DVDD}$  = 3.3V,  $V_{AVDDIO}$  = +12.0V,  $V_{AGND}$  =  $V_{DGND}$  = 0V,  $V_{AVSSIO}$  = -2.0V,  $V_{DACREF}$  = 2.5V,  $V_{ADCREF}$  = 2.5V (Internal),  $f_S$  = 400ksps, 10V analog input range set to range 1 (0 to +10V).  $T_A$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                   | SYMBOL | CONDITIONS                          | MIN | TYP   | MAX  | UNITS |

|---------------------------------------------|--------|-------------------------------------|-----|-------|------|-------|

| ACCURACY                                    |        |                                     |     |       |      |       |

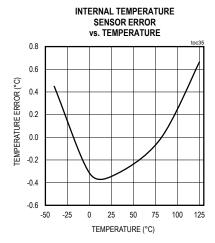

| Accuracy of Internal Sensor                 |        | 0°C ≤ T <sub>J</sub> ≤ +80°C        |     | ±0.3  | ±2.0 | °C    |

| (Notes 6, 9)                                |        | -40°C ≤ T <sub>J</sub> ≤ +125°C     |     | ±0.7  | ±5   | °C    |

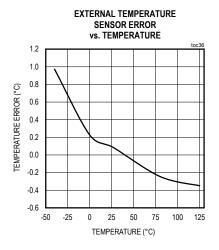

| Accuracy of External Sensor (Notes 6, 9)    |        | 0°C ≤ T <sub>RJ</sub> ≤ +80°C       |     | ±0.3  | ±2.0 | °C    |

|                                             |        | -40°C ≤ T <sub>RJ</sub> ≤ +150°C    |     | ±1.0  | ±5   | °C    |

| Temperature Measurement Resolution          |        |                                     |     | 0.125 |      | °C    |

| External Sensor Junction                    | High   |                                     |     | 68    |      | μA    |

| Current                                     | Low    |                                     |     | 4     |      | μA    |

| External Sensor Junction                    | High   | Series resistance cancellation mode |     | 136   |      | μΑ    |

| Current                                     | Low    | Series resistance cancellation mode |     | 8     |      | μA    |

| Remote Junction Current<br>Conversion Ratio |        |                                     |     | 17    |      |       |

| D0N/D1N Voltage                             |        | Internally generated                |     | 0.5   |      | V     |

### **Power-Supply Specifications**

| PARAMETER                                  | SYMBOL | CONDITIONS                     | MIN               | TYP | MAX   | UNITS |

|--------------------------------------------|--------|--------------------------------|-------------------|-----|-------|-------|

| V <sub>AVDD</sub>                          |        |                                | 4.75              |     | 5.25  | V     |

| V <sub>DVDD</sub>                          |        |                                | 1.62              |     | 5.50  | ٧     |

| V <sub>AVDDIO</sub>                        |        |                                | V <sub>AVDD</sub> |     | 15.75 | V     |

| V <sub>AVSSIO</sub>                        |        |                                | -12.0             |     | 0     | \ \   |

| V <sub>AVDDIO</sub> to V <sub>AVSSIO</sub> |        |                                | V <sub>AVDD</sub> |     | 24    | \ \   |

|                                            |        | All ports in high impedance    |                   | 14  | 18    |       |

|                                            |        | LPEN = 1                       |                   | 11  |       | A     |

| IAVDD                                      |        | All ports in ADC-related modes |                   | 17  |       | mA mA |

|                                            |        | All ports in DAC-related modes |                   | 18  |       |       |

| I <sub>DVDD</sub>                          |        | Serial interface in idle mode  |                   |     | 2     | μA    |

| I <sub>AVDDIO</sub>                        |        | All ports in mode 0            |                   |     | 150   | μA    |

| I <sub>AVSSIO</sub>                        |        | All ports in mode 0            | -400              |     |       | μA    |

### **Recommended VDDIO/VSSIO Supply Selection**

|         |            |                                            | ADC I                                                   | RANGE                                                    |                                                         |

|---------|------------|--------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|

|         |            | -10V to 0V                                 | -5V to +5V                                              | 0V to +10V                                               | 0 to 2.5V                                               |

| GE      | -10V to 0V | $V_{AVDDIO} = +5V$<br>$V_{AVSSIO} = -12V$  | V <sub>AVDDIO</sub> = +5V<br>V <sub>AVSSIO</sub> = -12V | V <sub>AVDDIO</sub> = +10V<br>V <sub>AVSSIO</sub> = -12V | V <sub>AVDDIO</sub> = +5V<br>V <sub>AVSSIO</sub> = -12V |

| C RANGE | -5V to +5V | $V_{AVDDIO} = +7V$<br>$V_{AVSSIO} = -10V$  | V <sub>AVDDIO</sub> = +7V<br>V <sub>AVSSIO</sub> = -7V  | $V_{AVDDIO} = +10V$<br>$V_{AVSSIO} = -7V$                | $V_{AVDDIO} = +7V$<br>$V_{AVSSIO} = -7V$                |

| DAC     | 0V to +10V | $V_{AVDDIO} = +12V$<br>$V_{AVSSIO} = -10V$ | $V_{AVDDIO} = +12V$<br>$V_{AVSSIO} = -5V$               | $V_{AVDDIO} = +12V$<br>$V_{AVSSIO} = -2V$                | $V_{AVDDIO} = +12V$<br>$V_{AVSSIO} = -2V$               |

The values of V<sub>AVDDIO</sub> and V<sub>AVSSIO</sub> supply voltages depend on the application circuit and the device configuration.

V<sub>AVDDIO</sub> needs to be the maximum of those four values:

- If one or more ports are in mode 3, 4, 5, 6, or 10 (DAC-related modes), V<sub>AVDDIO</sub> must be set, at minimum, to the

value of the largest voltage driven by any of the ports set in those modes. For improved linearity, it is recommended

to set V<sub>AVDDIO</sub> 2.0V above the largest voltage value.

- If one or more ports are in mode 7, 8, or 9 (ADC-related modes), V<sub>AVDDIO</sub> must be set, at minimum, to the value of the largest voltage applied to any of the ports set in those modes.

- If one or more ports are in mode 11 or 12 (Analog switch-related modes), V<sub>AVDDIO</sub> must be set, at minimum, to 2.0V above the value of the largest voltage applied to any of the ports functioning as analog switch terminals.

- V<sub>AVDDIO</sub> cannot be set lower than V<sub>AVDD</sub>.

V<sub>AVSSIO</sub> needs to be the minimum of those four values:

- If one or more ports are in mode 3, 4, 5, 6, or 10 (DAC-related modes), V<sub>AVSSIO</sub> must be set, at maximum, to the

value of the lowest voltage driven by any of the ports set in those modes. For improved linearity, it is recommended

to set V<sub>AVSSIO</sub> 2.0V below the lowest voltage value.

- If one or more ports are in mode 7, 8, or 9 (ADC-related modes), V<sub>AVSSIO</sub> must be set, at maximum, to the value

of the lowest voltage applied to any of the ports set in those modes.

- If one or more ports are in mode 11 or 12 (Analog Switch-related modes), V<sub>AVSSIO</sub> must be set, at maximum, to 2.0V below the value of the lowest voltage applied to any of the ports functioning as analog switch terminals.

- V<sub>AVSSIO</sub> cannot be set higher than V<sub>AGND</sub>.

For example, the MAX11312 can operate with only one voltage supply of 5V (±5%) connected to AVDD, AVDDIO, and DVDD, and one ground of 0V connected to AGND, DGND, and AVSSIO. However, the level of performance presented in the electrical specifications requires the setting of the supplies connected to AVDDIO and AVSSIO, as previously described.

### **Common PIXI Electrical Specifications**

$(V_{AVDD}$  = 4.75V to 5.25V,  $V_{DVDD}$  = 3.3V,  $V_{AVDDIO}$  = +12.0V,  $V_{AGND}$  =  $V_{DGND}$  = 0V,  $V_{AVSSIO}$  = -2.0V,  $V_{DACREF}$  = 2.5V,  $V_{ADCREF}$  = 2.5V (Internal),  $f_S$  = 400ksps, 10V analog input range set to range 1 (0 to +10V).  $T_A$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                     | SYMBOL    | CONDITIONS                                                            | MIN                          | TYP | MAX                          | UNITS |

|-------------------------------|-----------|-----------------------------------------------------------------------|------------------------------|-----|------------------------------|-------|

| PIXI PORTS                    | 1         |                                                                       | •                            |     |                              |       |

| Input Capacitance             |           | All PIXI ports                                                        |                              | 12  |                              | pF    |

| Input Resistance              |           | All PIXI input pins except ADC mode                                   | 50                           | 75  | 100                          | kΩ    |

| Startup Time                  |           | Between stable supplies and accessing registers                       |                              |     | 100                          | ms    |

| HIGH-VOLTAGE OUTPUT DRIVE     | R CHARACT | ERISTICS                                                              |                              |     |                              |       |

| Maximum Output Capacitance    |           |                                                                       |                              |     | 250                          | pF    |

| Output Low Voltage, DAC Mode  |           | Sinking 25mA, V <sub>AVSSIO</sub> = 0V,<br>V <sub>AVDDIO</sub> = 10V  |                              |     | V <sub>AVSSIO</sub><br>+ 1.0 | ٧     |

| Output High Voltage, DAC Mode |           | Sourcing 25mA, V <sub>AVSSIO</sub> = 0V,<br>V <sub>AVDDIO</sub> = 10V | V <sub>AVDDIO</sub><br>- 1.5 |     |                              | V     |

| Output Low Voltage, GPO Mode  |           | Sinking 2mA, V <sub>AVSSIO</sub> = 0V,<br>V <sub>AVDDIO</sub> = 10V   |                              |     | V <sub>AVSSIO</sub><br>+ 0.4 | V     |

| Output High Voltage, GPO Mode |           | Sourcing 2mA, V <sub>AVSSIO</sub> = 0V,<br>V <sub>AVDDIO</sub> = 10V  | V <sub>AVDDIO</sub><br>- 0.4 |     |                              | V     |

| Current Limit                 |           | Short to AVDDIO                                                       |                              | 75  |                              | mA    |

|                               |           | Short to AVSSIO                                                       |                              | 75  |                              | mA    |

- **Note 2:** Electrical specifications are production tested at  $T_A = +25^{\circ}C$ . Specifications over the entire operating temperature range are guaranteed by design and characterization. Typical specifications are at  $T_A = +25^{\circ}C$ .

- Note 3: DC accuracy specifications are tested for single-ended ADC inputs only.

- Note 4: The effective ADC sample rate for port X configured in mode 6, 7, or 8 is:

- [ADC sample rate per ADCCONV]/(([number of ports in modes 6,7,8] + [1 if TMPSEL ≠ 000]) x [2# OF SAMPLES for port X])

Note 5: See the Recommended VDDIO/VSSIO Supply Selection table for each range. For ports in modes 6, 7, 8, or 9, the voltage

- applied to those ports must be within the limits of their selected input range, whether in single-ended or differential mode.

- Note 6: Specification is guaranteed by design and characterization.

- Note 7: Switch controlled by GPI-configured port. One switch terminal connected to 0V, the other terminal connected to 5V through a 5mA current source. Timing is measured at the 2.5V transition point. Turn-on and turn-off delays are measured from the edge of the control signal to the 2.5V transition point. Turn-on and turn-off durations are measured between control signal transitions.

- **Note 8:** In DAC-related modes, the rate, at which PIXI ports configured in mode 1, 3, 4, 5, 6, or 10 are refreshed, is as follows: 1/(40µs x [number of ports in modes 1, 3, 4, 5, 6, 10])

- Note 9: Typical (typ) values represent the errors at the extremes of the given temperature range.

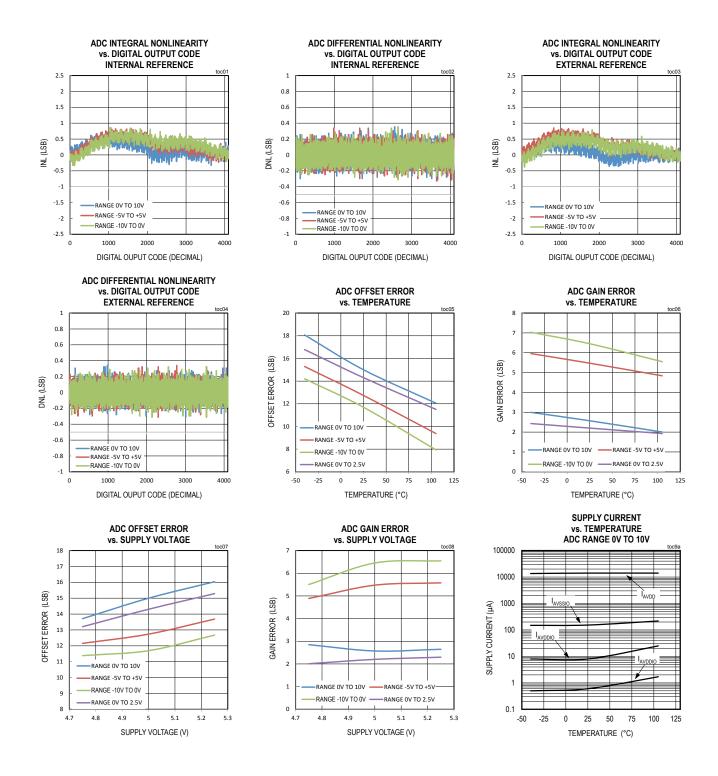

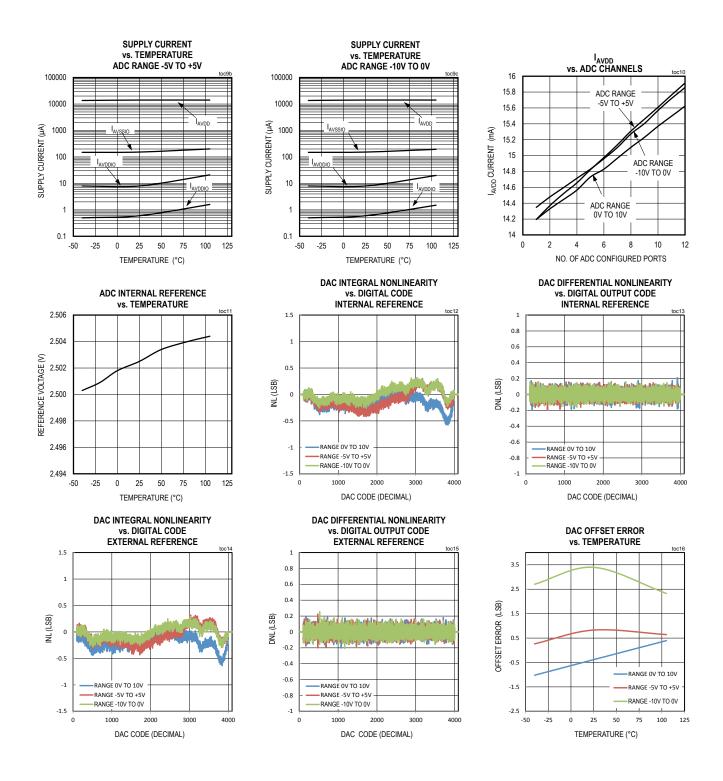

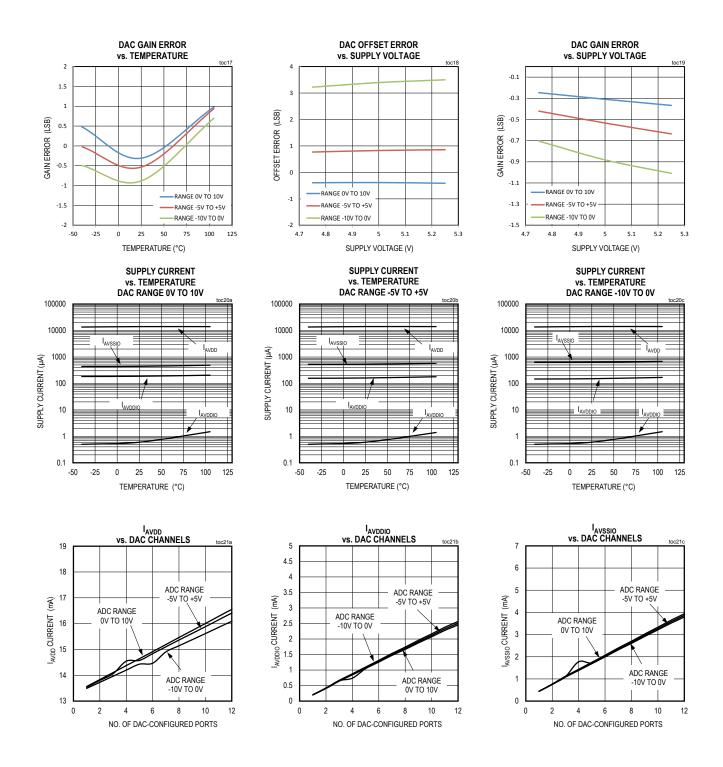

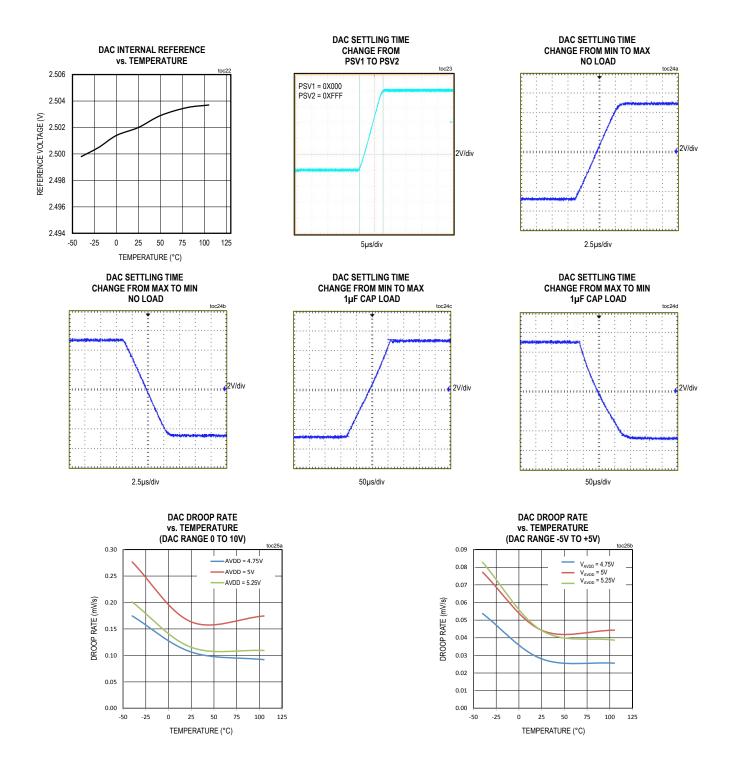

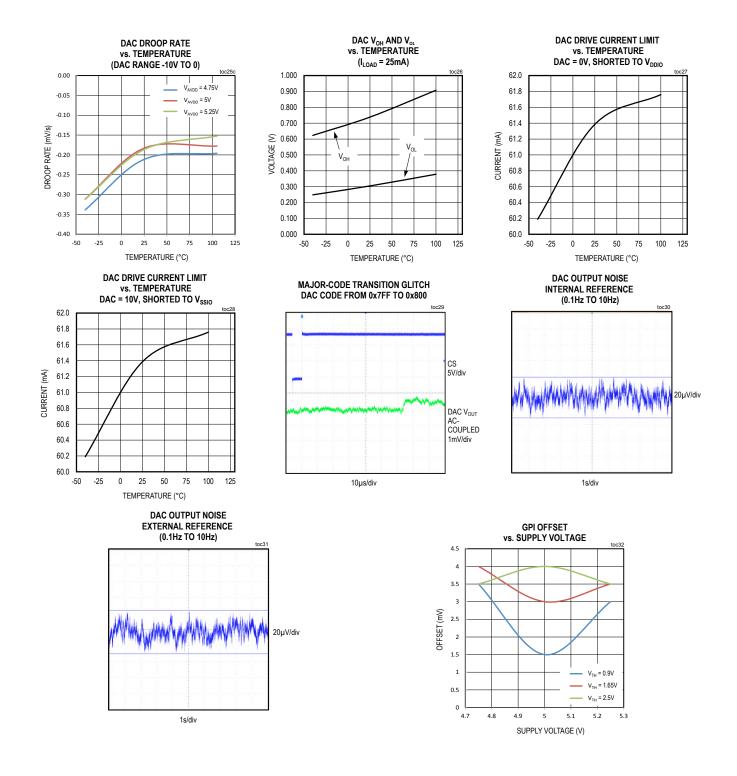

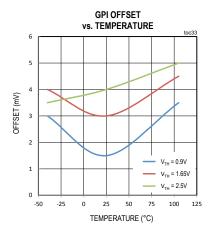

### **Typical Operating Characteristics**

(TA = +25°C, unless otherwise noted.)

$(T_A = +25^{\circ}C, unless otherwise noted.)$

$(T_A = +25^{\circ}C, unless otherwise noted.)$

$(T_A = +25^{\circ}C, unless otherwise noted.)$

$(T_A = +25^{\circ}C, unless otherwise noted.)$

(TA =  $+25^{\circ}$ C, unless otherwise noted.)

### **Pin Configuration**

### **Pin Description**

| PIN | NAME | FUNCTION                                 |

|-----|------|------------------------------------------|

| 1   | DVDD | Positive Digital Supply                  |

| 2   | SDA  | Serial Interface Input and Output        |

| 3   | SCL  | Serial Interface Clock Input             |

| 4   | AD0  | Slave Address Bit 0                      |

| 5   | AD1  | Slave Address Bit 1                      |

| 6   | ĪNT  | Interrupt Open-Drain Output. Active-low. |

| 7   | CNVT | ADC Trigger Control Input. Active-low.   |

### **Pin Description (continued)**

| PIN   | NAME        | FUNCTION                                                                                               |

|-------|-------------|--------------------------------------------------------------------------------------------------------|

| 8     | ADC_INT_REF | ADC Internal Voltage Reference Output. Connect a bypass capacitor at this pin (4.7μF to 10μF).         |

| 9     | DAC_REF     | DAC External/Internal Voltage Reference Input. Connect a bypass capacitor at this pin (4.7μF to 10μF). |

| 10    | D0P         | 1st External Temperature Sensor Positive Input                                                         |

| 11    | D0N         | 1st External Temperature Sensor Negative Input                                                         |

| 12    | AVDD        | Positive Analog Supply                                                                                 |

| 13    | AGND        | Analog Ground                                                                                          |

| 14    | PORT0       | Configurable Mixed-Signal Port 0                                                                       |

| 15    | D1P         | 2 <sup>nd</sup> External Temperature Sensor Positive Input                                             |

| 16    | D1N         | 2 <sup>nd</sup> External Temperature Sensor Negative Input                                             |

| 17    | PORT1       | Configurable Mixed-Signal Port 1                                                                       |

| 18,27 | AVDDIO      | Analog Positive Supply For Mixed-Signal Ports. Connect both pins to AVDDIO.                            |

| 19    | PORT2       | Configurable Mixed-Signal Port 2                                                                       |

| 20    | PORT3       | Configurable Mixed-Signal Port 3                                                                       |

| 21    | PORT4       | Configurable Mixed-Signal Port 4                                                                       |

| 22    | PORT5       | Configurable Mixed-Signal Port 5                                                                       |

| 23    | AVSSIO      | Analog Negative Supply for Mixed-Signal Ports.                                                         |

| 24    | PORT6       | Configurable Mixed-Signal Port 6                                                                       |

| 25    | PORT7       | Configurable Mixed-Signal Port 7                                                                       |

| 26    | AGND1       | Analog Ground                                                                                          |

| 28    | PORT8       | Configurable Mixed-Signal Port 8                                                                       |

| 29    | PORT9       | Configurable Mixed-Signal Port 9                                                                       |

| 30    | PORT10      | Configurable Mixed-Signal Port 10                                                                      |

| 31    | PORT11      | Configurable Mixed-Signal Port 11                                                                      |

| 32    | DGND        | Digital Ground                                                                                         |

| _     | EP          | Exposed Pad. Connect EP to AVSSIO.                                                                     |

## Control and Monitoring Application Circuit—PA Biasing—PIXI Solution

#### **Detailed Description**

#### **Functional Overview**

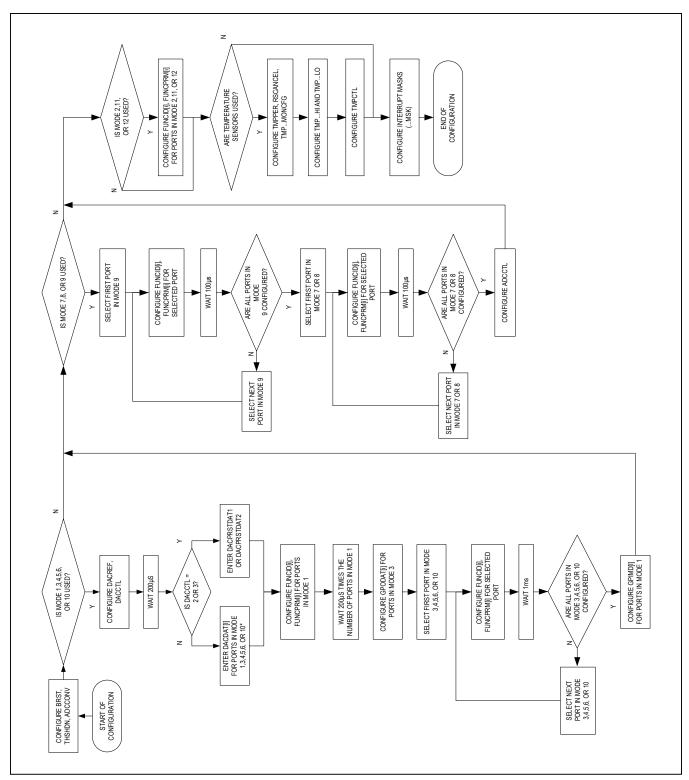

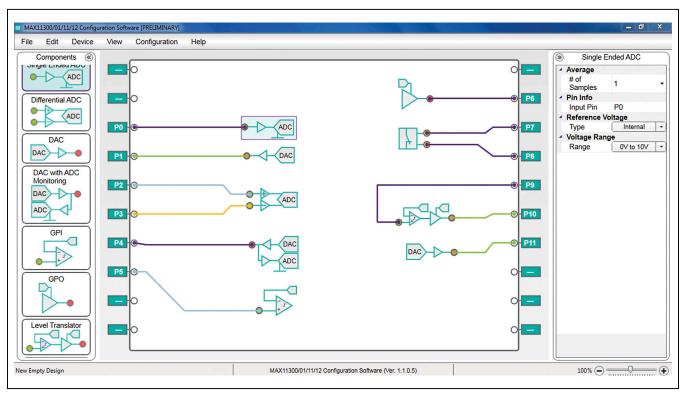

The MAX11312 has 12 configurable mixed-signal I/O ports. Each port is independently configured as a DAC output, an ADC, a GPI input, a GPO, or an analog switch terminal. User-controllable parameters are available for each of those configurations. The device offers one internal and two external temperature sensors. The serial interface operates as a Fast Mode I<sup>2</sup>C-compatible interface.

The DAC is used to drive out a voltage defined by the DAC data register of the DAC-configured ports. The DAC uses either an internal or external voltage reference. The selection of the voltage reference is set for all the ports and cannot be configured on a port-by-port basis.

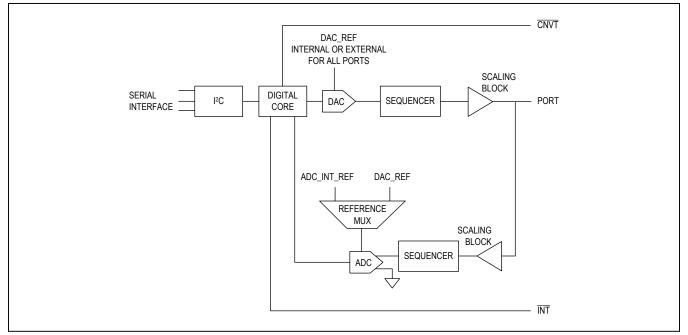

The ADC converts voltages applied to the ADC-configured ports. The ADC can operate in single-ended mode or in differential mode, by which any two ports can form a differential pair. The port configured as the negative input of the ADC can be used by more than one differential ADC input pairs. The ADC uses an internal voltage reference. In some configurations, the ADC uses the DAC voltage reference. The ADC voltage reference selection can be configured on a port-by-port basis.

Interrupts provide the host with the occurrence of userselected events through the configuration of an interrupt mask register.

#### **ADC Operations**

The ADC is a 12-bit, low-power, successive approximation analog-to-digital converter, capable of sampling a single input at up to 400ksps. The ADC's conversion rate can be programmed to 400ksps, 333ksps, 250ksps, or 200ksps. The default conversion rate setting is 200ksps. Each ADC-configured port can be programmed for one of five input voltage ranges: 0 to +10V, -5V to +5V, -10V to 0V, and 0 to +2.5V. The ADC uses the internal ADC 2.5V voltage reference or in some cases, the DAC voltage reference. The voltage reference can be selected on a port-by-port basis.

#### **ADC Control**

The ADC can be triggered using an external signal  $\overline{\text{CNVT}}$  or from a control bit.  $\overline{\text{CNVT}}$  is active-low and must remain low for a minimal duration of 0.5µs to trigger a conversion. Four configurations are available:

- · Idle mode (default setting).

- Single sweep mode. The ADC sweeps sequentially the ADC-configured ports, from the lowest index port to the highest index port, once CNVT is asserted.

- Single conversion mode. The ADC performs a single conversion at the current port in the series of ADCconfigured ports when CNVT is asserted.

- Continuous sweep mode. The ADC continuously sweeps the ADC-configured ports. The CNVT port has no effect in this mode.

#### **ADC Averaging Function**

ADC-configured ports can be configured to average blocks of 2, 4, 8, 16, 32, 64, or 128 conversion results. The corresponding ADC data register is updated only when the averaging is completed, thus decreasing the throughput proportionally. If the number of samples to average is modified for a given port, the content of the ADC data register for that port is cleared before starting to average the new block of samples.

#### **ADC Mode Change**

When users change the ADC active mode (continuous sweep, single sweep, or single conversion), the ADC data registers are reset. However, ADC data registers retain content when the ADC is changed to idle mode.

#### **ADC Configurations**

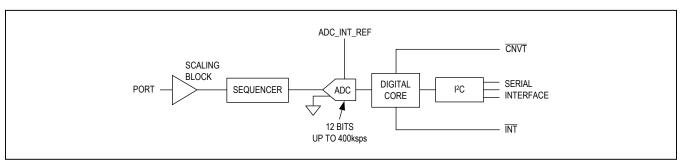

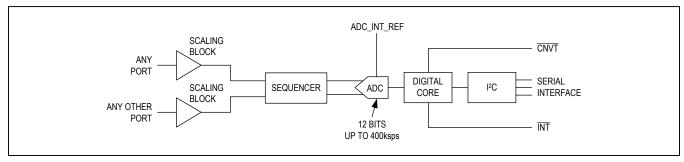

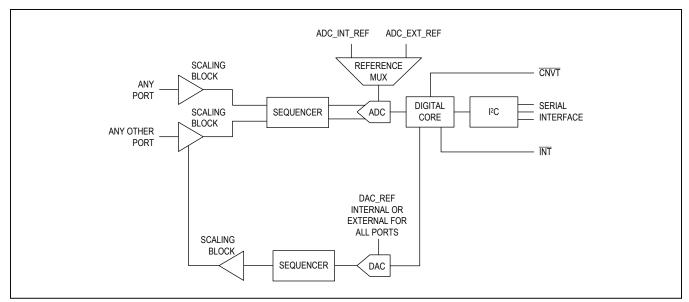

The ADC can operate in single-ended, differential, or pseudo-differential mode. In single-ended mode, the PIXI port is the positive input to the ADC while the negative input is grounded internally (Figure 2). In differential mode (Figure 3), any pair of PIXI ports can be configured as inputs to the differential ADC. In pseudo-differential mode (Figure 4), one PIXI port produces the voltage applied to the negative input of the ADC, while another PIXI port forms the positive input.

The ADC data format is straight binary in single-ended mode, and two's complement in differential and pseudo-differential modes.

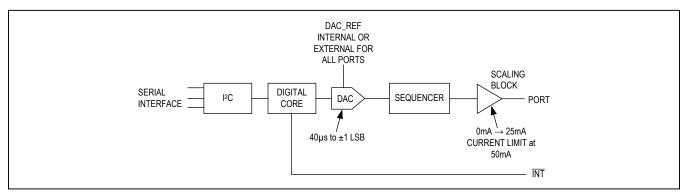

#### **DAC Operations**

The MAX11312 uses a 12-bit DAC, which operates at the rate of 40µs per port. Since up to 12 ports can be configured in DAC-related modes, the minimum refresh rate per port is 2.083KHz.

No external component is required to set the offset and gain of the DAC drivers. The PIXI port driver features a wide output voltage range of ±10V and high-current capability with dedicated power supplies (AVDDIO, AVSSIO).

The DAC uses either the internal or external voltage reference. Unlike the ADC, the DAC voltage reference cannot be configured on a port-by-port basis. DAC mode configuration is illustrated in Figure 5.

DAC operations can be monitored by the ADC. In such a mode, the ADC samples the DAC-configured port to allow the host to monitor that the voltage at the port is within expectations given the accuracy of the ADC and DAC. This ADC monitoring mode is shown in Figure 6.

By default, the DAC updates the DAC-configured ports sequentially. However, users can configure the DAC so that its sequence can jump to update the port that just received new data to convert. After having updated this port, the DAC continues its default sequence from that port. In that mode, users should allow a minimum of 80µs between DAC data register updates for subsequent jump operations.

In addition to port-specific DAC data registers, the host can also use the same data for all DAC-related ports using one of two preset DAC data registers.

All DAC output drivers are protected by overcurrent limit circuitry. In case of overcurrent, the MAX11312 generates an interrupt. Detailed status registers are offered to the host to determine which ports are current limited.

Figure 2. ADC with Single-Ended Input

Figure 3. ADC with Differential Inputs

Figure 4. ADC with Pseudo-Differential Input Set by DAC

Figure 5. DAC Configuration

#### **General-Purpose Input and Output**

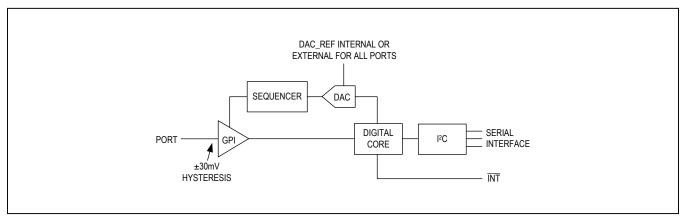

Each PIXI port can be configured as a GPI or a GPO. The GPI threshold is adjusted by setting the DAC data register of that GPI port to the corresponding voltage. If the DAC data register is set at 0x0FFF, the GPI threshold is the DAC reference voltage. The amplitude of the input signal must be contained within 0V to V<sub>AVDD</sub>. The GPI-configured port can be set to detect rising edges, falling edges, either rising or falling edges, or none.

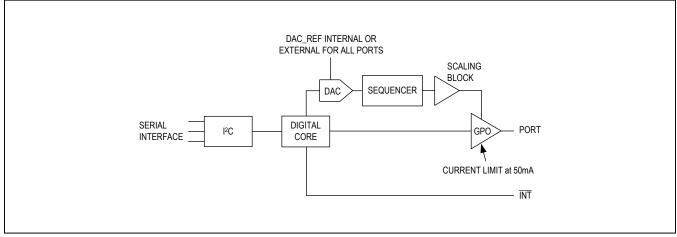

When a port is configured as GPO (Figure 8), the amplitude of its logic-one level is set by its DAC data register. If the DAC data register is set at 0x0FFF, the GPO logic-one

level is four times the DAC reference voltage. The logic-zero level is always 0V. The host can set the logic state of GPO-configured ports through the corresponding GPO data registers.

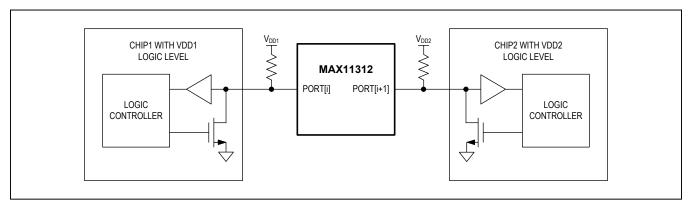

## Unidirectional and Bidirectional Level Translator Operations

By combining GPI and GPO-configured ports, unidirectional level translator paths can be formed. The signaling at the input of the path can be different from the signaling at the end (Figure 9). For example, a unidirectional path could convert a signal from 1.8V logic level to 3.3V logic level.

Figure 6. DAC Configuration with ADC Monitoring

The unidirectional path configuration allows for the transmission of signals received on a GPI-configured port to one or more GPO-configured ports.

Pairs of adjacent PIXI ports can also form bidirectional level translator paths that are targeted to operate with open-drain drivers (Figure 10). In this configuration, adjacent PIXI ports must be from the same six-channel group: PORT0 to PORT5 or PORT6 to PORT11. When used as a bidirectional level translator, the pair of PIXI ports must be accompanied with external pullup resistors to meet proper logic levels.

## Internally or Externally Controlled Analog Switch Operation

Two adjacent PIXI ports from the same group of ports (PORT0 to PORT5 or PORT6 to PORT11) can form a  $60\Omega$  analog switch that is controlled by two different configurations. Analog switches cannot be configured between programmable ports in different groups, such as between PORT5 and PORT6 or between PORT0 and PORT11. In one configuration, the switch is dynamically controlled by any other GPI-configured PIXI port, as illustrated in Figure 11. The signal applied to that GPI-configured port can be inverted.

In the other configuration, the switch is programmed to be permanently "ON" by configuring the corresponding PIXI port. To turn the switch "OFF", the host must set that PIXI port in high-impedance configuration.

#### **Power-Supply Brownout Detection**

The MAX11312 features a brownout detection circuit that monitors AVDDIO and AVDD pins. When AVDDIO goes below approximately 4.0V, an interrupt is registered, and the interrupt port is asserted if not masked. When AVDD goes below approximately 4.0V, the device resets.

#### I<sup>2</sup>C Operations

The MAX11312 serial interface is compatible with the I<sup>2</sup>C Fast Mode (SCL at 400kHz).

The MAX11312 has a configurable 7-bit slave address. The first four bits of all MAX11312 slave addresses are always 0111. Slave address bits A2, A1, and A0 are shown in <u>Table 1</u>. The AD0 and AD1 inputs are connected to any of three signals: DGND, DVDD, SDA, or SCL giving eight possible slave addresses, and allowing up to eight MAX11312 devices to share the bus.

Basic write and read transactions are structured as shown in Table 2 and Table 3, respectively. For write transactions, the targeted register content is modified only after the third byte has been fully received. A burst transaction would simply be the extension of the single register transaction, where the address is automatically incremented from one data word to the next (Table 4 and Table 5). Each time a new data sample is read or written, the register address is incremented by one until it reaches the last register

Table 1. MAX11312 Slave Addresses

| PIN AD1 | PIN AD0 |    |    | SL | AVE ADDRE | SS |    |    |

|---------|---------|----|----|----|-----------|----|----|----|

| PIN AD1 | PIN ADU | A6 | A5 | A4 | А3        | A2 | A1 | A0 |

| DGND    | DGND    | 0  | 1  | 1  | 1         | 0  | 0  | 0  |

| DGND    | SDA     | 0  | 1  | 1  | 1         | 0  | 0  | 1  |

| DGND    | SCL     | 0  | 1  | 1  | 1         | 0  | 1  | 0  |

| DGND    | DVDD    | 0  | 1  | 1  | 1         | 0  | 1  | 1  |

| DVDD    | DGND    | 0  | 1  | 1  | 1         | 1  | 0  | 0  |

| DVDD    | SDA     | 0  | 1  | 1  | 1         | 1  | 0  | 1  |

| DVDD    | SCL     | 0  | 1  | 1  | 1         | 1  | 1  | 0  |

| DVDD    | DVDD    | 0  | 1  | 1  | 1         | 1  | 1  | 1  |

### Table 2. Single Register I<sup>2</sup>C Write Transaction Format

|                      | В7 | В6 | B5      | B4         | В3        | B2    | B1 | В0   | N/ACK |

|----------------------|----|----|---------|------------|-----------|-------|----|------|-------|

| START                |    |    |         |            |           |       |    |      |       |

| 1 <sup>st</sup> byte |    |    | 7-Bit S | lave Addre | ss[6:0]   |       |    | R/WB | ACK   |

| 2 <sup>nd</sup> byte | 0  |    |         |            | Address   | [6:0] |    |      | ACK   |

| 3 <sup>rd</sup> byte |    |    |         | Da         | ata[15:8] |       |    |      | ACK   |

| 4 <sup>th</sup> byte |    |    |         | D          | ata[7:0]  |       |    |      | ACK   |

| STOP                 |    |    |         |            |           |       |    |      |       |

### Table 3. Single Register I<sup>2</sup>C Read Transaction Format

|                      | B7 | В6 | B5        | B4       | В3        | B2    | B1 | В0   | N/ACK            |

|----------------------|----|----|-----------|----------|-----------|-------|----|------|------------------|

| START                |    |    |           |          |           |       |    |      |                  |

| 1 <sup>st</sup> byte |    |    | 7-Bit Sla | ave Addr | ess[6:0]  |       |    | R/WB | ACK              |

| 2 <sup>nd</sup> byte | 0  |    |           |          | Address   | [6:0] |    |      | ACK              |

| RESTART              |    |    |           |          |           |       |    |      |                  |

| 1 <sup>st</sup> byte |    |    | 7-Bit Sla | ave Addr | ess[6:0]  |       |    | R/WB | ACK              |

| 3 <sup>rd</sup> byte |    |    |           | Da       | ata[15:8] |       |    |      | ACK              |

| 4 <sup>th</sup> byte |    |    |           | D        | ata[7:0]  |       |    |      | NACK (from host) |

| STOP                 |    |    |           |          |           |       |    |      |                  |

Table 4. Multiple Register I<sup>2</sup>C Write Transaction Format

|                       | В7 | В6 | B5      | B4          | В3         | B2     | B1 | В0   | N/ACK |

|-----------------------|----|----|---------|-------------|------------|--------|----|------|-------|

| START                 |    |    |         |             |            |        |    |      |       |

| 1 <sup>st</sup> byte  |    |    | 7-Bit S | Slave Addre | ess[6:0]   |        |    | R/WB | ACK   |

| 2 <sup>nd</sup> byte  | 0  |    |         |             | Address_   | N[6:0] |    |      | ACK   |

| 3 <sup>rd</sup> byte  |    |    |         | Dat         | ta_N[15:8] |        |    |      | ACK   |

| 4 <sup>th</sup> byte  |    |    |         | Da          | ata_N[7:0] |        |    |      | ACK   |

| 5 <sup>th</sup> byte  |    |    |         | Data        | N+1[15:8   | ]      |    |      | ACK   |

| 6 <sup>th</sup> byte  |    |    |         | Data        | a_N+1[7:0] |        |    |      | ACK   |

| 7 <sup>th</sup> byte  |    |    |         | Data        | N+2[15:8   | ]      |    |      | ACK   |

| 8 <sup>th</sup> byte  |    |    |         | Data        | a_N+2[7:0] |        |    |      | ACK   |

| 9 <sup>th</sup> byte  |    |    |         | Data        | _N+3[15:8  | ]      |    |      | ACK   |

| 10 <sup>th</sup> byte |    |    |         | Data        | a_N+3[7:0] |        |    |      | ACK   |

| 11 <sup>th</sup> byte |    |    |         |             |            |        |    |      | ACK   |

|                       |    |    |         |             |            |        |    |      |       |

| 25 <sup>th</sup> byte |    |    |         | Data        | _N+11[15:8 | B]     |    |      | ACK   |

| 26th byte             |    |    |         | Data        | a_N+11[7:0 | ]      |    |      | ACK   |

| STOP                  |    |    |         |             |            |        |    |      |       |

Table 5. Multiple Register I<sup>2</sup>C Read Transaction Format

|                       | В7 | В6 | B5    | B4            | В3            | B2 | B1 | В0   | N/ACK               |

|-----------------------|----|----|-------|---------------|---------------|----|----|------|---------------------|

| START                 |    |    |       |               |               |    |    |      |                     |

| 1 <sup>st</sup> byte  |    |    | 7-Bit | t Slave Addre | ess[6:0]      |    |    | R/WB | ACK                 |

| 2 <sup>nd</sup> byte  | 0  |    |       | P             | Address_N[6:0 | 0] |    |      | ACK                 |

| RESTART               |    |    |       |               |               |    |    |      |                     |

| 1 <sup>st</sup> byte  |    |    | 7-Bit | t Slave Addre | ess[6:0]      |    |    | R/WB | ACK                 |

| 3 <sup>rd</sup> byte  |    |    |       | Data_         | N[15:8]       |    |    |      | ACK                 |

| 4 <sup>th</sup> byte  |    |    |       | Data          | _N[7:0]       |    |    |      | ACK                 |

| 5 <sup>th</sup> byte  |    |    |       | Data_l        | N+1[7:0]      |    |    |      | ACK                 |

| 6 <sup>th</sup> byte  |    |    |       | Data_N        | l+1[15:8]     |    |    |      | ACK                 |

| 7 <sup>th</sup> byte  |    |    |       | Data_l        | N+1[7:0]      |    |    |      | ACK                 |

| 8 <sup>th</sup> byte  |    |    |       | Data_N        | l+2[15:8]     |    |    |      | ACK                 |

| 9 <sup>th</sup> byte  |    |    |       | Data_l        | N+2[7:0]      |    |    |      | ACK                 |

| 10 <sup>th</sup> byte |    |    |       | Data_N        | l+3[15:8]     |    |    |      | ACK                 |

| 11 <sup>th</sup> byte |    |    |       | Data_l        | N+3[7:0]      |    |    |      | ACK                 |

| •••                   |    |    |       |               |               |    |    |      |                     |

| 25 <sup>th</sup> byte |    |    |       | Data_N        | +11[15:8]     |    |    |      | ACK                 |

| 26 <sup>th</sup> byte |    |    |       | Data_N        | l+11[7:0]     |    |    |      | NACK<br>(from host) |

| STOP                  |    |    |       |               |               |    |    |      |                     |

address. The RESTART shown in <u>Tables 3</u> and  $\underline{5}$  could be replaced by a STOP followed by a START.

If a transaction targets an unused address, nothing is written within the MAX11312 for write transactions, and all zeros are read back for read transactions. Similarly, if a write transaction targets a read-only register, nothing is written to the device.

#### **Burst Transaction Address Incrementing Modes**

With a burst transaction, the address of the initial register is entered once. The data of the targeted register can then be written or read. If the serial clock keeps running without issuing RESTART, the device increments the address pointer and writes or reads the next data after the next

Figure 7. GPI Mode

Figure 8. GPO Mode

two bytes. This scheme goes on until the host produces a NACK (read transactions) or a STOP (write transactions).

There are two address incrementing modes. In one mode, the address is simply incremented by one (default mode), while in the other, the address is incremented contextually. When writing DAC data registers in a burst fashion using contextual addressing, the host would write the address of the first port that is DAC-configured (starting from the lowest port index). As long as the host does not issue a STOP and another two bytes are received, the next DAC-configured port is written. This scheme continues until the last DAC-configured port is reached. At that point, any

additional serial clock cycle results in looping back to the first DAC-configured port.

The contextual addressing scheme is only valid for writing DAC data registers, as described above, and reading ADC data registers.

#### **Interrupt Operations**

The device issues interrupts to alert the host of various events. All events are recorded by the interrupt register. The assertion of an interrupt register bit results in the assertion of the interrupt port (INT) if that interrupt bit is

Figure 9. Unidirectional Level Translator Path Mode

Figure 10. Bidirectional Level Translation Application Diagram

not masked. By default, all interrupts are masked upon power-up or reset. The interrupts are listed hereafter.

The ADCFLAG (ADC Flag) interrupt indicates that the ADC just completed a conversion or set of conversions. It is asserted either at the end of a conversion when the ADC is in single-conversion mode or at the end of a sweep when the ADC is either in single-sweep mode or continuous-sweep mode. ADCFLAG is cleared when the interrupt register is read.

The ADCDR (ADC Data Ready) interrupt is asserted when at least one ADC data register is refreshed. Since one conversion per ADC-configured port is performed per sweep, many sweeps may be required before refreshing the data register of a given ADC-configured port that utilizes the averaging function. (See the ADC Averaging Function section) To determine which ADC-configured port received a new data sample, the host must read the ADC status registers. ADCDR is cleared after the interrupt register and both ADC status registers are read subsequently.

The ADCDM (ADC Data Missed) interrupt is asserted when any ADC data register is not read by the host before new data is stored in that ADC data register. ADCDM is cleared after the interrupt register is read.

The GPIER (GPI Event Received) interrupt indicates that an event has been received on one of the GPI-configured ports. Each GPI port can be configured to generate an interrupt for an event such as detecting a rising edge, a falling edge, or either edge at the corresponding port. If the GPI port is configured to detect no edge, it is equivalent to masking the interrupt related to that port. A GPI status register allows the host to identify which port detected the event. GPIER is cleared after the interrupt register and both GPI status registers are read subsequently.

The GPIEM (GPI Event Missed) interrupt informs the host that it did not service the GPI interrupt caused by the occurrence of an event recorded by GPI status registers before another event was received on the same port. The host must read the interrupt register and the GPI status registers whenever a GPI event received interrupt occurs; otherwise, the GPIEM register is asserted upon receiving

the next event. This interrupt must be used in conjunction with the GPIER interrupt bit to operate properly. GPIEM is cleared after the interrupt register and both GPI status registers are read subsequently.

The DACOI (DAC Overcurrent) interrupt indicates that a DAC-configured port current exceeded approximately 50mA. This limit is not configurable. A DAC overcurrent status register allows the host to identify which DAC-configured port exceeded the 50mA current limit. DACOI is cleared after the interrupt register is read, and both DAC overcurrent status registers are read subsequently.

The TMPINT[2:0] (Internal Temperature Monitor) interrupt has three sources of interrupt, each independently controllable: a new internal temperature data is ready, the internal temperature value exceeds the maximum limit, or the internal temperature value is below the minimum limit. TMPINT is cleared after the interrupt register is read.

The TMPEXT1[2:0] (1st External Temperature Monitor) interrupt has three sources of interrupt, each independently controllable: a new first external temperature data is ready, the first external temperature value exceeds the maximum limit, or the first external temperature value is below the minimum limit. TMPEXT1 is cleared after the interrupt register is read.

The TMPEXT2[2:0] (2nd External Temperature Monitor) interrupt has three sources of interrupt, each independently controllable: a new second external temperature data is ready, the second external temperature value exceeds the maximum limit, or the second external temperature value is below the minimum limit. TMPEXT2 is cleared after the interrupt register is read.

The  $V_{MON}$  (High-Voltage Supply Monitor) Supply Voltage Failure) interrupt is triggered when AVDDIO supply voltage falls below 4V, approximately.  $V_{MON}$  is cleared after the interrupt register is read.

Figure 11. PIXI Ports as a Controllable Analog Switch

#### MAX11312

## PIXI, 12-Port Programmable Mixed-Signal I/O with 12-Bit ADC, 12-Bit DAC, Analog Switches, and GPIO

#### **Temperature Sensors Overview**

The device integrates one internal and two external temperature sensors. The external sensors are diodeconnected transistors, typically a low-cost, easily mounted 2N3904 NPN type, that replace conventional thermistors or thermocouples. The external sensors' accuracy is typically ±1°C over the -40°C to +150°C temperature range with no calibration necessary. Use of a transistor with a different ideality factor produces a proportionate difference in the absolute measured temperature. Parasitic series resistance results in a temperature reading error of about 0.25°C per

Ohm of resistance. The MAX11312 features a series resistance cancellation mode (RS\_CANCEL) that eliminates this error for resistances up to  $10\Omega$ . The external sensors can also measure the die temperature of other ICs, such as microprocessors, that contain a substrate-connected diode available for temperature-sensing purposes. Temperature data can be read from the temperature data registers. The temperature data format is in two's complement, with one LSB representing  $0.125^{\circ}C$ .

Register bits that are shown unused do not impact device functionality and read out as "0". Register bits that are shown as reserved cannot be written by a value different from their default value. Writing a different value to those bits may affect the functionality of the device. Register Description

| be written by a value different from their default value. Writing a different value to those bits may affect the functionality of the device.<br>Table 6. Register Table (Read/Write) | B4         B3         B2         B1         B0         DEFAULT | 0x1424      | GPIDM GPIDR ADCDM ADCDR ADCFLAG 0x0000 | ADCST[5:0] reserved reserved 0x00000 | reserved reserved ADCST 0x0000 | DACOIST[5:0] reserved reserved 0x0000 | reserved reserved DACOIST 0x0000 | GPIST[5:0] reserved 0x0000 | reserved reserved GPIST[11] 0x0000 | 0000×0 [0:                      | 000000                                          | 000000                                          | GPIDAT[5:0] reserved reserved 0x00000 | reserved reserved GPIDAT 0x0000 | GPODAT[5:0] reserved reserved 0x00000 | reserved reserved GPODAT 0x0000 | ont[1:0] DACCtL[1:0] ADCCTL[1:0] 0x0000 | GPID         GPIDR         ADCDM         ADCDR         ADCDR         ADCTLAG         OXFFFF           MMSK         MSK         MSK         MSK         OXFFFF |                            | rived reserved 0x0000       |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------|----------------------------------------|--------------------------------------|--------------------------------|---------------------------------------|----------------------------------|----------------------------|------------------------------------|---------------------------------|-------------------------------------------------|-------------------------------------------------|---------------------------------------|---------------------------------|---------------------------------------|---------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|--|