# High Efficiency Ultra Small Thinnest White LED Driver

The NCP5612 product is a dual output LED driver dedicated to the LCD display backlighting.

The built–in DC/DC converter is based on a high efficient charge pump structure with operating mode 1x and 1.5x. It provides a peak 87% efficiency together with a 0.2% LED to LED matching.

### Features

- Support the Single Wire Serial Link Protocol

- Peak Efficiency 90% with 1x and 1.5x Mode

- Programmable Dimming ICON Function

- Built-in Short Circuit Protection

- Provides 16 steps Current Control

- Controlled Start-up Inrush Current

- Built-in Automatic Open Load Protection

- Tight 0.2% Matching Tolerance

- Accurate 1% Output Current Tolerance

- Smallest Available Package on the Market

- This is a Pb–Free Device

### **Typical Applications**

- Portable Back Light

- Digital Cellular Phone Camera Photo Flash

- LCD and Key Board Simultaneous Drive

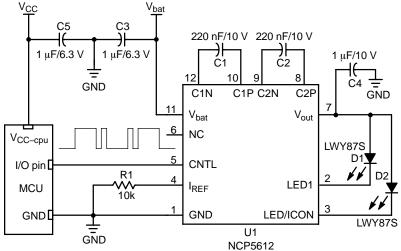

Figure 1. Typical Single Wire White LED Driver

# **ON Semiconductor®**

http://onsemi.com

YD = Specific Device Code

M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

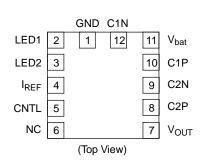

### PIN CONNECTIONS

## ORDERING INFORMATION

| Device       | Package             | Shipping†        |

|--------------|---------------------|------------------|

| NCP5612MUTBG | LLGA12<br>(Pb–Free) | 3000/Tape & Reel |

+ For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

Figure 2. Simplified Block Diagram

## **PIN FUNCTION DESCRIPTION**

| Pin No. | Symbol           | Function       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

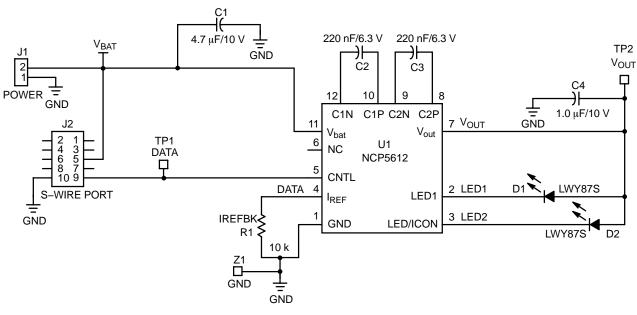

| 1       | GND              | POWER          | This pin is the GROUND signal for the power analog blocks and must be connected to the system ground. This pin is the GROUND reference for the DC/DC converter and the output current control. The pin must be connected to the system ground, a ground plane being strongly recommended.                                                                                                                                                                                                                                                                                                     |

| 2       | LED1             | INPUT, POWER   | This pin sinks to ground and monitors the current flowing into the first LED,<br>intended to be used in backlight application. The current is limited to 30 mA<br>maximum (Note 2).<br>The LED1 is deactivated when the ICON bit of the LED–REG register is High.<br>The LED1 is automatically disconnected when an open load is sensed pin 2<br>during the operation.                                                                                                                                                                                                                        |

| 3       | LED2             | INPUT, POWER   | This pin sinks to ground and monitors the current flowing into the second LED, intended to be used in backlight application. The current is limited to 30 mA maximum (Note 2). The LED2 fulfills the ICON function, LED1 being deactivated, when the ICON bit of the LED–REG register is High. The LED2 is automatically disconnected when an open load is sensed pin 3 during the operation.                                                                                                                                                                                                 |

| 4       | I <sub>REF</sub> | INPUT, ANALOG  | This pin provides the reference current, based on the internal band–gap voltage reference, to control the output current flowing in the LED. A 1% tolerance, or better, resistor shall be used to get the highest accuracy of the LED biases. An external current source can be used to bias this pin to dim the light coming out of the LED. In no case shall the voltage at pin 4 be forced either higher or lower than the 600 mV provided by the internal reference.                                                                                                                      |

| 5       | CNTL             | INPUT, DIGITAL | This pin supports the flow of data between the external MCU and the NCP5612 internal registers. The protocol makes profit of a Single Wire structure associated to a Serial 8 bits format data flow.                                                                                                                                                                                                                                                                                                                                                                                          |

| 6       | NC               | -              | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7       | Vout             | OUTPUT, POWER  | This pin provides the output voltage supplied by the DC/DC converter. The $V_{out}$ pin must be decoupled to ground by a 1 $\mu$ F ceramic capacitor located as close as possible to the pin. Cares must be observed to minimize the parasitic inductance at this pin. The circuit shall not operate without such bypass capacitor connected across the $V_{out}$ pin and ground. The output voltage is internally clamped to 5.5 V maximum in the event of no load situation. On the other hand, the output current is limited to 40 mA (typical) in the event of a short circuit to ground. |

| 8       | C2P              | POWER          | One side of the external charge pump capacitor ( $C_{FLY}$ ) is connected to this pin, associated with C2N (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9       | C2N              | POWER          | One side of the external charge pump capacitor ( $C_{FLY}$ ) is connected to this pin, associated with C2P (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10      | C1P              | POWER          | One side of the external charge pump capacitor ( $C_{FLY}$ ) is connected to this pin, associated with C1N (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11      | V <sub>BAT</sub> | INPUT, POWER   | Input Battery voltage to supply the analog and digital blocks. The pin must be decoupled to ground by a 1.0 $\mu F$ minimum ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12      | C1N              | POWER          | One side of the external charge pump capacitor ( $C_{FLY}$ ) is connected to this pin, associated with C1P (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

1. Using low ESR ceramic capacitor, 50 m $\Omega$  maximum, is mandatory to optimize the Charge Pump efficiency. 2. Total DC/DC output current is limited to 60 mA.

#### MAXIMUM RATINGS

| Rating                                                                                                                                               | Symbol                                                 | Value                              | Unit               |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------|--------------------|

| Power Supply                                                                                                                                         | V <sub>BAT</sub>                                       | 7.0                                | V                  |

| Output Power Supply                                                                                                                                  | Vout                                                   | 7.0                                | V                  |

| Digital Input Voltage<br>Digital Input Current                                                                                                       | CNTL                                                   | -0.3 < V < V <sub>BAT</sub><br>1.0 | V<br>mA            |

| Human Body Model: R = 1500 $\Omega$ , C = 100 pF (Note 3) Machine Model                                                                              | ESD                                                    | 2.0<br>200                         | kV<br>V            |

| LLGA12 Package<br>Power Dissipation @ T <sub>A</sub> = +85°C (Note 4)<br>Thermal Resistance, Junction–to–Case<br>Thermal Resistance, Junction–to–Air | Ρ <sub>D</sub><br>R <sub>θJC</sub><br>R <sub>θJA</sub> | 200<br>51<br>200                   | mW<br>°C/W<br>°C/W |

| Operating Ambient Temperature Range                                                                                                                  | T <sub>A</sub>                                         | -40 to +85                         | °C                 |

| Operating Junction Temperature Range                                                                                                                 | TJ                                                     | -40 to +125                        | °C                 |

| Maximum Junction Temperature                                                                                                                         | T <sub>Jmax</sub>                                      | +150                               | °C                 |

| Storage Temperature Range                                                                                                                            | T <sub>stg</sub>                                       | -65 to +150                        | °C                 |

| Latch-up Current Maximum Rating per JEDEC Standard: JESD78                                                                                           | -                                                      | ±100                               | mA                 |

| Moisture Sensitivity (Note 5)                                                                                                                        | -                                                      | 1                                  |                    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

3. This device series contains ESD protection and exceeds the following tests: Human Body Model (HBM) ±2.0 kV per JEDEC standard: JESD22–A114. Machine Model (MM) ±200 V per JEDEC standard: JESD22–A115.

4. The maximum package power dissipation limit must not be exceeded.

5. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

**POWER SUPPLY SECTION** (Typical values are referenced to  $T_A = +25^{\circ}C$ , Min & Max values are referenced  $-40^{\circ}C$  to  $+85^{\circ}C$  ambient temperature, operating conditions 2.85 V < V<sub>bat</sub> < 5.5 V, unless otherwise noted.)

| Rating                                                                                                                                                                                                                                                                                                                                      | Pin  | Symbol               | Min | Тур      | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|-----|----------|------|------|

| Power Supply                                                                                                                                                                                                                                                                                                                                | 11   | V <sub>bat</sub>     | 2.7 | -        | 5.5  | V    |

| Continuous DC Current in the Load @ V_f = 3.8 V, 3.2 V < V_{bat} < 5.5 V, ICON = L (30 mA per LED)                                                                                                                                                                                                                                          | 7    | l <sub>out</sub>     | 60  | _        | -    | mA   |

| Output ICON Current (ICON bit = H) @ 3.2 V < V <sub>bat</sub> < 4.2 V, T <sub>A</sub> = +25°C                                                                                                                                                                                                                                               | 7    | I <sub>ICONTOL</sub> | -   | 450      | 550  | μΑ   |

| Continuous Output Short Circuit Current                                                                                                                                                                                                                                                                                                     | 7    | I <sub>sch</sub>     | Ι   | 40       | 100  | mA   |

| Output Voltage Compliance (OVP)                                                                                                                                                                                                                                                                                                             | 7    | Vout                 | 4.8 | -        | 5.7  | V    |

| DC/DC Start Time (C <sub>out</sub> = 1.0 $\mu F$ ) from end of the CNTL T <sub>dst</sub> delay to full load operation, @ V <sub>bat</sub> = 3.6 V                                                                                                                                                                                           | 12   | T <sub>start</sub>   | -   | 150      | -    | μs   |

| Output Voltage Turn–off (C_{out} = 1 $\mu F)$ From Last Low Level at CNTL pin to $V_{out}$ = 5%                                                                                                                                                                                                                                             | 12   | T <sub>off</sub>     | -   | 500      | -    | μs   |

| Standby Current, $0^{\circ}C < T_A < +85^{\circ}C$<br>$V_{bat} = 3.6$ V, $I_{out} = 0$ mA, ICON = L                                                                                                                                                                                                                                         | 11   | I <sub>stdb</sub>    | -   | -        | 1.0  | μΑ   |

| Operating Current, @ I <sub>out</sub> = 0 mA, ICON = H, V <sub>bat</sub> = 3.6 V                                                                                                                                                                                                                                                            | 11   | I <sub>op</sub>      | -   | 600      | -    | μΑ   |

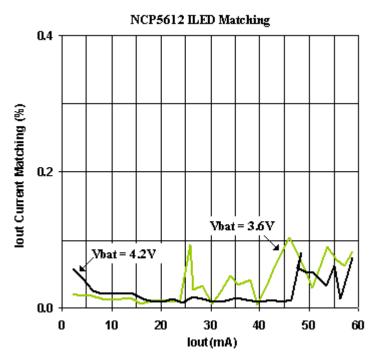

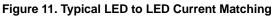

| Output LED to LED Current Matching, $V_{bat}$ = 3.6 V,<br>I <sub>LED</sub> = 10 mA, LED1 & LED2 are Identical -25°C < T <sub>A</sub> < 85°C                                                                                                                                                                                                 | 2, 3 | I <sub>MAT</sub>     | -   | ±0.2     | ±1.0 | %    |

| Output Current Tolerance @ V <sub>bat</sub> = 3.6 V, I <sub>LED</sub> = 10 mA –25°C < Ta < 85°C                                                                                                                                                                                                                                             | 2, 3 | I <sub>TOL</sub>     | Ι   | ±1.0     | -    | %    |

| Charge Pump Operating Frequency                                                                                                                                                                                                                                                                                                             | -    | F <sub>pwr</sub>     | -   | 1.0      | -    | MHz  |

| Thermal Shutdown Protection                                                                                                                                                                                                                                                                                                                 | -    | T <sub>SD</sub>      | -   | 160      | -    | °C   |

| Thermal Shutdown Protection Hysteresis                                                                                                                                                                                                                                                                                                      | -    | T <sub>SDH</sub>     | -   | 30       | -    | °C   |

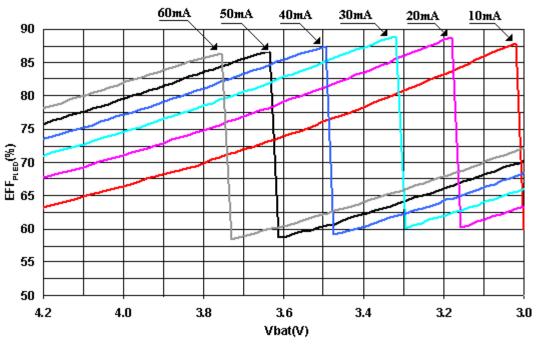

| $ \begin{array}{l} \mbox{Efficiency} - \mbox{LED1} = \mbox{LED2} = 10 \mbox{ mA}, \mbox{V}_{f} = 3.2 \mbox{ V}, \mbox{V}_{bat} = 3.8 \mbox{ V} \mbox{(Total} = 20 \mbox{ mA}) \\ - \mbox{LED1} = \mbox{LED2} = 30 \mbox{ mA}, \mbox{V}_{f} = 3.75 \mbox{ V}, \mbox{V}_{bat} = 3.8 \mbox{ V} \mbox{(Total} = 60 \mbox{ mA}) \\ \end{array} $ | -    | E <sub>PWR</sub>     | -   | 87<br>84 |      | %    |

**ANALOG SECTION** (Typical values are referenced to  $T_A = +25^{\circ}$ C, Min & Max values are referenced  $-40^{\circ}$ C to  $+85^{\circ}$ C ambient temperature, operating conditions 2.85 V < V<sub>bat</sub> < 5.5 V, unless otherwise noted.)

| Rating                                                       | Pin | Symbol            | Min | Тур | Max | Unit |

|--------------------------------------------------------------|-----|-------------------|-----|-----|-----|------|

| Reference Current @ V <sub>ref</sub> = 600 mV (Note 7)       | 4   | I <sub>REF</sub>  | 1.0 | _   | 60  | μΑ   |

| Reference Voltage (Note 7) $0^{\circ}C < T_A < +85^{\circ}C$ | 4   | V <sub>REF</sub>  | -3% | 600 | +3% | mV   |

| Base Reference Current (IREF) Current Ratio                  | -   | I <sub>LEDR</sub> | -   | 500 | -   | -    |

6. The overall output current tolerance depends upon the accuracy of the external resistor. Using 1% or better resistor is recommended.

7. The external circuit must not force the I<sub>REF</sub> pin voltage either higher or lower than the 600 mV specified.

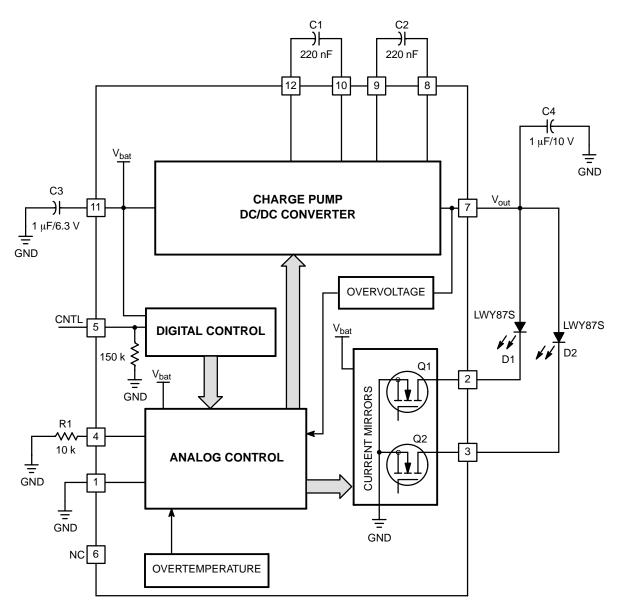

**DIGITAL PARAMETERS SECTION** (Typical values are referenced to  $T_A = +25^{\circ}$ C, Min & Max values are referenced  $-40^{\circ}$ C to  $+85^{\circ}$ C ambient temperature, operating conditions 2.85 V < V<sub>bat</sub> < 5.5 V, unless otherwise noted.) Note: Digital inputs undershoot < -0.30 V to ground, Digital inputs overshoot < 0.30 V to V<sub>BAT</sub>.

| Rating                                                    | Pin | Symbol                             | Min | Тур | Max              | Unit |

|-----------------------------------------------------------|-----|------------------------------------|-----|-----|------------------|------|

| Positive going Input High Voltage Threshold, CNTL signals | 5   | V <sub>IH</sub>                    | 1.4 | -   | V <sub>BAT</sub> | V    |

| Negative going Input Low Voltage Threshold, CNTL signals  | 5   | VIL                                | -   | -   | 0.6              | V    |

| Pull Down Resistor                                        | 5   | R <sub>cntl</sub>                  | -   | 150 | -                | kΩ   |

| Delay between two consecutive frame (Note 9)              | 5   | t <sub>idle</sub>                  | 10  | -   | -                | μs   |

| Wake up delay (Note 9)                                    | 5   | t <sub>wkp</sub>                   | -   | -   | 1.0              | μs   |

| CNTL signal rise and fall time (Note 9)                   | 5   | t <sub>r</sub> , t <sub>f</sub>    | -   | -   | 200              | ns   |

| Clocked CNTL High (Note 9)                                | 5   | t <sub>on</sub>                    | -   | -   | 75               | μs   |

| CNTL Low (Note 9)                                         | 5   | t <sub>on</sub> , t <sub>off</sub> | 1.0 | -   | -                | μs   |

| CNTL Store data delay (Note 9)                            | 5   | T <sub>dst</sub>                   | -   | 200 | 300              | μs   |

| Input CNTL frequency (Note 9)                             | 5   | F <sub>CNTL</sub>                  | _   | -   | 400              | kHz  |

8. see Timings Reference

9. Parameter not tested in production, guaranteed by design.

#### **APPLICATION INFORMATION**

Figure 4. Basic Cellular Phone Chip Set Digital Output Levels

#### **DC/DC Operation**

The converter is based on a charge pump technique to generate a DC voltage capable to supply the White LED load. The system regulates the current flowing into each LED by means of internal current mirrors associated with the white diodes. Consequently, the output voltage will be equal to the V<sub>f</sub> of the LED, plus the drop voltage (ranging from 150 mV to 400 mV, depending upon the output current and V<sub>bat</sub> / V<sub>f</sub> ratio) developed across the internal NMOS mirror. Typically, assuming a standard white LED forward biased at 10 mA, the output voltage will be 3.6 V.

The built-in OVP circuit continuously monitors the output voltage and stops the converter when the voltage is above 5.0 V typical. The converter resumes to normal operation when the voltage drops below the typical 5.0 V (no latch-up mechanism). Consequently, the chip can operate with no load during any test procedures.

#### Load Current Calculation

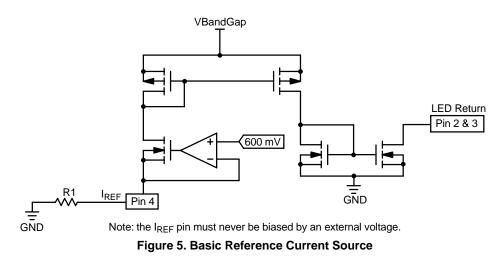

The load current is derived from the 600 mV reference voltage provided by the internal Band Gap associated to the

external resistor connected across  $I_{REF}$  pin and Ground (see Figure 5). In any case, no voltage shall be forced at  $I_{REF}$  pin, either downward or upward.

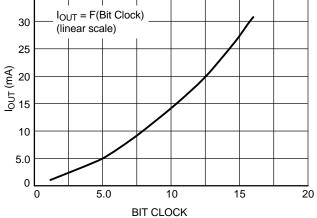

The reference current is multiplied by the internal current mirror, associated to the number of pulses as depicted Figure 9, to yield the output load current. Since the reference voltage is based on a temperature compensated Band Gap, a tight tolerance resistor will provide a very accurate load current. The resistor is calculated from the Ohm's law ( $R_{bias} = V_{ref}/I_{REF}$ ) and define the maximum current flowing into the LED when 20 pulses have been counted at the CNTL pin.

Since the reference current must be between the minimum and maximum specified, the resistor value will range between  $R_{bias} = 300/30 \text{ mA} = 10 \text{ k}\Omega$  and  $R_{bias} = 300/0.5 \text{ mA} = 600 \text{ k}\Omega$ . Obviously, the tolerance of such a resistor must be 1% or better, with a 100 ppm thermal coefficient, to get the expected overall tolerance.

Typical applications will run with  $R_{bias} = 10 \text{ k}\Omega$  to make profit of the full dynamic range provided by the S–Wire DATA byte.

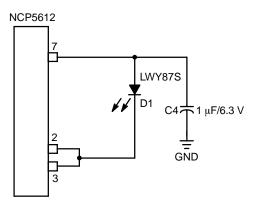

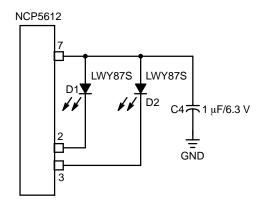

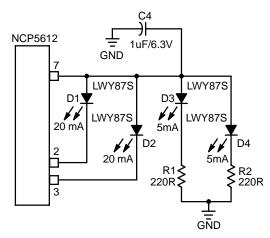

#### Load Connection

The NCP5612 is capable to drive the two LED simultaneously, as depicted (see Figure 1), but the load can be arranged to accommodate one or two LED if necessary

in the application (see Figure 6). In this case, the two current mirrors can be connected in parallel to drive a single powerful LED, thus yielding 60 mA current capability in a single LED.

Figure 6. Typical Single and Double LED Connections

Finally, an external network can be connected across  $V_{out}$  and ground, but the current through such network will not be regulated by the NCP5612 chip (see Figure 7). On top of that, the total current out of the  $V_{out}$  pin shall be limited to 60 mA.

Figure 7. Extra Load Connected to Vout

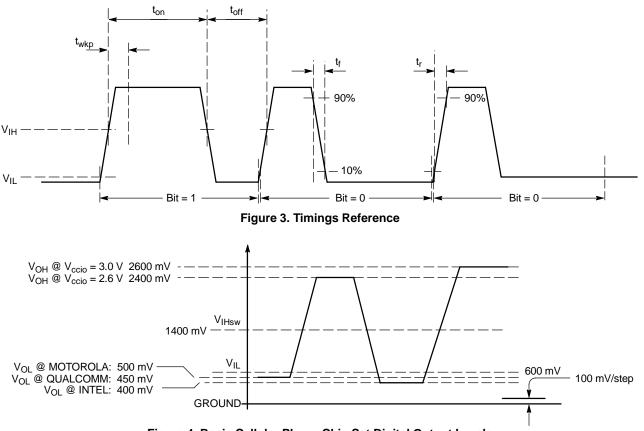

#### **Single Wire Serial Link Protocol**

The proposed S–WIRE uses a pulse count technique already existing in the data exchange systems. The protocol supports broken transmission, assuming the hold time is shorter than the maximum 200  $\mu$ s typical specified in the data sheet. The S–WIRE details are provided in the AND8264 application note.

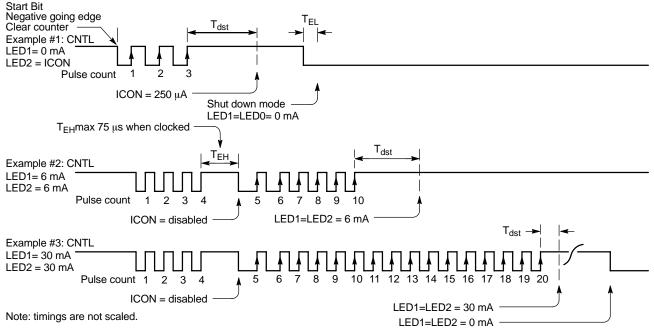

Based on the two examples provided in Figure 8, the CNTL pin supports two digital level:

$CNTL = Low \rightarrow$  the system is shut-off and no current flow in either LED1 or LED2.

$CNTL = High \rightarrow$  the system is active and the two LED are powered according to the selected sequence.

There is no time delay associated with the Low state and the LED are switched Off when the CNTL signal drops to Low. To program a new LED configuration, one shall send the number of pulses on the CNTL pin according to the true table:

The internal counter is reset to zero on the first negative going transient present on the CNTL pin

- The first four positive going pulses are used to control the ICON (LED2):

- 1. Pulse #1  $\rightarrow$  ICON = 100  $\mu$ A

- 2. Pulse #2  $\rightarrow$  ICON = 150  $\mu$ A

- 3. Pulse #3  $\rightarrow$  ICON = 250  $\mu$ A

- 4. Pulse #4  $\rightarrow$  ICON = 450 µA

- The fifth positive pulse will clear the ICON and activate the normal operation of LED1 and LED2

- The pulses from the fifth to the twentieth will increase the LED current according to a pseudo logarithmic scale (see Figure 9).

- Any pulses beyond the twentieth will not make change to the LED current if the delay between the pulses is shorter than 75 μs.

• The system returns to zero if a pulse, delayed by  $200 \ \mu s - T_{dst} -$ , follows the twentieth one and the cycle restart from the beginning.

Once the expected LED current value is reached, the CNTL pin must stay High to store the new data and maintain the LED active.

The contain of the counter is stored into the internal LED registers at the end of the built–in 200  $\mu$ s typical delay: no action will take place during the end of the last positive going pulse and the end of the T<sub>dst</sub> delay. Such a protocol prevent the system for broken transmission.

On the other hand, in order to avoid corrupted data transmission, the High level shall be 75  $\mu$ s maximum during a given data frame. Consequently, the pulse frequency is bounded by a 13 kHz minimum and a 400 kHz maximum.

Figure 8. Basic NCP5612 Programming Sequence

## DIMMING

The built-in Single Wire Serial Link interface provides a simple way to accurately control the output current flowing in the two LED. Provision have been made, at silicon level, to provide a full dimming of the backlight (NORMAL mode of operation), the ICON current being adjustable in four steps when it is activated.

#### Table 1. LED Dimming Configuration

| Pulse Count         | LED activity                                         |

|---------------------|------------------------------------------------------|

| Pulse 1             | LED#2 = 100 µA, LED#1 de-activated                   |

| Pulse 2             | LED#2 = 150 µA, LED#1 de-activated                   |

| Pulse 3             | LED#2 = 250 µA, LED#1 de-activated                   |

| Pulse 4             | LED#2 = 450 µA, LED#1 de-activated                   |

| Pulse 5 to Pulse 20 | ICON de-activated, NORMAL back-<br>light takes place |

The DC/DC converter is switched OFF and the two LED are disconnected when LED-REG=\$00.

When the ICON mode is activated, the DC/DC converter is switched OFF, LED#1 is deactivated from the LED current sense and the programmed bias current (powered from the  $V_{bat}$  source) is forced into LED#2.

| Bit Clock | I-LED(mA) | Bit C | Clock | I-LED(m | A) |  |

|-----------|-----------|-------|-------|---------|----|--|

| 1         | 1         | :     | 9     | 12      |    |  |

| 2         | 2         | 1     | 0     | 14      |    |  |

| 3         | 3         | 1     | 1     | 16      |    |  |

| 4         | 4         | 1     | 2     | 19      |    |  |

| 5         | 5         | 1     | 3     | 22      |    |  |

| 6         | 6         | 1     | 4     | 25      |    |  |

| 7         | 8         | 1     | 5     | 28      |    |  |

| 8         | 10        | 1     | 6     | 31      |    |  |

| 35        |           |       |       |         |    |  |

Figure 10. Typical Efficiency

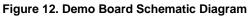

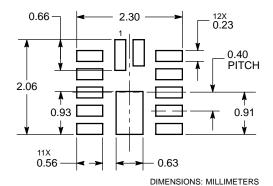

#### PACKAGE DIMENSIONS

LLGA12 **MU SUFFIX** CASE 513AA-01 ISSUE O

NOTES 1. DIMENSIONING AND TOLERANCING PER

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.20 MM FROM TERMINAL. COPLANARITY APPLIES TO THE EXPOSED 2. 3.

| - <b>T</b> . |                   |        | THE EXTOOLD |

|--------------|-------------------|--------|-------------|

|              | PAD AS WELL AS TH | E TERM | NALS.       |

|              |                   | -      |             |

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 0.50        | 0.60 |  |  |

| A1  | 0.00        | 0.05 |  |  |

| b   | 0.15        | 0.25 |  |  |

| D   | 2.00        | BSC  |  |  |

| D2  | 0.80        | 1.00 |  |  |

| Е   | 2.00        | BSC  |  |  |

| E2  | 0.55        | 0.65 |  |  |

| е   | 0.40        | BSC  |  |  |

| К   | 0.25        |      |  |  |

| L   | 0.30        | 0.50 |  |  |

| L1  | 0.40        | 0.60 |  |  |

#### SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.