#### Data Sheet

# CDK1307 Ultra Low Power, 20/40/65/80MSPS, 12/13-bit Analog-to-Digital Converters (ADCs)

#### FEATURES

- 13-bit resolution

- 20/40/65/80MSPS max sampling rate

- Ultra-Low Power Dissipation: 19/33/50/60mW

- 72.4dB SNR at 80MSPS and 8MHz FIN

- Internal reference circuitry

- 1.8V core supply voltage

- 1.7 3.6V I/O supply voltage

- Parallel CMOS output

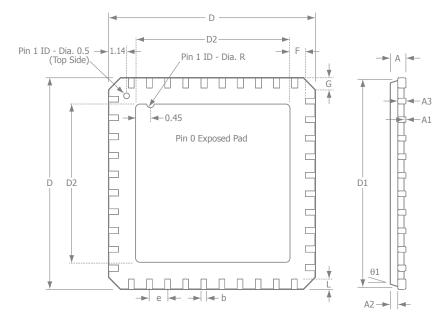

- 40-pin QFN package

- Pin compatible with CDK1308

#### APPLICATIONS

- Medical Imaging

- Portable Test Equipment

- Digital Oscilloscopes

- IF Communication

#### **General Description**

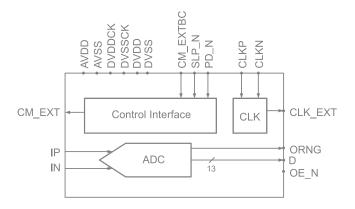

The CDK1307 is a high performance ultra low power Analog-to-Digital Converter (ADC). The ADC employs internal reference circuitry, a CMOS control interface and CMOS output data, and is based on a proprietary structure. Digital error correction is employed to ensure no missing codes in the complete full scale range.

Two idle modes with fast startup times exist. The entire chip can either be put in Standby Mode or Power Down mode. The two modes are optimized to allow the user to select the mode resulting in the smallest possible energy consumption during idle mode and startup.

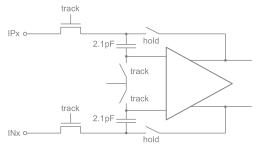

The CDK1307 has a highly linear THA optimized for frequencies up to Nyquist. The differential clock interface is optimized for low jitter clock sources and supports LVDS, LVPECL, sine wave, and CMOS clock inputs.

### Functional Block Diagram

### Ordering Information

| Part Number   | Speed  | Package | Pb-Free | RoHS Compliant | Operating Temperature Range | Packaging Method |

|---------------|--------|---------|---------|----------------|-----------------------------|------------------|

| CDK1307AILP40 | 20MSPS | QFN-40  | Yes     | Yes            | -40°C to +85°C              | Tray             |

| CDK1307BILP40 | 40MSPS | QFN-40  | Yes     | Yes            | -40°C to +85°C              | Tray             |

| CDK1307CILP40 | 65MSPS | QFN-40  | Yes     | Yes            | -40°C to +85°C              | Tray             |

| CDK1307DILP40 | 80MSPS | QFN-40  | Yes     | Yes            | -40°C to +85°C              | Tray             |

Moisture sensitivity level for all parts is MSL-2A.

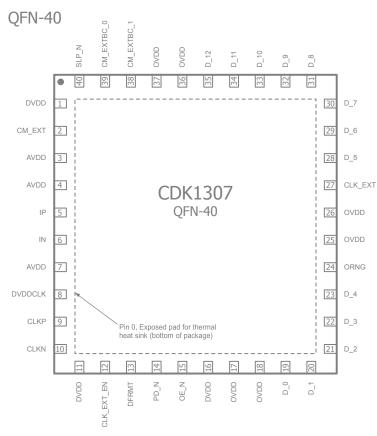

## Pin Configuration

### Pin Assignments

| Pin No.                   | Pin Name   | Description                                                                                                                                                     |

|---------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                         | VSS        | Ground connection for all power domains. Exposed pad                                                                                                            |

| 1, 11, 16                 | DVDD       | Digital and I/O-ring pre driver supply voltage, 1.8V                                                                                                            |

| 2                         | CM_EXT     | Common Mode voltage output                                                                                                                                      |

| 3, 4, 7                   | AVDD       | Analog supply voltage, 1.8V                                                                                                                                     |

| 5, 6                      | IP, IN     | Analog input (non-inverting, inverting)                                                                                                                         |

| 8                         | DVDDCLK    | Clock circuitry supply voltage, 1.8V                                                                                                                            |

| 9                         | CLKP       | Clock input, non-inverting (format: LVDS, LVPECL, CMOS/TTL, Sine Wave)                                                                                          |

| 10                        | CLKN       | Clock input, inverting. For CMOS input on CLKP, Connect CLKN to ground                                                                                          |

| 12                        | CLK_EXT_EN | CLK_EXT signal enabled when low (zero). Tristate when high.                                                                                                     |

| 13                        | DFRMT      | Data format selection. 0: Offset Binary, 1: Two's Complement                                                                                                    |

| 14                        | PD_N       | Full chip Power Down mode when Low. All digital outputs reset to zero. After chip power up always apply Power Down mode before using Active Mode to reset chip. |

| 15                        | OE_N       | Output Enable. Tristate when high                                                                                                                               |

| 17, 18, 25,<br>26, 36, 37 | OVDD       | I/O ring post-driver supply voltage. Voltage range 1.7 to 3.6V                                                                                                  |

| 19                        | D_0        | Output Data (LSB, 13-bit output or 1V <sub>pp</sub> full scale range)                                                                                           |

| 20                        | D_1        | Output Data (LSB, 12-bit output 2V <sub>pp</sub> full scale range)                                                                                              |

| 21                        | D_2        | Output Data                                                                                                                                                     |

| 22                        | D_3        | Output Data                                                                                                                                                     |

# Pin Assignments (Continued)

| Pin No. | Pin Name    | Description                                                                      |

|---------|-------------|----------------------------------------------------------------------------------|

| 23      | D_4         | Output Data                                                                      |

| 24      | ORNG        | Out of Range flag. High when input signal is out of range                        |

| 27      | CLK_EXT     | Output clock signal for data synchronization. CMOS levels                        |

| 28      | D_5         | Output Data                                                                      |

| 29      | D_6         | Output Data                                                                      |

| 30      | D_7         | Output Data                                                                      |

| 31      | D_8         | Output Data                                                                      |

| 32      | D_9         | Output Data                                                                      |

| 33      | D_10        | Output Data                                                                      |

| 34      | D_11        | Output Data (MSB for $1V_{pp}$ full scale range, see Reference Voltages section) |

| 35      | D_12        | Output Data (MSB for 2V <sub>pp</sub> full scale range)                          |

| 38, 39  | CM_EXTBC_1, | Bias control bits for the buffer driving pin CM_EXT                              |

|         | CM_EXTBC_0  | 00: OFF 01: 50μA                                                                 |

|         |             | 10: 500µA 11: 1mA                                                                |

| 40      | SLP_N       | Sleep Mode when low                                                              |

#### Absolute Maximum Ratings

The safety of the device is not guaranteed when it is operated above the "Absolute Maximum Ratings". The device should not be operated at these "absolute" limits. Adhere to the "Recommended Operating Conditions" for proper device function. The information contained in the Electrical Characteristics tables and Typical Performance plots reflect the operating conditions noted on the tables and plots.

| Parameter                           | Min  | Max  | Unit |

|-------------------------------------|------|------|------|

| AVDD                                | -0.3 | +2.3 | V    |

| DVDD                                | -0.3 | +2.3 | V    |

| AVSS, DVSSCK, DVSS, OVSS            | -0.3 | +0.3 | V    |

| OVDD, OVSS                          | -0.3 | +3.9 | V    |

| CLKP, CLKN                          | -0.3 | +3.9 | V    |

| Analog inputs and outpts (IPx, INx) | -0.3 | +2.3 | V    |

| Digital inputs                      | -0.3 | +3.9 | V    |

| Digital outputs                     | -0.3 | +3.9 | V    |

### **Reliability Information**

| Parameter                         | Min | Тур       | Max  | Unit |

|-----------------------------------|-----|-----------|------|------|

| Junction Temperature              |     |           | TBD  | °C   |

| Storage Temperature Range         | -60 |           | +150 | °C   |

| Lead Temperature (Soldering, 10s) |     | J-STD-020 |      |      |

### **ESD** Protection

| Product                | QFN-40 |

|------------------------|--------|

| Human Body Model (HBM) | 2kV    |

#### **Recommended Operating Conditions**

| Parameter                   | Min | Тур | Max | Unit |

|-----------------------------|-----|-----|-----|------|

| Operating Temperature Range | -40 |     | +85 | °C   |

#### **Electrical Characteristics**

(AVDD = 1.8V, DVDD = 1.8V, DVDDCLK = 1.8V, OVDD = 2.5V, 20/40/65/80MSPS clock, 50% clock duty cycle, -1dBFS 8MHz input signal, 13-bit output, unless otherwise noted)

| Symbol           | Parameter                  | Conditions                                                                                                                  | Min                  | Тур                  | Max                  | Units           |

|------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|-----------------|

| DC Accuracy      | /                          |                                                                                                                             |                      |                      |                      |                 |

|                  | No Missing Codes           |                                                                                                                             |                      | Guaranteed           | ł                    |                 |

|                  | Offset Error               | Midscale offset                                                                                                             |                      | 1                    |                      | mV              |

|                  | Gain Error                 | Full scale range deviation from typical                                                                                     | -6                   |                      | 6                    | %FS             |

| DNL              | Differential Non-Linearity | 12-bit level                                                                                                                |                      | ±0.2                 |                      | LSB             |

| INL              | Integral Non-Linearity     | 12-bit level                                                                                                                |                      | ±0.6                 |                      | LSB             |

| V <sub>CMO</sub> | Common Mode Voltage Output |                                                                                                                             |                      | V <sub>AVDD</sub> /2 |                      | V               |

| Analog Inpu      | t                          |                                                                                                                             |                      |                      |                      |                 |

| V <sub>CMI</sub> | Input Common Mode          | Analog input common mode voltage                                                                                            | V <sub>CM</sub> -0.1 |                      | V <sub>CM</sub> +0.2 | V               |

|                  | Full Scale Range, Normal   | Differential input voltage range,                                                                                           |                      | 2.0                  |                      | V <sub>pp</sub> |

| V <sub>FSR</sub> | Full Scale Range, Option   | Differential input voltage range, 1V<br>(see section Reference Voltages)                                                    |                      | 1.0                  |                      | V <sub>pp</sub> |

|                  | Input Capacitance          | Differential input capacitance                                                                                              |                      | 2                    |                      | pF              |

|                  | Bandwidth                  | Input bandwidth, full power                                                                                                 | 500                  |                      |                      | MHz             |

| Power Supp       | ly                         |                                                                                                                             |                      |                      |                      |                 |

| AVDD,<br>DVDD    | Core Supply Voltage        | Supply voltage to all 1.8V domain pins.<br>See Pin Configuration and Description                                            | 1.7                  | 1.8                  | 2.0                  | V               |

| OVDD             | I/O Supply Voltage         | Output driver supply voltage (OVDD).<br>Must be higher than or equal to Core Supply<br>Voltage ( $V_{OVDD} \ge V_{OCVDD}$ ) | 1.7                  | 2.5                  | 3.6                  | V               |

### Electrical Characteristics - CDK1307A

(AVDD = 1.8V, DVDD = 1.8V, DVDDCLK = 1.8V, OVDD = 2.5V, 20MSPS clock, 50% clock duty cycle, -1dBFS 8MHz input signal, 13-bit output, unless otherwise noted)

| Symbol           | Parameter                            | Conditions                                                                                                                                                                 | Min  | Тур                                                                                                                                                                                                                                                                            | Мах | Units |

|------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| Performance      |                                      |                                                                                                                                                                            |      |                                                                                                                                                                                                                                                                                |     |       |

|                  |                                      | $F_{IN} = 2MHz$                                                                                                                                                            |      | 72.5                                                                                                                                                                                                                                                                           |     | dBFS  |

| CNID             |                                      | $F_{IN} = 8MHz$                                                                                                                                                            | 71.5 | 72.2                                                                                                                                                                                                                                                                           |     | dBFS  |

| SNR              | Signal to Noise Ratio                | $F_{IN} \simeq FS/2$                                                                                                                                                       |      | 72.1                                                                                                                                                                                                                                                                           |     | dBFS  |

|                  |                                      | F <sub>IN</sub> = 20MHz                                                                                                                                                    |      | 71.6                                                                                                                                                                                                                                                                           |     | dBFS  |

|                  |                                      | F <sub>IN</sub> = 2MHz                                                                                                                                                     |      | 72.4                                                                                                                                                                                                                                                                           |     | dBFS  |

|                  |                                      | $F_{IN} = 8MHz$                                                                                                                                                            | 71   | 72.0                                                                                                                                                                                                                                                                           |     | dBFS  |

| SINAD            | Signal to Noise and Distortion Ratio | $F_{IN} \simeq FS/2$                                                                                                                                                       |      | 71.7                                                                                                                                                                                                                                                                           |     | dBFS  |

|                  |                                      | F <sub>IN</sub> = 20MHz                                                                                                                                                    |      | 71.3                                                                                                                                                                                                                                                                           |     | dBFS  |

|                  |                                      | F <sub>IN</sub> = 2MHz                                                                                                                                                     |      | 87                                                                                                                                                                                                                                                                             |     | dBc   |

| -                |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | 75   | 85                                                                                                                                                                                                                                                                             |     | dBc   |

| SFDR             | Spurious Free Dynamic Range          | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     |      | 80                                                                                                                                                                                                                                                                             |     | dBc   |

|                  |                                      | F <sub>IN</sub> = 20MHz                                                                                                                                                    |      | 72.5   72.2   72.1   71.6   72.4   72.7   71.7   71.3   87   85   80   87   85   80   -90   -95   -95   -95   -95   -87   -80   11.7   11.6   11.7   11.6   11.7   11.6   11.7   11.6   11.7   11.6   11.7   11.6   11.7   11.6   11.7   11.6   11.7   1.3   1.9.1   9.9   9.2 |     | dBc   |

|                  |                                      | F <sub>IN</sub> = 2MHz                                                                                                                                                     |      | -90                                                                                                                                                                                                                                                                            |     | dBc   |

|                  |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | -85  | -95                                                                                                                                                                                                                                                                            |     | dBc   |

| HD2              | Second order Harmonic Distortion     | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     |      | -95                                                                                                                                                                                                                                                                            |     | dBc   |

|                  |                                      | F <sub>IN</sub> = 20MHz                                                                                                                                                    |      | -95                                                                                                                                                                                                                                                                            |     | dBc   |

|                  | Third order Harmonic Distortion      | $F_{IN} = 2MHz$                                                                                                                                                            |      | -87                                                                                                                                                                                                                                                                            |     | dBc   |

|                  |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | -75  | -85                                                                                                                                                                                                                                                                            |     | dBc   |

| HD3              |                                      | $F_{IN} \simeq FS/2$                                                                                                                                                       |      | -80                                                                                                                                                                                                                                                                            |     | dBc   |

|                  |                                      | $F_{IN} = 20MHz$                                                                                                                                                           |      | -80                                                                                                                                                                                                                                                                            |     | dBc   |

|                  |                                      | $F_{IN} = 2MHz$                                                                                                                                                            |      | bits                                                                                                                                                                                                                                                                           |     |       |

|                  |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | 11.5 | 11.7                                                                                                                                                                                                                                                                           |     | bits  |

| ENOB             | Effective number of Bits             | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     |      | 11.6                                                                                                                                                                                                                                                                           |     | bits  |

|                  |                                      | $F_{IN} = 20MHz$                                                                                                                                                           |      | 11.6                                                                                                                                                                                                                                                                           |     | bits  |

| Power Supply     | /                                    |                                                                                                                                                                            |      | 1                                                                                                                                                                                                                                                                              | 1   | 1     |

| AI <sub>DD</sub> | Analog Supply Current                |                                                                                                                                                                            |      | 7.8                                                                                                                                                                                                                                                                            |     | mA    |

| DI <sub>DD</sub> | Digital Supply Current               | Digital core supply                                                                                                                                                        |      | 1.0                                                                                                                                                                                                                                                                            |     | mA    |

|                  |                                      | 2.5V output driver supply, sine wave input, $F_{\rm IN}=1 \mbox{MHz}, \mbox{CLK}\xspace$ CLK_EXT enabled                                                                   |      | 1.7                                                                                                                                                                                                                                                                            |     | mA    |

| OI <sub>DD</sub> | Output Driver Supply                 | 2.5V output driver supply, sine wave input, $F_{IN}=1 \mbox{MHz}, \mbox{CLK}\xspace$ CLK_EXT disabled                                                                      |      | 1.3                                                                                                                                                                                                                                                                            |     | mA    |

|                  | Analog Power Dissipation             |                                                                                                                                                                            |      | 14.0                                                                                                                                                                                                                                                                           |     | mW    |

|                  | Digital Power Dissipation            | $\begin{array}{l} \text{OVDD} = 2.5\text{V}, \text{5pF load on output bits}, \\ \text{F}_{\text{IN}} = 1\text{MHz}, \text{CLK}\_\text{EXT disabled} \end{array}$           |      | 5.1                                                                                                                                                                                                                                                                            |     | mW    |

|                  | Total Power Dissipation              | $\begin{array}{l} \mbox{OVDD} = 2.5 \mbox{V}, \mbox{5pF} \mbox{ load on output bits}, \\ \mbox{F}_{IN} = 1 \mbox{MHz}, \mbox{CLK} \mbox{EXT} \mbox{ disabled} \end{array}$ |      | 19.1                                                                                                                                                                                                                                                                           |     | mW    |

|                  | Power Down Dissipation               |                                                                                                                                                                            |      | 9.9                                                                                                                                                                                                                                                                            |     | μW    |

|                  | Sleep Mode                           | Power Dissipation, Sleep mode                                                                                                                                              |      | 9.2                                                                                                                                                                                                                                                                            |     | mW    |

| Clock Inputs     |                                      |                                                                                                                                                                            |      |                                                                                                                                                                                                                                                                                |     |       |

|                  | Max. Conversion Rate                 |                                                                                                                                                                            | 20   |                                                                                                                                                                                                                                                                                |     | MSPS  |

|                  | Min. Conversion Rate                 |                                                                                                                                                                            |      | 1                                                                                                                                                                                                                                                                              | 15  | MSPS  |

### Electrical Characteristics - CDK1307B

(AVDD = 1.8V, DVDD = 1.8V, DVDDCLK = 1.8V, OVDD = 2.5V, 40MSPS clock, 50% clock duty cycle, -1dBFS 8MHz input signal, 13-bit output, unless otherwise noted)

| Symbol           | Parameter                            | Conditions                                                                                                                                                                 | Min  | Тур                                                                     | Мах  | Units |

|------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------|------|-------|

| Performance      |                                      |                                                                                                                                                                            |      |                                                                         |      |       |

|                  |                                      | $F_{IN} = 2MHz$                                                                                                                                                            |      | 72.5                                                                    |      | dBFS  |

|                  |                                      | $F_{IN} = 8MHz$                                                                                                                                                            | 71.9 | 72.7                                                                    |      | dBFS  |

| SNR              | Signal to Noise Ratio                | $F_{IN} \simeq FS/2$                                                                                                                                                       |      | 72                                                                      |      | dBFS  |

|                  |                                      | F <sub>IN</sub> = 30MHz                                                                                                                                                    |      | 70.8                                                                    |      | dBFS  |

|                  |                                      | F <sub>IN</sub> = 2MHz                                                                                                                                                     |      | 71.7                                                                    |      | dBFS  |

|                  |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | 71   | 72.1                                                                    |      | dBFS  |

| SINAD            | Signal to Noise and Distortion Ratio | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     |      | 71.5                                                                    |      | dBFS  |

|                  |                                      | F <sub>IN</sub> = 30MHz                                                                                                                                                    |      | 71.2                                                                    |      | dBFS  |

|                  |                                      | F <sub>IN</sub> = 2MHz                                                                                                                                                     |      | 81                                                                      |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | 75   | 81                                                                      |      | dBc   |

| SFDR             | Spurious Free Dynamic Range          | $F_{IN} \simeq FS/2$                                                                                                                                                       |      | 80                                                                      |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 30MHz                                                                                                                                                    |      | 80                                                                      |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 2MHz                                                                                                                                                     |      | -90                                                                     |      | dBc   |

|                  |                                      | $F_{IN} = 8MHz$                                                                                                                                                            | -85  | -95                                                                     |      | dBc   |

| HD2              | Second order Harmonic Distortion     | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     |      | -95                                                                     |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 30MHz                                                                                                                                                    |      | 72.7   72   70.8   71.7   72.1   71.5   71.2   81   80   80   -90   -95 |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 2MHz                                                                                                                                                     |      | -81                                                                     |      | dBc   |

|                  | Third order Harmonic Distortion      | F <sub>IN</sub> = 8MHz                                                                                                                                                     |      | -81                                                                     |      | dBc   |

| HD3              |                                      | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     | -75  | -80                                                                     |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 30MHz                                                                                                                                                    |      | -80                                                                     |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 2MHz                                                                                                                                                     |      |                                                                         | bits |       |

|                  |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | 11.5 | 11.7                                                                    |      | bits  |

| ENOB             | Effective number of Bits             | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     |      | 11.6                                                                    |      | bits  |

|                  |                                      | F <sub>IN</sub> = 30MHz                                                                                                                                                    |      | 11.4                                                                    |      | bits  |

| Power Supply     | /                                    |                                                                                                                                                                            |      |                                                                         |      |       |

| AI <sub>DD</sub> | Analog Supply Current                |                                                                                                                                                                            |      | 13.4                                                                    |      | mA    |

| DI <sub>DD</sub> | Digital Supply Current               | Digital core supply                                                                                                                                                        |      | 1.7                                                                     |      | mA    |

|                  |                                      | 2.5V output driver supply, sine wave input, $F_{IN} = 1$ MHz, CLK_EXT enabled                                                                                              |      | 3.3                                                                     |      | mA    |

| OI <sub>DD</sub> | Output Driver Supply                 | 2.5V output driver supply, sine wave input, $F_{\rm IN}$ = 1MHz, CLK_EXT disabled                                                                                          |      | 2.4                                                                     |      | mA    |

|                  | Analog Power Dissipation             |                                                                                                                                                                            |      | 24.1                                                                    |      | mW    |

|                  | Digital Power Dissipation            | $\begin{array}{l} \mbox{OVDD} = 2.5 \mbox{V}, \mbox{5pF} \mbox{ load on output bits}, \\ \mbox{F}_{IN} = 1 \mbox{MHz}, \mbox{CLK} \mbox{EXT} \mbox{ disabled} \end{array}$ |      | 9.1                                                                     |      | mW    |

|                  | Total Power Dissipation              | $\begin{array}{l} \mbox{OVDD} = 2.5 \mbox{V}, \mbox{5pF} \mbox{ load on output bits}, \\ \mbox{F}_{IN} = 1 \mbox{MHz}, \mbox{CLK} \mbox{EXT} \mbox{ disabled} \end{array}$ |      | 33.2                                                                    |      | mW    |

|                  | Power Down Dissipation               |                                                                                                                                                                            |      | 9.7                                                                     |      | μW    |

|                  | Sleep Mode                           | Power Dissipation, Sleep mode                                                                                                                                              |      | 14.2                                                                    |      | mW    |

| Clock Inputs     |                                      |                                                                                                                                                                            |      |                                                                         |      |       |

|                  | Max. Conversion Rate                 |                                                                                                                                                                            | 40   |                                                                         |      | MSPS  |

|                  | Min. Conversion Rate                 |                                                                                                                                                                            |      |                                                                         | 20   | MSPS  |

### Electrical Characteristics - CDK1307C

(AVDD = 1.8V, DVDD = 1.8V, DVDDCLK = 1.8V, OVDD = 2.5V, 65MSPS clock, 50% clock duty cycle, -1dBFS 8MHz input signal, 13-bit output, unless otherwise noted)

| Symbol           | Parameter                            | Conditions                                                                                                                                                                 | Min  | Тур                                                                                                                                                                                                                                                                                                                                                         | Max  | Units |

|------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| Performance      |                                      |                                                                                                                                                                            |      |                                                                                                                                                                                                                                                                                                                                                             |      |       |

|                  |                                      | $F_{IN} = 8MHz$                                                                                                                                                            | 71.6 | 72.6                                                                                                                                                                                                                                                                                                                                                        |      | dBFS  |

|                  |                                      | $F_{IN} = 20MHz$                                                                                                                                                           |      | 71.8                                                                                                                                                                                                                                                                                                                                                        |      | dBFS  |

| SNR              | Signal to Noise Ratio                | $F_{IN} \simeq FS/2$                                                                                                                                                       |      | 71.5                                                                                                                                                                                                                                                                                                                                                        |      | dBFS  |

|                  |                                      | F <sub>IN</sub> = 40MHz                                                                                                                                                    |      | 70.4                                                                                                                                                                                                                                                                                                                                                        |      | dBFS  |

|                  |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | 70.5 | 71.7                                                                                                                                                                                                                                                                                                                                                        |      | dBFS  |

|                  |                                      | F <sub>IN</sub> = 20MHz                                                                                                                                                    |      | 71.7                                                                                                                                                                                                                                                                                                                                                        |      | dBFS  |

| SINAD            | Signal to Noise and Distortion Ratio | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     |      | 71.1                                                                                                                                                                                                                                                                                                                                                        |      | dBFS  |

|                  |                                      | F <sub>IN</sub> = 40MHz                                                                                                                                                    |      | 70                                                                                                                                                                                                                                                                                                                                                          |      | dBFS  |

|                  |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | 75   | 81                                                                                                                                                                                                                                                                                                                                                          |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 20MHz                                                                                                                                                    |      | 84                                                                                                                                                                                                                                                                                                                                                          |      | dBc   |

| SFDR             | Spurious Free Dynamic Range          | $F_{IN} \simeq FS/2$                                                                                                                                                       |      | 79                                                                                                                                                                                                                                                                                                                                                          |      | dBc   |

|                  |                                      | $F_{IN} = 40 MHz$                                                                                                                                                          |      | 72.6   71.8   71.7   70.4   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   71.7   70   81   84   799   -95   -84   -79   -79   11.6   11.5   11.3   20.4   2.3   5.1   3.5   3.6.7   12.9   49.6   9.3   20.4 |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | -85  | -95                                                                                                                                                                                                                                                                                                                                                         |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 20MHz                                                                                                                                                    |      | -95                                                                                                                                                                                                                                                                                                                                                         |      | dBc   |

| HD2              | Second order Harmonic Distortion     | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     |      | -95                                                                                                                                                                                                                                                                                                                                                         |      | dBc   |

|                  |                                      | $F_{IN} = 40MHz$                                                                                                                                                           |      | -95                                                                                                                                                                                                                                                                                                                                                         |      | dBc   |

|                  | Third order Harmonic Distortion      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | -75  | -81                                                                                                                                                                                                                                                                                                                                                         |      | dBc   |

|                  |                                      | $F_{IN} = 20MHz$                                                                                                                                                           |      | -84                                                                                                                                                                                                                                                                                                                                                         |      | dBc   |

| HD3              |                                      | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     |      | -79                                                                                                                                                                                                                                                                                                                                                         |      | dBc   |

|                  |                                      | $F_{IN} = 40MHz$                                                                                                                                                           |      | -79                                                                                                                                                                                                                                                                                                                                                         |      | dBc   |

|                  |                                      | F <sub>IN</sub> = 8MHz                                                                                                                                                     | 11.4 | 11.6                                                                                                                                                                                                                                                                                                                                                        | bits |       |

|                  |                                      | $F_{IN} = 20MHz$                                                                                                                                                           |      | 11.6                                                                                                                                                                                                                                                                                                                                                        |      | bits  |

| ENOB             | Effective number of Bits             | F <sub>IN</sub> ≃ FS/2                                                                                                                                                     |      | 11.5                                                                                                                                                                                                                                                                                                                                                        |      | bits  |

|                  |                                      | $F_{IN} = 40 MHz$                                                                                                                                                          |      | 11.3                                                                                                                                                                                                                                                                                                                                                        |      | bits  |

| Power Supply     | /                                    | LIY                                                                                                                                                                        | 1    |                                                                                                                                                                                                                                                                                                                                                             |      | 1     |

| AI <sub>DD</sub> | Analog Supply Current                |                                                                                                                                                                            |      | 20.4                                                                                                                                                                                                                                                                                                                                                        |      | mA    |

| DI <sub>DD</sub> | Digital Supply Current               | Digital core supply                                                                                                                                                        |      | 2.3                                                                                                                                                                                                                                                                                                                                                         |      | mA    |

|                  |                                      | 2.5V output driver supply, sine wave input, $F_{IN} = 1$ MHz, CLK_EXT enabled                                                                                              |      | 5.1                                                                                                                                                                                                                                                                                                                                                         |      | mA    |

| OI <sub>DD</sub> | Output Driver Supply                 | 2.5V output driver supply, sine wave input, $F_{IN} = 1$ MHz, CLK_EXT disabled                                                                                             |      | 3.5                                                                                                                                                                                                                                                                                                                                                         |      | mA    |

|                  | Analog Power Dissipation             |                                                                                                                                                                            |      | 36.7                                                                                                                                                                                                                                                                                                                                                        |      | mW    |

|                  | Digital Power Dissipation            | $\begin{array}{l} \mbox{OVDD} = 2.5 \mbox{V}, \mbox{5pF} \mbox{ load on output bits}, \\ \mbox{F}_{IN} = 1 \mbox{MHz}, \mbox{CLK} \mbox{EXT} \mbox{ disabled} \end{array}$ |      | 12.9                                                                                                                                                                                                                                                                                                                                                        |      | mW    |

|                  | Total Power Dissipation              | $\begin{array}{l} \mbox{OVDD} = 2.5 \mbox{V}, \mbox{5pF} \mbox{ load on output bits}, \\ \mbox{F}_{IN} = 1 \mbox{MHz}, \mbox{CLK}_{EXT} \mbox{ disabled} \end{array}$      |      | 49.6                                                                                                                                                                                                                                                                                                                                                        |      | mW    |

|                  | Power Down Dissipation               |                                                                                                                                                                            |      | 9.3                                                                                                                                                                                                                                                                                                                                                         |      | μW    |

|                  | Sleep Mode                           | Power Dissipation, Sleep mode                                                                                                                                              |      | 20.4                                                                                                                                                                                                                                                                                                                                                        |      | mW    |

| Clock Inputs     |                                      |                                                                                                                                                                            |      |                                                                                                                                                                                                                                                                                                                                                             |      |       |

|                  | Max. Conversion Rate                 |                                                                                                                                                                            | 65   |                                                                                                                                                                                                                                                                                                                                                             |      | MSPS  |

|                  | Min. Conversion Rate                 |                                                                                                                                                                            |      |                                                                                                                                                                                                                                                                                                                                                             | 40   | MSPS  |

### Electrical Characteristics - CDK1307D

(AVDD = 1.8V, DVDD = 1.8V, DVDDCLK = 1.8V, OVDD = 2.5V, 80MSPS clock, 50% clock duty cycle, -1dBFS 8MHz input signal, 13-bit output, unless otherwise noted)

| Symbol           | Parameter                            | Conditions                                                                                                                                                                     | Min  | Тур                                 | Max  | Units |

|------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------|------|-------|

| Performance      |                                      | · · · · · · · · · · · · · · · · · · ·                                                                                                                                          |      |                                     |      |       |

|                  |                                      | $F_{IN} = 8MHz$                                                                                                                                                                | 70.4 | 72                                  |      | dBFS  |

|                  |                                      | $F_{IN} = 20MHz$                                                                                                                                                               |      | 71.7                                |      | dBFS  |

| SNR              | Signal to Noise Ratio                | $F_{IN} = 30 MHz$                                                                                                                                                              |      | 71.2                                |      | dBFS  |

|                  |                                      | $F_{IN} \simeq FS/2$                                                                                                                                                           |      | 70.7                                |      | dBFS  |

|                  |                                      | $F_{IN} = 8MHz$                                                                                                                                                                | 69.5 | 70.5                                |      | dBFS  |

| 01110            |                                      | $F_{IN} = 20MHz$                                                                                                                                                               |      | 70.5                                |      | dBFS  |

| SINAD            | Signal to Noise and Distortion Ratio | $F_{IN} = 30 MHz$                                                                                                                                                              |      | 70.5                                |      | dBFS  |

|                  |                                      | $F_{IN} \simeq FS/2$                                                                                                                                                           |      | 70.3                                |      | dBFS  |

|                  |                                      | $F_{IN} = 8MHz$                                                                                                                                                                | 74   | 77                                  |      | dBc   |

|                  |                                      | $F_{IN} = 20 MHz$                                                                                                                                                              |      | 78                                  |      | dBc   |

| SFDR             | Spurious Free Dynamic Range          | $F_{IN} = 30 MHz$                                                                                                                                                              |      | 78                                  |      | dBc   |

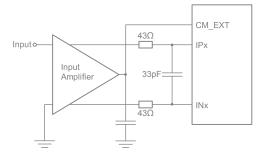

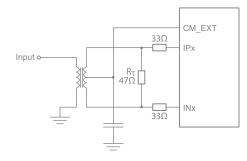

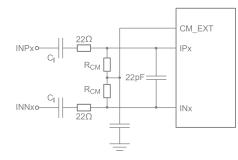

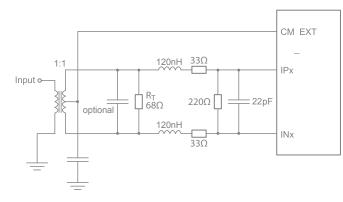

|                  |                                      | $F_{IN} \simeq FS/2$                                                                                                                                                           |      | 78                                  |      | dBc   |