#### **General Description**

The MAX8677A is an integrated 1-cell Li+ charger and Smart Power Selector™ with dual (DC and USB) power inputs. It can operate with either separate inputs for USB and AC adapter power\*, or from a single input that accepts both. All power switches for charging and switching the load between battery and external power are included on-chip. No external MOSFETs are required.

The MAX8677A features a Smart Power Selector to make the best use of limited USB or adapter power. The battery charge current and input current limit are independently set up to 1.5A and 2A, respectively. Input power not used by the system charges the battery. USB input current can be set to 100mA or 500mA. Automatic input selection switches the system load from battery to external power.

Other features include overvoltage protection (OVP), charge status and fault outputs, power-OK monitors, charge timer, and battery thermistor monitor. Additionally, on-chip thermal limiting reduces the battery charge rate to prevent overheating. The MAX8677A is available in a 4mm x 4mm, 24-pin TQFN-EP package.

### **Applications**

PDAs, Palmtops, and Wireless Handhelds Smart Cell Phones Portable Media/MP3 Players **GPS** Navigation Digital Cameras

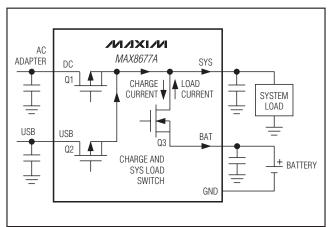

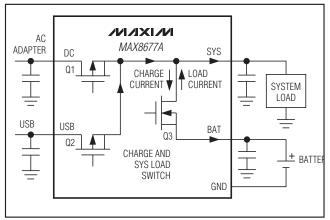

### Typical Operating Circuit

#### **Features**

- **♦ Complete Charger and Smart Power Selector**

- **♦ No External MOSFETs Required**

- **♦** Common or Separate USB and Adapter Inputs

- ♦ System Operates with Discharged or No Battery

- ♦ Automatic Adapter/USB/Battery Switchover

- ♦ Load Peaks Over Adapter Rating Are Supported by Battery

- ♦ Input Overvoltage Protection to 16V

- ♦ 40mΩ System-to-Battery Switch

- **♦ Thermal Regulation Prevents Overheating**

- ♦ CHG, DOK, UOK, and FLT Indicators

- ♦ 5.3V (typ) SYS Regulation Voltage

### **Ordering Information**

| PART |              | TEMP RANGE     | PIN-<br>PACKAGE           | PKG<br>CODE |  |

|------|--------------|----------------|---------------------------|-------------|--|

|      | MAX8677AETG+ | -40°C to +85°C | 24 TQFN-EP<br>(4mm x 4mm) | T2444-4     |  |

+Denotes a lead-free package.

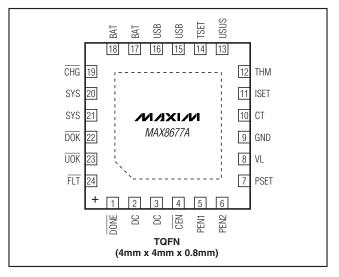

### Pin Configuration

Smart Power Selector is a trademark of Maxim Integrated Products, Inc.

\*Protected by U.S. Patent #6,507,172.

#### **ABSOLUTE MAXIMUM RATINGS**

| DC, PEN1 to GND  USB to GND  VL to GND  BAT, SYS, CEN, USUS, PEN2, TSET to GND  THM, PSET, ISET, CT to GND  DONE, CHG, DOK, UOK, FLT to GND  EP (exposed paddle) to GND  DC Continuous Current (total in 2 pins) | 0.3V to +9V<br>0.3V to +4V<br>0.3V to +6V<br>0.3V to VL + 0.3V<br>0.3V to +6V<br>0.3V to +0.3V |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| SYS Continuous Current (total in 2 pins)                                                                                                                                                                         |                                                                                                |

|                                                                                                                                                                                                                  |                                                                                                |

| USB Continuous Current (total in 2 pins)<br>BAT Continuous Current (total in 2 pins) | 2.4 ARMS       |

|--------------------------------------------------------------------------------------|----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}$ C                                 | C)             |

| (derate 27.8 mW/°C above +70°C)                                                      | 2222mW         |

| Operating Temperature Range                                                          | 40°C to +85°C  |

| Junction Temperature Range                                                           | 40°C to +125°C |

| Storage Temperature Range                                                            | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                                                    | +300°C         |

|                                                                                      |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DC} = 5V, THM = \overline{CEN} = USUS = GND, V_{BAT} = 4V, V_{PEN1} = V_{PEN2} = 5V, USB, TSET, \overline{DONE}, \overline{CHG}, \overline{DOK}, \overline{VOK}, \overline{FLT}$  are unconnected,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                 | со                                                                                           | NDITIONS                                                                                 | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|-------|

| DC-TO-SYS PREREGULATOR                    |                                                                                              |                                                                                          |      |      |      |       |

| DC Operating Range                        |                                                                                              |                                                                                          | 4.1  |      | 6.6  | V     |

| DC Standoff Voltage                       | V <sub>BAT</sub> = V <sub>SYS</sub> = 0V                                                     |                                                                                          |      |      | 14   | V     |

| DC Undervoltage Threshold                 | When V <sub>DOK</sub> goes low, V <sub>DC</sub>                                              | When $V_{\overline{DOK}}$ goes low, $V_{\overline{DC}}$ rising, 500mV typical hysteresis |      |      |      | V     |

| DC Overvoltage Threshold                  | When $V_{\overline{DOK}}$ goes high, $V_{\overline{D}}$                                      | C rising, 100mV typical hysteresis                                                       | 6.8  | 6.9  | 7.0  | V     |

| DC Supply Current                         | $I_{SYS} = I_{BAT} = 0mA, V_{\overline{CEN}}$                                                | = OV                                                                                     |      | 1    | 2    | m Λ   |

| DC Supply Current                         | $I_{SYS} = I_{BAT} = 0mA, V_{\overline{CEN}}$                                                | = 5V                                                                                     |      | 0.8  | 1.5  | mA    |

| DC Shutdown Current                       | $V_{DC} = V_{\overline{CEN}} = USUS = 5V$                                                    | $V$ , $V_{PEN1} = 0V$                                                                    |      | 195  | 333  | μΑ    |

| DC-to-SYS On-Resistance                   | $I_{SYS} = 400 \text{mA}, V_{\overline{CEN}} = 5 \text{V}$                                   |                                                                                          |      | 0.2  | 0.35 | Ω     |

| DC-to-BAT Dropout Voltage                 | When SYS regulation and 150mV hysteresis                                                     | When SYS regulation and charging stops, V <sub>DC</sub> falling, 150mV hysteresis        |      | 50   | 90   | mV    |

|                                           | V <sub>DC</sub> = 6V, V <sub>SYS</sub> = 5V,<br>T <sub>A</sub> = +25°C                       | R <sub>PSET</sub> = 1.5kΩ                                                                | 1800 | 2000 | 2200 | mA    |

|                                           |                                                                                              | $R_{PSET} = 3k\Omega$                                                                    | 900  | 1000 | 1100 |       |

| DC Current Limit                          |                                                                                              | $R_{PSET} = 6.3k\Omega$                                                                  | 450  | 475  | 500  |       |

| (See Table 2 for Input Source<br>Control) |                                                                                              | V <sub>PEN1</sub> = 0V, V <sub>PEN2</sub> = 5V<br>(500mA USB mode)                       | 450  | 475  | 500  |       |

|                                           |                                                                                              | V <sub>PEN1</sub> = 0V, V <sub>PEN2</sub> = 0V<br>(100mA USB mode)                       | 80   | 95   | 100  |       |

| PSET Resistance Range                     |                                                                                              | •                                                                                        | 1.5  |      | 6.3  | kΩ    |

| SYS Regulation Voltage                    | $V_{DC} = 6V$ , $I_{SYS} = 1$ mA to 1                                                        | I.75A, V <del>CEN</del> = 5V                                                             | 5.1  | 5.3  | 5.5  | V     |

| Lowert Commont Coft Chart Times           | Connecting DC when no USB present                                                            |                                                                                          |      | 1.5  |      | ms    |

| Input Current Soft-Start Time             | Connecting DC with USB                                                                       | Connecting DC with USB present                                                           |      |      |      | μs    |

| Thermal-Limit Temperature                 | mal-Limit Temperature Die temperature at which charging and input current limits are reduced |                                                                                          |      | 100  |      | °C    |

| Thermal-Limit Gain                        | ISYS reduction/die tempera                                                                   | ature (above +100°C)                                                                     |      | 5    |      | %/°C  |

| VL Voltage                                | I <sub>VL</sub> = 0mA to 10mA                                                                |                                                                                          | 3.0  | 3.3  | 3.6  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DC} = 5V, THM = \overline{CEN} = USUS = GND, V_{BAT} = 4V, V_{PEN1} = V_{PEN2} = 5V, USB, TSET, \overline{DONE}, \overline{CHG}, \overline{DOK}, \overline{UOK}, \overline{FLT} \ are unconnected, T_A = -40°C \ to +85°C, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 1)$

| PARAMETER                                               | COI                                                             | MIN                                                                                                | TYP   | MAX  | UNITS |          |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------|------|-------|----------|--|--|

| USB-TO-SYS PREREGULATOR                                 |                                                                 |                                                                                                    |       |      |       |          |  |  |

| USB Operating Range                                     |                                                                 |                                                                                                    | 4.1   |      | 6.6   | V        |  |  |

| USB Standoff Voltage                                    | V <sub>BAT</sub> = V <sub>SYS</sub> = 0V                        |                                                                                                    |       |      | 8     | V        |  |  |

| USB Undervoltage Threshold                              | When VUOK goes low, Vus                                         | B rising, 500mV hysteresis                                                                         | 3.95  | 4.0  | 4.05  | V        |  |  |

| USB Overvoltage Threshold                               | When VUOK goes high, VU                                         | When V <sub>UOK</sub> goes high, V <sub>USB</sub> rising, 100mV hysteresis                         |       |      |       | V        |  |  |

| LICE Consists Comment                                   | I <sub>SYS</sub> = I <sub>BAT</sub> = 0mA, V <sub>CEN</sub> =   | = 0V, V <sub>PEN2</sub> = low                                                                      |       | 1    | 2     | ^        |  |  |

| USB Supply Current                                      | I <sub>SYS</sub> = I <sub>BAT</sub> = 0mA, V <sub>CEN</sub> =   | = 5V, V <sub>PEN2</sub> = low                                                                      |       | 0.9  | 1.5   | mA       |  |  |

| USB Shutdown Current                                    | DC = unconnected, V <sub>USB</sub>                              | = V <del>CEN</del> = V <sub>USUS</sub> = 5V                                                        |       | 190  | 333   | μΑ       |  |  |

| USB-to-SYS On-Resistance                                | DC = unconnected, V <sub>USB</sub>                              | = V <del>CEN</del> = 5V, I <sub>SYS</sub> = 400mA                                                  |       | 0.2  | 0.31  | Ω        |  |  |

| USB-to-BAT Drop-Out Voltage                             | When SYS regulation and a 250mV hysteresis                      | charging stops, V <sub>USB</sub> falling,                                                          | 10    | 50   | 90    | mV       |  |  |

| USB Current Limit                                       | DC = unconnected,                                               | V <sub>PEN1</sub> = 0V,<br>V <sub>PEN2</sub> = 5V                                                  | 450   | 475  | 500   | A        |  |  |

| (See Table 2 for Input Source<br>Control)               | $V_{USB} = 5V,$ $T_A = +25^{\circ}C$                            | VPEN1 = 0V,<br>VPEN2 = 0V                                                                          | 80    | 95   | 100   | mA mA    |  |  |

| SYS Regulation Voltage                                  |                                                                 | DC = unconnected, V <sub>USB</sub> = 6V;<br>I <sub>SYS</sub> = 1mA to 400mA, V <sub>CEN</sub> = 5V |       |      |       | V        |  |  |

| Input Limiter Soft-Start Time                           | Input current ramp time                                         |                                                                                                    |       | 50   |       | μs       |  |  |

| Thermal-Limit Start Temperature                         |                                                                 |                                                                                                    | İ     | 100  |       | °C       |  |  |

| Thermal-Limit Gain                                      | ISYS reduction/die tempera                                      | ature (above +100°C)                                                                               |       | 5    |       | %/°C     |  |  |

| VL Voltage                                              | DC = unconnected, V <sub>USB</sub>                              | = 5V; I <sub>VL</sub> = 0 to 10mA                                                                  | 3.0   | 3.3  | 3.6   | V        |  |  |

| CHARGER                                                 |                                                                 |                                                                                                    |       |      |       |          |  |  |

| BAT-to-SYS On-Resistance                                | V <sub>DC</sub> = 0V, V <sub>BAT</sub> = 4.2V, I <sub>S</sub> V | /S = 1A                                                                                            |       | 0.04 | 0.08  | Ω        |  |  |

| BAT-to-SYS Reverse Regulation Voltage                   | VPEN1 = VPEN2 = 0V, ISYS                                        | = 200mA                                                                                            | 40    | 68   | 90    | mV       |  |  |

| DATE LE ME                                              |                                                                 | $T_A = +25^{\circ}C$                                                                               | 4.179 | 4.2  | 4.221 | <b>T</b> |  |  |

| BAT Regulation Voltage                                  | $I_{BAT} = 0mA$                                                 | $T_A = 0$ °C to +85°C                                                                              | 4.158 | 4.2  | 4.242 | V        |  |  |

| BAT Recharge Threshold                                  | Change in V <sub>BAT</sub> from DON                             | E to fast-charge                                                                                   | -135  | -95  | -45   | mV       |  |  |

| BAT Charge-Current Set Range                            | $R_{ISET} = 10k\Omega$ to $2k\Omega$ (Note                      | : 2)                                                                                               | 0.3   |      | 1.5   | А        |  |  |

|                                                         |                                                                 | $R_{ISET} = 2.4k\Omega$                                                                            | 1125  | 1250 | 1375  |          |  |  |

|                                                         |                                                                 | $R_{ISET} = 4k\Omega$                                                                              | 675   | 750  | 825   |          |  |  |

|                                                         |                                                                 | $R_{ISET} = 10k\Omega$                                                                             | 270   | 300  | 330   | 1        |  |  |

| BAT Charge-Current Accuracy,<br>Charger Loop in Control | Vsys = 5.5V,                                                    | $R_{ISET} = 4k\Omega$ , $V_{BAT} = 2.5V$ (prequal mode)                                            | 50    | 75.0 | 100   | mA       |  |  |

| Charger Loop in Control                                 | $T_A = 0$ °C to +85°C                                           | $R_{ISET} = 6.2k\Omega$ , $V_{BAT} = 2.5V$ (prequal mode)                                          | 23    | 48   | 73    |          |  |  |

|                                                         |                                                                 | $R_{ISET}$ = 10kΩ, $V_{BAT}$ = 2.5V (prequal mode)                                                 |       | 30   |       |          |  |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DC} = 5V, THM = \overline{CEN} = USUS = GND, V_{BAT} = 4V, V_{PEN1} = V_{PEN2} = 5V, USB, TSET, \overline{DONE}, \overline{CHG}, \overline{DOK}, \overline{UOK}, \overline{FLT}$  are unconnected,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                        |                                                                              | CONDITION                                                                              | IS                     | MIN                  | TYP   | MAX                  | UNITS               |  |

|--------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------|----------------------|-------|----------------------|---------------------|--|

| ISET Voltage                                     | RISET = $4k\Omega$ , $I_{BAT}$ = $(V_{ISET} = 1.5V)$ at full                 |                                                                                        | nt)                    | 0.9                  | 1.0   | 1.1                  | V                   |  |

| Charger Soft-Start Time                          | Charge-current ran                                                           | np time                                                                                |                        |                      | 1.5   |                      | ms                  |  |

| BAT Prequal Threshold                            | V <sub>BAT</sub> rising, 180m\                                               | V <sub>BAT</sub> rising, 180mV hysteresis                                              |                        |                      |       | 3.1                  | V                   |  |

| DATE I O                                         |                                                                              | No DC or U                                                                             | SB power connected     |                      | 3     | 6                    | μΑ                  |  |

| BAT Leakage Current                              | $V_{BAT} = 4.2V$                                                             | DC or USB                                                                              | connected, VCEN = 5V   |                      | 3     | 6                    | μΑ                  |  |

|                                                  |                                                                              | V <sub>TSET</sub> = 0                                                                  |                        |                      | 5     |                      |                     |  |

| DONE Threshold as a<br>Percentage of Fast-Charge | IBAT decreasing                                                              | V <sub>TSET</sub> = ope                                                                | en                     |                      | 10    |                      | %                   |  |

| rercentage of rast-onarge                        |                                                                              | V <sub>TSET</sub> = V <sub>L</sub>                                                     |                        |                      | 15    |                      | /0                  |  |

| Maximum Prequal Time                             | From V <sub>CEN</sub> falling t<br>V <sub>BAT</sub> = 2.5V, C <sub>T</sub> = |                                                                                        | al charge,             |                      | 30    |                      | Min                 |  |

| Maximum Fast-Charge Time                         | From VCEN falling t                                                          | From $V_{\overline{CEN}}$ falling to $V_{\overline{FLT}}$ falling, $C_T = 0.068 \mu F$ |                        |                      |       |                      | Min                 |  |

| Timer Accuracy                                   | $C_T = 0.068 \mu F$                                                          |                                                                                        | •                      | -20                  |       | +20                  | %                   |  |

| Timer Extend Threshold                           | Percentage of fast-<br>clock operates at h                                   | •                                                                                      | below which timer      |                      | 50    |                      | %                   |  |

| Timer Suspend Threshold                          | Percentage of fast-<br>clock pauses                                          | Percentage of fast-charge current below which timer                                    |                        |                      |       |                      | %                   |  |

| THM                                              | ·                                                                            |                                                                                        |                        |                      |       |                      | II.                 |  |

| THM Threshold, Cold                              | When charging is s                                                           | suspended, 2%                                                                          | hysteresis             | 72                   | 74    | 76                   | % of V <sub>L</sub> |  |

| THM Threshold, Hot                               | When charging is s                                                           | suspended, 2%                                                                          | hysteresis             | 26                   | 28    | 30                   | % of V <sub>L</sub> |  |

| THM Threshold, Disabled                          | When THM function                                                            | n is disabled                                                                          |                        |                      | 3     |                      | % of V <sub>L</sub> |  |

| TUNAL                                            | THM = GND or V <sub>L</sub> ; T <sub>A</sub> = +25°C                         |                                                                                        |                        | -0.1                 | 0.001 | +0.2                 |                     |  |

| THM Input Leakage                                | THM = GND or $V_L$ ; $T_A = +85^{\circ}C$                                    |                                                                                        |                        |                      | 0.01  |                      | μA                  |  |

| LOGIC I/O: CHG, FLT, DONE, D                     | OOK, UOK, PEN1, PE                                                           | N2, CEN, TSE                                                                           | T, USUS                |                      |       |                      | -                   |  |

|                                                  | High level                                                                   |                                                                                        |                        | 1.3                  |       |                      |                     |  |

| Logic Input Thresholds                           | Low level                                                                    |                                                                                        |                        |                      |       | 0.4                  | V                   |  |

|                                                  | Hysteresis                                                                   |                                                                                        |                        |                      | 50    |                      | mV                  |  |

|                                                  | High level                                                                   |                                                                                        |                        | V <sub>L</sub> - 0.3 |       |                      |                     |  |

| TSET Input Threshold                             | Midlevel                                                                     | Midlevel                                                                               |                        |                      |       | V <sub>L</sub> - 1.2 | V                   |  |

|                                                  | Low level                                                                    | Low level                                                                              |                        |                      |       | 0.3                  |                     |  |

| TCFT Input Dios Correct                          | TSET = GND                                                                   |                                                                                        |                        | -20                  | -6    |                      |                     |  |

| TSET Input-Bias Current                          | TSET = V <sub>L</sub>                                                        |                                                                                        |                        |                      | 6     | 20                   | μΑ                  |  |

| Logio Input Logicoso Currost                     | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                       | .,                                                                                     | T <sub>A</sub> = +25°C |                      | 0.001 | 1                    | , . Λ               |  |

| Logic Input-Leakage Current                      | $V_{INPUT} = 0V \text{ to } 5.5$                                             | $PUT = 0V \text{ to } 5.5V$ $T_A = +85^{\circ}C$                                       |                        |                      | 0.01  |                      | μA                  |  |

| Logic Output Voltage, Low                        | Sinking 1mA                                                                  |                                                                                        |                        |                      | 25    | 100                  | mV                  |  |

| Logic Output-Leakage Current,                    | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                       |                                                                                        | T <sub>A</sub> = +25°C |                      | 0.001 | 1                    |                     |  |

| High                                             | i V∩IT = 5.5V                                                                |                                                                                        | T <sub>A</sub> = +85°C |                      | 0.01  |                      | μΑ                  |  |

**Note 1:** Limits are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design.

Note 2: Guaranteed by design.

\_\_ /N/XI/N

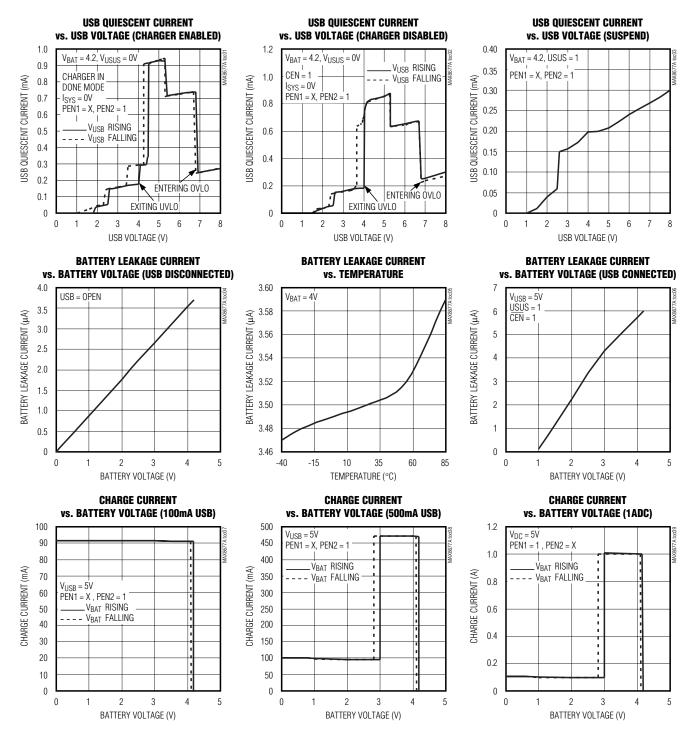

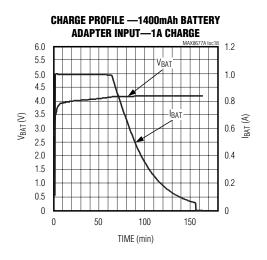

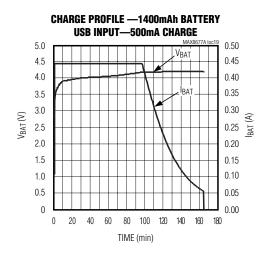

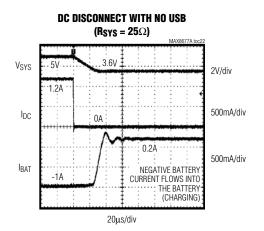

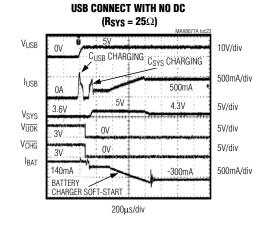

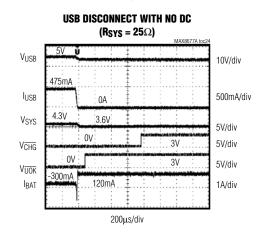

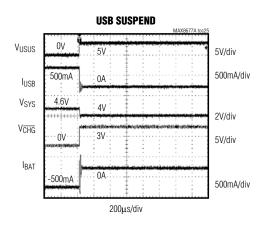

**Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

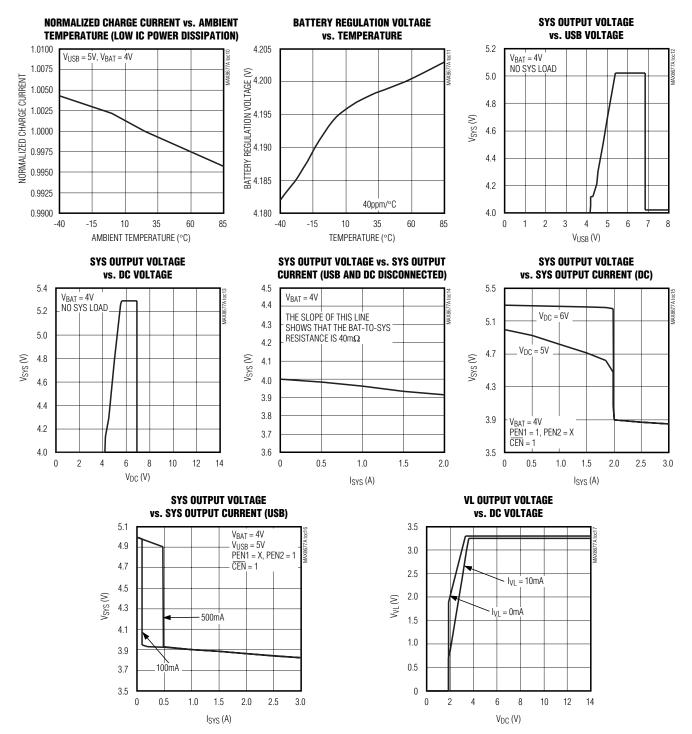

Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

**Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### **Pin Description**

| PIN  | NAME | FUNCTION                                                                                                                                                                                                                                             |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | DONE | Charge Done Output. Active-low, open-drain output pulls low when the charger enters the DONE state. No charging current flows when DONE is low. See Figure 5.                                                                                        |

| 2, 3 | DC   | DC Power Input. DC is capable of delivering up to 2A to SYS. DC supports both AC adapter and USB inputs. The DC current limit is set with PEN1, PEN2, USUS, and R <sub>PSET</sub> . See Table 2. Both DC pins must be connected together externally. |

| 4    | CEN  | Charger Enable Input. Connect CEN to GND to enable battery charging when a valid source is connected at DC or USB. Connect to VL or drive high with a logic signal to disable battery charging.                                                      |

| 5    | PEN1 | DC Input Limit Control. If PEN1 is high, the DC input current limit is 3000/R <sub>PSET</sub> . If PEN1 is low, the DC limit is set by PEN2 and USUS. See Table 2.                                                                                   |

### \_Pin Description (continued)

| PIN     | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 6       | PEN2 | USB High/Low Control. PEN2 sets the DC or USB current limit to 100mA (PEN2 low) or 500mA (PEN2 high). PEN2 controls both DC and USB current limits when PEN1 is low. See Table 2.                                                                                                                                                                                        |  |  |  |  |  |  |

| 7       | PSET | DC Input Current-Limit Set. Connect a resistor to ground to program the DC current limit to 3000/RPSET.                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 8       | VL   | Logic LDO Output. VL is the output of an LDO that powers the MAX8667A internal circuitry. VL also provides 3.3V at up to 10mA to power external circuitry. Connect a 0.1µF capacitor from VL to GND.                                                                                                                                                                     |  |  |  |  |  |  |

| 9 GND   |      | Ground                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 10 CT   |      | Charge Timer Program Pin. A capacitor from CT to GND sets the fast-charge (tFSTCHG) and prequal (tPREQUAL) fault timers. Connect to GND to disable the timer.                                                                                                                                                                                                            |  |  |  |  |  |  |

| 11 ISET |      | Charge Current Set Input. A resistor (R <sub>ISET</sub> ) from ISET to GND programs the maximum charge current up to 1.5A. The prequal charge current is 10% of the set maximum charge current.                                                                                                                                                                          |  |  |  |  |  |  |

| 12 THM  |      | Thermistor Input. Connect a negative temperature coefficient (NTC) thermistor that has good thermal contact with the battery from THM to GND. Connect a resistor equal to the thermistor +25°C resistance from THM to VL. Charging is suspended when the thermistor is outside the hot and cold limits. Connect THM to GND to disable the thermistor temperature sensor. |  |  |  |  |  |  |

| 13 USUS |      | USB Suspend Input. With PEN1 low, driving USUS high turns off both the USB and DC inputs. With PEN1 high, driving USUS high turns off only the USB input. See Table 2.                                                                                                                                                                                                   |  |  |  |  |  |  |

| 14      | TSET | Termination Current Set Pin. Connect to GND, leave open, or connect to VL for a 5%, 10%, or 15% (of ICHGMAX termination current (ITERM) threshold.                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 15, 16  | USB  | USB Power Input. USB is capable of delivering up to 0.5A to SYS. The USB current limit is set with PEN2 and USUS. See Table 2. Both USB pins must be connected together externally.                                                                                                                                                                                      |  |  |  |  |  |  |

| 17, 18  | BAT  | Battery Connection. Connect to a single-cell Li+ battery. The battery charges from SYS when a valid source is present at DC or USB. BAT powers SYS when neither DC nor USB power is present, or when the SYS load exceeds the input current limit. Both BAT pins must be connected together externally.                                                                  |  |  |  |  |  |  |

| 19      | CHG  | Charger Status Output. Active-low, open-drain output pulls low when the battery is in fast-charge or prequal. Otherwise, $\overline{\text{CHG}}$ is high impedance.                                                                                                                                                                                                      |  |  |  |  |  |  |

|         |      | System Supply Output. SYS is connected to BAT through an internal $40m\Omega$ system load switch when DC or USB is invalid, or when the SYS load is greater than the input current limit.                                                                                                                                                                                |  |  |  |  |  |  |

| 20, 21  | SYS  | When a valid voltage is present at DC or USB, SYS is limited to 5.3V. When the system load (I <sub>SYS</sub> ) exceeds the DC or USB current limit, SYS is regulated to 68mV below BAT, and both the USB input and the battery service SYS.                                                                                                                              |  |  |  |  |  |  |

|         |      | Bypass SYS to GND with a 10µF X5R or X7R ceramic capacitor. Both SYS pins must be connected together externally.                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 22      | DOK  | DC Power-OK Output. Active-low, open-drain output pulls low when a valid input is detected at DC.                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 23      | ŪOK  | USB Power-OK Output. Active-low, open-drain output pulls low when a valid input is detected at USB.                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 24      | FLT  | Fault Output. Active-low, open-drain output pulls low when the battery timer expires before prequal or fast-charge complete.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| _       | EP   | Exposed Paddle. Connect the exposed paddle to GND. Connecting the exposed paddle does not remove the requirement for proper ground connections to the appropriate pins.                                                                                                                                                                                                  |  |  |  |  |  |  |

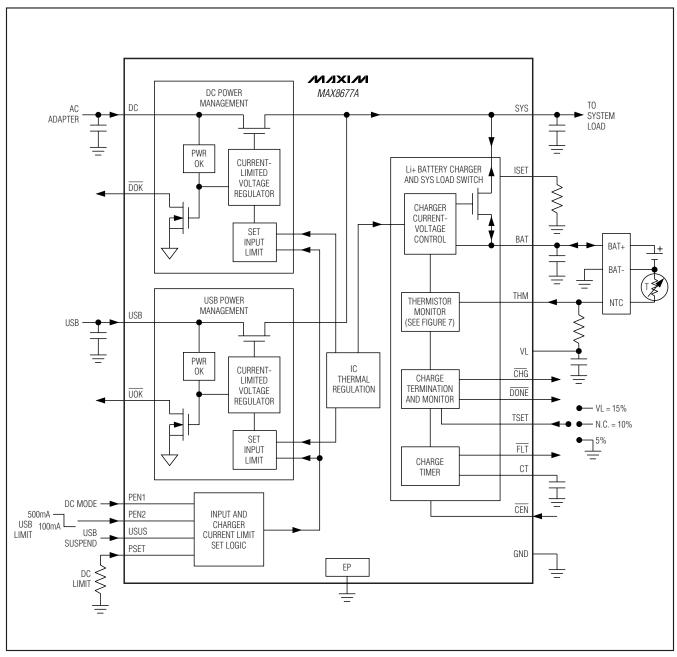

Figure 1. Block Diagram

#### Circuit Description

The MAX8677A contains an Li+ battery charger, as well as power MOSFETs and control circuitry to manage power flow in portable devices. See Figure 1. The

charger has two power inputs, DC and USB. These can be separately connected to an AC adapter output and a USB port, or the DC input can be a single power input that connects to either an adapter or USB. Logic inputs, PEN1 and PEN2, select the correct current limits

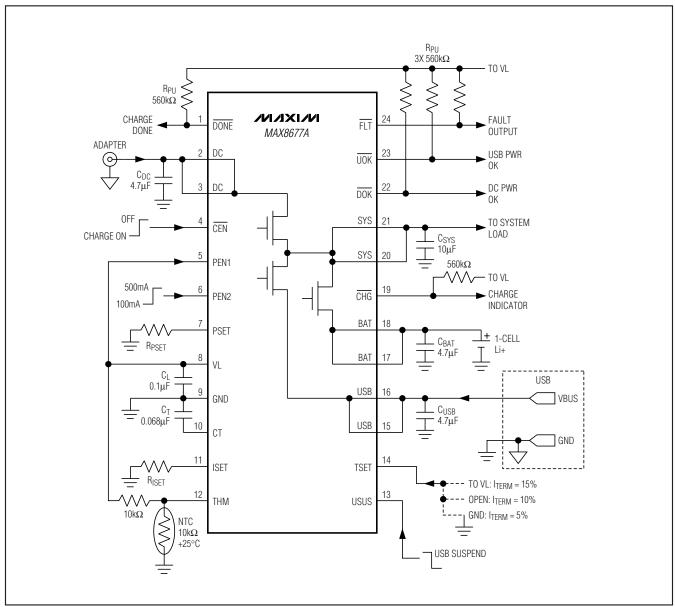

Figure 2. Typical Application Circuit Using Separate DC and USB Connectors

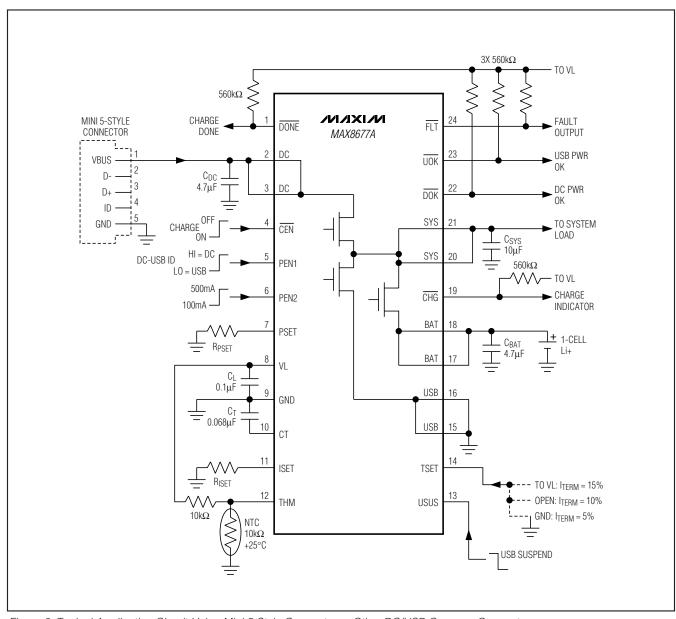

for two-input or single-input operation. Figure 2 is the typical application circuit using separate DC and USB connectors. Figure 3 is the typical application circuit using a Mini 5-style connector or other DC/USB common connector.

In addition to charging the battery, the MAX8677A also supplies power to the system through the SYS output.

The charging current is also provided from SYS so that the set input current limit controls the total SYS current, which is the sum of the system load current and the battery-charging current. SYS is powered from either the DC input pin or the USB input pin. If both the DC and USB are connected, DC takes precedence.

Figure 3. Typical Application Circuit Using Mini 5-Style Connector or Other DC/USB Common Connector

In some instances, there may not be enough adapter current or USB current to supply peak system loads. The MAX8677A Smart Power Selector circuitry offers flexible power distribution from an AC adapter or USB source to the battery and system load. The battery is charged with any available power not used by the system load. If a system load peak exceeds the input

current limit, supplemental current is taken from the battery. Thermal limiting prevents overheating by reducing power drawn from the input source. In the past, it might have been necessary to reduce system functionality to limit current drain when a USB source is connected. However, in the MAX8677A, this is no longer the case. When the DC or USB source hits its limit, the battery supplies supplemental current to maintain the load.

Table 1. External Components List for Figures 2 and 3

| COMPONENT (FIGURES 2, 3)                      |                                          | PART                                                                   |  |  |  |

|-----------------------------------------------|------------------------------------------|------------------------------------------------------------------------|--|--|--|

| CIN                                           | Input filter capacitor                   | 4.7µF ceramic capacitor                                                |  |  |  |

| CL VL filter capacitor                        |                                          | 0.1µF ceramic capacitor                                                |  |  |  |

| C <sub>SYS</sub> SYS output bypass capacitors |                                          | 10μF ceramic capacitor                                                 |  |  |  |

| C <sub>BAT</sub> Battery bypass capacitor     |                                          | 4.7µF ceramic capacitor                                                |  |  |  |

| CT                                            | Charger timing capacitor                 | 0.068µF low TC ceramic capacitor                                       |  |  |  |

| R <sub>PU</sub> (x 4)                         | Logic output pullup resistors            | 560k $Ω$                                                               |  |  |  |

| THM                                           | Negative TC thermistor                   | Phillips NTC thermistor, P/N 2322-640-63103, 10k $\Omega$ ±5% at +25°C |  |  |  |

| RT THM pullup resistor                        |                                          | 10kΩ ±1%                                                               |  |  |  |

| RPSET                                         | Input current-limit programming resistor | 1.5k $\Omega$ ±1% for 2A limit                                         |  |  |  |

| RISET                                         | Fast-charge current programming resistor | 3kΩ ±1% for 1A charging                                                |  |  |  |

The MAX8677A features OVP. Part of this protection is a 5.3V voltage limiter at SYS. If the DC or USB input exceeds 5.3V, SYS still limits at 5.3V. It is expected that the SYS limiter will not need to operate, and will be in dropout in most cases. A typical 5VAC adapter operates below the limit level, so both DC and SYS would be at 5V in that case.

The MAX8677A has numerous other charging and power-management features, which are detailed in the following sections.

#### **Smart Power Selector**

The MAX8677A Smart Power Selector seamlessly distributes power between the external inputs, the battery, and the system load (Figure 4). The basic functions performed are:

With both an external power supply (USB or adapter) and battery connected:

Figure 4. Smart Power Selector Block Diagram

When the system load requirements are less than the input current limit, the battery is charged with residual power from the input.

When the system load requirements exceed the input current limit, the battery supplies supplemental current to the load.

- When the battery is connected and there is no external power input, the system is powered from the battery.

- When an external power input is connected and there is no battery, the system is powered from the external power input.

A thermal-limiting circuit reduces the battery charge rate and external power-source current to prevent the MAX8677A from overheating.

#### **System Load Switch**

An internal 40m $\Omega$  MOSFET connects SYS to BAT (Q3, Figure 4) when no voltage source is available at DC or USB. When an external source is detected at DC or USB, this switch is opened and SYS is powered from the valid input source through the input limiter.

The SYS-BAT switch also holds up SYS when the system load exceeds the input current limit. If that should happen, the SYS-BAT switch turns on so that the battery supplies additional SYS load current. If the system load continuously exceeds the input current limit, the battery does not charge, even though external power is connected. This is not expected to occur in most cases, since high loads usually occur only in short peaks. During these peaks, battery energy is used, but at all other times the battery charges.

#### **Input Limiter**

The input voltage limiter is essentially an LDO regulator designed to run in dropout. While in dropout, the regulator dissipates a small I²R loss through the  $0.2\Omega$  MOSFET (Q1, Figure 4) between DC and SYS. With an AC adapter or USB source connected, the input limiter distributes power from the external power source to the system load and battery charger. In addition to the input limiter's primary function of passing power to the system and charger loads at SYS, it performs several additional functions to optimize use of available power:

- Input Voltage Limiting. If an input voltage is above the overvoltage threshold (6.9V typ), the MAX8677A enters overvoltage lockout (OVLO). OVLO protects the MAX8677A and downstream circuitry from high-voltage stress up to 14V at DC and 8V at USB. In OVLO, VL remains on, the input switch that sees overvoltage (Q1, Q3, Figure 4) opens, and the appropriate power-monitor output (DOK, UOK) is high impedance, and CHG is high impedance.

- If both DC and USB see overvoltage, both input switches (Q1 and Q2, Figure 4) open and the charger turns off. The BAT-SYS switch (Q3, Figure 4) closes, allowing the battery to power SYS.

- An input is also invalid if it is less than BAT, or less than the DC undervoltage threshold of 3.5V (falling). With an invalid input voltage, SYS connects to BAT through a  $40m\Omega$  switch (Q3, Figure 4).

- Input Overcurrent Protection. The current at DC and USB is limited to prevent input overload. This current limit can be selected to match the capabilities of the source, whether it is a 100mA or 500mA USB source, or an AC adapter. When the load exceeds the input current limit, SYS drops to 68mV below BAT and the battery supplies supplemental load current.

- Thermal Limiting. The MAX8677A reduces input limiter current by 5%/°C when its die temperature exceeds +100°C. The system load (SYS) has priority over the charger current, so input current is first reduced by lowering charge current. If the junction temperature still reaches +120°C in spite of charge-current reduction, no input (DC or USB) current is drawn, the battery supplies the entire system load, and SYS is regulated at 68mV below BAT. Note that this on-chip thermal-limiting circuitry is not related to and operates independently from the thermistor input.

- Adaptive Battery Charging. While the system is powered from DC, the charger draws power from SYS to charge the battery. If the charger load plus system load exceeds the input current limit, an adaptive charger control loop reduces charge current to prevent the SYS voltage from collapsing. Maintaining a higher SYS voltage improves efficiency and reduces power dissipation in the input limiter.

The total current through the switch (Q1 or Q2 in Figure 4) is the sum of the load current at SYS and the battery charging current. The limiter clamps at 5.3V, so input voltages greater than 5.3V can increase power dissipation in the limiter. The limiter power loss is (VDC - 5.3) x I, but not less than I<sup>2</sup> x 0.2 $\Omega$ . Also note that the MAX8677A turns off any input that exceeds 6.9V (nominal).

#### DC and USB Connections and Current-Limit Options

#### Input Current Limit

The input and charger current limits are set as shown in Table 2. It is often preferable to change the input current limit as the input power source is changed. The MAX8677A facilitates this by allowing different input current limits for DC and USB as shown in Table 2.

**Table 2. Input Limiter Control Logic**

| POWER SOURCE                           | DOK | ŪОК | PEN1 | PEN2 | usus | DC INPUT<br>CURRENT<br>LIMIT | USB INPUT<br>CURRENT<br>LIMIT        | MAXIMUM<br>CHARGE<br>CURRENT* |       |

|----------------------------------------|-----|-----|------|------|------|------------------------------|--------------------------------------|-------------------------------|-------|

| AC adapter at DC input                 | L   | Χ   | Н    | Χ    | Χ    | 3000/R <sub>PSET</sub>       |                                      | 3000/RISET                    |       |

|                                        | L   | Χ   | L    | L    | Ш    | 100mA                        | USB input off; DC input has priority | ·                             | 100mA |

| USB power at DC input                  | L   | Χ   | L    | Η    | Ш    | 500mA                        |                                      | 500mA                         |       |

|                                        | L   | Χ   | L    | Χ    | Н    | USB suspend                  |                                      | 0                             |       |

| LICD                                   | Н   | L   | Χ    | L    | Ш    |                              | 100mA                                | 3000/R <sub>ISET</sub>        |       |

| USB power at USB input; DC unconnected | Н   | L   | Χ    | Н    | L    | No DC input                  | 500mA                                | 3000/HISET                    |       |

| DO UNCONNECTED                         | Н   | Ĺ   | Х    | Χ    | Н    | INO DO INPUL                 | USB suspend                          | 0                             |       |

| DC and USB unconnected                 | Н   | Н   | Х    | Х    | Х    |                              | No USB input                         | 0                             |       |

<sup>\*</sup>Charge current cannot exceed the input current limit. Charge may be less than the maximum charge current if the total SYS load exceeds the input current limit.

\_\_ /VI/XI/VI

When the input current limit is reached, the first action taken by the MAX8677A is to reduce the battery charge current. This allows the regulator to stay in dropout, or at 5.3V, during heavy loads, thus reducing power dissipation. If, after the charge current is reduced to 0mA, the load at SYS still exceeds the input current limit, SYS begins to fall. When the SYS voltage drops to BAT, the SYS-BAT switch turns on, using battery power to support the system load during the load peak.

The MAX8677A features flexible input connections (at the DC and USB input pins) and current-limit settings (set by PEN1, PEN2, PSET, and ISET) to accommodate nearly any input power configuration. However, it is expected that most systems use one of two external power schemes: separate connections for USB and an AC adapter, or a single connector that accepts either USB or AC adapter output. Input and charger current limit are controlled by PEN1, PEN2, RPSET, and RISET, as shown in Table 2.

#### Separate Adapter and USB Connectors

When the AC adapter and USB have separate connectors, the adapter output connects to DC and the USB source connects to USB. PEN1 is permanently tied high (to DC or VL). The DC current limit is set by RPSET, while the USB current limit is set by PEN2 and USUS.

#### Single Common Connector for USB or Adapter

When a single connector is used for both AC adapter and USB sources, the DC input is used for both input sources. When an AC adapter is connected at DC, PEN1 should be pulled high to select the current limit set by RPSET. When a USB source is connected, PEN1 should be low to select 500mA, 100mA, or USB suspend (further selected by PEN2 and USUS). PEN1 can be pulled up by the AC adapter power to implement hardware adapter/USB selection.

#### **USB Suspend**

Driving USUS high when PEN1 is low turns off charging, as well as the SYS output and reduces input current to 190µA to accommodate USB suspend mode.

#### **Power Monitor Outputs (UOK, DOK)**

DOK is an open-drain output that pulls low when the DC input has valid power. UOK is an open-drain output that pulls low when the USB input sees valid power. A valid input for DC or USB is between 4.1V and 6.6V. If a single power-OK output is preferred, DOK and UOK can be wire-ORed together. The combined output then pulls low if either USB or DC sees a valid input.

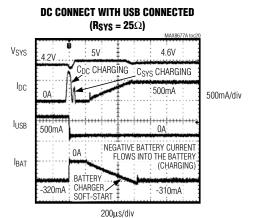

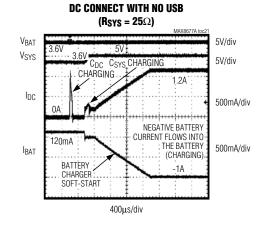

#### Soft-Start

To prevent input transients that can cause instability in the USB or AC adapter power source, the rate of change of input current and charge current is limited. When a valid DC or USB input is connected, the input current limit is ramped from zero to the set current-limit value (as shown in Table 2). If DC is connected with no USB power present, input current ramps in 1.5ms. If DC is connected with USB already present, input current ramps in 50µs. When USB is connected with no DC present, input current ramps also ramps in 50µs. If USB is connected with DC already present, the USB input is ignored.

If an adapter is plugged into DC while USB is already powered, the input current limit reramps from zero back up to the DC current limit so that the AC adapter does not see a load step. During this transition, if the input current limit falls below the SYS load current, the battery supplies the additional current needed to support the load. Additionally, capacitance can be added to SYS to support the load during input power transitions.

When the charger is turned on, charge current ramps from zero to the ISET current value in typically 1.5ms. Charge current also ramps when transitioning to fast-charge from prequal and when changing the USB charge current from 100mA to 500mA with PEN2. There is no dl/dt limiting, however, if ISET is changed suddenly using a switch at RISET.

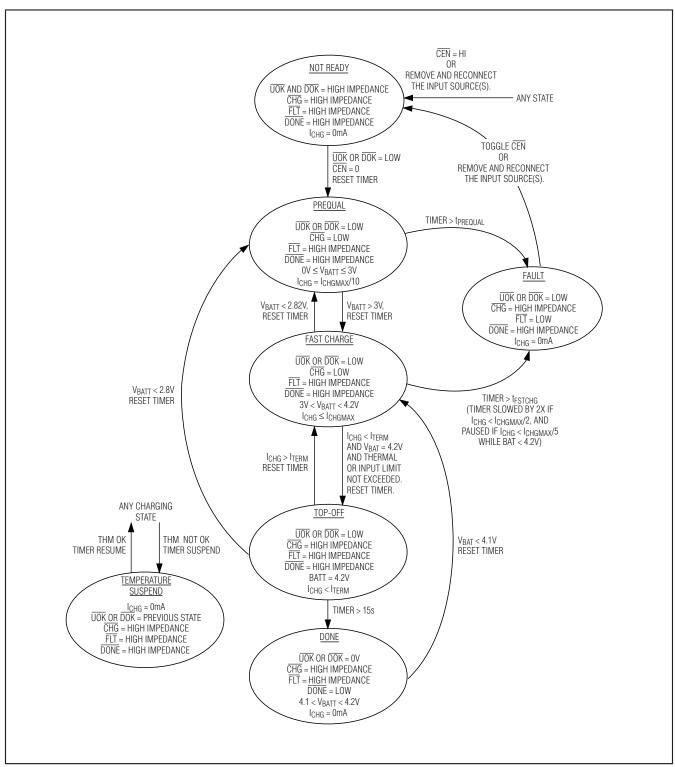

#### Battery Charger

The battery charger state diagram is illustrated in Figure 5. With a valid DC or USB input, the battery charger initiates a charge cycle when the charger is enabled. It first detects the battery voltage. If the battery voltage is less than the BAT pregual threshold (3.0V), the charger enters prequal mode in which the battery charges at 10% of the maximum fast-charge current. This reduced charge rate ensures that the battery is not damaged by the fast-charge current while deeply discharged. Once the battery voltage rises to 3.0V, the charger transitions to fast-charge mode and applies the maximum charge current. As charging continues, the battery voltage rises until it approaches the battery regulation voltage (4.2V) where charge current starts tapering down. When charge current decreases to 5%, 10%, or 15% (as set by TSET) of the fast-charge current, the charger enters a brief 15s top-off, and then charging stops. If the battery voltage subsequently drops below the 4.1V recharge threshold, charging restarts and the timers reset.

Figure 5. MAX8677A Charger State Flowchart

16

#### Charge Enable (CEN)

When  $\overline{\text{CEN}}$  is low, the charger is on. When  $\overline{\text{CEN}}$  is high, the charger turns off.  $\overline{\text{CEN}}$  does not affect the SYS output. In many systems, there is no need for the system controller (typically a microprocessor) to disable the charger, because the MAX8677A Smart Power Selector circuitry independently manages charging and adapter/battery power hand-off. In these situations,  $\overline{\text{CEN}}$  can be connected to ground.

#### **Setting the Charge Current**

ISET adjusts charge current to match the capacity of the battery. A resistor from ISET to ground sets the maximum fast-charge current:

Determine the I<sub>CHGMAX</sub> value by considering the characteristics of the battery. It is not necessary to limit the charge current based on the capabilities of the expected AC adapter/USB charging input, the system load, or thermal limitations of the PCB. The MAX8677A automatically adjusts the charging algorithm to accommodate these factors.

#### **Monitoring the Charge Current**

In addition to setting the charge current, ISET can also be used to monitor the actual current charging the battery. The ISET output voltage is:

VISET = ICHG x 1.5V/ICHGMAX = ICHG x RISET/2000

where I<sub>CHGMAX</sub> is the set fast-charge current and I<sub>CHG</sub> is the actual battery charge current. A 1.5V output indicates the battery is being charged at the maximum set fast-charge current; 0V indicates no charging. This voltage is also used by the charger control circuitry to set and monitor the battery current. Avoid adding more than 10pF capacitance directly to the ISET pin. If filtering of the charge-current monitor is necessary, add a resistor of  $100 \text{k}\Omega$  or more between ISET and the filter capacitor to preserve charger stability. See Figure 6.

Note that the actual charge current can be less than the set fast-charge current when the charger enters voltage mode or when charge current is reduced by the input current limiter or thermal limiter. This prevents the charger from overloading the input source or overheating the system.

#### **Charge Termination**

When the charge current falls to the termination threshold AND the charger is in voltage mode, charging is complete. Charging continues for a brief 15s top-off period and then enters the DONE state in which charging stops. The termination current threshold (ITERM) is set by TSET to a percentage of the fast-charge current:

Connect TSET to GND for ITERM = ICHGMAX x 5%

Figure 6. Monitoring the Charge Current with the ISET Voltage

Leave TSET open for ITERM = ICHGMAX x 10% Connect TSET to VL for ITERM = ICHGMAX x 15%

When the charger enters DONE 15s later, the DONE output goes low. Note that if charge current falls to ITERM as a result of the input or thermal limiter, the charger does not enter DONE. For the charger to enter DONE, the charge current must be less than ITERM, the charger must be in voltage mode, and the input or thermal limiter must not be reducing the charge current.

### Charge Status Outputs

#### Charge Output (CHG)

CHG is an open-drain, active-low output that is low during charging. CHG is low when the battery charger is in its prequalification and fast-charge states. When charge current falls to the charge termination threshold and the charger is in voltage mode, CHG goes high impedance. CHG goes high impedance if the thermistor causes the charger to enter temperature suspend mode.

When the MAX8677A is used with a microprocessor ( $\mu$ P), connect a pullup resistor between  $\overline{CHG}$  and the logic I/O voltage to indicate charge status to the  $\mu$ P. Alternatively,  $\overline{CHG}$  can sink up to 20mA for an LED indicator.

#### Charge Done Output (DONE)

DONE is an open-drain, active-low output that goes low when charging is complete. The charger enters its DONE state 15s after charge current falls to the

charge-termination threshold and the charger is in voltage mode. The charger exits the DONE state, and fast-charge resumes, if the battery voltage subsequently drops 100mV, or if input power or  $\overline{\text{CEN}}$  is cycled.

When the MAX8677A is used in <u>conjunction</u> with a  $\mu$ P, connect a pullup resistor between <u>DONE</u> and the logic I/O <u>voltage</u> to indicate charge status to the  $\mu$ P. Alternatively, <u>DONE</u> can sink up to 20mA for an LED indicator.

#### Fault Output (FLT) and Charge Timer

FLT is an open-drain, active-low output that goes low during a battery fault. The fault state occurs when either the prequal or fast-charge timer expires. The prequal and fast-charge fault timers are set by CCT:

$$t_{PREQUAL} = 30min \times \frac{C_{CT}}{0.068\mu F}$$

$$t_{FSTCHG} = 300min \times \frac{C_{CT}}{0.068\mu F}$$

While in fast-charge mode, a large system load or device self-heating can cause the MAX8677A to reduce charge current. Under these circumstances, the fast-charge timer adjusts to ensure that adequate charge time is still allowed. Consequently, the fast-charge timer is slowed by 2x if charge current is reduced below 50% of the programmed fast-charge level. If charge current is reduced to below 20% of the

programmed level, the fast-charge timer is paused. The fast-charge timer is not adjusted if the charger is in voltage mode where charge current reduces due to current tapering under normal charging.

To exit a fault state, toggle  $\overline{\text{CEN}}$  or remove and reconnect the input source(s). Note also that thermistor out-of-range or on-chip thermal-limit conditions are not considered faults.

When the MAX8677A is used in conjunction with a  $\mu P$ , connect a pullup resistor between  $\overline{FLT}$  and the logic I/O voltage to indicate fault status to the  $\mu P$ . Alternatively,  $\overline{FLT}$  can sink up to 20mA for an LED indicator.

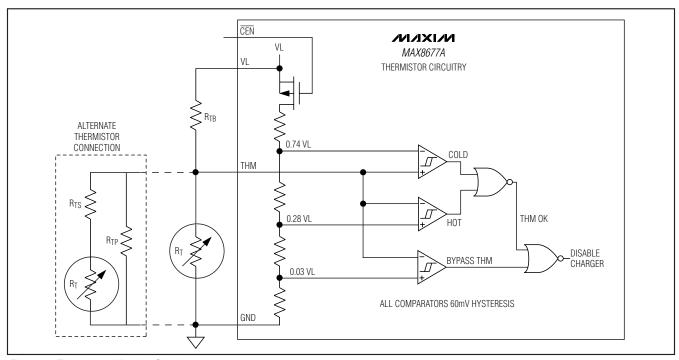

#### Thermistor Input (THM)

The THM input connects to an external negative temperature coefficient (NTC) thermistor to monitor battery or system temperature. Charging is suspended when the thermistor temperature is out of range. The charge timers are suspended and hold their state but no fault is indicated. When the thermistor comes back into range, charging resumes and the charge timer continues from where it left off. Connecting THM to GND disables the thermistor monitoring function. Table 3 lists fault temperatures for different thermistors.

Since the thermistor monitoring circuit employs an external bias resistor from THM to VL (R<sub>TB</sub>, Figure 7), the thermistor is not limited only to  $10k\Omega$  (at +25°C).

Figure 7. Thermistor Monitor Circuitry

Any resistance thermistor can be used as long as the value of R<sub>TB</sub> is equivalent to the thermistor's +25°C resistance. For example, with a 10k $\Omega$  at +25°C thermistor, use 10k $\Omega$  at R<sub>TB</sub>, and with a 100k $\Omega$  at +25°C thermistor, use 100k $\Omega$ .

For a typical  $10k\Omega$  (at  $+25^{\circ}C$ ) thermistor and a  $10k\Omega$  RTB resistor, the charger enters a temperature suspend state when the thermistor resistance falls below  $3.97k\Omega$  (too hot) or rises above  $28.7k\Omega$  (too cold). This corresponds to a 0°C to  $+50^{\circ}C$  range when using a  $10k\Omega$  NTC thermistor with a beta of 3500. The general relation of thermistor resistance to temperature is defined by the following equation:

$$R_T = R_{25} \times e^{\left\{\beta \left(\frac{1}{T+273} - \frac{1}{298}\right)\right\}}$$

where:

$\mbox{R}_{T} = \mbox{The resistance}$  in  $\Omega$  of the thermistor at temperature T in Celsius

$R_{25}$  = The resistance in  $\Omega$  of the thermistor at +25°C

$\beta$  = The material constant of the thermistor, which typically ranges from 3000K to 5000K

T = The temperature of the thermistor in °C

Table 3 shows the MAX8677A THM temperature limits for different thermistor material constants.

Some designs might prefer other thermistor temperature limits. Threshold adjustment can be accommodated by changing RTB, connecting a resistor in series and/or in parallel with the thermistor, or using a thermistor with different  $\beta$ . For example, a +45°C hot threshold and 0°C cold threshold can be realized by using a thermistor with a  $\beta$  of 4250 and connecting 120k $\Omega$  in parallel. Since the thermistor resistance near 0°C is much higher than it is near +50°C, a large parallel resistance lowers the cold threshold, while only slightly lowering the hot threshold. Conversely, a small series resistance raises the cold threshold, while only slightly raising the

hot threshold. Raising R<sub>TB</sub> lowers both the hot and cold thresholds, while lowering R<sub>TB</sub> raises both thresholds.

#### **Power Dissipation**

It is important to ensure that the heat generated by the MAX8677A is dissipated into the PCB. The package's exposed paddle must be soldered to the PCB with multiple vias tightly packed under the exposed paddle to ensure optimum thermal contact to the ground plane. This minimizes heat rise in the IC and ensures that maximum charging current is maintained over the widest range of external conditions. Table 4 shows the thermal characteristics of the MAX8677A package.

**Table 4. Package Thermal Characteristics**

| SINGLE-LAYER     | MULTILAYER                                   |

|------------------|----------------------------------------------|

| PCB              | PCB                                          |

| 1666.7mW         | 2222.2mW                                     |

| Derate 20.8mW/°C | Derate 27.8mW/°C                             |

| above +70°C      | above +70°C                                  |

| 48°C/W           | 36°C/W<br>2.7°C/W                            |

|                  | PCB  1666.7mW  Derate 20.8mW/°C  above +70°C |

#### **PCB Layout and Routing**

Good design minimizes ground bounce and voltage gradients in the ground plane, which can result in instability or regulation errors. GND should connect to the power-ground plane at only one point to minimize the effects of power-ground currents. Battery ground should connect directly to the power-ground plane. Connect GND to the exposed paddle directly under the IC. Use multiple tightly spaced vias to the ground plane under the exposed paddle to help cool the IC. Position input capacitors from DC, SYS, BAT, and USB to the power-ground plane as close as possible to the IC. Keep high-current traces, such as those to DC, SYS, and BAT, as short and wide as possible. Refer to the MAX8677A evaluation kit for a suitable PCB layout example.

**Table 3. Fault Temperatures for Different Thermistors**

| •                                  |       |       |       |       |       |

|------------------------------------|-------|-------|-------|-------|-------|

| Thermistor β (K)                   | 3000  | 3250  | 3500  | 3750  | 4250  |

| R <sub>TB</sub> (kΩ) (Figure 7)    | 10    | 10    | 10    | 10    | 10    |

| Resistance at +25°C (kΩ)           | 10    | 10    | 10    | 10    | 10    |

| Resistance at +50°C (kΩ)           | 4.59  | 4.30  | 4.03  | 3.78  | 3.32  |

| Resistance at 0°C (kΩ)             | 25.14 | 27.15 | 29.32 | 31.66 | 36.91 |

| Nominal Hot-Trip Temperature (°C)  | 55    | 53    | 51    | 49    | 46    |

| Nominal Cold-Trip Temperature (°C) | -3    | -1    | 0     | 2     | 4.5   |

**Chip Information**

PROCESS: BICMOS

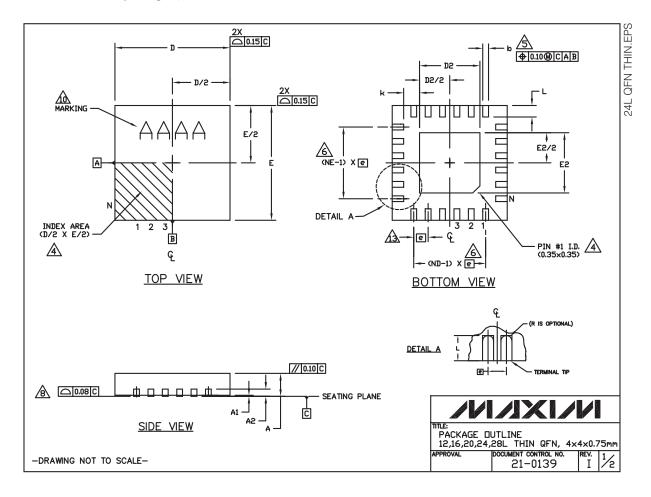

#### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

| COMMON DIMENSIONS |           |      |      |           |      |      |           |      |      |           |      |      |           |      |      |

|-------------------|-----------|------|------|-----------|------|------|-----------|------|------|-----------|------|------|-----------|------|------|

| PKG               | 12L 4×4   |      |      | 16L 4×4   |      |      | 20L 4×4   |      |      | 24L 4×4   |      |      | 28L 4×4   |      |      |

| REF.              | MIN.      | NDM. | MAX. | MIN.      | NOM. | MAX. | MIN.      | NDM. | MAX. | MIN.      | NDM. | MAX. | MIN.      | NDM. | MAX. |

| Α                 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 |

| A1                | 0.0       | 0.02 | 0.05 | 0.0       | 0.02 | 0.05 | 0.0       | 0.02 | 0.05 | 0.0       | 0.02 | 0.05 | 0.0       | 0.02 | 0.05 |

| A2                | 0.20 REF  |      |      |

| b                 | 0.25      | 0.30 | 0.35 | 0.25      | 0.30 | 0.35 | 0.20      | 0.25 | 0.30 | 0.18      | 0.23 | 0.30 | 0.15      | 0.20 | 0.25 |

| D                 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 |

| Ε                 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 |

| e                 | 0.80 BSC. |      |      | 0.65 BSC. |      |      | 0.50 BSC. |      |      | 0.50 BSC. |      |      | 0.40 BSC. |      |      |

| k                 | 0.25      | -    | -    | 0.25      | -    | -    | 0.25      | -    | ı    | 0.25      | -    | ı    | 0.25      | -    | -    |

| L                 | 0.45      | 0.55 | 0.65 | 0.45      | 0.55 | 0.65 | 0.45      | 0.55 | 0.65 | 0.30      | 0.40 | 0.50 | 0.30      | 0.40 | 0.50 |

| N                 | 12        |      |      | 16        |      |      | 20        |      |      | 24        |      |      | 28        |      |      |

| ND                | 3         |      | 4    |           |      | 5    |           |      | 6    |           | 7    |      |           |      |      |

| NE                | 3         |      |      | 4         |      |      | 5         |      |      | 6         |      |      | 7         |      |      |

| Jedec<br>Var.     | WGGB      |      |      | WGGC      |      |      | WGGD-1    |      |      | WGGD-2    |      |      | VGGE      |      |      |

| EXPOSED PAD VARIATIONS |           |           |      |      |      |      |  |  |  |  |

|------------------------|-----------|-----------|------|------|------|------|--|--|--|--|

| PKG.                   |           | D2        |      | E2   |      |      |  |  |  |  |

| CODES                  | MIN.      | NDM.      | MAX. | MIN. | NDM. | MAX. |  |  |  |  |

| T1244-3                | 1.95 2.10 |           | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T1244-4                | 1.95      | 1.95 2.10 |      | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T1644-3                | 1.95 2.10 |           | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T1644-4                | 1.95      | 2.10      | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T2044-2                | 1.95      | 2.10      | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T2044-3                | 1.95      | 2.10      | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T2444-2                | 1.95      | 2.10      | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T2444-3                | 2.45      | 2.60      | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |

| T2444-4                | 2.45      | 2.60      | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |

| T2444N-4               | 2.45      | 2.60      | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |

| T2444M-1               | 2.45      | 2.60      | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |

| T2844-1                | 2.50      | 2.60      | 2.70 | 2.50 | 2.60 | 2.70 |  |  |  |  |

#### NUTES

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- N IS THE TOTAL NUMBER OF TERMINALS.

- ⚠ THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- 🛕 DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25mm AND 0.30mm FROM TERMINAL TIP.

- ⚠ ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- & COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

- 11. COPLANARITY SHALL NOT EXCEED 0.08mm.

- 12. WARPAGE SHALL NOT EXCEED 0.10mm. ⚠ LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "e", ±0.05.

- 14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- 15. ALL DIMENSIONS ARE THE SAME FOR LEADED (-) & POFREE (+) PACKAGE CODES.

TITLE: PACKAGE DUTLINE 12,16,20,24,28L THIN QFN, 4×4×0.75mm DOCUMENT CONTROL NO. 21-0139

-DRAWING NOT TO SCALE-

### **Revision History**

Pages changed at Rev 1: 1, 3, 21

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001: