# DataSheet

austriamicrosystems

# AS3977 Multi-Channel Narrowband FSK Transmitter

# 1 General Description

The AS3977 is a low-power fully integrated ETSI, FCC and ARIB compliant FSK transmitter capable of operating at any ISM frequency in the range of 300 to 928 MHz. It is based on a sigmadelta controlled fractional-N synthesizer phase locked loop (PLL) with fully integrated voltage controlled oscillator (VCO). The power amplifier (PA) output is programmable and can deliver power ranging from –20dBm up to +10dBm. An on-chip low drop-out (LDO) regulator is available in case an accurate output power independent of voltage supply variation is required. The output signal can be shaped using a programmable Gaussian filter to minimize the occupied bandwidth and adjacent channel power. The maximum data rate can be up to 100 kb/s – depending on the required filtering. The FSK frequency deviation is programmable up to a maximum of 64 kHz.

The crystal oscillator can handle a wide range of frequencies. For narrow-band applications, a temperature sensor with digital read-out is included that allows compensation of the crystal frequency drift due to temperature variation.

The AS3977 is connected to an external microcontroller via a bidirectional digital interface. The device operates at very low current consumption with a power supply range from 2.0V to 3.6V and can be powered down when not in use.

The device is fabricated in austriamicroystems advanced  $0.35 \mu m$  SiGe-BiCMOS technology.

# 2 Key Features

- Fully integrated UHF transmitter

- Compliant to ETSI EN 300-220, FCC CFR47 part 15 and ARIB STD-T67

- Multi-channel with narrow bandwidth

- 300 928 MHz operating frequency range (ISM)

- Filtered FSK

- Data rate up to 100 kb/s

- FSK deviation programmable up to 64kHz

- Extremely low power consumption

# Main Characteristics

- 2.0 3.6V power supply

- Power down current consumption 100 nA (3V, 25°C)

- Output power up to +10dBm

- Occupied bandwidth 6 kHz (4.8 kb/s, FFSK, ARIB)

- -40 to 85°C temperature range

# **Additional Features**

- Sigma-Delta controlled fractional-N synthesizer

- Resolution of synthesizer < 100Hz</li>

- Fully integrated PLL

- Fully integrated voltage controlled oscillator (VCO)

- 4kV ESD protection (1.5kV for the Analog pins)

- 12 20 MHz crystal oscillator

- On-chip temperature sensor with digital readout for AFC purposes

- Fast frequency hopping with predefined channel selection

- Microcontroller clock output to save addition crystal

- Constant output power over battery life time

- Integrated Manchester coder

- Digital lock detector

- Low drop-out regulator

- Bi-directional serial interface

- Low Power Down Mode current consumption

# 3 Applications

The AS3977 is suitable for Remote keyless entry systems, Short range radio data transmission, Domestic and consumer remote control units, Cordless alarm systems, Remote metering, and Low power telemetry.

*austriamicrosystems austriamicrosystems*

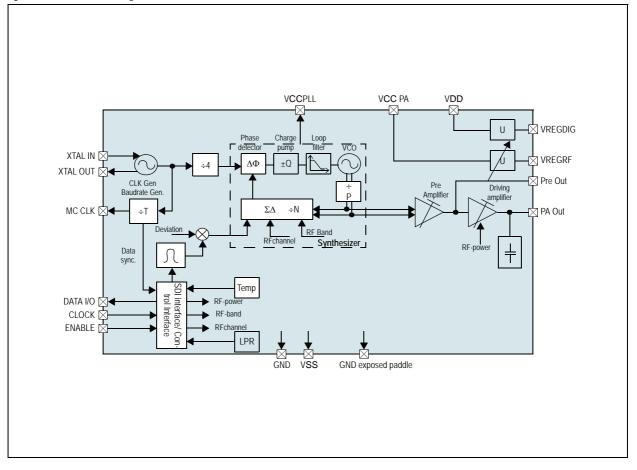

### Figure 1. AS3977 Block Diagram

# Contents

| 1 | General Description                                                                                                    | 1        |

|---|------------------------------------------------------------------------------------------------------------------------|----------|

| 2 | Key Features                                                                                                           | 1        |

| 3 | Applications                                                                                                           | 1        |

| 4 | Pin Assignments                                                                                                        | 5        |

|   | 4.1 Pin Descriptions                                                                                                   | . 5      |

| 5 | Absolute Maximum Ratings                                                                                               |          |

|   | Electrical Characteristics                                                                                             |          |

|   | Timing Characteristics                                                                                                 | 15       |

| ' | 7.1 Timing Parameters                                                                                                  | 16       |

| Q | •                                                                                                                      | 10       |

| 0 | Detailed System Description                                                                                            |          |

|   | 8.1 Reference Frequency Generator                                                                                      | 17       |

|   | 8.2 Phase Locked Loop                                                                                                  | 17       |

|   | 8.3 Gaussian Filter and Digital Modulator                                                                              | 17       |

|   | 8.4 Power Amplifier                                                                                                    | 17       |

|   | 8.5 Temperature Sensor                                                                                                 | 17       |

|   | 8.6 Low Power Reset                                                                                                    | 17       |

|   | 8.7 Low Drop Out Regulators                                                                                            | 17       |

|   | 8.8 SDI / Control Interface                                                                                            | 18       |

|   | 8.9 Baud Rate Generator                                                                                                | 18       |

| 9 | Application Information                                                                                                | 19       |

|   | 9.1 Operation Modes                                                                                                    | 19       |

|   | 9.2 Transmitter Control Interface                                                                                      | 20       |

|   | 9.2.1 Configuration Diagram                                                                                            |          |

|   | 9.2.2 Power On Reset                                                                                                   |          |

|   | 9.2.3 Writing of Data to Addressable Registers                                                                         |          |

|   | 9.2.4 Reading of Data from Addressable Registers                                                                       |          |

|   | 9.2.5 Transmitting Data                                                                                                |          |

|   | 9.3 Transmitter Control States                                                                                         |          |

|   | 9.3.1 Power Down State                                                                                                 |          |

|   | 9.3.2 Active Edge of CLK                                                                                               |          |

|   | 9.3.3 Active State                                                                                                     |          |

|   | 9.3.4 Transmit State                                                                                                   | 26       |

|   | 9.4 ENABLE Signal Functionality                                                                                        |          |

|   | 9.5 Communication and Command Byte Structure                                                                           |          |

|   | 9.6 Transmitter Configuration Register                                                                                 | 29       |

|   | 9.7 Special Bits                                                                                                       | 33       |

|   | 9.7.1 LT (Lock Transmit)                                                                                               |          |

|   | 9.7.2 LS (Low Power Supply Voltage)                                                                                    |          |

|   | 9.7.3 MCCS, CLKS and PSC<br>9.7.4 SETPD (Set Power Down)                                                               |          |

|   |                                                                                                                        |          |

|   | 9.8 Output Frequency Setting.                                                                                          | 34<br>25 |

|   | 9.8.1 Implementation<br>9.8.2 Optional Frequency Calculation with Overlapping Fractional Bands by Using the Bit INT<8> |          |

|   | 9.8.2 Optional Frequency Calculation with Overlapping Fractional Bands by Osing the Bit INT<8>                         |          |

|   | 9.9 Baud Rate Generator                                                                                                |          |

|   |                                                                                                                        | 20       |

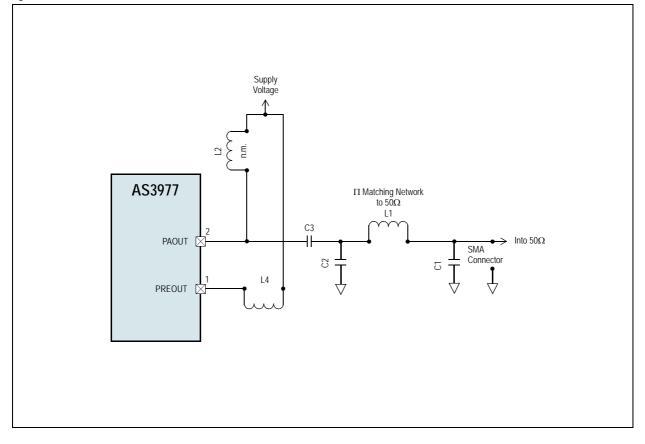

| 9.10 Reference Design PREOUT and PAOUT Connection                              | 38   |

|--------------------------------------------------------------------------------|------|

| 9.10.1 Matching Circuit and PREOUT and PAOUT Connections to the Supply Voltage | . 38 |

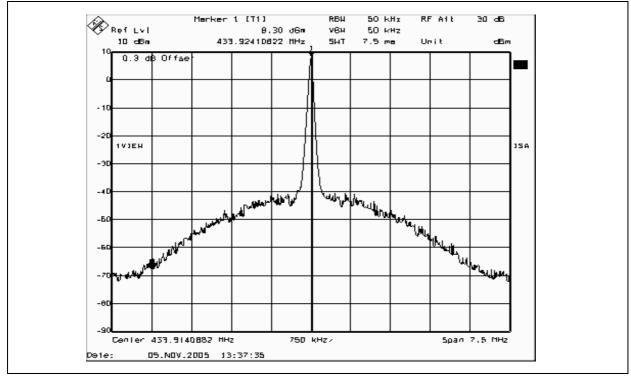

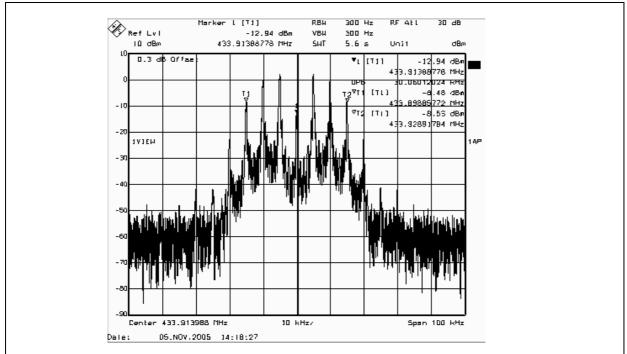

| 10 Measurement Results                                                         | 41   |

| 10.0.1 Applicable Radio Standards                                              | . 43 |

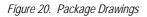

| 11 Package Drawings and Markings                                               | 44   |

| 12 Ordering Information                                                        | 46   |

# 4 Pin Assignments

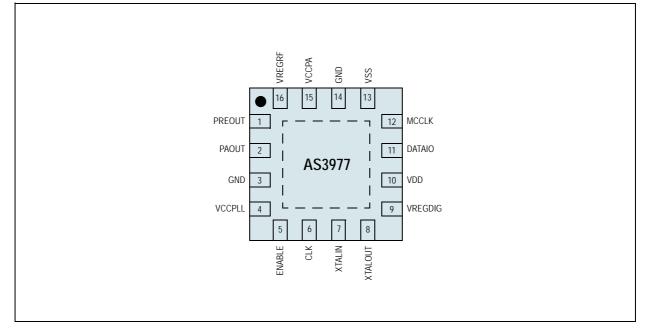

Figure 2. Pin Assignments (Top View)

# 4.1 Pin Descriptions

## Table 1. Pin Descriptions

| Pin Name | Pin Number | Туре               | Description                                                                                                                       |

|----------|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| PREOUT   | 1          | PREOUT             | Open Collector preamplifier output, need a feeding coil<br>connected to VREGRF or VDD and is the input for the Power<br>amplifier |

| PAOUT    | 2          | PREOUT             | Open Collector power amplifier output, need a feeding coil connected to VREGRF or VDD                                             |

| RESERVED | 3          |                    | Must be connected to GND                                                                                                          |

| VCCPLL   | 4          | Positive Power Pin | Positive supplies of VCO, for optimum performance, add decoupling capacitors on this Pin.                                         |

| ENABLE   | 5          |                    | Digital CMOS level input, internal Pull down resistor > 60k                                                                       |

Data Sheet - Pin Assignments

# Table 1. Pin Descriptions

| Pin Name | Pin Number | Туре               | Description                                                                                                                             |

|----------|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| CLK      | 6          | CLK                | SDI clock                                                                                                                               |

| XTALIN   | 7          |                    | XTAL oscillator input, DC Level approximately 1 Volt, needs an DC Blocker in case of external clock                                     |

| XTALOUT  | 8          |                    | XTAL oscillator output, DC Level approximately 1 Volt                                                                                   |

| VREGDIG  | 9          |                    | Voltage regulator2 (VRegDig) output, requires a capacitor with nominal 100 nF.                                                          |

| VDD      | 10         | Positive Power Pin | Positive supply of digital part and voltage regulator2 (VRegDig)                                                                        |

| DATAIO   | 11         | DATAIO             | Digital CMOS level input Pin, SDI data input / output                                                                                   |

| MCCLK    | 12         | MCCCLK             | Micro controller clock output Digital output with variable driver strength                                                              |

| VSS      | 13         | GND Pin            | Negative supply of digital part                                                                                                         |

| Reserved | 14         |                    | Must be connected to GND                                                                                                                |

| VCCPA    | 15         | Positive Power Pin | Positive supply of PA and voltage regulator                                                                                             |

| VREGRF   | 16         |                    | Voltage regulator output to feed the RF Amplifier. For optimum performance a capacitor with nominal $1\mu$ F and 100 nF is recommended. |

| GND      | 17         | GND Power Pin      | Negative supply of analogue part (exposed paddle)                                                                                       |

| -        | •          |                    |                                                                                                                                         |

# 5 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" (see Table 3) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Tahla 2  | Absolute Maximum      | Datinac |

|----------|-----------------------|---------|

| IADIC Z. | Αυσυμίε Ινιαλιπμίπη Ι | Naunus  |

| Paran                                         | neter                                     | Min  | Max | Units | Comments                                                                                                                                                                                                                                                   |

|-----------------------------------------------|-------------------------------------------|------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Positive supply                               | voltage (V <sub>SUP</sub> )               | -0.5 | 5.0 | V     | Voltage on all supply Pins VCCPA, VCCPLL, VDD                                                                                                                                                                                                              |

| Negative supply vo                            | Negative supply voltage (GND, Vss)        |      | 0   | V     |                                                                                                                                                                                                                                                            |

| Input current (latch-                         | up immunity) (I <sub>SCR</sub> )          | -40  | 40  | mA    | Norm: Jedec 17                                                                                                                                                                                                                                             |

| ESD for Digital Pins                          | ESD <sub>DHBM</sub>                       | ±4   |     | kV    | Norm MIL 883 E method 3015<br>(Human Body Model)                                                                                                                                                                                                           |

|                                               | ESD <sub>DMM</sub>                        | ±200 |     | V     | Norm: EIJA IC-121<br>(Machine Model)                                                                                                                                                                                                                       |

| ESD for Analog Pins                           | ESD <sub>AHBM</sub>                       | ±1.5 |     | kV    | Norm MIL 883 E method 3015<br>(Human Body Model)                                                                                                                                                                                                           |

| LOD TOT Analog Fills                          | ESD <sub>AMM</sub>                        | ±100 |     | V     | Norm: EIJA IC-121<br>(Machine Model)                                                                                                                                                                                                                       |

| ESD for RF Pins                               | ESD <sub>RFHBM</sub>                      | ±1.5 |     | kV    | Norm MIL 883 E method 3015<br>(Human Body Model)                                                                                                                                                                                                           |

|                                               | ESD <sub>RFMM</sub>                       | ±100 |     | V     | Norm: EIJA IC-121<br>(Machine Model)                                                                                                                                                                                                                       |

| Total power<br>(all supplies                  |                                           |      | 200 | mW    |                                                                                                                                                                                                                                                            |

| Storage temper                                | Storage temperature, (T <sub>STRG</sub> ) |      | 125 | °C    |                                                                                                                                                                                                                                                            |

| Package body temperature (T <sub>BODY</sub> ) |                                           |      | 260 | ٥C    | Norm: IPC/JEDEC J-STD-020C.<br>The reflow peak soldering temperature (body<br>temperature) specified is in accordance with IPC/<br>JEDEC J-STD-020C "Moisture/Reflow Sensitivity<br>Classification for Non-Hermetic Solid State Surface<br>Mount Devices". |

| Humidity non                                  | -condensing                               | 5    | 85  | %     |                                                                                                                                                                                                                                                            |

# 6 Electrical Characteristics

Table 3. Operating Conditions

| Symbol           | Parameter                       | Conditions                                | Min  | Тур | Мах | Units |

|------------------|---------------------------------|-------------------------------------------|------|-----|-----|-------|

| V <sub>SUP</sub> | Positive supply voltage analog  | Voltage on all supply<br>VCCPA,VCCPLL,VDD | 2.0  |     | 3.6 | V     |

| GND              | Negative supply voltage analog  |                                           | 0    |     | 0   | V     |

| Vss              | Negative supply voltage digital |                                           | 0    |     | 0   | V     |

| A-D              | Difference of supplies          | VCC-VDD, GND-VSS                          | -0.1 |     | 0.1 | V     |

| Тамв             | Ambient Temperature             |                                           | -40  |     | 85  | ٥C    |

Table 4. Block Specification

| Symbol               | Parameter                                               | Conditions                                                                                                                                           | Min   | Тур  | Мах | Units    |

|----------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----|----------|

| fout315              |                                                         |                                                                                                                                                      | 300   |      | 320 |          |

| fout434              | Output Frequency Dense                                  |                                                                                                                                                      | 425   |      | 450 |          |

| f <sub>OUT868</sub>  | - Output Frequency Range                                |                                                                                                                                                      | 865   |      | 870 | - MHz    |

| fout915              |                                                         |                                                                                                                                                      | 902   |      | 928 |          |

| P <sub>OUT</sub>     | Output Power                                            | Depends on Power Setting                                                                                                                             |       |      |     |          |

| frout                | FSK Data Rate                                           | Internal Manchester Coding                                                                                                                           | 1     |      | 100 | - kbit/s |

| f <sub>FSKdata</sub> | T SK Dala Kale                                          | Internal Manchester Coung                                                                                                                            | 0.5   |      | 50  | - KUIUS  |

| 315MHz Fi            | equency Band Section, FCC part 15 is                    | applicable                                                                                                                                           |       |      |     |          |

| $\Delta FSK_1$       | FSK Deviation                                           | programmable (8bit)<br>Resolution of FSK Deviation (see Table 5)                                                                                     | 0     |      | ±64 | kHz      |

|                      | Spurious Emissions                                      | 216-960MHz                                                                                                                                           |       |      | -49 |          |

| P <sub>SPE1</sub>    | (max. –19.6dBm radiated fundamental power) <sup>1</sup> | at frequencies > 960Mhz<br>at harmonics                                                                                                              |       |      | -41 | dBm      |

|                      |                                                         |                                                                                                                                                      |       |      | -40 |          |

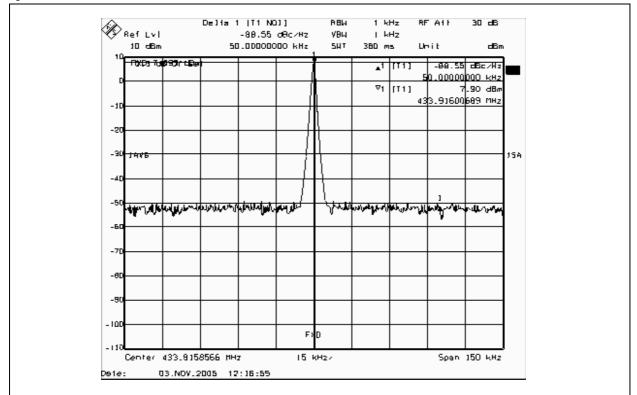

|                      | Phase noise @ 50 kHz                                    | Charge pump setting: I <sub>CHP</sub> =50µA;                                                                                                         |       | -86  |     |          |

|                      | Phase noise @ 250 kHz                                   | V <sub>SUP</sub> =2.03.6V,<br>TAMB=-4085°C                                                                                                           |       | -92  |     | dBc/Hz   |

|                      | Phase noise @ 1 MHz                                     |                                                                                                                                                      |       | -102 |     |          |

| 434MHz Fi            | equency Band Section, EN 300 220 ar                     | nd/or ARIB STD-T67 are applicable                                                                                                                    |       |      |     |          |

| $\Delta FSK_2$       | FSK Deviation                                           | Small deviation (ARIB), programmable (8bit)                                                                                                          | ±1.25 |      | ±4  | - 647    |

|                      |                                                         | Resolution of FSK Deviation (see Table 5)                                                                                                            | 0     |      | ±64 | kHz<br>ł |

|                      | Phase noise @ 50 kHz                                    | Charge pump setting: I <sub>CHP</sub> =50µA;                                                                                                         |       | -86  | -83 |          |

|                      | Phase noise @ 250 kHz                                   | V <sub>SUP</sub> =2.03.6V,                                                                                                                           |       | -94  |     | dBc/Hz   |

|                      | Phase noise @ 1 MHz                                     | Тамв=-40…85°С                                                                                                                                        |       | -102 |     |          |

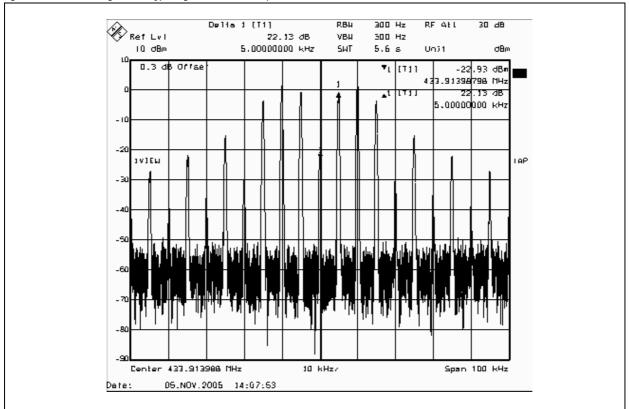

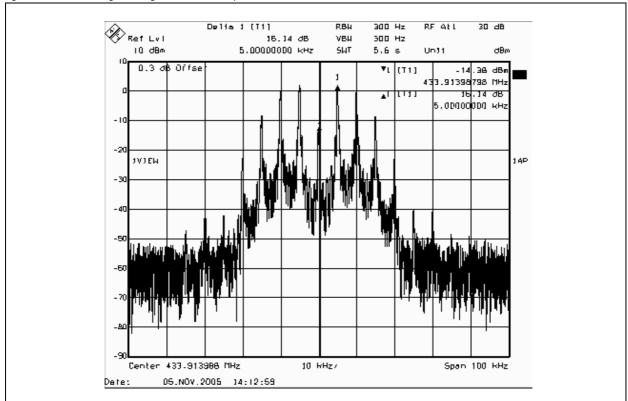

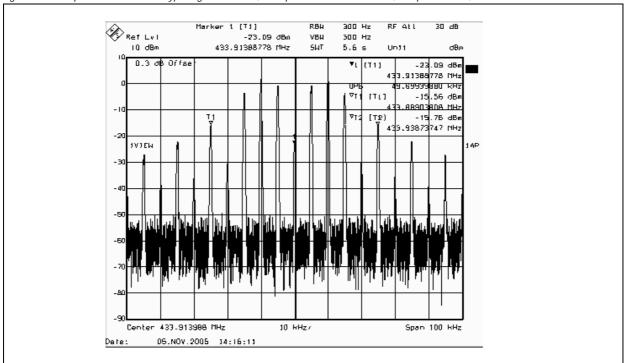

| P <sub>ACP2</sub>    | Adjacent Channel Power                                  | ARIB, f <sub>REF</sub> =4MHz, I <sub>CHP</sub> =50µA                                                                                                 |       |      | -40 | dBc      |

|                      |                                                         | Channel spacing 12.5 kHz, FSK data rate<br>4.8 kbit/s (ARIB)<br>FSK Deviation ±1.8 KHz                                                               |       |      | 8.5 |          |

| OBW <sub>2</sub>     | Occupied Bandwidth                                      | GF Setting (see Gaussian Filter Clock<br>Setting on page 38)<br>Channel spacing 25 kHz,<br>FSK data rate 9.6 kbit/s (ARIB)<br>FSK Deviation ±3.0 KHz | 8.5   |      | 16  | kHz      |

#### Table 4. Block Specification (Continued)

| Symbol            | Parameter                                              | Conditions                                                                   | Min | Тур | Max | Units  |

|-------------------|--------------------------------------------------------|------------------------------------------------------------------------------|-----|-----|-----|--------|

| P <sub>SPE2</sub> | Spurious Emissions<br>excluding Harmonics <sup>1</sup> | 47-74MHz<br>87.5-118MHz<br>174-230MHz<br>470-862MHz (EN 300 220)             |     |     | -54 | dBm    |

|                   | Spurious Emissions                                     | at other frequencies < 1GHz                                                  |     |     | -36 |        |

|                   | and Harmonics <sup>1</sup>                             | at ≥ 1GHz (EN 300 220)                                                       |     |     | -30 | dBm    |

|                   |                                                        | ARIB                                                                         |     |     | -29 |        |

| ferror            | Output Frequency Error                                 | With ideal crystal,<br>V <sub>SUP</sub> =2.0…3.6V,<br>TAMB=-40…85°C          |     |     | ±1  | ppm    |

| 868MHz Fr         | equency Band Section, EN 300 220 is                    | applicable                                                                   |     |     |     |        |

| $\Delta FSK_3$    | FSK Deviation                                          | programmable (8bit)<br>Resolution of FSK Deviation (see Table 5)             | 0   |     | ±64 | kHz    |

| P <sub>SPE3</sub> | Spurious Emissions<br>excluding Harmonics <sup>1</sup> | 47-74MHz<br>87.5-118MHz<br>174-230MHz<br>470-862MHz (@-10dBm radiated power) |     |     | -54 | dBm    |

|                   | Spurious Emissions                                     | at other frequencies < 1GHz                                                  |     |     | -36 | dDma   |

|                   | and Harmonics <sup>1</sup>                             | at frequencies $\geq$ 1GHz                                                   |     |     | -30 | dBm    |

|                   | Phase noise @ 50 kHz                                   | Charge pump setting: I <sub>CHP</sub> =50µA;                                 |     |     | -78 |        |

|                   | Phase noise @ 250 kHz                                  | V <sub>SUP</sub> =2.03.6V,                                                   |     |     | -85 | dBc/Hz |

|                   | Phase noise @ 1 MHz                                    | Тамв=-4085°С                                                                 |     |     | -89 | -      |

| 915MHz Fr         | equency Band Section, FCC part 15 is                   | applicable                                                                   |     |     |     |        |

| $\Delta FSK_4$    | FSK Deviation                                          | programmable (8bit)<br>Resolution of FSK Deviation (see Table 5)             | 0   |     | ±64 | kHz    |

|                   | Spurious Emissions                                     | 216-960MHz                                                                   |     |     | -49 |        |

| P <sub>SPE4</sub> | (max. –1dBm radiated fundamental power) <sup>1</sup>   | at frequencies > 960MHz and harmonics                                        |     |     | -41 | dBm    |

1. These parameters will not be tested.

#### Table 5. Resolution of FSK Deviation

| Symbol               | Parameter                                | Conditions                                                                                  | Equation for Min. Resolution                        | Units |  |  |  |  |  |  |  |

|----------------------|------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------|-------|--|--|--|--|--|--|--|

| 315MHz and           | 315MHz and 434MHz Frequency Band Section |                                                                                             |                                                     |       |  |  |  |  |  |  |  |

| ∆FSK <sub>res1</sub> | Resolution of FSK Deviation <sup>1</sup> | For detailed information, See FSK<br>Deviation Setting and Frequency<br>Trimming on page 37 | $\Delta F = (INT < 8 > +1). \frac{f_{REF}}{2^{16}}$ | Hz    |  |  |  |  |  |  |  |

| 868MHz and           | 1915MHz Frequency Band Section           |                                                                                             |                                                     |       |  |  |  |  |  |  |  |

| ∆FSK <sub>res2</sub> | Resolution of FSK Deviation <sup>1</sup> | For detailed information, See FSK<br>Deviation Setting and Frequency<br>Trimming on page 37 | $\Delta F = (INT < 8> +1). \frac{f_{REF}}{2^{15}}$  | Hz    |  |  |  |  |  |  |  |

### 1. INT<8> refer to Register Settings

### Table 6. Reference Frequency Generator and Micro Controller Clock Driver

| Symbol     | Parameter | Conditions | Min | Тур | Мах | Units |

|------------|-----------|------------|-----|-----|-----|-------|

| Crystal Os | cillator  |            |     |     |     |       |

| Symbol             | Parameter                                        | Conditions                                                                        | Min                  | Тур | Мах                  | Units |

|--------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|-----|----------------------|-------|

| f <sub>XOSC</sub>  | Crystal Oscillator Frequency                     |                                                                                   | 12                   | 16  | 20                   | MHz   |

| t <sub>xosc</sub>  | Crystal Oscillator Start up time                 | $V_{SUP}=2.03.6V$ ,<br>TAMB=-4085°C<br>crystal series resistance $\leq 100\Omega$ |                      |     | 1.5                  | ms    |

| R <sub>XOSC</sub>  | Crystal Oscillator Oscillation Margin<br>Level   | f <sub>XOSC</sub> =13.56MHz, C <sub>L</sub> =12pF                                 | 1500                 |     |                      | Ω     |

| $\Delta f/f_0$     | Frequency Stability vs. Temperature <sup>1</sup> | AS3977 Only                                                                       |                      |     | ±1                   | ppm   |

| Micro Cont         | roller Clock Driver                              |                                                                                   |                      |     |                      |       |

| f <sub>MCCLK</sub> | Clock output frequency                           | depending on configuration register settings and crystal                          |                      |     | 4                    | MHz   |

| V <sub>MCL</sub>   | Low level output voltage                         | V <sub>SUP</sub> =3V, at nominal high level output current                        |                      |     | 0.1*V <sub>SUP</sub> | V     |

| V <sub>MCH</sub>   | High level output voltage                        | V <sub>SUP</sub> =3V, at nominal high level output current                        | 0.9*V <sub>SUP</sub> |     |                      | V     |

| CLMCC              | Capacitive load                                  |                                                                                   |                      |     | 20                   | pF    |

| t <sub>RMCC</sub>  | Rise time                                        |                                                                                   |                      |     | 62.5                 | ns    |

| t <sub>FMCC</sub>  | Fall time                                        |                                                                                   |                      |     | 62.5                 | ns    |

| I <sub>MCH</sub>   | High level output current                        |                                                                                   |                      |     | 1                    | mA    |

| I <sub>MCL</sub>   | Low level output current                         |                                                                                   |                      |     | 1                    | mA    |

## Table 6. (Continued)Reference Frequency Generator and Micro Controller Clock Driver

#### 1. These parameters will not be tested.

### Table 7. Phase Locked Loop

| Symbol            | Parameter                   | Conditions                                                               | Min | Тур | Мах | Units |

|-------------------|-----------------------------|--------------------------------------------------------------------------|-----|-----|-----|-------|

| f <sub>REF</sub>  | Comparison Frequency        | depending on f <sub>XOSC</sub><br>(reference divider division ratio = 4) | 3.0 | 4.0 | 5.0 | MHz   |

| Afo               | Output Frequency Decolution | tput Frequency Resolution four315 / four434<br>four868 / four915         | 46  | 61  | 77  | Hz    |

| $\Delta f_{O}$    |                             |                                                                          | 92  | 122 | 153 | ΠZ    |

| <b>t</b> SYNTH    | Synthesizer Start up Time   |                                                                          |     | 500 |     | μs    |

| t <sub>LOCK</sub> | Synthesizer Lock Time       | $\Delta f$ =600kHz,<br>f <sub>ERROR</sub> @ t <sub>LOCK</sub> =10kHz     |     | 50  | 200 | μs    |

### Table 8. Loop Filter Bandwidth

| Symbol          | Parameter                   |           | Conditions                   | Min | Тур | Мах | Units |  |  |  |

|-----------------|-----------------------------|-----------|------------------------------|-----|-----|-----|-------|--|--|--|

| Filter Band     | Filter Bandwidth at 315 MHz |           |                              |     |     |     |       |  |  |  |

|                 |                             | @ 12.5 µA |                              |     | 55  |     |       |  |  |  |

| f               | ICHP                        | @ 25 µA   | Reference Frequency = $4MHz$ |     | 85  |     | 6117  |  |  |  |

| f <sub>BW</sub> |                             | @ 37.5µA  | VSUP = 3.0 V;<br>TAMB = 25°C |     | 115 |     | kHz   |  |  |  |

|                 |                             | @ 50 µA   |                              |     | 170 |     |       |  |  |  |

| Filter Band     | Filter Bandwidth at 433 MHz |           |                              |     |     |     |       |  |  |  |

### Table 8. (Continued)Loop Filter Bandwidth

| Symbol          | Paramet              | er        | Conditions                                  | Min | Тур | Мах | Units |

|-----------------|----------------------|-----------|---------------------------------------------|-----|-----|-----|-------|

|                 |                      | @ 12.5 µA |                                             |     | 50  |     |       |

| f <sub>BW</sub> | Charge pump setting: | @ 25 µA   | Reference Frequency = 4MHz<br>VSUP = 3.0 V; |     | 70  |     | kHz   |

| IBM             | I <sub>CHP</sub>     | @ 37.5µA  | VSOP = 3.0 V,<br>ТАМВ = 25°С                |     | 90  |     | КПД   |

|                 |                      | @ 50 µA   |                                             |     | 120 |     |       |

| Filter Band     | width at 868 MHz     |           |                                             |     |     |     |       |

|                 |                      | @ 12.5 µA |                                             |     | 50  |     |       |

| f <sub>BW</sub> | Charge pump setting: | @ 25 µA   | Reference Frequency = 4MHz<br>VSUP = 3.0 V; |     | 70  |     | kHz   |

| IBM             | I <sub>CHP</sub>     | @ 37.5µA  | VSOP = 3.0 V,<br>ТАМВ = 25°С                |     | 90  |     | КПД   |

|                 | (                    | @ 50 µA   |                                             |     | 120 |     |       |

| Symbol | Parameter                                                     | Conditions                                                                                                                                                                                  | Min  | Тур            | Мах  | Units |

|--------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|-------|

| Роит   | Min. Output Power @ 50 $\Omega$                               | Vsup=3V, @ 25°C,<br>Power depending on power setting with or<br>without the use of the internal voltage<br>regulator, external matching network<br>included                                 |      | -20            |      | dBm   |

| Роит   | Max. Output Power @ 50 $\Omega$                               | VsuP=3V, @ 25°C,<br>Power depending on power setting with or<br>without the use of the internal voltage<br>regulator, external matching network<br>included                                 |      | 8              |      | dBm   |

| Роит   | Output Power<br>Variation@ 50Ω <sup>1</sup><br>(300 – 320MHz) | Vsup=3V, @ 25°C,<br>Power depending on register setting with<br>or without the use of the internal voltage<br>regulator,<br>external matching network included,<br>strong AB operation mode | -2.5 |                | +2.5 | dBm   |

| Роит   | Output Power<br>Variation@ 50Ω <sup>1</sup><br>(425 – 450MHz) | Vsup=3V, @ 25°C,<br>Power depending on register setting with<br>or without the use of the internal voltage<br>regulator,<br>external matching network included,<br>strong AB operation mode | -2.0 |                | +2.0 | dBm   |

| Роит   | Output Power Variation vs. VDD and<br>Temperature @ 50Ω       | VSUP=2.23.6V, TAMB=-4085°C, With<br>the use of the internal voltage regulator,<br>external matching network included,<br>strong AB operation mode                                           | -2.8 | +0.6 /<br>-1.5 | 1.0  | dB    |

| Роит   | Output Power Variation vs.<br>Temperature @ 50Ω               | VSUP=3V, TAMB=-4085°C,<br>Without the use of the internal voltage<br>regulator,<br>external matching network included,<br>strong AB operation mode                                          |      | +1.5 /<br>-2.0 |      | dB    |

| Роит   | Max Output Power @ 50 $\Omega$                                | VsuP=3.6V, @ 25°C,<br>Power depending on power setting<br>without the use of the internal voltage<br>regulator,<br>external matching network included                                       |      | 10             |      | dBm   |

1. Limits by production test measurement uncertainties

| Symbol | Parameter                                               | Conditions                                                                                                                                                                                            | Min  | Тур            | Мах  | Units |

|--------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|-------|

| Роит   | Min Output Power<br>@ 50Ω                               | VSUP=3V, @ 25°C,<br>Power depending on power setting with or<br>without the use of the internal voltage<br>regulator,<br>external matching network included                                           |      | -20            |      | dBm   |

| Роит   | Max Output Power<br>@ 50Ω                               | VSUP=3V, @ 25°C,<br>Power depending on power setting with or<br>without the use of the internal voltage<br>regulator, external matching network<br>included                                           |      | 4              |      | dBm   |

| Роит   | Output Power Variation @ 50 $\Omega^1$                  | VSUP=3V, @ 25°C,<br>Power depending on register setting with<br>or without the use of the internal voltage<br>regulator, external matching network<br>included, strong AB operation mode <sup>2</sup> | -3.5 |                | +3.5 | dBm   |

| Роит   | Output Power Variation vs. VDD and<br>Temperature @ 50Ω | VSUP=2.23.6V,<br>TAMB= -4085°C,<br>With the use of the internal voltage<br>regulator, external matching network<br>included, strong AB operation mode <sup>2</sup>                                    |      | +2.0 /<br>-3.0 |      | dB    |

| Роит   | Output Power Variation vs.<br>Temperature @ 50Ω         | VSUP=3V,<br>TAMB=-4085°C,<br>Without the use of the internal voltage<br>regulator, external matching network<br>included, strong AB operation mode <sup>2</sup>                                       |      | +2.0 /<br>-3.0 |      | dB    |

1. Limits by production test measurement uncertainties

2. Power line matching needs to be adjusted to VDD to ensure strong AB operation mode

Table 11. Antenna Tuning Circuit

| Symbol             | Parameter                        | Conditions         | Min | Тур  | Мах | Units |

|--------------------|----------------------------------|--------------------|-----|------|-----|-------|

| C <sub>Atmin</sub> | Minimum Antenna tuning Capacitor | ATCPH <3:0> = 0000 |     | 0.11 |     | pF    |

| C <sub>Atmax</sub> | Maximum Antenna tuning Capacitor | ATCPH <3:0> = 1111 |     | 1.51 |     | pF    |

Table 12. Low Power Reset (Bit LT)

| Symbol           | Parameter                                | Conditions                | Min  | Тур  | Мах  | Units |

|------------------|------------------------------------------|---------------------------|------|------|------|-------|

| V <sub>LPR</sub> | Low Power Detection Threshold<br>Voltage | Decreasing Supply Voltage | 1.85 | 1.95 | 2.05 | V     |

| V <sub>LPR</sub> | Low Power Release Threshold<br>Voltage   | Rising Supply Voltage     |      | 2.05 |      | V     |

#### Table 13. Low Supply Voltage Detector (Bit LS)

| ſ | Symbol          | Parameter                                 | Conditions                | Min | Тур  | Мах | Units |

|---|-----------------|-------------------------------------------|---------------------------|-----|------|-----|-------|

|   | $V_{\text{LS}}$ | Low Supply Detection Threshold<br>Voltage | Decreasing Supply Voltage | 2.0 | 2.1  | 2.2 | V     |

|   | V <sub>LS</sub> | Low Supply Release Threshold<br>Voltage   | Rising Supply Voltage     |     | 2.17 |     |       |

### Table 14. Temperature Sensor

| Symbol             | Parameter                                  | Conditions                                                        | Min | Тур  | Мах                   | Units    |

|--------------------|--------------------------------------------|-------------------------------------------------------------------|-----|------|-----------------------|----------|

| ERR <sub>TS</sub>  | Absolute Error                             | Tamb = -4085°C                                                    | -5  |      | +5                    | ٥C       |

| ERR <sub>TSL</sub> | Absolute Error (limited temperature range) | Тамв = -2065°С                                                    |     | ±2   |                       | °C       |

|                    | Conversion Factor                          | Tamb = -4085°C                                                    |     | 0.19 |                       | °C/bit   |

| OR <sub>TS</sub>   | Output Resolution                          |                                                                   |     | 10   |                       | bit      |

| CR <sub>TS</sub>   | Conversion Rate                            | $f_{TS} = f_{CRYSTAL}/12$<br>after startup time of 256 / $f_{TS}$ |     |      | f <sub>TS</sub> /1354 | samples/ |

Table 15. Voltage Regulator for Power Amplifier

| Symbol       | Parameter                                    | Conditions                | Min   | Тур | Мах | Units |

|--------------|----------------------------------------------|---------------------------|-------|-----|-----|-------|

| VREGRF       | Output Voltage for supply Power<br>Amplifier | Adjustable, nominal value | 1.7   |     | 2.0 | V     |

| D_VREGR<br>F | Regulator Tolerance                          |                           | -0.15 |     | 0.1 | V     |

Table 16. Current Consumption

| Symbol                 | Parameter                                                             | Conditio                                  | Min                                    | Тур | Мах  | Units |    |  |

|------------------------|-----------------------------------------------------------------------|-------------------------------------------|----------------------------------------|-----|------|-------|----|--|

|                        |                                                                       | VSUP=3V @ 25°C                            |                                        |     | 100  | 250   |    |  |

| Ipdwn                  | Power Down Mode                                                       | Vsup=2.03.6V,<br>Тамв=-4085°С             |                                        |     | 1000 | 5000  | nA |  |

|                        |                                                                       | VSUP=3V @<br>C <sub>load</sub> ≤20pF, fcL |                                        |     | 1    | 1.25  |    |  |

| I <sub>CLKEN</sub>     | Clock Enable Mode                                                     | VSUP=2.0<br>Тамв=-4085°С,<br>fclk=20N     | Cload≤20pF,                            |     | 1.25 | 1.6   | mA |  |

| I <sub>Temp_sens</sub> | Temperature sensor Current                                            | Vsup=2.03.6V,<br>Тамв=-4085°С             |                                        |     | 0.25 |       | mA |  |

| I <sub>PLLEN</sub>     | PLL Enable Mode                                                       | Vsup=2.03.6V,<br>Тамв=-4085°С             |                                        |     | 5.6  |       | mA |  |

|                        |                                                                       | VSUP=3V @ 25°C                            | without the use of                     |     | 13.5 | 16.5  | mA |  |

| ITX8dBm <sub>31</sub>  | Transmit Mode @ 8dBm output<br>power,<br>315 MHz band @ 50Ω including | VSUP=2.03.6V,<br>TAMB=-4085°C             | the internal regulator <sup>1</sup>    |     | 15.5 | 19    | mA |  |

| 5                      | matching network, strong AB                                           | VSUP=3V @ 25°C                            | with the use of the                    |     | 14.0 | 17.0  | mA |  |

|                        | operation                                                             | VSUP=2.23.6V,<br>Tamb=-4085°C             | internal regulator                     |     | 16.0 | 19.5  | mA |  |

|                        |                                                                       | VSUP=3V @ 25°C                            | without the use of                     |     | 12.5 | 15.5  | mA |  |

| ITX8dBm <sub>43</sub>  | Transmit Mode @ 8dBm output<br>power,<br>422 MUz band @ 500 including | VSUP=2.03.6V,<br>Tamb=-4085°C             | the internal regulator                 |     | 14.5 | 18    | mA |  |

| 3                      | matching network, strong AB                                           | VSUP=3V @ 25°C                            |                                        |     | 13.0 | 16.0  | mA |  |

|                        | operation                                                             | VSUP=2.23.6V,<br>TAMB=-4085°C             | with the use of the internal regulator |     | 15   | 18.5  | mA |  |

### Table 16. Current Consumption

| Symbol                | Parameter                                                                                                                                                                                  | Conditio                               | Min                    | Тур  | Мах  | Units |    |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------|------|------|-------|----|

|                       |                                                                                                                                                                                            | VSUP=3V @ 25°C                         | without the use of     |      | 14.5 | 17.5  | mA |

| ITX4dBm <sub>86</sub> | X4dBm <sub>86</sub> 868 MHz and 906MHz band @     VSUP=2.03.0V,<br>TAMB=-4085°C     rec       8     50Ω including matching<br>network, strong AB operation     VSUP=3V @ 25°C     with the | 1001 2.00.01                           | the internal regulator |      | 16.5 | 19.0  | mA |

| 8                     |                                                                                                                                                                                            | VSUP=3V @ 25°C                         | with the use of the    |      | 15.0 | 18.0  | mA |

|                       |                                                                                                                                                                                            | with the use of the internal regulator |                        | 17.0 | 19.5 | mA    |    |

1. Power line matching needs to be adjusted to VDD to ensure strong AB operation mode

Table 17. DC/AC Characteristics for Digital Interface

| Symbol         | Parameter                                                                       | Conditions                                       | Min                   | Тур       | Мах            | Units      |

|----------------|---------------------------------------------------------------------------------|--------------------------------------------------|-----------------------|-----------|----------------|------------|

| CMOS Inpu      | ut                                                                              |                                                  |                       |           |                |            |

| Viн            | High Level Input Voltage                                                        |                                                  | 0.7 *<br>Vsup         |           | VSUP +<br>0.1  | V          |

| Vil            | Low Level Input Voltage                                                         |                                                  | V <sub>GND</sub> -0.1 |           | 0.3 * VSUP     | V          |

| lı∟            | Low Level Input Leakage Current                                                 | no internal pull up/down                         |                       |           | ±1             | μA         |

| Ін             | High Level Input Leakage Current                                                | no internal pull up/down                         |                       |           | ±1             | μA         |

| lihpd          | High Level Input Leakage Current with<br>internal pull down                     | VSUP=3.6V, VIN=3.6V                              | 15                    |           | 60             | μA         |

|                | ne following specification is valid for the D rengths according MCCDS register. | ATAIO standard CMOS output. The MCCL             | K output can          | be progra | mmed to differ | ent driver |

|                |                                                                                 | ATAIO standard CMOS output. The MCCL             | K output can          | be progra | mmed to differ | ent driver |

| Voн            | High level output voltage                                                       | VSUP=3V, at nominal high level output<br>current | VSUP-0.5              |           |                | V          |

| Vol            | Low level output voltage                                                        | VSUP=3V, at nominal low level output<br>current  |                       |           | Vss+0.4        | V          |

| CL             | Capacitive load                                                                 |                                                  |                       |           | 20             | pF         |

| t <sub>R</sub> | Rise time                                                                       |                                                  |                       |           | 50             | ns         |

| t <sub>F</sub> | Fall time                                                                       |                                                  |                       |           | 50             | ns         |

| ЮН             | High level output current                                                       |                                                  |                       |           | 1              | mA         |

| lol            | Low level output current                                                        |                                                  |                       |           | 1              | mA         |

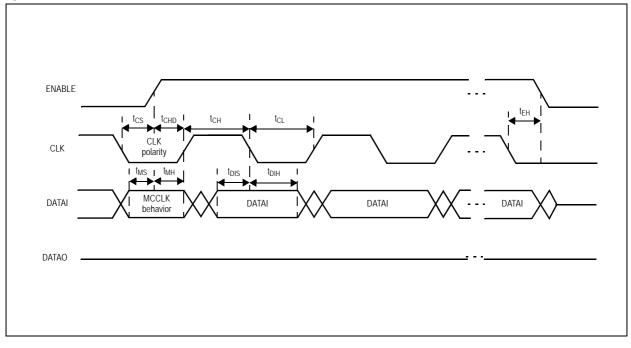

# 7 Timing Characteristics

Be aware that the Power Down Mode can be entered by setting ENABLE low for more than 2<sup>16</sup> XTAL cycles (Power Down Timer).

Figure 3. Write Data

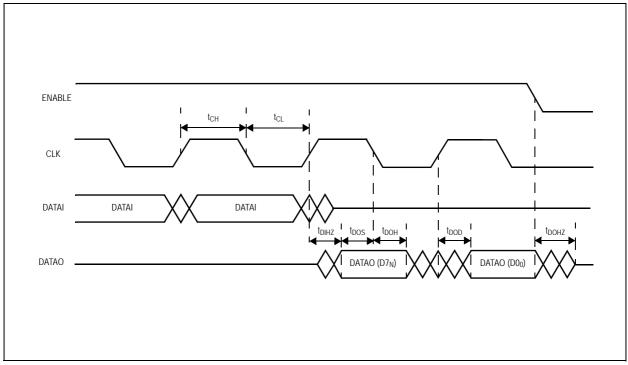

Figure 4. Read Data

# 7.1 Timing Parameters

Table 18. Timing Parameters

| Symbol            | Parameter                              | Condition                                               | Min       | Тур  | Max | Units |

|-------------------|----------------------------------------|---------------------------------------------------------|-----------|------|-----|-------|

| General           |                                        |                                                         |           |      |     |       |

| BR <sub>SDI</sub> | Bit rate                               |                                                         |           |      | 2   | Mbps  |

| tсн               | Clock high time                        |                                                         | 250       |      |     | ns    |

| tCL               | Clock low time                         |                                                         | 250       |      |     | ns    |

| Write timing      |                                        |                                                         |           |      |     |       |

| t <sub>DIS</sub>  | Data in setup time                     |                                                         | 20        |      |     | ns    |

| t <sub>DIH</sub>  | Data in hold time                      |                                                         | 10        |      |     | ns    |

| t <sub>EH</sub>   | Enable hold time                       |                                                         | 20        |      |     | ns    |

| Read timing       |                                        |                                                         |           | •    |     | •     |

| t <sub>DIHZ</sub> | Data in to high impedance delay        | time for the $\mu C$ to release the DATAIO bus          |           |      | 45  | ns    |

| t <sub>DOS</sub>  | Data out setup time                    |                                                         | 130       |      |     | ns    |

| t <sub>DOH</sub>  | Data out hold time                     |                                                         | 135       |      |     | ns    |

| t <sub>DOD</sub>  | Data out delay                         |                                                         |           |      | 80  | ns    |

| t <sub>DOHZ</sub> | Data out to high impedance delay       | time for the SDI to release the DATAIO bus              |           |      | 80  | ns    |

| Timing param      | neters when leaving the Power Down Mod | e (for determination of CLK polarity and MC             | CLK behav | ior) |     | •     |

| tcs               | Clock setup time<br>(CLK polarity)     | Setup time of CLK with respect to<br>ENABLE rising edge | 20        |      |     | ns    |

| t <sub>CHD</sub>  | Clock hold time<br>(CLK polarity)      | Hold time of CLK with respect to ENABLE rising edge     | 20        |      |     | ns    |

| t <sub>MS</sub>   | Data in setup time<br>(MCCLK behavior) | DATAIO setup time with respect to<br>ENABLE rising edge | 20        |      |     | ns    |

| t <sub>MH</sub>   | Data in hold time<br>(MCCLK behavior)  | DATAIO hold time with respect to<br>ENABLE rising edge  | 20        |      |     | ns    |

# 8 Detailed System Description

The AS3977 is based on a fully integrated sigma-delta controlled fractional-N synthesizer phase locked loop (PLL) and a power amplifier (PA). A reference frequency generator including a crystal oscillator provides the comparison frequency of the PLL and a high-precision clock output. A programmable Gaussian filter enables to minimize the occupied bandwidth and adjacent channel power. A temperature sensor with digital readout is included that allows compensation of the crystal frequency drift due to temperature variation. An on-chip low drop out regulator (LDO) is available in case an accurate output power independent of supply voltage variation is required. A second LDO for the digital supply voltage helps to minimize interference between the analog and digital part and decreases the current consumption of the digital part. A PROM enables the compensation of process variation. The AS3977 is controlled by an external microcontroller via a bi-directional serial digital interface (SDI).

# 8.1 Reference Frequency Generator

The reference frequency generator consists of a crystal oscillator and frequency divider. The crystal oscillator can be driven externally in case an external clock frequency is supplied.

# 8.2 Phase Locked Loop

The PLL is of standard charge pump type. The phase frequency detector is designed such that dead zone problems are avoided. The charge pump current is programmable. All loop filter components are on-chip, the bandwidth is programmable through the charge pump current. The differential based voltage controlled oscillator (VCO) has integrated inductors and varactors. The VCO operates at a center frequency around 1.8GHz. To cover the specified frequency range over process variation, the sufficiently wide overall tuning range is split into 16 overlapping frequency bands. At start up of the PLL, an automatic range select circuit (ARS) selects the proper frequency band. The VCO output frequency is divided by 2, 4, and 6, which enables to cover output frequencies in the range of 850 – 928 MHZ, 425 – 450 MHz and 300 – 320 MHz, respectively. A lock detector enables to monitor the PLL lock status.

# 8.3 Gaussian Filter and Digital Modulator

The programmable sigma-delta modulator controls the output frequency of the PLL. The order of the modulator is programmable (MASH2 or MASH3). In combination with the programmable Gaussian filter for the data signal, the modulator performs the FSK modulation with programmable deviation, whereby the Gaussian Filter enables to minimize the occupied bandwidth and the adjacent channel power.

# 8.4 Power Amplifier

The power amplifier is single ended and consists of a preamplifier and an output stage, both with open collector. The necessary external chokes can be connected to a LDO in case an accurate output power independent of supply voltage variation is required. The output power is programmable up to 10dBm.

## 8.5 Temperature Sensor

The AS3977 includes a temperature sensor to measure the absolute temperature inside the chip. The analog value is converted to a digital value and can then be read out by the microcontroller in order to control the output frequency and/or the transmission power. The value of the chip temperature in degree can be obtained using following formula:

Temperature =

$$TS < 9...0 > * 0.19 - 50$$

(EQ 1)

The temperature sensor can be used to compensate the crystal drift over temperature.

**Note:** AS3977 has the same temperature than the crystal only at start up and the temperature will increase immediately thereafter due to self heating.

Temperature sensor must be used only in the Clock Enable Mode as a stand alone block. It is mandatory to be used with the PLL and Power Amplifier switched off.

## 8.6 Low Power Reset

The low power reset (LPR) disables the power amplifier, if the supply voltage falls below the low power threshold.

## 8.7 Low Drop Out Regulators

In order to avoid stability issues, external capacitors are required. (see Table 1)

# 8.8 SDI / Control Interface

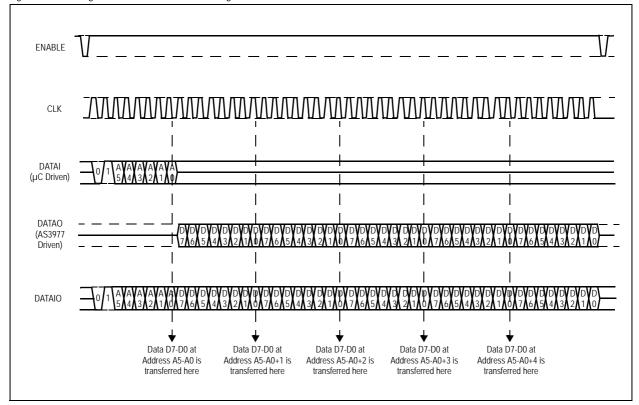

This interface enables a serial and synchronous communication between external microcontroller and AS3977. Data can be written to and read out from AS3977. Additionally, it facilitates the transmission of TX-data. The rising edge on the SDI enable signal (transition to the active state), while the device is in Power Down Mode has various effects on the circuit:

- It wakes up the crystal oscillator (this takes maximum 1.5 ms with the specified Crystal parameters)

- It sets the transfer and sampling edge of the AS3977 SDI data signal.

- It activates the Micro Controller clock output depending on the register setting and the value of the data signal.

Thus, the wakeup event through the SDI interface determines the basic communication between AS3977 and the microcontroller. In addition it takes some time to have a stable crystal oscillator clock available. Therefore all functions that require a stable crystal oscillator clock are not immediately available after the wakeup.

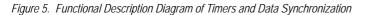

## 8.9 Baud Rate Generator

This module generates two clocks; one used for the microcontroller (MCCLK) and one as baud rate clock with 50% duty cycle. The baud rate clock is used by the microcontroller to properly synchronize the provided data during transmission with the internal Manchester coder.

The baud rate generator maintains the behavior of MCCLK and keeps it properly synchronized to the TX data clock. For example, a missing synchronization can occur when clock settings are changed by an asynchronous event like SDI programming or when a new transmission starts.

The Baud rate generator offers different types of data outputs: one fully asynchronous, one synchronous and one synchronous but Manchester coded. By means of AS3977 command control Byte, any of the three different output data types can be selected.

# 9 Application Information

The Prescaler divides the XTAL frequency by  $f_{OUT} {=} 2^{\cdot PSC {<} 2:0{>} *} f_{IN}$

The Compare timer divides by  $f_{OUT}=f_{IN}/(TCV+1)$  and the Postscaler divides the input frequency by  $f_{OUT}=2^{-ASC<1:0>*}f_{IN}$  which leads into a data frequency of:

$$f_{OUT=2}^{(PSC<2:0>+ASC<1:0>+1)} f_{IN} / (TCV+1)$$

(EQ 2)

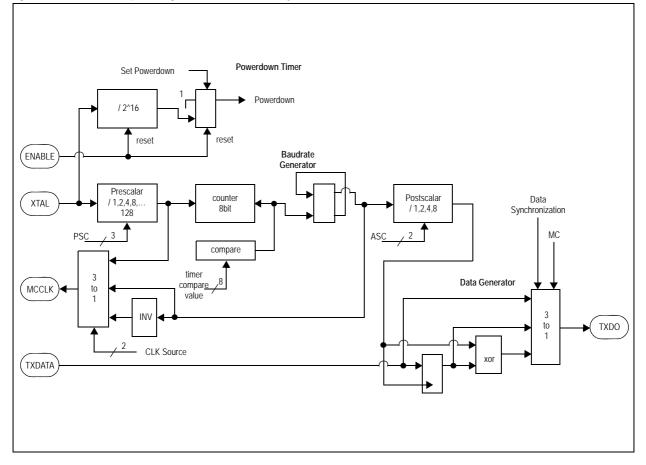

# 9.1 Operation Modes

All modes are controlled by the SDI interface.

Power Down Mode

The AS3977 is connected to the power supply and can be switched to power down mode. The current consumption is limited by the leakage current.

Clock Enable Mode

In this mode, only the reference frequency generator is switched on and a clock signal is supplied via the clock output.

PLL Enable Mode

The PLL is switched on and locked at the selected output frequency. The power amplifier is in power down mode. This mode enables OOK-ASK modulation by switching the PA on and off.

Transmit Mode

The PLL is switched on and locked at the selected output frequency. The power amplifier is in power on mode. This is the FSK mode for transmitting data.

AS3977

Data Sheet - Application Information

austriamicrosystems

Figure 6. Operation Mode Relations

## 9.2 Transmitter Control Interface

The AS3977 is controlled by an external micro controller (µC) via. a bi-directional communication interface (serial digital interface, SDI). The SDI enables data to be read from and written to internal control registers without the necessity of an internal clock signal. Analog de-bouncing of clock and data input is implemented in order to improve the overall system reliability.

The SDI-control interface includes a state machine, which expects a command control word as first byte and in reference to this byte, the interface is configured as write, read, or transmit operation. This method enables an effective and easy control of basic transmitter functions. Four preset independent output frequencies and two preset independent output power levels and modulation types can be selected using the control-command byte, thus enabling fast channel hopping and/or fast changes to the output power level and modulation type. The selection of the active output frequency and/or power level and modulation type is done using the so-called command byte.

As an additional feature, the AS3977 provides a configurable clock signal derived from the crystal frequency. The purpose of this clock signal is to provide a µC clock and to enable data synchronization.

A timer is included to power down (Power Down Mode) the transmitter after a certain time, which is defined as 2<sup>16</sup> multiplied with the crystal oscillator- Period.

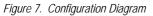

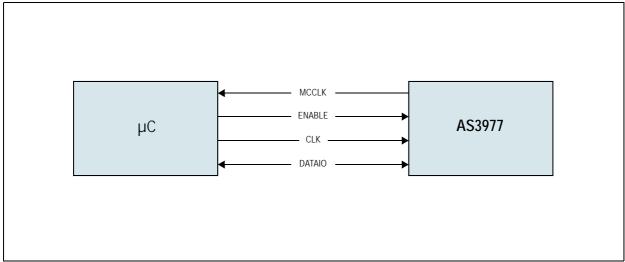

## 9.2.1 Configuration Diagram

The interface has one clock signal for the external  $\mu$ C and the SDI input clock. As the MCCLK line can be used to clock the SDI Interface as well as must have a high impedance pin during the clocking phase of the microcontroller, the Pin must be bi-directional. The pad behavior is selected by configuration bits and by setting the SDI DATA-IO Line of the SDI interface when leaving PD. Possible configurations between the interface and the  $\mu$ C are done using 4 wires as shown in Figure 7.

MCCLK is simply connected to the micro controller and can be used to clock a timer or interrupt logic.

A connection using a set of three wires is required to implement the SDI protocol.

- ENABLE signal is used to activate the interface and to wake up the whole IC. In addition, the rising edge of the ENABLE after power down mode is used to set the starting point of the communication protocol.

- CLK represents the SDI clock and both edges can be used for data transfer, dependable on the configuration after wake-up.

- DATAIO is a bi-directional signal that goes from microcontroller to the Interface during write and transmit-commands, while it is in the other direction when the interface is sending data read from the micro controller.

The interface supports the following functionality for the micro controller clock output (MCCLK).

- MCCLK can be inactive (MCCLK level not defined), always active after start-up (MCCLK is clocking) or clocking only during transmit.

- It is possible to configure and to maintain MCCLK settings (even when leaving PD).

- Maximum frequency is specified to f<sub>XOSC</sub> (by using the prescaler output with a division ratio of 1, PSC=0).

- Minimum frequency is f<sub>XOSC</sub> / 65280 (by using the baud rate generator output with prescaler division ratio of 128 and timer counter value of 255).

The rising edge of ENABLE after a Power Down Mode selects the transfer edge of the SDI-CLK by sampling the SDI clock value itself. This configuration will be valid until the next PD. Each bit must be transferred and sampled according to the configured edges. For example, if at the first rising edge of SDI enable SDI clock is LOW, then each bit is transferred from the microcontroller on the rising edge of SDI clock and it is sampled from AS3977 on falling edge of the SDI clock. This is valid for read as well as for write commands.

During the first byte of the WRITE command communication (command and address), the SDI master drives each new data bit on the transfer active edge and the SDI slave samples it on the next opposite edge. This protocol will be valid until the last data bit has been written to the external registers. Data' are transferred to the registers byte by byte after sampling of the last bit.

It is not necessary to enter the PD mode for reset the Interface. The rising edge of SDI-ENABLE signal starts the communication.

When the command is READ, a direction change on the SDI data wire will be done. This change has to be performed synchronously on SDI master and slave side, however, the master always provide the SDI clock. After sampling the last addressed bit, the SDI slave pin becomes active on the following SDI clock edge and the first readable bit read is transferred from SDI slave to the master.

In any case, the SDI master has to reset the SDI interface on the last bit of the data in order to stop the communication by applying an Enable

LOW pulse (duration: min > 1 SDI CLK cycle, max: < 1/f<sub>crystal</sub> \* 2<sup>16</sup>).

Revision 3.6

## 9.2.2 Power On Reset

For stable start up of the AS3977 and to avoid unwanted crystal oscillation, it is strongly recommended to perform a power on reset (Hardware Reset Method). This can be performed as described in Table 19 and must be carried out every time when the supply voltage is less than the minimum allowed value (see Operating Conditions on page 8).

Table 19. Power On Reset

| Step                                                                        | Hardware Reset Method                             |  |  |  |

|-----------------------------------------------------------------------------|---------------------------------------------------|--|--|--|

| 1                                                                           | Apply Power to the AS3977                         |  |  |  |

| 2                                                                           | Apply Enable high pulse (Low-High-Low transition) |  |  |  |

| 3 Power on reset complete after xtal start up + 2 <sup>16</sup> xtal cycles |                                                   |  |  |  |

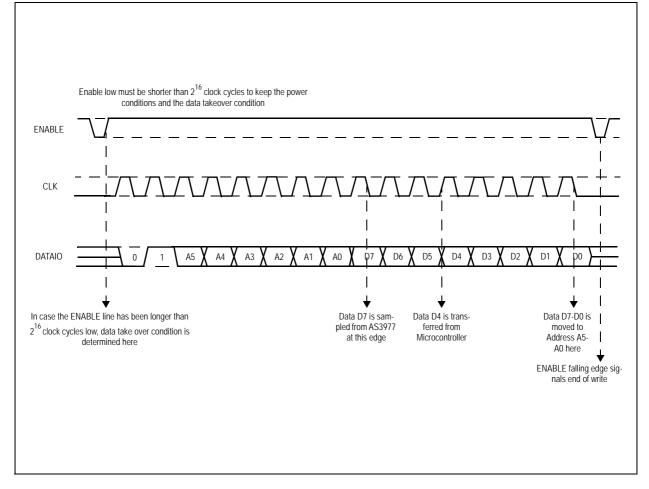

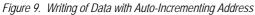

#### 9.2.3 Writing of Data to Addressable Registers

When the Power Down Mode is left, the level of CLK at the rising edge of ENABLE determines the sampling edge of CLK. If CLK is low, when ENABLE rises, DATAI is sampled at the falling edge of CLK (see Figure 8 and Figure 9), if CLK is high when ENABLE rises, DATAI is sampled at the rising edge of CLK.

An Enable LOW pulse indicates the end of the WRITE command after register has been written.

Figure 8 illustrates a write command in which the initialization of DATAIO take over condition is done at the falling edge of CLK signal.

Figure 8. Writing of a Single Byte (falling edge sampling)

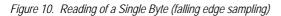

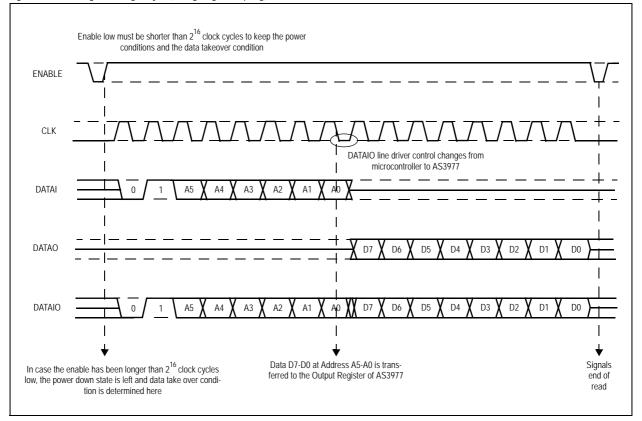

#### 9.2.4 Reading of Data from Addressable Registers

By leaving the Power Down Mode through a rising edge of ENABLE, the level of CLK determines the sampling edge of CLK. If CLK is low, DATAI is sampled at the falling edge of CLK (see Figure 10 and Figure 11), if CLK is high when ENABLE rises, DATAI is sampled at the rising edge of CLK. Consequently, data to be read from the microcontroller are driven by the slave (AS3977) at the transfer edge and sampled by the master ( $\mu$ C) at the sampling edge of CLK. An Enable LOW pulse has to be performed after register data has been transferred in order to indicate the end of the READ command and prepare the Interface to the next command control Byte.

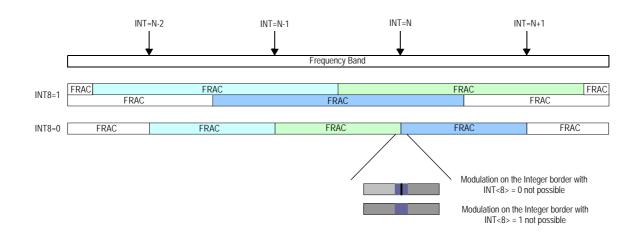

The command control Byte for a read command consists of a command code and an address. The Command code has to be provided from least significant bit (LSB) to most significant bit (MSB), e.g. for a read it is <C0, C1> = "01". After the command code, the address of register to be read has to be provided from the MSB to the LSB. Then one or more data bytes can be transferred from the SDI slave to the master, always from the MSB to the LSB. To transfer bytes from consecutive addresses, SDI master has to keep the SDI enable signal high and the SDI clock has to be active as long as data need to be read from the slave.