# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better

and more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas

Technology Corporation product best suited to the customer's application; they do not convey any

license under any intellectual property rights, or any other rights, belonging to Renesas Technology

Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

SH7708 Series

SH7708, SH7708S, SH7708R

Hardware Manual

Renesas SuperH<sup>TM</sup> RISC engine

#### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# **Preface**

The SH7708, SH7708S, and SH7708R(SH7708 Series) use a RISC (reduced instruction set computer) type CPU to achieve high-performance computational processing. Also incorporating the peripheral functions required for system configuration plus power-down features essential for microcontroller application systems, the SH7708 Series is a new-generation RISC microcontroller (SuperH<sup>TM</sup> RISC engine).

The SH7708 Series has a RISC type instruction set, with basic instructions executed in one state, offering a drastic improvement in instruction execution speed. It also has an on-chip 32-bit multiplier (producing a 64-bit result) capable of high-speed multiply-and-accumulate operations. The SH7708 Series's instructions are upward-compatible with those of the SH-1 and SH-2, facilitating migration from these series to the SH7708 Series.

SH7708R is completely pin compatible with the SH7708S. On-chip supporting modules that enable a user system to be configured with a minimum of components include oscillation circuits, an interrupt controller (INTC), timers, a realtime clock (RTC), and a serial communication interface (SCI). A user break controller (UBC) is provided as an on-chip module supporting program development, allowing easy configuration of a simple debugger.

On-chip cache memory improves CPU processing performance, and a built-in memory management unit (MMU) performs address translation between a 4-gigabyte virtual space and physical space. An on-chip bus state controller (BSC) provides more efficient external memory access, and enables direct connection to synchronous DRAM, DRAM, and pseudo-SRAM without the need for glue logic.

This hardware manual describes the hardware of the SH7708 Series. Details of instructions can be found in the programming manual.

Note: \* SuperH is a trademark of Hitachi, Ltd.

#### Related Manuals

SH7708Series instructions

SH-3/SH-3E/SH3-DSP Programming Manual

Please consult your Hitachi sales representative for details of development environment system.

# Revisions and Additions in this Edition

| Item                                              | Description                                                                         |

|---------------------------------------------------|-------------------------------------------------------------------------------------|

| 12.4.3 Usage Note about Periodic Interrupt on RTC | New section added                                                                   |

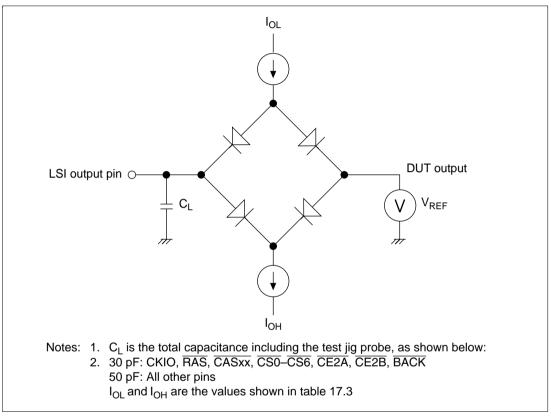

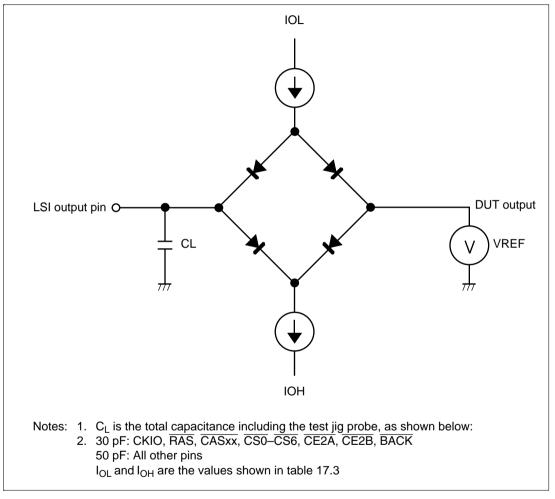

| Figure 16.65 Output Load Circuits                 | [Former Edition]                                                                    |

| Figure 17.65 Output Load Circuits                 | The mark of VRER = $\downarrow$                                                     |

|                                                   | [This Edition]                                                                      |

|                                                   | The mark of VRER = V                                                                |

|                                                   | 12.4.3 Usage Note about Periodic Interrupt on RTC Figure 16.65 Output Load Circuits |

# Contents

| Sect | ion 1           | Overview and Pin Functions             | 1  |

|------|-----------------|----------------------------------------|----|

| 1.1  | SH77            | 708 Series Features                    | 1  |

| 1.2  | 2 Block Diagram |                                        | 6  |

| 1.3  | Pin D           | escription                             | 7  |

|      | 1.3.1           | Pin Arrangement                        | 7  |

|      | 1.3.2           | SH7708 Series Pin Functions            | 8  |

| Sect | ion 2           | CPU                                    | 13 |

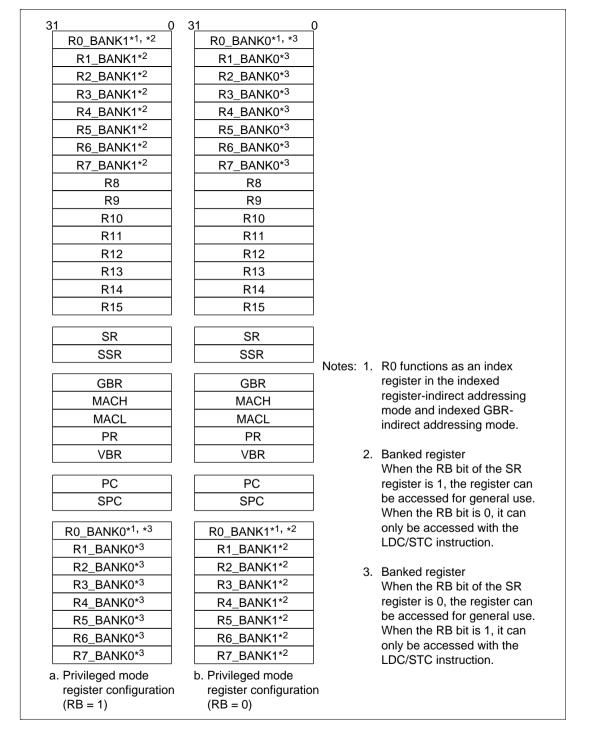

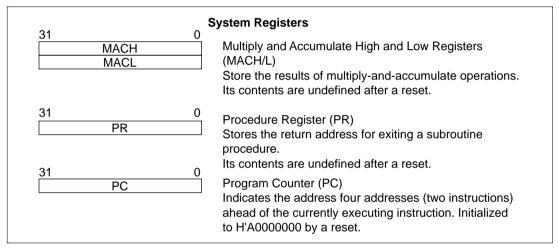

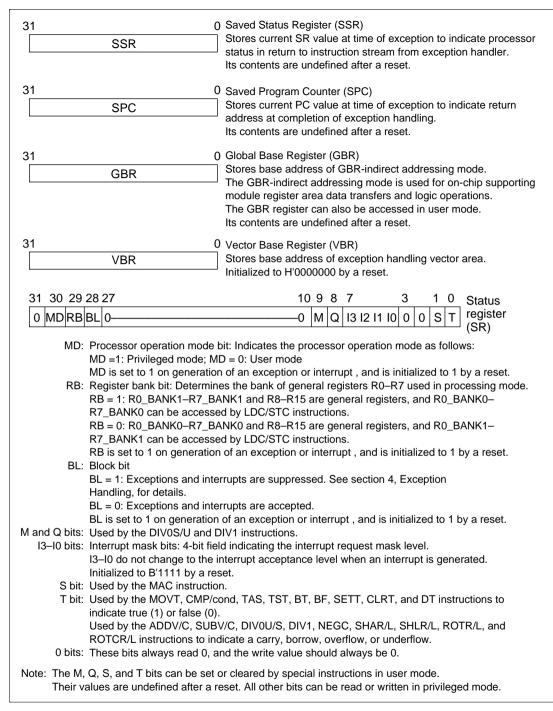

| 2.1  | Regi            | ster Configuration                     | 13 |

|      | 2.1.1           | Privileged Mode and Banks              | 13 |

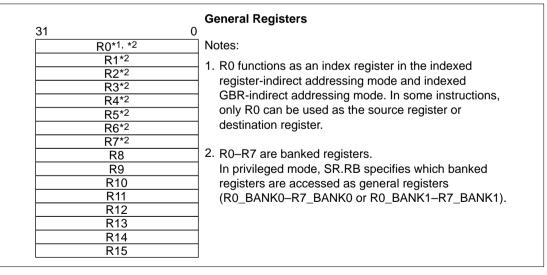

|      | 2.1.2           | General Registers                      | 16 |

|      | 2.1.3           | System Registers                       | 17 |

|      | 2.1.4           | Control Registers                      | 17 |

| 2.2  | Data l          | Formats                                | 19 |

|      | 2.2.1           | Data Format in Registers               | 19 |

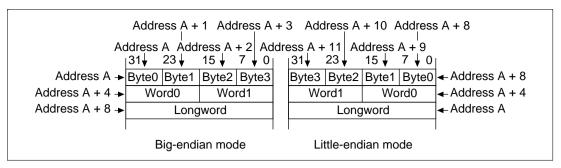

|      | 2.2.2           | Data Format in Memory                  | 19 |

| 2.3  | Instru          | ction Features                         | 20 |

|      | 2.3.1           | Execution Environment                  | 20 |

|      | 2.3.2           | Addressing Modes                       | 22 |

|      | 2.3.3           | Instruction Formats                    | 26 |

| 2.4  | Instru          | ction Set                              | 29 |

|      | 2.4.1           | Instruction Set Classified by Function | 29 |

|      | 2.4.2           | Instruction Code Map                   | 45 |

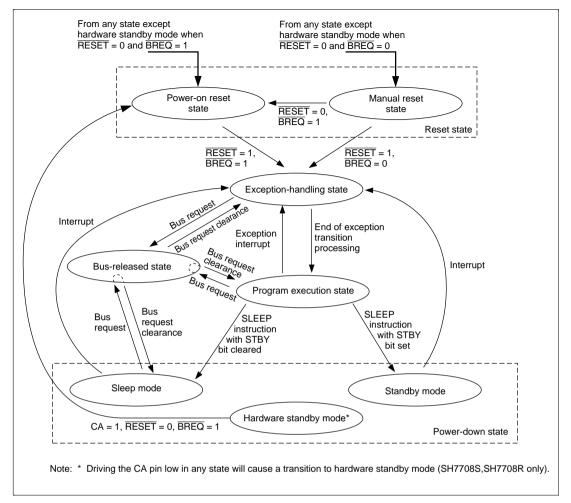

| 2.5  | Proce           | ssor States and Processor Modes        | 48 |

|      | 2.5.1           | Processor States                       | 48 |

|      | 2.5.2           | Processor Modes                        | 49 |

| 2.6  |                 | e Note                                 | 50 |

|      | _               |                                        |    |

| Sect | ion 3           | Memory Management Unit (MMU)           | 51 |

| 3.1  | Overv           | view                                   | 51 |

|      | 3.1.1           | Features                               | 51 |

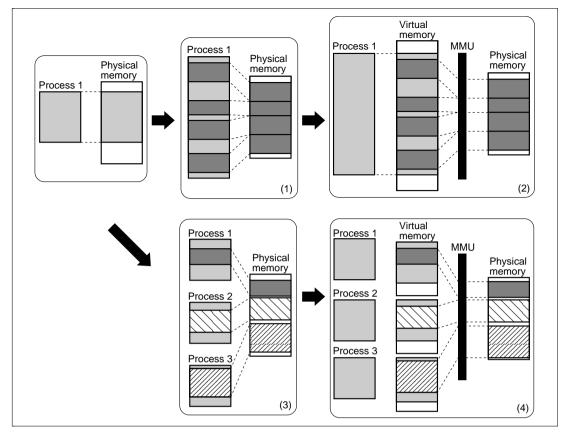

|      | 3.1.2           | Role of MMU                            | 51 |

|      | 3.1.3           | SH7708 Series MMU                      | 54 |

|      | 3.1.4           | Register Configuration                 | 57 |

| 3.2  | Regis           | ter Description                        | 58 |

| 3.3  | TLB 1           | Functions                              | 60 |

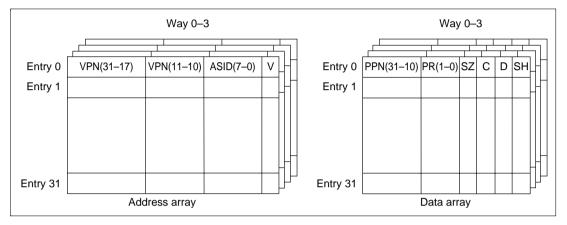

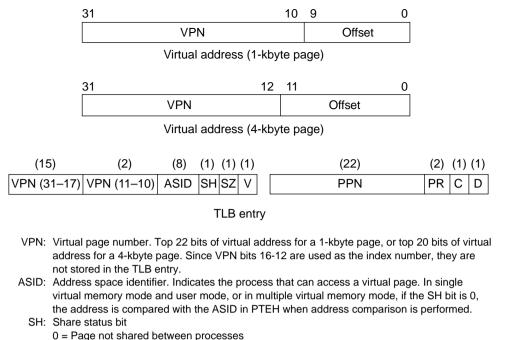

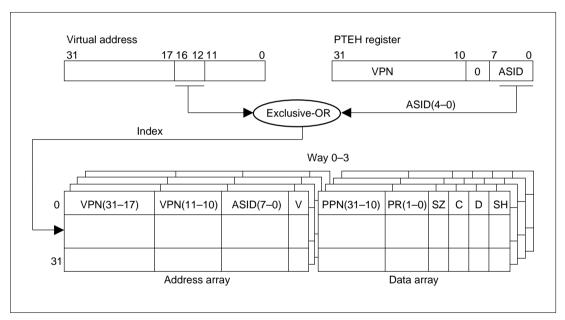

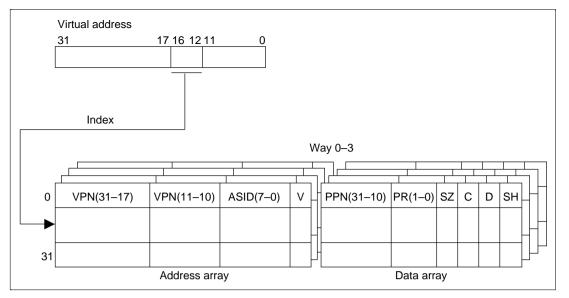

|      | 3.3.1           | Configuration of the TLB               | 60 |

|      | 3.3.2           | TLB Indexing                           | 62 |

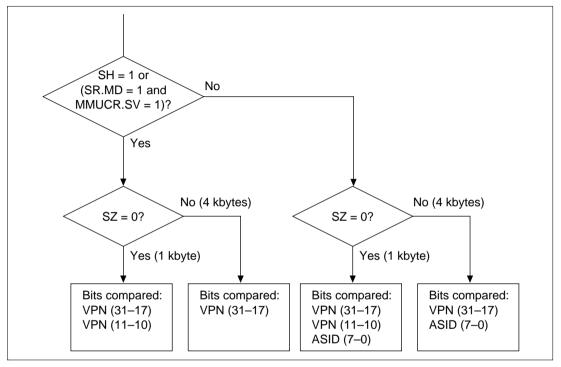

|      | 3.3.3           | TLB Address Comparison                 | 63 |

|      | 3.3.4  | Page Management Information               | 65 |

|------|--------|-------------------------------------------|----|

| 3.4  | MMU    | Functions                                 | 66 |

|      | 3.4.1  | MMU Hardware Management                   | 66 |

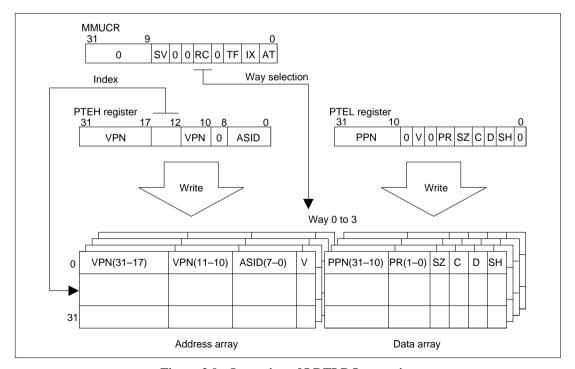

|      | 3.4.2  | MMU Software Management                   | 66 |

|      | 3.4.3  | MMU Instruction (LDLTB)                   | 67 |

|      | 3.4.4  | Avoiding Synonym Problems                 | 68 |

| 3.5  | MMU    | Exceptions                                | 70 |

|      | 3.5.1  | TLB Miss Exception                        | 70 |

|      | 3.5.2  | TLB Protection Violation Exception        | 71 |

|      | 3.5.3  | TLB Invalid Exception                     | 72 |

|      | 3.5.4  | Initial Page Write Exception              | 73 |

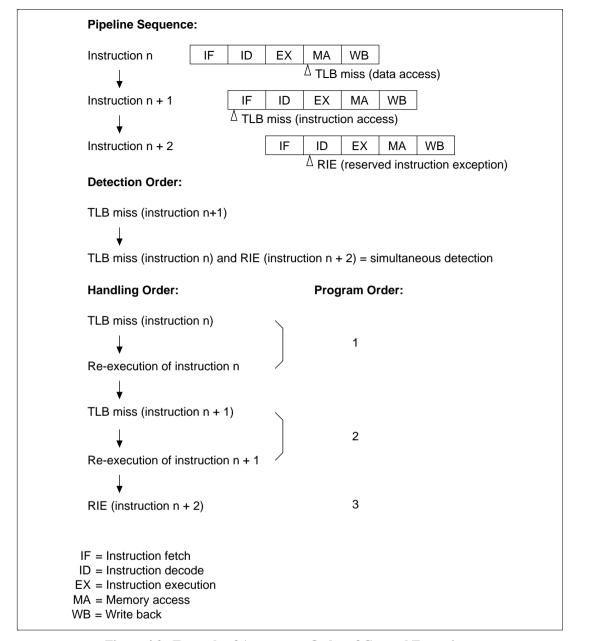

|      | 3.5.5  | Processing Flow in Event of MMU Exception |    |

|      |        | (Same Processing Flow for Address Error)  | 75 |

| 3.6  | Memo   | ory-Mapped TLB                            | 77 |

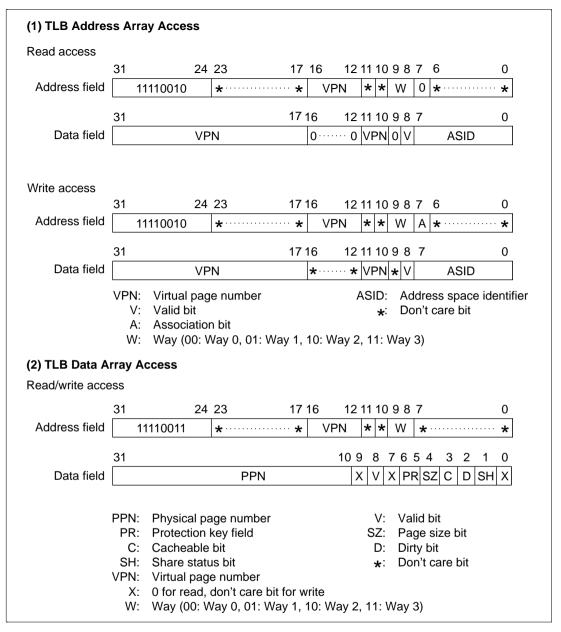

|      | 3.6.1  | Address Array                             | 77 |

|      | 3.6.2  | Data Array                                | 78 |

|      | 3.6.3  | Usage Examples                            | 80 |

| 3.7  | Usage  | Note                                      | 80 |

|      |        |                                           |    |

| Sect | ion 4  | Exception Handling                        | 81 |

| 4.1  |        | iew                                       | 81 |

|      | 4.1.1  | Features                                  | 81 |

|      | 4.1.2  | Register Configuration                    | 81 |

| 4.2  | Excep  | tion Handling Function                    | 81 |

|      | 4.2.1  | Exception Handling Flow                   | 81 |

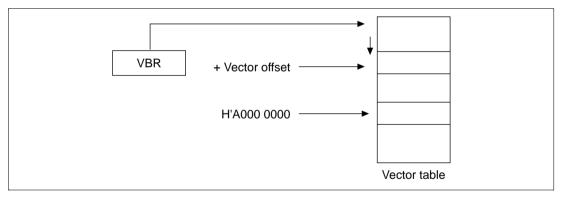

|      | 4.2.2  | Exception Handling Vector Addresses       | 82 |

|      | 4.2.3  | Acceptance of Exceptions                  | 84 |

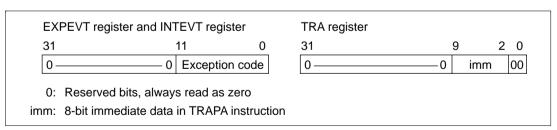

|      | 4.2.4  | Exception Codes                           | 86 |

|      | 4.2.5  | Exception Request Masks                   | 87 |

|      | 4.2.6  | Returning from Exception Handling         | 88 |

| 4.3  | Regist | er Description                            | 88 |

| 4.4  | Excep  | tion Handler Operation                    | 89 |

|      | 4.4.1  | Reset                                     | 89 |

|      | 4.4.2  | Interrupts                                | 89 |

|      | 4.4.3  | General Exceptions                        | 89 |

| 4.5  | Indivi | dual Exception Operations                 | 90 |

|      | 4.5.1  | Resets                                    | 90 |

|      | 4.5.2  | General Exceptions                        | 91 |

|      | 4.5.3  | Interrupts                                | 94 |

| 4.6  | Cautio | ons                                       | 95 |

|      |        |                                           |    |

| Sect | ion 5  | Cache                                     | 97 |

| 5.1  | Overv  | iew                                       | 97 |

| ii   |        |                                           |    |

|      | 5.1.1   | Features                                          | 9   |

|------|---------|---------------------------------------------------|-----|

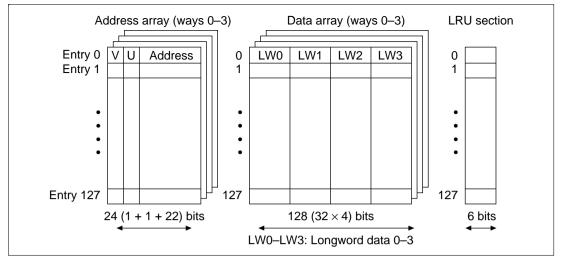

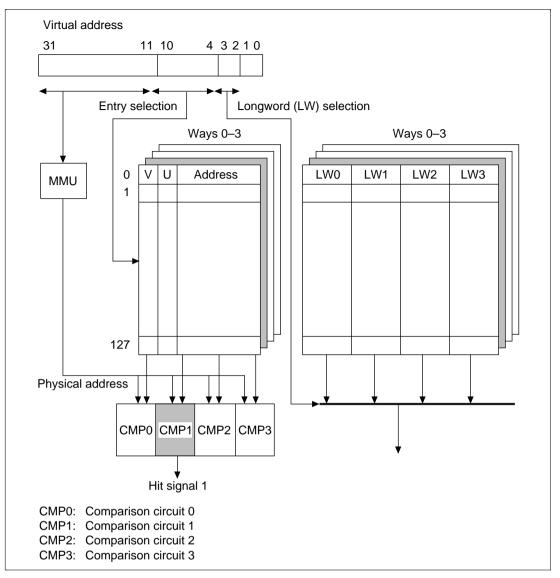

|      | 5.1.2   | Cache Structure                                   | 97  |

|      | 5.1.3   | Register Configuration                            | 99  |

| 5.2  | Regist  | er Description                                    | 99  |

|      | 5.2.1   | Cache Control Register (CCR)                      | 99  |

| 5.3  | Cache   | Operation                                         | 100 |

|      | 5.3.1   | Searching the Cache                               | 100 |

|      | 5.3.2   | Read Access                                       | 102 |

|      | 5.3.3   | Write Access                                      | 102 |

|      | 5.3.4   | Write-Back Buffer                                 | 102 |

|      | 5.3.5   | Coherency of Cache and External Memory            | 103 |

|      | 5.3.6   | RAM Mode                                          | 103 |

| 5.4  | Memo    | ry-Mapped Cache                                   | 103 |

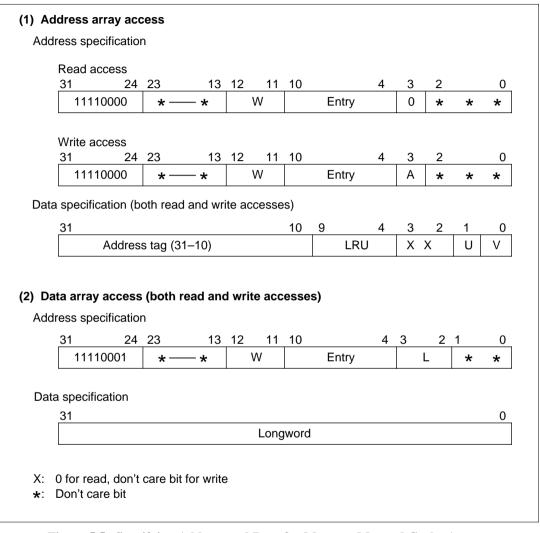

|      | 5.4.1   | Address Array                                     | 103 |

|      | 5.4.2   | Data Array                                        | 104 |

| 5.5  | Usage   | Examples                                          | 106 |

|      | 5.5.1   | Invalidating Specific Entries                     | 106 |

|      | 5.5.2   | Reading the Data of a Specific Entry              | 106 |

|      |         |                                                   |     |

| Sect |         | Interrupt Controller (INTC)                       |     |

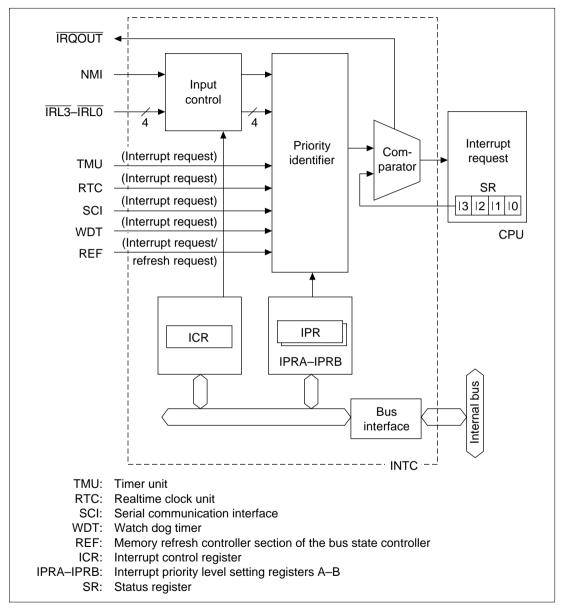

| 6.1  | Overv   | iew                                               | 107 |

|      | 6.1.1   | Features                                          |     |

|      | 6.1.2   | Block Diagram                                     | 108 |

|      | 6.1.3   | Pin Configuration                                 | 109 |

|      | 6.1.4   | Register Configuration                            | 109 |

| 6.2  | Interru | pt Sources                                        | 109 |

|      | 6.2.1   | NMI Interrupts                                    | 110 |

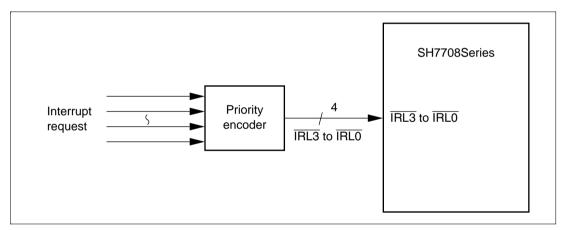

|      | 6.2.2   | IRL Interrupts                                    | 110 |

|      | 6.2.3   | On-Chip Supporting Module Interrupts              | 112 |

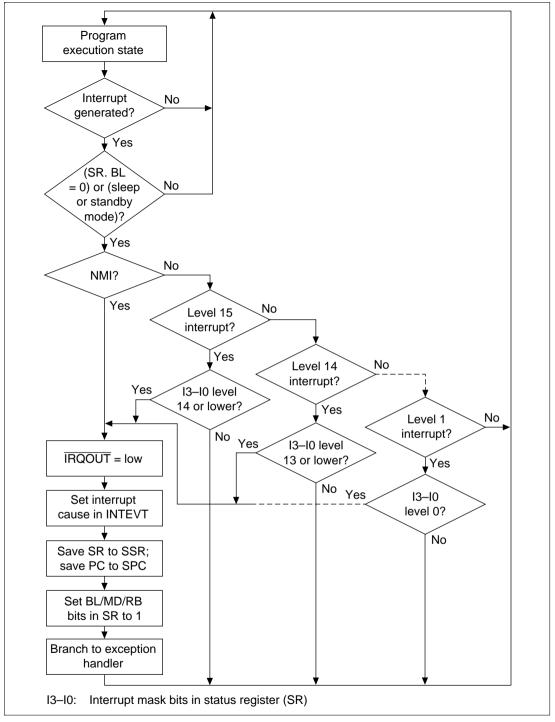

|      | 6.2.4   | Interrupt Exception Handling and Priority         | 112 |

| 6.3  | INTC    | Registers                                         | 115 |

|      | 6.3.1   | Interrupt Priority Registers A and B (IPRA, IPRB) | 115 |

|      | 6.3.2   | Interrupt Control Register (ICR)                  | 116 |

| 6.4  | INTC    | Operation                                         | 117 |

|      | 6.4.1   | Interrupt Sequence                                | 117 |

|      | 6.4.2   | Multiple Interrupts                               | 119 |

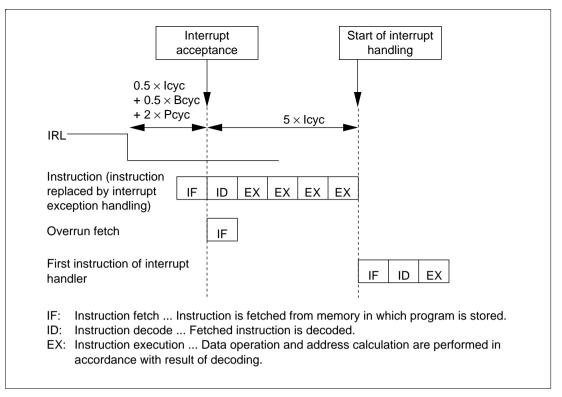

| 6.5  | Interru | ppt Response Time                                 | 120 |

|      |         |                                                   |     |

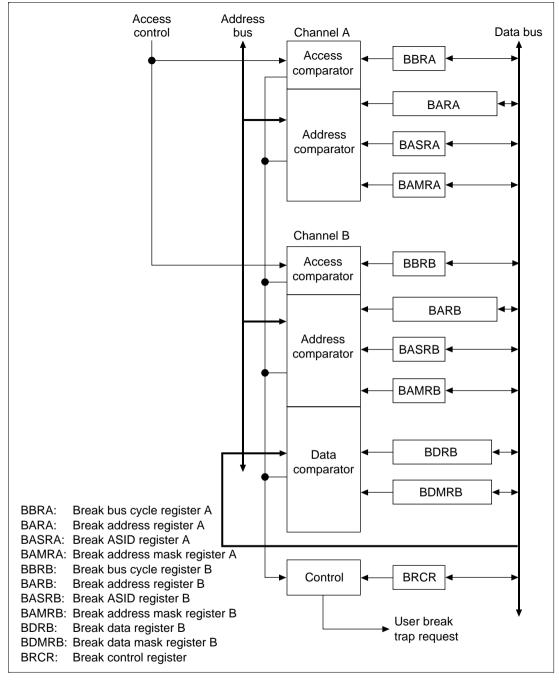

|      |         | User Break Controller (UBC)                       |     |

| 7.1  |         | iew                                               | 123 |

|      | 7.1.1   | Features                                          | 123 |

|      | 7.1.2   | Block Diagram                                     | 123 |

|      | 7.1.3   | Register Configuration                            | 125 |

|      |         |                                                   | ii  |

| 26                                                              |

|-----------------------------------------------------------------|

| 26                                                              |

| 26                                                              |

| 27                                                              |

| 27                                                              |

| 27                                                              |

| 28                                                              |

| 28                                                              |

| 29                                                              |

| 30                                                              |

| 31                                                              |

| 32                                                              |

| 34                                                              |

| 34                                                              |

| 35                                                              |

| 36                                                              |

| 37                                                              |

| 88                                                              |

| 10                                                              |

|                                                                 |

| 11                                                              |

| 11                                                              |

| 11                                                              |

| 12                                                              |

| 13                                                              |

| 13                                                              |

| 13                                                              |

| 15                                                              |

|                                                                 |

| 15                                                              |

| 15                                                              |

| 15<br>15                                                        |

| 15<br>15<br>15                                                  |

| 15<br>15<br>15<br>16                                            |

| 15<br>15<br>15<br>16<br>17                                      |

| 15<br>15<br>16<br>17                                            |

| 15<br>15<br>15<br>16<br>17<br>17                                |

| 15<br>15<br>15<br>16<br>17<br>17<br>17                          |

| 15<br>15<br>16<br>17<br>17<br>17<br>18                          |

| 15<br>15<br>16<br>17<br>17<br>17<br>18<br>18                    |

| 15<br>15<br>16<br>17<br>17<br>17<br>18<br>18<br>18              |

| 15<br>15<br>16<br>17<br>17<br>17<br>18<br>18<br>18<br>18        |

| 15<br>15<br>16<br>17<br>17<br>17<br>18<br>18<br>18              |

| 2'2'2'2'3'3'3'3'3'3'3'3'4'0'4'1'4'1'4'1'4'1'4'1'4'1'4'1'4'1'4'1 |

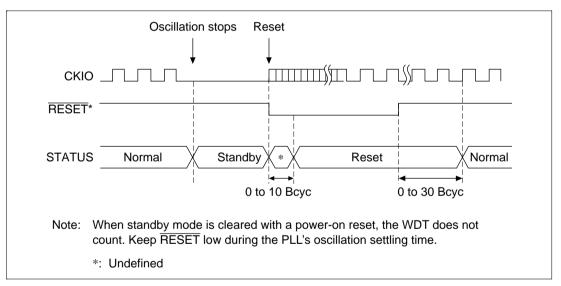

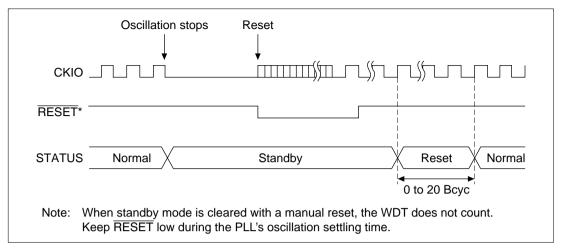

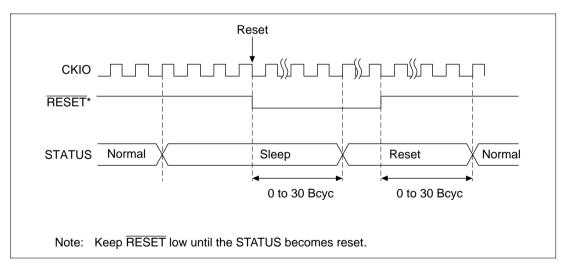

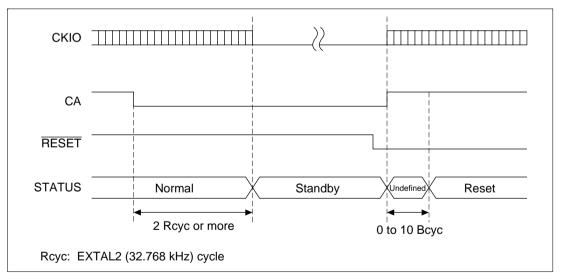

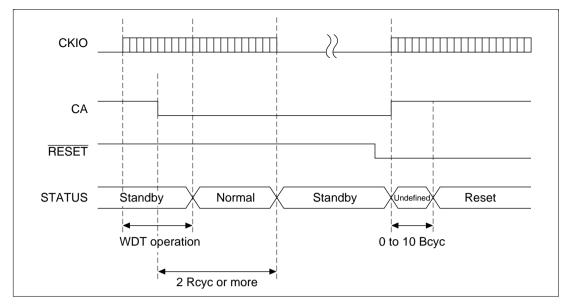

|      | 8.7.1  | Transition to Hardware Standby Mode            | 153 |

|------|--------|------------------------------------------------|-----|

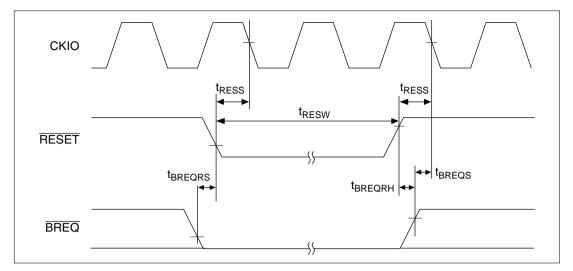

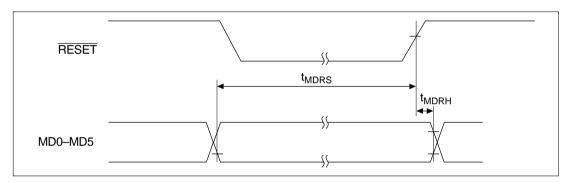

|      | 8.7.2  | Canceling Hardware Standby Mode                | 154 |

|      | 8.7.3  | Hardware Standby Mode Timing                   | 154 |

| Sect | ion 9  | On-Chip Oscillation Circuits                   | 157 |

| 9.1  |        | iew                                            |     |

|      | 9.1.1  | Features                                       | 157 |

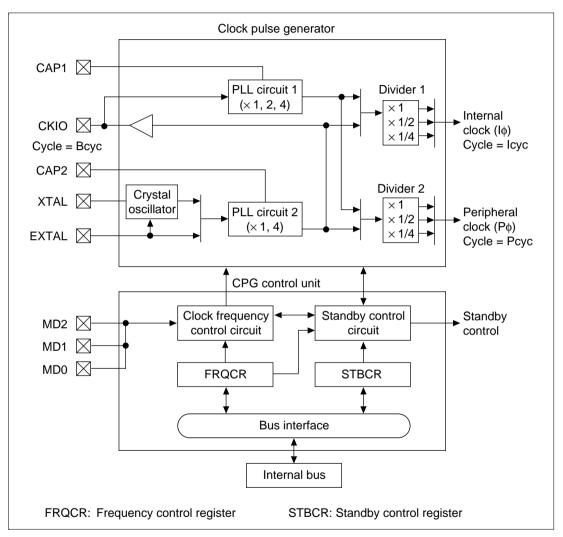

| 9.2  | Overv  | iew of the CPG                                 | 158 |

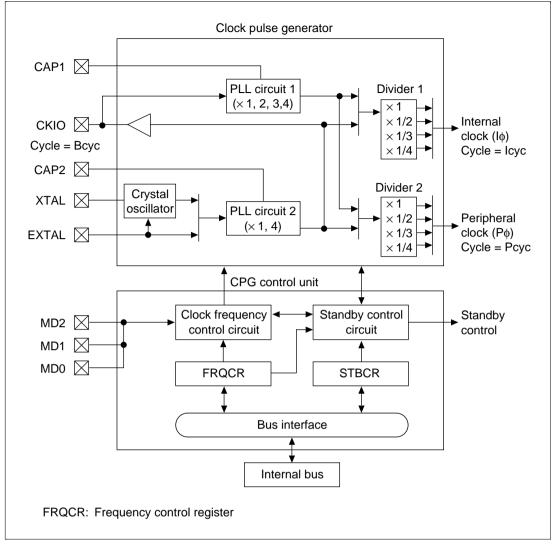

|      | 9.2.1  | CPG Block Diagram                              | 158 |

|      | 9.2.2  | CPG Pin Configuration                          | 161 |

|      | 9.2.3  | CPG Register Configuration                     | 161 |

| 9.3  | Clock  | Operating Modes                                | 162 |

| 9.4  | Regist | er Descriptions                                | 170 |

|      | 9.4.1  | Frequency Control Register (FRQCR)             | 170 |

| 9.5  | Chang  | ing the Frequency                              | 174 |

|      | 9.5.1  | Changing the Multiplication Rate               | 174 |

|      | 9.5.2  | Changing the Division Ratio                    | 174 |

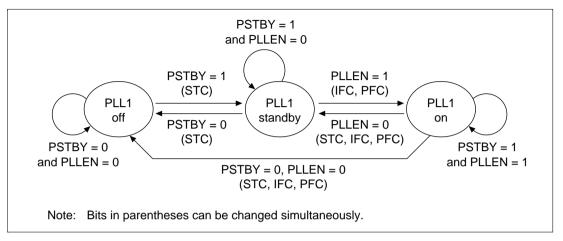

| 9.6  | PLL S  | tandby Function                                | 175 |

|      | 9.6.1  | Overview of the PLL Standby Function           | 175 |

|      | 9.6.2  | Usage                                          | 175 |

| 9.7  | Contro | olling Clock Output                            | 176 |

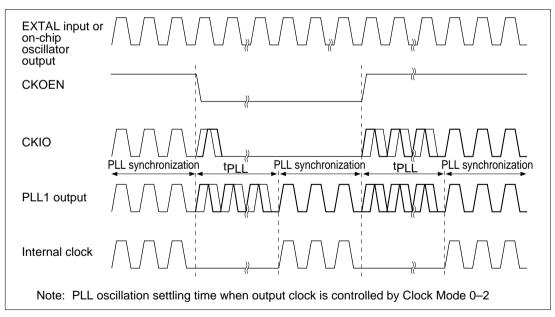

|      | 9.7.1  | Clock Modes 0–2                                | 176 |

|      | 9.7.2  | Clock Modes 3 and 4                            | 176 |

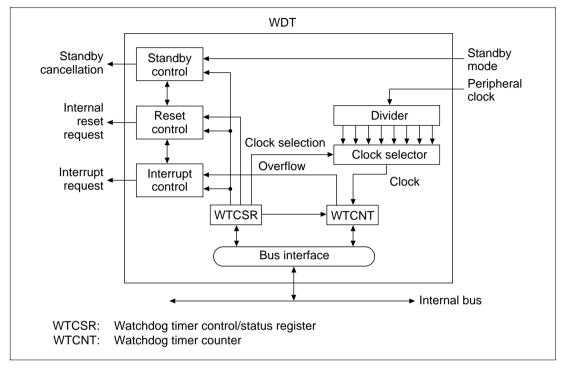

| 9.8  | Overv  | iew of the Watchdog Timer (WDT)                | 177 |

|      | 9.8.1  | Block Diagram of the WDT                       | 177 |

|      | 9.8.2  | Register Configurations                        | 177 |

| 9.9  | WDT    | Registers                                      | 178 |

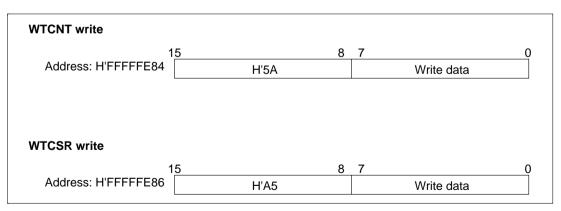

|      | 9.9.1  | Watchdog Timer Counter (WTCNT)                 | 178 |

|      | 9.9.2  | Watchdog Timer Control/Status Register (WTCSR) | 178 |

|      | 9.9.3  | Notes on Register Access                       | 180 |

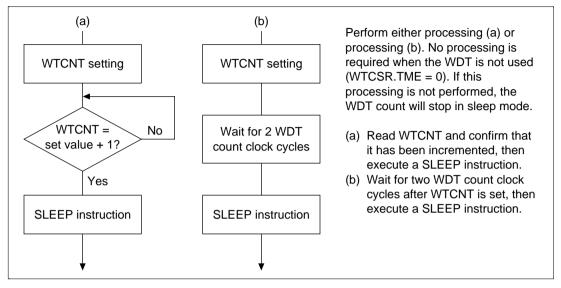

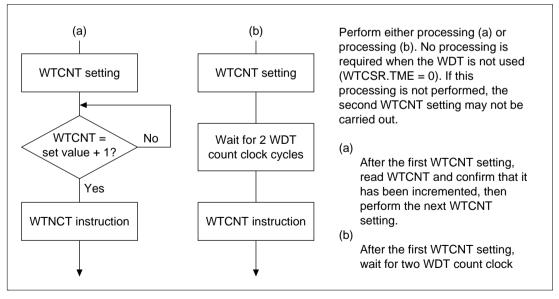

| 9.10 | Using  | the WDT                                        | 181 |

|      | 9.10.1 | Canceling Standbys                             | 181 |

|      | 9.10.2 | Changing the Frequency                         | 181 |

|      | 9.10.3 | Using Watchdog Timer Mode                      | 182 |

|      | 9.10.4 | Using Interval Timer Mode                      | 182 |

|      | 9.10.5 | Usage Notes                                    | 183 |

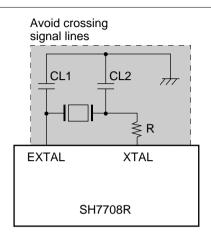

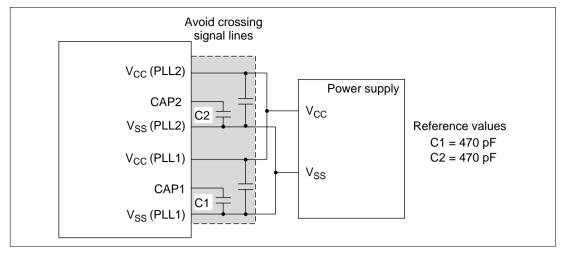

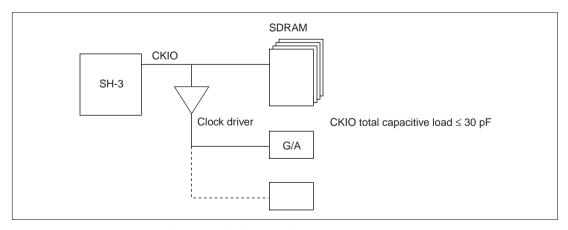

| 9.11 | Notes  | on Board Design                                | 184 |

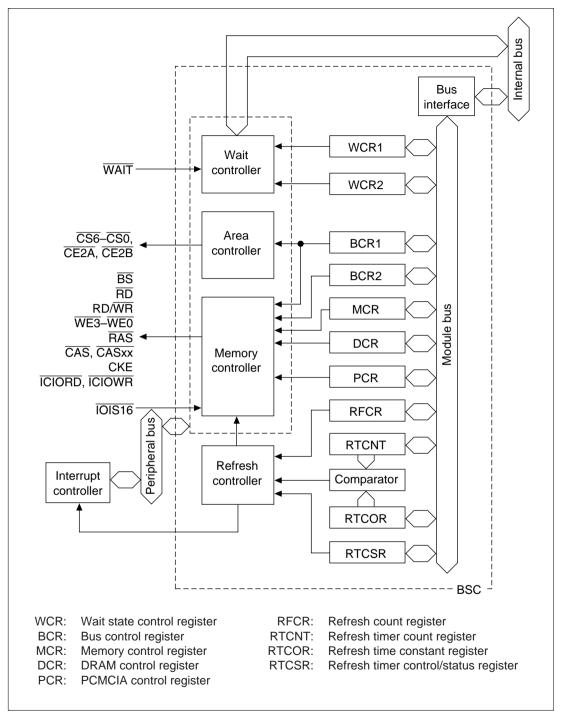

| Sect | ion 10 | Bus State Controller (BSC)                     | 187 |

| 10.1 |        | iew                                            |     |

|      | 10.1.1 | Features                                       | 187 |

|      | 10.1.2 |                                                |     |

|      | 10.1.3 | Pin Configuration                              |     |

|      |        |                                                | ٧   |

|       | 10.1.4  | Register Configuration                                        | 192 |

|-------|---------|---------------------------------------------------------------|-----|

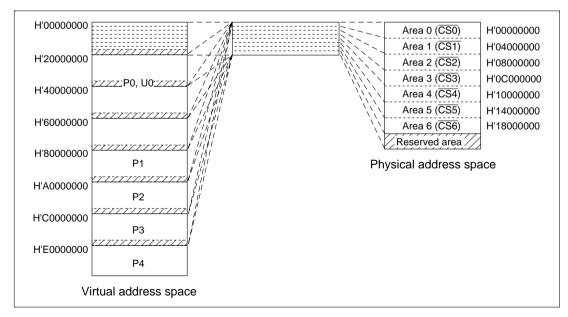

|       | 10.1.5  | Area Overview                                                 | 193 |

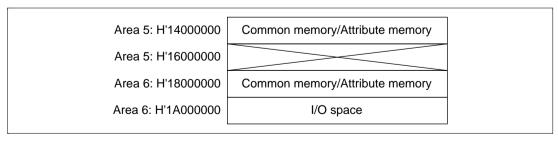

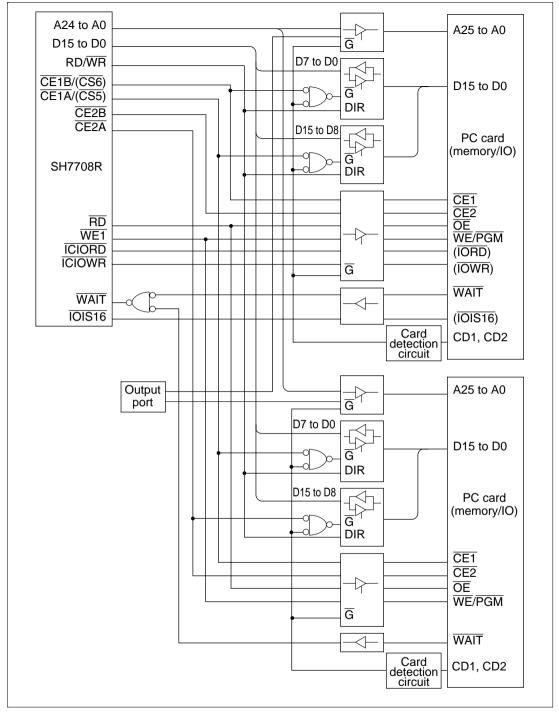

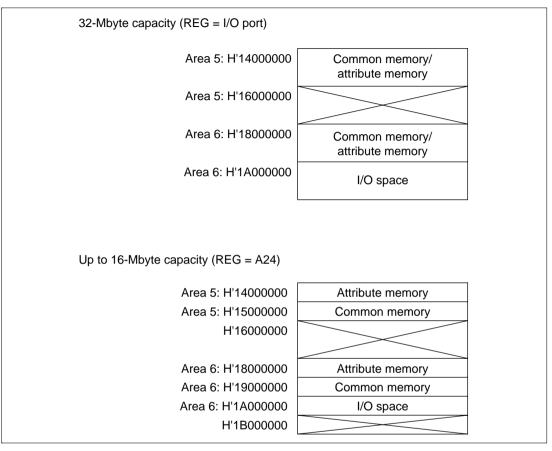

|       | 10.1.6  | PCMCIA Support                                                | 196 |

| 10.2  | BSC R   | egisters                                                      | 200 |

|       | 10.2.1  | Bus Control Register 1 (BCR1)                                 | 200 |

|       | 10.2.2  | Bus Control Register 2 (BCR2)                                 | 203 |

|       | 10.2.3  | Wait State Control Register 1 (WCR1)                          | 204 |

|       | 10.2.4  | Wait State Control Register 2 (WCR2)                          | 206 |

|       | 10.2.5  | Individual Memory Control Register (MCR)                      | 209 |

|       | 10.2.6  | DRAM Control Register (DCR)                                   | 214 |

|       | 10.2.7  | PCMCIA Control Register (PCR)                                 | 216 |

|       | 10.2.8  | Synchronous DRAM Mode Register (SDMR)                         | 217 |

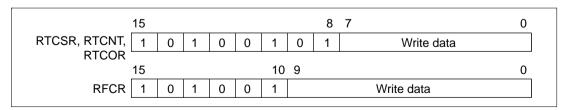

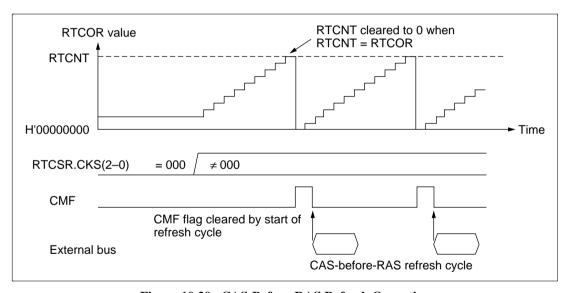

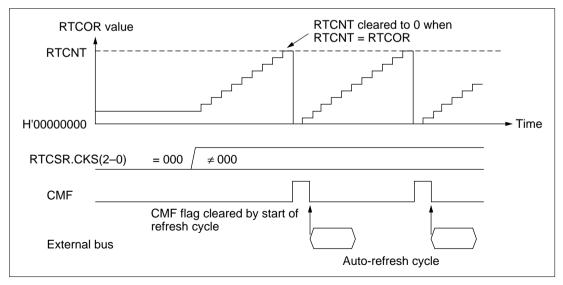

|       | 10.2.9  | Refresh Timer Control/Status Register (RTCSR)                 | 218 |

|       | 10.2.10 | Refresh Timer Counter (RTCNT)                                 | 220 |

|       | 10.2.11 | Refresh Time Constant Register (RTCOR)                        | 221 |

|       | 10.2.12 | Refresh Count Register (RFCR)                                 | 221 |

|       | 10.2.13 | Cautions on Accessing Refresh Control Related Registers       | 222 |

| 10.3  | BSC O   | peration                                                      | 223 |

|       | 10.3.1  | Endian/Access Size and Data Alignment                         | 223 |

|       | 10.3.2  | Description of Areas                                          | 229 |

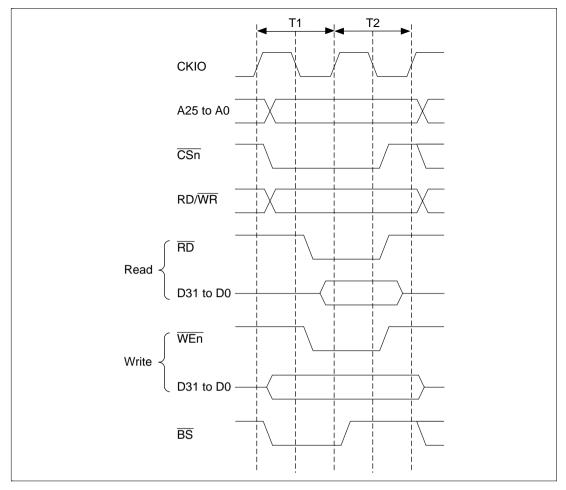

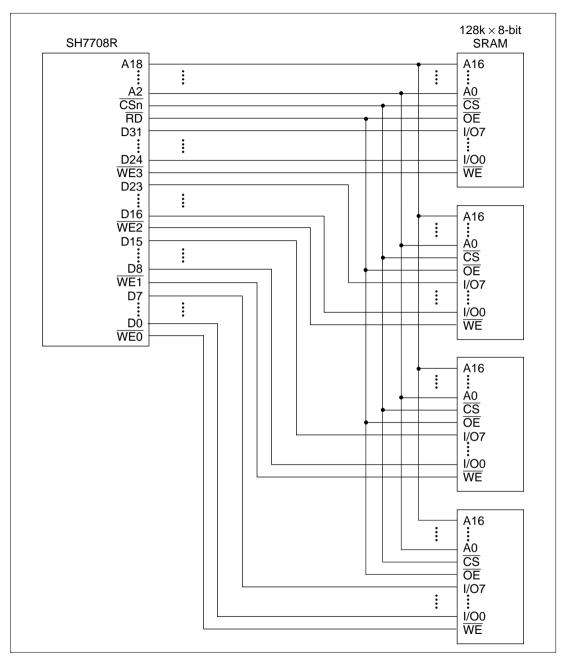

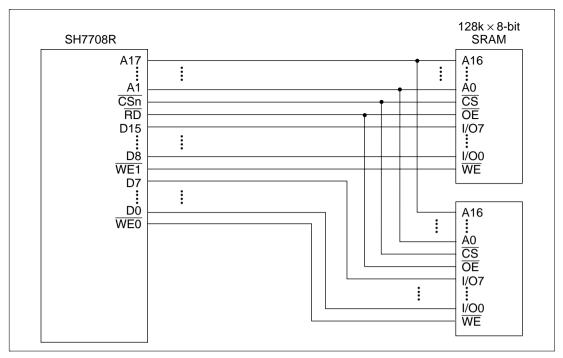

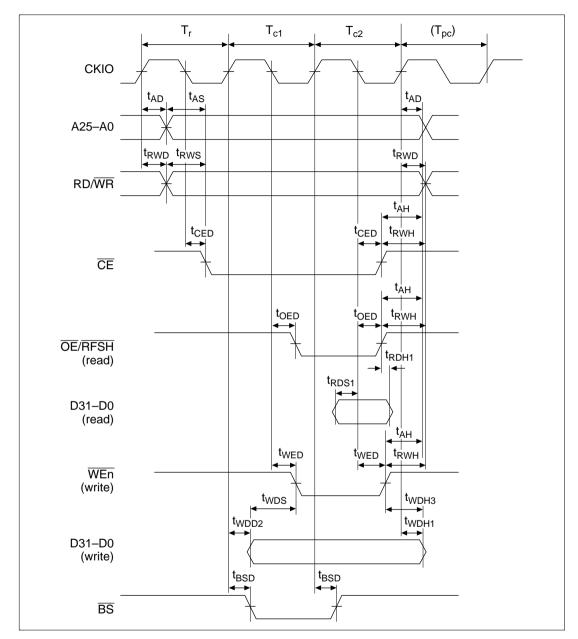

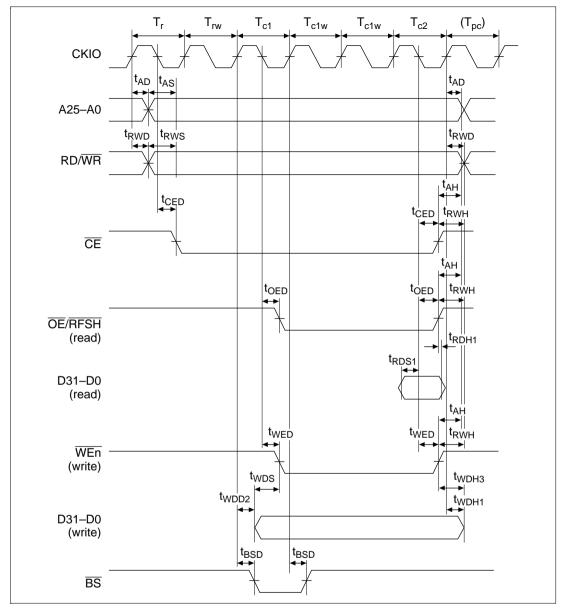

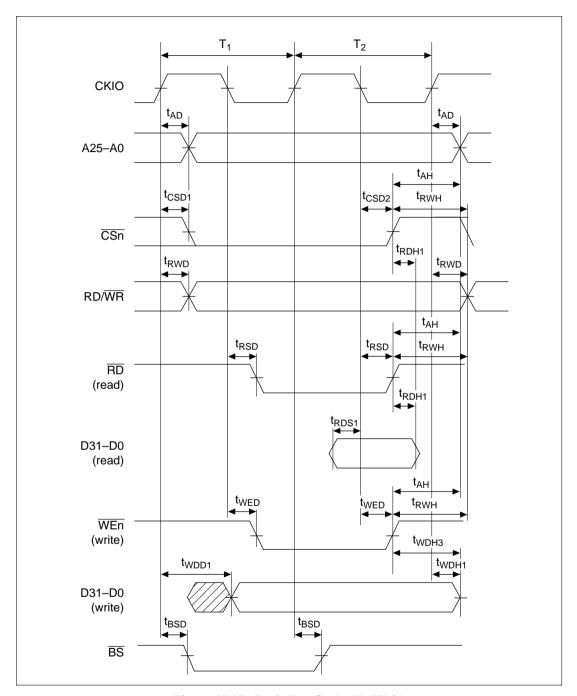

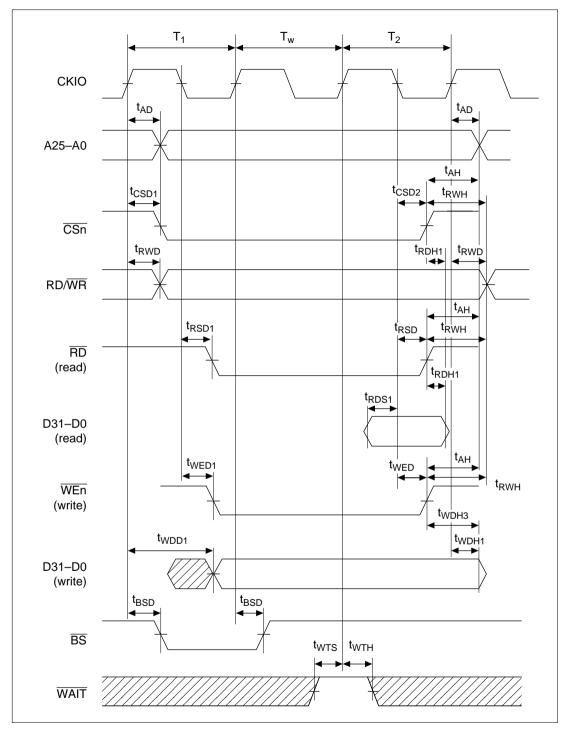

|       | 10.3.3  | Basic Interface                                               | 232 |

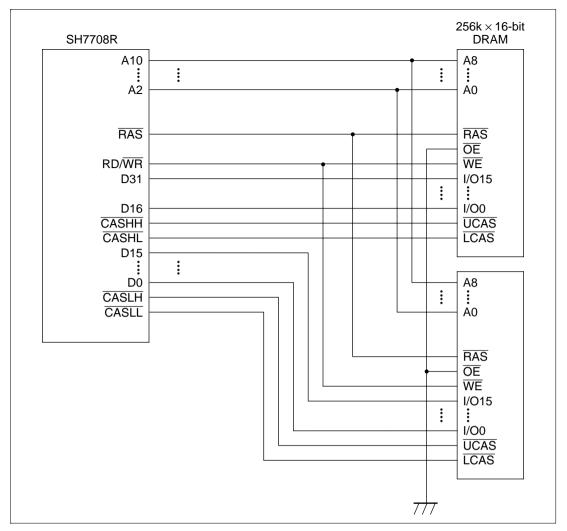

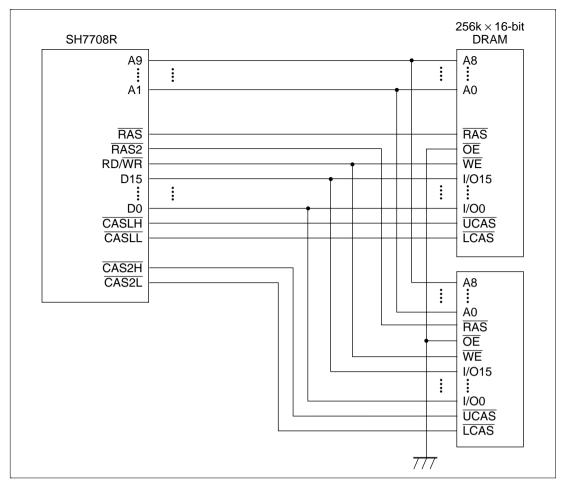

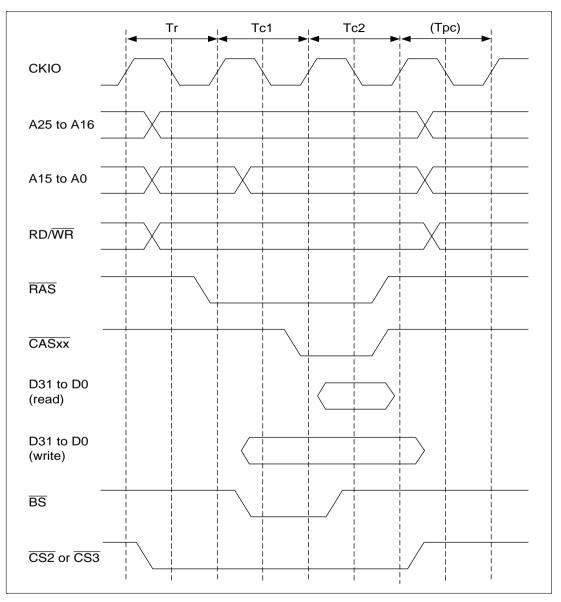

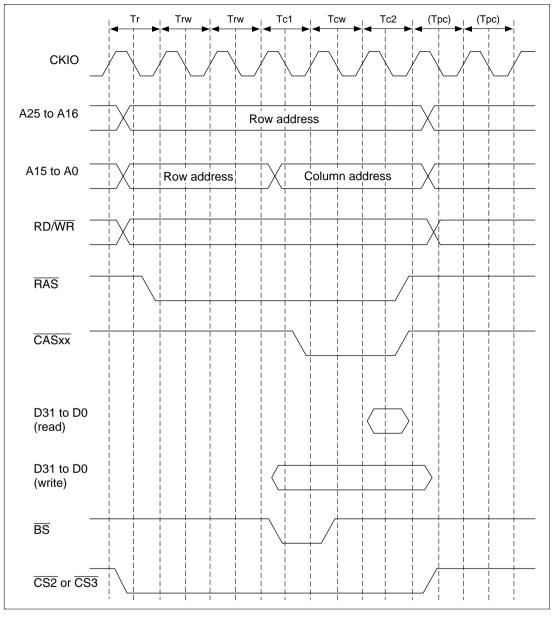

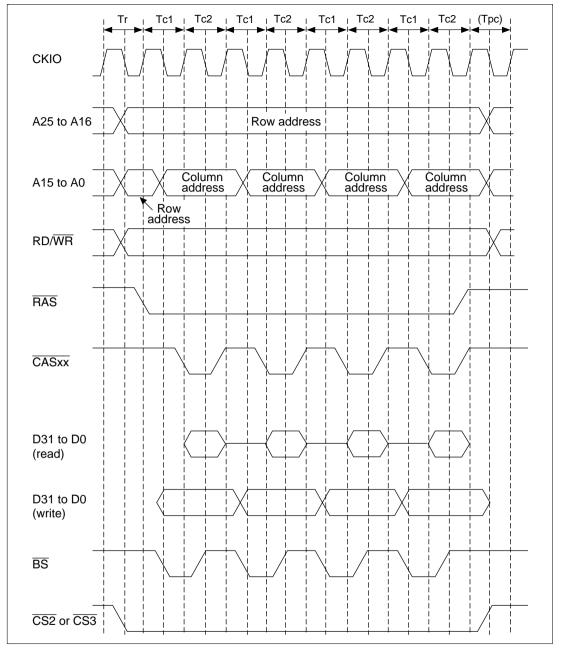

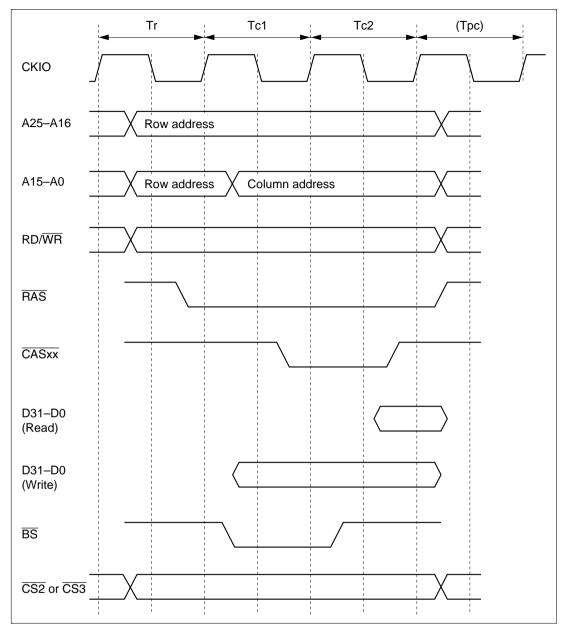

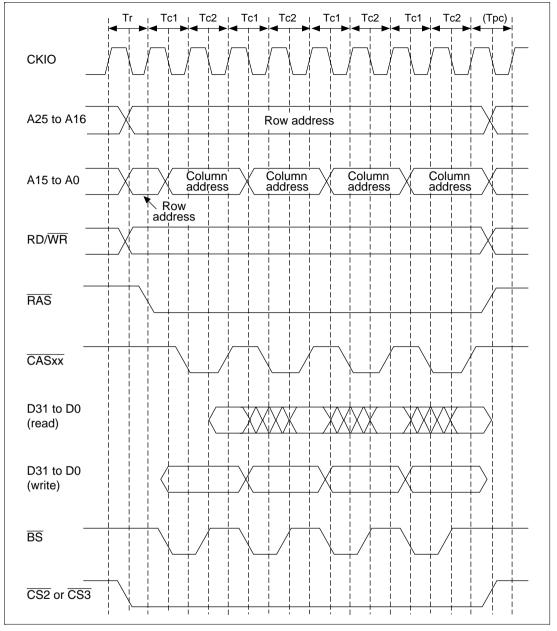

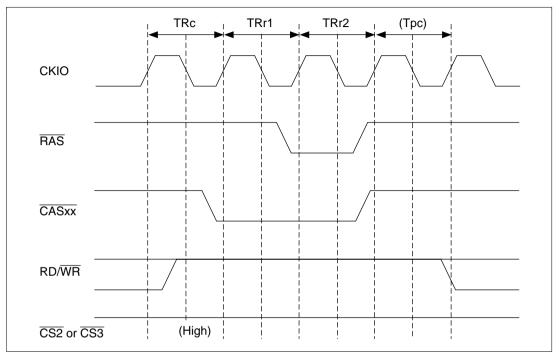

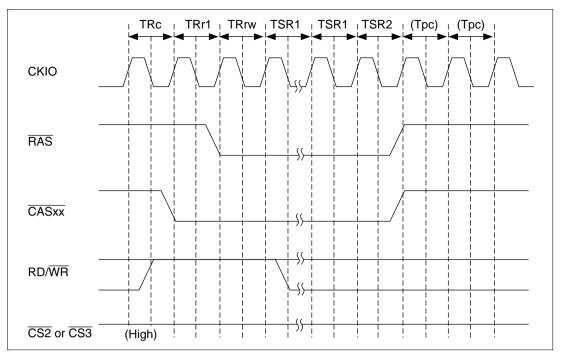

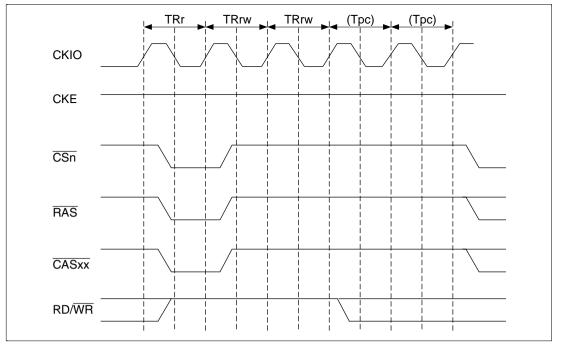

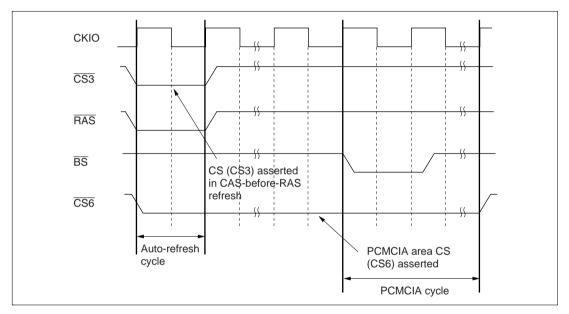

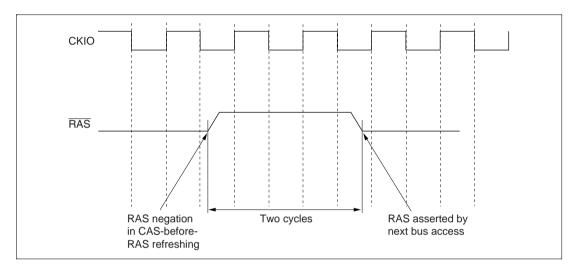

|       | 10.3.4  | DRAM Interface                                                | 239 |

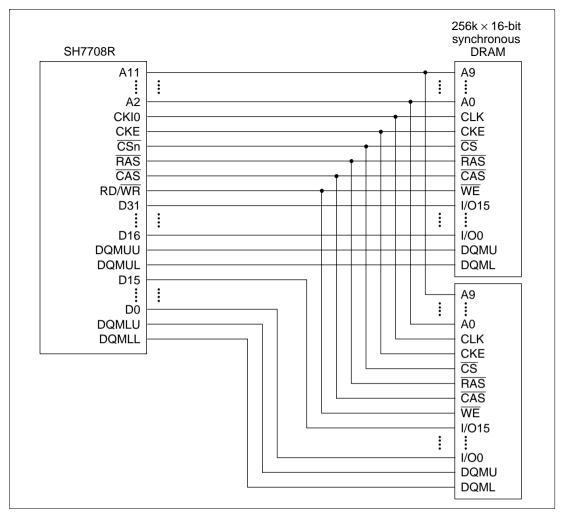

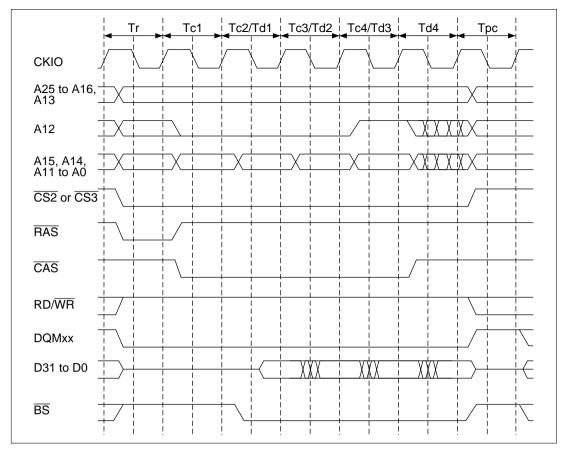

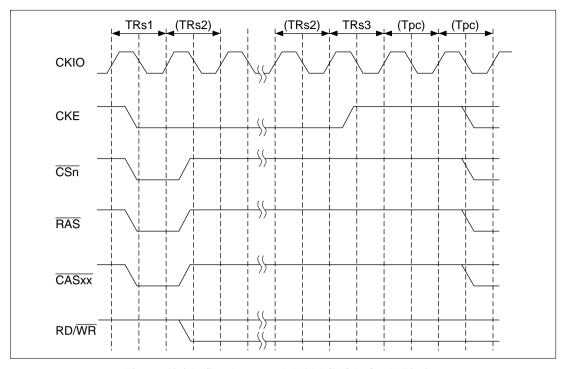

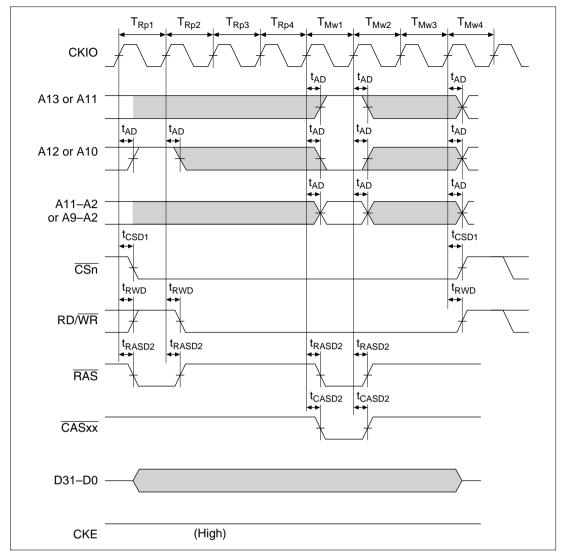

|       | 10.3.5  | Synchronous DRAM Interface                                    | 255 |

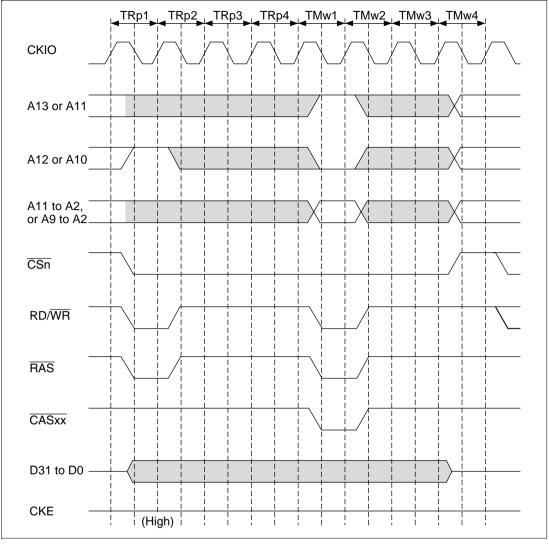

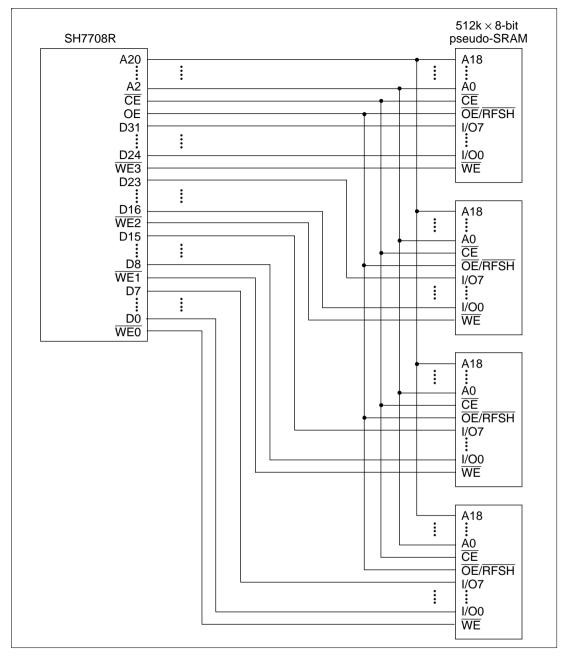

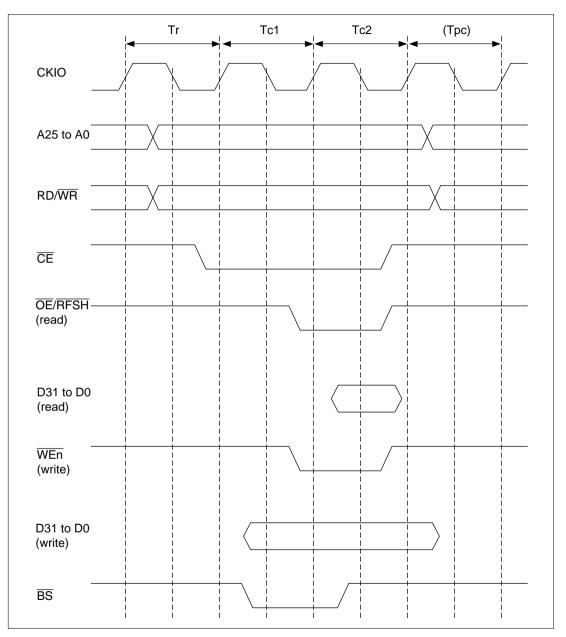

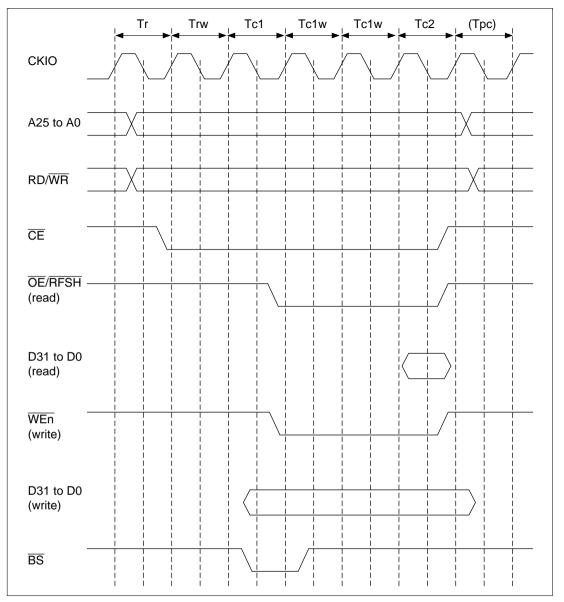

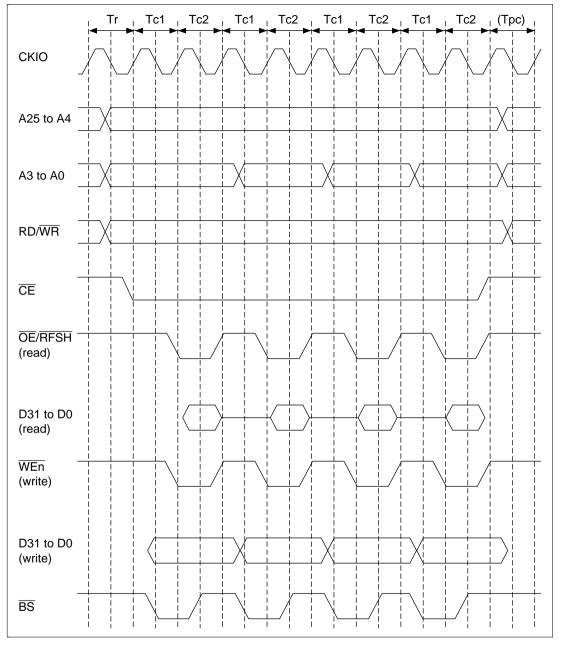

|       | 10.3.6  | Pseudo-SRAM Direct Connection                                 | 271 |

|       | 10.3.7  | Burst ROM Interface                                           | 280 |

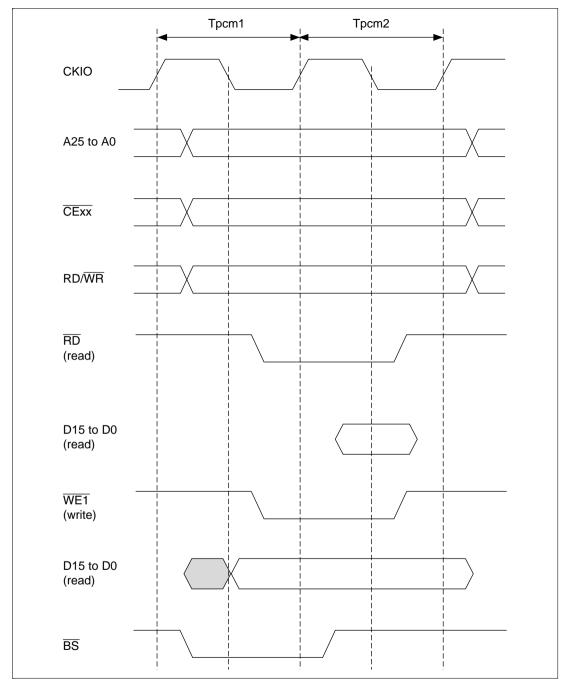

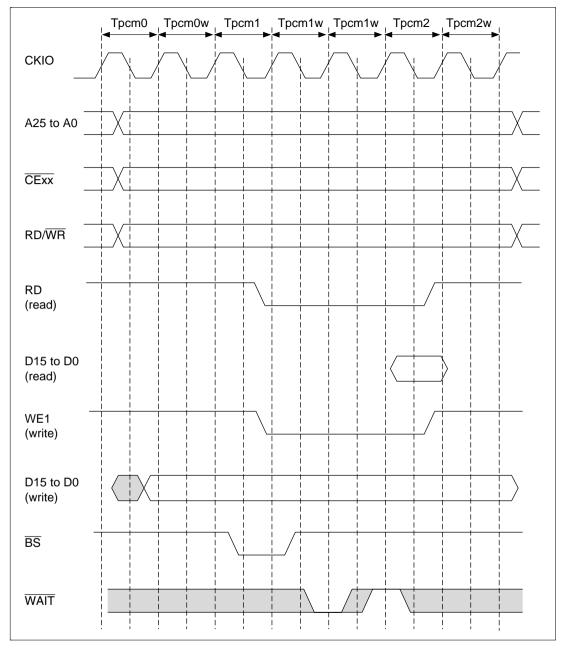

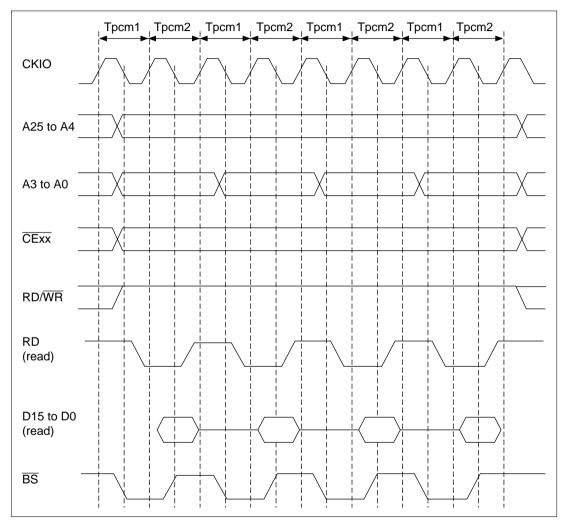

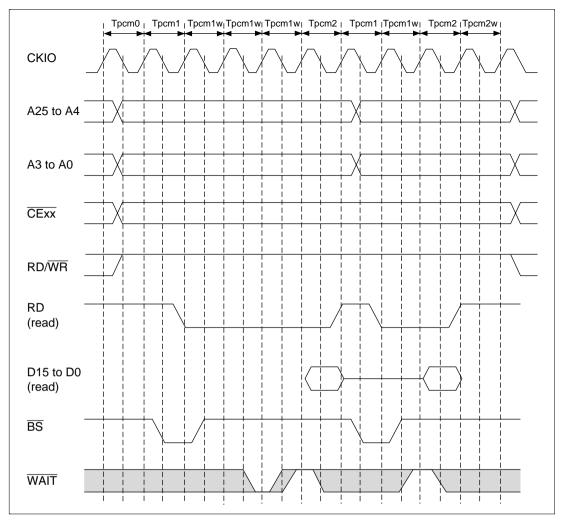

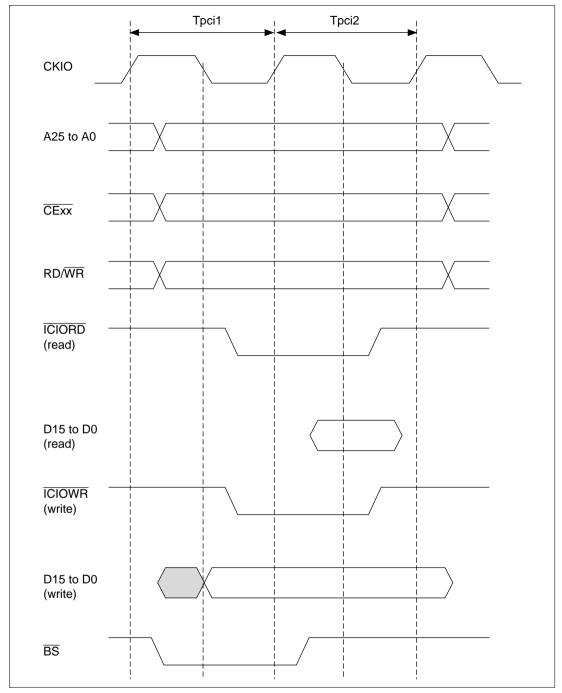

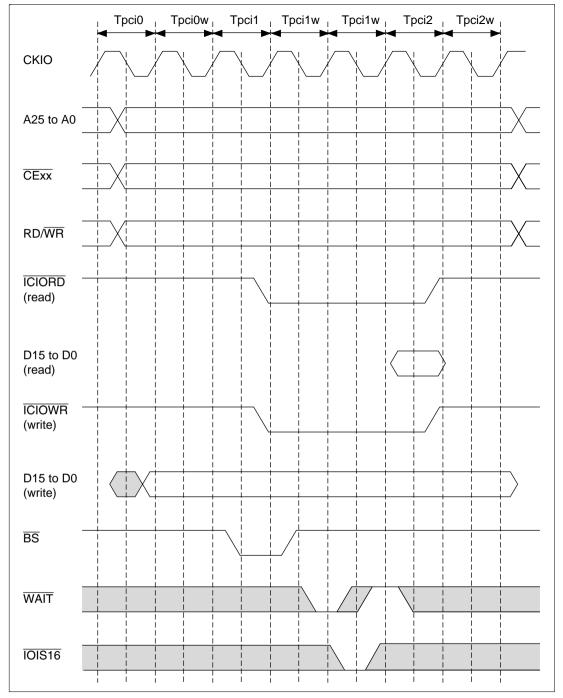

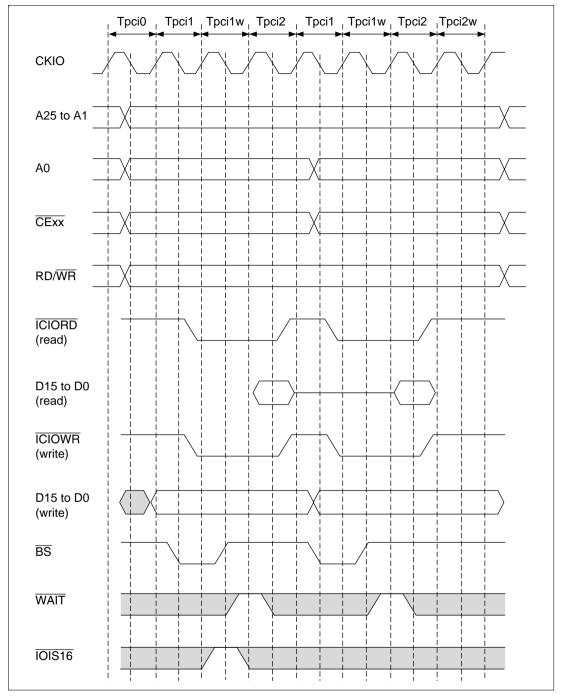

|       | 10.3.8  | PCMCIA Interface                                              | 283 |

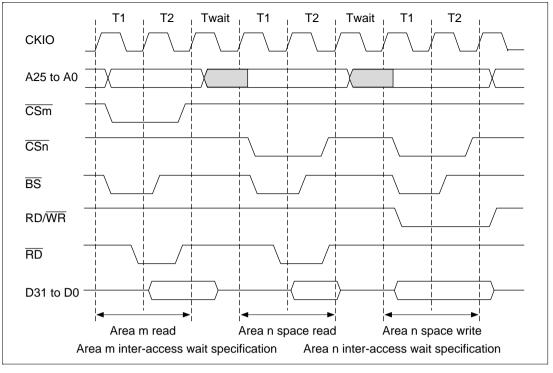

|       | 10.3.9  | Waits between Access Cycles                                   | 295 |

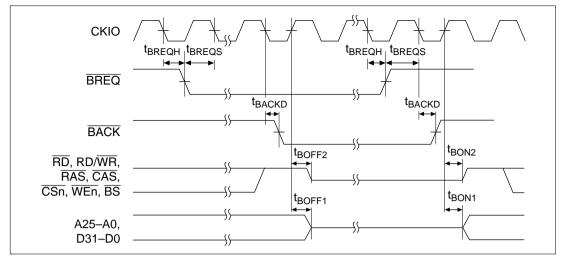

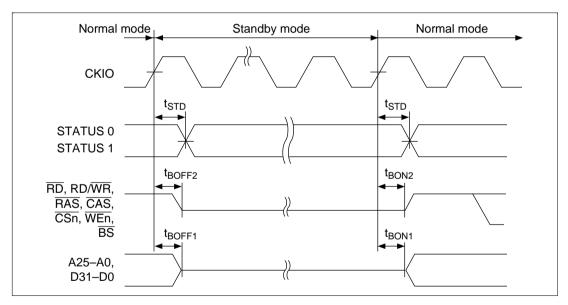

|       | 10.3.10 | Bus Arbitration                                               | 296 |

| 10.4  | Usage l | Notes                                                         | 297 |

|       | 10.4.1  | Area 2 and 3 Bus Width Setting                                | 297 |

|       |         | When Area 6 is Designated for PCMCIA, with a 16-Bit Bus Width |     |

|       | 10.4.3  | Self-Refreshing                                               | 298 |

|       | 10.4.4  | PCMCIA Area Access                                            | 299 |

|       | 10.4.5  | Note on DRAM Connection for Areas 2 and 3                     | 300 |

|       |         |                                                               |     |

| Secti | on 11   | Timer (TMU)                                                   | 301 |

| 11.1  | Overvio | ew                                                            | 301 |

|       | 11.1.1  | Features                                                      | 301 |

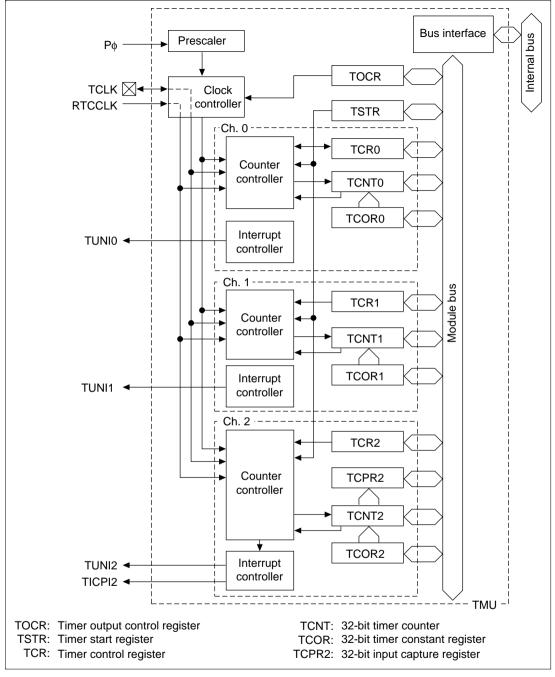

|       | 11.1.2  | Block Diagram                                                 | 301 |

|       | 11.1.3  | Pin Configuration                                             | 303 |

|       |         | Register Configuration                                        | 303 |

| 11.2  |         | Registers                                                     | 304 |

|       |         | Timer Output Control Register (TOCR)                          |     |

| vi    |         |                                                               |     |

|       |         |                                                               |     |

|       | 11.2.2 Timer Start Register (TSTR)                  | 30: |

|-------|-----------------------------------------------------|-----|

|       | 11.2.3 Timer Control Register (TCR)                 | 30  |

|       | 11.2.4 Timer Constant Register (TCOR)               | 309 |

|       | 11.2.5 Timer Counters (TCNT)                        | 310 |

|       | 11.2.6 Input Capture Register (TCPR2)               | 31  |

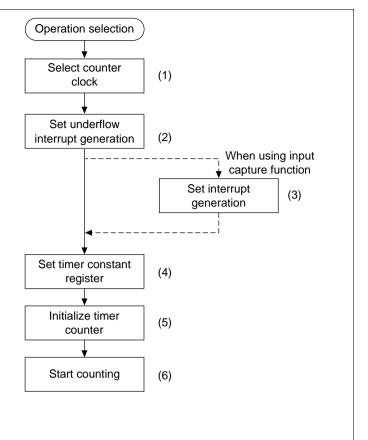

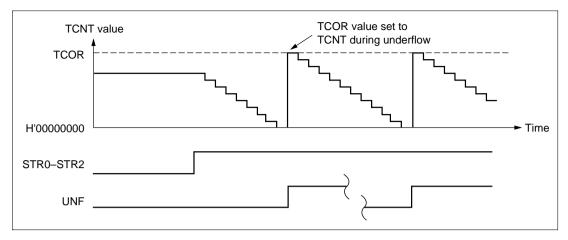

| 11.3  | TMU Operation                                       | 312 |

|       | 11.3.1 Overview                                     | 312 |

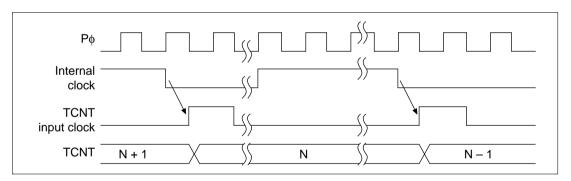

|       | 11.3.2 Basic Functions                              | 312 |

| 11.4  | Interrupts                                          | 310 |

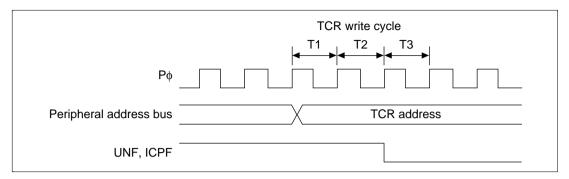

|       | 11.4.1 Status Flag Set Timing                       |     |

|       | 11.4.2 Status Flag Clear Timing                     |     |

|       | 11.4.3 Interrupt Sources and Priorities             |     |

| 11.5  | Usage Notes                                         |     |

|       | 11.5.1 Writing to Registers                         |     |

|       | 11.5.2 Reading Registers                            |     |

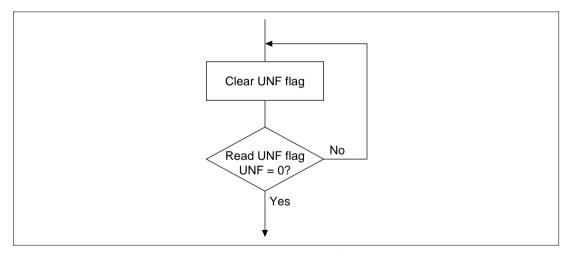

|       | 11.5.3 Clearing UNF in the TCR Register             |     |

|       |                                                     |     |

| Secti | ion 12 Realtime Clock (RTC)                         | 319 |

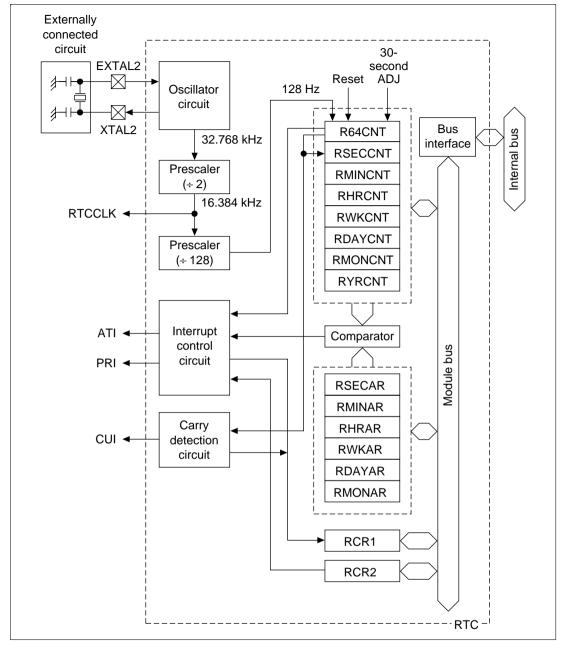

| 12.1  | Overview                                            |     |

|       | 12.1.1 Features                                     |     |

|       | 12.1.2 Block Diagram.                               |     |

|       | 12.1.3 Pin Configuration                            |     |

|       | 12.1.4 RTC Register Configuration                   |     |

| 12.2  | RTC Registers                                       |     |

| 12.2  | 12.2.1 64-Hz Counter (R64CNT)                       |     |

|       | 12.2.2 Second Counter (RSECCNT)                     |     |

|       | 12.2.3 Minute Counter (RMINCNT)                     |     |

|       | 12.2.4 Hour Counter (RHRCNT)                        |     |

|       | 12.2.5 Day of the Week Counter (RWKCNT)             |     |

|       | 12.2.6 Date Counter (RDAYCNT)                       |     |

|       | 12.2.7 Month Counter (RMONCNT)                      |     |

|       | 12.2.8 Year Counter (RYRCNT)                        |     |

|       | 12.2.9 Second Alarm Register (RSECAR)               |     |

|       | 12.2.10 Minute Alarm Register (RMINAR)              |     |

|       | 12.2.11 Hour Alarm Register (RHRAR)                 |     |

|       | 12.2.12 Day of the Week Alarm Register (RWKAR)      |     |

|       | 12.2.13 Date Alarm Register (RDAYAR)                |     |

|       | 12.2.14 Month Alarm Register (RMONAR)               |     |

|       | 12.2.15 RTC Control Register 1 (RCR1)               |     |

|       | 12.2.16 RTC Control Register 2 (RCR2)               |     |

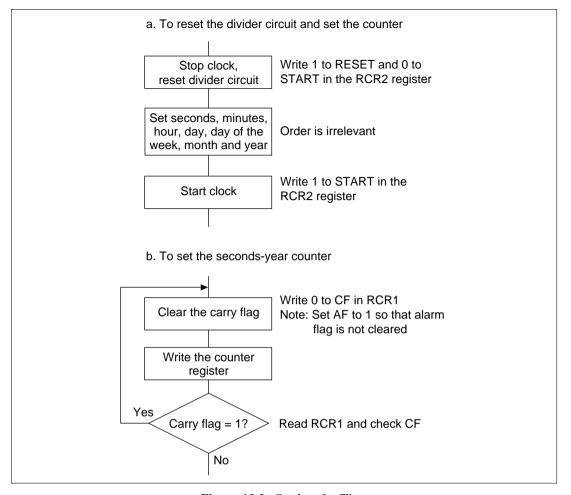

| 12.3  | RTC Operation                                       |     |

| 14.3  | 12.3.1 Initial Settings of Registers after Power-On |     |

|       | 12.3.2 Setting the Time                             |     |

|       | 12.3.2 Setting the Time                             | JJ. |

|       |                                                     | ١/  |

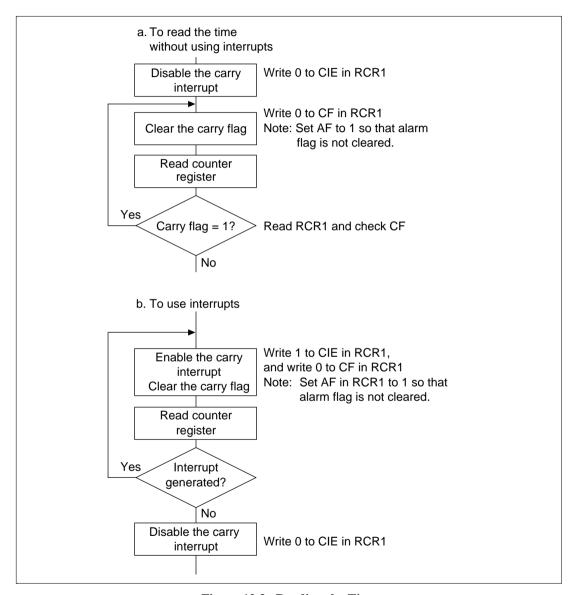

|       | 12.3.3  | Reading the Time                           | 335             |

|-------|---------|--------------------------------------------|-----------------|

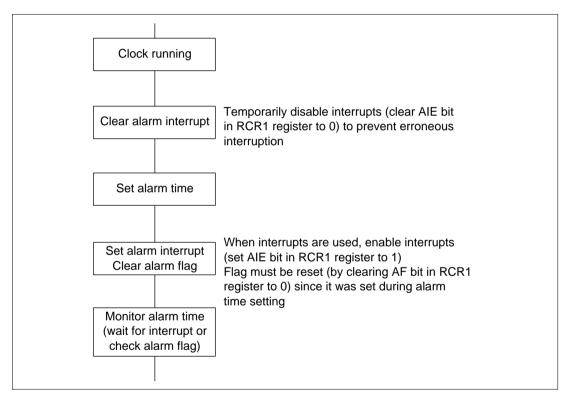

|       | 12.3.4  | Alarm Function                             | 336             |

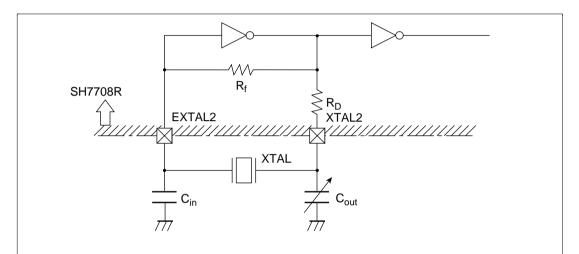

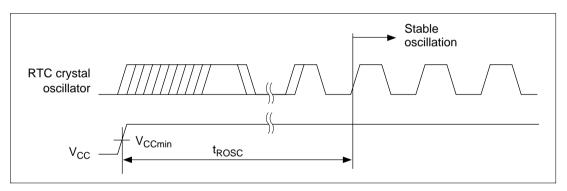

|       | 12.3.5  | Crystal Oscillator Circuit                 | 337             |

| 12.4  | Usage 1 | Notes                                      | 338             |

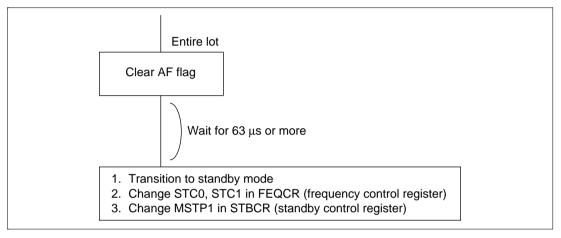

|       | 12.4.1  | Flag Clearing                              | 338             |

|       | 12.4.2  | Register Writes during RTC Count           | 338             |

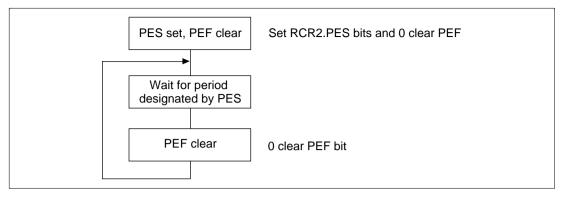

|       | 12.4.3  | Usage Note about Periodic Interrupt on RTC | 338             |

| ~     |         |                                            |                 |

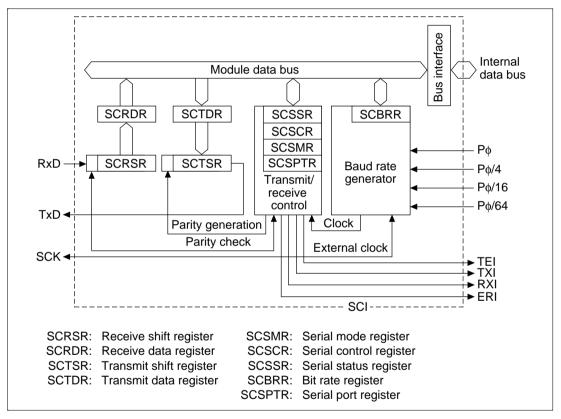

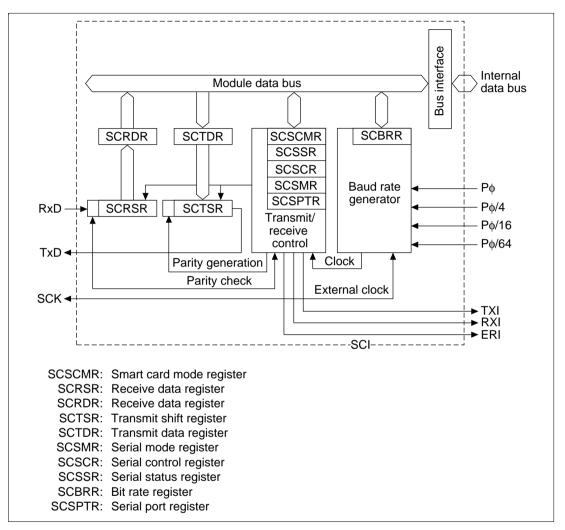

|       |         | Serial Communication Interface (SCI)       |                 |

| 13.1  |         | ew                                         |                 |

|       |         | Features                                   |                 |

|       |         | Block Diagram                              |                 |

|       |         | Pin Configuration                          |                 |

|       |         | Register Configuration                     |                 |

| 13.2  | _       | er Descriptions                            |                 |

|       |         | Receive Shift Register (SCRSR)             |                 |

|       |         | Receive Data Register (SCRDR)              |                 |

|       |         | Transmit Shift Register (SCTSR)            |                 |

|       |         | Transmit Data Register (SCTDR)             |                 |

|       |         | Serial Mode Register (SCSMR)               |                 |

|       | 13.2.6  | , , , , , , , , , , , , , , , , , , , ,    |                 |

|       | 13.2.7  |                                            |                 |

|       |         | Serial Port Register (SCSPTR)              |                 |

|       |         | Bit Rate Register (SCBRR)                  |                 |

| 13.3  | -       | on                                         |                 |

|       |         | Overview                                   |                 |

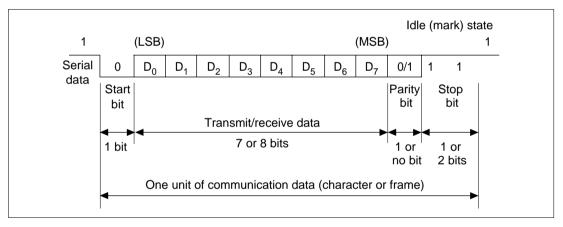

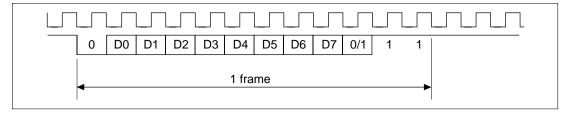

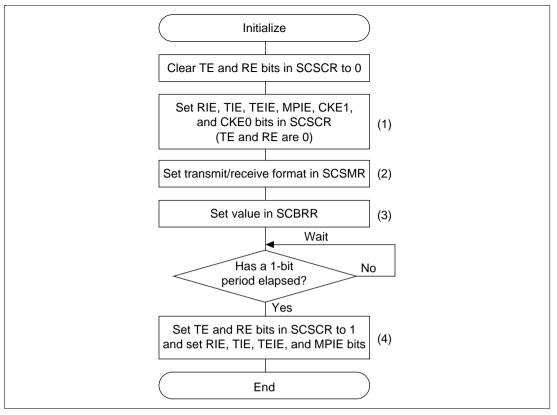

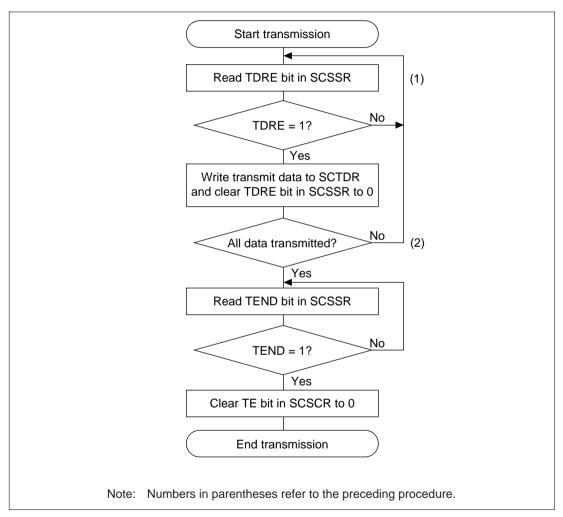

|       |         | Operation in Asynchronous Mode             |                 |

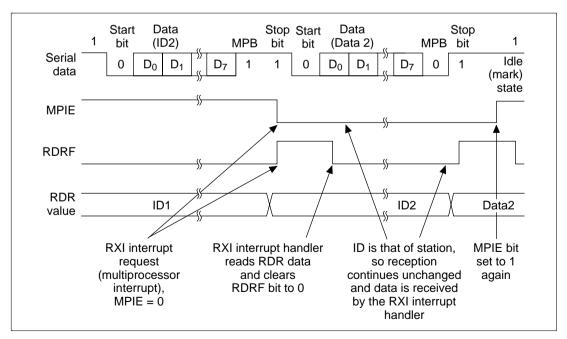

|       |         | Multiprocessor Communication               |                 |

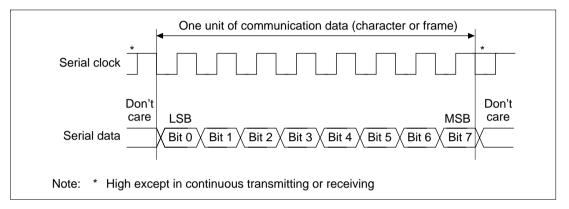

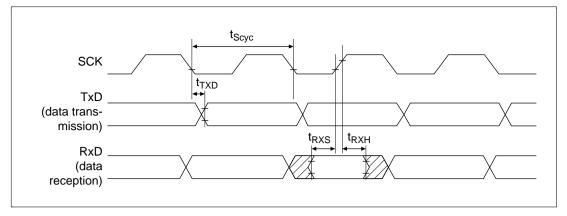

|       |         | Synchronous Operation                      |                 |

| 13.4  |         | errupt Sources                             |                 |

| 13.5  | Usage 1 | Notes                                      | 394             |

| Secti | ion 14  | Smart Card Interface                       | 300             |

|       |         | ew                                         |                 |

| 17.1  |         | Features                                   |                 |

|       |         | Block Diagram.                             |                 |

|       |         | Pin Configuration                          |                 |

|       |         | Register Configuration                     | 401             |

| 14.2  |         | er Descriptions                            |                 |

| 17.2  | 14.2.1  | •                                          |                 |

|       |         | Serial Status Register (SCSSR)             |                 |

| 14.3  |         | -                                          |                 |

| 17.5  | _       | Overview                                   |                 |

| :::   | 17.3.1  | 0.01.10.0                                  | <del>-0-1</del> |

| viii  |         |                                            |                 |

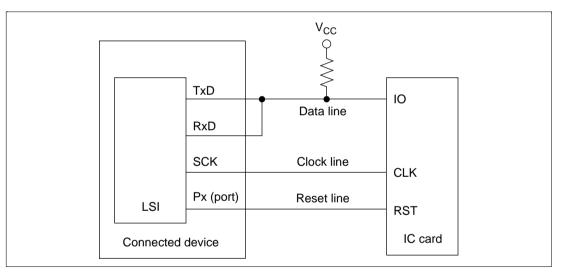

|     | 14.3.2 Pin Connections                                             | 405 |

|-----|--------------------------------------------------------------------|-----|

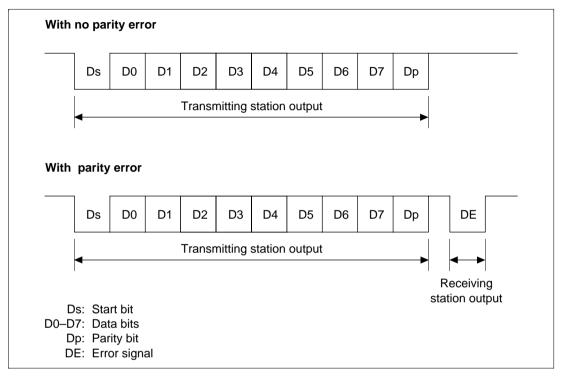

|     | 14.3.3 Data Format                                                 | 406 |

|     | 14.3.4 Register Settings                                           | 407 |

|     | 14.3.5 Clock                                                       | 409 |

|     | 14.3.6 Data Transmission and Reception                             | 412 |

| 14. | Usage Notes                                                        | 418 |

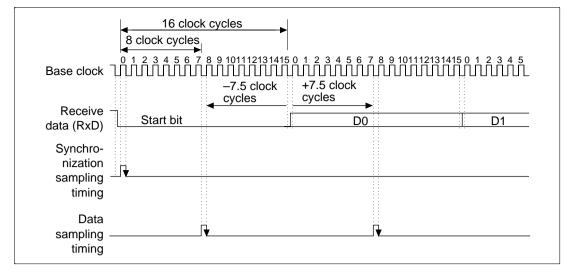

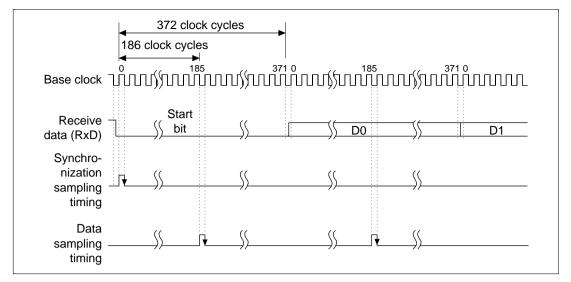

|     | 14.4.1 Receive Data Timing and Receive Margin in Asynchronous Mode | 418 |

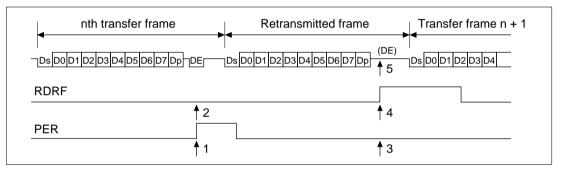

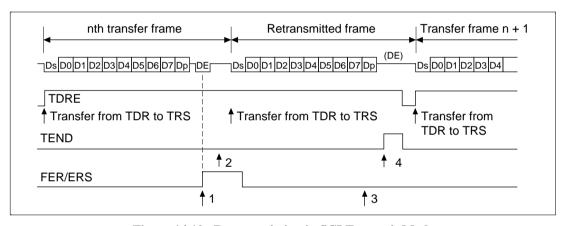

|     | 14.4.2 Retransmission (Receive and Transmit Modes)                 | 420 |

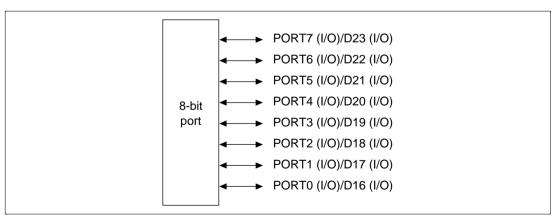

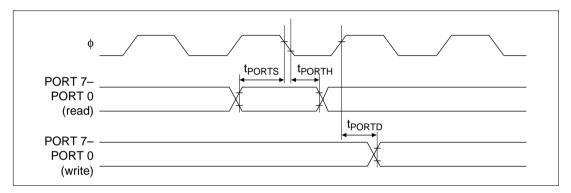

| Se  | on 15 I/O Ports                                                    | 423 |

| 15. | Overview                                                           | 423 |

|     | 15.1.1 Features                                                    | 423 |

|     | 15.1.2 Block Diagram                                               | 423 |

|     | 15.1.3 Pin Configuration                                           | 426 |

|     | 15.1.4 Register Configuration                                      | 427 |

| 15. | Register Descriptions                                              | 427 |

|     | 15.2.1 Port Control Register (PCTR)                                | 427 |

|     | 15.2.2 Port Data Register (PDTR)                                   | 428 |

|     | 15.2.3 Serial Port Register (SCSPTR)                               | 429 |

| Se  | on 16 Electrical Characteristics (-SH7708, SH7708S-)               | 431 |

| 16. | Absolute Maximum Ratings                                           | 431 |

| 16. | DC Characteristics                                                 | 432 |

| 16. | AC Characteristics                                                 | 433 |

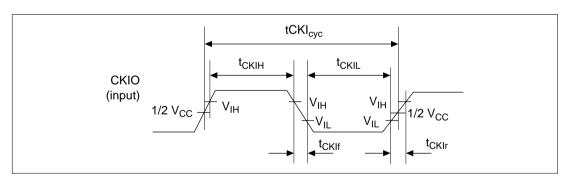

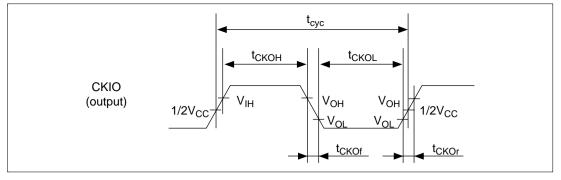

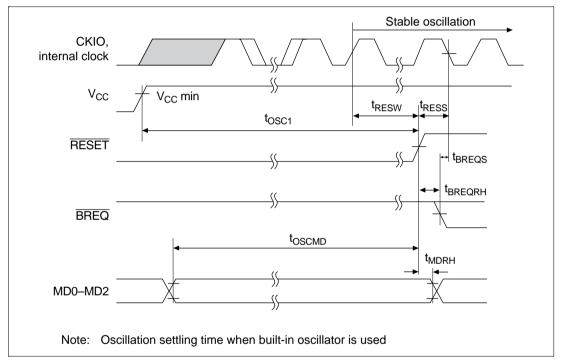

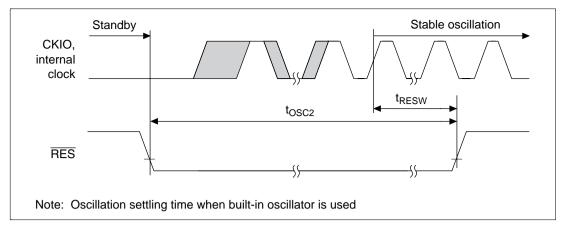

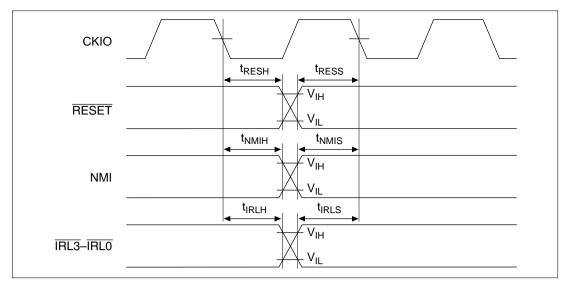

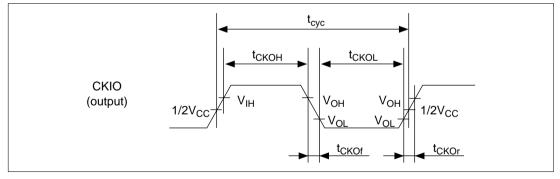

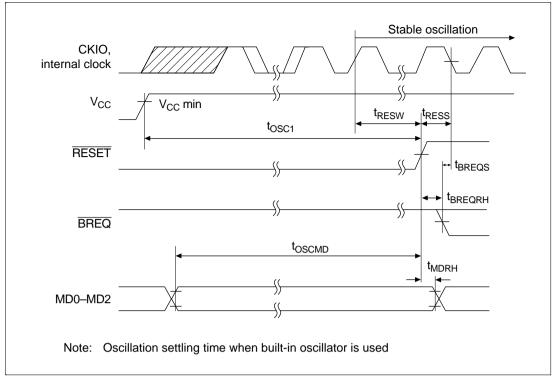

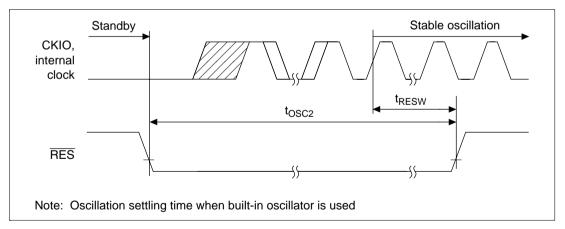

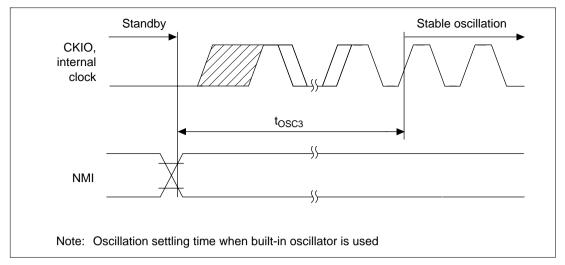

|     | 16.3.1 Clock Timing                                                | 434 |

|     | 16.3.2 Control Signal Timing                                       | 444 |

|     | 16.3.3 AC Bus Timing Specifications                                | 448 |

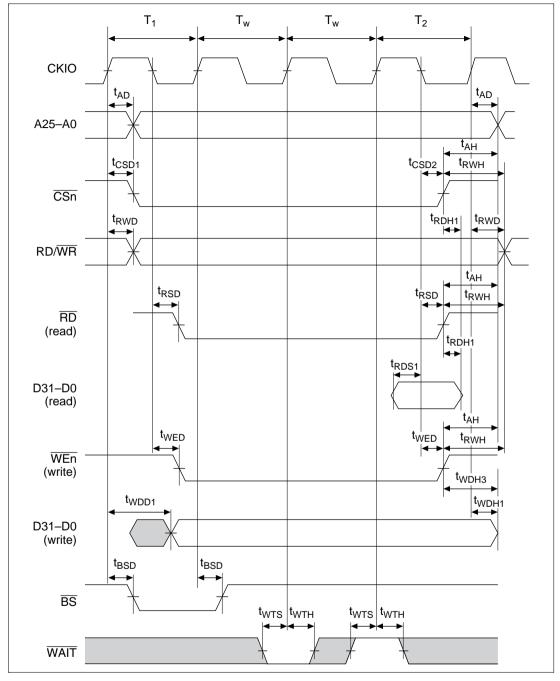

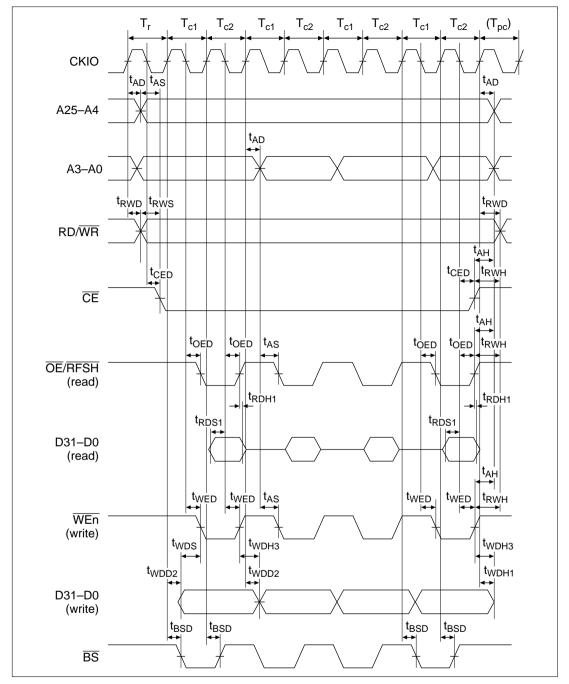

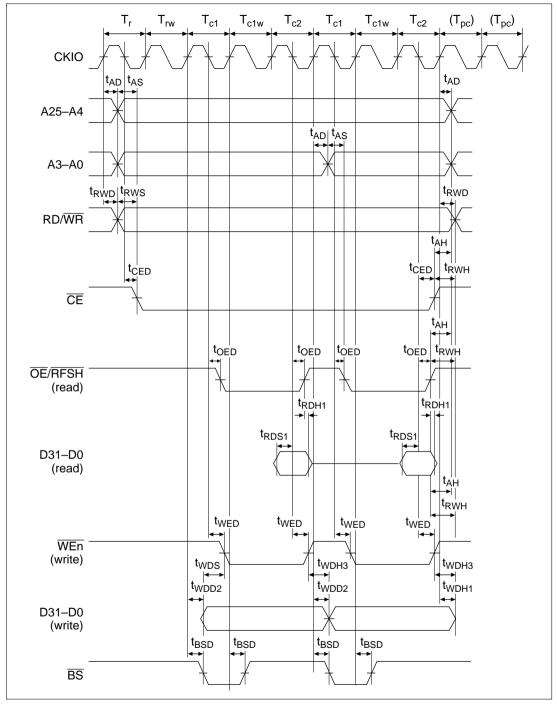

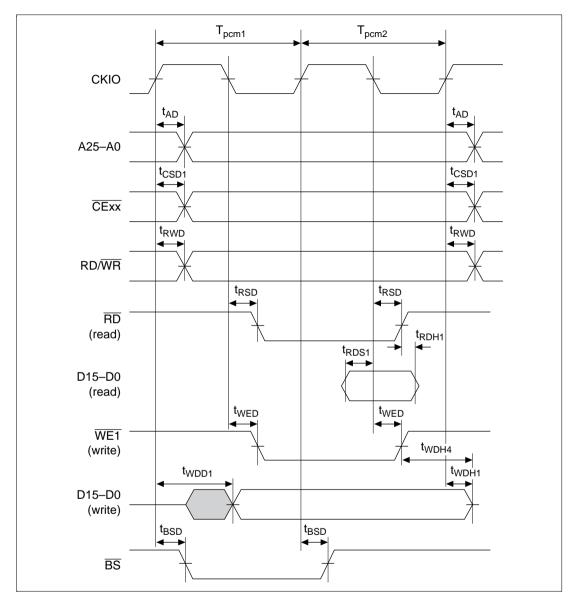

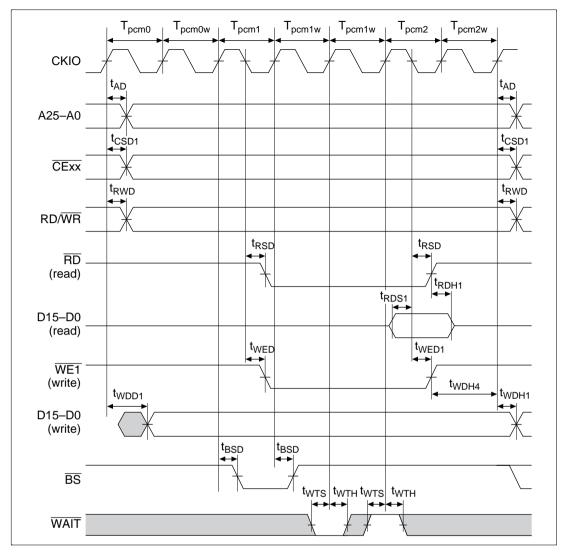

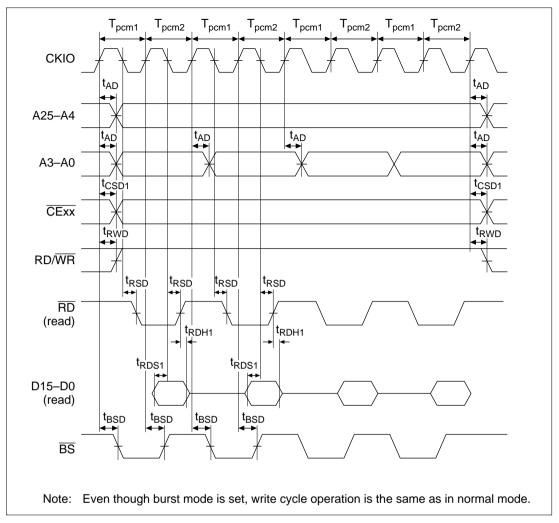

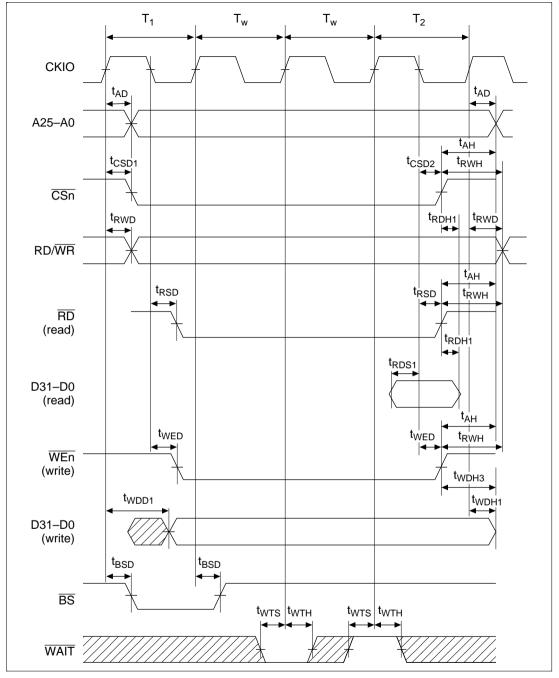

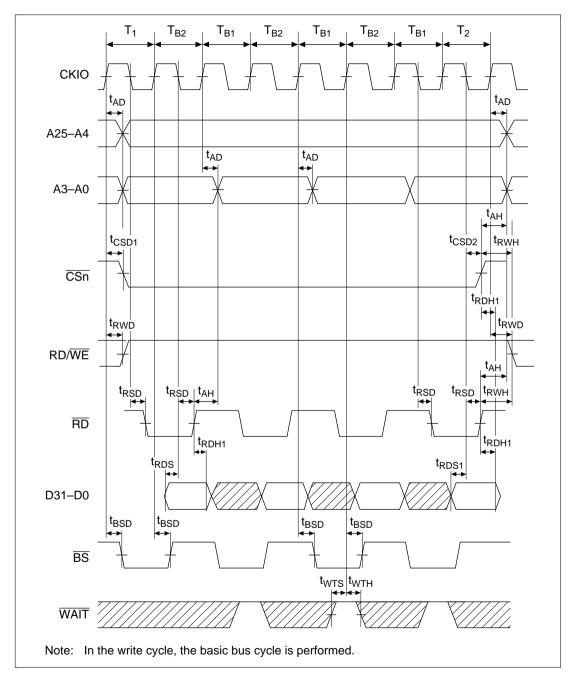

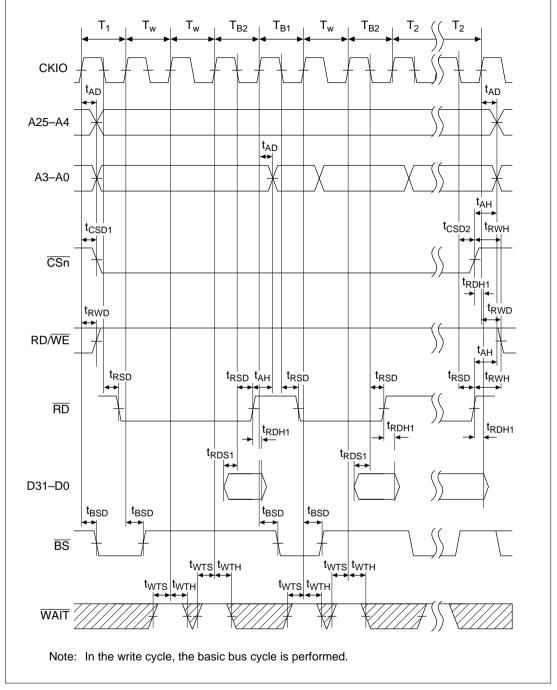

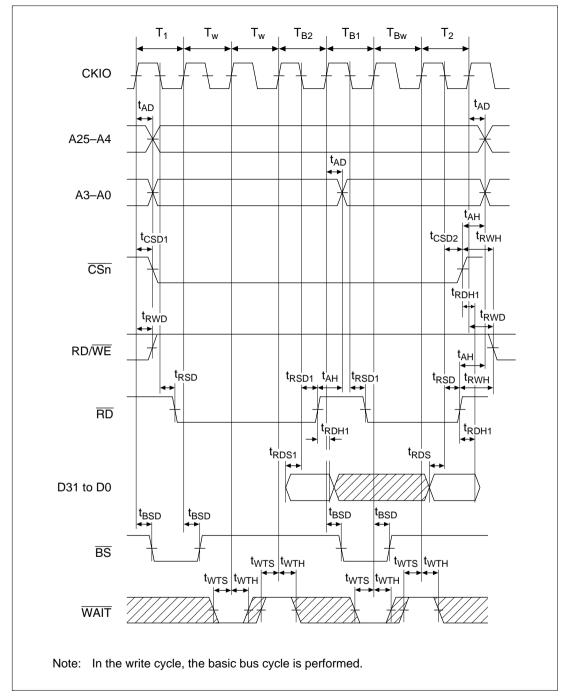

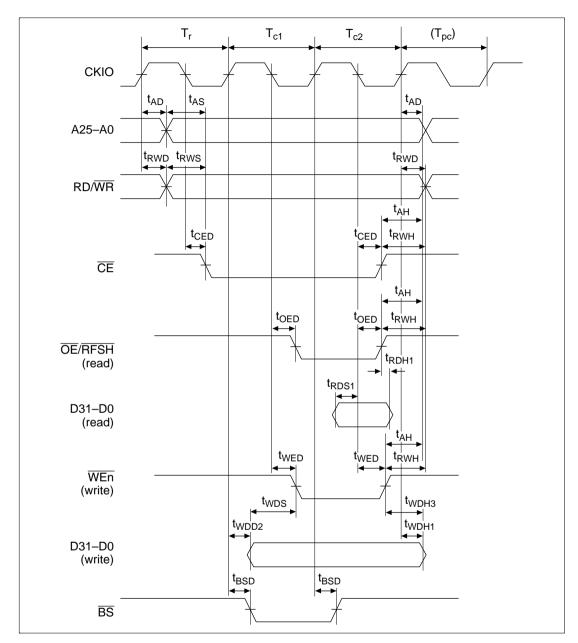

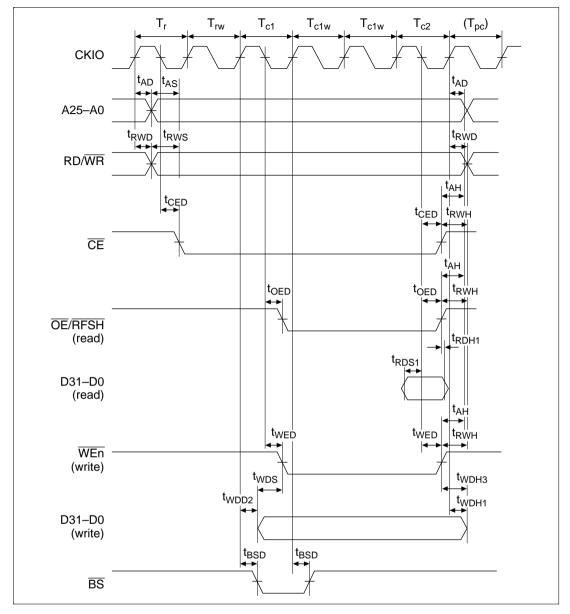

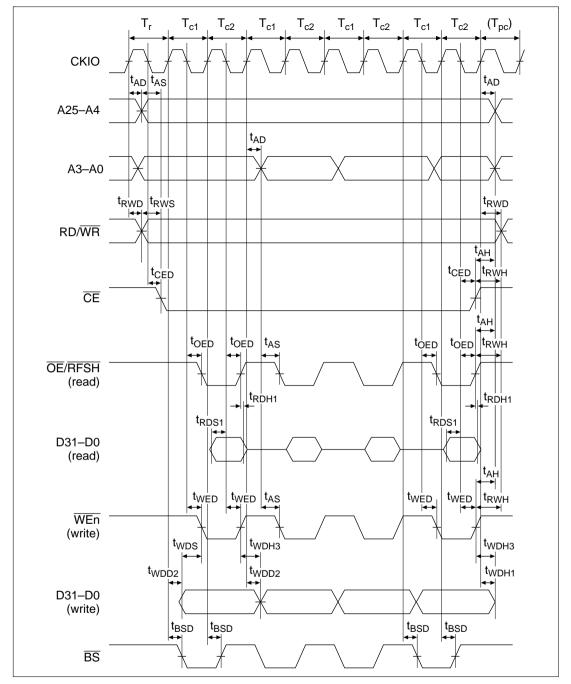

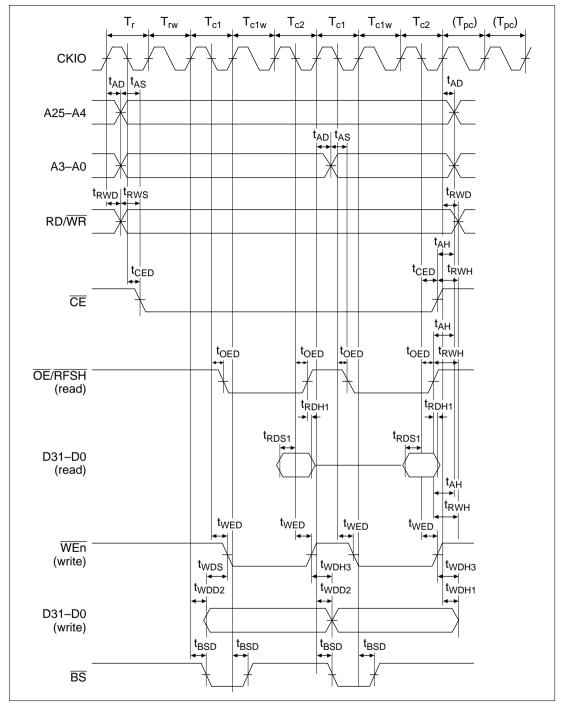

|     | 16.3.4 Basic Timing                                                | 452 |

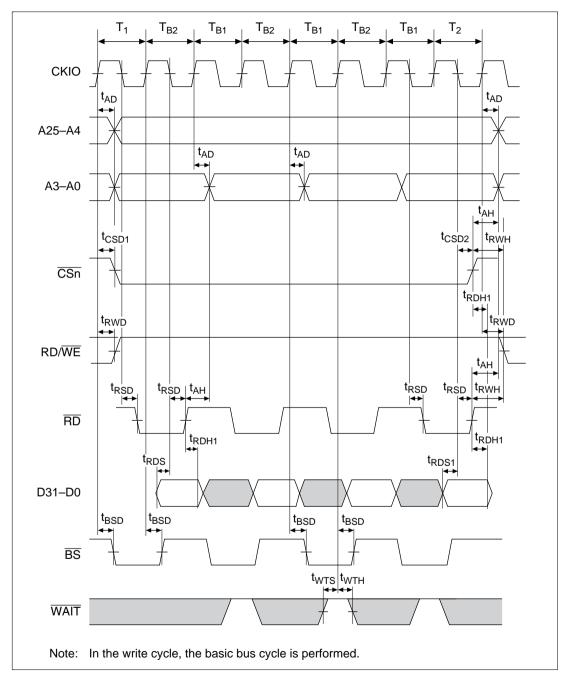

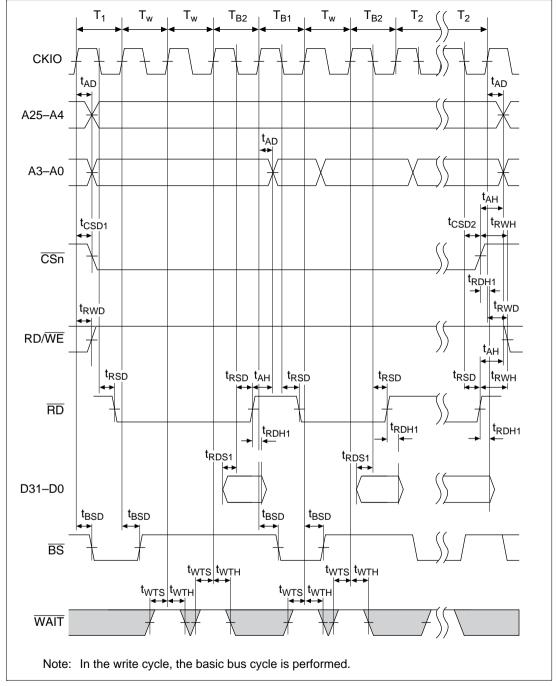

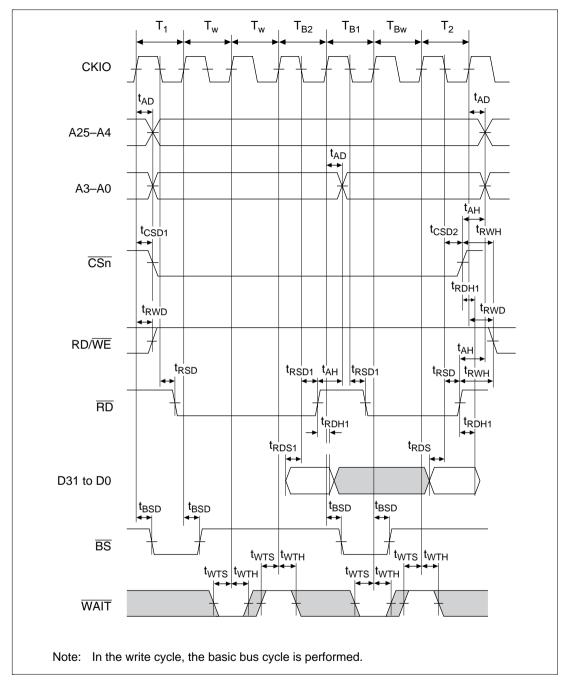

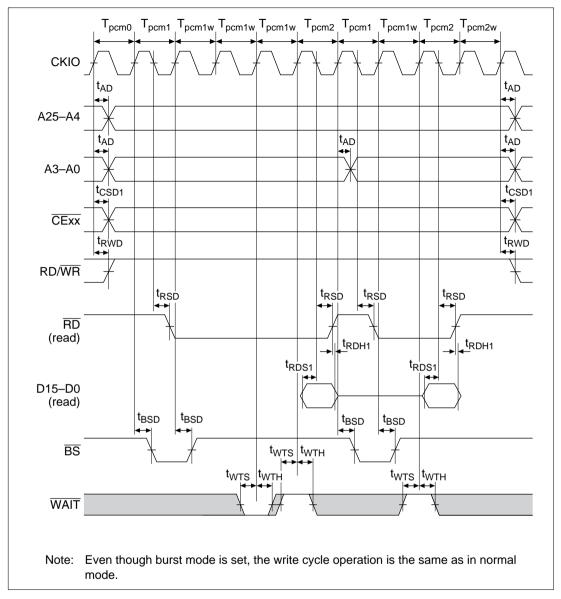

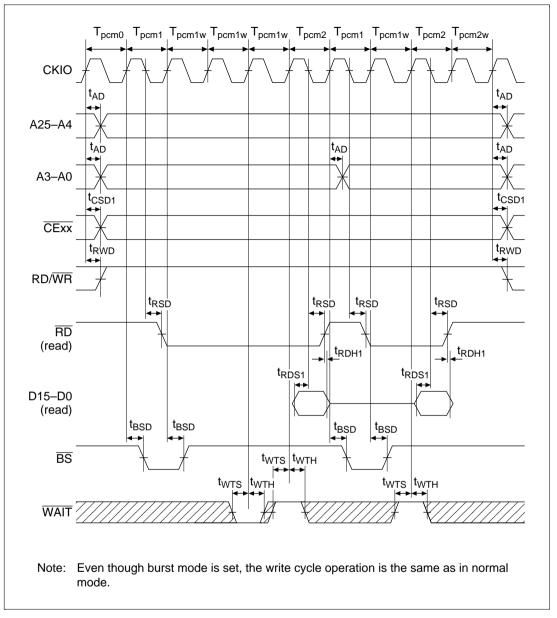

|     | 16.3.5 Burst ROM Timing                                            | 455 |

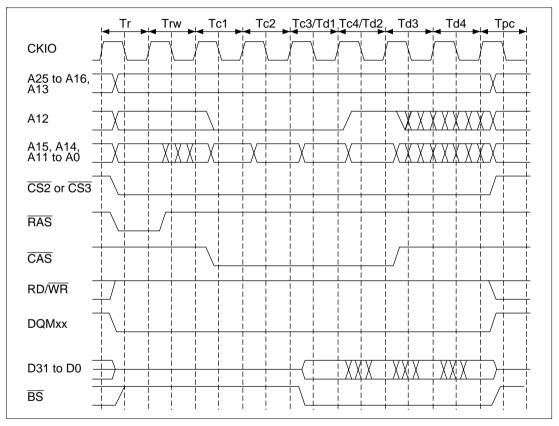

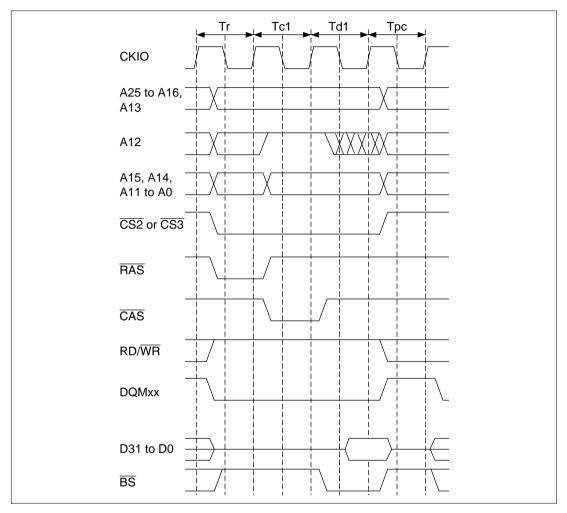

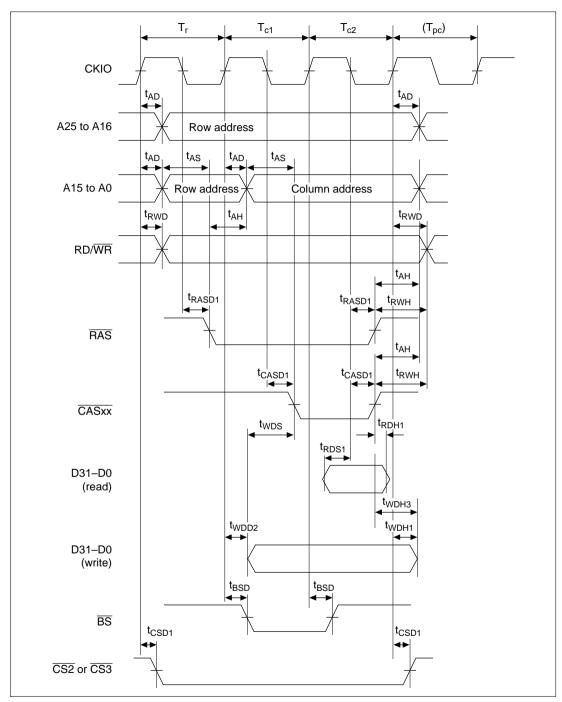

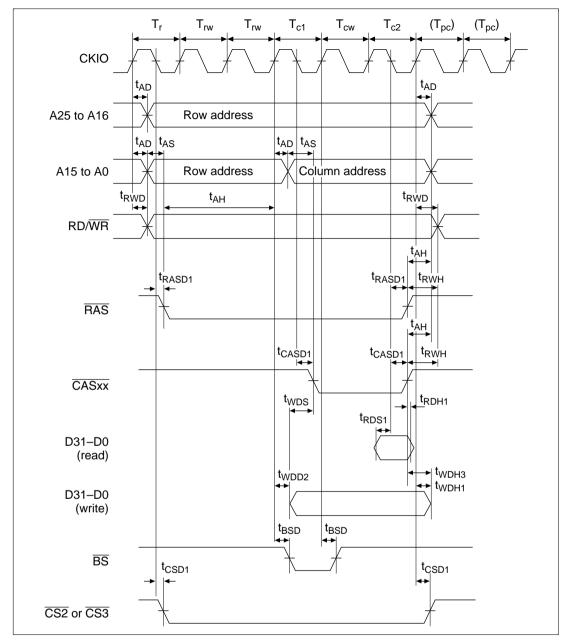

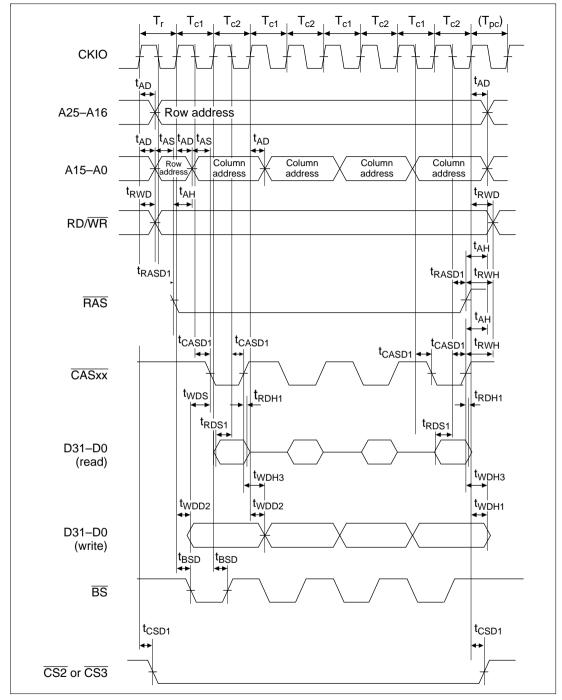

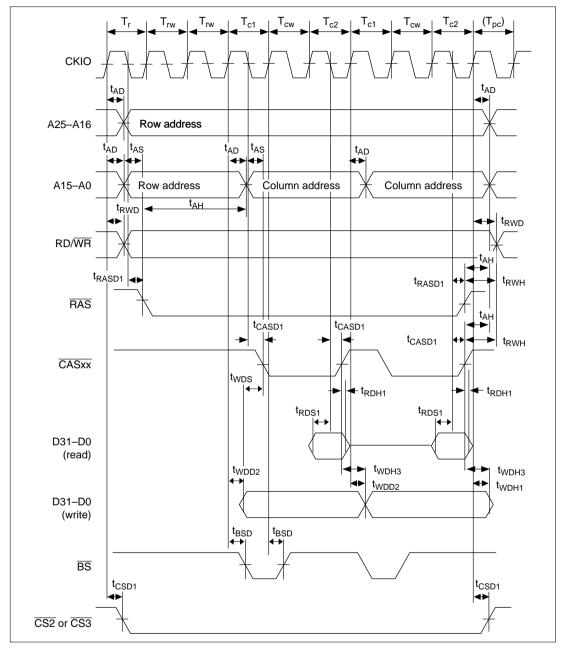

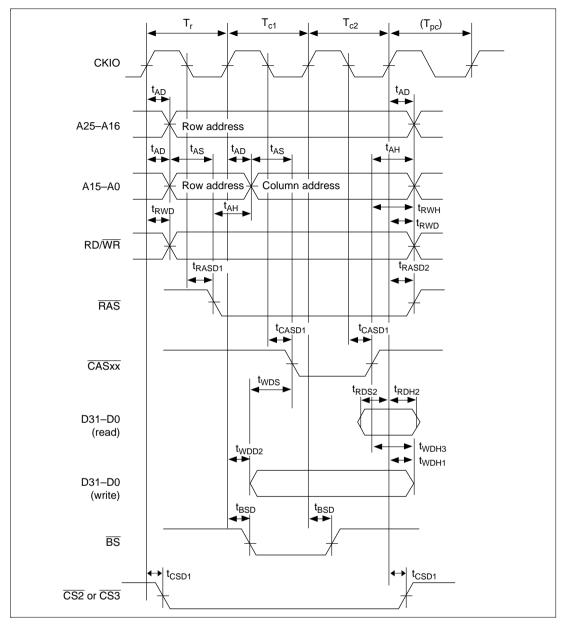

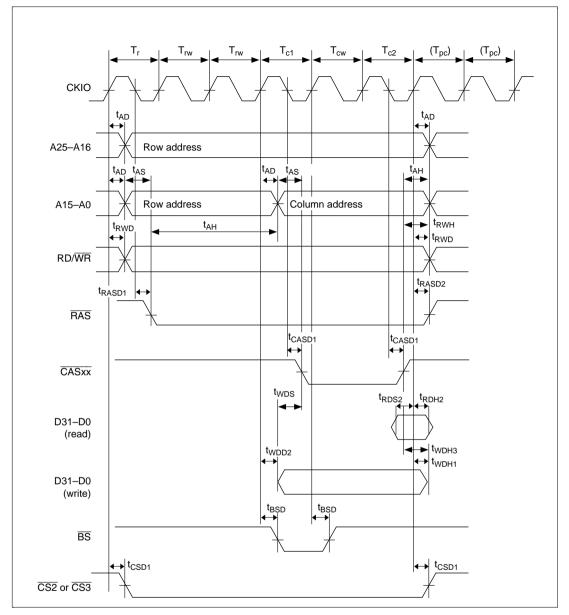

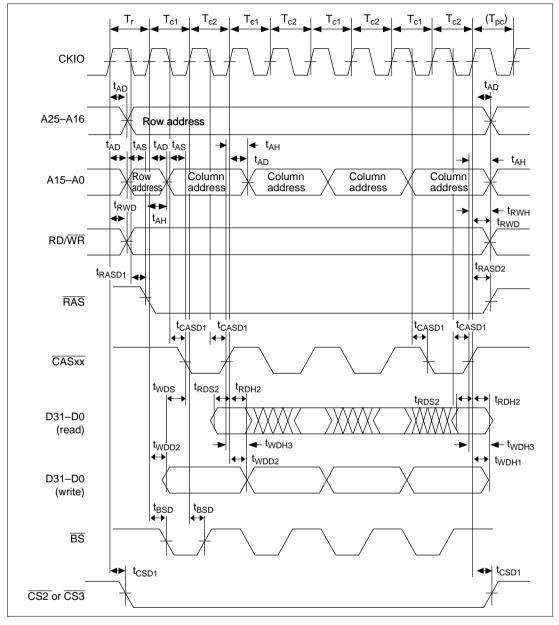

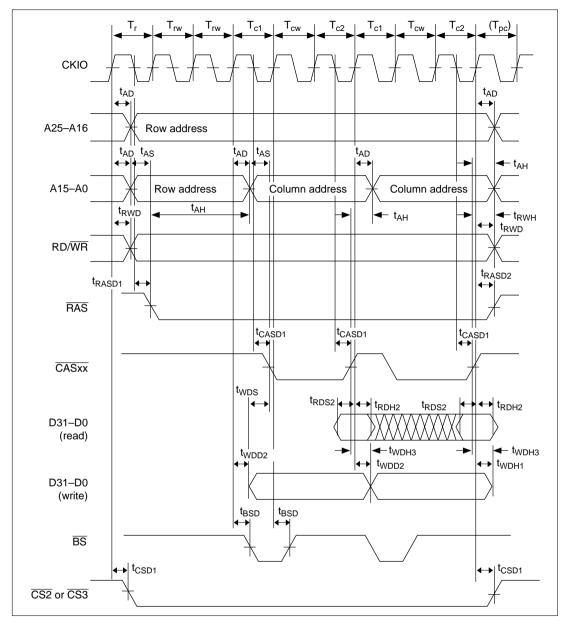

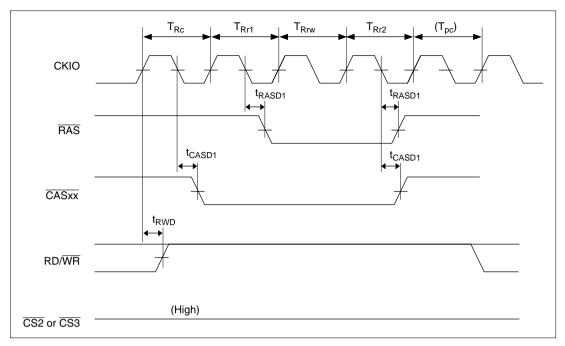

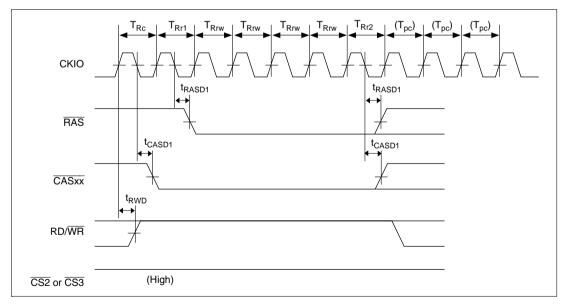

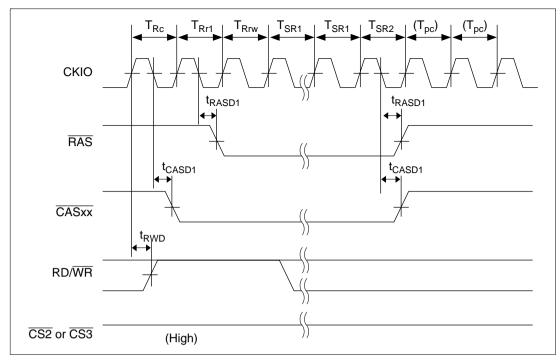

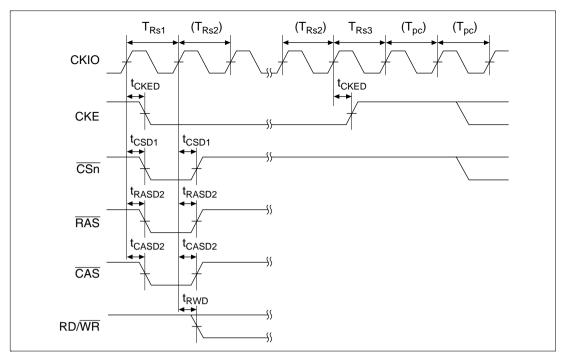

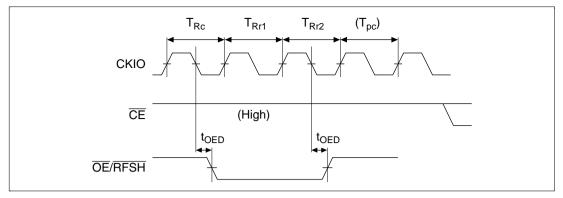

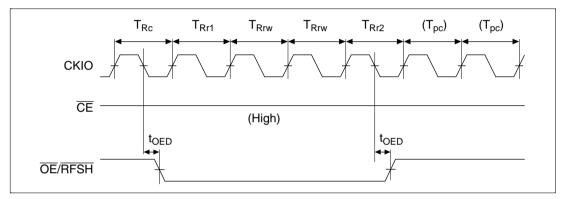

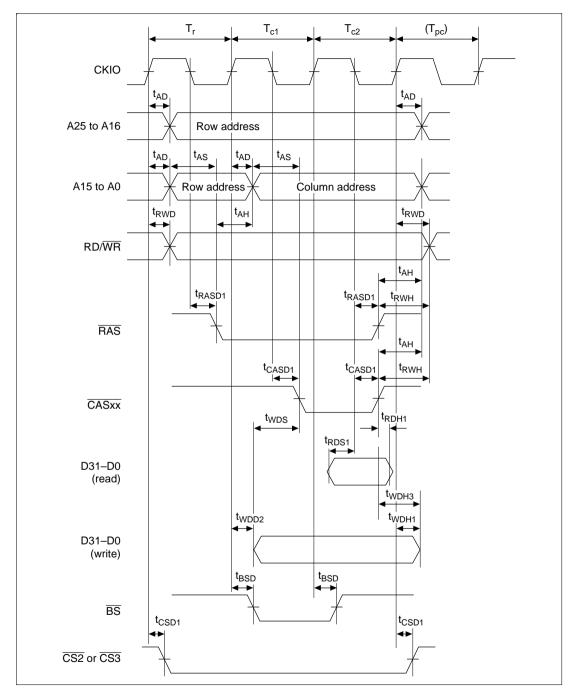

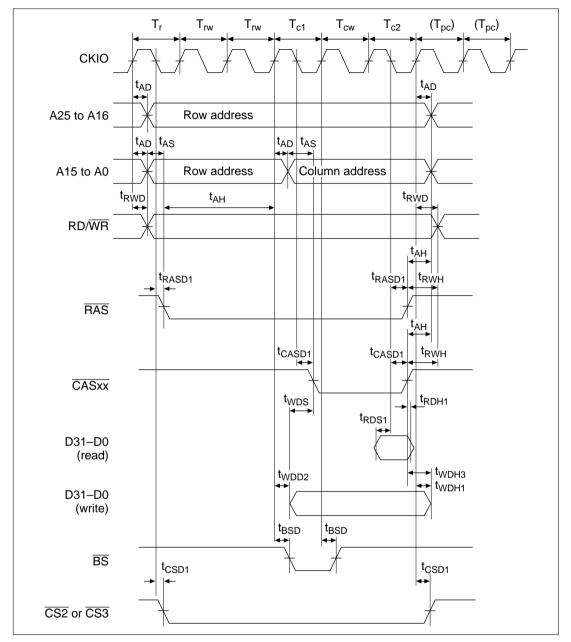

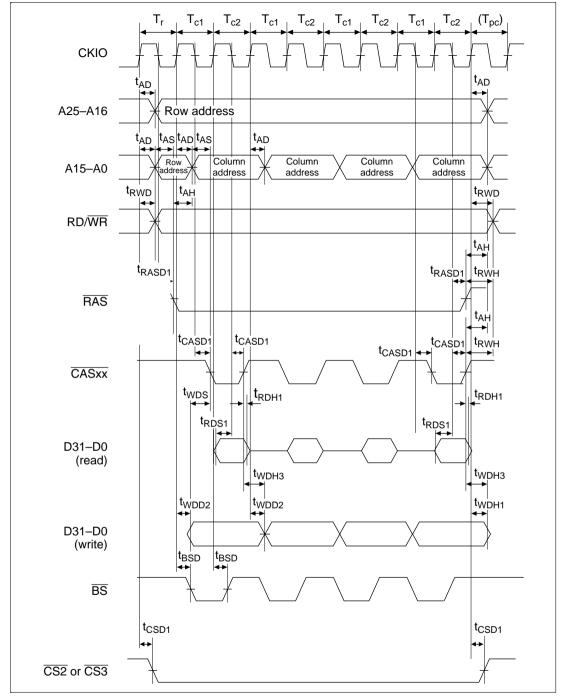

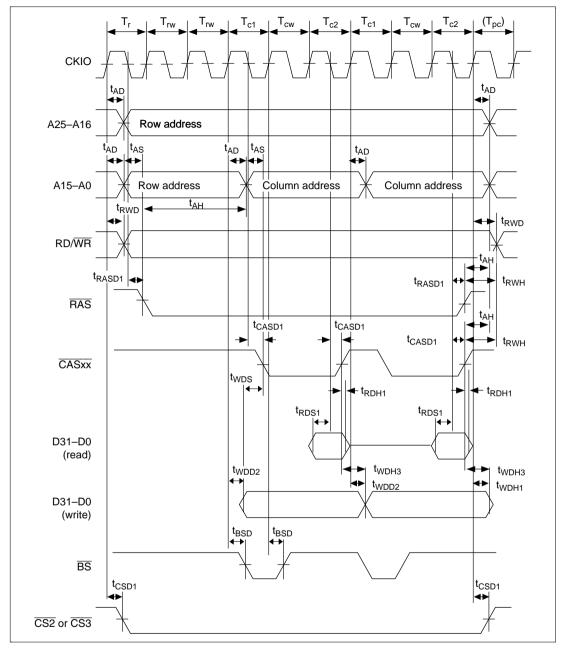

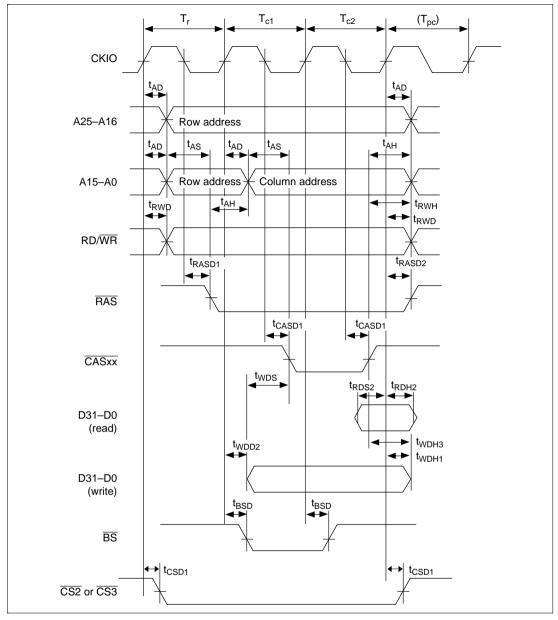

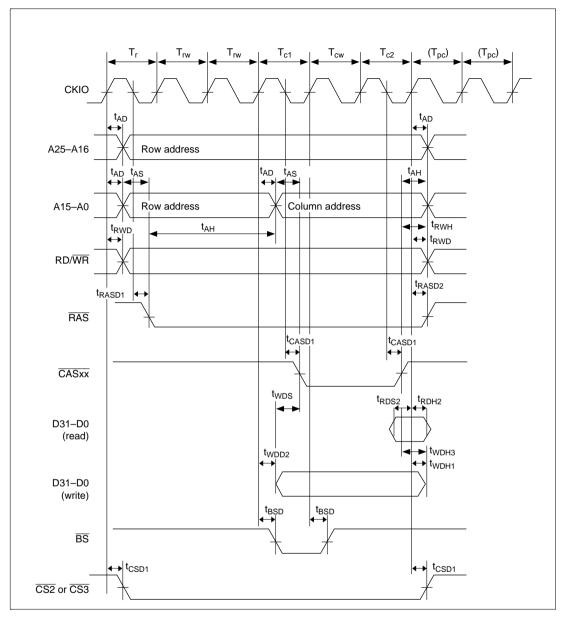

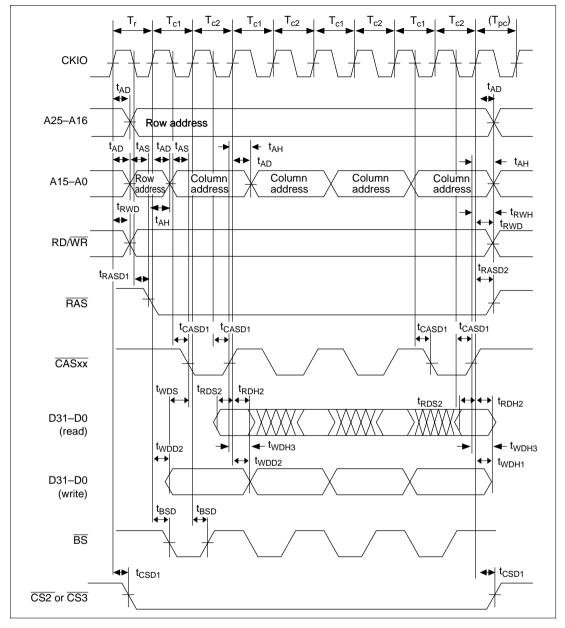

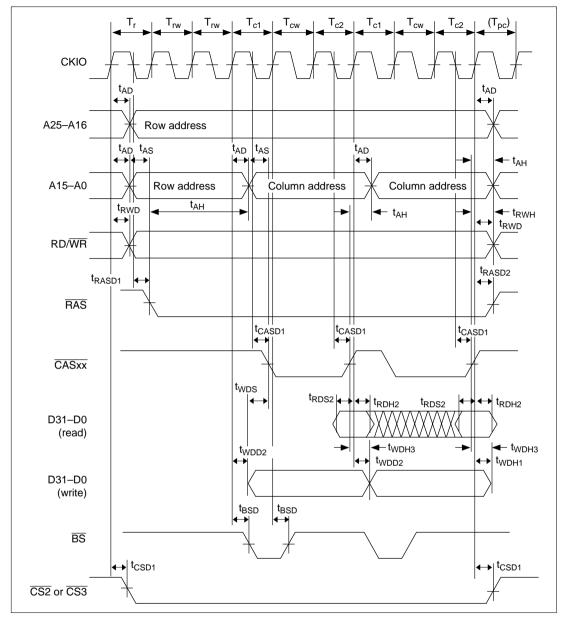

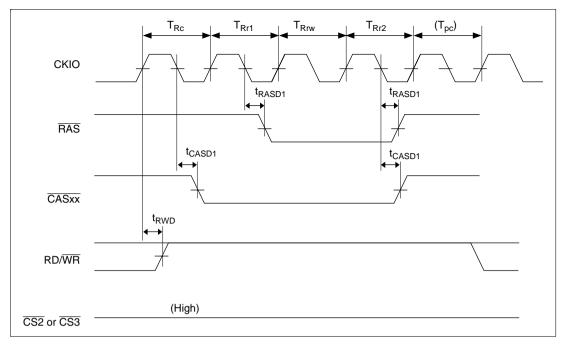

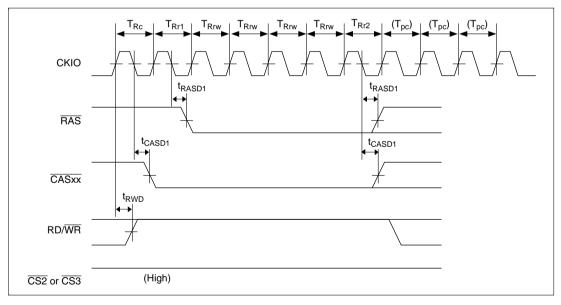

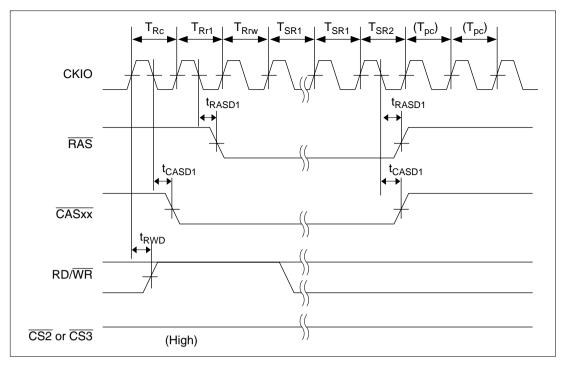

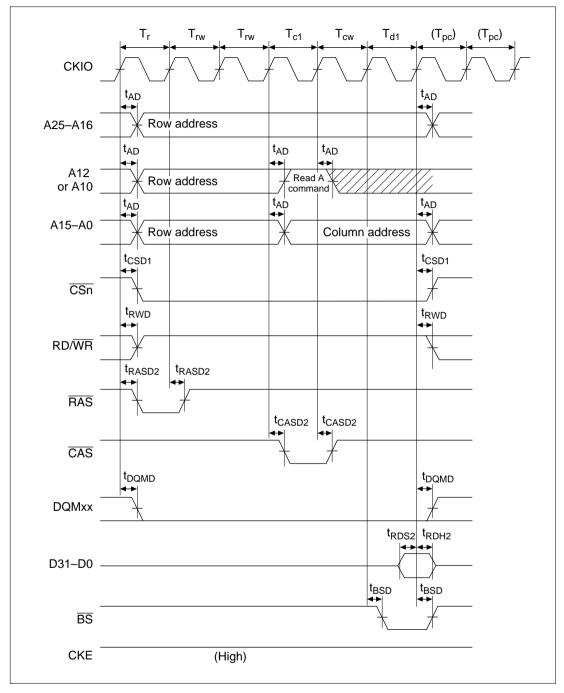

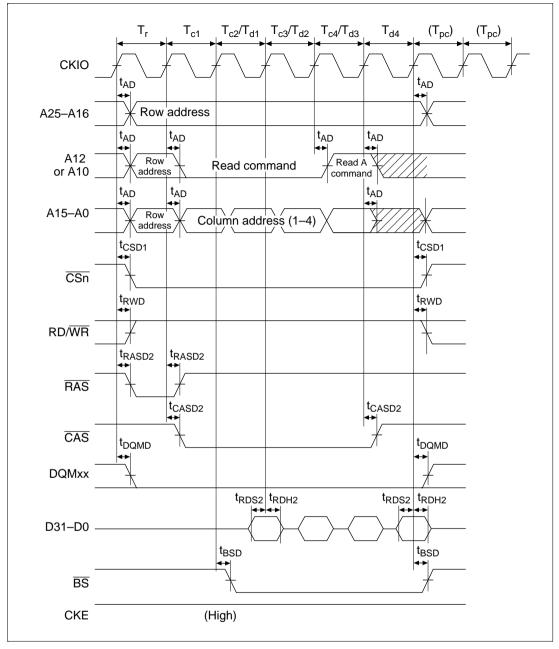

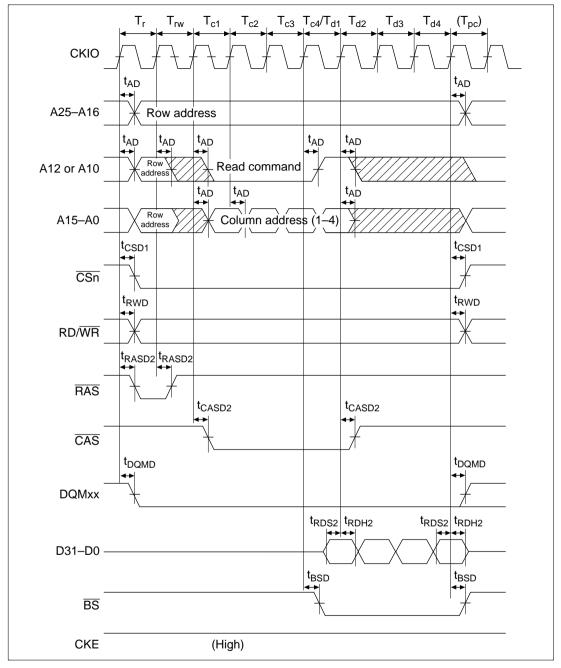

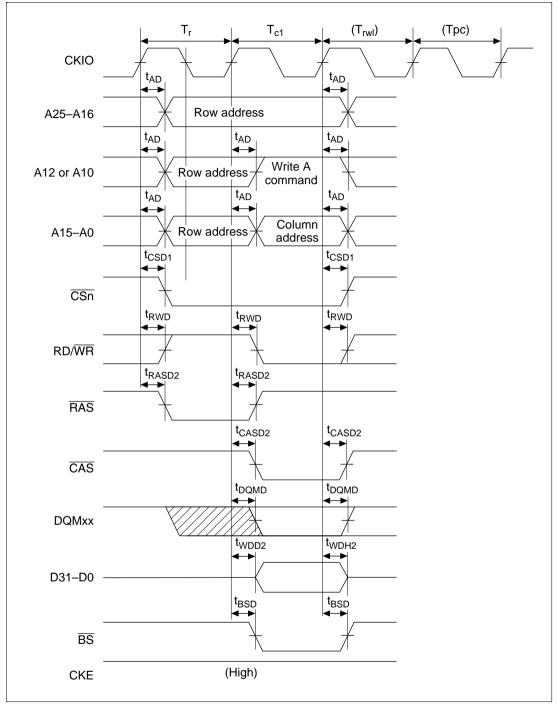

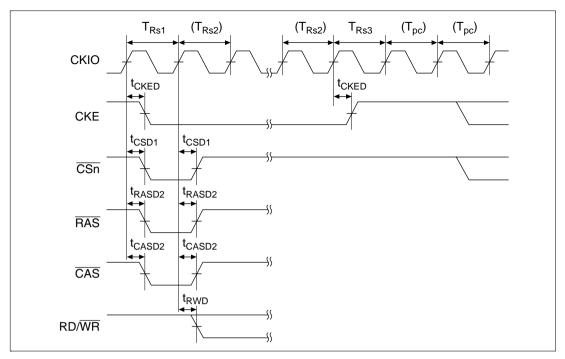

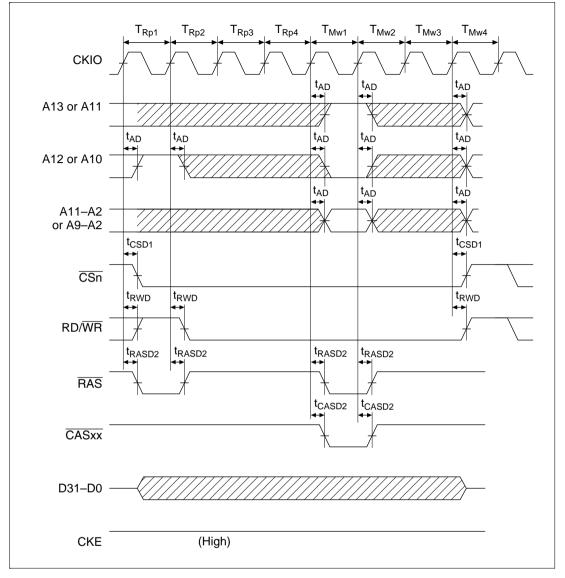

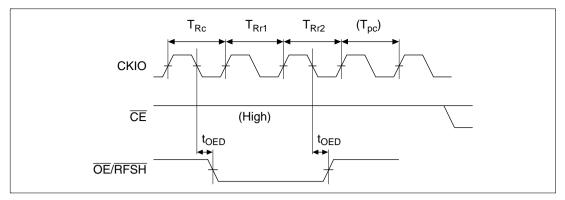

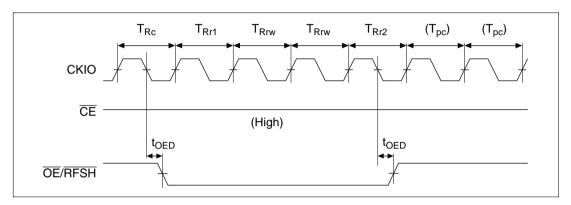

|     | 16.3.6 DRAM Timing                                                 | 458 |

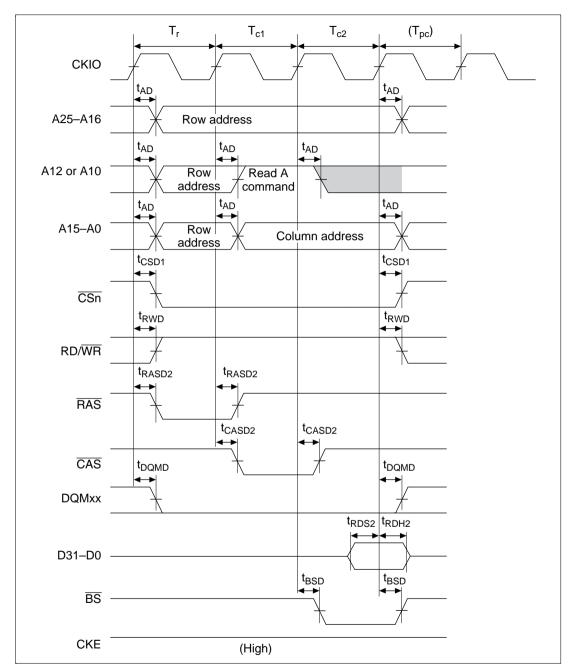

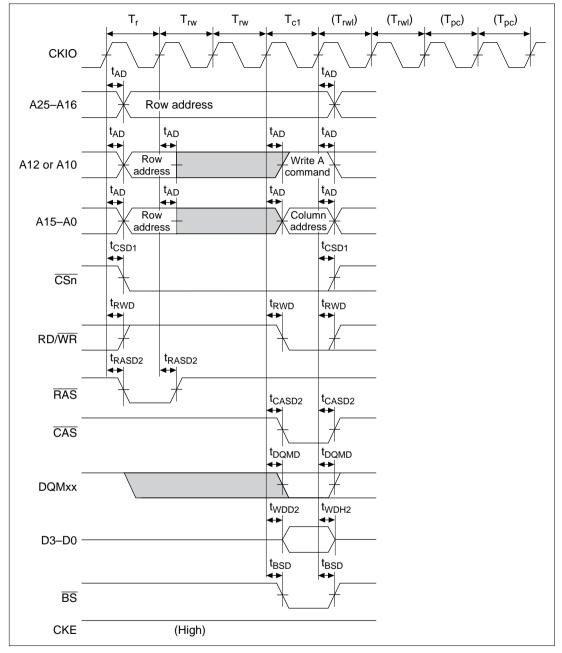

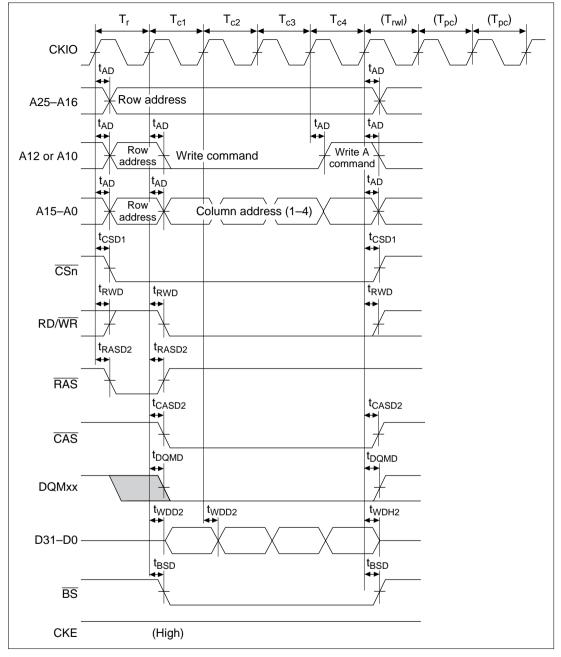

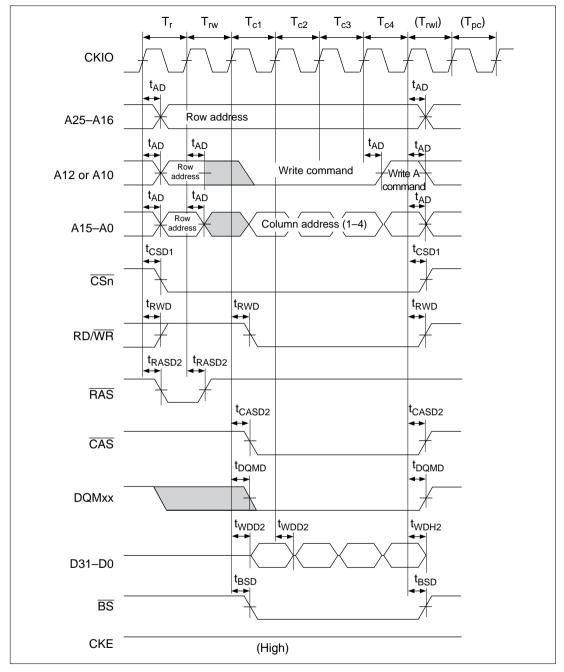

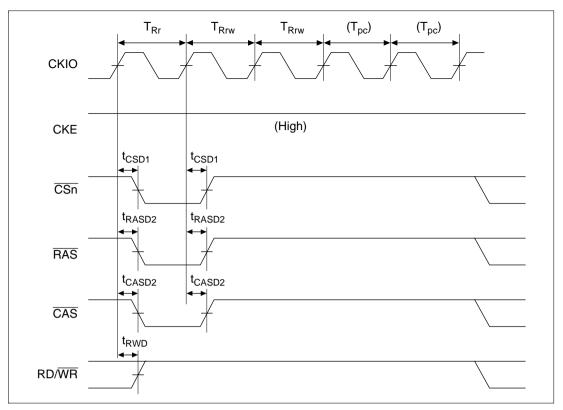

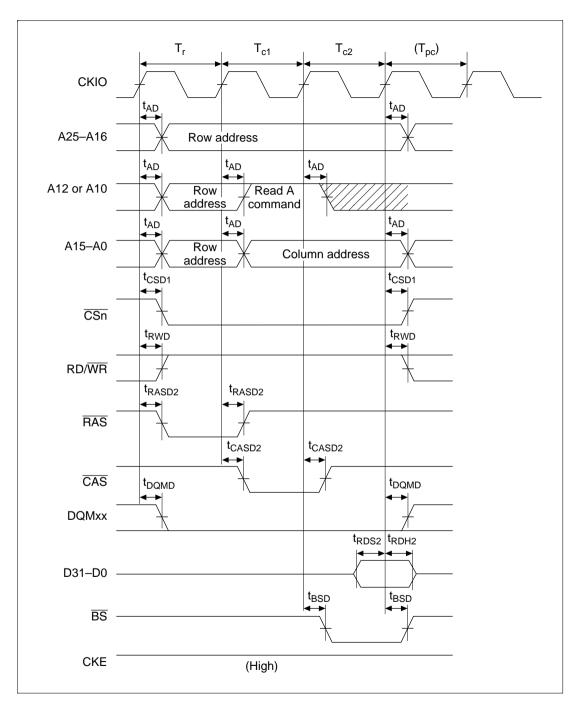

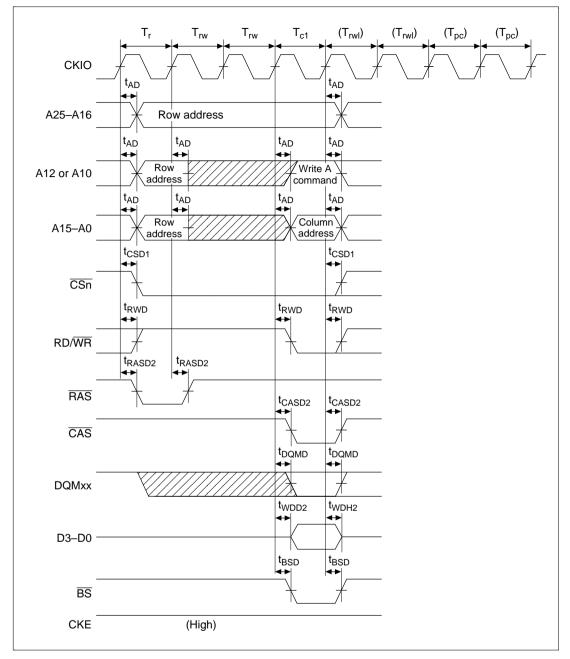

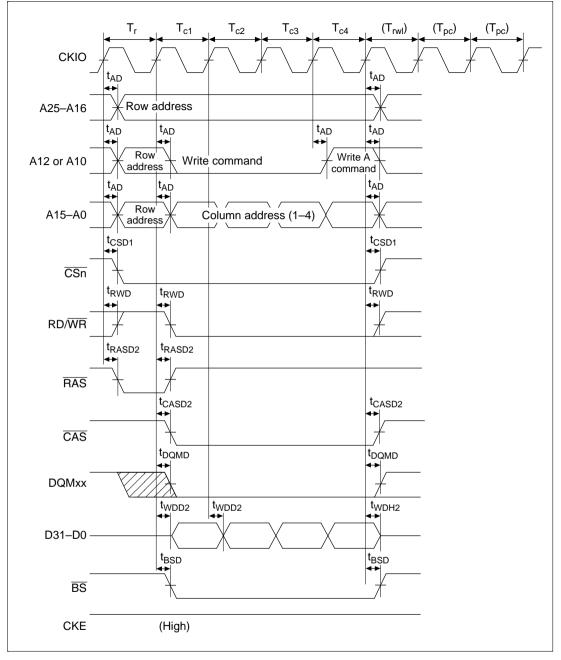

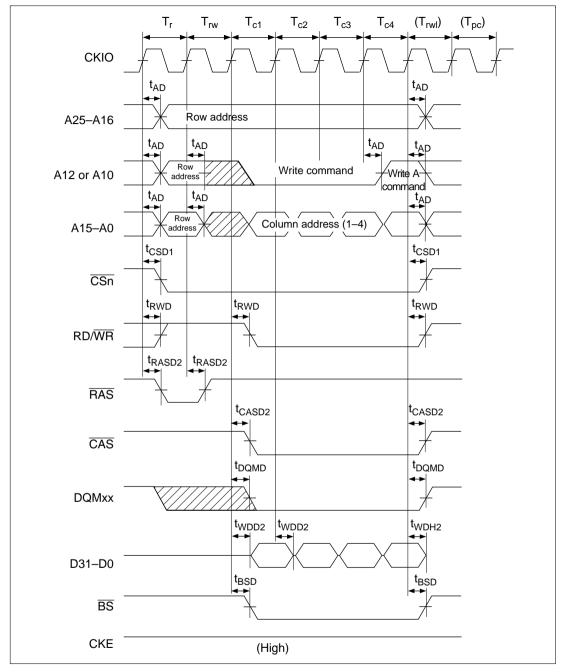

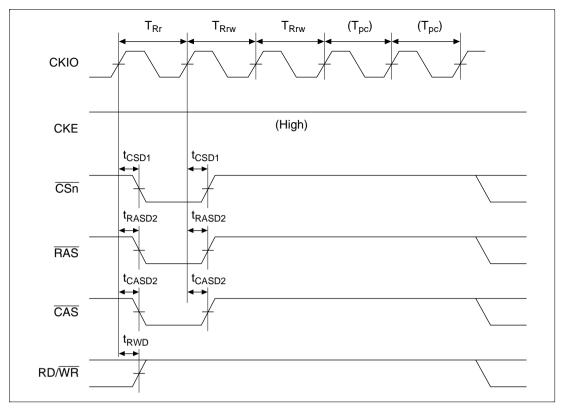

|     | 16.3.7 Synchronous DRAM Timing                                     | 468 |

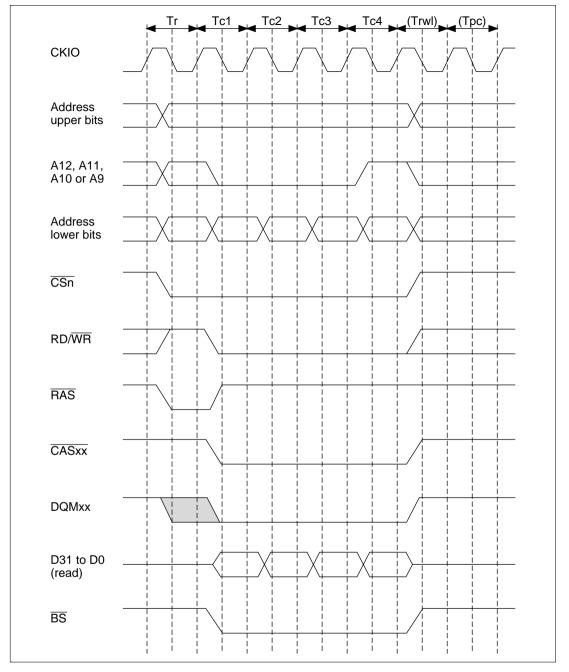

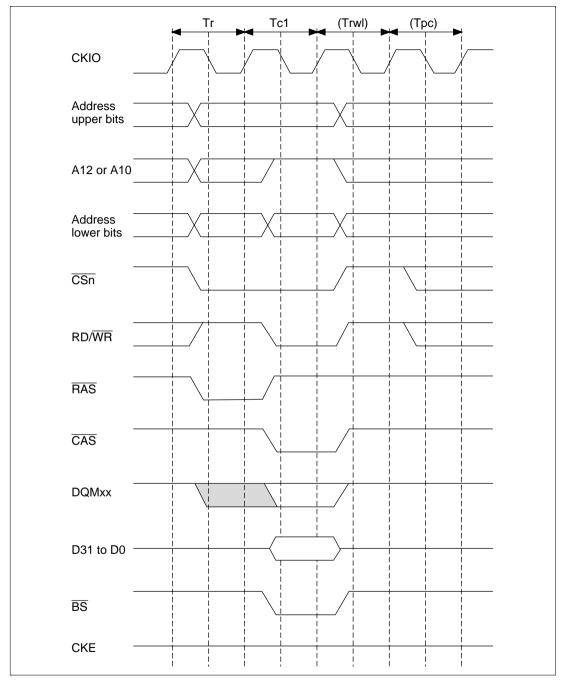

|     | 16.3.8 Pseudo-SRAM Timing                                          | 479 |

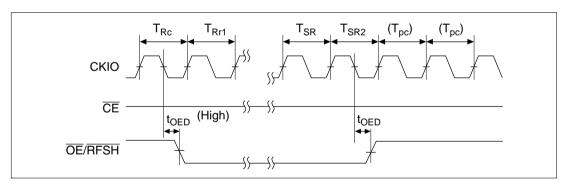

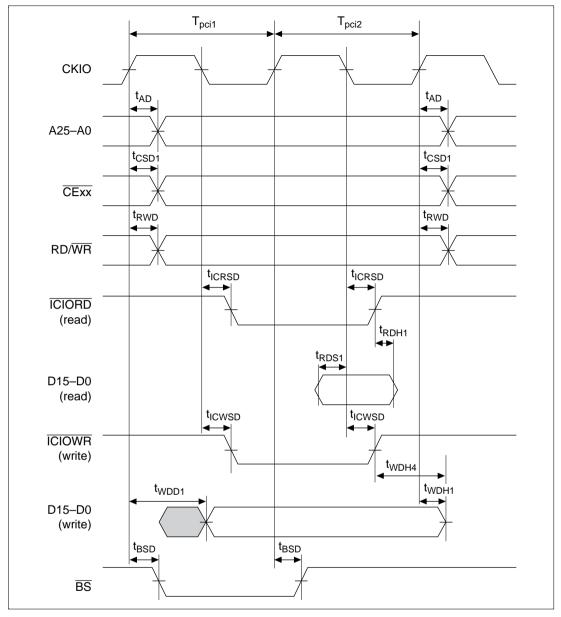

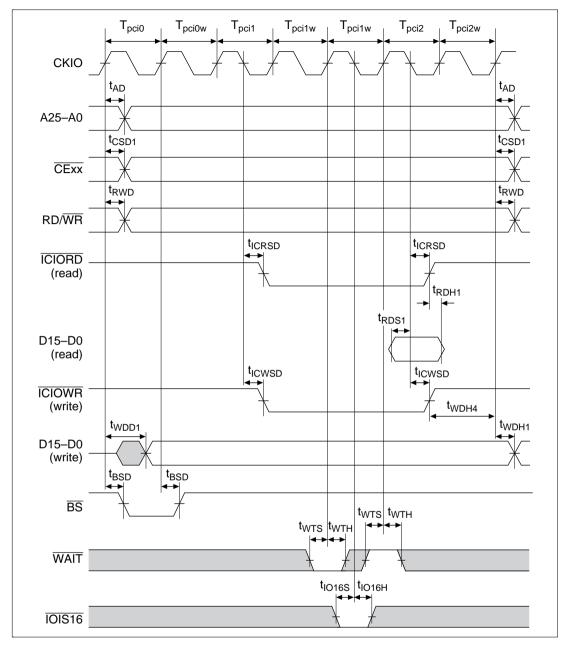

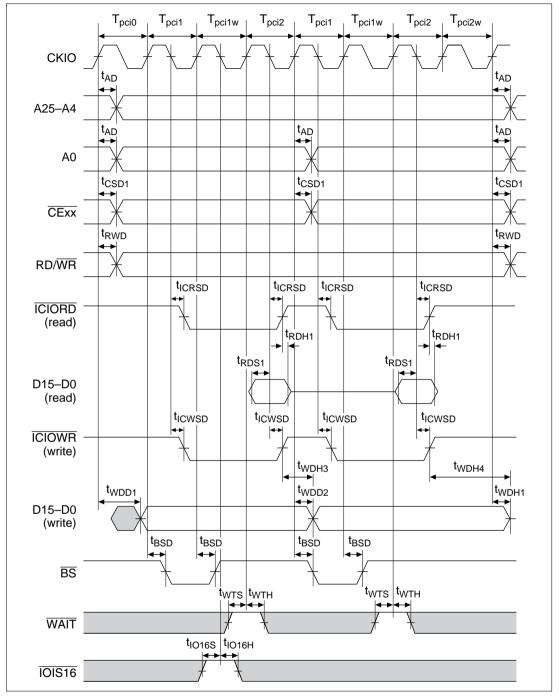

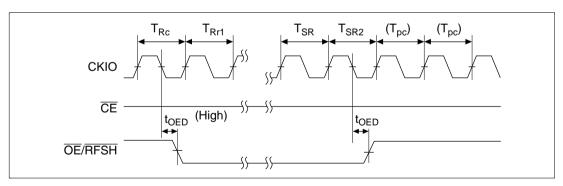

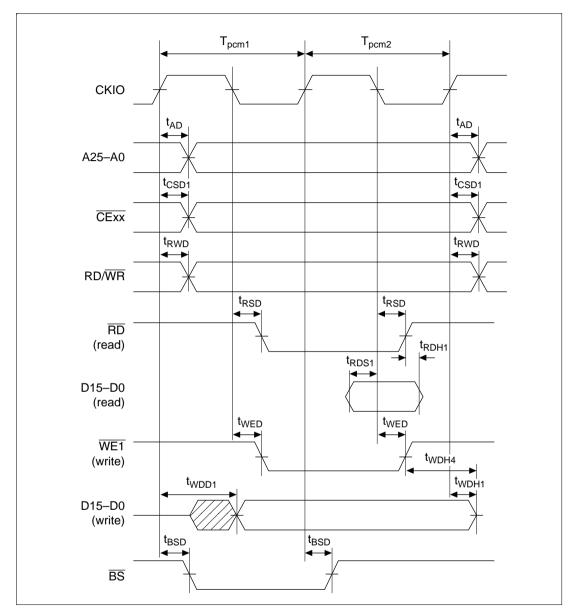

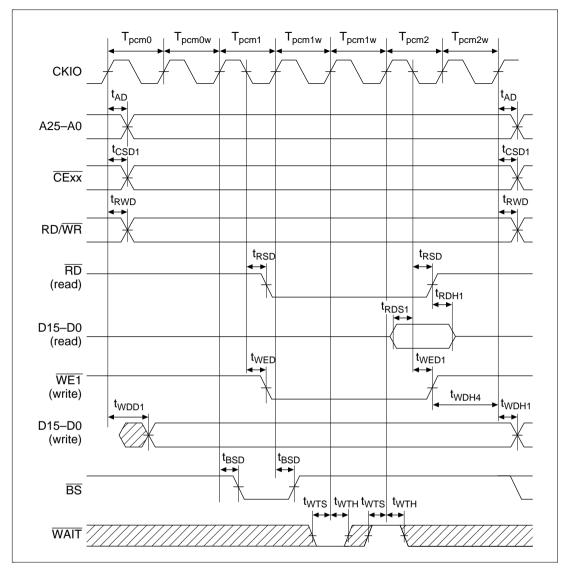

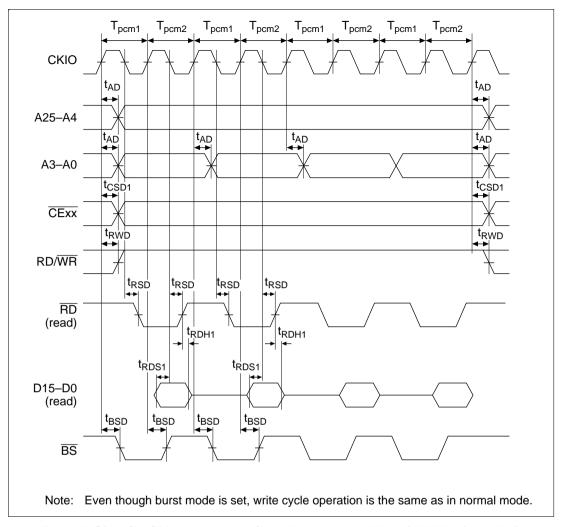

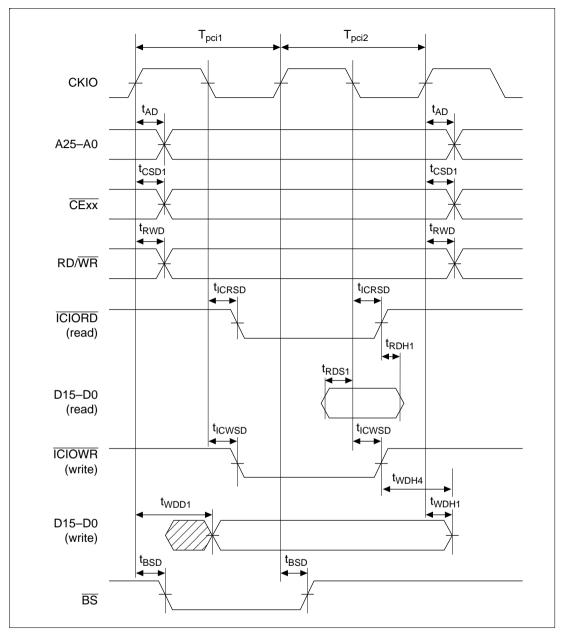

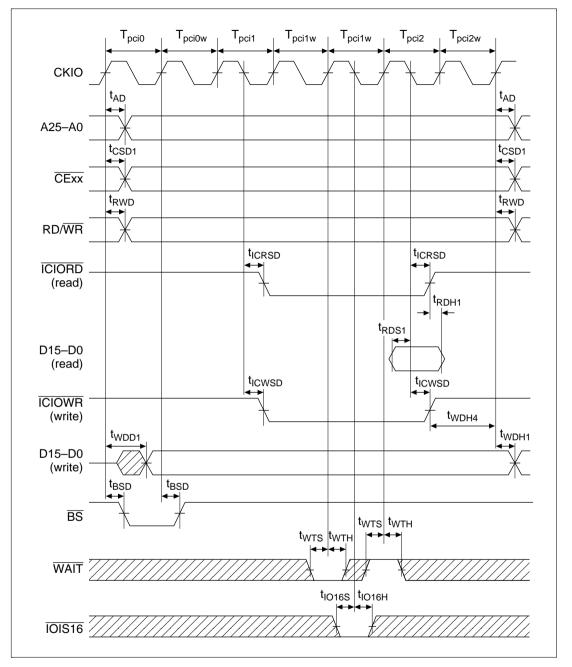

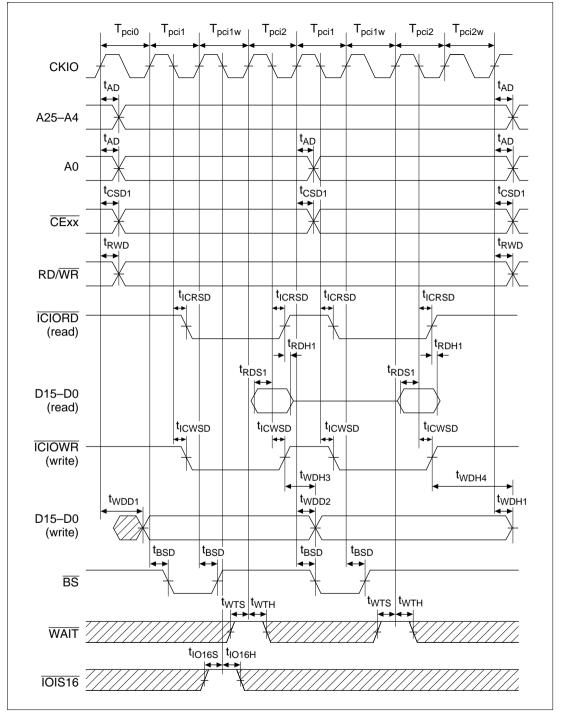

|     | 16.3.9 PCMCIA Timing                                               | 484 |

|     | 16.3.10 Peripheral Module Signal Timing                            | 491 |

|     | 16.3.11 AC Characteristics Test Conditions                         | 494 |

| Se  | on 17 Electrical Characteristics (-SH7708R-)                       | 495 |

| 17. | Absolute Maximum Ratings                                           |     |

| 17. | DC Characteristics                                                 | 496 |

| 17. | AC Characteristics                                                 |     |

|     | 17.3.1 Clock Timing                                                |     |

|     | 17.3.2 Control Signal Timing                                       |     |

|     | 17.3.3 AC Bus Timing Specifications                                |     |

|     |                                                                    | ix  |

|      | 17.3.4 Basic Timing                                   |          | 512 |

|------|-------------------------------------------------------|----------|-----|

|      | 17.3.5 Burst ROM Timing                               |          | 515 |

|      | 17.3.6 DRAM Timing                                    |          | 518 |

|      | 17.3.7 Synchronous DRAM Timing                        |          | 528 |

|      | 17.3.8 Pseudo-SRAM Timing                             |          | 539 |

|      | 17.3.9 PCMCIA Timing                                  |          | 544 |

|      | 17.3.10 Peripheral Module Signal Timing               |          |     |

|      | 17.3.11 AC Characteristics Test Conditions            |          | 554 |

|      |                                                       |          |     |

| Appe | pendix A Pin Functions                                |          | 555 |

| A.1  | Pin States                                            |          | 555 |

| A.2  | Pin Specifications                                    |          | 558 |

| A.3  |                                                       |          | 561 |

| A.4  | Pin States in Access to Each Address Space            |          | 562 |

|      |                                                       |          |     |

|      | pendix B Control Registers                            |          |     |

|      | Register Address Map                                  |          |     |

| B.2  | Register Bit List                                     |          |     |

| B.3  | Register States in Reset and Power-Down States        |          | 608 |

|      |                                                       |          |     |

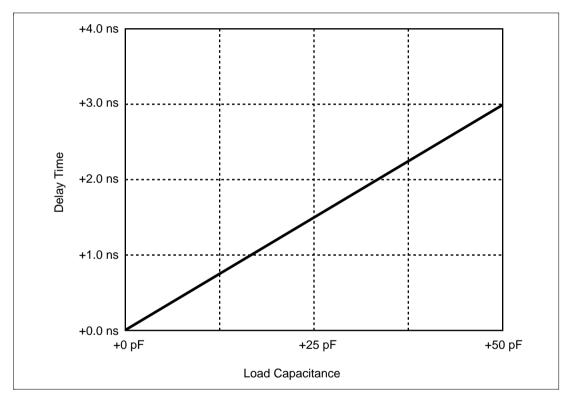

| Appe | pendix C Delay Time Variation Due to Load Capacitance | <b>)</b> | 612 |

|      |                                                       |          |     |

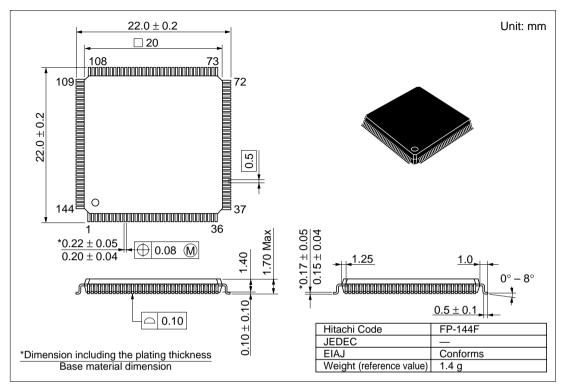

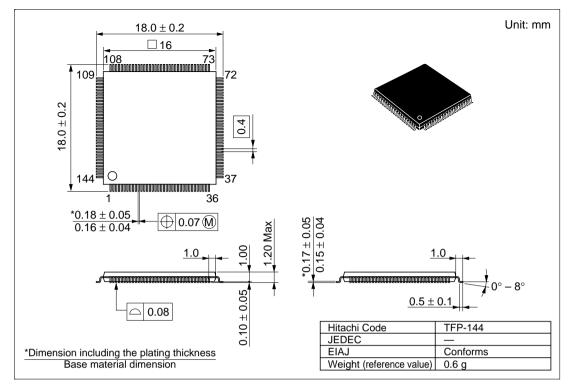

| Appe | pendix D Package Dimensions                           |          | 613 |

# Section 1 Overview and Pin Functions

#### 1.1 SH7708 Series Features

The SH7708, SH7708S, and SH7708R(SH7708 Series) are 32-bit RISC (reduced instruction set computer) microcomputers, featuring object code upward-compatibility with SH-1 and SH-2 microcomputers. The SH7708R is completely pin compatible with the SH7708S. It includes an 8-kbyte cache with a choice of write-back or write-through mode, and an MMU (memory management unit) with a 128-entry 4-way set associative TLB (translation lookaside buffer).

The SH7708 Series has an on-chip bus state controller (BSC) that allows direct connection to DRAM, synchronous DRAM (SDRAM), and pseudo-SRAM (PSRAM) without external circuitry. Its 16-bit fixed-length instruction set enables program code size to be reduced by almost 50% compared with 32-bit instructions.

The features of the SH7708 Series are summarized in table 1.1.

## **Table 1.1 SH7708 Series Features**

| Item                     | Features                                                                                               |

|--------------------------|--------------------------------------------------------------------------------------------------------|

| CPU                      | Original Hitachi SuperH RISC engine architecture                                                       |

|                          | 32-bit internal data bus                                                                               |

|                          | General-register machine                                                                               |

|                          | <ul> <li>Sixteen 32-bit general registers (eight 32-bit bank registers)</li> </ul>                     |

|                          | — Five 32-bit control registers                                                                        |

|                          | — Four 32-bit system registers                                                                         |

|                          | <ul> <li>RISC-type instruction set (upward compatibility with the SH-1 and SH-2<br/>series)</li> </ul> |

|                          | <ul> <li>Instruction length: 16-bit fixed length for improved code efficiency</li> </ul>               |

|                          | <ul> <li>Load-store architecture</li> </ul>                                                            |

|                          | <ul> <li>Delayed branch instructions</li> </ul>                                                        |

|                          | <ul> <li>C-oriented instruction set</li> </ul>                                                         |

|                          | Instruction execution time: one instruction/cycle for basic instructions                               |

|                          | <ul> <li>Logical address space: 4 Gbytes (448-Mbyte actual memory space)</li> </ul>                    |

|                          | Space identifier ASID: 8 bits, 256 logical address spaces                                              |

|                          | On-chip multiplier                                                                                     |

|                          | Five-stage pipeline                                                                                    |

| Operating modes,         | , , ,                                                                                                  |

| clock pulse<br>generator | doubling circuit, or a clock output by combining them by PLL synchronization                           |

|                          | Processing states: -                                                                                   |

|                          | Power-on reset state                                                                                   |

|                          | Manual reset state                                                                                     |

|                          | Exception processing state                                                                             |

|                          | Program execution state                                                                                |

|                          | — Power-down state                                                                                     |

|                          | — Bus-released state                                                                                   |

|                          | Power-down modes:                                                                                      |

|                          | — Sleep mode                                                                                           |

|                          | — Standby mode                                                                                         |

|                          | Hardware Standby mode(SH7708S, SH7708R only)  On this shade water agreement.                           |

|                          | On-chip clock pulse generator                                                                          |

|                          | One watchdog timer channel                                                                             |

# Table 1.1 SH7708 Series Features (cont)

| Item                | Features                                                                                                                    |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Memory              | 4 Gbytes of address space, 256 address spaces (8-bit ASID)                                                                  |  |  |  |  |

| management          | Supports single virtual memory mode and multiple virtual memory mode                                                        |  |  |  |  |

| unit (MMU)          | Paging system                                                                                                               |  |  |  |  |

|                     | Supports multiple page sizes: 1 or 4 kbytes                                                                                 |  |  |  |  |

|                     | 128-entry, 4-way set associative TLB                                                                                        |  |  |  |  |

|                     | <ul> <li>Supports software selection of replacement method and random-replacement algorithms</li> </ul>                     |  |  |  |  |

|                     | <ul> <li>Contents of TLB are directly accessible by address mapping</li> </ul>                                              |  |  |  |  |

| Cache memory        | Choice of operating mode                                                                                                    |  |  |  |  |

|                     | Normal mode (8-kbyte cache)                                                                                                 |  |  |  |  |

|                     | <ul> <li>RAM mode (4-kbyte cache + 4-kbyte RAM)</li> </ul>                                                                  |  |  |  |  |

|                     | Mixed instruction/data, 128 entries, 16-byte block length                                                                   |  |  |  |  |

|                     | <ul> <li>4-way set associative (8-kbyte cache)</li> </ul>                                                                   |  |  |  |  |

|                     | <ul> <li>2-way set associative (4-kbyte cache)</li> </ul>                                                                   |  |  |  |  |

|                     | <ul> <li>Selectable write method (write-back/write-through), LRU (least recently used)<br/>replacement algorithm</li> </ul> |  |  |  |  |

|                     | Single-stage write-back buffer                                                                                              |  |  |  |  |

|                     | <ul> <li>Contents of TLB can be accessed directly by address mapping (can be used<br/>as on-chip memory)</li> </ul>         |  |  |  |  |

| Interrupt           | 5 external interrupt pins (NMI, IRL0 to IRL3)                                                                               |  |  |  |  |

| controller          | Encoded input of 15 external interrupt sources via pins IRL0 to IRL3                                                        |  |  |  |  |

| (INTC)              | On-chip peripheral interrupts: priority levels set for each module                                                          |  |  |  |  |

| User break          | Supports debugging by user break interrupts                                                                                 |  |  |  |  |

| controller<br>(UBC) | 2 break channels                                                                                                            |  |  |  |  |

|                     | <ul> <li>Addresses, data values, type of access, and data size can all be set as break<br/>conditions</li> </ul>            |  |  |  |  |

|                     | Supports a sequential break function                                                                                        |  |  |  |  |

**Table 1.1** SH7708 Series Features (cont)

| Item                   | Features                                                                                                                                                    |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bus state              | Supports external memory access                                                                                                                             |  |  |  |

| controller<br>(BSC)    | — 32/16/8-bit external data bus                                                                                                                             |  |  |  |

| (500)                  | <ul> <li>Physical address space divided into seven areas, each a maximum 64</li> <li>Mbytes, with the following features settable for each area:</li> </ul> |  |  |  |

|                        | — Bus size (8, 16, or 32 bits)                                                                                                                              |  |  |  |

|                        | <ul> <li>Number of wait cycles (also supports a hardware wait function)</li> </ul>                                                                          |  |  |  |

|                        | <ul> <li>Setting the type of space enables direct connection to DRAM,<br/>synchronous DRAM, pseudo-SRAM, and burst ROM</li> </ul>                           |  |  |  |

|                        | <ul> <li>Supports fast page mode and EDO for DRAM</li> </ul>                                                                                                |  |  |  |

|                        | Supports PCMCIA interface                                                                                                                                   |  |  |  |

|                        | <ul> <li>Outputs chip select signal (CS0–CS6) for corresponding area</li> </ul>                                                                             |  |  |  |

|                        | DRAM/synchronous DRAM/pseudo-SRAM refresh function                                                                                                          |  |  |  |

|                        | Programmable refresh interval                                                                                                                               |  |  |  |

|                        | <ul> <li>Supports CAS-before-RAS refresh and self-refresh modes</li> </ul>                                                                                  |  |  |  |

|                        | <ul> <li>DRAM/synchronous DRAM/pseudo-SRAM burst access function</li> </ul>                                                                                 |  |  |  |

|                        | Usable as either big- or little-endian machine                                                                                                              |  |  |  |

| Timer                  | 3-channel auto-reload type 32-bit timer                                                                                                                     |  |  |  |

|                        | Input capture function                                                                                                                                      |  |  |  |

|                        | 6 types of counter input clock can be selected                                                                                                              |  |  |  |

|                        | Maximum resolution: 2 MHz                                                                                                                                   |  |  |  |

| Realtime clock         | On-chip clock and calendar functions                                                                                                                        |  |  |  |

| (RTC)                  | <ul> <li>On-chip 32-kHz crystal oscillator circuit with a maximum resolution (interrupt<br/>cycle) of 1/256 second</li> </ul>                               |  |  |  |

| Serial communi-        | Selection of asynchronous or synchronous mode                                                                                                               |  |  |  |

| cation interface (SCI) | Full-duplex communication                                                                                                                                   |  |  |  |

| (001)                  | Supports smart card interface                                                                                                                               |  |  |  |

| Package                | 144-pin plastic QFP(FP-144)                                                                                                                                 |  |  |  |

|                        | 144-pin plastic TQFP (TFP-144)*                                                                                                                             |  |  |  |

Note: \* SH7708S only

**Table 1.1** SH7708 Series Features (cont)

| Item               | Features          |                     |                        |                 |                 |                                       |

|--------------------|-------------------|---------------------|------------------------|-----------------|-----------------|---------------------------------------|

| Product<br>Line-up | Product<br>Number | On-chip<br>Voltage  | Operation<br>Frequency | Mask<br>Version | Model           | Package                               |

|                    | SH7708            | 3.3V±0.3V           | 60MHz                  | _               | HD6417708F60    | 144-pin<br>Plastic LQFP<br>(FP-144F)  |

|                    | SH7708S           | 3.3V±0.3V           | 60MHz                  | _               | HD6417708SF60   | -                                     |

|                    |                   |                     |                        | _               | HD6417708STF60  | 144-pin<br>Plastic TQFP<br>(TFP-144)  |

|                    | SH7708R           | 3.15-3.6V<br>(typ.) | 100MHz                 | _               | HD6417708RF100  | 144-pin<br>Plastic L-QFP<br>(FP-144F) |

|                    |                   |                     |                        | A-mask          | HD6417708RF100A | -                                     |

# 1.2 Block Diagram

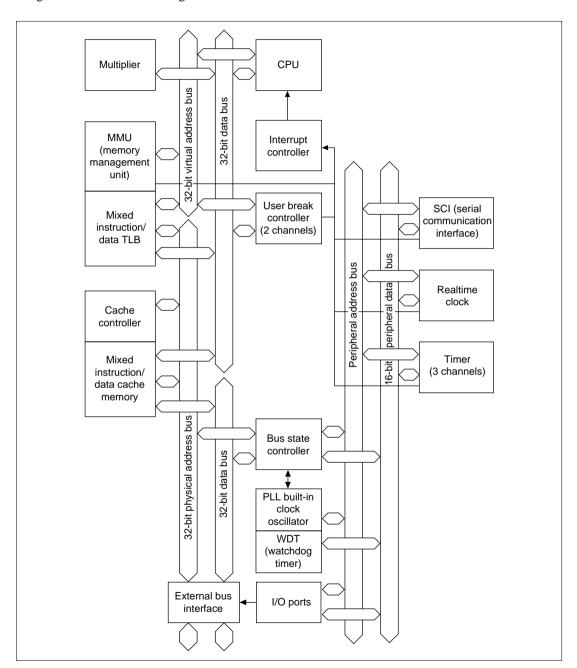

Figure 1.1 shows a block diagram of the SH7708 Series.

Figure 1.1 SH7708 Series Block Diagram

### 1.3 Pin Description

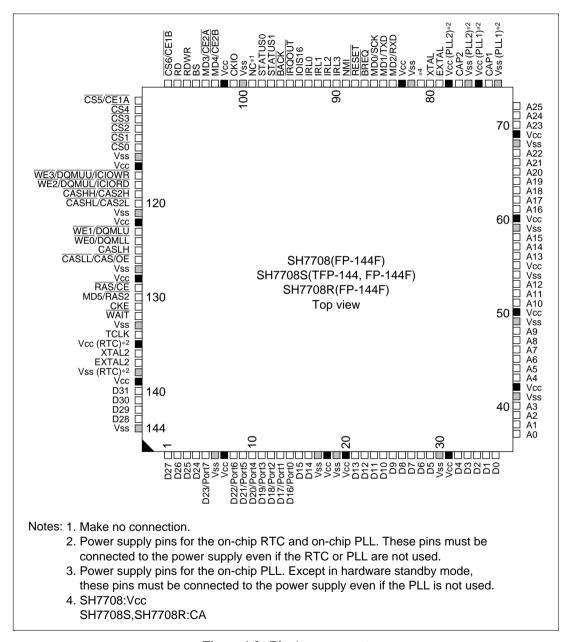

#### 1.3.1 Pin Arrangement

Figure 1.2 Pin Arrangement

# 1.3.2 SH7708 Series Pin Functions

**Table 1.2** SH7708 Series Pin Functions

| No. | Terminal        | I/O   | Description   |

|-----|-----------------|-------|---------------|

| 1   | D27             | I/O   | Data bus      |

| 2   | D26             | I/O   | Data bus      |

| 3   | D25             | I/O   | Data bus      |

| 4   | D24             | I/O   | Data bus      |

| 5   | D23/Port7       | I/O   | Data bus/port |

| 6   | V <sub>SS</sub> | Power | Power (0 V)   |

| 7   | V <sub>CC</sub> | Power | Power (3.3 V) |

| 8   | D22/Port6       | I/O   | Data bus/port |

| 9   | D21/Port5       | I/O   | Data bus/port |

| 10  | D20/Port4       | I/O   | Data bus/port |

| 11  | D19/Port3       | I/O   | Data bus/port |

| 12  | D18/Port2       | I/O   | Data bus/port |

| 13  | D17/Port1       | I/O   | Data bus/port |

| 14  | D16/Port0       | I/O   | Data bus/port |

| 15  | D15             | I/O   | Data bus      |

| 16  | D14             | I/O   | Data bus      |

| 17  | V <sub>SS</sub> | Power | Power (0 V)   |

| 18  | $V_{CC}$        | Power | Power (3.3 V) |

| 19  | V <sub>SS</sub> | Power | Power (0 V)   |

| 20  | V <sub>CC</sub> | Power | Power (3.3 V) |

| 21  | D13             | I/O   | Data bus      |

| 22  | D12             | I/O   | Data bus      |

| 23  | D11             | I/O   | Data bus      |

| 24  | D10             | I/O   | Data bus      |

| 25  | D9              | I/O   | Data bus      |

| 26  | D8              | I/O   | Data bus      |

| 27  | D7              | I/O   | Data bus      |

| 28  | D6              | I/O   | Data bus      |

| 29  | D5              | I/O   | Data bus      |

Table 1.2 SH7708 Series Pin Functions (cont)

| No. | Terminal        | I/O   | Description   |

|-----|-----------------|-------|---------------|

| 30  | V <sub>SS</sub> | Power | Power (0 V)   |

| 31  | V <sub>CC</sub> | Power | Power (3.3 V) |

| 32  | D4              | I/O   | Data bus      |

| 33  | D3              | I/O   | Data bus      |

| 34  | D2              | I/O   | Data bus      |

| 35  | D1              | I/O   | Data bus      |

| 36  | D0              | I/O   | Data bus      |

| 37  | A0              | 0     | Address bus   |

| 38  | A1              | 0     | Address bus   |

| 39  | A2              | 0     | Address bus   |

| 40  | A3              | 0     | Address bus   |

| 41  | V <sub>SS</sub> | Power | Power (0 V)   |

| 42  | V <sub>CC</sub> | Power | Power (3.3 V) |

| 43  | A4              | 0     | Address bus   |

| 44  | A5              | 0     | Address bus   |

| 45  | A6              | 0     | Address bus   |

| 46  | A7              | 0     | Address bus   |

| 47  | A8              | 0     | Address bus   |

| 48  | A9              | 0     | Address bus   |

| 49  | V <sub>SS</sub> | Power | Power (0 V)   |

| 50  | $V_{CC}$        | Power | Power (3.3 V) |

| 51  | A10             | 0     | Address bus   |

| 52  | A11             | 0     | Address bus   |

| 53  | A12             | 0     | Address bus   |

| 54  | $V_{SS}$        | Power | Power (0 V)   |

| 55  | V <sub>CC</sub> | Power | Power (3.3 V) |

| 56  | A13             | 0     | Address bus   |

| 57  | A14             | 0     | Address bus   |

| 58  | A15             | 0     | Address bus   |

| 59  | V <sub>SS</sub> | Power | Power (0 V)   |

| 60  | V <sub>CC</sub> | Power | Power (3.3 V) |

**Table 1.2** SH7708 Series Pin Functions (cont)

| No.                     | Terminal                 | I/O   | Description                           |

|-------------------------|--------------------------|-------|---------------------------------------|

| 61                      | A16                      | 0     | Address bus                           |

| 62                      | A17                      | 0     | Address bus                           |

| 63                      | A18                      | 0     | Address bus                           |

| 64                      | A19                      | 0     | Address bus                           |

| 65                      | A20                      | 0     | Address bus                           |

| 66                      | A21                      | 0     | Address bus                           |

| 67                      | A22                      | 0     | Address bus                           |

| 68                      | V <sub>SS</sub>          | Power | Power (0 V)                           |

| 69                      | V <sub>CC</sub>          | Power | Power (3.3 V)                         |

| 70                      | A23                      | 0     | Address bus                           |

| 71                      | A24                      | 0     | Address bus                           |

| 72                      | A25                      | 0     | Address bus                           |

| 73                      | V <sub>SS</sub> (PLL1)*2 | Power | Power (0 V) for PLL1                  |

| 74                      | CAP1                     | 0     | External capacitance pin for PLL1     |

| 75                      | V <sub>CC</sub> (PLL1)*2 | Power | Power (3.3 V) for PLL1                |

| 76                      | V <sub>SS</sub> (PLL2)*2 | Power | Power (0 V) for PLL2                  |

| 77                      | CAP2                     | 0     | External capacitance pin for PLL2     |

| 78                      | V <sub>CC</sub> (PLL2)*2 | Power | Power (3.3 V) for PLL2                |

| 79                      | EXTAL                    | 1     | External clock/crystal oscillator pin |

| 80                      | XTAL                     | 0     | Crystal oscillator pin                |

| 81(SH7708)              | V <sub>CC</sub>          | Power | Power(3.3V)                           |

| 81(SH7708S,<br>SH7708R) | CA                       | I     | Chip active                           |

| 82                      | V <sub>SS</sub>          | Power | Power (0 V)                           |

| 83                      | V <sub>CC</sub>          | Power | Power (3.3 V)                         |

| 84                      | MD2/RXD                  | 1     | Operating mode pin/serial data input  |

| 85                      | MD1/TXD                  | I/O   | Operating mode pin/serial data output |

| 86                      | MD0/SCK                  | I/O   | Operating mode pin/serial clock       |

| 87                      | BREQ                     | 1     | Bus request                           |

| 88                      | RESET                    | 1     | Reset                                 |

| 89                      | NMI                      | 1     | Nonmaskable interrupt request         |

| 90                      | ĪRL3                     | I     | External interrupt source input       |

Table 1.2 SH7708 Series Pin Functions (cont)

| No. | Terminal         | I/O   | Description                       |

|-----|------------------|-------|-----------------------------------|

| 91  | IRL2             | I     | External interrupt source input   |

| 92  | ĪRL1             | Ī     | External interrupt source input   |

| 93  | ĪRL0             | I     | External interrupt source input   |

| 94  | IOIS16           | I     | IO16-bit instruction              |

| 95  | IRQOUT           | 0     | Bus request notification output   |

| 96  | BACK             | 0     | Bus acknowledge                   |

| 97  | STATUS1          | 0     | Processor status                  |

| 98  | STATUS0          | 0     | Processor status                  |

| 99  | NC               | 0     | Leave unconnected                 |

| 100 | V <sub>SS</sub>  | Power | Power (0 V)                       |

| 101 | CKIO             | I/O   | System clock I/O                  |

| 102 | V <sub>CC</sub>  | Power | Power (3.3 V)                     |

| 103 | MD4/CE2B         | I/O   | Operating mode pin/PCMCIA CE pin  |

| 104 | MD3/CE2A         | I/O   | Operating mode pin/PCMCIA CE pin  |

| 105 | BS               | 0     | Bus cycle start                   |

| 106 | RD/WR            | 0     | Read/write                        |

| 107 | RD               | 0     | Read pulse                        |

| 108 | CS6/CE1B         | 0     | Chip select 6/PCMCIA CE pin       |

| 109 | CS5/CE1A         | 0     | Chip select 5/PCMCIA CE pin       |

| 110 | CS4              | 0     | Chip select 4                     |

| 111 | CS3              | 0     | Chip select 3                     |

| 112 | CS2              | 0     | Chip select 2                     |

| 113 | CS1              | 0     | Chip select 1                     |

| 114 | CS0              | 0     | Chip select 0                     |

| 115 | V <sub>SS</sub>  | Power | Power (0 V)                       |

| 116 | V <sub>CC</sub>  | Power | Power (3.3 V)                     |

| 117 | WE3/DQMUU/ICIOWR | 0     | D31-D24 selection signal/IO write |

| 118 | WE2/DQMUL/ICIORD | 0     | D23-D16 selection signal/IO read  |

| 119 | CASHH/CAS2H      | 0     | D31–D24/D15–D8 selection signal   |

| 120 | CASHL/CAS2L      | 0     | D23-D16/D7-D0 selection signal    |

| 121 | V <sub>SS</sub>  | Power | Power (0 V)                       |

**Table 1.2** SH7708 Series Pin Functions (cont)

| 122 V <sub>C</sub> |             |       |                                         |

|--------------------|-------------|-------|-----------------------------------------|