# **24LCS21A**

# 1K 2.5V Dual Mode I<sup>2</sup>C<sup>™</sup> Serial EEPROM

#### Features:

- · Single Supply with Operation Down to 2.5V

- Completely Implements DDC1™/DDC2™ Interface for Monitor Identification, Including Recovery to DDC1

- · Low-Power CMOS Technology:

- 1 mA active current, typical

- 10 μA standby current, typical at 5.5V

- 2-Wire Serial Interface Bus, I<sup>2</sup>C<sup>™</sup> Compatible

- 100 kHz (2.5V) and 400 kHz (5V) Compatibility

- · Self-Timed Write Cycle (including Auto-Erase)

- · Hardware Write-Protect Pin

- Page Write Buffer for up to Eight Bytes

- 1,000,000 Erase/Write Cycles Ensured

- Data Retention > 200 years

- ESD Protection > 4000V

- · 8-pin PDIP and SOIC Package

- · Available for Extended Temperature Ranges:

- Industrial (I): -40°C to +70°C

- · Pb-Free and RoHS Compliant

#### **Description:**

The Microchip Technology Inc. 24LCS21A is a 128 x 8-bit dual-mode Electrically Erasable PROM. This device is designed for use in applications requiring storage and serial transmission of configuration and control information. Two modes of operation have been implemented: Transmit-Only mode and Bidirectional mode. Upon power-up, the device will be in the Transmit-Only mode, sending a serial bit stream of the memory array from 00h to 7Fh, clocked by the VCLK pin. A valid high-to-low transition on the SCL pin will cause the device to enter the Transition mode and look for a valid control byte on the I<sup>2</sup>C bus. If it detects a valid control byte from the master, it will switch into Bidirectional mode, with byte selectable read/write capability of the memory array using SCL. If no control byte is received, the device will revert to the Transmit-Only mode after it receives 128 consecutive VCLK pulses while the SCL pin is idle. The 24LCS21A also enables the user to write-protect the entire memory array using its write-protect pin. The 24LCS21A is available in a standard 8-pin PDIP and SOIC package in industrial temperature range.

DDC is a trademark of the Video Electronics Standards Assoc.  $I^2C$  is a trademark of Philips Corporation.

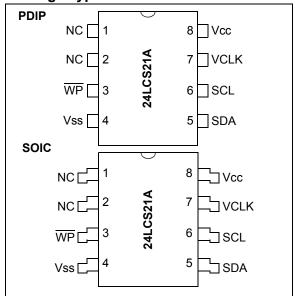

#### **Package Types**

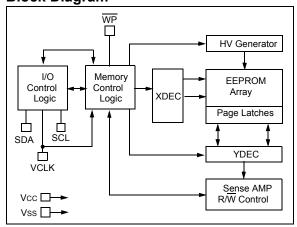

## **Block Diagram**

#### **Pin Function Table**

| Name | Function                          |

|------|-----------------------------------|

| WP   | Write-Protect (active low)        |

| Vss  | Ground                            |

| SDA  | Serial Address/Data I/O           |

| SCL  | Serial Clock (Bidirectional mode) |

| VCLK | Serial Clock (Transmit-Only mode) |

| Vcc  | +2.5V to 5.5V Power Supply        |

| NC   | No Connection                     |

#### 1.0 ELECTRICAL CHARACTERISTICS

# Absolute Maximum Ratings(†)

| Vcc                                    | 7.0\              |

|----------------------------------------|-------------------|

| All inputs and outputs w.r.t. Vss      | 0.6V to Vcc +1.0\ |

| Storage temperature                    | 65°C to +150°C    |

| Ambient temperature with power applied | 40°C to +125°C    |

| ESD protection on all pins             | ≥4 k\             |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 1-1: DC CHARACTERISTICS

| DC CHARACTERISTICS                                                         | Vcc = +2.5V to 5.5V<br>Industrial (I): TA = -40°C to +85°C |              |             |                          |                                                                          |

|----------------------------------------------------------------------------|------------------------------------------------------------|--------------|-------------|--------------------------|--------------------------------------------------------------------------|

| Parameter                                                                  | Symbol                                                     | Min          | Max         | Units                    | Conditions                                                               |

| SCL and SDA pins:<br>High-level input voltage<br>Low-level input voltage   | VIH<br>VIL                                                 | 0.7 Vcc<br>— | <br>0.3 Vcc | V<br>V                   |                                                                          |

| Input levels on VCLK pin: High-level input voltage Low-level input voltage | VIH<br>VIL                                                 | 2.0<br>—     | <br>0.2 Vcc | V<br>V                   | Vcc ≥ 2.7V (Note)<br>Vcc < 2.7V (Note)                                   |

| Hysteresis of Schmitt Trigger inputs                                       | VHYS                                                       | .05 Vcc      | _           | V                        | (Note)                                                                   |

| Low-level output voltage                                                   | Vol1                                                       | _            | 0.4         | V                        | IOL = 3 mA, VCC = 2.5V (Note)                                            |

| Low-level output voltage                                                   | Vol2                                                       | _            | 0.6         | V                        | IOL = 6 mA, VCC = 2.5V                                                   |

| Input leakage current                                                      | ILI                                                        | _            | ±1          | μΑ                       | VIN = Vss or Vcc                                                         |

| Output leakage current                                                     | ILO                                                        | _            | ±1          | μΑ                       | Vout = Vss or Vcc                                                        |

| Pin capacitance (all inputs/outputs)                                       | CIN, COUT                                                  |              | 10          | pF                       | Vcc = 5.0V ( <b>Note</b> )<br>TA = 25°C, FcLK = 1 MHz                    |

| Operating current                                                          | Icc Write<br>Icc Read                                      |              | 3<br>1      | mA<br>mA                 | Vcc = 5.5V<br>Vcc = 5.5V, SCL = 400 kHz                                  |

| Standby current                                                            | Iccs                                                       | _            | 30<br>100   | μ <b>Α</b><br>μ <b>Α</b> | Vcc = 3.0V, SDA = SCL = Vcc<br>Vcc = 5.5V, SDA = SCL = Vcc<br>Vclk = Vss |

**Note:** This parameter is periodically sampled and not 100% tested.

TABLE 1-2: AC CHARACTERISTICS

| Parameter                                         | Symbol  | Vcc = 2.5-4.5V<br>Standard Mode |      | Vcc = 4.5 - 5.5V<br>Fast Mode |      | Units  | Remarks                                                       |

|---------------------------------------------------|---------|---------------------------------|------|-------------------------------|------|--------|---------------------------------------------------------------|

|                                                   |         | Min                             | Max  | Min                           | Max  |        |                                                               |

| Clock frequency                                   | FCLK    | _                               | 100  | _                             | 400  | kHz    |                                                               |

| Clock high time                                   | THIGH   | 4000                            | _    | 600                           | _    | ns     |                                                               |

| Clock low time                                    | TLOW    | 4700                            | _    | 1300                          | _    | ns     |                                                               |

| SDA and SCL rise time                             | TR      | _                               | 1000 | _                             | 300  | ns     | (Note 1)                                                      |

| SDA and SCL fall time                             | TF      |                                 | 300  | _                             | 300  | ns     | (Note 1)                                                      |

| Start condition hold time                         | THD:STA | 4000                            | _    | 600                           | _    | ns     | After this period the first clock pulse is generated          |

| Start condition setup time                        | Tsu:sta | 4700                            |      | 600                           | _    | ns     | Only relevant for repeated Start condition                    |

| Data input hold time                              | THD:DAT | 0                               |      | 0                             | _    | ns     | (Note 2)                                                      |

| Data input setup time                             | TSU:DAT | 250                             | _    | 100                           | _    | ns     |                                                               |

| Stop condition setup time                         | Tsu:sto | 4000                            | _    | 600                           | _    | ns     |                                                               |

| Output valid from clock                           | TAA     | l                               | 3500 | _                             | 900  | ns     | (Note 2)                                                      |

| Bus free time                                     | TBUF    | 4700                            | _    | 1300                          | _    | ns     | Time the bus must be free before a new transmission can start |

| Output fall time from VIH minimum to VIL maximum  | Tof     | _                               | 250  | 20 + 0.1<br>CB                | 250  | ns     | (Note 1), CB ≤ 100 pF                                         |

| Input filter spike suppression (SDA and SCL pins) | TSP     | l                               | 50   | _                             | 50   | ns     | (Note 3)                                                      |

| Write cycle time                                  | Twr     |                                 | 10   | _                             | 10   | ms     | Byte or Page mode                                             |

| <b>Transmit-Only Mode Param</b>                   | eters   |                                 |      |                               |      |        |                                                               |

| Output valid from VCLK                            | TVAA    |                                 | 2000 | _                             | 1000 | ns     |                                                               |

| VCLK high time                                    | Tvhigh  | 4000                            | _    | 600                           |      | ns     |                                                               |

| VCLK low time                                     | TvLow   | 4700                            | _    | 1300                          | _    | ns     |                                                               |

| VCLK setup time                                   | TVHST   | 0                               |      | 0                             |      | ns     |                                                               |

| VCLK hold time                                    | TSPVL   | 4000                            |      | 600                           |      | ns     |                                                               |

| Mode transition time                              | TVHZ    |                                 | 1000 |                               | 500  | ns     |                                                               |

| Transmit-only power-up time                       | TVPU    | 0                               |      | 0                             |      | ns     |                                                               |

| Input filter spike suppression (VCLK pin)         | TSPV    | _                               | 100  | _                             | 100  | ns     |                                                               |

| Endurance                                         |         | 1M                              | _    | 1M                            | _    | cycles | 25°C, Vcc = 5.0V, Block mode (Note 4)                         |

- **Note 1:** Not 100% tested. CB = Total capacitance of one bus line in pF.

- 2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

- **3:** The combined TsP and VHYs specifications are due to Schmitt Trigger inputs which provide noise and spike suppression. This eliminates the need for a Ti specification for standard operation.

- **4:** This parameter is not tested but ensured by characterization. For endurance estimates in a specific application, please consult the Total Endurance™ Model which can be obtained from Microchip's web site at www.microchip.com.

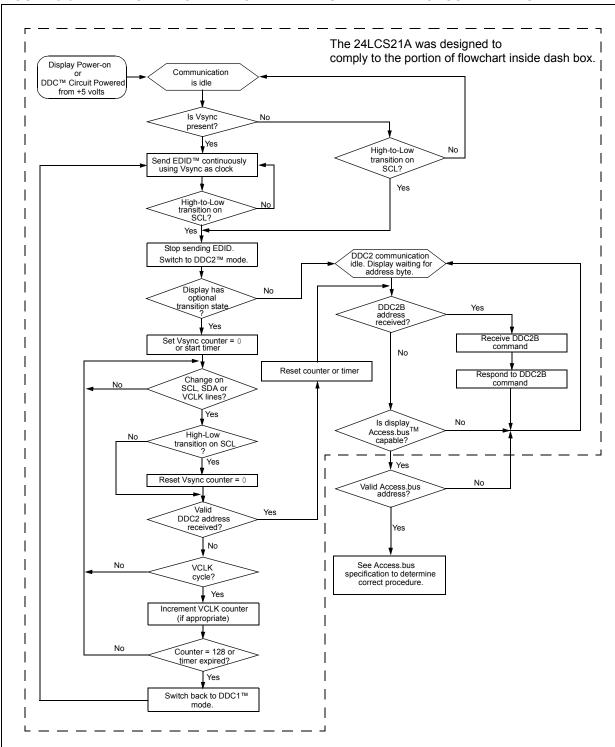

#### 2.0 FUNCTIONAL DESCRIPTION

The 24LCS21A is designed to comply to the DDC Standard proposed by VESA® (Figure 3-3) with the exception that it is not Access.bus™ capable. It operates in two modes, the Transmit-Only mode and the Bidirectional mode. There is a separate 2-wire protocol to support each mode, each having a separate clock input but sharing a common data line (SDA). The device enters the Transmit-Only mode upon power-up. In this mode, the device transmits data bits on the SDA pin in response to a clock signal on the VCLK pin. The device will remain in this mode until a valid high-to-low transition is placed on the SCL input. When a valid transition on SCL is recognized, the device will switch into the Bidirectional mode and look for its control byte to be sent by the master. If it detects its control byte, it will stay in the Bidirectional mode. Otherwise, it will revert to the Transmit-Only mode after it sees 128 VCLK pulses.

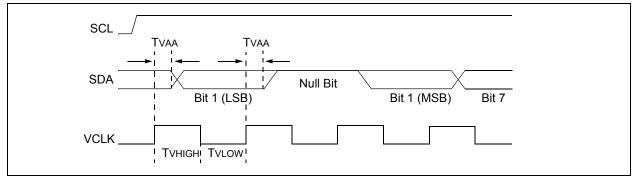

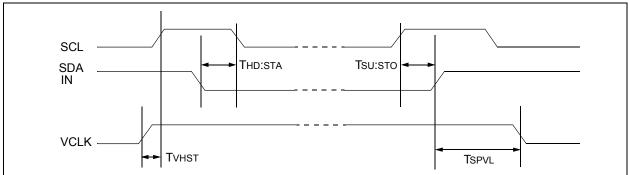

## 2.1 Transmit-Only Mode

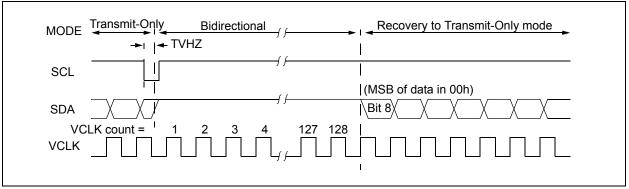

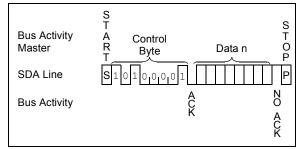

The device will power up in the Transmit-Only mode at address 00h. This mode supports a unidirectional 2-wire protocol for continuous transmission of the contents of the memory array. This device requires that

it be initialized prior to valid data being sent in the Transmit-Only mode (Section 2.2 "Initialization Procedure"). In this mode, data is transmitted on the SDA pin in 8-bit bytes, with each byte followed by a ninth, null bit (Figure 2-1). The clock source for the Transmit-Only mode is provided on the VCLK pin, and a data bit is output on the rising edge on this pin. The eight bits in each byte are transmitted Most Significant bit first. Each byte within the memory array will be output in sequence. After address 7Fh in the memory array is transmitted, the internal Address Pointers will wrap around to the first memory location (00h) and continue. The Bidirectional mode Clock (SCL) pin must be held high for the device to remain in the Transmit-Only mode.

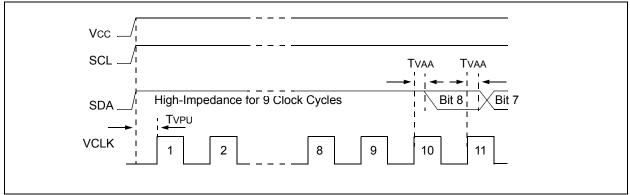

#### 2.2 Initialization Procedure

After Vcc has stabilized, the device will be in the Transmit-Only mode. Nine clock cycles on the VCLK pin must be given to the device for it to perform internal sychronization. During this period, the SDA pin will be in a high-impedance state. On the rising edge of the tenth clock cycle, the device will output the first valid data bit which will be the Most Significant bit in address 00h. (Figure 2-2).

FIGURE 2-1: TRANSMIT-ONLY MODE

FIGURE 2-2: DEVICE INITIALIZATION

#### 3.0 BIDIRECTIONAL MODE

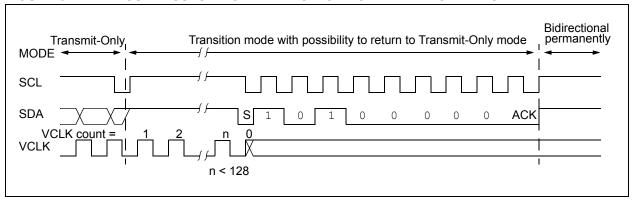

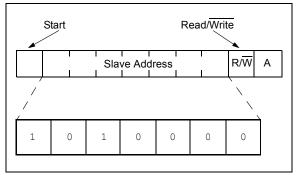

Before the 24LCS21A can be switched into the Bidirectional mode (Figure 3-1), it must enter the Transition mode, which is done by applying a valid high-tolow transition on the Bidirectional mode clock (SCL). As soon it enters the Transition mode, it looks for a control byte, '1010 000X' on the  $I^2C^{TM}$  bus, and starts to count pulses on VCLK. Any high-to-low transition on the SCL line will reset the count. If it sees a pulse count of 128 on VCLK while the SCL line is idle, it will revert back to the Transmit-Only mode and transmit its contents starting with the Most Significant bit in address 00h. However, if it detects the control byte on the  $I^2C^{TM}$ bus, (Figure 3-2) it will switch to the Bidirectional mode. Once the device has made the transition to the Bidirectional mode, the only way to switch the device back to the Transmit-Only mode is to remove power from the device. The mode transition process is shown in detail in Figure 3-3.

Once the device has switched into the Bidirectional mode, the VCLK input is disregarded, with the exception that a logic high level is required to enable write capability. This mode supports a two-wire Bidirectional data transmission protocol (I<sup>2</sup>C™). In this protocol, a device that sends data on the bus is defined to be the transmitter, and a device that receives data from the bus is defined to be the receiver. The bus must be controlled by a master device that generates the Bidirectional mode clock (SCL), controls access to the bus and generates the Start and Stop conditions, while the 24LCS21A acts as the slave. Both master and slave can operate as transmitter or receiver, but the master device determines which mode is activated. In the Bidirectional mode, the 24LCS21A only responds to commands for device '1010 000X'.

FIGURE 3-1: MODE TRANSITION WITH RECOVERY TO TRANSMIT-ONLY MODE

FIGURE 3-2: SUCCESSFUL MODE TRANSITION TO BIDIRECTIONAL MODE

FIGURE 3-3: DISPLAY OPERATION PER DDC STANDARD PROPOSED BY VESA®

- **Note 1:** The base flowchart is copyright © 1993, 1994, 1995 Video Electronic Standard Association (VESA) from VESA's Display Data Channel (DDC) Standard Proposal ver. 2p rev. 0, used by permission of VESA.

- 2: The dash box and text "The 24LCS21A and... inside dash box." are added by Microchip Technology Inc.

- 3: Vsync signal is normally used to derive a signal for VCLK pin on the 24LCS21A.

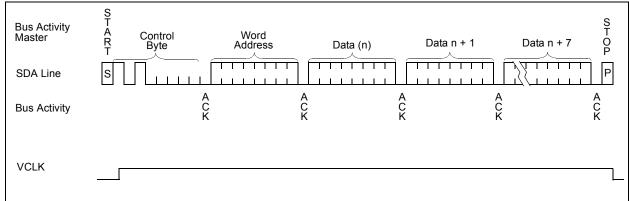

# 3.1 Bidirectional Mode Bus Characteristics

The following bus protocol has been defined:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is high. Changes in the data line while the clock line is high will be interpreted as a Start or Stop condition.

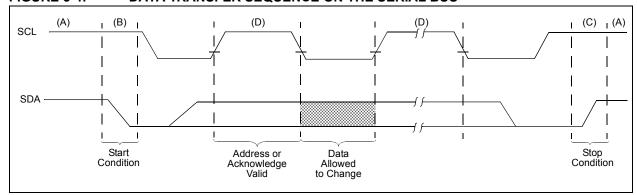

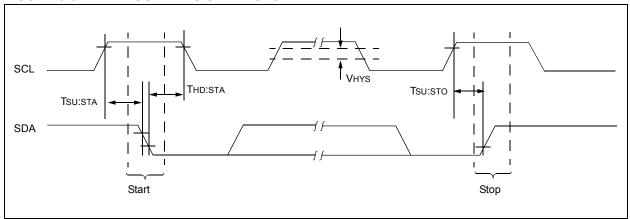

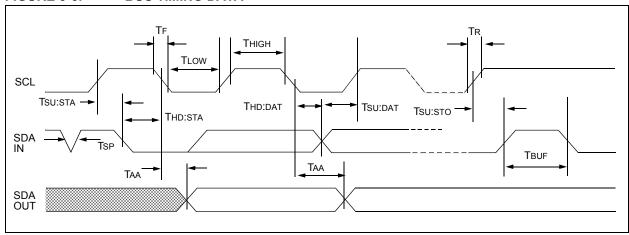

Accordingly, the following bus conditions have been defined (Figure 3-4).

#### 3.1.1 BUS NOT BUSY (A)

Both data and clock lines remain high.

#### 3.1.2 START DATA TRANSFER (B)

A high-to-low transition of the SDA line while the clock (SCL) is high determines a Start condition. All commands must be preceded by a Start condition.

#### 3.1.3 STOP DATA TRANSFER (C)

A low-to-high transition of the SDA line while the clock (SCL) is high determines a Stop condition. All operations must be ended with a Stop condition.

#### 3.1.4 DATA VALID (D)

The state of the data line represents valid data when, after a Start condition, the data line is stable for the duration of the high period of the clock signal.

The data on the line must be changed during the low period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a Start condition and terminated with a Stop condition. The number of the data bytes transferred between the Start and Stop conditions is determined by the master device and is theoretically unlimited, although only the last eight will be stored when doing a write operation. When an overwrite does occur it will replace data in a first-in first-out (FIFO) fashion.

Note: Once switched into Bidirectional mode, the 24LCS21A will remain in that mode until power is removed. Removing power is the only way to reset the 24LCS21A into the Transmit-Only mode.

#### 3.1.5 ACKNOWLEDGE

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this Acknowledge bit.

Note: The 24LCS21A does not generate any Acknowledge bits if an internal programming cycle is in progress.

The device that acknowledges has to pull down the SDA line during the Acknowledge clock pulse in such a way that the SDA line is stable low during the high period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an Acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line high to enable the master to generate the Stop condition.

#### FIGURE 3-4: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

FIGURE 3-5: BUS TIMING START/STOP

FIGURE 3-6: BUS TIMING DATA

#### 3.1.6 SLAVE ADDRESS

After generating a Start condition, the bus master transmits the slave address consisting of a 7-bit device code (1010000) for the 24LCS21A.

The eighth bit of slave address determines whether the master device wants to read or write to the 24LCS21A (Figure 3-7).

The 24LCS21A monitors the bus for its corresponding slave address continuously. It generates an Acknowledge bit if the slave address was true and it is not in a programming mode.

| Operation | Slave Address | R/W |

|-----------|---------------|-----|

| Read      | 1010000       | 1   |

| Write     | 1010000       | 0   |

FIGURE 3-7: CONTROL BYTE ALLOCATION

#### 4.0 WRITE OPERATION

#### 4.1 Byte Write

Following the Start signal from the master, the slave address (four bits), three zero bits (000) and the  $R/\overline{W}$ bit which is a logic low are placed onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an Acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the master is the word address and will be written into the Address Pointer of the 24LCS21A. After receiving another Acknowledge signal from the 24LCS21A the master device will transmit the data word to be written into the addressed memory location. The 24LCS21A acknowledges again and the master generates a Stop condition. This initiates the internal write cycle, and during this time the 24LCS21A will not generate Acknowledge signals (Figure 4-1).

It is required that VCLK be held at a logic high level during command and data transfer in order to program the device. This applies to both byte write and page write operation. Note, however, that the VCLK is ignored during the self-timed program operation. Changing VCLK from high-to-low during the self-timed program operation will <u>not</u> halt programming of the device.

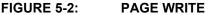

#### 4.2 Page Write

The write control byte, word address and the first data byte are transmitted to the 24LCS21A in the same way as in a byte write. But instead of generating a Stop condition the master transmits up to eight data bytes to the 24LCS21A, which are temporarily stored in the onchip page buffer and will be written into the memory after the master has transmitted a Stop condition. After the receipt of each word, the three lower order Address Pointer bits are internally incremented by one. The higher order five bits of the word address remains constant. If the master should transmit more than eight words prior to generating the Stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the Stop condition is received an internal write cycle will begin (Figure 5-2).

It is required that VCLK be held at a logic high level during command and data transfer in order to program the device. This applies to both byte write and page write operation. Note, however, that the VCLK is ignored during the self-timed program operation. Changing VCLK from high-to-low during the self-timed program operation will <u>not</u> halt programming of the device.

Page write operations are limited to writing Note: bytes within a single physical page, regardless of the number of bytes actually being written. Physical page boundaries start at addresses that are integer multiples of the page buffer size (or 'page size') and end at addresses that are integer multiples of [page size - 1]. If a Page Write command attempts to write across a physical page boundary, the result is that the data wraps around to the beginning of the current page (overwriting data previously stored there), instead of being written to the next page as might be expected. It is therefore necessary for the application software to prevent page write operations that would attempt to cross a page boundary.

# Bus Activity Master S T A Control Byte Address Data O P SDA Line Bus Activity A C C C C C K K K BYTE WRITE

VCLK

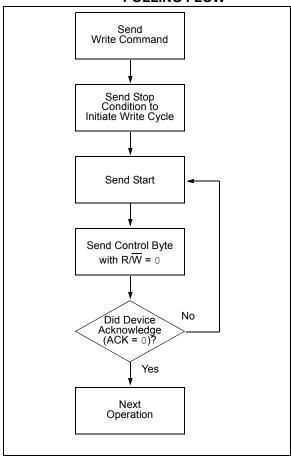

#### 5.0 ACKNOWLEDGE POLLING

Since the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the Stop condition for a Write command has been issued from the master, the device initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master sending a Start condition followed by the control byte for a Write command (R/ $\overline{W}$  = 0). If the device is still busy with the write cycle, then no ACK will be returned. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next Read or Write command. See Figure 5-1 for the flow diagram.

FIGURE 5-1: ACKNOWLEDGE POLLING FLOW

#### 6.0 WRITE PROTECTION

When using the 24LCS21A in the Bidirectional mode, the VCLK pin can be used as a write-protect control pin. Setting VCLK high allows normal write operations, while setting VCLK low prevents writing to any location in the array. Connecting the VCLK pin to Vss would allow the 24LCS21A to operate as a serial ROM, although this configuration would prevent using the device in the Transmit-Only mode.

Additionally, pin 3 performs a flexible write-protect function. The 24LCS21A contains a write protection control fuse whose factory default state is cleared. Writing any data to address 7Fh (normally the checksum in  $\overline{DDC}$  applications), sets the fuse which enables the  $\overline{WP}$  pin. Until this fuse is set, the 24LCS21A is always write enabled (if VCLK = 1). After the fuse is set, the write capability of the 24LCS21A is determined by both VCLK and  $\overline{WP}$  pins (Table 6-1).

TABLE 6-1: WRITE-PROTECT TRUTH TABLE

| VCLK | WP     | Address<br>7Fh Written | Mode<br>for<br>00h-7Fh |

|------|--------|------------------------|------------------------|

| 0    | X      | Х                      | Read-only              |

| 1    | X      | No                     | R/W                    |

| 1    | 1/open | Х                      | R/W                    |

| 1    | 0      | Yes                    | Read-only              |

#### 7.0 READ OPERATION

Read operations are initiated in the same way as write operations with the exception that the R/W bit of the slave address is set to one. There are three basic types of read operations: current address read, random read and sequential read.

#### 7.1 Current Address Read

The 24LCS21A contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with  $R/\overline{W}$  bit set to one, the 24LCS21A issues an acknowledge and transmits the eight-bit data word. The master will not acknowledge the transfer, but does generate a Stop condition and the 24LCS21A discontinues transmission (Figure 7-1).

FIGURE 7-1: CURRENT ADDRESS READ

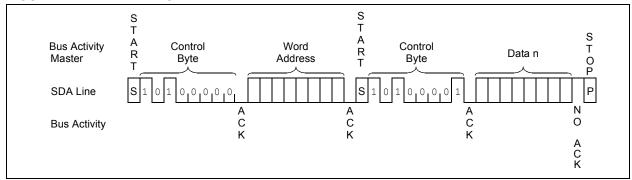

#### 7.2 Random Read

Random read operations allow the master to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the 24LCS21A as part of a write operation. After the word address is sent, the master generates a Start condition following the acknowledge. This terminates the write operation, but not before the internal Address Pointer is set. Then the master issues the control byte again, but with the  $R/\overline{W}$  bit set to a one. The 24LCS21A will then issue an acknowledge and transmits the 8-bit data word. The master will not acknowledge the transfer, but does generate a Stop condition and the 24LCS21A discontinues transmission (Figure 7-2).

#### FIGURE 7-2: RANDOM READ

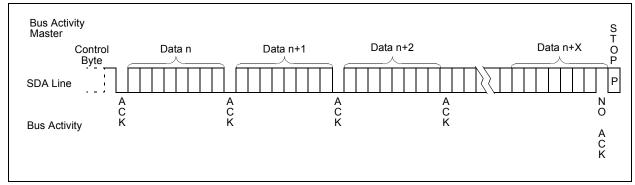

#### FIGURE 7-3: SEQUENTIAL READ

## 7.3 Sequential Read

Sequential reads are initiated in the same way as a random read except that after the 24LCS21A transmits the first data byte, the master issues an acknowledge as opposed to a Stop condition in a random read. This directs the 24LCS21A to transmit the next sequentially addressed 8-bit word (Figure 7-3).

To provide sequential reads the 24LCS21A contains an internal Address Pointer which is incremented by one at the completion of each operation. This Address Pointer allows the entire memory contents to be serially read during one operation.

#### 7.4 Noise Protection

The 24LCS21A employs a Vcc threshold detector circuit which disables the internal erase/write logic if the Vcc is below 1.5 volts at nominal conditions.

The SDA, SCL and VCLK inputs have Schmitt Trigger and filter circuits which suppress noise spikes to assure proper device operation even on a noisy bus.

#### 8.0 PIN DESCRIPTIONS

#### 8.1 SDA

This pin is used to transfer addresses and data into and out of the device, when the device is in the Bidirectional mode. In the Transmit-Only mode, which only allows data to be read from the device, data is also transferred on the SDA pin. This pin is an open drain terminal, therefore the SDA bus requires a pull-up resistor to Vcc (typical 10 K $\Omega$  for 100 kHz, 1 K $\Omega$  for 400 kHz).

For normal data transfer in the Bidirectional mode, SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the Start and Stop conditions.

#### 8.2 SCL

This pin is the clock input for the Bidirectional mode, and is used to synchronize data transfer to and from the device. It is also used as the signaling input to switch the device from the Transmit-Only mode to the Bidirectional mode. It must remain high for the chip to continue operation in the Transmit-Only mode.

#### 8.3 VCLK

This pin is the clock input for the Transmit-Only mode (DDC1). In the Transmit-Only mode, each bit is clocked out on the rising edge of this signal. In the Bidirectional mode, a high logic level is required on this pin to enable write capability.

#### 8.4 WP

This pin is used for flexible write protection of the 24LCS21A. When the last memory location (7Fh) is written with any data, this pin is enabled and determines the write capability of the 24LCS21A (Table 6-1).

## **APPENDIX A: REVISION HISTORY**

#### **Revision F**

Corrections to Section 1.0, Electrical Characteristics.

#### **Revision G**

Revised Section 8.4; Added On-Line Support page.

#### **Revision H**

Features Section - Add Pb-free and remove Commercial Temp; Revised Description; Table 1-1, Remove Commercial Temp, Revised Input/Output conditions; Revise Product ID section.

# PRODUCT IDENTIFICATION SYSTEM

$\underline{\text{To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales of fice.}\\$

| 24LCS21AT Dual Mode I2C Serial EEPROM (Tape and Reel)  Temperature I = -40°C to +85°C  Range: | PART NO.<br>Device    | X /XX XXX Temperature Package Pattern Range                                        |

|-----------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------|

| Range:                                                                                        | Device:               |                                                                                    |

| Package:  P = Plastic DIP (300 mil Body), 8-lead SN = Plastic SOIC (150 mil Body), 8-lead     | Temperature<br>Range: | I = -40°C to +85°C                                                                 |

|                                                                                               | Package:              | P = Plastic DIP (300 mil Body), 8-lead<br>SN = Plastic SOIC (150 mil Body), 8-lead |

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

- · Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com

## **READER RESPONSE**

To:

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:  | Technical Publications Manager        | Total Pages Sent                                        |

|------|---------------------------------------|---------------------------------------------------------|

| RE:  | Reader Response                       |                                                         |

| Fror | m: Name                               |                                                         |

|      | • •                                   |                                                         |

|      | ·                                     |                                                         |

|      | •                                     |                                                         |

| Ann  | Telephone: ()<br>lication (optional): | FAX: ()                                                 |

|      | uld you like a reply?YN               |                                                         |

|      | ice: 24LCS21A                         | Literature Number: DS21161H                             |

|      |                                       | Eliciature Number. Bozinom                              |

|      | estions:                              |                                                         |

| 1.   | What are the best features of this do | ocument?                                                |

|      |                                       |                                                         |

| 2    | How does this document meet your      | hardware and software development needs?                |

|      | non door and doormone more your       | natural of and communic development necess.             |

|      |                                       |                                                         |

| 3.   | Do you find the organization of this  | document easy to follow? If not, why?                   |

|      |                                       |                                                         |

|      |                                       |                                                         |

| 4.   | What additions to the document do     | you think would enhance the structure and subject?      |

|      |                                       |                                                         |

| 5.   | What deletions from the document of   | could be made without affecting the overall usefulness? |

| 0.   | Trial deletione from the decament     | is and the manest ansetting the everal assignment.      |

|      |                                       |                                                         |

| 6.   | Is there any incorrect or misleading  | information (what and where)?                           |

|      |                                       |                                                         |

|      |                                       |                                                         |

| 7.   | How would you improve this docume     | ent?                                                    |

|      |                                       |                                                         |

|      |                                       |                                                         |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA

Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississa

Mississauga, Ontario, Canada Tel: 905-673-0699

Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Fuzhou

Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen Tel: 86-755-8203-2660

Fax: 86-755-8203-1760

**China - Shunde** Tel: 86-757-2839-5507

Fax: 86-757-2839-5571

China - Wuhan Tel: 86-27-5980-5300

Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singanoro

Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-572-9526

Fax: 886-3-572-6459 **Taiwan - Kaohsiung**

Tel: 886-7-536-4818

Fax: 886-7-536-4803 **Taiwan - Taipei**

Tel: 886-2-2500-6610

Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351

Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich**

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869

Tel: 44-118-921-5869 Fax: 44-118-921-5820

10/05/07

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.