## USB2640i/USB2641i

# Industrial Temperature USB 2.0 Flash Media Controller and USB Hub Combo

#### PRODUCT FEATURES

**Datasheet**

#### **General Description**

The SMSC USB2640i/USB2641i is a USB 2.0 compliant, Hi-Speed hub for USB port expansion with an attached mass storage class peripheral controller. The controller allows read/write capability to popular flash media from the following families:

- Secure Digital™ (SD)

- MultiMediaCard<sup>™</sup> (MMC)

- xD-Picture Card<sup>™</sup> (xD)<sup>1</sup>

- Memory Stick<sup>®</sup>(MS)

The USB2640i/USB2641i is a fully integrated, single chip solution providing USB expansion and integrated flash card media reader/writer capability of ultra high performance operation. Average sustained transfer rates exceeding 35 MB/s are possible<sup>2</sup>.

#### **Highlights**

- Hub controller with internally connected ultra fast flash media reader/writer and 2 exposed downstream ports for external peripheral expansion

- Flash media reader/writer employs multiplexed card interfaces which are optimized for use with single card insertion combo sockets

- Hardware-controlled data flow architecture for all selfmapped media

- Optional support for external firmware access via SPI interface

#### PortMap

Flexible port mapping and port disable sequencing supports multiple platform designs

#### PortSwap

Programmable USB differential-pair pin locations eases PCB design by aligning USB signal traces directly to connectors

#### PHYBoost

Programmable USB transceiver drive strength recovers signal integrity

#### **Features**

- Compliant with the following flash media card specifications:

SD 2.0 / MMC 4.2 / MS 1.43 / MS-Pro 1.02 / MS-PRO-HG

1.01 / MS-Duo 1.10 / xD 1.2

- Supports a single external 3.3 V supply source; internal regulators provide 1.8 V internal core voltage for additional bill of materials and power savings

- The transaction translator (TT) in the hub supports operation of Full-Speed and Low-Speed peripherals

- 9 K RAM | 64 K on-chip ROM

- Enhanced EMI rejection and ESD protection performance

- Onboard 24 MHz crystal driver circuit

- Optional external 24 MHz clock input

- Up to 9 GPIOs for special functions

- 8051 8-bit microprocessor

- Hub and flash media reader/writer configuration from a single source: External I<sup>2</sup>C ROM or external SPI ROM

- Configures internal code using an external I<sup>2</sup>C EEPROM

- Supports external code using a SPI Flash EEPROM

- Customizable vendor ID, product ID, language ID

- EEPROM update via USB

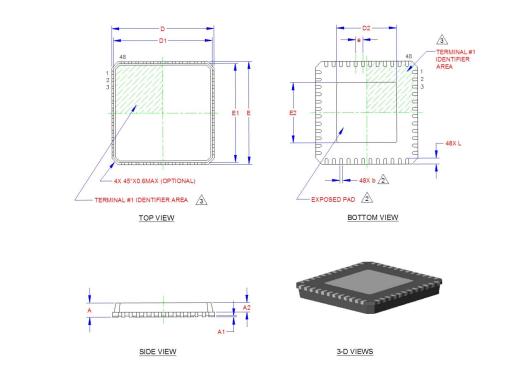

- 48-pin QFN lead-free, RoHS compliant package (7x7 mm)

- The SMSC USB2640i/USB2641i supports the industrial temperature range of -40°C to 85°C

#### **Applications**

- Desktop and mobile PCs

- Personal mobile devices

- Printers

- GPS navigation systems

- Media Players/Viewers

- Consumer A/V

- Set-top boxes

- Industrial products

<sup>1.</sup>Support and capabilities for xD-Picture Card are not applicable for the USB2641i. Please obtain a user license from the xD-Picture Card License Office to support this flash media format

<sup>2.</sup> Host and media dependent.

#### **ORDER NUMBERS:**

#### USB2640i/USB2641i-HZH-XX for 48-PIN, QFN LEAD-FREE ROHS COMPLIANT PACKAGE

"XX" in the order number indicates the internal ROM firmware revision level.

Please contact your SMSC representative for more information.

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright © 2009 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC makes the following part-numbered device available for purchase only by customers who are xD-Picture Card licensees: USB2640i.

By purchasing or ordering any of such devices, Buyer represents, warrants, and agrees that Buyer is a duly licensed Licensee under an xD-Picture Card<sup>TM</sup> License Agreement with Fuji Photo Film Co., Ltd., Olympus Optical Co., Ltd., and Toshiba Corporation; and that Buyer will maintain in effect such xD-Picture Card license and will give SMSCreasonable advance notice of any termination or expiration of such xD-Picture Card license, but in no event less than five days advance notice. SMSC may discontinue making such devices available for purchase by Buyer and/or discontinue further deliveries of such xD-Picture Card license shall expire, terminate, or cease to be in force, or if Buyer is or becomes in default of such xD-Picture Card license.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| Chap<br>1.1<br>1.2               | Device                              | Overview                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chap                             | oter 2                              | Acronyms                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chap                             | oter 3                              | Pin Configurations1                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chap                             | oter 4                              | Block Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>Chap</b> 5.1                  |                                     | Pin Tables         1           Tables         1                                                                                                                                                                                                                                                                                                                                                                                    |

| Chap<br>6.1<br>6.2<br>6.3<br>6.4 | USB26<br>Buffer<br>Port Po          | Pin Descriptions1640i/USB2641i Pin Descriptions1Type Descriptions2ower Control2BOOT Sequence2                                                                                                                                                                                                                                                                                                                                      |

| Chap 7.1 7.2 7.3                 | Hub 7.1.1 7.1.2 Card F Systen 7.3.1 | Configuration Options       2         Hub Configuration Options       2         VBus Detect       2         teader       2         n Configurations       2         EEPROM/SPI Interface       2                                                                                                                                                                                                                                   |

| 7.4<br>7.5                       |                                     | EEPROM Data Descriptor       2         EEPROM Data Descriptor Register Descriptions       3         A0h-A7h: Device Power Configuration       3         Hub Controller Configurations       4         I^2C EEPROM       4         In-Circuit EEPROM Programming       4         t Configuration Option:       4         Internal POR Hardware Reset       4         External Hardware nRESET       5         USB Bus Reset       5 |

| <b>Chap</b> 8.1                  |                                     | Pin Reset States                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Chap<br>9.1<br>9.2<br>9.3        | Ceram                               | AC Specifications       5         tor/Crystal       5         ic Resonator       5         al Clock       5         I <sup>2</sup> C EEPROM       5         USB 2.0       5                                                                                                                                                                                                                                                        |

| <b>Chap</b><br>10.1<br>10.2      | Maxim                               | DC Parameters5um Guaranteed Ratings5ing Conditions5                                                                                                                                                                                                                                                                                                                                                                                |

| Спа  |

|------|

| Cha  |

| 10.3 |

| 10.3 |

## **List of Tables**

| Table 5.1  | USB2640i 48-Pin Table                          | 15 |

|------------|------------------------------------------------|----|

| Table 5.2  | USB2641i 48-Pin Table                          | 16 |

| Table 6.1  | USB2640i/USB2641i Pin Descriptions             | 18 |

| Table 6.2  | USB2640i/USB2641i Buffer Type Descriptions     | 24 |

| Table 7.1  | Internal Flash Media Controller Configurations | 29 |

| Table 7.2  | Hub Controller Configurations                  | 31 |

| Table 7.3  | Other Internal Configurations                  | 31 |

| Table 7.4  | Port Map Register for Ports 1 & 2              | 47 |

| Table 7.5  | Port Map Register for Port 3                   | 48 |

| Table 7.6  | nRESET Timing for EEPROM Mode                  | 50 |

| Table 8.1  | Legend for Pin Reset States Table              | 52 |

| Table 8.2  | USB2640i Pin Reset States                      | 52 |

| Table 8.3  | USB2641i Pin Reset States                      | 54 |

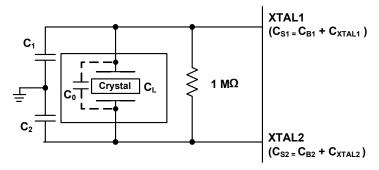

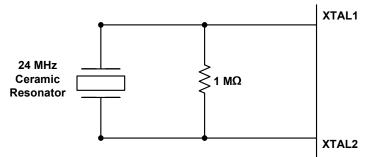

| Table 9.1  | Crystal Circuit Legend                         | 56 |

| Table 10.1 | Pin Capacitance                                | 61 |

| Table 11.1 | USB2640i/USB2641i GPIO Usage                   | 62 |

|            |                                                |    |

# **List of Figures**

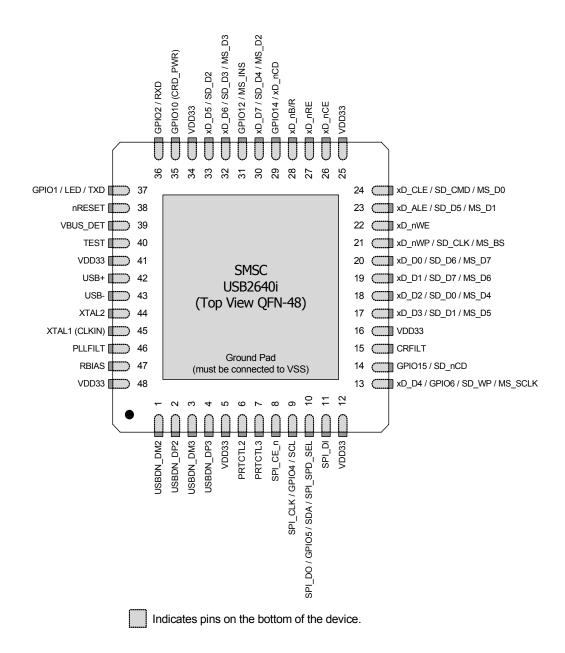

| igure 3.1   | USB2640i 48-Pin QFN                           | 11 |

|-------------|-----------------------------------------------|----|

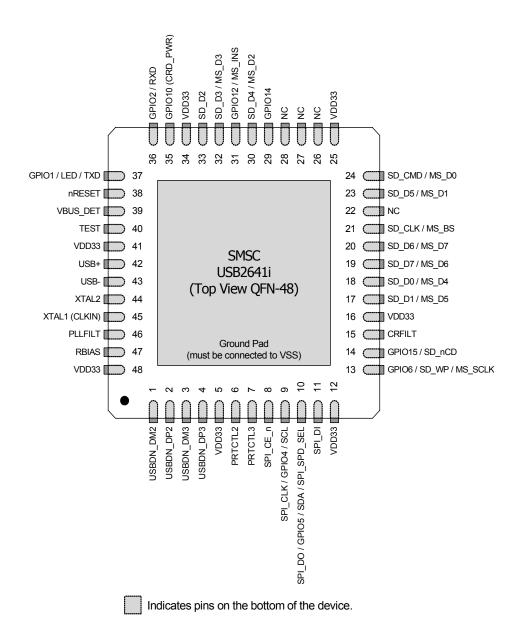

| igure 3.2   | USB2641i 48-Pin QFN                           | 12 |

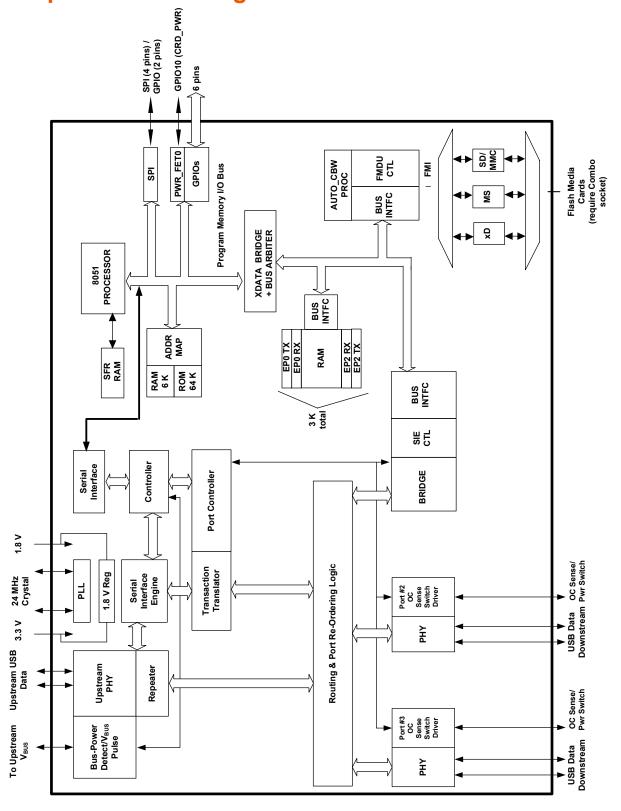

| igure 4.1   | USB2640i Block Diagram                        | 13 |

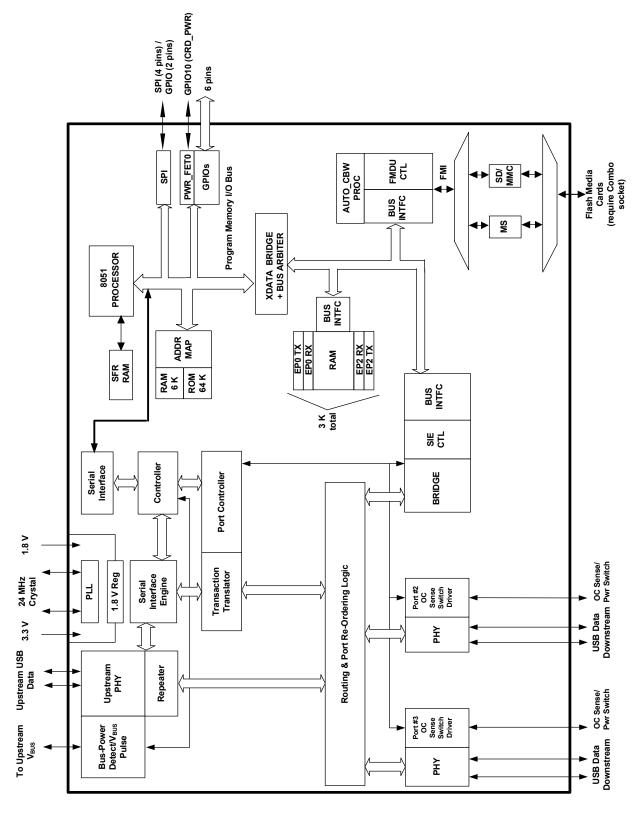

| igure 4.2   | USB2641i Block Diagram                        | 14 |

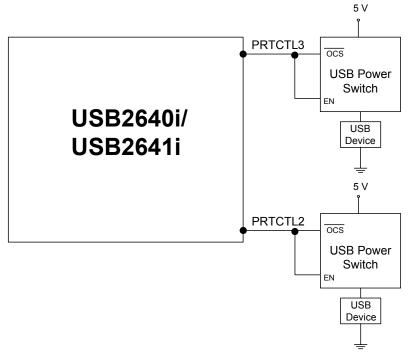

| igure 6.1   | Port Power Control with USB Power Switch      | 25 |

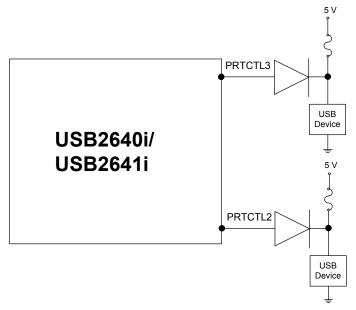

| igure 6.2   | Port Power control with Poly Fuse             | 26 |

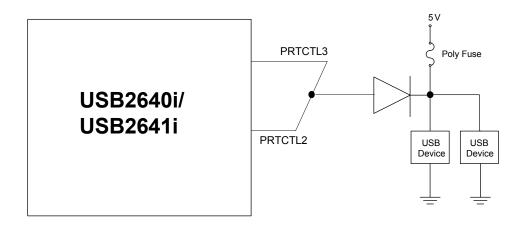

| igure 6.3   | Port Power with Ganged Control with Poly Fuse | 26 |

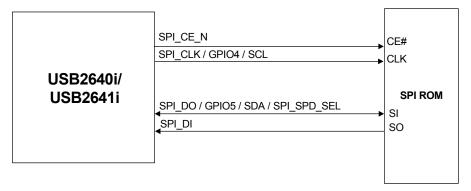

| igure 6.4   | USB2640i/USB2641i SPI ROM Connection          | 27 |

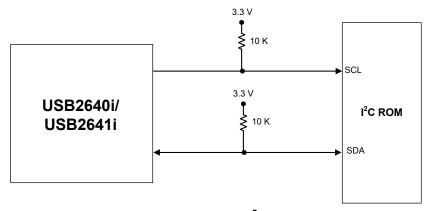

| igure 6.5   | USB2640i/USB2641i I <sup>2</sup> C Connection | 27 |

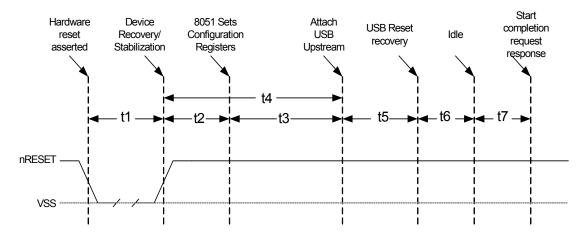

| igure 7.1   | nRESET Timing for EEPROM Mode                 | 5( |

| igure 8.1   | Pin Reset States                              | 52 |

| igure 9.1   | Typical Crystal Circuit                       | 56 |

| igure 9.2   | Capacitance Formulas                          | 56 |

| igure 9.3   | Ceramic Resonator Usage with SMSC IC          | 57 |

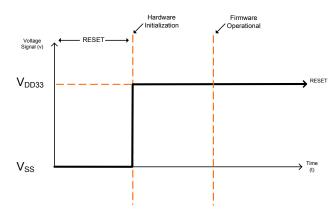

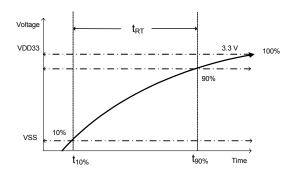

| Figure 10.1 | Supply Rise Time Models                       | 58 |

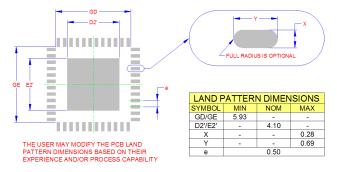

| Figure 12.1 | USB2640i/USB2641i 48-Pin QFN                  | 63 |

## **Chapter 1 Overview**

The SMSC USB2640i/USB2641i is an integrated USB 2.0 compliant, Hi-Speed hub for USB port expansion with an attached bulk only mass storage class peripheral controller. This multi-format flash media controller and USB Hub Combo features three downstream ports: one port is dedicated to an internally connected ultra fast flash media reader/writer and two exposed downstream ports are available for external peripheral expansion.

The SMSC USB2640i/USB2641i is an ultra fast, OEM-configurable, hub controller IC with three downstream ports for embedded USB solutions. The USB2640i/USB2641i will attach to an upstream port as a Full-Speed Hub or as a Full-Hi-Speed Hub. The hub supports Low-Speed, Full-Speed, and Hi-Speed (if operating as a Hi-Speed Hub) downstream devices on all of the enabled downstream ports.

All required resistors on the USB ports are integrated into the hub. This includes all series termination resistors on D+ and D- pins and all required pull-down and pull-up resistors on D+ and D- pins. The over-current sense inputs for the downstream facing ports have internal pull-up resistors.

The USB2640i/USB2641i includes programmable features such as:

**PortMap** which provides flexible port mapping and disable sequences. The downstream ports of a USB2640i/USB2641i hub can be reordered or disabled in any sequence to support multiple platform designs with minimum effort. For any port that is disabled, the USB2640i/USB2641i automatically reorders the remaining ports to match the USB host controller's port numbering scheme.

**PortSwap** which adds per-port programmability to USB differential-pair pin locations. PortSwap allows direct alignment of USB signals (D+/D-) to connectors avoiding uneven trace length or crossing of the USB differential signals on the PCB.

**PHYBoost** which enables four programmable levels of USB signal drive strength in downstream port transceivers. PHYBoost attempts to restore USB signal integrity that has been compromised by system level variables such as poor PCB layout, long cables, etc.

#### 1.1 Device Features

#### **Hardware Features**

- Single chip flash media controller

- The SMSC USB2640i/USB2641i supports the industrial temperature range of -40°C to 85°C

- Transaction translator (TT) in the hub supports operation of FS and LS peripherals

- Full power management with individual or ganged power control of each downstream port

- Optional support for external firmware access via SPI interface

- 30 MHz or 60 MHz operation support

- Single bit or dual bit mode support

- Mode 0 or mode 3 SPI support

#### Compliant with the following flash media card specifications:

- Secure Digital 2.0 / MultiMediaCard 4.2

- SD 2.0, HS-SD, HC-SD

- TransFlash™ and reduced form factor media

- 1/4/8 bit MMC 4.2

- SDIO and MMC streaming mode support

- Memory Stick 1.43

- Memory Stick Pro Format 1.02

- Memory Stick Pro-HG Duo Format 1.01

- Memory Stick, MS Duo, HS-MS, MS Pro-HG, MS Pro

- Memory Stick Duo 1.10

- xD-Picture Card 1.2 (USB2640i only)

- On board 24 MHz crystal driver circuit

- Optional external 24 MHz clock input

- Must be used with an external resistor divider to provide a 1.8 V signal

- Up to 9 GPIOs: Configuration and polarity for special function use such as LED indicators, button inputs, and power control to memory devices

- The number of actual GPIOs depends on the implementation configuration used

- One GPIO available with up to 200 mA drive and protected "fold-back" short circuit current

- 8051 8-bit microprocessor

- 60 MHz single cycle execution

- 64 KB ROM; 9 KB RAM

- Internal regulator for 1.8 V core operation

- Optimized pinout improves signal flow, easing implementation and allowing for improved signal integrity treatment

#### **Software Features**

- Optimized for low latency interrupt handling

- Hub and flash media reader/writer configuration from a single source: External I<sup>2</sup>C ROM or external SPI ROM

- EEPROM update via USB

- Please see the USB2640i/USB2641i Software Release Notes for additional software features

#### 1.2 **OEM Selectable Features**

#### Hub

A default configuration is available in USB2640i/USB2641i following a reset. The USB2640i/USB2641i may also be configured by an external I<sup>2</sup>C EEPROM or via external SPI ROM flash.

The USB2640i/USB2641i supports several OEM selectable features:

- Compound Device support (port is permanently hardwired to a downstream USB peripheral device), on a port-by-port basis.

- Select over-current sensing and port power control on an individual (port-by-port) or ganged (all ports together) basis to match the OEM's choice of circuit board component selection.

- Port power control and over-current detection/delay features

- Configure the delay time for filtering the over-current sense inputs.

- Configure the delay time for turning on downstream port power.

- Bus- or self-powered selection

- Hub port disable or non-removable configurations

- Flexible port mapping and disable sequence. Ports can be disabled/reordered in any sequence to support multiple platforms with a single design. The hub will automatically reorder the remaining ports to match the host controller's numbering scheme.

- Programmable USB differential-pair pin location.

- Eases PCB layout by aligning USB signal lines directly to connectors

- Programmable USB signal drive strength. Recover USB signal integrity due to compromised system environments using four levels of signal drive strength.

- Indicate the maximum current that the 2-port hub consumes from the USB upstream port.

- Indicate the maximum current required for the hub controller.

#### Flash Media Controller

- Customize vendor ID, product ID, and device ID.

- 12-hex digit (max) serial number string

- Customizable vendor specific data by optional use of external serial EEPROM

- 28-character manufacturer ID and product string for flash media reader/writer

- LED blink interval or duration

# **Chapter 2 Acronyms**

FM: Flash Media

FMC: Flash Media Controller

FS: Full-speed Device

LS: Low-speed Device

HS: Hi-speed Device

I<sup>2</sup>C<sup>®</sup>: Inter-Integrated Circuit<sup>1</sup>

MMC: MultiMediaCard

MS: Memory Stick

MSC: Memory Stick Controller

**OCS:** Over-current Sense

RXD: Received eXchange Data

SD: Secure Digital

**SDC:** Secure Digital Controller **TXD:** Transmit eXchange Data

**UART:** Universal Asynchronous Receiver-Transmitter

**UCHAR:** Unsigned Character

**UINT:** Unsigned Integer **xD:** xD-Picture Card

Standard Microsystems is a registered trademark and SMSC is a trademark of Standard Microsystems Corporation. Other product and company names are trademarks or registered trademarks of their respective holders.

\*Note: In order to develop, make, use, or sell readers and/or other products using or incorporating any of the SMSC devices made the subject of this document or to use related SMSC software programs, technical information and licenses under patent and other intellectual property rights from or through various persons or entities, including without limitation media standard companies, forums, and associations, and other patent holders may be required. These media standard companies, forums, and associations include without limitation the following: Sony Corporation (Memory Stick, Memory Stick Pro); SD3 LLC (Secure Digital); MultiMedia Card Association (MultiMediaCard); the SSFDC Forum (SmartMedia); the Compact Flash Association (Compact Flash); and Fuji Photo Film Co., Ltd., Olympus Optical Co., Ltd., and Toshiba Corporation (xD-Picture Card). SMSC does not make such licenses or technical information available; does not promise or represent that any such licenses or technical information will actually be obtainable from or through the various persons or entities (including the media standard companies, forums, and associations), or with respect to the terms under which they may be made available; and is not responsible for the accuracy or sufficiency of, or otherwise with respect to, any such technical information.

SMSC's obligations (if any) under the Terms of Sale Agreement, or any other agreement with any customer, or otherwise, with respect to infringement, including without limitation any obligations to defend or settle claims, to reimburse for costs, or to pay damages, shall not apply to any of the devices made the subject of this document or any software programs related to any of such devices, or to any combinations involving any of them, with respect to infringement or claimed infringement of any existing or future patents related to solid state disk or other flash memory technology or applications ("Solid State Disk Patents"). By making any purchase of any of the devices made the subject of this document, the customer represents, warrants, and agrees that it has obtained all necessary licenses under then-existing Solid State Disk Patents for the manufacture, use and sale of solid state disk and other flash memory products and that the customer will timely obtain at no cost or expense to SMSC all necessary licenses under Solid State Disk Patents; that the manufacture and testing by or for SMSC of the units of any of the devices made the subject of this document which may be sold to the customer, and any sale by SMSC of such units to the customer, are valid exercises of the customer's rights and licenses under such Solid State Disk Patents; that SMSC shall have no obligation for royalties or otherwise under any Solid State Disk Patents by reason of any such manufacture, use, or sale of such units; and that SMSC shall have no obligation for any costs or expenses related to the customer's obtaining or having obtained rights or licenses under any Solid State Disk Patents.

SMSC MAKES NO WARRANTIES, EXPRESS, IMPLIED, OR STATUTORY, IN REGARD TO INFRINGEMENT OR OTHER VIOLATION OF INTELLECTUAL PROPERTY RIGHTS. SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES AGAINST INFRINGEMENT AND THE LIKE.

No license is granted by SMSC expressly, by implication, by estoppel or otherwise, under any patent, trademark, copyright, mask work right, trade secret, or other intellectual property right. \*\*To obtain this software program the appropriate SMSC Software License Agreement must be executed and in effect. Forms of these Software License Agreements may be obtained by contacting SMSC.

<sup>1.1&</sup>lt;sup>2</sup>C is a registered trademark of Philips Corporation.

# **Chapter 3 Pin Configurations**

Figure 3.1 USB2640i 48-Pin QFN

Figure 3.2 USB2641i 48-Pin QFN

# **Chapter 4 Block Diagrams**

Figure 4.1 USB2640i Block Diagram

Figure 4.2 USB2641i Block Diagram

# **Chapter 5 Pin Tables**

## 5.1 48-Pin Tables

Table 5.1 USB2640i 48-Pin Table

| xD-PICTURE CARD (Only in USB2640i) / SECURE DIGITAL / MEMORY STICK INTERFACE (18 PINS) |                              |                               |                             |  |  |  |  |

|----------------------------------------------------------------------------------------|------------------------------|-------------------------------|-----------------------------|--|--|--|--|

| xD_D3 /<br>SD_D1 /<br>MS_D5                                                            | xD_D2 /<br>SD_D0 /<br>MS_D4  | xD_D1 /<br>SD_D7 /<br>MS_D6   | xD_D0 /<br>SD_D6 /<br>MS_D7 |  |  |  |  |

| xD_nWP /<br>SD_CLK /<br>MS_BS                                                          | xD_ALE /<br>SD_D5 /<br>MS_D1 | xD_CLE /<br>SD_CMD /<br>MS_D0 | xD_D7 /<br>SD_D4 /<br>MS_D2 |  |  |  |  |

| xD_D6 /<br>SD_D3 /<br>MS_D3                                                            | xD_D5 /<br>SD_D2             | xD_nRE                        | xD_nWE                      |  |  |  |  |

| xD_D4 /<br>GPIO6 /<br>SD_WP /<br>MS_SCLK                                               | xD_nB/R                      | xD_nCE                        | GPIO12 /<br>MS_INS          |  |  |  |  |

| GPIO14 /<br>xD_nCD                                                                     | GPIO15 /<br>SD_nCD           |                               |                             |  |  |  |  |

|                                                                                        | USB INTERFACE (5 PINS)       |                               |                             |  |  |  |  |

| USB+                                                                                   | USB-                         | XTAL1 (CLKIN)                 | XTAL2                       |  |  |  |  |

| RBIAS                                                                                  |                              |                               |                             |  |  |  |  |

| 2-PORT USB INTERFACE (7 PINS)                                                          |                              |                               |                             |  |  |  |  |

| USBDN_DP2                                                                              | USBDN_DM2                    | PRTCTL2                       | PRTCTL3                     |  |  |  |  |

| USBDN_DP3                                                                              | USBDN_DM3                    | VBUS_DET                      |                             |  |  |  |  |

Table 5.1 USB2640i 48-Pin Table (continued)

| SPI INTERFACE (4 PINS) |                             |                                             |                |  |  |

|------------------------|-----------------------------|---------------------------------------------|----------------|--|--|

| SPI_CE_n               | SPI_CLK /<br>GPIO4 /<br>SCL | SPI_DO /<br>GPIO5 /<br>SDA /<br>SPI_SPD_SEL | SPI_DI         |  |  |

|                        | MISC (                      | 5 PINS)                                     |                |  |  |

| nRESET                 | TEST                        | GPIO1 /<br>LED /<br>TXD                     | GPIO2 /<br>RXD |  |  |

| GPIO10<br>(CRD_PWR)    |                             |                                             |                |  |  |

|                        | POWER AND GI                | ROUND (9 PINS)                              |                |  |  |

| (7) VDD33              | CRFILT                      | PLLFILT                                     |                |  |  |

| TOTAL 48               |                             |                                             |                |  |  |

#### Table 5.2 USB2641i 48-Pin Table

| SECURE DIGITAL / MEMORY STICK INTERFACE (14 PINS) |                  |                    |                  |  |  |  |

|---------------------------------------------------|------------------|--------------------|------------------|--|--|--|

| SD_D1 /<br>MS_D5                                  | SD_D0 /<br>MS_D4 | SD_D7 /<br>MS_D6   | SD_D6 /<br>MS_D7 |  |  |  |

| SD_CLK /<br>MS_BS                                 | SD_D5 /<br>MS_D1 | SD_CMD /<br>MS_D0  | SD_D4/<br>MS_D2  |  |  |  |

| SD_D3 /<br>MS_D3                                  | SD_D2            | GPIO12 /<br>MS_INS | GPIO14           |  |  |  |

| GPIO6 / GPIO15 / SD_WP / SD_nCD                   |                  |                    |                  |  |  |  |

| USB INTERFACE (5 PINS)                            |                  |                    |                  |  |  |  |

| USB+                                              | USB+ USB-        |                    | XTAL2            |  |  |  |

#### Table 5.2 USB2641i 48-Pin Table (continued)

| RBIAS                          |                            |                                             |                |  |  |  |  |

|--------------------------------|----------------------------|---------------------------------------------|----------------|--|--|--|--|

|                                | 2-PORT USB INT             | ERFACE (7 PINS)                             |                |  |  |  |  |

| USBDN_DP2                      | USBDN_DM2                  | PRTCTL2                                     | PRTCTL3        |  |  |  |  |

| USBDN_DP3                      | USBDN_DM3                  | VBUS_DET                                    |                |  |  |  |  |

|                                | SPI INTERFA                | ACE (4 PINS)                                |                |  |  |  |  |

| SPI_CLK / SPI_CE_n GPIO4 / SCL |                            | SPI_DO /<br>GPIO5 /<br>SDA /<br>SPI_SPD_SEL | SPI_DI         |  |  |  |  |

|                                | MISC (5 PINS)              |                                             |                |  |  |  |  |

| nRESET TEST                    |                            | GPIO1 /<br>LED /<br>TXD                     | GPIO2 /<br>RXD |  |  |  |  |

| GPIO10<br>(CRD_PWR)            |                            |                                             |                |  |  |  |  |

|                                | POWER AND GROUND (13 PINS) |                                             |                |  |  |  |  |

| (7) VDD33                      | (7) VDD33 CRFILT           |                                             | PLLFILT        |  |  |  |  |

| (4) NC                         |                            |                                             |                |  |  |  |  |

| TOTAL 48                       |                            |                                             |                |  |  |  |  |

# **Chapter 6 Pin Descriptions**

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface. The pin descriptions below are applied when using the internal default firmware and can be referenced in Chapter 7, "Configuration Options," on page 28. Please reference Chapter 2, Acronyms for a list of the acronyms used.

The "n" symbol in the signal name indicates that the active, or asserted, state occurs when the signal is at a low voltage level. When "n" is not present in the signal name, the signal is asserted at a high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term assert, or assertion, indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation, indicates that a signal is inactive.

## 6.1 USB2640i/USB2641i Pin Descriptions

Table 6.1 USB2640i/USB2641i Pin Descriptions

| SYMBOL    | 48-PIN<br>QFN                                | BUFFER<br>TYPE<br>(Table 6.2) | DESCRIPTION                                                                                                                                                |

|-----------|----------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | xD-PI                                        | CTURE CAR                     | D INTERFACE (APPLIES ONLY TO USB2640i)                                                                                                                     |

| xD_D[7:0] | 30<br>32<br>33<br>13<br>17<br>18<br>19<br>20 | I/O12PU                       | xD-Picture Card Data 7-0  These pins are the bi-directional data signal xD_D7 - xD_D0 and have weak internal pull-up resistors.                            |

| xD_ALE    | 23                                           | O12PD                         | xD-Picture Card Address Strobe                                                                                                                             |

|           |                                              |                               | This pin is an active high Address Latch Enable signal for the xD-Picture Card device. This pin has a weak pull-down resistor that is permanently enabled. |

| xD_nB/R   | 28                                           | IPU                           | xD-Picture Card Busy or Data Ready                                                                                                                         |

|           |                                              |                               | This pin is connected to the BSY/RDY pin of the xD-Picture Card device.                                                                                    |

|           |                                              |                               | When using the internal FET, this pin has an internal weak pull-up resistor that is tied to the output of the internal power FET.                          |

|           |                                              |                               | If an external FET is used (the internal FET is disabled), then the internal pull-up is not available (an external pull-up is required).                   |

Table 6.1 USB2640i/USB2641i Pin Descriptions (continued)

| SYMBOL   | 48-PIN<br>QFN | BUFFER<br>TYPE<br>(Table 6.2) | DESCRIPTION                                                                                                                                                |

|----------|---------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xD_nCE   | 26            | O12PU                         | xD-Picture Card Chip Enable                                                                                                                                |

|          |               |                               | This pin is an active low chip enable signal for the xD-Picture Card device.                                                                               |

|          |               |                               | When using the internal FET, this pin has an internal weak pull-up resistor that is tied to the output of the internal power FET.                          |

|          |               |                               | If an external FET is used (the internal FET is disabled), then the internal pull-up is not available (an external pull-up is required).                   |

| xD_CLE   | 24            | O12PD                         | xD-Picture Card Command Strobe                                                                                                                             |

|          |               |                               | This pin is an active high Command Latch Enable signal for the xD-Picture Card device. This pin has a weak pull-down resistor that is permanently enabled. |

| GPIO14 / | 29            | I/O12                         | This general purpose pin may be used either as input, edge sensitive interrupt input, or output. Custom firmware is required to activate this function.    |

| xD_nCD   |               |                               | xD-Picture Card Detection GPIO                                                                                                                             |

|          |               |                               | This is a GPIO designated by the default firmware as the xD-Picture Card detection pin.                                                                    |

| xD_nRE   | 27            | O12PU                         | xD-Picture Read Enable                                                                                                                                     |

|          |               |                               | This pin is an active low read strobe signal for the xD-Picture Card device.                                                                               |

|          |               |                               | When using the internal FET, this pin has an internal weak pull-up resistor that is tied to the output of the internal power FET.                          |

|          |               |                               | If an external FET is used (the internal FET is disabled), then the internal pull-up is not available (an external pull-up is required).                   |

| xD_nWE   | 22            | O12PU                         | xD-Picture Card Write Enable                                                                                                                               |

|          |               |                               | This pin is an active low write strobe signal for the xD-Picture Card device.                                                                              |

|          |               |                               | When using the internal FET, this pin has an internal weak pull-up resistor that is tied to the output of the internal power FET.                          |

|          |               |                               | If an external FET is used (the internal FET is disabled), then the internal pull-up is not available (an external pull-up is required).                   |

| xD_nWP   | 21            | O12PD                         | xD-Picture Card Write Protect                                                                                                                              |

|          |               |                               | This pin is an active low write protect signal for the xD-Picture Card device. This pin has a weak pull-down resistor that is permanently enabled.         |

|          |               | N                             | MEMORY STICK INTERFACE                                                                                                                                     |

| MS_BS    | 21            | O12                           | Memory Stick Bus State                                                                                                                                     |

|          |               |                               | This pin is connected to the bus state pin of the MS device. It is used to control the Bus States 0, 1, 2, and 3 (BS0, BS1, and BS3) of the MS device.     |

Table 6.1 USB2640i/USB2641i Pin Descriptions (continued)

| SYMBOL    | 48-PIN<br>QFN                                | BUFFER<br>TYPE<br>(Table 6.2) | DESCRIPTION                                                                                                                                                                                                                  |

|-----------|----------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO12 /  | 31                                           | I/O12                         | This general purpose pin may be used either as input, edge sensitive interrupt input, or output. Custom firmware is required to activate this function.                                                                      |

| MS_INS    |                                              | IPU                           | Memory Stick Card Insertion GPIO                                                                                                                                                                                             |

|           |                                              |                               | This is a GPIO designated by the default firmware as the Memory Stick card detection pin and has an internal weak pull-up resistor.                                                                                          |

| MS_SCLK   | 13                                           | O12                           | Memory Stick System Clock                                                                                                                                                                                                    |

|           |                                              |                               | This pin is an output clock signal to the MS device.                                                                                                                                                                         |

| MS_D[7:0] | 20<br>19                                     | I/O12PD                       | Memory Stick System Data In/Out                                                                                                                                                                                              |

|           | 17<br>18<br>32                               |                               | These pins are the bi-directional data signals for the MS device. In serial mode, the most significant bit (MSB) of each byte is transmitted first by either MSC or MS device on MS_D0.                                      |

|           | 30<br>23<br>24                               |                               | MS_D0, MS_D2, and MS_D3 have weak pull-down resistors. MS_D1 has a pull down resistor if in parallel mode, otherwise it is disabled. In 4- or 8-bit parallel modes, all MS_D7 - MS_D0 signals have weak pull-down resistors. |

|           | I                                            | SECURE DIC                    | GITAL / MULTIMEDIACARD INTERFACE                                                                                                                                                                                             |

| SD_D[7:0] | 19<br>20<br>23<br>30<br>32<br>33<br>17<br>18 | I/O12PU                       | Secure Digital Data 7-0  These are the bi-directional data signals SD_D0-SD_D7 and have weak pull-up resistors.                                                                                                              |

| SD_CLK    | 21                                           | O12                           | Secure Digital Clock                                                                                                                                                                                                         |

|           |                                              |                               | This is an output clock signal to the SD/MMC device.                                                                                                                                                                         |

| SD_CMD    | 24                                           | I/O12PU                       | Secure Digital Command                                                                                                                                                                                                       |

|           |                                              |                               | This is a bi-directional signal that connects to the CMD signal of the SD/MMC device and has an internal weak pull-up resistor.                                                                                              |

| GPIO6 /   | 13                                           | I/O12                         | This general purpose pin may be used either as input, edge sensitive interrupt input, or output. Custom firmware is required to activate this function.                                                                      |

| SD_WP     |                                              |                               | Secure Digital Write Protected GPIO                                                                                                                                                                                          |

|           |                                              |                               | This is a GPIO designated by the default firmware as the Secure Digital card mechanical write protect detect pin.                                                                                                            |

| GPIO15 /  | 14                                           | I/O12                         | This general purpose pin may be used either as input, edge sensitive interrupt input, or output. Custom firmware is required to activate this function.                                                                      |

| SD_nCD    |                                              |                               | Secure Digital Card Detect GPIO                                                                                                                                                                                              |

|           |                                              |                               | This is a GPIO designated by the default firmware as the Secure Digital card detection pin.                                                                                                                                  |

Table 6.1 USB2640i/USB2641i Pin Descriptions (continued)

| SYMBOL            | 48-PIN<br>QFN | BUFFER<br>TYPE<br>(Table 6.2) | DESCRIPTION                                                                                                                                                                                    |  |  |  |  |

|-------------------|---------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                   | USB INTERFACE |                               |                                                                                                                                                                                                |  |  |  |  |

| USB-<br>USB+      | 43            | I/O-U                         | USB Bus Data                                                                                                                                                                                   |  |  |  |  |

| 0351              | 42            |                               | These pins connect to the upstream USB bus data signals. USB+ and USB- can be swapped using the PortSwap feature (See Section 7.3.5.20, "F1h: Port Swap," on page 46).                         |  |  |  |  |

| USBDN_DM<br>[3:2] | 3<br>1        | I/O-U                         | USB Bus Data                                                                                                                                                                                   |  |  |  |  |

| USBDN_DP<br>[3:2] | 4 2           |                               | These pins connect to the downstream USB bus data signals and can be swapped using the PortSwap feature (See Section 7.3.5.20, "F1h: Port Swap," on page 46).                                  |  |  |  |  |

| PRTCTL[3:2]       | 7<br>6        | I/OD12PU                      | USB Power Enable                                                                                                                                                                               |  |  |  |  |

|                   |               |                               | As an output, these pins enable power to downstream USB peripheral devices and have weak internal pull-up resistors. See Section 6.3, "Port Power Control" for diagram and usage instructions. |  |  |  |  |

|                   |               |                               | As an input, when the power is enabled, these pins monitor the over-<br>current condition. When an over-current condition is detected, the<br>pins turn the power off.                         |  |  |  |  |

| VBUS_DET          | 39            | I                             | Detect Upstream VBUS Power                                                                                                                                                                     |  |  |  |  |

|                   |               |                               | Detects the state of upstream VBUS power. The Hub monitors VBUS_DET to determine when to assert the internal D+ pull-up resistor (signaling a connect event).                                  |  |  |  |  |

|                   |               |                               | When designing a detachable hub, connect this pin to the VBUS power pin of the USB port that is upstream of the Hub.                                                                           |  |  |  |  |

|                   |               |                               | For self-powered applications with a permanently attached host, this pin should be pulled up, typically to VDD33.                                                                              |  |  |  |  |

|                   |               |                               | VBUS is a 3.3 volt input. A resistor divider must be used if connecting to 5 volts of USB power.                                                                                               |  |  |  |  |

| RBIAS             | 47            | I-R                           | USB Transceiver Bias                                                                                                                                                                           |  |  |  |  |

|                   |               |                               | A 12.0 k $\Omega$ ±1.0% resistor is attached from VSS to this pin in order to set the transceiver's internal bias currents.                                                                    |  |  |  |  |

| XTAL1<br>(CLKIN)  | 45            | ICLKx                         | 24 MHz Crystal Input or External clock Input                                                                                                                                                   |  |  |  |  |

| (32)              |               |                               | This pin can be connected to one terminal of the crystal or it can be connected to an external 24 MHz 1.8 V clock when a crystal is not used.                                                  |  |  |  |  |

| XTAL2             | 44            | OCLKx                         | 24 MHz Crystal Output                                                                                                                                                                          |  |  |  |  |

|                   |               |                               | This is the other terminal of the crystal, or it is left open when an external clock source is used to drive XTAL1(CLKIN).                                                                     |  |  |  |  |

Table 6.1 USB2640i/USB2641i Pin Descriptions (continued)

| SYMBOL      | 48-PIN<br>QFN | BUFFER<br>TYPE<br>(Table 6.2) | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |

|-------------|---------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |               |                               | SPI INTERFACE                                                                                                                                                                                                                                                                                                                |

| SPI_CE_n    | 8             | O12                           | SPI Chip Enable                                                                                                                                                                                                                                                                                                              |

|             |               |                               | This is the active low chip enable output.                                                                                                                                                                                                                                                                                   |

|             |               |                               | When the SPI interface is enabled, drive this pin high in power down states.                                                                                                                                                                                                                                                 |

| SPI_CLK /   | 9             | I/O12                         | SPI Clock                                                                                                                                                                                                                                                                                                                    |

|             |               |                               | This is the SPI clock out to the serial ROM. See Section 6.4, "ROM BOOT Sequence" for diagram and usage instructions. During reset, drive this pin low.                                                                                                                                                                      |

| GPIO4 /     |               |                               | This pin may be used either as input, edge sensitive interrupt input, or output. Custom firmware is required to activate this function.                                                                                                                                                                                      |

| SCL         |               |                               | When configured, this is the I <sup>2</sup> C EEPROM clock pin.                                                                                                                                                                                                                                                              |

| SPI_DO /    | 10            | I/O12                         | SPI Data Out                                                                                                                                                                                                                                                                                                                 |

|             |               |                               | This is the data out for the SPI port. See Section 6.4, "ROM BOOT Sequence" for diagram and usage instructions.                                                                                                                                                                                                              |

| GPIO5 /     |               |                               | This pin may be used either as input, edge sensitive interrupt input, or output. Custom firmware is required to activate this function.                                                                                                                                                                                      |

| SDA /       |               |                               | This pin is the data pin when the device is connected to the optional I <sup>2</sup> C EEPROM.                                                                                                                                                                                                                               |

| SPI_SPD_SEL |               |                               | This pin is used to select the speed of the SPI interface. During nRESET assertion, this pin will be tri-stated with the weak pull-down resistor enabled. When nRESET is negated, the value on the pin will be internally latched, and the pin will revert to SPI_DO functionality, the internal pull-down will be disabled. |

|             |               |                               | '0' = 30 MHz (No external resistor should be applied) '1' = 60 MHz (A 10 K external pull-up resistor must be applied)                                                                                                                                                                                                        |

|             |               |                               | If the latched value is '1', then the pin is tri-stated when the chip is in the suspend state.                                                                                                                                                                                                                               |

|             |               |                               | If the latched value is '0', then the pin is driven low during a suspend state.                                                                                                                                                                                                                                              |

| SPI_DI      | 11            | I/O12PD                       | SPI Data In                                                                                                                                                                                                                                                                                                                  |

|             |               |                               | This is the data in to the controller from the ROM. This pin has a weak internal pull-down applied at all times to prevent floating.                                                                                                                                                                                         |

|             |               |                               | MISC                                                                                                                                                                                                                                                                                                                         |

| GPIO1 /     | 37            | I/O12                         | This pin may be used either as input, edge sensitive interrupt input, or output. Custom firmware is required to activate this function.                                                                                                                                                                                      |

| LED /       |               |                               | GPIO1 can be used as an LED output.                                                                                                                                                                                                                                                                                          |

| TXD         |               |                               | The signal can be used as input to the TxD of UART in the device. Custom firmware is required to activate this function.                                                                                                                                                                                                     |

Table 6.1 USB2640i/USB2641i Pin Descriptions (continued)

| SYMBOL    | 48-PIN<br>QFN  | BUFFER<br>TYPE<br>(Table 6.2)  | DESCRIPTION                                                                                                                                                                                          |

|-----------|----------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO2 /   | 36             | I/O12                          | This pin may be used either as input, edge sensitive interrupt input, or output. Custom firmware is required to activate this function.                                                              |

| RXD       |                |                                | This signal can used as input to the RXD of the internal UART. Custom firmware is required to activate this function.                                                                                |

| GPIO10    | 35             | I/O200                         | Card power drive: 3.3 V (100 mA or 200 mA)                                                                                                                                                           |

| (CRD_PWR) |                |                                | This pin powers the multiplexed flash media interface (slot) for xD, MS, and SD/MMC. If card power is not being used to power the multiplexed flash media interface, this pin may be used as a GPIO. |

|           |                |                                | It is a requirement for this to be the only FET used to power xD-Picture Card devices. Failure to do this will violate xD voltage specification on xD-Picture Card device pins.                      |

|           |                |                                | Bits 0, 1, 2, and 3 control FET 2 of Register A5h. Please reference Section 7.3.4.5, "A8h: LED Blink Interval (1 byte)," on page 38.                                                                 |

| nRESET    | 38             | IS                             | RESET Input                                                                                                                                                                                          |

|           |                |                                | The system uses this active low signal to reset the chip. The active low pulse should be at least 1 $\mu s$ wide.                                                                                    |

| TEST      | 40             | I                              | TEST Input                                                                                                                                                                                           |

|           |                |                                | Tie this pin to ground for normal operation.                                                                                                                                                         |

| NC        | 22<br>26       |                                | No Connects                                                                                                                                                                                          |

|           | 27<br>28       |                                | No connect pins only apply to the USB2641i. No trace or signal should be routed or attached to these pins.                                                                                           |

|           |                | D                              | IGITAL / POWER / GROUND                                                                                                                                                                              |

| CRFILT    | 15             |                                | VDD Core Regulator Filter Capacitor                                                                                                                                                                  |

|           |                |                                | This pin must have a 1.0 $\mu\text{F}$ (or greater) $\pm20\%$ (ESR <0.1 $\Omega)$ capacitor to VSS.                                                                                                  |

| VDD33     | 5<br>12        |                                | 3.3 V Power and Voltage Regulator Inputs                                                                                                                                                             |

|           | 16<br>25<br>34 |                                | Please refer to Chapter 10, "DC Parameters," on page 58 for more information.                                                                                                                        |

|           | 41<br>48       |                                | Pins 16 and 48 each require an external bypass capacitor of 4.7 $\mu\text{F}$ minimum.                                                                                                               |

| PLLFILT   | 46             | PLL Regulator Filter Capacitor |                                                                                                                                                                                                      |

|           |                |                                | This pin must have a 1.0 $\mu\text{F}$ (or greater) $\pm20\%$ (ESR <0.1 $\Omega)$ capacitor to VSS.                                                                                                  |

| VSS       | ePad           |                                | The ground pad / ePad is the only VSS for the device and must be tied to ground with multiple vias.                                                                                                  |

# 6.2 Buffer Type Descriptions

Table 6.2 USB2640i/USB2641i Buffer Type Descriptions

| BUFFER   | DESCRIPTION                                                                                     |

|----------|-------------------------------------------------------------------------------------------------|

| 1        | Input.                                                                                          |

| IPU      | Input, weak internal pull-up.                                                                   |

| IS       | Input with Schmitt trigger.                                                                     |

| I/O12    | Input/output buffer with 12 mA sink and 12 mA source.                                           |

| I/O200   | Input/output buffer 12 mA with FET disabled, 100/200 mA source only when the FET is enabled.    |

| I/O12PD  | Input/output buffer with 12 mA sink and 12 mA source, with an internal weak pull-down resistor. |

| I/O12PU  | Open drain, 12 mA sink with pull-up. Input with Schmitt trigger.                                |

| I/OD12PU | Input/open drain output buffer with a 12 mA sink.                                               |

| O12      | Output buffer with a 12 mA sink and a 12 mA source.                                             |

| O12PD    | Output buffer with 12 mA sink and 12 mA source, with a pull-down resistor.                      |

| O12PU    | Output buffer with 12 mA sink and 12 mA source, with a pull-up resistor.                        |

| ICLKx    | XTAL clock input.                                                                               |

| OCLKx    | XTAL clock output.                                                                              |

| I/O-U    | Analog input/output as defined in the USB 2.0 Specification.                                    |

| I-R      | RBIAS.                                                                                          |

#### 6.3 Port Power Control

#### Port Power Control Using USB Power Switch

The USB2640i/USB2641i has a single port power control and over-current sense signal for each downstream port. When disabling port power, the driver will actively drive a '0'. To avoid unnecessary power dissipation, the internal pull-up resistor will be disabled at that time. When port power is enabled, the output driver is disabled, and the pull-up resistor is enabled creating an open drain output. If there is an over-current situation, the USB Power Switch will assert the open drain OCS signal. The Schmitt trigger input will detect this event as a low. The open drain output does not interfere. The internal over-current sense filter handles the transient conditions, such as low voltage, while the device is powering up.

Figure 6.1 Port Power Control with USB Power Switch

#### Port Power Control Using a Poly Fuse

When using the USB2640i/USB2641i with a poly fuse, an external diode must be used (See Figure 6.2). When disabling port power, the USB2640i/USB2641i will drive a '0'. This procedure will have no effect since the external diode will isolate the pin from the load. When port power is enabled, the USB2640i/USB2641i output driver is disabled, and the pull-up resistor is enabled which creates an open drain output. The open drain output condition means that the pull-up resistor is providing 3.3 volts to the anode of the diode. If there is an over-current situation, the poly fuse will open causing the cathode of the diode to go to 0 volts. The anode of the diode will be at 0.7 volt, and the Schmitt trigger input will register this as a low resulting in an over-current detection. The open drain output does not interfere.

Figure 6.2 Port Power control with Poly Fuse

When using a single poly fuse to power all devices, note that for the ganged situation, all power control pins must be tied together.

Figure 6.3 Port Power with Ganged Control with Poly Fuse

## 6.4 ROM BOOT Sequence

After power-on reset, the internal firmware checks for an external SPI flash device that contains a valid signature of "2DFU" (device firmware upgrade) beginning at address 0xFFFA. If a valid signature is found, then the external ROM is enabled and code execution begins at address 0x0000 in the external SPI device. Otherwise, code execution continues from the internal ROM.

If there is no SPI ROM detected, the internal firmware then checks for the presence of an I<sup>2</sup>C ROM. The firmware looks for the signature 'ATA2' at the offset of 0xFC-0xFF in the I<sup>2</sup>C ROM. The firmware reads in the I<sup>2</sup>C ROM to configure the hardware and software internally. Please refer to section 7.3.2 EEPROM Data Descriptor on page 29 for the details of the configuration options.

The SPI ROM required for the USB2640i/USB2641i must be 1 Mbit and support either 30 MHz or 60 MHz. The frequency used is set using the SPI\_SPD\_SEL. For 30 MHz operation, this pin must be pulled to ground through a 100  $k\Omega$  resistor. For 60 MHz operation, this pin must pulled up through a 100  $k\Omega$  resistor. SPI\_SPD\_SEL: This pin is used to choose the speed of the SPI interface. During nRESET assertion, this pin will be tri-stated with the weak pull-down resistor enabled. When nRESET is negated, the value on the pin will be internally latched, and the pin will revert to SPI\_DO functionality, the internal pull-down will be disabled.

The firmware can determine the speed of operation on the SPI port by checking the SPI\_SPEED in the SPI\_CTL register (0x2400 - RESET = 0x02). Both 1- and 2-bit SPI operation is supported. For optimum throughput, a 2-bit SPI ROM is recommended. Both mode 0 and mode 3 SPI ROMS are also supported.

Figure 6.4 USB2640i/USB2641i SPI ROM Connection

Figure 6.5 USB2640i/USB2641i I<sup>2</sup>C Connection

# **Chapter 7 Configuration Options**

#### 7.1 Hub

SMSC's USB 2.0 hub is fully compliant to the Universal Serial Bus Specification available from the USB Implementer's Forum found at http://www.usb.org (Revision 2.0 April 27, 2000 and the 12/7/2000 and 5/28/2002 Errata). Please reference Chapter 11 (Hub Specification) for general details regarding hub operation and functionality.

The hub provides 1 transaction translator (TT) that is shared by both downstream ports (defined as a single-TT configuration). The TT contains 4 non-periodic buffers.

## 7.1.1 Hub Configuration Options

The SMSC hub supports a large number of features (some are mutually exclusive), and must be configured in order to correctly function when attached to a USB host controller. There are two principal ways to configure the hub:

- via the internal default settings or

- by settings stored in an external EEPROM or SPI Flash device.

#### 7.1.1.1 Power Switching Polarity

The hub only supports active high port power controllers.

#### 7.1.2 VBus Detect

According to Section 7.2.1 of the USB 2.0 Specification, a downstream port cannot provide power to its D+ or D- pull-up resistors unless the upstream port's VBUS is in the asserted (powered) state. The VBUS\_DET pin on the hub monitors the state of the upstream VBUS signal and will not pull-up the D+ resistor if VBUS is not active. If VBUS goes from an active to an inactive state (not powered), the hub will remove power from the D+ pull-up resistor within 10 seconds.

#### 7.2 Card Reader

The SMSC USB2640i/USB2641i is fully compliant with the following flash media card reader specifications: