# Universal 3.5mmØ Accessory Management IC

#### **General Description**

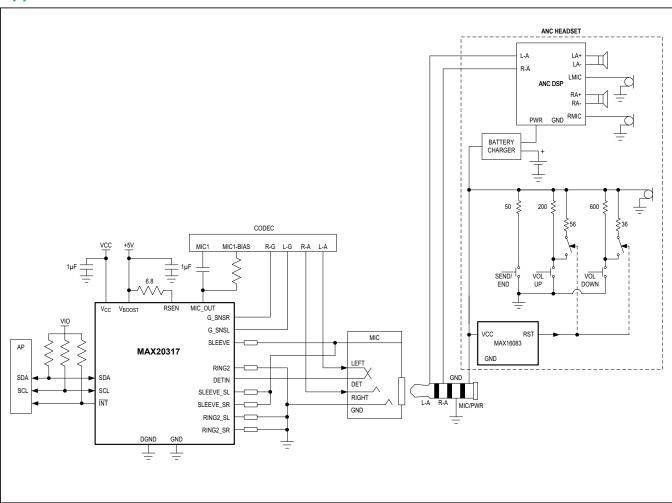

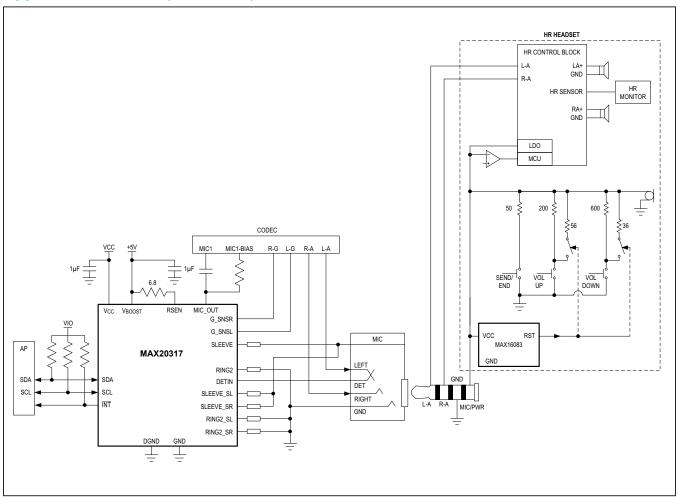

The MAX20317 is an I<sup>2</sup>C controllable, universal 3.5mmØ accessory management IC. The device provides a universal jack interface solution, as well as a compact solution for the power management and interface control of a powered accessory, such as an active noise cancelling (ANC) headset.

The MAX20317 automatically measures headset impedance with a high precision, triple current source 8 bit ADC. After impedance detection, the device also detects when a headset is in a CTIA or OMTP configuration and automatically configures the SLEEVE and RING2 terminals to correctly connect the microphone and ground lines.

When a boost supply is applied, the MAX20317 can detect the presence of an ANC headset. When the ANC headset is detected and enabled, a button-press monitoring circuit activates and flags button presses by detecting the voltage drop across a sense resistor.

The MAX20317 provides a power line communication tool to a headset to exchange the data with the host device.

The MAX20317 has the two separate ground sense inputs from the SLEEVE and RING2 terminals of the connector to provide a high ground isolation to the audio codec.

The MAX20317 is available in a space-saving, 20-bump, 0.4mm pitch, 1.65mm x 2.05mm wafer-level package (WLP) and operates over the -40 $^{\circ}$ C to +85 $^{\circ}$ C extended temperature range.

### **Applications**

- Smart Phones

- Tablet PCs

- Phablet

- Notebook PCs

#### **Benefits and Features**

- Allows Wide Range of Applications by Supporting Universal 3.5mm Jack Types

- · Auto-Configuration for CTIA and OMTP Headsets

- Supports MEMS Microphone

- 50mΩ Ground Switch

- Enables Long Utilization of Accessories by Supplying Power Through 3.5mm Jack

- · Powered Accessory/Headset Detection

- Bypass Switch to Power Accessories such as ANC Headsets

- Programmable Button Detection in Powered Accessory Mode

- Empowers New Path in Data Communication to Accessories

- Power Line Communication by 3.5mm Jack

- Bidirectional Digital Data Communication in Power Mode

- Allow Emergence of New Accessory Types

- Provides Comfortable Sounds by Introducing Automatic Volume Adjustment

- Adaptive Volume Control Based on Precision Headset Impedance

- · False Insertion Detection

- Saves Board Space with Small Form Factor

- 1.65mm x 2.05mm 4 x 5 Array 20 Bump 0.4mm Pitch WLP

Ordering Information appears at end of data sheet.

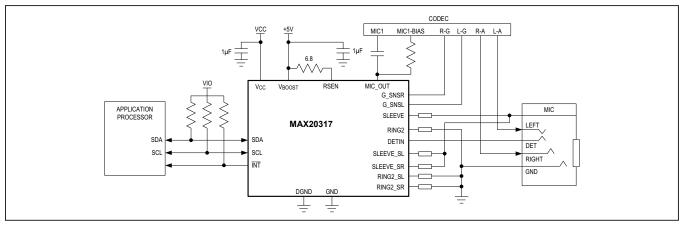

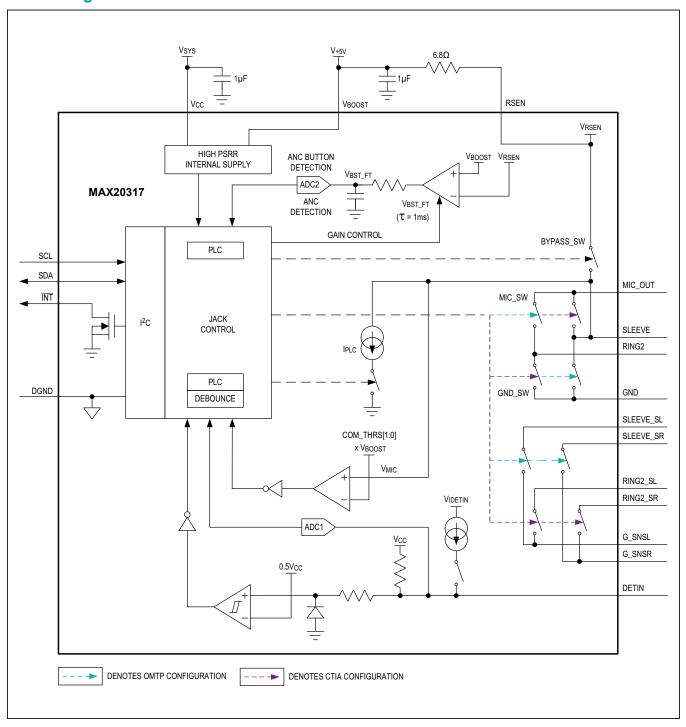

# **Typical Application Circuit**

# **Absolute Maximum Ratings**

| All voltages are referred to GND unless oth        | erwise noted               |

|----------------------------------------------------|----------------------------|

| V <sub>CC</sub> , SCL, SDA, INT                    | 0.3V to +6V                |

| V <sub>BOOST</sub> , RSEN                          | 0.3V to +12V               |

| MIC_OUT                                            | $-0.3V$ to $V_{CC} + 0.3V$ |

| DETIN                                              |                            |

| SLEEVE, SLEEVE_SL, SLEEVE_SR,                      |                            |

| RING2, RING2_SL, RING2_SR                          | 0.3V to +6V                |

| G_SNSL, G_SNSR                                     | 0.3V to +0.3V              |

| Continuous Current into V <sub>BOOST</sub> , RSEN, |                            |

| MIC_OUT, RING2, SLEEVE                             | ±200mA                     |

| Continuous Current into Any Other Terminal   | ±100mA         |

|----------------------------------------------|----------------|

| Continuous Power Dissipation (Multilayer Boa | rd)            |

| (Derate 18.02mW/°C above +70°C)              | 1441.6mW       |

| Operating Temperature Range                  | 40°C to +85°C  |

| Junction Temperature                         | +150°C         |

| Storage Temperature Range                    | 65°C to +150°C |

| Soldering Temperature (Reflow)               | +260°C         |

|                                              |                |

#### **Package Thermal Characteristics (Note 1)**

WLP

Junction-to-Ambient Thermal Resistance, Four Layer Board (θ<sub>JA</sub>)......55.49°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

$(V_{CC}$  = +3.0V to +5.5V,  $V_{BOOST}$  = 0V to +5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = +3.5V,  $T_A$  = +25°C.) (Note 2)

| PARAMETER                      | SYMBOL                | CONDITIONS                                                                              | MIN                      | TYP                      | MAX                      | UNITS |

|--------------------------------|-----------------------|-----------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|-------|

| V <sub>CC</sub>                |                       |                                                                                         |                          |                          |                          |       |

| Supply Voltage Range           | V <sub>CC</sub>       |                                                                                         | 3                        |                          | 5.5                      | V     |

| V <sub>CC</sub> POR            | V <sub>CCPOR</sub>    |                                                                                         | 0.9                      | 1.7                      | 2.45                     | V     |

|                                |                       | V <sub>CC</sub> = +3.5V, DETIN = 1                                                      |                          | 2                        | 5                        |       |

| V <sub>CC</sub> Supply Current | I <sub>VCC</sub>      | BYPASS (0x08[2]) = 0, DETIN = 0                                                         |                          | 10                       | 15                       | μA    |

| VCC Supply Sulfolic            | 1,000                 | V <sub>CC</sub> = +3.5V, BYPASS (0x08[2]) = 1,<br>DETIN = 0, I <sub>VBOOST</sub> = 30mA |                          | 0.1                      | 0.2                      | mA    |

| Bypass Supply Voltage<br>Range | V <sub>BOOST</sub>    |                                                                                         |                          |                          | 5.5                      | V     |

| DETIN                          |                       |                                                                                         |                          |                          |                          |       |

| DETIN Pullup Current           | I <sub>DETIN_PU</sub> |                                                                                         |                          | 4.5                      |                          | μA    |

| DETIN Detection<br>Threshold   |                       |                                                                                         | 1/3 x<br>V <sub>CC</sub> | 1/2 x<br>V <sub>CC</sub> | 2/3 x<br>V <sub>CC</sub> | V     |

|                                |                       | SET_IDET (0x0B[5:4]) = 01                                                               | 95                       | 100                      | 105                      | μA    |

| DETIN Current Source           | I <sub>DETIN</sub>    | SET_IDET (0x0B[5:4]) = 10                                                               | 1.05                     | 1.1                      | 1.15                     | mA    |

|                                |                       | SET_IDET (0x0B[5:4]) = 11                                                               | 5.25                     | 5.5                      | 5.75                     | IIIA  |

# **Electrical Characteristics (continued)**

$(V_{CC}$  = +3.0V to +5.5V,  $V_{BOOST}$  = 0V to +5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = +3.5V,  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                    | SYMBOL                  | CONDITIONS                                                                                                                                       | MIN TYP MAX |       | UNITS |                     |

|----------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-------|---------------------|

| BYPASS SWITCH                                |                         |                                                                                                                                                  |             |       |       |                     |

| Output Shutdown<br>R <sub>SEN</sub> Drop     | V <sub>SH</sub>         | V <sub>BOOST</sub> = 5.0V                                                                                                                        | 1.28        | 1.36  | 1.44  | V                   |

| Bypass Switch R <sub>ON</sub>                | R <sub>BYPASS</sub>     | $V_{CC}$ = 4.2V, $V_{BOOST}$ = 5.0V,<br>$I_{BYPASS}$ = 150mA                                                                                     |             | 1     | 1.5   | Ω                   |

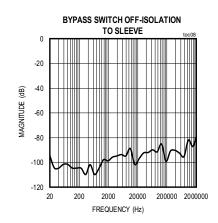

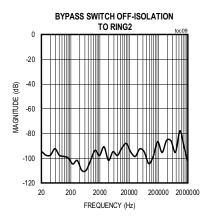

| Off Isolation to SLEEVE                      |                         | $V_{RSEN} = 5V \pm 50$ mV,<br>f = 20Hz to 20kHz                                                                                                  |             | -90   |       | dB                  |

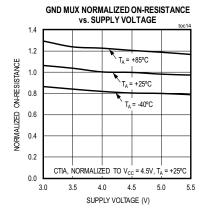

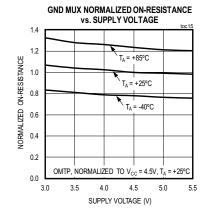

| SLEEVE, RING2 (GND MU                        | X SWITCH)               |                                                                                                                                                  |             |       |       |                     |

| Ground MUX Switch RON                        | R <sub>GMP</sub>        | V <sub>CC</sub> = 3.5V                                                                                                                           |             | 50    | 85    | mΩ                  |

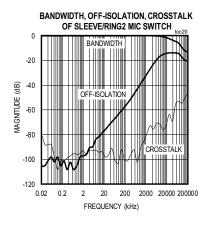

| Ground MUX Switch<br>Bandwidth               |                         | $R_{SOURCE} = R_{LOAD} = 50\Omega$                                                                                                               |             | 300   |       | MHz                 |

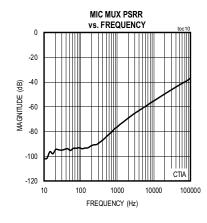

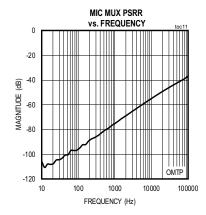

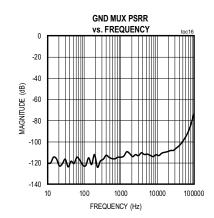

| Ground Switch PSRR                           | PSRR <sub>GNDSW</sub>   | V <sub>CC</sub> = 3.5V, R <sub>SOURCE</sub> = 50Ω, f = 217Hz                                                                                     |             | -96   |       | dB                  |

| Ground Bypass Switch<br>THD                  |                         | 100mV <sub>Pk-Pk</sub> , DC bias = 0V, f = 20Hz<br>to 20KHz, R <sub>SOURCE</sub> = R <sub>LOAD</sub> = $50\Omega$                                |             | 0.002 |       | %                   |

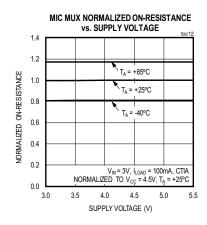

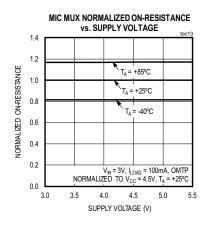

| SLEEVE, RING2 (MIC MUX                       | SWITCH)                 |                                                                                                                                                  |             |       |       |                     |

| MIC Switch Turn-On Time                      |                         |                                                                                                                                                  |             | 5     |       | μs                  |

| MIC Switch Turn-Off Time                     |                         |                                                                                                                                                  |             | 4     |       | μs                  |

| MIC Switch R <sub>ON</sub>                   | R <sub>MIC</sub>        | V <sub>CC</sub> = 3.5V, I = 10mA                                                                                                                 |             | 1     | 2     | Ω                   |

| MIC Switch Bandwidth                         |                         | R <sub>SOURCE</sub> = R <sub>LOAD</sub> = 50Ω                                                                                                    |             | 25    |       | MHz                 |

| MIC Switch PSRR                              |                         | $V_{CC}$ = 3.5V, $R_{SOURCE}$ = $50\Omega$ , $f$ = 217Hz                                                                                         |             | -90   |       | dB                  |

| MIC Switch Isolation                         |                         |                                                                                                                                                  |             | -90   |       | dB                  |

| V <sub>BOOST</sub> , RSEN (ANC DET           | ECTION)                 |                                                                                                                                                  |             |       |       |                     |

| ANC Headset Detection<br>Accuracy            |                         | Using 6.8Ω External Sense for ANC detection, range from 1.5 to 5mA (ADC2_HL(0x0B[2])) = 1. Thresholds I <sup>2</sup> C Programmable by HSDET_VAL | -3          |       | +3    | %                   |

| Button Press Current<br>Measurement Accuracy |                         | Using $6.8\Omega$ External Sense, range from 5mA to 200mA (ADC2_HL(0x0B[2])) = 0. Thresholds I <sup>2</sup> C Programmable by HSDET_VAL          | -3          |       | +3    | %                   |

|                                              |                         | COM_THRS[1:0](0x08[1:0]) = 00                                                                                                                    | 87          | 88    | 89    | %V <sub>BOOST</sub> |

| ANC Button Detection Interrupt Falling Edge  | VCOM DET                | COM_THRS[1:0] (0x08[1:0]) = 01                                                                                                                   | 89          | 90    | 91    | %V <sub>BOOST</sub> |

| Threshold                                    | V <sub>COM_DET</sub>    | COM_THRS[1:0] (0x08[1:0]) = 10                                                                                                                   | 91          | 92    | 93    | %V <sub>BOOST</sub> |

|                                              |                         | COM_THRS[1:0] (0x08[1:0]) = 11                                                                                                                   | 93          | 94    | 95    | %V <sub>BOOST</sub> |

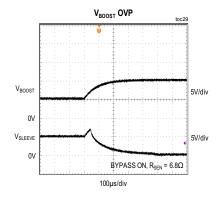

| BOOST OVP OVLO<br>Threshold                  | V <sub>BOOST_OVLO</sub> | V <sub>BOOST</sub> slew rate ≤ 1V/μs                                                                                                             | 5.6         | 5.75  | 5.94  | V                   |

# **Electrical Characteristics (continued)**

$(V_{CC}$  = +3.0V to +5.5V,  $V_{BOOST}$  = 0V to +5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = +3.5V,  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                            | SYMBOL                | CONDITIONS                                                                                         | MIN                  | TYP   | MAX                  | UNITS               |

|------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------|----------------------|-------|----------------------|---------------------|

| GROUND SENSE SWITCH                                  | (G_SNSR/G_SN          | NSL)                                                                                               |                      |       |                      |                     |

| G_SNS Switch Turn-On<br>Time                         |                       |                                                                                                    |                      | 50    |                      | μs                  |

| G_SNS Switch Turn-Off<br>Time                        |                       |                                                                                                    |                      | 3     |                      | μs                  |

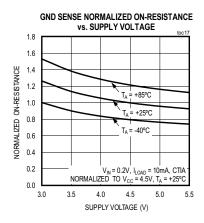

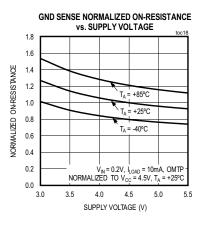

| G_SNS Switch R <sub>ON</sub>                         |                       | I <sub>LOAD</sub> = 10mA                                                                           |                      | 8.0   | 1.5                  | Ω                   |

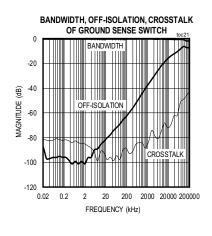

| G_SNS Switch Bandwidth                               |                       | $R_{SOURCE} = R_{LOAD} = 50\Omega,$<br>$C_{LOAD} = 10pF$                                           |                      | 300   |                      | MHz                 |

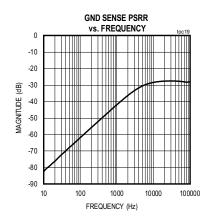

| G_SNS Switch PSRR                                    |                       | $V_{CC}$ = 3.3V, $R_{SOURCE}$ = $R_{LOAD}$ = 50 $\Omega$ , $f$ = 217Hz, $V_{IN}$ = 3.3V ±0.1V      |                      | -90   |                      | dB                  |

| G_SNS Switch Cross talk                              |                       | $V_{CC}$ = 3.3V, $R_{SOURCE}$ = $R_{LOAD}$ = 50 $\Omega$ , $f$ = 20Hz to 20kHz, $V_{MIC}$ = ±150mV |                      | -90   |                      | dB                  |

| DIGITAL SIGNALS (SDA, S                              | CL, INT)              |                                                                                                    |                      |       |                      |                     |

| Input Logic-High                                     | V <sub>IH</sub>       |                                                                                                    | 1.4                  |       |                      | V                   |

| Input Logic-Low                                      | V <sub>IL</sub>       |                                                                                                    |                      |       | 0.4                  | V                   |

| Input Leakage Current                                |                       |                                                                                                    | -1                   |       | 1                    | μA                  |

| Output Logic-High<br>Leakage Current<br>(Open-Drain) | loh_lkg               | V <sub>IO</sub> = 5V                                                                               |                      |       | 1                    | μΑ                  |

| Output Logic-Low                                     | V <sub>OL</sub>       | I <sub>SINK</sub> = 4mA                                                                            |                      |       | 0.4                  | V                   |

| POWER LINE COMMUNICATION                             | ATION                 |                                                                                                    |                      |       |                      |                     |

| PLC Logic-High                                       |                       | V <sub>BOOST</sub> = 5V, Low is V <sub>RSENSE</sub> below V <sub>COM_DET</sub>                     |                      |       | V <sub>COM_DET</sub> | V                   |

| PLC Logic-Low                                        |                       | V <sub>BOOST</sub> = 5V, High is V <sub>RSENSE</sub> above V <sub>COM_DET</sub>                    | V <sub>COM_DET</sub> |       |                      | V                   |

| Time Unit                                            | t <sub>UNIT</sub>     | I <sup>2</sup> C Programmable (24/30μs)<br>Inferred from 1μs clock                                 |                      | 24/30 |                      | μs                  |

| TX Logic 0                                           | t <sub>TXLOGIC0</sub> |                                                                                                    | 90                   |       | 110                  | % t <sub>UNIT</sub> |

| TX Logic 1                                           | tTXLOGIC1             | Period for low and high                                                                            | 40                   |       | 60                   | % t <sub>UNIT</sub> |

| RX Logic 0                                           | t <sub>RXLOGIC0</sub> |                                                                                                    | 85                   |       | 115                  | % t <sub>UNIT</sub> |

| RX Logic 1                                           | t <sub>RXLOGIC1</sub> | Period for low and high                                                                            | 35                   |       | 65                   | % t <sub>UNIT</sub> |

| DI O TV O                                            | _                     | PLC_SINK (0x18[6]) = 0                                                                             | 90                   | 100   | 110                  | mA                  |

| PLC TX Current Sink                                  | I <sub>PLC</sub>      | PLC_SINK(0x18[6]) = 1                                                                              | 70                   | 80    | 90                   | mA                  |

# **Electrical Characteristics (continued)**

$(V_{CC}$  = +3.0V to +5.5V,  $V_{BOOST}$  = 0V to +5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = +3.5V,  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                                          | SYMBOL               | CONDITIONS MIN TYP MAX                         |     | UNITS |     |

|--------------------------------------------------------------------|----------------------|------------------------------------------------|-----|-------|-----|

| DYNAMIC                                                            |                      |                                                |     |       |     |

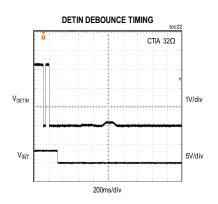

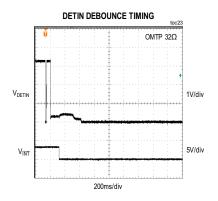

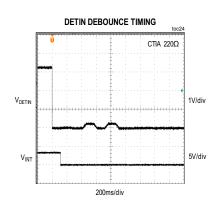

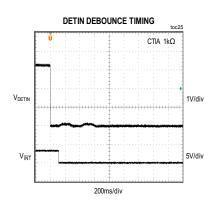

| DETIN Dahawaa Tiraa                                                |                      | DETIN Falling Edge, DET_DEBOUNCE (0x08[6]) = 0 | 115 |       |     |

| DETIN Debounce Time                                                | <sup>t</sup> DIDEB   | DETIN Falling Edge, DET_DEBOUNCE (0x08[6]) = 1 | 300 |       | ms  |

| SEND/END Debounce<br>Time                                          | <sup>t</sup> SEDEB   | I <sup>2</sup> C selectable: 20/30/40/50ms     | 30  |       | ms  |

| I <sub>DETIN</sub> Rise Time                                       | t <sub>IDETINR</sub> | Rising                                         | 50  |       | ms  |

| I <sub>DETIN</sub> Fall Time                                       | t <sub>IDETINF</sub> | Falling                                        | 50  |       | ms  |

| I <sup>2</sup> C TIMING                                            |                      |                                                |     |       |     |

| I <sup>2</sup> C Serial Clock<br>Frequency                         | f <sub>SCL</sub>     |                                                | 400 |       | kHz |

| ESD PROTECTION                                                     |                      |                                                |     |       |     |

| DETIN                                                              |                      | Human Body Model                               | ±15 |       | kV  |

| SLEEVE, RING2,<br>SLEEVE_SR, SLEEVE_<br>SL, RING2_SR, RING2_<br>SL |                      | Human Body Model                               | ±10 |       | kV  |

| All Other Pins                                                     |                      | Human Body Model                               | ±2  |       | kV  |

| THERMAL PROTECTION                                                 |                      |                                                |     |       |     |

| Thermal Shutdown                                                   | T <sub>SHDN</sub>    | Low to high                                    | 130 |       | °C  |

| Thermal Hysteresis                                                 | T <sub>HYST</sub>    | High to low                                    | 20  |       | °C  |

Note 2: All devices are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design.

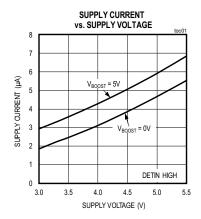

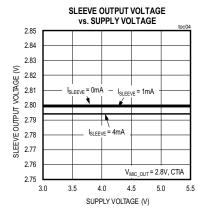

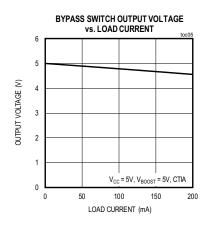

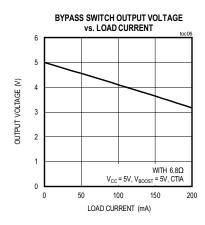

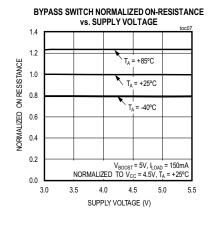

# **Typical Operating Characteristics**

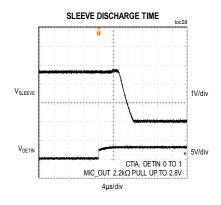

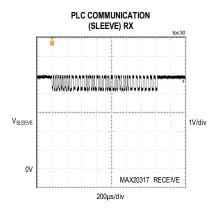

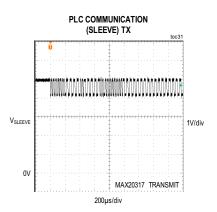

$(V_{CC}$  = +3.5V, R<sub>SEN</sub> = 6.8 $\Omega$ , T<sub>A</sub> = +25 $^{\circ}$ C unless otherwise noted.)

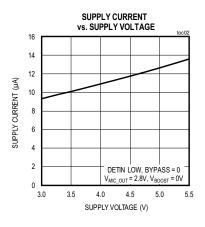

# **Typical Operating Characteristics (continued)**

$(V_{CC} = +3.5V, R_{SEN} = 6.8\Omega, T_A = +25^{\circ}C \text{ unless otherwise noted.})$

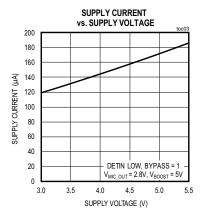

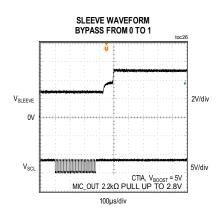

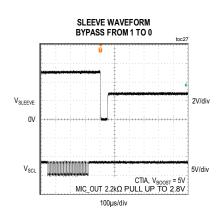

# **Typical Operating Characteristics (continued)**

$(V_{CC} = +3.5V, R_{SEN} = 6.8\Omega, T_A = +25^{\circ}C \text{ unless otherwise noted.})$

# **Typical Operating Characteristics (continued)**

( $V_{CC}$  = +3.5V,  $R_{SEN}$  = 6.8 $\Omega$ ,  $T_A$  = +25 $^{\circ}$ C unless otherwise noted.)

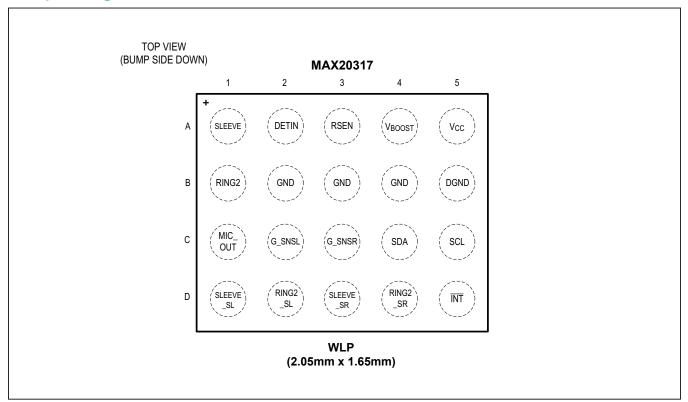

# **Bump Configuration**

# **Bump Descriptions**

| BUMP | NAME               | FUNCTION                                                                                                                                   |

|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| A1   | SLEEVE             | Jack Sleeve Pin Contact                                                                                                                    |

| A2   | DETIN              | Jack Insertion Detection Input. An internal comparator monitors DETIN for jack insertion/ removal events.                                  |

| А3   | RSEN               | RSEN connection for Bypass mode                                                                                                            |

| A4   | V <sub>BOOST</sub> | Supply Voltage Input for Bypass Mode. Bypass V <sub>BOOST</sub> to ground with a 1µF ceramic capacitor as close as possible to the device. |

| A5   | V <sub>CC</sub>    | Supply Voltage Input. Bypass $V_{CC}$ to ground with a 1 $\mu$ F decoupling capacitor as close as possible to the device.                  |

# **Bump Descriptions (continued)**

| BUMP       | NAME      | FUNCTION                                                                                                                                     |

|------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| B1         | RING2     | Jack Ring2 Pin Connection                                                                                                                    |

| B2, B3, B4 | GND       | Ground. Connect all GND and DGND pins together.                                                                                              |

| B5         | DGND      | Digital Ground. Connect all GND and DGND pins together.                                                                                      |

| C1         | MIC_OUT   | Microphone to Phone Codec Output                                                                                                             |

| C2         | G_SNSL    | Left Ground Reference Sense. G_SNSL is a ground reference prior to the ground switch to obtain a high ground isolation for the audio codec.  |

| C3         | G_SNSR    | Right Ground Reference Sense. G_SNSL is a ground reference prior to the ground switch to obtain a high ground isolation for the audio codec. |

| C4         | SDA       | I <sup>2</sup> C Data Line                                                                                                                   |

| C5         | SCL       | I <sup>2</sup> C Clock                                                                                                                       |

| D1         | SLEEVE_SL | Jack Sleeve Kelvin Pin Contact for Left Audio Line                                                                                           |

| D2         | RING2_SL  | Jack Ring2 Kelvin Pin Contact for Left Audio Line                                                                                            |

| D3         | SLEEVE_SR | Jack Sleeve Kelvin Pin Contact for Right Audio Line                                                                                          |

| D4         | RING2_SR  | Jack Ring2 Kelvin Pin Contact for Right Audio Line                                                                                           |

| D5         | ĪNT       | I <sup>2</sup> C Active-Low, Open-Drain Interrupt Output. Connect INT to an external pullup resistor.                                        |

# **Block Diagram**

#### **Detailed Description**

The MAX20317 supports both CTIA and OMTP headsets. The advanced method used to detect the headset type provides error free connections to ground and the microphone line. Manual control allows for future expansion of accessory types and functions.

In addition to detecting the jack configuration, the MAX20317 also reliably detects ANC headsets and headset button press events. A built-in, low offset 8-bit ADC provides a precise method of detecting an ANC headset and button presses in ANC music mode. These functions are handled automatically by the device, but can also be controlled manually.

For both ANC and normal headsets, the MAX20317 measures the impedance of the speaker. High precision current sources and an 8-bit ADC permit high accuracy sensing of low impedance headsets, even distinguishing between  $16\Omega$  and  $32\Omega$  speakers. This is useful in dynamic volume scaling applications.

The MAX20317 features power-line communication (PLC) for accessories powered by the microphone line. Data transmits above audio frequencies to prevent interference with the audio signal to the headset. This permits accessories to communicate with the device while a system is in music mode.

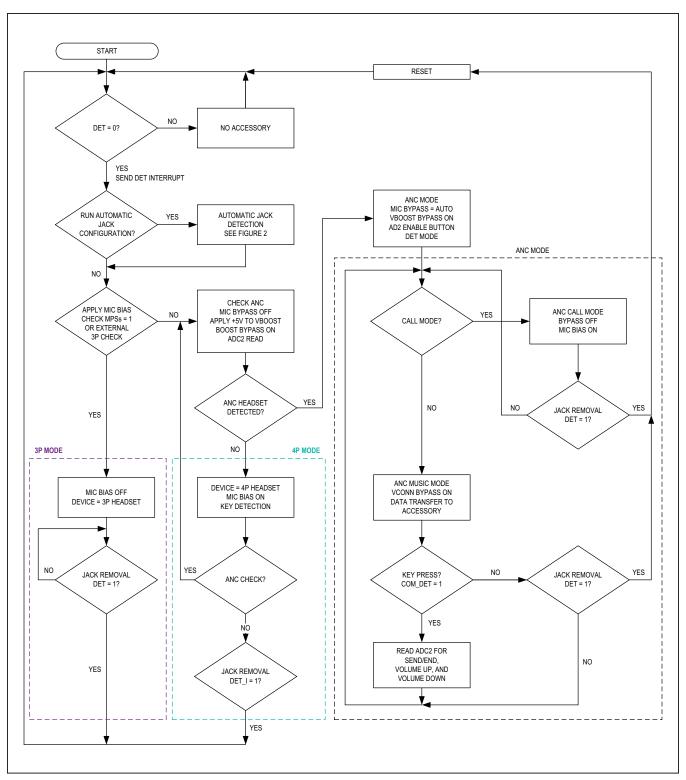

After the startup process is complete and the DEVICE\_READY bit (0x03[2]) is set, the MAX20317 enters normal operation. During this stage, an external controller and CODEC can confirm the jack type, either 3P or 4P, to enable or disable a MIC bias, detect the presence of an ANC headset, and communicate with accessories or use

the headset microphone. The full system flowchart is shown in <u>Figure 1</u>, while <u>Figure 2</u> details the jack detection process when a headset is connected.

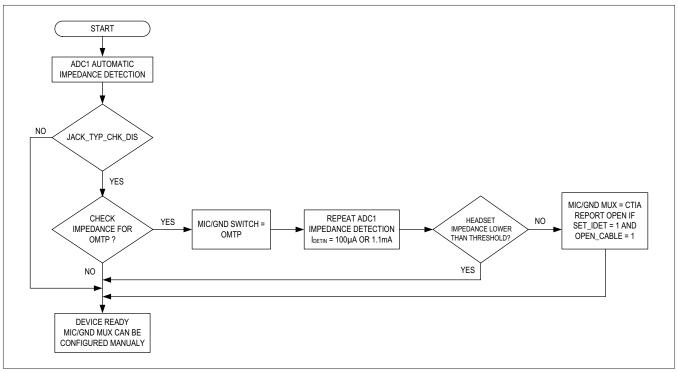

#### **Impedance Detection**

When the MAX20317 detects the presence of a headset, it can measure the headset impedance. DETIN applies a current,  $I_{DETIN}$ , to the left channel of the 3.5mm jack and reads the resulting DC voltage with ADC1. This measurement occurs automatically when DET goes low after a DETIN debounce period or triggers manually upon receipt of an  $I^2C$  command while DET = 0. The start condition is set with ADC\_CTRL[1:0] (0x0A[3:2]).

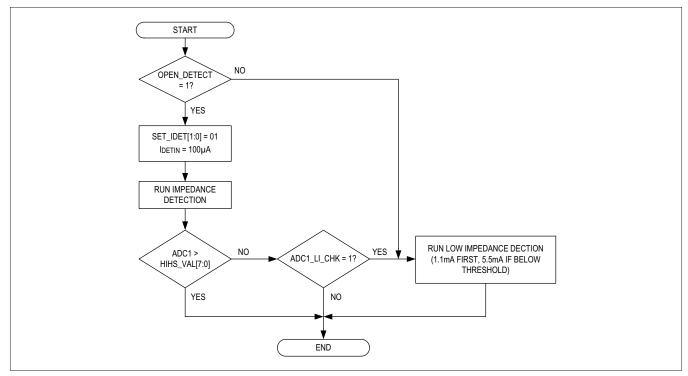

Automatic impedance measurements begin when a head-set insertion event forces DET low. The MIC and GND switches close in a CTIA configuration. If the OPEN\_DETECT bit (0x09[4]) is HIGH, IDETIN is set to 100 $\mu$ A for a high-impedance measurement. If the voltage measured by ADC1 is less than the value saved in HIHS\_VAL (register 0x0E), or if OPEN\_DETECT is low, a low impedance measurement is performed with IDETIN = 1.1mA. If the voltage is still too low, the low-impedance measurement is repeated with IDETIN = 5.5mA. This automatic process is illustrated in Figure 3.

Alternatively, the MAX20317 can measure impedance only upon receipt of an I<sup>2</sup>C command. Setting ADC1\_CTRL[1:0] to 01 or 10 causes the impedance measurement to trigger when FORCE\_ADC1\_START (0x0B[1]) goes high. The I<sub>DETIN</sub> value for manual impedance measurements is set by SET\_IDET[1:0] (0x0B[5:4]). After an automatic measurement, SET\_IDET[1:0] equals the last I<sub>DETIN</sub> value used in the impedance check, but it can be forced to any value for manual tests.

Figure 1. Full operation of the MAX20317

Figure 2. Automatic Jack Detection

Figure 3. ADC1 Automatic Impedance Detection

#### **CTIA/OMTP Detection**

The impedance measurement process is also used to identify a jack as CTIA or OMTP. When JACK\_ TYP CHK DIS = 0 (0x0A[6]), CTIA/OMTP detection begins after an automatic impedance measurement. This second measurement keeps the last value of IDETIN. either 100µA or 1.1mA, and measures the L-channel impedance with the MIC and GND MUX switches closed in OMTP mode. If the voltage measured by ADC1 is less than the threshold defined in OMTP VAL (register 0x0F) when testing a low-impedance headset, or HIHS VAL for high-impedance headsets, the MIC and GND MUX switches remain configured for OMTP. Otherwise, the switches connect in the CTIA configuration. Automatic jack detection is disabled when ADC1 is controlled manually or when JACK TYP CHK DIS = 1 and the MIC and GND switches must be set by FORCE MG SW[1:0] (0x09[1:0]) and MANUAL MG SW (0x09[5]).

#### **Open Cable Check**

If OPEN\_DETECT = 1 (0x09[4], the MAX20317 performs an open cable check after determining the jack type. If a high-impedance measurement exceeds the HIHS\_VAL threshold, the cable is considered open and the OPEN\_CABLE flag (0x03[4]) is set. This feature helps ensure that a there is a clean connection to a real headset when DET goes LOW after the DETIN debounce period.

#### **ANC Headset Detection**

The MAX20317 identifies ANC headsets by measuring the current drawn through an external resistor connected to RSEN. If there is +5V present on  $V_{BOOST}$ , an automatic measurement launches when the bypass switch closes. An internal, high-gain differential amplifier measures the current through the sense resistor and is read by ADC2. If the current is higher than HSDET\_VAL (register 0x10), the headset is considered to be ANC and the ANC\_HS bit (0x05[7]) is set. ANC headset detection is only compatible with CTIA headsets.

#### **ANC Current Sense**

The MAX20317 automatically detects ANC button presses while in BYPASS mode through the current sense resistor. When a button is pressed, the microphone voltage drops, triggering a COM\_DET interrupt. This also triggers an automatic ADC2 conversion. The ADC2 conversion continues as long as the microphone voltage is below the COM\_DET threshold set by COM\_THRS[1:0] (0x08[1:0]).

#### **Pop-Up Noise Suppression**

In order to prevent any pop-up noise, SLEEVE and RING2 are discharged immediately after a headset is unplugged.

#### **Microphone Short Protection**

Overcurrent protection on RSEN protects the MAX20317 from drawing too much current through the sense resistor. When the voltage drop across the sense resistor exceeds  $V_{SH}$  for longer than the time set in tSHO\_DEB[1:0] (0x0D[1:0]), the MPSs bit (0x04[4]) is set and triggers an interrupt. The MAX20317 exits bypass mode and resets BYPASS to "0." The device also exits bypass mode if an overvoltage condition occurs on  $V_{BOOST}$ .

#### **Power Line Communication**

A one-wire accessory Power-Line-Communication Protocol (PLC) enables communication between a master device and a single accessory device over the microphone power line. The protocol allows the master to configure, control, and read the status of the attached accessory. When the accessory is powered, power line communication takes place over the microphone using biphase mark code (BMC).

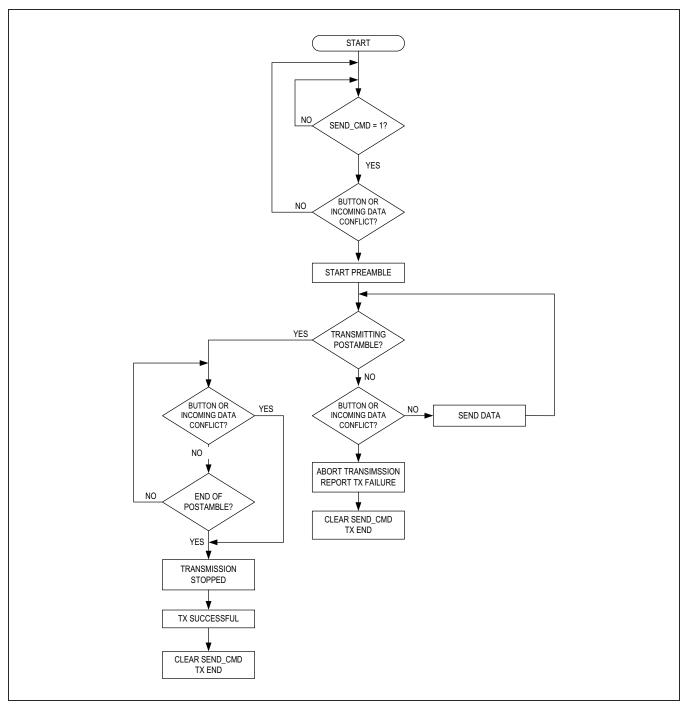

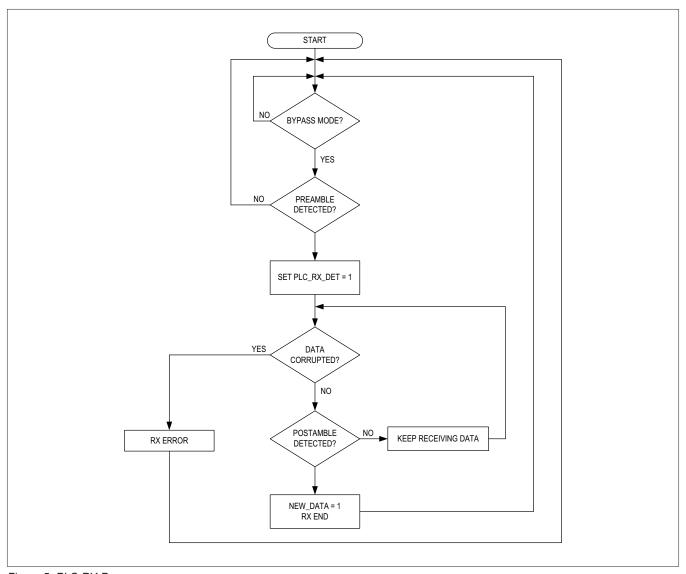

The PLC can be implemented on any single power line between two devices. Error checking, including parity and checksum, is included in the protocol to validate all data transferred between devices. The protocol is defined by a physical layer, which describes the physical communication protocol, and the logical layer that includes high-level commands and handshakes. Figure 4 and Figure 5 show the process of sending and receiving PLC data, respectively. The MAX20317 supports physical data transfer between the master device and slave accessory. The meaning of the data contained in each individual accessory must be defined by the manufacturer of the master device.

#### **SLEEVE and RING2 Ground Sense**

Because audio systems require high levels of isolation between audio channels, the MAX20317 incorporates separate ground sense connections for SLEEVE and RING2. These ground sense contacts provide channel isolation with a Kelvin contact, especially when an EMC filter is included between the 3.5mm jack and the MAX20317. Individual left- and right-channel ground sense outputs provide separate return paths for SLEEVE and RING2.

#### I<sup>2</sup>C Interface

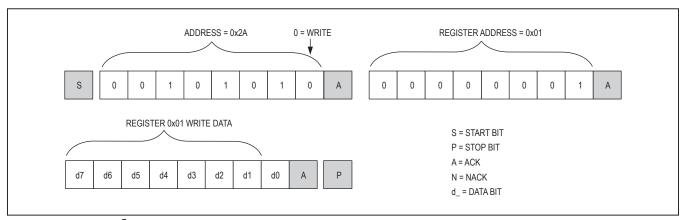

The MAX20317 uses the two-wire  $I^2C$  interface to communicate with a host application processor. The configuration settings and status information provided through this interface are detailed in the register descriptions (<u>Tables 2</u> – <u>31</u>). MAX20317 uses the seven-bit slave address 0b0010101 (0x2A for writes, 0x2B for reads).

Figure 4. PLC TX Process

Figure 5. PLC RX Process

#### **Applications Information**

#### I<sup>2</sup>C Serial Interface

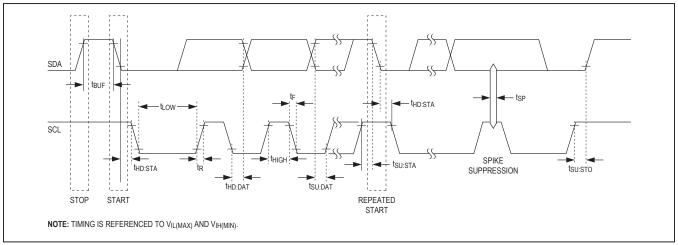

The I $^2$ C serial interface is used to configure the device. Figure 6 shows the I $^2$ C timing diagram.

#### **Serial Addressing**

When in I<sup>2</sup>C mode, the device operates as a slave device that sends and receives data through an I<sup>2</sup>C-compatible 2-wire interface. The interface uses a serial data line (SDA) and a serial-clock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the MAX20317 and generates the SCL clock that synchronizes the data transfer. The SDA line operates as both an input and an open drain output. A pullup resistor is required on

SDA. The SCL line operates only as an input. A pullup resistor is required on SCL if there are multiple masters on the 2-wire interface, or if the master in a single-master system has an open drain SCL output. Each transmission consists of a START condition sent by a master, followed by the MAX20317 7-bit slave address plus R/W bit, a register address byte, one or more data bytes, and finally a STOP condition.

#### **Start and Stop Conditions**

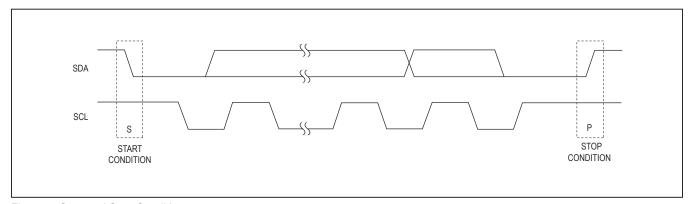

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high (Figure 7). When the master has finished communicating with the slave, it issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission.

Figure 6. I<sup>2</sup>C Timing Diagram

Figure 7. Start and Stop Conditions

#### **Bit Transfer**

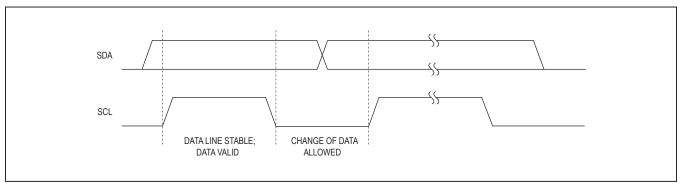

One data bit is transferred during each clock pulse (<u>Figure 8</u>). The data on SDA must remain stable while SCL is high.

#### **Acknowledge**

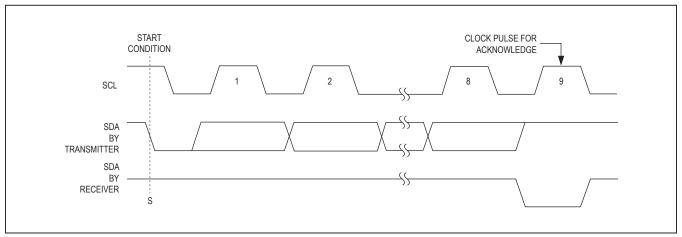

The acknowledge bit is a clocked 9th bit (Figure 9), which the recipient uses to handshake receipt of each byte of data. Thus, each byte transferred effectively requires 9 bits. The master generates the 9th clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse. The SDA line is stable low during the high period of the clock pulse. When the master is transmitting to the MAX20317, it generates the acknowledge bit because the device is the recipient. When the device is transmitting to the master, the master generates the acknowledge bit because the master is the recipient. If the device does not pull SDA low, a not acknowledge is indicated.

#### **Slave Address**

The device has a 7-bit slave address. The bit following a 7-bit slave address is the  $R/\overline{W}$  bit, which is low for a write command and high for a read command. The slave address for the device is 0b00101011 for read commands and 0b00101010 for write commands. This is summarized in Table 1.

Table 1. I<sup>2</sup>C Slave Addresses

| ADDRESS FORMAT      | VAI  | _UE       |

|---------------------|------|-----------|

| ADDRESS FORMAI      | HEX  | BINARY    |

| 7-BIT SLAVE ADDRESS | 0x15 | 001 0101  |

| WRITE ADDRESS       | 0x2A | 0010 1010 |

| READ ADDRESS        | 0x2B | 0010 1011 |

Figure 8. Bit Transfer

Figure 9. Acknowledge

#### **Bus Reset**

The MAX20317 resets the bus with the  $I^2C$  start condition for reads. When the  $R/\overline{W}$  bit is set to 1, the MAX20317 transmits data to the master, thus the master is reading from the device.

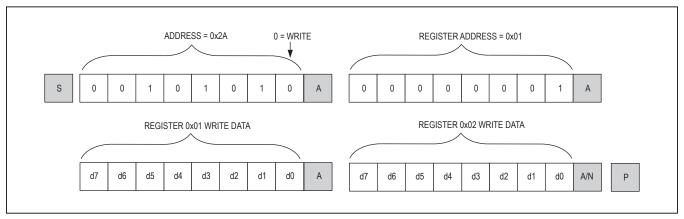

#### **Format for Writing**

A write to the MAX20317 comprises the transmission of the slave address with the  $R/\overline{W}$  bit set to zero, followed by at least 1 byte of information. The first byte of information is the register address or command byte. The register address determines which register of the device is to be written by the next byte, if received. If a STOP (P) condition is detected after the register address is received, then the device takes no further action beyond storing the register address. Any bytes received after the register address are data bytes. The first data byte goes into the register selected by the register address and subsequent

data bytes go into subsequent registers (<u>Figure 10</u>). If multiple data bytes are transmitted before a STOP condition, these bytes are stored in subsequent registers because the register addresses auto-increments (Figure 11).

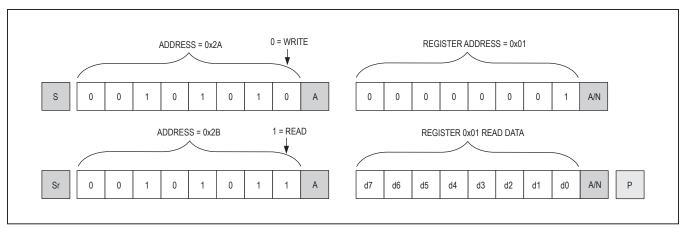

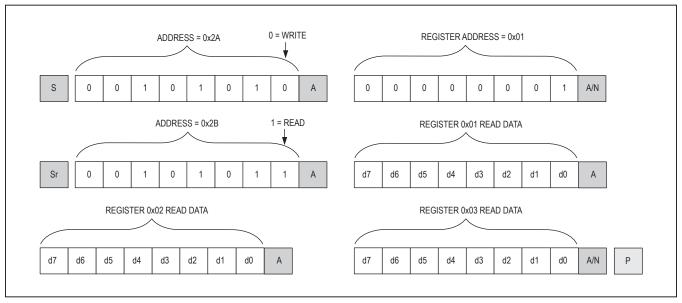

#### Format for Reading

The MAX20317 is read using the internally stored register address as an address pointer, the same way the stored register address is used as an address pointer for a write. The pointer auto-increments after each data byte is read using the same rules as for a write. Thus, a read is initiated by first configuring the register address by performing a write (Figure 12). The master can now read consecutive bytes from the device, with the first data byte being read from the register addressed pointed by the previously written register address (Figure 13). Once the master sends a NACK, the MAX20317 stop sending valid data.

Figure 10. Format for I<sup>2</sup>C Write

Figure 11. Format for Writing to Multiple Registers

Figure 12. Format for Reads (Repeated Start)

Figure 13. Format for Reading Multiple Registers

#### **Power Line Communication**

#### **Physical Structure**

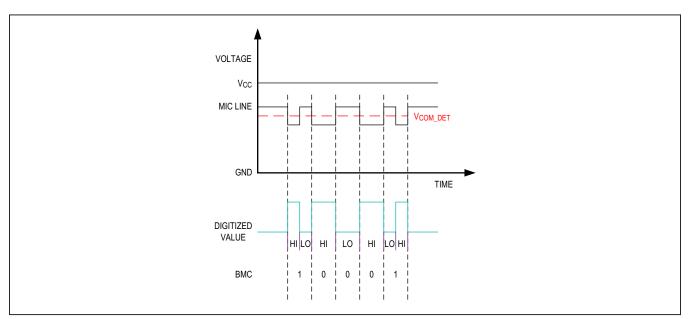

In biphase mark code, high and low bits are defined by state transitions. In the MAX20317, the PLC code comprises a time unit and the low and high states of the MIC line. The time unit,  $t_{UNIT}$  defines the interval of time in which a bit is determined to be either 0 or 1. By default,  $t_{UNIT} = 24\mu s$ , but setting the FREQ bit (0x18[4]) HIGH increases  $t_{UNIT}$  to 30 $\mu s$ . A bit is considered 0 if no MIC state transition occurs during  $t_{UNIT}$ . If there is a state change, either high to low or low to high, the bit is 1.

When the MIC line is above the  $V_{COM\_DET}$  threshold, a low state is recorded. Conversely, a high state is recorded when the MIC line is below the  $V_{COM\_DET}$  threshold. For example, MIC line transitions and their corresponding logic values and BMC bits are shown in Figure 14.

#### **Transmission Format**

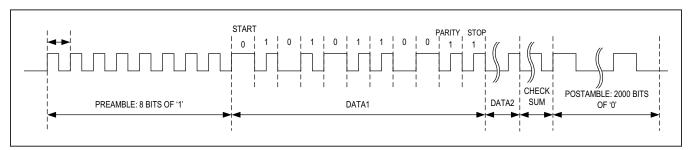

A valid PLC packet comprises a preamble, two data bytes, checksum, and postamble. The preamble is eight consecutive 1 bits. After a successful preamble, data transfer takes place until an error condition occurs or the end of transmission is reached.

Each byte of data begins with a 0 bit to indicate the start condition followed by one byte of data. A parity and stop bit are transmitted at the end of each byte. The stop bit is always 1. If parity is disabled, a parity bit of 1 will be sent, but ignored by the device.

Following the data bytes, a checksum is transmitted. The checksum is generated as NOT(DATA1 + DATA2). Transmission will end with the checksum unless the postamble is enabled. The postamble transmits 0 for a duration of 50ms. A typical data packet is shown in Figure 15.

Figure 14. Determination of PLC Data Bit

Figure 15. Sample PLC Data Packet

# 12C Register Map

| 4       |                  |     | i                | Ğ                    |                    | à                      | 6               | Ğ                | 2                        | Ġ                        |

|---------|------------------|-----|------------------|----------------------|--------------------|------------------------|-----------------|------------------|--------------------------|--------------------------|

| ADDRESS | NAME             | ¥/  | ρ/               | g                    | Bo                 | <b>D</b> 4             | 20              | <b>B</b> 2       | 2                        | PO                       |

| 00X0    | DEVICE_ID        | ~   |                  | CHIP_ID[3:0]         | [D:E]QI            |                        |                 | CHIP_F           | CHIP_REV[3:0]            |                          |

| 0x01    | ADC1_VAL         | R   |                  |                      |                    | ADC1_                  | ADC1_VAL[7:0]   |                  |                          |                          |

| 0x02    | ADC2_VAL         | æ   |                  |                      |                    | ADC2_                  | ADC2_VAL[7:0]   |                  |                          |                          |

| 0x03    | STATUS1          | œ   | IDET_L           | IDET_LVL[1:0]        | COM_DET            | OPEN_<br>CABLE         | JACK_<br>TYPE   | DEVICE_<br>RDY   | E0C1                     | EOC2                     |

| 0x04    | STATUS2          | œ   | VOL_UP           | VOL_<br>DOWN         | VBOOST_<br>OV      | MPSs                   | MIC_IN          | SWD              | DET                      | DETIN                    |

| 0×05    | STATUS3          | Я   | ANC_HS           | THT_CMP              | SAR_CMP            | V94_CMP                | I               | I                | I                        | VOL_RFU                  |

| 90x0    | IRQ              | R/C | SWDi             | EOCi                 | COM_DETi           | MPS/<br>VBOOST_<br>OVi | MIC_INi         | DEVICE_<br>RDYi  | DETI                     | DETINi                   |

| 0x0     | MASK             | R/W | SWDm             | EOCm                 | COM_<br>DETm       | MPS/<br>VBOOST_<br>OVm | MIC_INm         | DEVICE_<br>RDYm  | DETm                     | DETINm                   |

| 0×08    | CONTROL1         | R/W | I                | DEBOUNCE             | DETIN_<br>OVERRIDE | MIC_OUT_<br>DELAY      | I               | BYPASS           | COM_TI                   | COM_THRS[1:0]            |

| 60×0    | CONTROL2         | R/W | MANUAL_<br>G_SNS | MANUAL_<br>MIC_SW    | MANUAL_<br>MG_SW   | OPEN_<br>DETECT        | FORCE_<br>G_SNS | FORCE_<br>MIC_SW | FORCE_M                  | FORCE_MG_SW[1:0]         |

| 0x0A    | ADC_<br>CONTROL1 | R/W | IDET_FLAT        | JACK_TYP_<br>CHK_DIS | I                  | ADC1_<br>L1_CHK        | ADC1_(          | ADC1_CTL[1:0]    | ADC2_(                   | ADC2_CTL[1:0]            |

| 0x0B    | ADC_<br>CONTROL2 | R/W | I                | I                    | SET_ID             | SET_IDET[1:0]          | I               | ADC2_HL          | FORCE_<br>ADC1_<br>START | FORCE_<br>ADC2_<br>START |

| 0×0C    | TIMING           | R/W | ADC1_A           | ADC1_AVG#[1:0]       | ADC2_AVG#[1:0]     | VG#[1:0]               | tANCDET         | tANCDET_DEB[1:0] | tANCBPD                  | tANCBPD_DEB[1:0]         |

|         |                  |     |                  |                      |                    |                        |                 |                  |                          |                          |

# I2C Register Map (continued)

| ı       |                             |     |    |             |                 |                |                |                 |               |                 |

|---------|-----------------------------|-----|----|-------------|-----------------|----------------|----------------|-----------------|---------------|-----------------|

| ADDRESS | NAME                        | R/W | B7 | B6          | B5              | B4             | B3             | B2              | B1            | B0              |

| 0x0D    | SHORT<br>CURRENT<br>CONTROL | R/W |    |             | FU              | FU[5:0]        |                |                 | _O_CHS        | tSHO_DEB[1:0]   |

| 0x0E    | HIHS_VAL                    | R/W |    |             |                 | HIHS           | HIHS_VAL[7:0]  |                 |               |                 |

| 0x0F    | OMTP_VAL                    | R/W |    |             |                 | OMTP           | OMTP_VAL[7:0]  |                 |               |                 |

| 0x10    | HSDET_VAL                   | R/W |    |             |                 | HSDET          | HSDET_VAL[7:0] |                 |               |                 |

| 0x11    | VOL0_TH                     | R/W |    |             |                 | 10/            | VOL0[7:0]      |                 |               |                 |

| 0x12    | VOL1_TH                     | R/W |    |             |                 | IOA            | VOL1[7:0]      |                 |               |                 |

| 0x13    | VOL2_TH                     | R/W |    |             |                 | 10/            | VOL2[7:0]      |                 |               |                 |

| 0x14    | VOL3_TH                     | R/W |    |             |                 | IOA            | VOL3[7:0]      |                 |               |                 |

| 0x15    | PLC_STAT                    | ď   | I  | I           | PLC_<br>TX_ERR  | PLC_<br>TX_OK  | PLC_TXP        | PLC_<br>RX_ERR  | NEW_DATA      | PLC_<br>RX_DET  |

| 0x16    | PLC_IRQ                     | R/C | I  | I           | PLC_<br>TX_ERRi | PLC_<br>TX_OKi | PLC_TXPi       | PLC_<br>RX_ERRi | NEW_DATAi     | PLC_<br>RX_DETI |

| 0x17    | PLC_MASK                    | R/W | I  | I           | PLC_<br>TX_ERRm | PLC_<br>TX_OKm | PLC_TXPm       | PLC_<br>RX_ERRm | NEW_<br>DATAm | PLC_<br>RX_DETm |

| 0x18    | PLC_CON1                    | R/W | I  | PLC_SINK    | POS_<br>AM_DIS  | FREQ           | PARIT          | PARITY[1:0]     | I             | SEND_<br>CMD    |

| 0x19    | ACC_ID                      | œ   |    | ACC_ID[3:0] | D[3:0]          |                |                | ACC_C           | ACC_CAT[3:0]  |                 |

| 0x1A    | ACC_DB1                     | œ   |    |             |                 | ACC            | ACC_DB1[7:0]   |                 |               |                 |

| 0x1B    | ACC_DB2                     | Я   |    |             |                 | ACC_           | ACC_DB2[7:0]   |                 |               |                 |

| 0x1C    | ACC_ADD                     | R/W |    |             |                 | ACC_,          | ACC_ADD[7:0]   |                 |               |                 |

| 0x1D    | ACC_DATA                    | R/W |    |             |                 | ACC_           | ACC_DAT[7:0]   |                 |               |                 |

|         |                             |     |    |             |                 |                |                |                 |               |                 |

# Table 2. DEVICE\_ID Register (0x00)

| ADDRESS           | 0x00                      |                        |                  |          |   |        |          |   |

|-------------------|---------------------------|------------------------|------------------|----------|---|--------|----------|---|

| MODE              | Read Only                 |                        |                  |          |   |        |          |   |

| BIT               | 7                         | 6                      | 5                | 4        | 3 | 2      | 1        | 0 |

| NAME              |                           | CHIP                   | _ID[3:0]         |          |   | CHIP_F | REV[3:0] |   |

| RESET             | 0                         | 0                      | 0                | 1        | 0 | 0      | 0        | 0 |

| CHIP_ID<br>[3:0]  | Chip ID<br>Shows info     | rmation about th       | ne version of M  | AX20317  |   |        |          |   |

| CHIP_REV<br>[3:0] | Chip Revisi<br>Shows info | on<br>rmation about th | ne revision of M | 1AX20317 |   |        |          |   |

# Table 3. ADC1\_VAL Register (0x01)

| ADDRESS           | 0x01                      | 0x01                                                                            |   |   |   |   |   |   |  |  |  |

|-------------------|---------------------------|---------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|--|

| MODE              | Read Only                 | Read Only                                                                       |   |   |   |   |   |   |  |  |  |

| BIT               | 7                         | 6                                                                               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

| NAME              |                           | ADC1_VAL[7:0]                                                                   |   |   |   |   |   |   |  |  |  |

| RESET             | 0                         | 0                                                                               | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| ADC1_VAL<br>[7:0] | ADC1 Value<br>Read only r | ADC1 Value Read only register for the latest ADC1 conversion (8-bit resolution) |   |   |   |   |   |   |  |  |  |

# Table 4. ADC2\_VAL Register (0x02)

| ADDRESS           | 0x02                      | 0x02                                                                            |   |   |   |   |   |   |  |  |

|-------------------|---------------------------|---------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|

| MODE              | Read Only                 | Read Only                                                                       |   |   |   |   |   |   |  |  |

| BIT               | 7                         | 6                                                                               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| NAME              |                           | ADC2_VAL[7:0]                                                                   |   |   |   |   |   |   |  |  |

| RESET             | 0                         | 0                                                                               | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| ADC2_VAL<br>[7:0] | ADC2 Value<br>Read only r | ADC2 Value Read only register for the latest ADC2 conversion (8-bit resolution) |   |   |   |   |   |   |  |  |

# Table 5. STATUS1 Register (0x03)

| ADDRESS           | 0x03                                                                                                                                                                    |                                                                                                                                                                                                                                                                           |         |                |               |                |      |      |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|---------------|----------------|------|------|--|

| MODE              | Read Only                                                                                                                                                               |                                                                                                                                                                                                                                                                           |         |                |               |                |      |      |  |

| BIT               | 7                                                                                                                                                                       | 6                                                                                                                                                                                                                                                                         | 5       | 4              | 3             | 2              | 1    | 0    |  |

| NAME              | IDET_                                                                                                                                                                   | _LVL[1:0]                                                                                                                                                                                                                                                                 | COM_DET | OPEN_<br>CABLE | JACK_<br>TYPE | DEVICE_<br>RDY | EOC1 | EOC2 |  |

| RESET             | 0                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                         | 0       | 0              | 0             | 0              | 0    | 0    |  |

| IDET_LVL<br>[1:0] | Shows the<br>00 = No Ja<br>01 = 100µA<br>10 = 1.1mA                                                                                                                     | I <sub>DETIN</sub> Level Shows the last I <sub>DETIN</sub> current level used in an ADC1 Impedance Detection 00 = No Jack Insertion Default 01 = 100µA 10 = 1.1mA 11 = 5.5mA                                                                                              |         |                |               |                |      |      |  |

| COM_DET           | Indicates a 0 = No com                                                                                                                                                  | Communication Request Status Indicates a valid button press when MIC_IN drops below the threshold set by COM_THRS[1:0] 0 = No communication is requested. 1 = MIC voltage is below threshold after the debounce time.                                                     |         |                |               |                |      |      |  |

| OPEN_<br>CABLE    | Indicates if<br>0 = Cable i                                                                                                                                             | Open Cable Detected Indicates if a cable is an open connection 0 = Cable is not open 1 = High impedance is detected for both CTIA and OMTP, and SET_IDET[1:0] = 01.                                                                                                       |         |                |               |                |      |      |  |

| JACK_<br>TYPE     |                                                                                                                                                                         | ,                                                                                                                                                                                                                                                                         |         |                |               |                |      |      |  |

| DEVICE_<br>RDY    | Indicates the detection if 0 = MIC/GN                                                                                                                                   | Device Ready Indicates the device is ready for manual control after jack detection is complete. This bit is set after impedance detection if JACK_TYP_CHK_DIS = 1.  0 = MIC/GND switch position has NOT been finalized.  1 = MIC/GND SW position is set. Device is ready. |         |                |               |                |      |      |  |

| EOC1              | 0 = ADC1 d                                                                                                                                                              | End of ADC1 conversion 0 = ADC1 conversion is not started or is in progress. 1 = ADC1 conversion is complete and the result is available in ADC1_VAL (register 0x01).                                                                                                     |         |                |               |                |      |      |  |

| EOC2              | End of ADC2 conversion  0 = ADC2 conversion is not started or is in progress.  1 = ADC2 conversion is complete and the result is available in ADC2_VAL (register 0x02). |                                                                                                                                                                                                                                                                           |         |                |               |                |      |      |  |

# Table 6. STATUS2 Register (0x04)

| ADDRESS       | 0x04                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |      |        |     |     |       |  |  |

|---------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|--------|-----|-----|-------|--|--|

| MODE          | Read Only                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |      |        |     |     |       |  |  |

| BIT           | 7                                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5             | 4    | 3      | 2   | 1   | 0     |  |  |

| NAME          | VOL_UP                                                  | VOL_DWN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VBOOST_<br>OV | MPSs | MIC_IN | SWD | DET | DETIN |  |  |

| RESET         | 0                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0             | 0    | 0      | 0   | 0   | 0     |  |  |