### 16-Bit Mono Audio Voice Codec

#### **General Description**

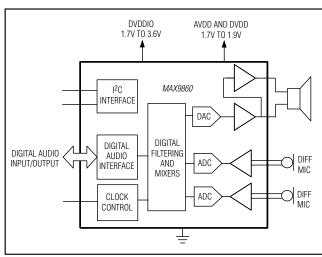

The MAX9860 is a low-power, voiceband, mono audio codec designed to provide a complete audio solution for wireless voice headsets and other mono voice audio devices. Using an on-chip bridge-tied load mono headphone amplifier, the MAX9860 can output 30mW into a  $32\Omega$  earpiece while operating from a single 1.8V power supply. Very low power consumption makes it an ideal choice for battery-powered applications.

The MAX9860's flexible clocking circuitry utilizes common system clock frequencies ranging from 10MHz to 60MHz, eliminating the need for an external PLL and multiple crystal oscillators. Both the ADC and DAC support sample rates of 8kHz to 48kHz in either synchronous or asynchronous operation. Both master and slave timing modes are supported.

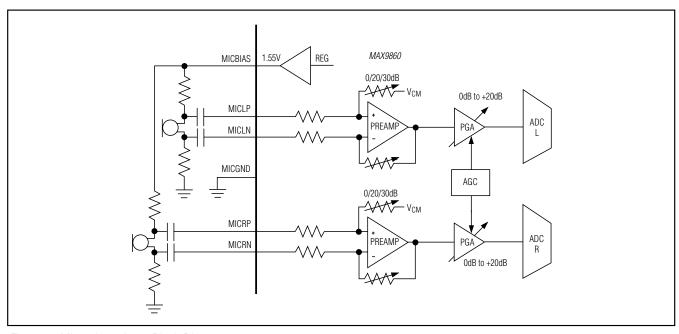

Two differential microphone inputs are available with a user-programmable preamplifier and programmable gain amplifier. Automatic gain control with selectable attack/release times and signal threshold allows maximum dynamic range. A noise gate with selectable threshold provides a means to quiet the channel when no signal is present. Both the DAC and ADC digital filters provide full attenuation for out-of-band signals as well as a 5th order GSM-compliant digital highpass filter. A digital side tone mixer provides loopback of the microphones/ADC signal to the DAC/headphone output.

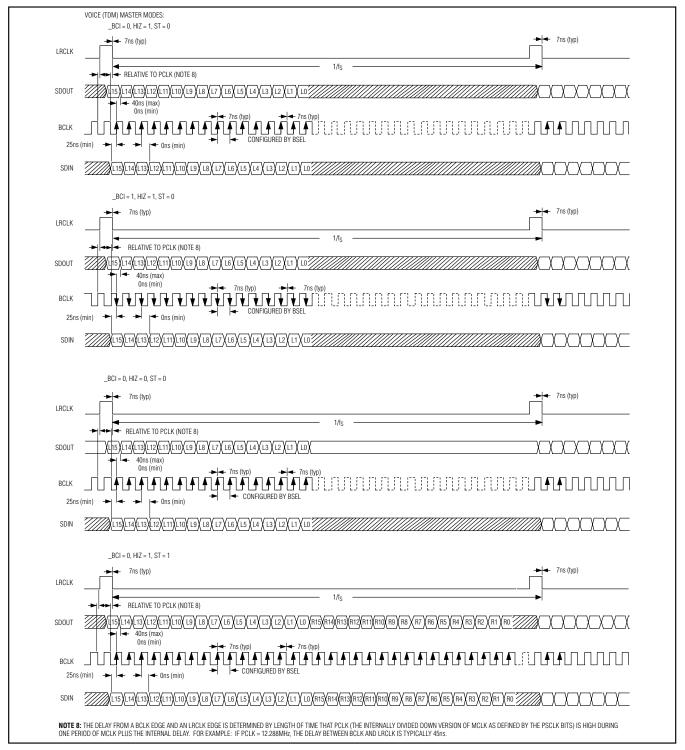

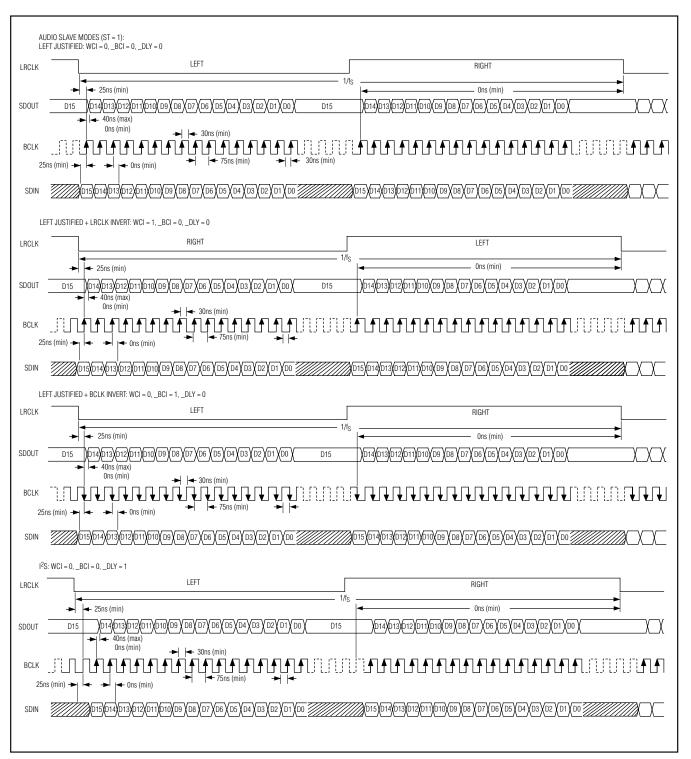

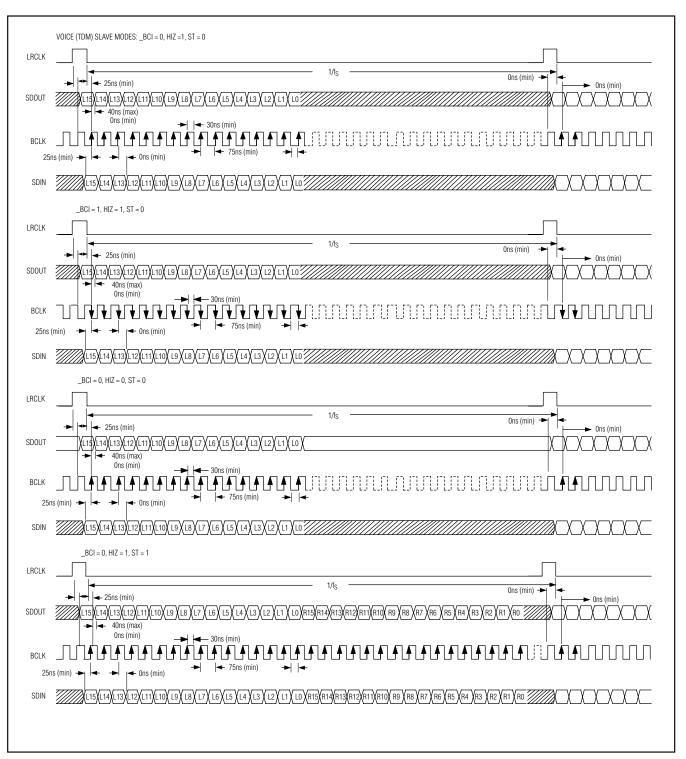

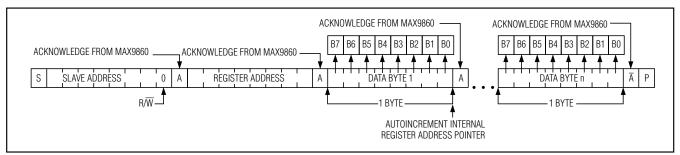

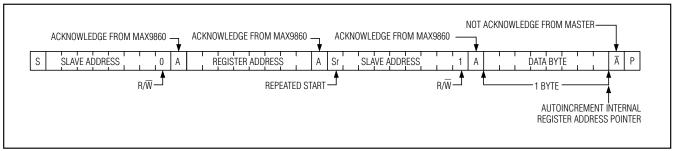

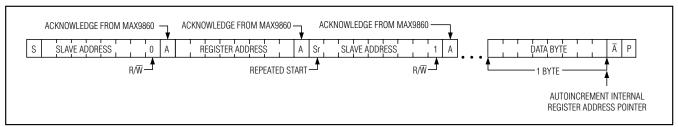

Serial DAC and ADC data is transferred over a flexible digital I<sup>2</sup>S-compatible interface that also supports TDM mode. Mode settings, volume control, and shutdown are programmed through a 2-wire, I<sup>2</sup>C-compatible interface.

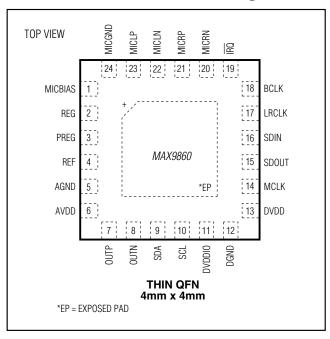

The MAX9860 is fully specified over the -40 $^{\circ}$ C to +85 $^{\circ}$ C extended temperature range and is available in a low-profile, 4mm x 4mm, 24-pin thin QFN package.

#### **Applications**

**Audio Headsets**

Portable Navigation Device

Mobile Phones

**Smart Phones**

**VoIP Phones**

**Audio Accessories**

Pin Configuration and Typical Operating Circuit appear at end of data sheet.

#### Features

- ♦ 1.8V Single-Supply Operation

- Digital Highpass Elliptical Filters with Notch for 217Hz (GSM)

- ♦ Mono 30mW BTL Headphone Amplifier

- **♦ Dual Low-Noise Microphone Inputs**

- ◆ Automatic Microphone Gain Control and Noise Gate

- ♦ 90dB DAC DR (fs = 48kHz)

- ♦ 81dB ADC DR (fs = 48kHz)

- ♦ Supports Master Clock Frequencies from 10MHz to 60MHz

- ♦ Supports Sample Rates from 8kHz to 48kHz

- ♦ Flexible Digital Audio Interface

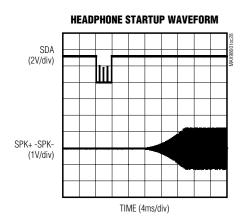

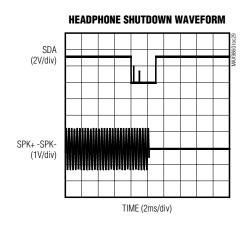

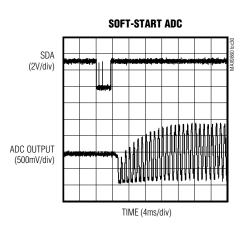

- ♦ Clickless/Popless Operation

- ♦ 2-Wire, I2C-Compatible Control Interface

- ♦ Available in 24-Pin, Thin QFN, 4mm x 4mm x 0.8mm Package

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX9860ETG+ | -40°C to +85°C | 24 TQFN-EP* |

<sup>+</sup>Denotes a lead-free/RoHS-compliant package.

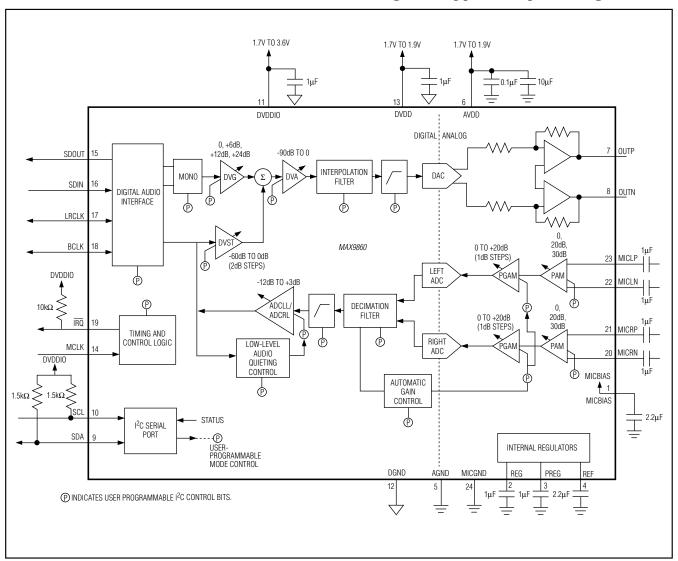

#### Simplified Block Diagram

<sup>\*</sup>EP = Exposed pad.

## 16-Bit Mono Audio Voice Codec

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to AGND.)                        | ( |

|-------------------------------------------------------|---|

| DVDDIO, SDA, SCL, IRQ0.3V to +3.6V                    |   |

| AVDD, DVDD0.3V to +2V                                 |   |

| AGND, DGND, MICGND0.3V to +0.3V                       | ( |

| OUTP, OUTN, PREG, REF, MICBIAS0.3V to (VAVDD + 0.3V)  | ; |

| MICLP, MICLN, MICRP, MICRN, REG0.3V to (VPREG + 0.3V) | , |

| MCLK, LRCLK, BCLK,                                    | 1 |

| SDOUT, SDIN0.3V to (V <sub>DVDDIO</sub> + 0.3V)       | , |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| 24-Pin TQFN (derate 27.8mW/°C above +                 | -70°C,         |

| multilayer board)                                     | 2222mW         |

| Operating Temperature Range                           | 40°C to +85°C  |

| Storage Temperature Range                             | 65°C to +150°C |

| Junction Temperature                                  | +150°C         |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL CHARACTERISTICS (Note 1)

**TQFN**

Junction-to-Ambient Thermal Resistance ( $\theta$ JA)......36°C/W Junction-to-Case Thermal Resistance ( $\theta$ JC)......3°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty$ , headphone load  $(R_L)$  connected between OUTP and OUTN,  $C_{REF} = 2.2\mu F$ ,  $C_{MICBIAS} = C_{PREG} = C_{REG} = 1\mu F$ ,  $A_{VPRE} = +20dB$ ,  $A_{VMICPGA} = 0dB$ ,  $f_{MCLK} = 13MHz$ ,  $f_{LRCLK} = 8kHz$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                         | SYMBOL                  | CONDITIO                                                      | NS               | MIN  | TYP  | MAX | UNITS            |

|-----------------------------------|-------------------------|---------------------------------------------------------------|------------------|------|------|-----|------------------|

|                                   |                         | AVDD (inferred from HP o                                      | utput PSRR)      | 1.7  | 1.8  | 1.9 |                  |

| Supply Voltage Range              |                         | DVDD (inferred from code tests)                               | c performance    | 1.7  | 1.8  | 1.9 | V                |

|                                   |                         | DVDDIO                                                        |                  | 1.7  | 1.8  | 3.6 |                  |

|                                   |                         | DAC playback mode                                             | AVDD             |      | 1.46 | 2.2 |                  |

|                                   |                         | (48kHz)                                                       | DVDD             |      | 1.05 | 1.6 |                  |

|                                   |                         | Full operation                                                | AVDD             |      | 4.08 | 5.7 |                  |

| Total Supply Current              |                         | 8kHz mono ADC + DAC                                           | DVDD             |      | 0.78 | 1.0 | A                |

| (Note 3)                          | IAVDD+DVDD              | Full operation                                                | AVDD             |      | 6.17 | 9.0 | mA               |

|                                   |                         | 8kHz stereo ADC + DAC                                         | DVDD             |      | 0.8  | 1.2 |                  |

|                                   | Stereo ADC only (48kHz) | AVDD                                                          |                  | 5.38 | 8.0  | ]   |                  |

|                                   |                         | Stereo ADC only (48KHZ)                                       | DVDD             |      | 1.68 | 2.2 | ]                |

|                                   |                         |                                                               | AVDD             |      | 0.56 | 5   |                  |

| Shutdown Supply Current           | ISHDN                   | T <sub>A</sub> = +25°C                                        | DVDD +<br>DVDDIO |      | 1.65 | 5   | μA               |

| Shutdown to Full Operation        |                         |                                                               |                  |      | 10   |     | ms               |

| DAC (Note 4)                      |                         |                                                               |                  | ı    |      |     | •                |

| Gain Error                        |                         |                                                               |                  |      | ±1   | ±5  | %                |

| Dynamic Range (Note 5)            | DR                      | +0dB volume setting, $f_S = 8$ at headphone output, $T_A = 8$ |                  | 84   | 90   |     | dB               |

| DAC Full-Scale Output             |                         |                                                               |                  |      | 1    |     | V <sub>RMS</sub> |

| DAC Path Phase Delay              |                         | f = 1kHz, 0dBFS, HP<br>filter disabled, digital               | fs = 8kHz        |      | 1.2  |     | ms               |

| Dito Fatti Hado Bolay             |                         | input to analog output                                        | fs = 16kHz       |      | 0.59 |     | 1110             |

| Total Harmonic Distortion + Noise | THD+N                   | $f = 1kHz$ , $f_{MCLK} = 12.288N$<br>$f_{LRCLK} = 48kHz$      | MHz,             |      | -87  |     | dB               |

## **16-Bit Mono Audio Voice Codec**

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, \ R_L = \infty, \ headphone \ load \ (R_L) \ connected \ between OUTP \ and OUTN, \ C_{REF} = 2.2 \mu F, \ C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, \ A_{VPRE} = +20 dB, \ A_{VMICPGA} = 0 dB, \ f_{MCLK} = 13 MHz, \ f_{LRCLK} = 8 kHz, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. Typical values are at T_A = +25 °C.) (Note 2)$

| PARAMETER                                                                                          | SYMBOL              | CONDITIONS                                                                  | MIN TYP MAX                | UNITS            |  |

|----------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------|----------------------------|------------------|--|

| Dower Cumply Dejection Detic                                                                       | PSRR                | $f = 1kHz$ , $V_{RIPPLE} = 100mV_{P-P}$ , $A_{VPGA} = 0dB$                  | 94                         | - dB             |  |

| Power-Supply Rejection Ratio                                                                       | PONN                | $f = 10kHz$ , $V_{RIPPLE} = 100mV_{P-P}$ , $A_{VPGA} = 0dB$                 | 71                         | ив               |  |

| DAC LOWPASS DIGITAL FILTER                                                                         |                     |                                                                             |                            |                  |  |

| Passband Cutoff                                                                                    | fpLp                | With respect to fs within ripple; fs = 8kHz to 48kHz                        | 0.448 x<br>fs              | Hz               |  |

|                                                                                                    |                     | -3dB cutoff                                                                 | 0.451                      | fs               |  |

| Passband Ripple                                                                                    |                     | f < fplp                                                                    | ±0.1                       | dB               |  |

| Stopband Cutoff                                                                                    | f <sub>SLP</sub>    | With respect to fs; fs = 8kHz to 48kHz                                      | 0.476 x<br>fs              | Hz               |  |

| Stopband Attenuation                                                                               |                     | $f > f_{SLP}, f = 20Hz to 20kHz$                                            | 75                         | dB               |  |

| DAC HIGHPASS DIGITAL FILTER                                                                        | ₹                   |                                                                             |                            |                  |  |

|                                                                                                    |                     | DVFLT = 0x1<br>(elliptical for 16kHz GSM)                                   | 0.0161<br>x fs             |                  |  |

|                                                                                                    | fDHPPB              | DVFLT = 0x2<br>(500Hz Butterworth for 16kHz)                                | 0.0312<br>x fs             | Hz               |  |

| 5th Order Passband Cutoff<br>(-3dB from Peak, I <sup>2</sup> C Register<br>Programmable) (Note 6)  |                     | DVFLT = 0x3<br>(elliptical for 8kHz GSM)                                    | 0.0321<br>x f <sub>S</sub> |                  |  |

| rrogrammable) (Note 6)                                                                             |                     | DVFLT = 0x4<br>(500Hz Butterworth for 8kHz)                                 | 0.0625<br>x f <sub>S</sub> |                  |  |

|                                                                                                    |                     | DVFLT = 0x5<br>(200Hz Butterworth for 48kHz)                                | 0.0042<br>x f <sub>S</sub> |                  |  |

|                                                                                                    |                     | DVFLT = 0x1<br>(elliptical for 16kHz GSM)                                   | 0.0139<br>x f <sub>S</sub> |                  |  |

|                                                                                                    |                     | DVFLT = 0x2<br>(500Hz Butterworth for 16kHz)                                | 0.0156<br>x f <sub>S</sub> |                  |  |

| 5th Order Stopband Cutoff<br>(-30dB from Peak, I <sup>2</sup> C Register<br>Programmable) (Note 6) | fDHPSB              | DVFLT = 0x3<br>(elliptical for 8kHz GSM)                                    | 0.0279<br>x fs             | Hz               |  |

| Trogrammable) (Note o)                                                                             |                     | DVFLT = 0x4<br>(500Hz Butterworth for 8kHz)                                 | 0.0312<br>x f <sub>S</sub> |                  |  |

|                                                                                                    |                     | DVFLT = 0x5<br>(200Hz Butterworth for 48kHz)                                | 0.0021<br>x fg             |                  |  |

| DC Blocking                                                                                        | DC <sub>Atten</sub> | DVFLT ≠ 0x0                                                                 | 90                         | dB               |  |

| ADC                                                                                                | •                   |                                                                             | •                          | •                |  |

| Full-Scale Input Voltage                                                                           | 0dBFS               | Differential MIC Input, A <sub>VPRE</sub> = 0dB,<br>A <sub>VPGA</sub> = 0dB |                            | V <sub>P-P</sub> |  |

| Channel Gain Mismatch                                                                              |                     |                                                                             | ±0.3                       | %                |  |

## **16-Bit Mono Audio Voice Codec**

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDDIO} = V_{DVDDIO} = +1.8V, \ R_L = \infty, \ headphone \ load \ (R_L) \ connected \ between \ OUTP \ and \ OUTN, \ C_{REF} = 2.2 \mu F, \ C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, \ A_{VPRE} = +20 dB, \ A_{VMICPGA} = 0 dB, \ f_{MCLK} = 13 MHz, \ f_{LRCLK} = 8 kHz, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted.$  Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                                                         | SYMBOL           | CONDITION                                                                          | S                      | MIN           | TYP                        | MAX | UNITS |

|---------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------|------------------------|---------------|----------------------------|-----|-------|

| Dynamic Range (Note 5)                                                                            | DR               | fs = 8kHz, A <sub>VPRE</sub> = 0dB,<br>A-weighted from 20Hz to fs/2                |                        |               | 81                         |     | dB    |

|                                                                                                   |                  | $f_S = 48kHz$ , $A_{VPRE} = 0dB$ , 1                                               | A = +25°C              | 75            | 83                         |     |       |

| ADO Diseas Delevi                                                                                 |                  | f = 1kHz, 0dBFS, HP filter                                                         | $f_S = 8kHz$           |               | 1.2                        |     |       |

| ADC Phase Delay                                                                                   |                  | disabled, analog input to digital output                                           | f <sub>S</sub> = 16kHz |               | 0.61                       |     | ms    |

| Total Harmonic Distortion                                                                         | THD              | $f = 1kHz$ , $f_S = 48kHz$ , $T_A =$                                               | +25°C                  | -70           | -75                        |     | dB    |

| Dayyar Cupply Paigation Patia                                                                     | PSRR             | f = 1kHz, V <sub>RIPPLE</sub> = 100mV<br>A <sub>VPGA</sub> = 0dB                   | P-P,                   |               | 82                         |     | dB    |

| Power-Supply Rejection Ratio                                                                      | PORR             | f = 10kHz, V <sub>RIPPLE</sub> = 100mV <sub>P-P</sub> ,<br>A <sub>VPGA</sub> = 0dB |                        | 76            |                            |     | uБ    |

| Channel Crosstalk                                                                                 |                  | Driven channel at -1dBFS,                                                          | f = 1kHz               |               | -92                        |     | dB    |

| ADC LOWPASS DIGITAL FILTER                                                                        |                  |                                                                                    |                        |               |                            |     |       |

| Passband Cutoff                                                                                   | fpLp             | With respect to fs within ripple;<br>fs = 8kHz to 48kHz                            |                        | (             | 0.445 x<br>f <sub>S</sub>  |     | Hz    |

|                                                                                                   |                  | -3dB cutoff                                                                        |                        |               | 0.449                      |     | fs    |

| Passband Ripple                                                                                   |                  | f < fpLP                                                                           |                        |               | ±0.1                       |     | dB    |

| Stopband Cutoff                                                                                   | f <sub>SLP</sub> | With respect to fs; fs = 8kH                                                       | z to 48kHz             |               | 0.469 x<br>f <sub>S</sub>  |     | Hz    |

| Stopband Attenuation                                                                              |                  | f > f <sub>SLP</sub>                                                               |                        |               | 74                         |     | dB    |

| ADC HIGHPASS DIGITAL FILTER                                                                       | 1                |                                                                                    |                        |               |                            |     |       |

|                                                                                                   |                  | AVFLT = 0x1 (elliptical for                                                        | 16kHz GSM)             | (             | 0.0161<br>x f <sub>S</sub> |     |       |

| 5th Order Passband Cutoff<br>(-3dB from Peak, I <sup>2</sup> C Register<br>Programmable) (Note 6) |                  | AVFLT = 0x2 (500Hz Butterworth for 16kHz)                                          |                        | 0.031<br>x fs | 0.0312<br>x f <sub>S</sub> |     |       |

|                                                                                                   | fahppb           | AVFLT = 0x3 (elliptical for 8kHz GSM)                                              |                        | (             | 0.0321<br>x f <sub>S</sub> |     | Hz    |

|                                                                                                   |                  | AVFLT = 0x4<br>(500Hz Butterworth for 8kHz)                                        |                        | (             | 0.0625<br>x f <sub>S</sub> |     |       |

|                                                                                                   |                  | AVFLT = 0x5<br>(200Hz Butterworth for 48k                                          | Hz)                    | (             | 0.0042<br>x f <sub>S</sub> |     |       |

## **16-Bit Mono Audio Voice Codec**

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, \ R_L = \infty, \ headphone \ load \ (R_L) \ connected \ between OUTP \ and OUTN, \ C_{REF} = 2.2 \mu F, \ C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, \ A_{VPRE} = +20 dB, \ A_{VMICPGA} = 0 dB, \ f_{MCLK} = 13 MHz, \ f_{LRCLK} = 8 kHz, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. Typical values are at T_A = +25 °C.) (Note 2)$

| PARAMETER                                                                                          | SYMBOL  | CONDITION                                              | NS                 | MIN | TYP                        | MAX   | UNITS           |

|----------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------|--------------------|-----|----------------------------|-------|-----------------|

|                                                                                                    |         | AVFLT = 0x1<br>(elliptical for 16kHz GSM)              |                    |     | 0.0139<br>x f <sub>S</sub> |       |                 |

|                                                                                                    |         | AVFLT = 0x2<br>(500Hz Butterworth for 16k              | «Hz)               |     | 0.0156<br>x f <sub>S</sub> |       |                 |

| 5th Order Stopband Cutoff<br>(-30dB from peak, I <sup>2</sup> C Register<br>Programmable) (Note 6) | fAHPSB  | AVFLT = 0x3<br>(elliptical for 8kHz GSM)               |                    |     | 0.0279<br>x f <sub>S</sub> |       | Hz              |

| Tregrammable) (Note 0)                                                                             |         | AVFLT = 0x4<br>(500Hz Butterworth for 8kh              | Hz)                |     | 0.0312<br>x f <sub>S</sub> |       |                 |

|                                                                                                    |         | AVFLT = 0x5<br>(200Hz Butterworth for 48k              | (Hz)               |     | 0.0021<br>x fs             |       |                 |

| DC Blocking                                                                                        | DCATTEN | AVFLT ≠ 0x0                                            |                    |     | 90                         |       | dB              |

| CLOCKING                                                                                           |         |                                                        |                    |     |                            |       |                 |

| MCLK Input Frequency                                                                               |         | MCLK is not required to be or related to the desired L |                    | 10  |                            | 60    | MHz             |

| MCLK Duty Cycle                                                                                    |         |                                                        |                    | 40  | 50                         | 60    | %               |

| Maximum MCLK Input Jitter                                                                          |         | For guaranteed performan                               | ice limits         |     | 100                        |       | psrms           |

| LRCLK Data Rate Frequency                                                                          |         |                                                        |                    | 8   |                            | 48    | kHz             |

| LRCLK PLL Lock Time                                                                                |         |                                                        |                    |     | 12                         | 25    | ms              |

| LRCLK Acceptable Jitter for Maintaining PLL Lock                                                   |         |                                                        |                    |     | ±20                        |       | ns              |

| MONO HEADPHONE AMPLIFIER                                                                           |         | 1                                                      |                    | I.  |                            |       |                 |

| Output Power                                                                                       | Роит    | f = 1kHz, THD+N ≤ 1%                                   | $R_L = 16\Omega$   | 30  | 50                         |       | mW              |

| Output Fower                                                                                       | FOUI    | $T_A = +25$ °C                                         | $R_L = 32\Omega$   |     | 33                         |       | IIIVV           |

| Total Harmonic Distortion + Noise                                                                  | THD+N   | $R_L = 32\Omega$ , $P_{OUT} = 25$ mW,                  | f = 1kHz           |     | 0.05                       |       | %               |

| Total Haiffioriic Distortion + Noise                                                               | IIID+N  | $R_L = 16\Omega$ , $P_{OUT} = 25$ mW,                  | f = 1kHz           |     | 0.08                       |       | /0              |

| Dynamic Range (Note 5)                                                                             | DR      | +0dB volume setting, DAC<br>fs = 8kHz to 48kHz         | Cinput at          |     | 90                         |       | dB              |

|                                                                                                    |         | $V_{AVDD} = 1.7V \text{ to } 1.9V$                     |                    | 60  | 84                         |       |                 |

| Power-Supply Rejection Ratio                                                                       | PSRR    | $V_{RIPPLE} = 100 \text{mV}_{P-P}, f = 2$              | .17Hz              |     | 86                         |       | dB              |

|                                                                                                    |         | VRIPPLE = 100mVp-p, f = 20kHz                          |                    |     | 71                         |       | 1               |

| Output Offset Voltage                                                                              | Vos     | Voutp - Voutn, TA =+25°0                               | C                  |     |                            | ± 3.5 | mV              |

| Canaditiva Driva Canadility                                                                        |         | No quatained agaillations                              | $R_L = 32\Omega$   |     | 500                        |       | ۵۲              |

| Capacitive Drive Capability                                                                        |         | No sustained oscillations                              | R <sub>L</sub> = ∞ |     | 100                        |       | <del>i</del> pF |

| Click-and-Pop Level                                                                                |         | Peak voltage into/out of sh<br>A-weighted              | utdown, 32sps,     |     | -70                        |       | dBV             |

## **16-Bit Mono Audio Voice Codec**

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, \ R_L = \infty, \ headphone \ load \ (R_L) \ connected \ between \ OUTP \ and \ OUTN, \ C_{REF} = 2.2\mu F, \ C_{MICBIAS} = C_{PREG} = C_{REG} = 1\mu F, \ A_{VPRE} = +20dB, \ A_{VMICPGA} = 0dB, \ f_{MCLK} = 13MHz, \ f_{LRCLK} = 8kHz, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. Typical values are at T_A = +25°C.) (Note 2)$

| PARAMETER                         | SYMBOL                                               | CONDITION                                                       | IS             | MIN   | TYP  | MAX  | UNITS             |

|-----------------------------------|------------------------------------------------------|-----------------------------------------------------------------|----------------|-------|------|------|-------------------|

| MICROPHONE AMPLIFIER              |                                                      | 1                                                               |                | •     |      |      | •                 |

|                                   |                                                      |                                                                 | PAM = 00       |       | Off  |      |                   |

| December 11 Control               | ۸                                                    | T 0500                                                          | PAM = 01       | -0.5  | 0    | +0.5 | -10               |

| Preamplifier Gain                 | AVPRE                                                | $T_A = +25^{\circ}C$                                            | PAM = 10       | 19    | 20   | 21   | dB                |

|                                   |                                                      |                                                                 | PAM = 11       | 29    | 30   | 31   |                   |

| MIC PGA Gain                      | A. a. u.o.o.o. a                                     | PGAM = 0x14-0x1F                                                |                |       | 0    |      | ٩D                |

| MIC PGA Gain                      | Avmicpga                                             | PGAM = 0x00                                                     |                |       | +20  |      | dB                |

| MIC PGA Gain Step Size            |                                                      |                                                                 |                |       | 1    |      | dB                |

| Common-Mode Rejection Ratio       | CMRR                                                 | $V_{IN} = 100 \text{mV}_{P-P} \text{ at } 217 \text{Hz}$        |                |       | 50   |      | dB                |

| MIC Input Resistance              | R <sub>IN_MIC</sub>                                  | All gain settings, measured MICLN/MICRN                         | d at           | 30    | 50   |      | kΩ                |

| MIC Input Bias Voltage            |                                                      |                                                                 |                | 0.7   | 0.8  | 0.9  | V                 |

| Total Harmonic Distortion + Noise | TUD. N                                               | AVPRE = 0dB, AVMICPGA = VIN = 1VP-P, f = 1kHz                   | OdB,           |       | -75  |      | dB                |

| Total Harmonic Distortion + Noise | THD+N                                                | AVPRE = +30dB, AVMICPGA<br>VIN = 31mV <sub>P-P</sub> , f = 1kHz | 4 = 0dB,       |       | -66  |      | dB                |

| 1410.5                            |                                                      | V <sub>AVDD</sub> = 1.7V to 1.9V                                |                | 60    | 95   |      | dB                |

| MIC Power-Supply Rejection        | PSRR                                                 | VRIPPLE = 100mV at 1kHz,                                        | input referred |       | 82   |      | dB                |

| Ratio                             | V <sub>RIPPLE</sub> = 100mV at 10kHz, input referred |                                                                 |                | 76    |      | dB   |                   |

| MICROPHONE BIAS                   |                                                      |                                                                 |                |       |      |      |                   |

| MICBIAS Output Voltage            | VMICBIAS                                             | $I_{LOAD} = 1$ mA, $T_A = +25$ °C                               |                | 1.5   | 1.55 | 1.6  | V                 |

| Load Regulation                   |                                                      | $I_{LOAD} = 1mA \text{ to } 2mA$                                |                |       | 0.2  | 10   | mV                |

| MICBIAS Line Ripple Rejection     | LRR                                                  | VRIPPLE = 100mVp-p at 217                                       | 7Hz            |       | 82   |      | dB                |

| MICBIAS LINE HIPPIE NEJECTION     | LIIII                                                | VRIPPLE = 100mVp-p at 10k                                       | кНz            |       | 81   |      | dB                |

| MICBIAS Noise Voltage             |                                                      | A-weighted                                                      |                |       | 9.5  |      | μV <sub>RMS</sub> |

| AUTOMATIC GAIN CONTROL            |                                                      |                                                                 |                |       |      |      |                   |

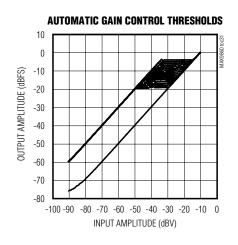

| AGC Hold Duration                 |                                                      | AGCHLD[1:0] setting rang                                        | e, FREQ ≠ 0    | 50    |      | 400  | ms                |

| AGC Attack Time                   |                                                      | AGCATK[1:0] setting range                                       | e, FREQ ≠ 0    | 3     |      | 200  | ms                |

| AGC Release Time                  |                                                      | AGCRLS[2:0] setting range                                       | e, FREQ ≠ 0    | 0.078 |      | 10   | S                 |

| AGC Threshold Level               |                                                      | AGCSTH[3:0] setting range, FREQ ≠ 0                             |                | -3    |      | -18  | dB                |

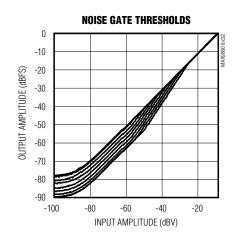

| NOISE GATE                        |                                                      |                                                                 |                |       |      |      |                   |

| NG Attack and Release Time        |                                                      |                                                                 |                |       | 0.5  |      | S                 |

| NG Threshold Level                |                                                      |                                                                 |                | -72   |      | -16  | dB                |

| Noise Gate Threshold Step Size    |                                                      |                                                                 |                |       | 4    |      | dB                |

| NG Attenuation                    |                                                      |                                                                 |                | 0     |      | 12   | dB                |

| DIGITAL SIDETONE                  |                                                      |                                                                 |                |       |      |      |                   |

| Sidetone Gain Adjust              | DVST                                                 | 2dB steps                                                       |                | -60   |      | 0    | dB                |

| Sidetone Phase Delay              | PDLY                                                 | MIC input to headphone output, f = 1kHz, HP filter              | 8kHz           |       | 2.2  |      | ms                |

|                                   |                                                      | disabled                                                        | 16kHz          |       | 1.1  |      |                   |

## **16-Bit Mono Audio Voice Codec**

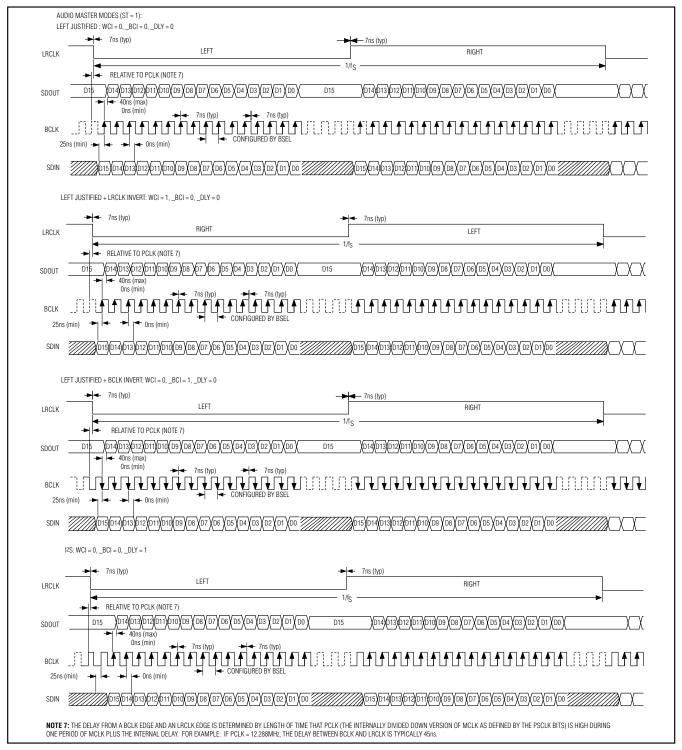

#### **DIGITAL AUDIO INTERFACE ELECTRICAL CHARACTERISTICS**

(V<sub>DVDD</sub> = V<sub>DVDDIO</sub> = 1.8V, unless otherwise noted.) (Note 2)

| PARAMETER                                   | SYMBOL                          | CONDITIONS                             | MIN | TYP | MAX | UNITS |

|---------------------------------------------|---------------------------------|----------------------------------------|-----|-----|-----|-------|

| BCLK Cycle Time                             | tBCLKS                          | Slave operation                        | 75  |     |     | ns    |

| BCLK High Time                              | tBCLKH                          | Slave operation                        | 30  |     |     | ns    |

| BCLK Low Time                               | tBCLKL                          | Slave operation                        | 30  |     |     | ns    |

| BCLK or LRCLK Rise and Fall Time            | t <sub>R</sub> , t <sub>F</sub> | Master operation                       | 7   |     | ns  |       |

| SDIN or LRCLK to BCLK Rising Setup Time     | tsu                             | ABCI = DBCI = 0                        | 25  |     |     | ns    |

| SDIN or LRCLK to BCLK Falling<br>Setup Time | tsu                             | ABCI = DBCI = 1                        | 25  |     |     | ns    |

| SDIN or LRCLK to BCLK Rising<br>Hold Time   | tHD                             | ABCI = DBCI = 0                        | 0   |     |     | ns    |

| SDIN or LRCLK to BCLK Falling<br>Hold Time  | tHD                             | ABCI = DBCI = 1                        | 0   |     |     | ns    |

| SDOUT Delay Time from BCLK<br>Rising Edge   | t <sub>DLY</sub>                | ABCI = DBCI = 0, C <sub>L</sub> = 30pF | 0   |     | 40  | ns    |

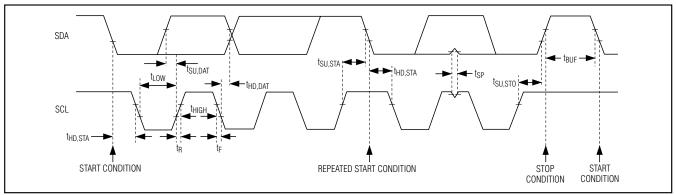

#### I<sup>2</sup>C INTERFACE ELECTRICAL CHARACTERISTICS

(V<sub>DVDD</sub> = V<sub>DVDDIO</sub> = 1.8V, unless otherwise noted.) (Note 2)

| PARAMETER                                       | SYMBOL         | CONDITIONS              | MIN      | TYP | MAX | UNITS |

|-------------------------------------------------|----------------|-------------------------|----------|-----|-----|-------|

| Serial-Clock Frequency                          | fscl           |                         | 0        |     | 400 | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF           |                         | 1.3      |     |     | μs    |

| Hold Time (Repeated) START<br>Condition         | thd,sta        |                         | 0.6      |     |     | μs    |

| SCL Pulse Width Low                             | tLOW           |                         | 1.3      |     |     | μs    |

| SCL Pulse Width High                            | thigh          |                         | 0.6      |     |     | μs    |

| Setup Time for a Repeated START Condition       | tsu,sta        |                         | 0.6      |     |     | μs    |

| Data Hold Time                                  | thd,dat        |                         | 0        |     | 900 | ns    |

| Data Setup Time                                 | tsu,dat        |                         | 100      |     |     | ns    |

| SDA and SCL Receiving<br>Rise Time              | t <sub>R</sub> | C <sub>B</sub> is in pF | 20 + 0.1 | Св  | 300 | ns    |

| SDA and SCL Receiving<br>Fall Time              | tF             | C <sub>B</sub> is in pF | 20 + 0.1 | СВ  | 300 | ns    |

## 16-Bit Mono Audio Voice Codec

#### I<sup>2</sup>C INTERFACE ELECTRICAL CHARACTERISTICS (continued)

$(V_{DVDD} = V_{DVDDIO} = 1.8V$ , unless otherwise noted.) (Note 2)

| PARAMETER                       | SYMBOL                            | CONDITIONS                                                      | MIN                           | ГҮР МАХ                      | UNITS |

|---------------------------------|-----------------------------------|-----------------------------------------------------------------|-------------------------------|------------------------------|-------|

| SDA Transmitting<br>Fall Time   | tF                                | C <sub>B</sub> is in pF                                         | 20 + 0.1C <sub>B</sub>        | 250                          | ns    |

| Setup Time for STOP Condition   | tsu,sto                           |                                                                 | 0.6                           |                              | μs    |

| Bus Capacitance                 | CB                                |                                                                 |                               | 400                          | рF    |

| Pulse Width of Suppressed Spike | tsp                               |                                                                 | 0                             | 50                           | ns    |

| DIGITAL INPUTS (LRCLK, BCLK     | K, SDIN, MCLI                     | <b>(</b> )                                                      |                               |                              |       |

| Input Voltage High              | VIH                               |                                                                 | 0.7<br>x V <sub>D</sub> VDDIO |                              | V     |

| Input Voltage Low               | V <sub>IL</sub>                   |                                                                 |                               | 0.3<br>x V <sub>DVDDIO</sub> | V     |

| MCLK Input Voltage High         |                                   |                                                                 | 1.4                           |                              | V     |

| MCLK Input Voltage Low          |                                   |                                                                 |                               | 0.4                          | V     |

| Input Leakage Current           | I <sub>IH</sub> , I <sub>IL</sub> | $T_A = +25^{\circ}C$                                            | -1                            | +1                           | μΑ    |

| Input Capacitance               |                                   |                                                                 |                               | 3                            | рF    |

| DIGITAL INPUTS (SCL, SDA)       |                                   |                                                                 |                               |                              |       |

| Input Voltage High              | VIH                               |                                                                 | 0.7<br>x V <sub>DVDD</sub>    |                              | V     |

| Input Voltage Low               | VIL                               |                                                                 |                               | 0.3<br>x V <sub>DVDD</sub>   | V     |

| Input Hysteresis                |                                   |                                                                 |                               | 200                          | mV    |

| Input Leakage Current           | I <sub>IH</sub> , I <sub>IL</sub> | $T_A = +25^{\circ}C$                                            | -1                            | +1                           | μΑ    |

| Input Capacitance               |                                   |                                                                 |                               | 3                            | рF    |

| CMOS DIGITAL OUTPUTS (BCL       | K, LRCLK, SI                      | DOUT)                                                           |                               |                              |       |

| Output Low Voltage              | V <sub>OL</sub>                   | I <sub>OL</sub> = 3mA                                           |                               | 0.4                          | V     |

| Output High Voltage             | VoH                               | I <sub>OL</sub> = 3mA                                           | V <sub>D</sub> VDDIO<br>- 0.4 |                              | V     |

| OPEN-DRAIN DIGITAL OUTPUT       | S (SDA, IRQ)                      |                                                                 | •                             |                              |       |

| Output High Leakage Current     | Іон                               | V <sub>OUT</sub> = V <sub>DVDDIO</sub> , T <sub>A</sub> = +25°C | -1                            | +1                           | μΑ    |

| Output Low Voltage              | V <sub>OL</sub>                   | I <sub>OL</sub> = 3mA                                           |                               | 0.4                          | V     |

- Note 2: All devices are 100% production tested at room temperature. All temperature limits are guaranteed by design.

- **Note 3:** Supply current measurements taken with no applied signal at microphone inputs. A digital zero audio signal used for all digital serial audio inputs. Headphone outputs are loaded as stated in the global conditions.

- Note 4: DAC performance is measured at headphone outputs.

- Note 5: ADC, DAC, and headphone amplifier dynamic ranges are measured using the EIAJ method. -60dBV 1kHz input signal, A-weighted and normalized to 0dBFS.

- Note 6: Notch for GSM filters occurs at 217Hz.

### 16-Bit Mono Audio Voice Codec

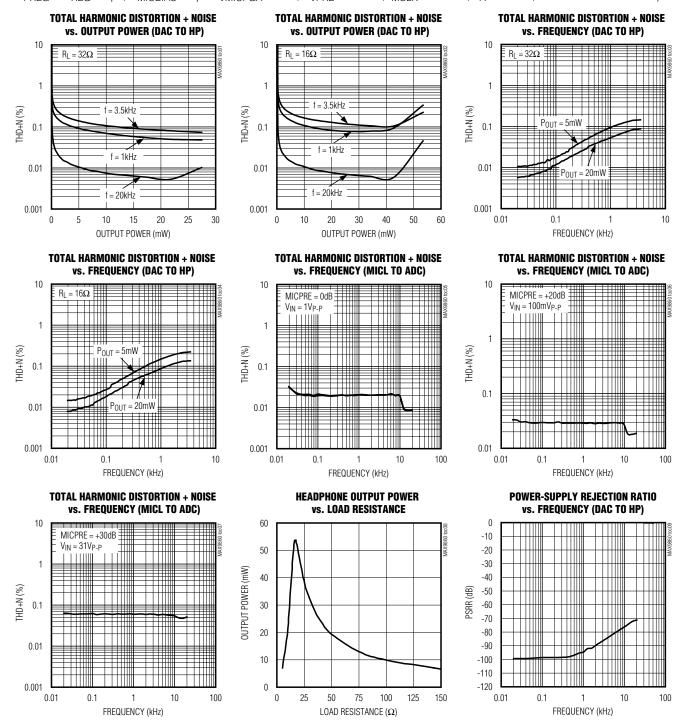

### **Typical Operating Characteristics**

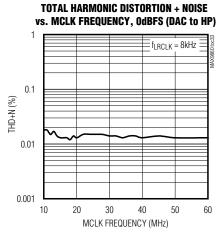

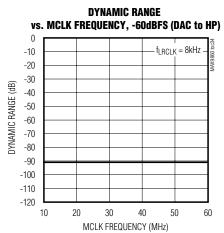

$(V_{AVDD} = +1.8V, V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty$ , headphone load  $(R_L)$  connected between OUTP and OUTN,  $C_{REF} = 2.2\mu F$ ,  $C_{PREG} = C_{REG} = 1\mu F$ ,  $C_{MICBIAS} = 1\mu F$  Avmicpga = 0dB,  $A_{VPRE} = +20dB$ ,  $f_{MCLK} = 13MHz$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

## 16-Bit Mono Audio Voice Codec

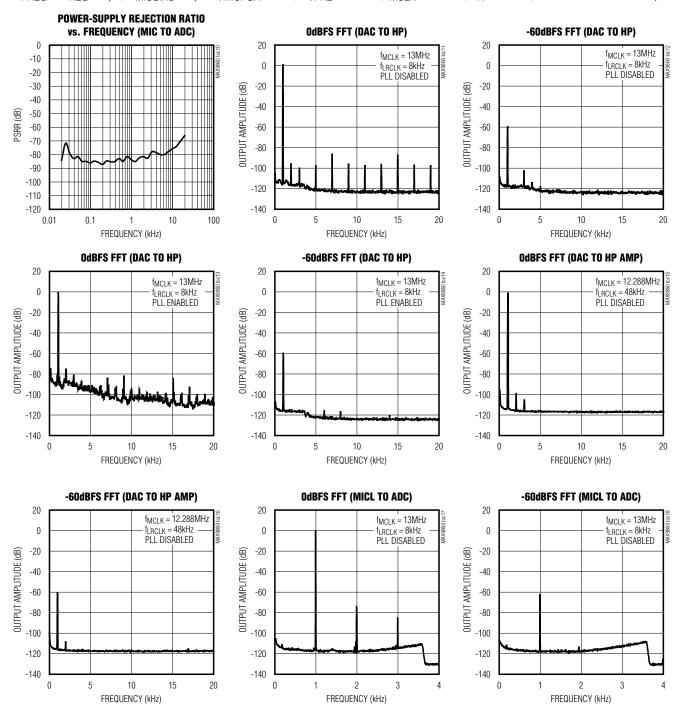

### Typical Operating Characteristics (continued)

$(V_{AVDD} = +1.8V, V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty$ , headphone load  $(R_L)$  connected between OUTP and OUTN,  $C_{REF} = 2.2\mu F$ ,  $C_{PREG} = C_{REG} = 1\mu F$ ,  $C_{MICBIAS} = 1\mu F$  Avmicpga = 0dB,  $A_{VPRE} = +20dB$ ,  $f_{MCLK} = 13MHz$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

## **16-Bit Mono Audio Voice Codec**

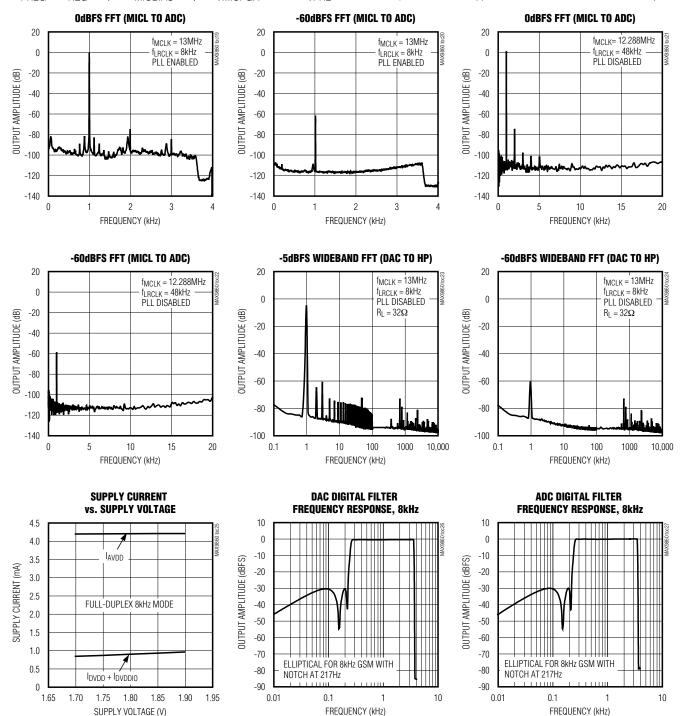

### Typical Operating Characteristics (continued)

$(V_{AVDD} = +1.8V, V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty, headphone load (R_L) connected between OUTP and OUTN, C_{REF} = 2.2 \mu F, C_{PREG} = C_{REG} = 1 \mu F, C_{MICBIAS} = 1 \mu F A_{VMICPGA} = 0 dB, A_{VPRE} = +20 dB, f_{MCLK} = 13 MHz, T_A = +25 °C, unless otherwise noted.)$

## **16-Bit Mono Audio Voice Codec**

### Typical Operating Characteristics (continued)

$(V_{AVDD} = +1.8V, V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty$ , headphone load  $(R_L)$  connected between OUTP and OUTN,  $C_{REF} = 2.2\mu F$ ,  $C_{PREG} = C_{REG} = 1\mu F$ ,  $C_{MICBIAS} = 1\mu F$  Avmicpga = 0dB,  $A_{VPRE} = +20dB$ ,  $f_{MCLK} = 13MHz$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

## 16-Bit Mono Audio Voice Codec

## **Pin Description**

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                         |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | MICBIAS | Microphone Bias. +1.55V microphone bias for internal and/or external microphone. An external resistor from $2.2k\Omega$ to $470\Omega$ should be used to set the microphone current. Bypass to MICGND with a $1\mu$ F capacitor. |

| 2   | REG     | Internal Bias. PREG/2 voltage reference. Bypass to AGND with a 1µF capacitor (+0.8V).                                                                                                                                            |

| 3   | PREG    | Positive Internal Regulated Supply. Bypass to AGND with a 1µF capacitor (+1.6V).                                                                                                                                                 |

| 4   | REF     | Converter Reference (1.23V). Bypass to AGND with a 2.2µF capacitor.                                                                                                                                                              |

| 5   | AGND    | Analog Ground                                                                                                                                                                                                                    |

| 6   | AVDD    | Analog Power Supply. Bypass to AGND with 10µF and 0.1µF capacitors.                                                                                                                                                              |

| 7   | OUTP    | Positive Headphone Output                                                                                                                                                                                                        |

| 8   | OUTN    | Negative Headphone Output                                                                                                                                                                                                        |

| 9   | SDA     | I <sup>2</sup> C Serial-Data Input/Output                                                                                                                                                                                        |

| 10  | SCL     | I <sup>2</sup> C Serial-Data Clock                                                                                                                                                                                               |

| 11  | DVDDIO  | Digital Interface Power Supply. Supply for digital audio interface. Bypass to DGND with a 1µF capacitor.                                                                                                                         |

| 12  | DGND    | Digital Ground                                                                                                                                                                                                                   |

| 13  | DVDD    | Digital Core Power Supply. Bypass to DGND with a 1µF capacitor.                                                                                                                                                                  |

| 14  | MCLK    | Master Clock Input                                                                                                                                                                                                               |

| 15  | SDOUT   | Serial Audio Interface ADC Data Output                                                                                                                                                                                           |

| 16  | SDIN    | Serial Audio Interface DAC Data Input                                                                                                                                                                                            |

| 17  | LRCLK   | Serial Audio Interface Left/Right Clock                                                                                                                                                                                          |

| 18  | BCLK    | Serial Audio Interface Bit Clock                                                                                                                                                                                                 |

| 19  | ĪRQ     | Interrupt Request. $\overline{\text{IRQ}}$ is an active-low open drain output. Pull up to DVDDIO with a $10k\Omega$ resistor.                                                                                                    |

| 20  | MICRN   | Negative Right Microphone Input. AC-couple to low-side of microphone or connect to negative signal. AC-couple to ground for single-ended operation.                                                                              |

| 21  | MICRP   | Positive Right Microphone Input. AC-couple to high-side of microphone or connect to positive signal. AC-couple the signal for single-ended operation.                                                                            |

| 22  | MICLN   | Negative Left Microphone Input. AC-couple to low-side of microphone or connect to negative signal. AC-couple to ground for single-ended operation.                                                                               |

| 23  | MICLP   | Positive Left Microphone Input. AC-couple to high-side of microphone or connect to positive signal. AC-couple the signal for single-ended operation.                                                                             |

| 24  | MICGND  | MICBIAS Ground. Connect to AGND.                                                                                                                                                                                                 |

| _   | EP      | Exposed Pad. Connect to AGND.                                                                                                                                                                                                    |

## 16-Bit Mono Audio Voice Codec

#### **Detailed Description**

The MAX9860 low-power, voiceband, mono audio codec provides a complete audio solution for wireless voice headsets and other mono audio devices.

The mono playback path accepts digital audio over a flexible digital audio interface compatible with I<sup>2</sup>S, TDM, and left-justified audio signals. An oversampling sigmadelta DAC converts an incoming digital data stream to analog audio and outputs through the mono bridge-tied load headphone amplifier.

The stereo record path has two microphone inputs with selectable gain. The microphones are powered by an integrated microphone bias. An oversampling sigmadelta ADC converts the microphone signals and outputs the digital bit stream over the digital audio interface.

The record path includes automatic gain control (AGC) to optimize the signal level and a noise gate to reduce idle noise. The automatic gain control monitors the outputs of the ADC and makes constant adjustments to the input gain to reduce the dynamic range of the incoming microphone signal by up to 20dB. The noise gate corrects for the increase in noise typically associated with AGC by lowering the gain when there is no audio signal.

Integrated digital filtering provides a range of notch and highpass filters for both the playback and record paths

to limit undesirable low-frequency signals and GSM transmission noise. The digital filtering provides attenuation of out-of-band energy by up to 76dB, eliminating audible aliasing. A digital sidetone function allows audio from the record path to be summed into the playback path after digital filtering.

The MAX9860's flexible clock circuitry utilizes a programmable clock divider and a digital PLL to allow the DAC and ADC to operate at maximum dynamic range for all combinations of master clock (MCLK) and sample rate (LRCLK). Any master clock between 10MHz to 60MHz is supported as are all sample rates from 8kHz to 48kHz. Master and slave mode are supported for maximum flexibility.

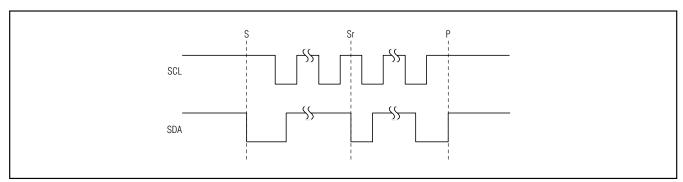

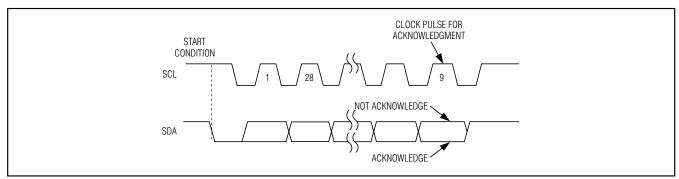

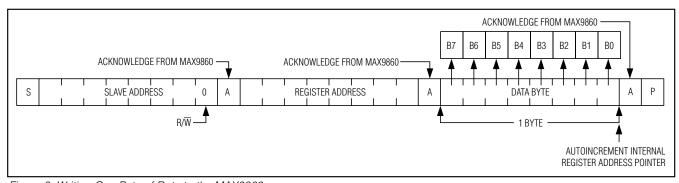

#### **I<sup>2</sup>C** Registers

The MAX9860 audio codec is completely controlled through software using an I<sup>2</sup>C interface. The power-on default setting is software shutdown, requiring that the internal registers be programmed to activate the device. See Table 1 for the device's complete register map.

#### I<sup>2</sup>C Slave Address

The MAX9860 responds to the slave address 0x20 for all write commands and 0x21 for all read operations.

## **16-Bit Mono Audio Voice Codec**

Table 1. I<sup>2</sup>C Register Map

| REGISTER                           | В7    | В6        | В5   | В4   | В3    | B2            | В    | 1    | В0     | REGISTER<br>ADDRESS | POR  | R/W |

|------------------------------------|-------|-----------|------|------|-------|---------------|------|------|--------|---------------------|------|-----|

| STATUS/INTERRUPT                   |       |           | l l  |      |       |               |      |      |        | <u> </u>            |      |     |

| Interrupt Status                   | CLD   | SLD       | ULK  | 0    | 0     | 0             | С    | )    | 0      | 0x00                |      | R   |

| Microphone NG/AGC<br>Readback      |       | NG        |      |      |       | AG            | С    |      |        | 0x01                | _    | R   |

| Interrupt Enable                   | ICLD  | ISLD      | IULK | 0    | 0     | 0             | C    | )    | 0      | 0x02                | 0x00 | R/W |

| CLOCK CONTROL                      |       |           |      |      | •     |               | •    |      |        |                     |      |     |

| System Clock                       | 0     | 0         | PSC  | CLK  | 0     | FI            | REQ  |      | 16KHZ  | 0x03                | 0x00 | R/W |

| Stereo Audio Clock<br>Control High | PLL   |           |      |      | NHI   |               |      |      |        | 0x04                | 0x00 | R/W |

| Stereo Audio Clock<br>Control Low  |       |           |      |      | NLO   |               |      |      |        | 0x05                | 0x00 | R/W |

| DIGITAL AUDIO INTE                 | RFACE |           |      |      |       |               |      |      |        |                     |      |     |

| Interface                          | MAS   | WCI       | DBCI | DDLY | HIZ   | TD            | M    | 0    | 0      | 0x06                | 0x00 | R/W |

| Interface                          | 0     | 0         | ABCI | ADLY | ' ST  |               | ·    | BSE  |        | 0x07                | 0x00 | R/W |

| DIGITAL FILTERING                  |       |           |      |      |       |               |      |      |        |                     |      |     |

| Voice Filter                       |       | A۱        | /FLT |      |       | DVFLT         |      |      |        | 0x08                | 0x00 | R/W |

| DIGITAL LEVEL CON                  | TROL  |           |      |      |       |               |      |      |        |                     |      |     |

| DAC Attenuation                    |       |           |      |      | DVA   |               |      |      |        | 0x09                | 0x00 | R/W |

| ADC Output Levels                  |       | AE        | CRL  |      |       | ADCLL         |      |      | 0x0A   | 0x00                | R/W  |     |

| DAC Gain and Sidetone              | 0     |           | DVG  |      |       | DVST          |      |      | 0x0B   | 0x00                | R/W  |     |

| MICROPHONE LEVEL                   |       | OL        |      |      |       |               |      |      |        | 1                   |      |     |

| Microphone Gain                    | 0     |           | PAM  |      |       | PG            | AM   |      |        | 0x0C                | 0x00 | R/W |

| RESERVED                           | ı     | <u> </u>  | -    |      |       |               |      |      |        | 1                   |      |     |

| Reserved                           | 0     | 0         |      | 0    | 0     | 0             | )    | 0    | 0      | 0x0D                | 0x   | 00  |

| MICROPHONE AUTO                    |       |           |      |      |       |               |      | 1    |        | T                   |      |     |

| Microphone AGC                     | AGCSR | RC AGCRLS |      |      | A     | AGCATK AGCHLD |      | 0x0E | 0x00   | R/W                 |      |     |

| Noise Gate,<br>Microphone AGC      |       | ANTH      |      |      |       | ,             | AGCT | H    |        | 0x0F                | 0x00 | R/W |

| POWER MANAGEME                     | NT    |           |      |      |       |               |      |      |        |                     |      |     |

| System Shutdown                    | SHDN  | 0         | 0    | 0    | DACEN | I 0           | ADC  | LEN  | ADCREN | 0x10                | 0x00 | R/W |

## **16-Bit Mono Audio Voice Codec**

#### Status/Interrupt

Status registers 0x00 and 0x01 are read-only registers that report the status of various device functions. The status register bits are cleared upon a read operation of the status register and are set the next time the event occurs. Register 0x02 determines whether or not the status flags in register 0x00 simultaneously sets  $\overline{IRQ}$  high.

**Table 2. Status/Interrupt Registers**

| REGISTER ADDRESS | B7   | В6   | B5   | B4  | В3 | B2 | B1 | В0 |

|------------------|------|------|------|-----|----|----|----|----|

| 0x00             | CLD  | SLD  | ULK  | 0   | 0  | 0  | 0  | 0  |

| 0x01             |      | NG   |      | AGC |    |    |    |    |

| 0x02             | ICLD | ISLD | IULK | 0   | 0  | 0  | 0  | 0  |

| BITS | FUNCTION                                                                                                                                                                                                                                                      |             |  |  |  |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|--|

| CLD  | Clip Detect Flag. Indicates that a signal has become clipped in the ADC or DAC digital signal paths. CLD also indicates that the AGC function, when enabled, has set the microphone PGA to 0dB and no further gain reduction is possible.                     |             |  |  |  |  |  |  |

| SLD  | Slew Level Detect Flag. When volume or gain changes are made, the slewing circuitry smoothly steps through all intermediate settings. When SLD is set high, all slewing has completed and the volume or gain is at its final value.                           |             |  |  |  |  |  |  |

| ULK  | Digital PLL Unlock Flag. Indicates that the digital audio PLL for the ADC or DAC has become unlocked and digital signal data is not reliable. When beginning operation in master mode, this flag goes high and can be cleared by reading the status register. |             |  |  |  |  |  |  |

|      | Noise Gate Attenuation. When the noise gate is enabled these bits indicate the current noise gate attenuation.                                                                                                                                                |             |  |  |  |  |  |  |

|      | Code                                                                                                                                                                                                                                                          | Attenuation |  |  |  |  |  |  |

|      | 000                                                                                                                                                                                                                                                           | 0dB         |  |  |  |  |  |  |

|      | 001                                                                                                                                                                                                                                                           | 1dB         |  |  |  |  |  |  |

| NG   | 010                                                                                                                                                                                                                                                           | 2dB         |  |  |  |  |  |  |

| NG   | 011                                                                                                                                                                                                                                                           | 3dB         |  |  |  |  |  |  |

|      | 100                                                                                                                                                                                                                                                           | 6dB         |  |  |  |  |  |  |

|      | 101                                                                                                                                                                                                                                                           | 8dB         |  |  |  |  |  |  |

|      | 110                                                                                                                                                                                                                                                           | 10dB        |  |  |  |  |  |  |

|      | 111 12dB                                                                                                                                                                                                                                                      |             |  |  |  |  |  |  |

| AGC  | AGC Gain. When the AGC is enabled these bits indicate the AGC of indicated by these bits correspond to the levels defined for the PGA                                                                                                                         |             |  |  |  |  |  |  |

## 16-Bit Mono Audio Voice Codec

#### **Clock Control**

The MAX9860 can work with a master clock (MCLK) supplied from any system clock within the range of 10MHz to 60MHz. Internally, the MAX9860 requires a 10MHz to 20MHz clock so a prescaler divides by 1, 2, or 4 to create the internal clock (PCLK). PCLK is used to clock all portions of the MAX9860.

The MAX9860 is capable of supporting any sample rate from 8kHz to 48kHz, including all common sample rates (8kHz, 16kHz, 24kHz, 32kHz, 44.1kHz, 48kHz). To accommodate a wide range of system architectures, the MAX9860 supports three main clocking modes:

**Normal Mode:** This mode uses a 15-bit clock divider coefficient to set the sample rate relative to the

prescaled MCLK input (PCLK). This allows high flexibility in both the MCLK and LRCLK frequencies and can be used in either master or slave mode.

**Exact Integer Mode:** Common MCLK frequencies (12MHz, 13MHz, and 19.2MHz) can be programmed to operate in exact integer mode for both 8kHz and 16kHz sample rates. In these modes, the MCLK and LRCLK rates are selected by using the FREQ and 16KHZ bits instead of the NHI, NLO, and PLL control bits.

**PLL Mode:** When operating in slave mode, a PLL can be enabled to lock onto externally generated LRCLK signals that are asynchronously related to PCLK.

Table 3. Clock Control Registers

| REGISTER ADDRESS | B7  | В6      | B5 | B4 | В3 | B2   | B1 | В0    |

|------------------|-----|---------|----|----|----|------|----|-------|

| 0x03             | 0   | 0 PSCLK |    |    | 0  | FREQ |    | 16KHZ |

| 0x04             | PLL | NHI     |    |    |    |      |    |       |

| 0x05             |     |         |    | NI | _O |      |    |       |

| BITS       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | MCLK Prescaler Divides MCLK down to generate a PCLK between 10MHz and 20MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PSCLK[1:0] | 00 = Disable clock for low-power shutdown. 01 = Select if MCLK is between 10MHz and 20MHz. 10 = Select if MCLK is between 20MHz and 40MHz. 11 = Select if MCLK is greater than 40MHz.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FREQ[1:0]  | Integer Clock Mode Enables exact integer mode for three predefined PCLK frequencies. Exact integer mode is normally intended for master mode, but can be enabled in slave mode if the externally supplied LRCLK exactly matches the frequency specified in each mode.  00 = Normal operation (configure clocking with the PLL, NHI, and NLO bits). 01 = Select when PCLK is 12MHz (LRCLK = PCLK/1500 or PCLK/750). 10 = Select when PCLK is 13MHz (LRCLK = PCLK/1625 or PCLK/812.5). 11 = Select when PCLK is 19.2MHz (LRCLK = PCLK/2400 or PCLK/1200).  When FREQ ≠ 00, the PLL, NHI, and NLO bits are unused. |

| 16KHZ      | 16kHz Mode  When FREQ ≠ 00:  0 = LRCLK is exactly 8kHz.  1 = LRCLK is exactly 16kHz.  When FREQ = 00, 16KHZ is used to set the AGC clock rate:  0 = Use when LRCLK ≤ 24kHz.  1 = Use when LRCLK > 24kHz.                                                                                                                                                                                                                                                                                                                                                                                                        |

## **16-Bit Mono Audio Voice Codec**

**Table 3. Clock Control Registers (continued)**