# GC4016 MULTI-STANDARD QUAD DDC CHIP

# **Data Manual**

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Literature Number: SLWS133B August 2001 – Revised July 2009 SLWS133B-AUGUST 2001-REVISED JULY 2009

# **Contents**

| 1 | Introd | uction    |                                                     | 7         |

|---|--------|-----------|-----------------------------------------------------|-----------|

|   | 1.1    | Features  |                                                     | Z         |

|   | 1.1.1  | Block Dia | agram                                               | <u>8</u>  |

|   | 1.2    | Functiona | al Description                                      | 9         |

|   | 1.2.1  |           | nterface                                            | _         |

|   | 1.2.2  | •         | mat                                                 |           |

|   | 1.2.3  | The Dow   | nconverters                                         | <u>12</u> |

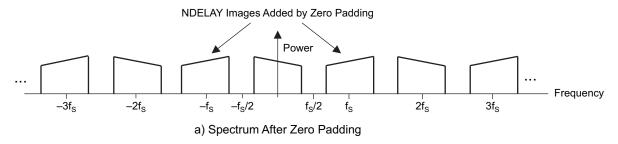

|   |        |           | Zero-Padding                                        |           |

|   |        |           | The Numerically Controlled Oscillator (NCO)         |           |

|   |        |           | Five-Stage CIC Filter                               |           |

|   |        |           | Coarse Channel Gain                                 |           |

|   |        |           | The First Decimate-by-Two Filter (CFIR)             |           |

|   |        |           | The Second Decimate-by-Two Filter (PFIR)            |           |

|   |        |           | Complex-to-Real Mode                                |           |

|   | 1.2.4  |           | nnel Modes                                          |           |

|   |        |           | Double-Bandwidth Downconverter Mode (Splitl/Q Mode) |           |

|   |        |           | Wideband Downconvert Mode                           |           |

|   |        |           | Complex Input, Narrowband Output                    |           |

|   |        |           | Complex-Input, Double-Bandwidth (SplitI/Q) Mode     |           |

|   |        |           | Multichannel Summary                                |           |

|   | 1.2.5  | -         | er                                                  |           |

|   |        |           | Functional Description                              |           |

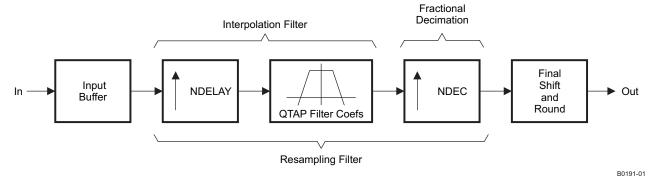

|   |        |           | The Resampler Filter                                |           |

|   |        |           | Restrictions on NMULT                               |           |

|   |        |           | The Resampler Clock Divider                         | _         |

|   |        |           | Final Shift and Round                               |           |

|   |        |           | Bypassing the Resampler                             |           |

|   |        |           | Adaptive Ratio Change                               |           |

|   |        |           | Gain                                                |           |

|   |        |           | unter                                               |           |

|   | 1.2.8  | •         | lodes                                               |           |

|   |        |           | Microprocessor Mode                                 |           |

|   |        |           | Wide-Word Microprocessor Mode                       |           |

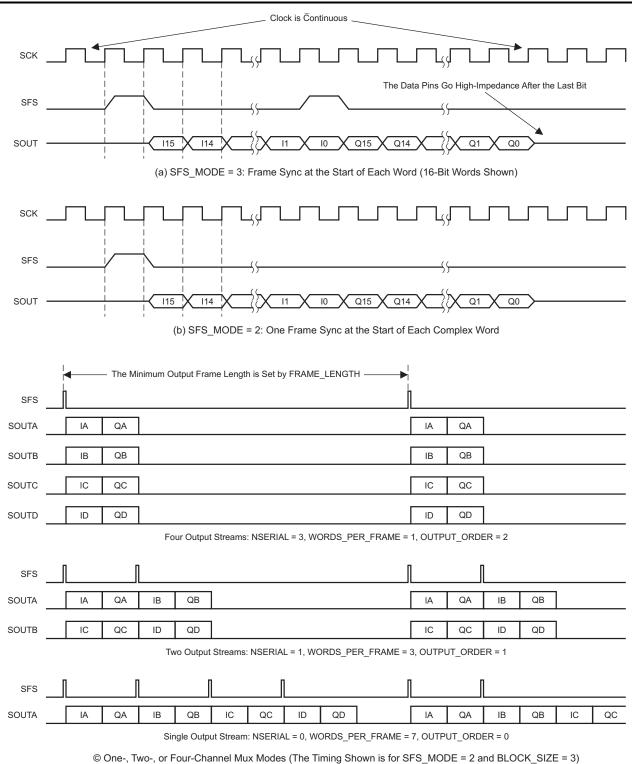

|   |        |           | Synchronous Serial Outputs                          |           |

|   |        |           | Asynchronous Serial Outputs                         |           |

|   |        |           | Nibble-Mode Output                                  |           |

|   |        |           | Link-Mode Output                                    |           |

|   | 4.0.0  |           | Parallel-Mode Output                                |           |

|   |        | J         | Name Mada                                           |           |

|   |        |           | Down Modes                                          | _         |

|   |        | •         | onization                                           |           |

|   | 1.2.12 |           | tion                                                |           |

|   |        |           | Initializing Multiple GC4016 Chips                  |           |

|   | 4 0 40 |           | Initializing Stand-Alone GC4016 Chips               |           |

|   |        |           | tency                                               |           |

|   |        | •         | stics                                               |           |

|   |        |           |                                                     |           |

| 2 |        |           | evision Register                                    |           |

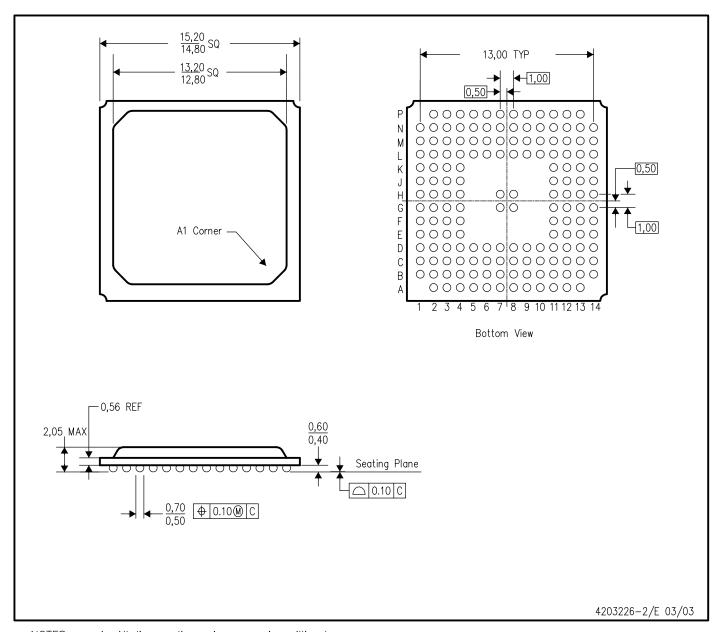

| 2 |        |           | PB 160-Ball Plastic Ball-Grid Array (PBGA)          |           |

|   | 2.1    | GC4016F   | rd 100-daii Fiasiic daii-Giiu Affay (PDGA)          | <u>44</u> |

SLWS133B-AUGUST 2001-REVISED JULY 2009

www.ti.com

| 3 | Contr       | ol Regi   | sters                                 | 49        |

|---|-------------|-----------|---------------------------------------|-----------|

|   | 3.1         | _         | Controls                              |           |

|   | 3.2         |           | Registers                             |           |

|   | 3.3         |           | oefficient Pages                      |           |

|   | 3.4         |           | pefficient Pages                      |           |

|   | 3.5         |           | l Frequency Pages                     |           |

|   | 3.6         |           | l Control Pages                       |           |

|   | 3.7         | Resamp    | oler Coefficient Pages (Pages 32–63)  | 57        |

|   | 3.8         | Resamp    | oler Control Page (Page 64)           | <u>59</u> |

|   | 3.9         | -         | oler Ratio Page (Page 65)             |           |

|   | 3.10        | Channe    | l Output Pages (Pages 96 and 97)      | 61        |

|   | 3.11        | Output (  | Control Page (Page 98)                | <u>61</u> |

| 4 | Speci       | ification | IS                                    | 68        |

|   | <b>4</b> .1 |           | e Maximum Ratings                     |           |

|   | 4.2         |           | mended Operating Conditions           |           |

|   | 4.3         |           | l Characteristics                     |           |

|   | 4.3.1       |           | Consumption                           |           |

|   | 4.4         |           | racteristics                          |           |

|   | 4.5         |           | racteristics                          |           |

| 5 | ilaaA       | cation N  | Notes                                 | 71        |

|   | 5.1         |           | and Ground Connections                | _         |

|   | 5.2         |           | ensitive Device                       |           |

|   | 5.3         |           | e-Sensitive Package                   |           |

|   | 5.4         |           | I Management                          |           |

|   | 5.5         |           | e CFIR Filter Sets                    |           |

|   | 5.6         | -         | e PFIR Filter Sets                    |           |

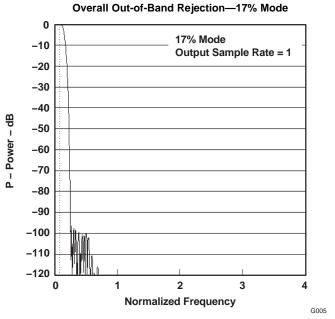

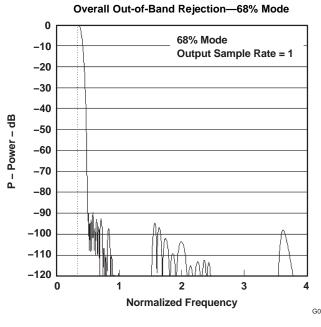

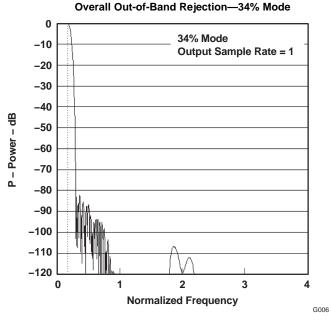

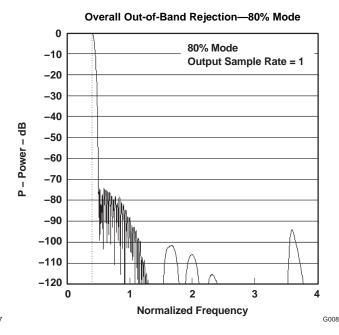

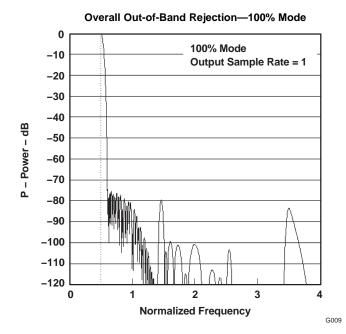

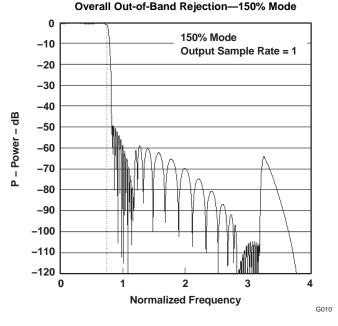

|   | 5.7         | -         | Spectral Responses of Example Filters |           |

|   | 5.8         |           | e Resampler Configurations            |           |

|   |             | 5.8.1     | Bypass Mode                           |           |

|   |             | 5.8.2     | Resampling Modes                      |           |

|   | 5.9         | GC4016    | Configuration Generator               |           |

|   | 5.10        |           | e GSM Application                     |           |

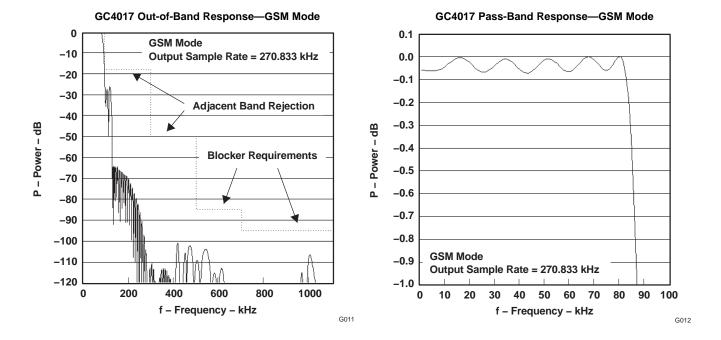

|   |             | 5.10.1    | GSM Filter Response                   | 77        |

|   |             | 5.10.2    | Oversampling Using the Resampler      | <u>78</u> |

|   |             | 5.10.3    | Gain                                  | 78        |

|   |             | 5.10.4    | GSM Configuration                     | 79        |

|   | 5.11        | Example   | e IS-136 DAMPS Application            | 79        |

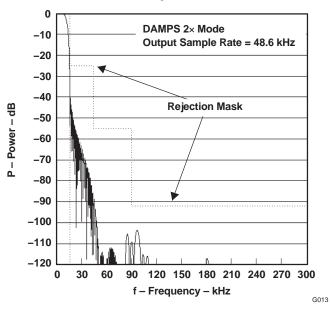

|   |             | 5.11.1    | DAMPS Filter Response                 | 80        |

|   |             | 5.11.2    | Oversampling Using the Resampler      | 81        |

|   |             | 5.11.3    | Gain                                  | <u>81</u> |

|   |             | 5.11.4    | DAMPS Configuration                   | <u>81</u> |

|   | 5.12        | Example   | e IS-95 NB-CDMA Application           | 83        |

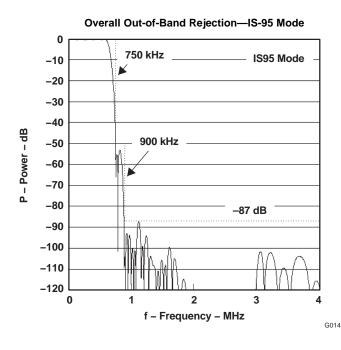

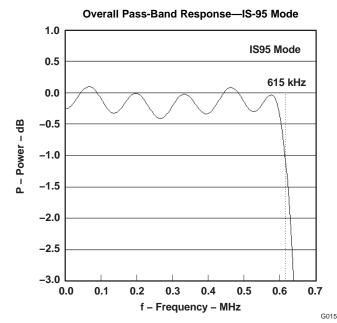

|   |             | 5.12.1    | IS-95 Filter Response                 | 83        |

|   |             | 5.12.2    | Oversampling Using the Resampler      | 84        |

|   |             | 5.12.3    | Gain                                  | 84        |

|   |             | 5.12.4    | IS-95 NB-CDMA Configuration           | 84        |

|   | 5.13        | UMTS V    | NB-CDMA Applications                  | 85        |

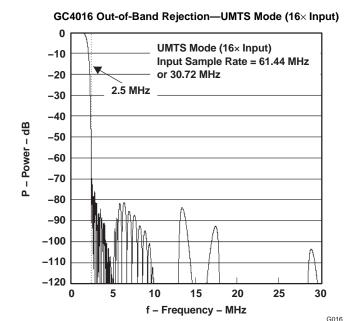

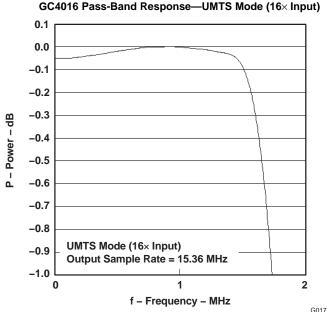

|   |             | 5.13.1    | UMTS Filter Response                  | 85        |

|   |             | 5.13.2    | Oversampling Using the Resampler      | 86        |

|   |             | 5.13.3    | Gain                                  |           |

|   |             | 5.13.4    | UMTS Configuration                    |           |

|   | 5.14        | Diagnos   | stics                                 | 87        |

# GC4016 MULTI-STANDARD QUAD DDC CHIP

| LWS133B-AUGUST 2001-REVISED JULY 2009 w | ww.ti.com |

|-----------------------------------------|-----------|

| 5.15 Output Test Configuration          | <u>91</u> |

| 5.16 Revision History                   | <u>93</u> |

| EVISION HISTORY                         | 0.4       |

# **List of Figures**

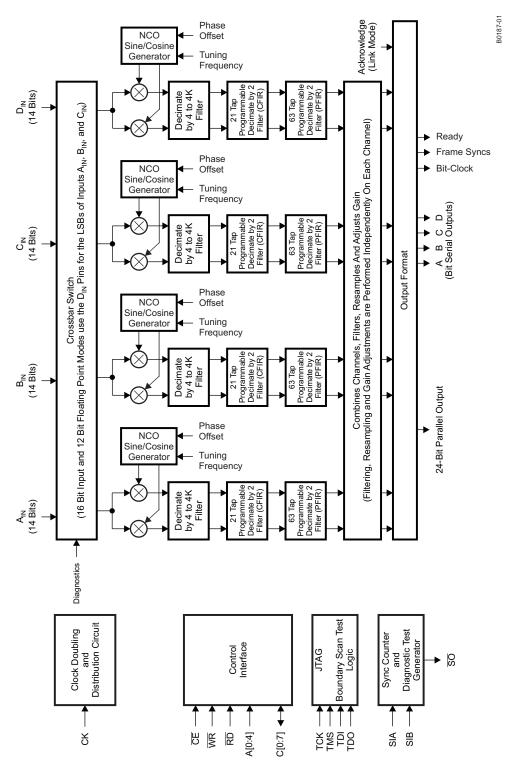

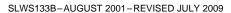

| 1-1  | GC4016 Block Diagram                                 | . 9       |

|------|------------------------------------------------------|-----------|

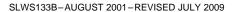

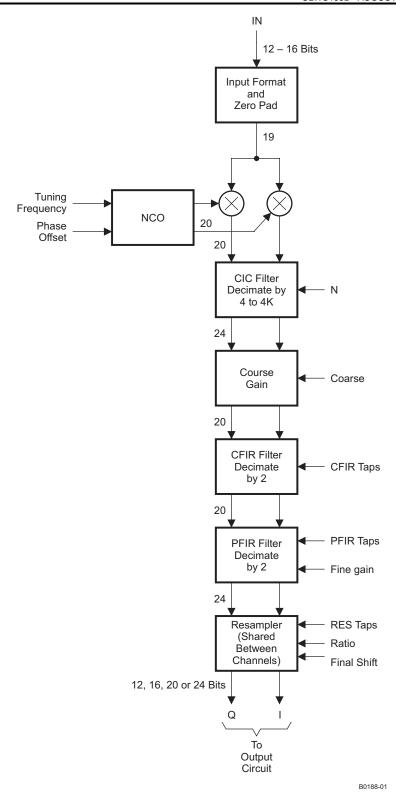

| 1-2  | Normal Control I/O Timing                            | <u>11</u> |

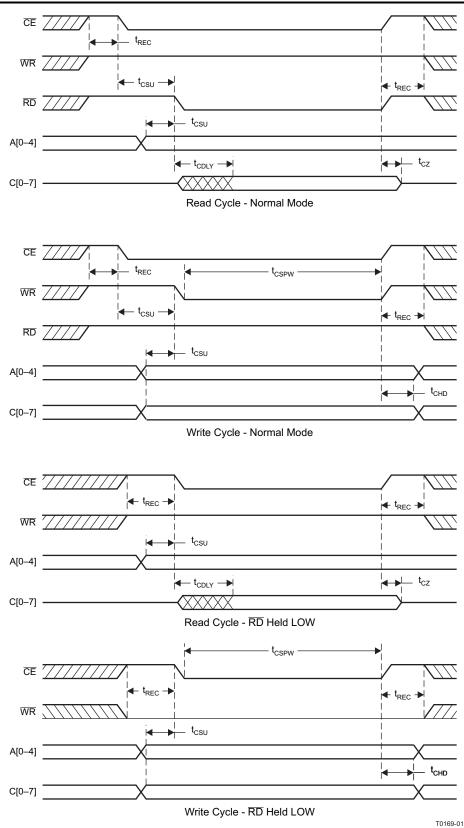

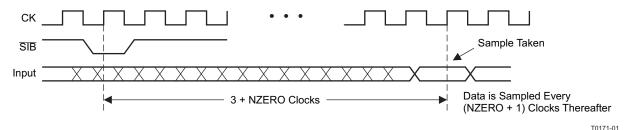

| 1-3  | Edge-Write Control Timing                            | <u>12</u> |

| 1-4  | Downconverter Channel                                | <u>16</u> |

| 1-5  | Zero-Pad Synchronization                             | <u>16</u> |

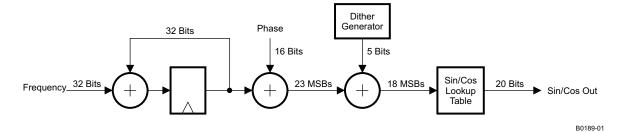

| 1-6  | NCO Circuit                                          | <u>17</u> |

| 1-7  | Example NCO Spurs                                    | <u>17</u> |

| 1-8  | NCO Peak Spur Plots                                  | <u>18</u> |

| 1-9  | Five-Stage CIC Decimate-by-N Filter                  | <u>18</u> |

| 1-10 | Typical CFIR Specifications                          | 20        |

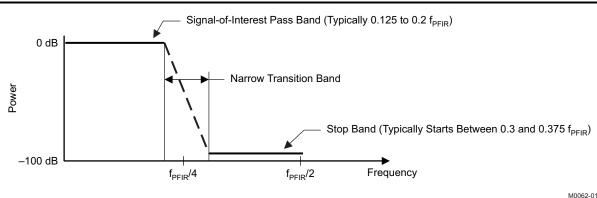

| 1-11 | Typical PFIR Specifications                          | <u>21</u> |

| 1-12 | Resampler Channel Block Diagram                      | <u>24</u> |

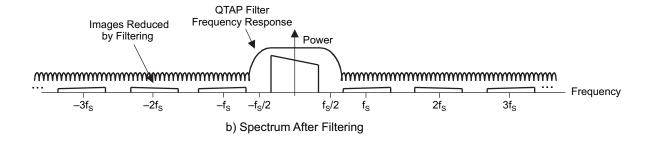

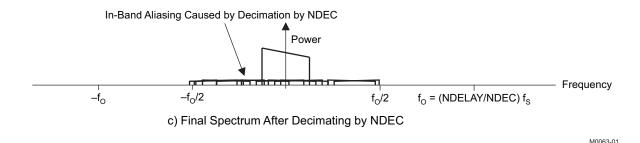

| 1-13 | The Resampler Spectral Response                      | <u>26</u> |

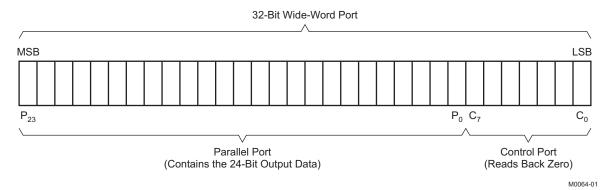

| 1-14 | Wide-Word Microprocessor Port                        | <u>32</u> |

| 1-15 | Serial Output Formats                                | <u>36</u> |

| 1-16 | Parallel-Mode Timing                                 | <u>39</u> |

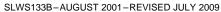

| 2-1  | GC4016 Terminal Assignments                          | <u>45</u> |

| 5-1  | cfir_17 With pfir_17                                 | <u>74</u> |

| 5-2  | cfir_34 With pfir_34                                 | <u>74</u> |

| 5-3  | cfir_68 With pfir_68                                 | <u>74</u> |

| 5-4  | cfir_80 With pfir_80                                 | <u>74</u> |

| 5-5  | cfir_100 With pfir_100                               | <u>75</u> |

| 5-6  | cfir_150 With pfir_150                               | <u>75</u> |

| 5-7  | Frequency Response for the Example GSM Application   | <u>78</u> |

| 5-8  | Frequency Response for the Example DAMPS Application | 80        |

| 5-9  | Frequency Response for the Example IS-95 Application | <u>83</u> |

| 5-10 | Frequency Response for the Example LIMTS Application | 86        |

SLWS133B-AUGUST 2001-REVISED JULY 2009

# **List of Tables**

| Input Mode Controls                               | <u>13</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multichannel Mode Settings                        | <u>23</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Output Mode Controls                              | <u>30</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Channel Output Map, Synchronous Four-Channel Mode | <u>31</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Channel Output Map, Synchronous Two-Channel Mode  | <u>31</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Channel Output Map, Single-Channel Mode           | <u>32</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Sync Modes                                        | <u>40</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Recommended Sync Settings                         | <u>42</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Mask Revisions                                    | <u>43</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GC4016 Terminal Locations (Top View)              | <u>46</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Terminal Functions                                | <u>46</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Global Control Registers                          | <u>49</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Page Assignments                                  | <u>51</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CFIR Coefficient Pages                            | <u>51</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PFIR Coefficient Pages                            | <u>52</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Channel Control Registers                         | <u>53</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Resampler Coefficient Pages (Single-Filter Mode)  | <u>58</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Resampler Control Registers                       | <u>59</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Resampler Ratio Page                              | <u>61</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Output Control Registers                          | <u>61</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Example CFIR Filters                              | <u>72</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Default PFIR Filters                              | <u>73</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Resampler Bypass Mode                             | <u>75</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Resampler Modes                                   | <u>75</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Desired GSM Specifictions                         | <u>77</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Example GSM Configuration                         | <u>79</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Desired DAMPS Specifications                      | <u>79</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Example DAMPS Configuration                       | <u>81</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Desired IS-95 NB-CDMA Specifications              | <u>83</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Example IS-95 NB-CDMA Configuration               | <u>84</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Desired UMTS Specifications                       | <u>85</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Example UMTS Configuration                        | <u>87</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Diagnostic Test 1, Expected Checksum = EC         | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Diagnostic Test 2, Expected Checksum = 4C         | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Diagnostic Test 3, Expected Checksum = EF         | <u>89</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Diagnostic Test 4, Expected Checksum = 18         | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GC4016 Register Assignment Quick Reference Guide  | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                   | Input Mode Controls  Multichannel Mode Settings  Output Mode Controls  Channel Output Map, Synchronous Four-Channel Mode  Channel Output Map, Synchronous Two-Channel Mode  Channel Output Map, Synchronous Two-Channel Mode  Sync Modes.  Recommended Sync Settings  Mask Revisions.  GC4016 Terminal Locations (Top View).  Terminal Functions.  Global Control Registers.  Page Assignments  CFIR Coefficient Pages  PFIR Coefficient Pages  Channel Control Registers.  Resampler Poefficient Pages (Single-Filter Mode).  Resampler Control Registers.  Resampler Ratio Page  Output Control Registers.  Resampler Ratio Page  Default PFIR Filters.  Default PFIR Filters.  Default Default PFIR Specifications  Example GSM Specifications  Example DAMPS Specifications  Example DAMPS Specifications  Example IS-95 NB-CDMA Configuration  Desired JAMPS Specifications  Example IS-95 NB-CDMA Configuration.  Desired UMTS Specifications  Example IS-95 NB-CDMA Configuration.  Desired UMTS Specifications  Example UMTS Configuration.  Diagnostic Test 1, Expected Checksum = EC  Diagnostic Test 2, Expected Checksum = ED  Diagnostic Test 3, Expected Checksum = 18  GC4016 Register Assignment Quick Reference Guide  GC4016 Register Assignment Quick Reference Guide |

#### 1 Introduction

#### 1.1 Features

- Input Rates up to 100 MSPS

- Four Independent Digital Downconvert (DDC) Channels

- Single-Channel GC4011 and Dual-Channel GC4012 Derivatives Are Available

- Independent Decimation and Resampling

- Independent Tuning, Phase and Gain Controls

- Input Crossbar Switch for:

- Four 14-Bit Inputs

- Three 16-Bit Inputs

- Three 12-Bit + 3-Bit Exponent Inputs

- Two 14-Bit Differential Inputs

- Decimation Factors of:

- 32 to 16,384 in Each Channel

- 16 to 32 by Combining Two Channels

- 8 to 16 by Combining Four Channels

- Zero-Padding for Lower Decimation Factors

- Resampler for Arbitrary Decimation Factors

- Peak Detection Counters for AGC Loop Controls

- Outputs Can Be:

- Bit Serial

- Nibble Serial (Link Port)

- Parallel Port

- Memory-Mapped Registers

- 12-, 16-, 20-, or 24-Bit Output Samples

- 0.02-Hz Tuning Resolution

- >100-dB Far-Band Rejection

- >115-dB Spurious-Free Dynamic Range

- User Programmable 21-Tap and 63-Tap Decimate-by-Two Filters, Independent per Channel

- Nyquist Filtering for QPSK or QAM Symbol Data

- Resampler Provides Additional Filtering and Allows Arbitrary Input/Output Rate Selections

- Microprocessor Interface for Control

- Built-In Diagnostics

- Application Examples:

- Four 4× Oversampled GSM, DAMPS, or IS-95 CDMA Carriers

- Two 8× Oversampled IS-95 CDMA Carriers

- Two 2× Oversampled 3.84-MB UMTS Carriers

- One 4× Oversampled 3.84-MB UMTS Carrier

- Core Power Consumption at 80 MHz, 2.5 V:

- 100 mW per DAMPS Channel

- 115 mW per GSM Channel

- 115 mW per IS-95 Channel

- 620 mW per 3.84-MB UMTS Channel

- Industrial Temperature Range (–40°C to 85°C)

- GC4016-PB 160-Ball PBGA

- Package: 15-mm × 15-mm

- 3.3-V I/O Voltage, 2.5-V Core Voltage

- JTAG Boundary Scan

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.

SLWS133B-AUGUST 2001-REVISED JULY 2009

#### 1.1.1 Block Diagram

Figure 1-1. GC4016 Block Diagram

www.ti.com

#### 1.2 Functional Description

The GC4016 quad receiver chip contains four identical downconversion circuits. Each downconversion circuit accepts a real sample rate up to 100 MHz, downconverts a selected carrier frequency to zero, decimates the signal rate by a programmable factor ranging from 32 to 16,384, and then resamples the channel to adjust the sample rate up or down by an arbitrary factor. In the real output mode, the output sample rate is doubled and the signal is output as a real signal centered at  $f_{out}/4$ . The channels may be combined to produce wider band and/or oversampled outputs or to process complex input data. The chip outputs the downconverted signals in any one of several formats (microprocessor, four serial lines, one TDM serial line, nibble, link, or 24-bit parallel port. The chip contains two user-programmable output filters per path which can be used to shape arbitrarily the received data spectrum. These filters can be used as Nyquist receive filters for digital data transmission. The chip also contains a resampling filter to provide additional filtering and to allow the user complete flexibility in the selection of input and output sample rates.

Two downconverter paths can be merged to be used as a single complex input downconversion circuit. Two paths may also be combined to support wider band output rates or oversampled outputs. Four paths may be combined to support both wider band output and oversampling.

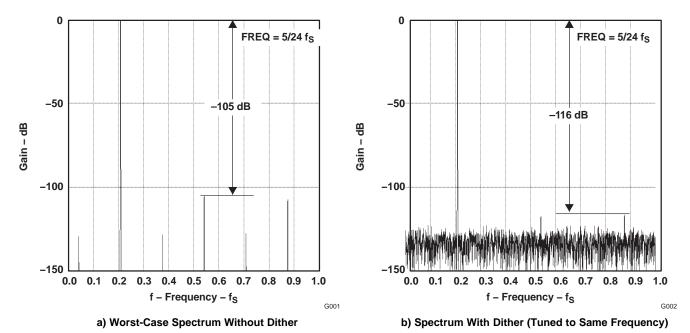

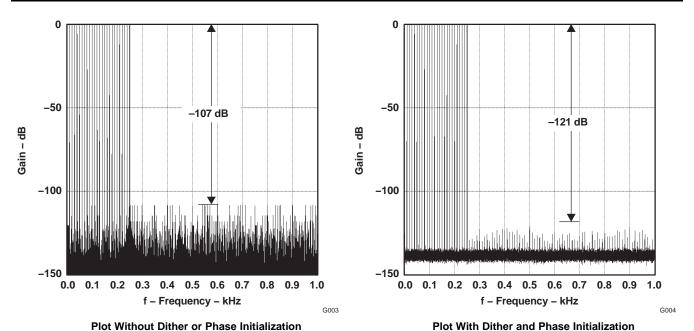

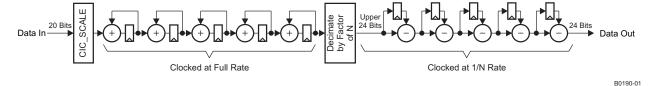

The downconverters are designed to maintain over 115 dB of spurious-free

dynamic range and over 100 dB of out-of-band rejection. A five-stage CIC and 20-bit internal data paths support this high-dynamic-range signal-processing requirement. Each downconvert circuit accepts 16-bit inputs and produces 24-bit outputs (can be rounded back to 12, 16, or 20 bits). The frequencies and phase offsets of the four sine/cosine sequence generators can be independently specified, as can the decimation and filter parameters of each circuit.

On-chip diagnostic circuits are provided to simplify system debug and maintenance.

The chip receives configuration and control information over a microprocessor-compatible bus consisting of an 8-bit data I/O port, a 5-bit address port, a chip-enable strobe, a read strobe, and a write strobe. The chip's control registers (8 bits each) are memory mapped into the 5-bit address space of the control port.

The applications section, Section 5. illustrates how to set the control registers and coefficients for specific wireless-communication standards.

#### 1.2.1 Control Interface

The chip is configured by writing control information into control registers within the chip. The control registers are grouped into eight global registers and 128 pages of registers, each page containing up to 16 registers. The global registers are accessed as addresses 0 through 7. Address 2 is the page register that selects which page is accessed by addresses 16 through 31. The contents of these control registers and how to use them are described in Section 3.

The registers are written to or read from using the C[0:7], A[0:4],  $\overline{CE}$ ,  $\overline{RD}$ , and  $\overline{WR}$  terminals. Each control register has been assigned a unique address within the chip. This interface is designed to allow the GC4016 chip to appear to an external processor as a memory-mapped peripheral (the  $\overline{RD}$  terminal is equivalent to a memory-chip  $\overline{OE}$  terminal).

An external processor (a microprocessor, computer, or DSP chip) can write into a register by setting A[0:4] to the desired register address, selecting the chip using the  $\overline{CE}$  terminal, setting C[0:7] to the desired value, and then pulsing  $\overline{WR}$  low. The data is written into the selected register when both  $\overline{WR}$  and  $\overline{CE}$  are low, and is held when either signal goes high. An alternate *edge-write* mode can be used to strobe the data into the selected register when either  $\overline{WR}$  or  $\overline{CE}$  goes high. This is useful for processors that do not specify

valid data when the write strobe goes low, but specify that the data must be stable before the write strobe goes high. The edge-write mode is necessary for these processors, as some control registers (such as most sync or reset registers) are sensitive to transient values on the **C[0:7]** data bus.

www.ti.com

To read from a control register, the processor must set A[0:4] to the desired address, select the chip with the  $\overline{CE}$  terminal, and then set  $\overline{RD}$  low. The chip then drives C[0:7] with the contents of the selected register. After the processor has read the value from C[0:7], it should set  $\overline{RD}$  and  $\overline{CE}$  high. The C[0:7] terminals are turned off (high impedance) whenever  $\overline{CE}$  or  $\overline{RD}$  is high or when  $\overline{WR}$  is low. The chip only drives these terminals when both  $\overline{CE}$  and  $\overline{RD}$  are low and  $\overline{WR}$  is high.

One can also ground the  $\overline{RD}$  terminal and use the  $\overline{WR}$  terminal as a read/write direction control and use the  $\overline{CE}$  terminal as a control I/O strobe. Figure 1-2 shows timing diagrams illustrating both I/O modes.

The edge-write mode, enabled by the EDGE\_WRITE control bit in register 0, allows for rising-edge write cycles. In this mode, the **C[0:7]** data only must be stable for a setup time before the rising edge of the write strobe, and held for a small hold time afterward. This mode is appropriate for processors that do not provide stable data before the start of the write pulse. Figure 1-3 shows the timing for this mode.

The setup, hold, and pulse-duration requirements for control read or write operations are given in Section 4.

The chip also operates in a 4-bit address mode, which is intended to be used with the expansion bus of the 4-address-bit Tl320C6X DSP chip. Address terminal A3 is grounded in this mode, and the LSB of the page register (address 2) is used in its place. The 4-bit mode is turned on using the 4\_BIT\_ADDRESS control bit in address 4.

Figure 1-2. Normal Control I/O Timing

Submit Documentation Feedback

Figure 1-3. Edge-Write Control Timing

#### 1.2.2 Input Format

The chip accepts five input formats:

- Four input ports of 14-bit data

- Three input ports of 16-bit data

- Two input ports of 14-bit, low-voltage differential data

- Three ports of 12-bit floating-point data with 3-bit exponent

- Three ports of multiplexed, dual-channel, 12-bit floating-point data with 3-bit exponent

The 12-, 14-, and 16-bit input words are in a 2s-complement format. The MSB\_POL control bit in address 27 of the channel-control pages can be used to convert offset binary data to the desired 2s-complement format. The 3-bit exponent in the floating-point format is an unsigned integer ranging from 0 to 7. All inputs are converted to the internal 19-bit format at the input to each channel. The 14- and 16-bit input words are put into the upper 14 and 16 bits, respectively, of the 19-bit word. The unused LSBs are cleared.

The 12-bit floating-point word is shifted down, sign-extended by the amount specified by the 3-bit exponent, and then put into the MSBs of 19-bit word.

A crossbar switch allows the user to route any input source to any downconverter channel.

Table 1-1 shows the suggested control register settings required for each input mode. See Section 3.6 for detailed descriptions of each control setting.

#### 1.2.3 The Downconverters