# **Complete Current Share 10A DC/DC Power Module**

#### ISL8200AM

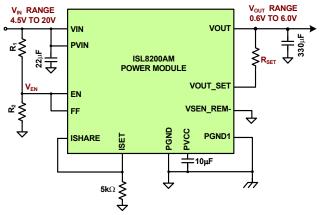

The ISL8200AM is a simple and easy to use high power, current-sharing DC/DC power module for Datacom/Telecom/FPGA power hungry applications. All that is needed is the ISL8200AM, a few passive components and one VOUT setting resistor to have a complete 10A design ready for market.

The ease of use virtually eliminates the design and manufacturing risks while dramatically improving time to market.

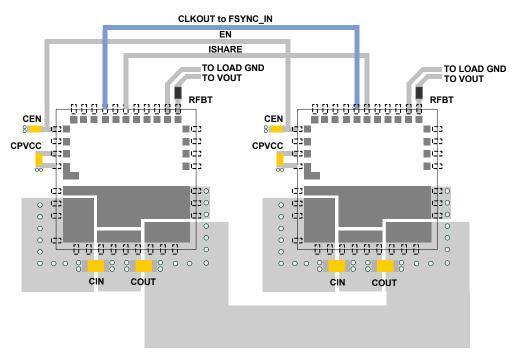

Need more output current? Parallel up to six ISL8200AM modules to scale up to a 60A solution (see Figure 6 on page 10).

The simplicity of the ISL8200AM is in its "Off The Shelf", unassisted implementation versus a discrete implementation. Patented current sharing in multi-phase operation greatly reduces ripple currents, BOM cost and complexity. For example, parallel 2 for 20A and up to 6 for 60A. The output voltage can be precisely regulated to as low as 0.6V with  $\pm 1\%$  output voltage regulation over line, load, and temperature variations.

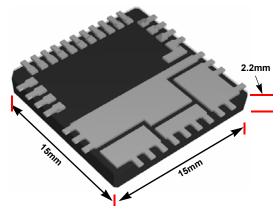

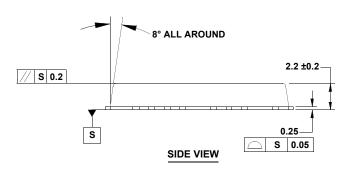

The ISL8200AM's thermally enhanced, compact QFN package, operates at full load and over-temperature, without requiring forced air cooling. It's so thin it can even fit on the back side of the PCB. Easy access to all pins with few external components, reduces the PCB design to a component layer and a simple ground layer.

#### **Features**

- Complete Switch Mode Power Supply in One Package

- Patented Current Share Architecture Reduces Layout Sensitivity when Modules are Paralleled

- Programmable Phase Shift (1 to 6 Phase)

- Extremely Low Profile (2.2mm Height)

- Input Voltage Range +4.5V to +20V at 10A, Current Share up to 60A

- A Single Resistor Sets V<sub>OUT</sub> from +0.6V to +6V

- Output Overvoltage, Overcurrent and Over-Temperature Protection and Undervoltage Indication

- RoHS Compliant

### **Applications**

- Servers, Telecom and Datacom Applications

- · Industrial and Medical Equipment

- · Point of Load Regulation

### **Related Literature**

- AN1738 "ISL8200AMEV1PHZ Evaluation Board User's Guide"

- ISL8200AM iSim Model (Product Information Page)

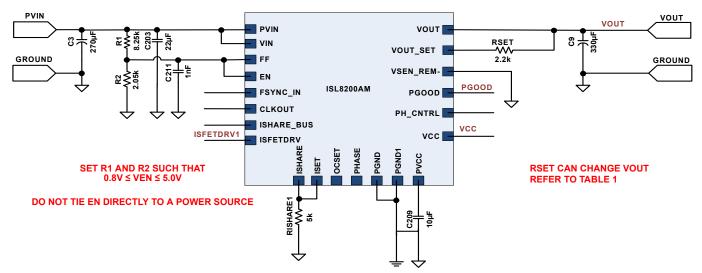

# **Complete Functional Schematic**

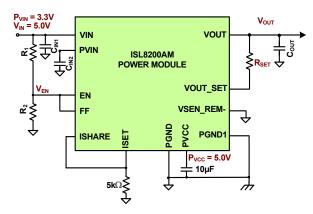

FIGURE 1. COMPLETE 10A DESIGN, JUST SELECT  $R_{\text{SET}}$  FOR THE DESIRED  $V_{\text{OUT}}$

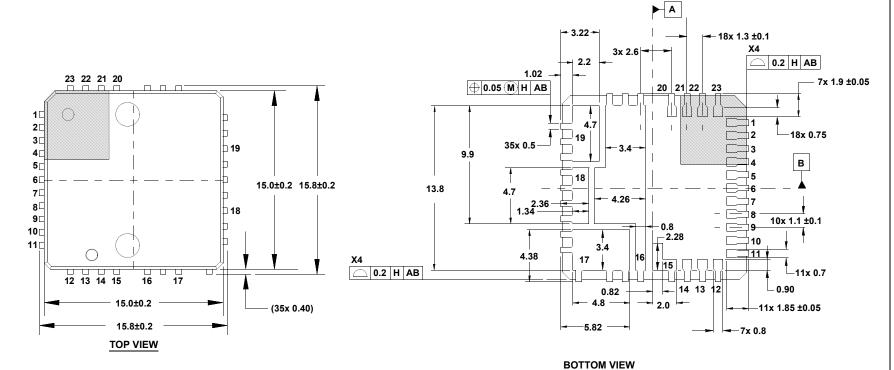

### **ISL8200AM Package**

FIGURE 2. THE 2.2mm HEIGHT IS IDEAL FOR THE BACKSIDE

OF PCBS WHEN SPACE AND HEIGHT IS A PREMIUM

# **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART MARKING | TEMP.<br>RANGE (°C) | PACKAGE<br>(RoHS Compliant) | PKG. DWG. # |

|--------------------------------|--------------|---------------------|-----------------------------|-------------|

| ISL8200AMIRZ                   | ISL8200AM    | -40°C to +85°C      | 23 Ld QFN                   | L23.15x15   |

#### NOTES:

- 1. Add "-T" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

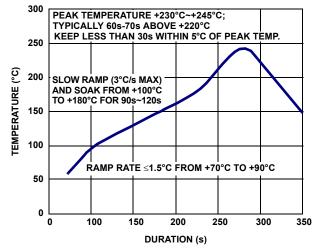

- These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil

Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL8200AM. For more information on MSL please see techbrief TB363.

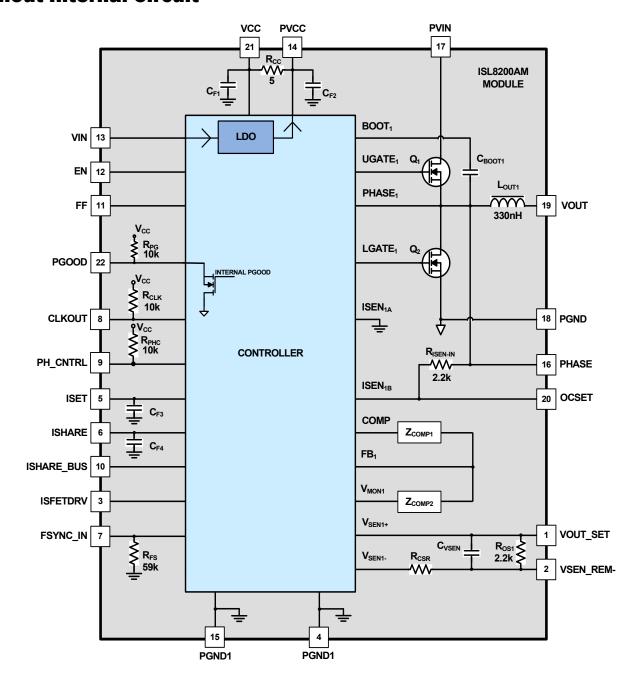

### **Pinout Internal Circuit**

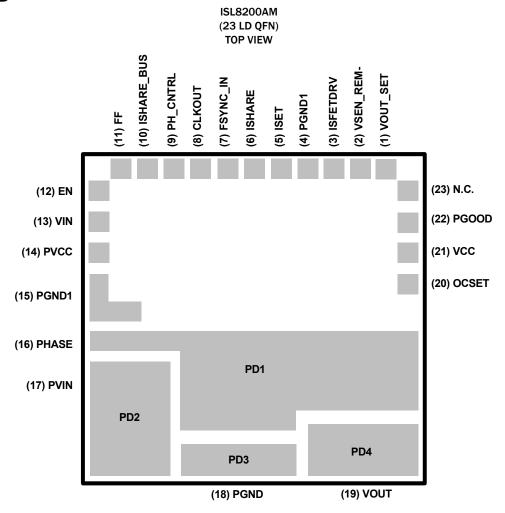

# **Pin Configuration**

# **Pin Descriptions**

| PIN#  | PIN NAME  | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VOUT_SET  | Analog Voltage Input - Used with $V_{OUT}$ to program the regulator output voltage. The typical input impedance of VOUT_SET with respect to VSEN_REM- is $500 \mathrm{k}\Omega$ . The voltage input typ. is 0.6V.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2     | VSEN_REM- | Analog Voltage Input - This pin is the negative input of standard unity gain operational amplifier for differential remote sense for the regulator, and should connect to the negative rail of the load/processor. This pin can be used for V <sub>OUT</sub> trimming by connecting a resistor from this pin to the VOUT_SET pin.                                                                                                                                                                                                                                                                                                   |

| 3     | ISFETDRV  | Digital Output - This pin is used to drive an optional NFET, which will connect ISHARE with the system ISHARE bus upon completing a pre-bias startup. The voltage output range is 0V to 5V.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4, 15 | PGND1     | Normal Ground - All voltage levels are referenced to this pad. This pad provides a return path for the low side MOSFET drives and internal power circuitries as well as all analog signals. PGND and PGND1 should be connected together with a ground plane.                                                                                                                                                                                                                                                                                                                                                                        |

| 5     | ISET      | Analog Current Output - This pin sources a 15 $\mu$ A offset current plus Channel 1's average current. The voltage (VISET) set by an external resistor (RISET) represents the average current level of the local active module. For full-scale current, RISET should be ~10k $\Omega$ . The output current range is 15 $\mu$ A to 126 $\mu$ A typ.  The ISET and ISHARE pins are used for current sharing purposes with multiple ISL8200AM modules. In the single module configuration, this pin can be tied to the ISHARE pin. In multi-phase operation, if noise is a concern, add an additional 10pF capacitor to the ISET line. |

# Pin Descriptions (Continued)

| PIN# | PIN NAME   | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6    | ISHARE     | Analog Current Output - Cascaded system level overcurrent shutdown pin. This pin is used where you have multiple modules configured for current sharing and is used with a common current share bus. The bus sums each of the modules' average current contribution to the load to protect for a overcurrent condition at the load. The pin sources $15\mu$ A plus average module's output current. The shared bus voltage ( $V_{ISHARE}$ ) is developed across an external resistor ( $R_{ISHARE}$ ). $V_{ISHARE}$ represents the average current of all active channel(s) that are connected together. The ISHARE bus voltage is compared with each module's internal reference voltage set by each module's $R_{ISET}$ resistor. This will generate an individual current share error signal in each cascaded controller. The share bus impedance $R_{ISHARE}$ should be set as $R_{ISET}/NCTRL$ , $R_{ISET}$ divided by the number of active current sharing controllers. The output current from this pin generates a voltage across the external resistor. This voltage, $V_{ISHARE}$ , is compared to an internal $1.2V$ threshold for average overcurrent protection. For full-scale current, $R_{ISHARE}$ should be ~ $10k\Omega$ . Typically $10k\Omega$ is used for $R_{SHARE}$ and $R_{SET}$ . The output current range is $15\mu$ A to $126\mu$ A typ. |

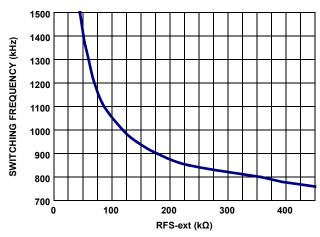

| 7    | FSYNC_IN   | Analog Input Control Pin - An optional external resistor (RFS-ext) connected to this pin and ground will increase the oscillator switching frequency. It has an internal $59k\Omega$ resistor for a default frequency of $700kHz$ . The internal oscillator will lock to an external frequency source when connected to a square waveform. The external source is typically the CLKOUT signal from another ISL8200AM or an external clock. The internal oscillator synchronizes with the leading positive edge of the input signal. The input voltage range for the external source is 0V to 5V Square Wave. When not synchronized to an external clock, a 100pF capacitor between FSYNC_IN and PGND1 is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8    | CLKOUT     | Digital Voltage Output - This pin provides a clock signal to synchronize with other ISL8200AM(s). When there is more than one ISL8200AM in the system, the two independent regulators can be programmed via PH_CNTRL for different degrees of phase delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9    | PH_CNTRL   | Analog Input - The voltage level on this pin is used to program the phase shift of the CLKOUT clock signal to synchronize with other module(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10   | ISHARE_BUS | Open pin until first PWM pulse is generated. Then, via an internal FET, this pin connects the module's ISHARE to the system's ISHARE bus after pre-bias is complete and soft-start is initiated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

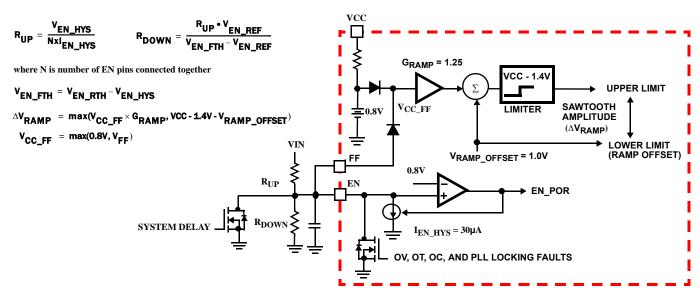

| 11   | FF         | Analog Voltage Input - The voltage on this pin is fed into the controller, adjusting the sawtooth amplitude to generate the feed-forward function. The input voltage range is 0.8V to V <sub>CC</sub> . Typically, FF is connected to EN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12   | EN         | This is a double function pin: Analog Input Voltage - The input voltage to this pin is compared with a precision 0.8V reference and enables the digital soft-start. The input voltage range is OV to V <sub>CC</sub> or V <sub>IN</sub> through a pull-up resistor maintaining a typical current of 5mA.  Analog Voltage Output - This pin can be used as a voltage monitor for input bus undervoltage lockout. The hysteresis levels of the lockout can be programmed via this pin using a resistor divider network. Furthermore, during fault conditions (such as overvoltage, overcurrent, and over-temperature), this pin is used to communicate the information to other cascaded modules by pulling the wired OR low as it is an Open Drain. The output voltage range is OV to V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13   | VIN        | Analog Voltage Input - This pin should be tied directly to the input rail when using the internal linear regulator. It provides power to the internal linear drive circuitry. When used with an external 5V supply, this pin should be tied directly to PVCC. The internal linear device is protected against the reversed bias generated by the remaining charge of the decoupling capacitor at VCC when losing the input rail. The input voltage range is 4.5V to 20V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14   | PVCC       | Analog Output - This pin is the output of the internal series linear regulator. It provides the bias for both low-side and high-side drives. Its operational voltage range is 4.5V to 5.6V. The decoupling ceramic capacitor in the PVCC pin is 10µF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16   | PHASE      | Analog Output - This pin is the phase node of the regulator. The output voltage range is 0V to 30V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17   | PVIN       | Analog Input - This input voltage is applied to the power FETs with the FET's ground being the PGND pin. It is recommended to place input decoupling capacitance, 22µF, directly between the PVIN pin and the PGND pin as close as possible to the module. The input voltage range is 3V to 20V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18   | PGND       | All voltage levels are referenced to this pad. This is the low side MOSFET ground. PGND and PGND1 should be connected together with a ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19   | VOUT       | Output voltage from the module. The output voltage range is 0.6V to 6V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

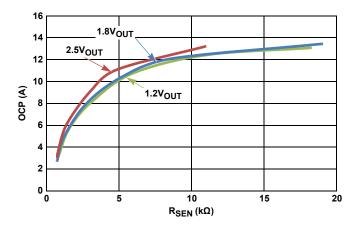

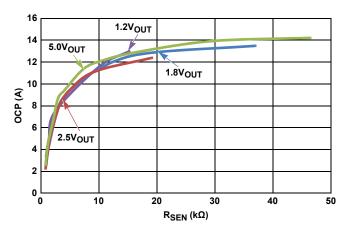

| 20   | OCSET      | Analog Input - This pin is used with the PHASE pin to set the current limit of the module. The input voltage range is 0V to 30V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 21   | vcc        | Analog Input - This pin provides bias power for the analog circuitry. It's operational range is 4.5V to 5.6V. In 3.3V applications, VCC, PVCC and VIN should be shorted to allow operation at the low end input as it relates to the V <sub>CC</sub> falling threshold limit. This pin can be powered either by the internal linear regulator or by an external voltage source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

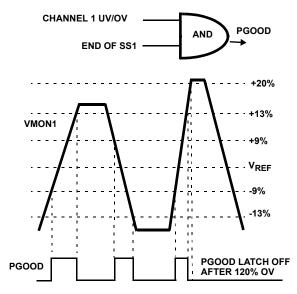

| 22   | PGOOD      | Analog Output - This pin, pulled up to VCC via an internal $10k\Omega$ resistor, provides a Power Good signal when the output is within 9% of nominal output regulation point with 4% hysteresis ( $13\%/9\%$ ), and soft-start is complete. An external pull-up is not required. PGOOD monitors the outputs (VMON1) of the internal differential amplifiers. The output voltage range is 0V to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

4 intersil

# Pin Descriptions (Continued)

| PIN# | PIN NAME | PIN DESCRIPTION                                                                                                                                                                                                                                    |  |  |  |  |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 23   | NC       | Not internal connected                                                                                                                                                                                                                             |  |  |  |  |

| PD1  |          | Used for both the PHASE pin (Pin # 16) and for heat removal connecting to heat dissipation layers using vias. Connect this pad to a copper island on the PCB board with the same shape as the pad; this is electrically connected to PHASE pin 16. |  |  |  |  |

| PD2  |          | Used for both the PVIN pin (Pin # 17) and for heat removal connecting to heat dissipation layers using vias. Connect this pad to a copper island on the PCB board with the same shape as the pad; this is electrically connected to PVIN pin 17.   |  |  |  |  |

| PD3  |          | Used for both the PGND pin (Pin # 18) and for heat removal connecting to heat dissipation layers using vias. Connect this pad to a copper island on the PCB board with the same shape as the pad; this is electrically connected to PGND pin 18.   |  |  |  |  |

| PD4  | 001      | Used for both the VOUT pin (Pin # 19) and for heat removal connecting to heat dissipation layers using vias. Connect this pad to a copper island on the PCB board with the same shape as the pad; this is electrically connected to VOUT pin 19.   |  |  |  |  |

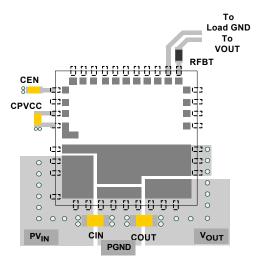

# **Typical Application Circuits**

FIGURE 3. SINGLE PHASE 10A 1.2V OUTPUT CIRCUIT

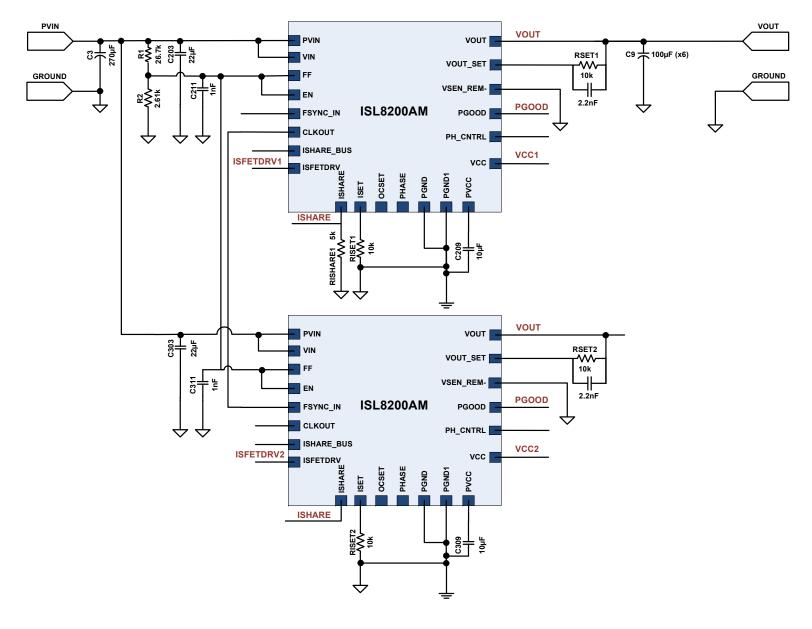

# Typical Application Circuits (continued)

FIGURE 4. TWO PHASE 20A 3.3V OUTPUT CIRCUIT

FN8271.4 March 7. 2013

#### **Absolute Maximum Ratings**

| Input Voltage, PVIN, V <sub>IN</sub>                                                 | 0.3V to +27V                |

|--------------------------------------------------------------------------------------|-----------------------------|

| Driver Bias Voltage, PVCC                                                            | -0.3V to +6.0V              |

| Signal Bias Voltage, V <sub>CC</sub>                                                 | -0.3V to +6.5V              |

| BOOT/UGATE Voltage, V <sub>BOOT</sub>                                                | 0.3V to +36V                |

| Phase Voltage, V <sub>PHASE</sub> V <sub>BOOT</sub> - 7V t<br>BOOT to PHASE Voltage, | o V <sub>BOOT</sub> + 0.3V  |

| V <sub>BOOT</sub> - V <sub>PHASE</sub> 0.3                                           | V to V <sub>CC</sub> + 0.3V |

| Input, Output or I/O Voltage0.3                                                      | V to V <sub>CC</sub> + 0.3V |

| ESD Rating                                                                           |                             |

| Human Body Model (Tested per JESD22-A114E)                                           | $\dots\dots\dots 2kV$       |

| Machine Model (Tested per JESD22-A115-A)                                             | 200V                        |

| Charge Device Model (Tested per JESD22-C101C)                                        | $\dots\dots 1kV$            |

| Latch Up (Tested per JESD-78B; Class 2, Level A)                                     | 100mA                       |

#### **Thermal Information**

| Thermal Resistance (Typical)      | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|-----------------------------------|----------------------|----------------------|

| QFN Package (Notes 4, 5)          | 13                   | 2.0                  |

| Maximum Storage Temperature Range | 5                    | 5°C to +150°C        |

#### **Recommended Operating Conditions**

| Input Voltage                          |                |

|----------------------------------------|----------------|

| P <sub>VIN</sub>                       | 3V to 20V      |

| V <sub>IN</sub>                        | 4.5V to 20V    |

| Driver Bias Voltage, PVCC              | 4.5V to 5.6V   |

| Signal Bias Voltage, V <sub>CC</sub>   | 4.5V to 5.6V   |

| Boot to Phase Voltage                  |                |

| V <sub>BOOT</sub> - V <sub>PHASE</sub> | <6V            |

| Industrial Ambient Temperature Range   | 40°C to +85°C  |

| Junction Temperature Range             | 40°C to +125°C |

|                                        |                |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

- 4. θ<sub>IA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board (i.e., 4-layer type without thermal vias see tech brief <u>TB379</u>) per JEDEC standards except that the top and bottom layers assume solid plains.

- 5. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

### **Electrical Specifications** Boldface limits apply over the operating temperature range, -40 °C to +85 °C.

| PARAMETER                               | SYMBOL               | TEST CONDITIONS                                                                     | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS  |

|-----------------------------------------|----------------------|-------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|--------|

| VCC SUPPLY CURRENT                      | •                    |                                                                                     |                 | •               |                 |        |

| Nominal Supply V <sub>IN</sub> Current  | I <sub>Q_VIN</sub>   | PVIN = V <sub>IN</sub> = 20V; No Load; F <sub>SW</sub> = 700kHz                     |                 | 36              |                 | mA     |

| Nominal Supply V <sub>IN</sub> Current  | I <sub>Q_VIN</sub>   | PVIN = V <sub>IN</sub> = 4.5V; No Load; F <sub>SW</sub> = 700kHz                    |                 | 27              |                 | mA     |

| Shutdown Supply V <sub>CC</sub> Current | lvcc                 | EN = 0V, V <sub>CC</sub> = 2.97V                                                    |                 | 9               |                 | mA     |

| INTERNAL LINEAR REGULATOR               | <u>'</u>             |                                                                                     | 1               |                 |                 |        |

| Maximum Current                         | I <sub>PVCC</sub>    | PVCC = 4V to 5.6V                                                                   |                 | 320             |                 | mA     |

| Saturated Equivalent Impedance          | R <sub>LDO</sub>     | P-Channel MOSFET (V <sub>IN</sub> = 5V)                                             |                 | 1               |                 | Ω      |

| PVCC Voltage Level (Note 7)             | PVCC                 | I <sub>PVCC</sub> = 0mA, V <sub>IN</sub> = 12V                                      | 5.15            | 5.4             | 5.60            | ٧      |

| POWER-ON RESET (Note 7)                 | <u>'</u>             |                                                                                     | 1               |                 |                 |        |

| Rising VCC Threshold                    |                      |                                                                                     |                 | 2.85            | 2.97            | ٧      |

| Falling VCC Threshold                   |                      |                                                                                     |                 | 2.65            | 2.75            | ٧      |

| Rising PVCC Threshold                   |                      |                                                                                     |                 | 2.85            | 2.97            | ٧      |

| Falling PVCC Threshold                  |                      |                                                                                     |                 | 2.65            | 2.75            | ٧      |

| System Soft-start Delay                 | t <sub>SS_DLY</sub>  | After PLL, $V_{CC}$ , and PVCC PORs, and EN above their thresholds                  |                 | 384             |                 | Cycles |

| ENABLE (Note 7)                         | <u>'</u>             |                                                                                     | 1               |                 |                 |        |

| Turn-On Threshold Voltage               |                      |                                                                                     | 0.75            | 0.8             | 0.86            | ٧      |

| Hysteresis Sink Current                 | I <sub>EN_HYS</sub>  |                                                                                     | 21              | 30              | 35              | μΑ     |

| Undervoltage Lockout Hysteresis         | V <sub>EN_HYS</sub>  | $V_{EN\_RTH}$ = 10.6V; $V_{EN\_FTH}$ = 9V<br>$R_{UP}$ = 53.6kΩ, $R_{DOWN}$ = 5.23kΩ |                 | 1.6             |                 | V      |

| Sink Current                            | I <sub>EN_SINK</sub> | VEN = 1V                                                                            | 15.4            |                 |                 | mA     |

| Sink Impedance                          | R <sub>EN_SINK</sub> | VEN = 1V                                                                            |                 |                 | 64              | Ω      |

| OSCILLATOR                              |                      |                                                                                     |                 |                 |                 |        |

| Oscillator Frequency                    | FOSC                 | $R_{FS}$ = 59kΩ; Figure 34                                                          |                 | 700             |                 | kHz    |

| Total Variation (Note 7)                |                      | V <sub>CC</sub> = 5V;                                                               | -9              |                 | +9              | %      |

intersil FN8271.4 March 7, 2013

### **Electrical Specifications** Boldface limits apply over the operating temperature range, -40 °C to +85 °C. (Continued)

| PARAMETER                                                                                                      | SYMBOL                               | TEST CONDITIONS                                                                                                   | MIN<br>(Note 7) | TYP<br>(Note 6)       | MAX<br>(Note 7)                                  | UNITS             |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|--------------------------------------------------|-------------------|

| FREQUENCY SYNCHRONIZATION AND P                                                                                | HASE LOCK LOOP                       | (Note 7)                                                                                                          |                 | +                     | +                                                |                   |

| Synchronization Frequency                                                                                      |                                      | V <sub>CC</sub> = 5.4V                                                                                            | FOSC            |                       | 1500                                             | kHz               |

| PLL Locking Time                                                                                               |                                      | V <sub>CC</sub> = 5.4V; F <sub>SW</sub> = 700kHz                                                                  |                 | 210                   |                                                  | μs                |

| Input Signal Duty Cycle Range                                                                                  |                                      |                                                                                                                   | 10              |                       | 90                                               | %                 |

| PWM (Note 7)                                                                                                   |                                      |                                                                                                                   |                 |                       |                                                  |                   |

| Minimum PWM OFF Time                                                                                           | t <sub>MIN_OFF</sub>                 |                                                                                                                   | 310             | 345                   | 410                                              | ns                |

| Current Sampling Blanking Time                                                                                 | t <sub>BLANKING</sub>                |                                                                                                                   |                 | 175                   |                                                  | ns                |

| OUTPUT CHARACTERISTICS                                                                                         |                                      |                                                                                                                   |                 |                       |                                                  |                   |

| Output Continuous Current Range                                                                                | I <sub>OUT(DC)</sub>                 | PVIN = V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.2V                                                             | 0               |                       | 10                                               | Α                 |

| Line Regulation Accuracy                                                                                       | $\Delta V_{OUT}/\Delta V_{IN}$       | $V_{OUT} = 1.2V$ , $I_{OUT} = 0A$ , $PVIN = V_{IN} = 3.5V$ to $20V$                                               |                 | 0.15                  |                                                  | %                 |

| Ç                                                                                                              | 001/ IN                              | $V_{OUT} = 1.2V, I_{OUT} = 10A, PVIN = V_{IN} = 5V \text{ to } 20V$                                               |                 | 0.15                  |                                                  | %                 |

| Load Regulation Accuracy                                                                                       | ΔV <sub>ΟυΤ</sub> /ΔΙ <sub>ΟυΤ</sub> | I <sub>OUT</sub> = 0A to 10A, V <sub>OUT</sub> = 1.2V, PVIN = V <sub>IN</sub> = 12V                               |                 | 0.1                   |                                                  | %                 |

| Output Ripple Voltage                                                                                          | ΔV <sub>OUT</sub>                    | $I_{OUT} = 10A, V_{OUT} = 1.2V, PVIN = V_{IN} = 12V$                                                              |                 | 27                    |                                                  | mV <sub>P-P</sub> |

| a a para a p | 001                                  | I <sub>OUT</sub> = 0A, V <sub>OUT</sub> = 1.2V, PVIN = V <sub>IN</sub> = 12V                                      |                 | 19                    |                                                  | mV <sub>P-P</sub> |

| DYNAMIC CHARACTERISTICS                                                                                        |                                      | -001 0.3, 001 ===3, 1.11 1 <sub>IN</sub> ==1                                                                      |                 |                       |                                                  | ···· F-F          |

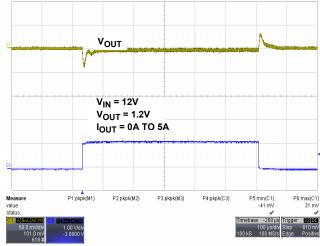

| Voltage Change For Positive Load Step                                                                          | ΔV <sub>OUT-DP</sub>                 | $I_{OUT}$ = 0A to 5A. Current slew rate = 2.5A/ $\mu$ s,<br>PVIN = V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.2V |                 | 45                    |                                                  | mV <sub>P-P</sub> |

| Voltage Change For Negative Load<br>Step                                                                       | ΔV <sub>OUT-DN</sub>                 | $I_{OUT}$ = 5A to 0A. Current slew rate = 2.5A/ $\mu$ s,<br>PVIN = V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.2V |                 | 55                    |                                                  | mV <sub>P-P</sub> |

| REFERENCE (Note 7)                                                                                             |                                      |                                                                                                                   |                 |                       |                                                  |                   |

| Reference Voltage (Include Error and                                                                           | V <sub>REF</sub>                     |                                                                                                                   |                 | 0.6                   |                                                  | V                 |

| Differential Amplifiers' Offsets)                                                                              | NEI                                  |                                                                                                                   | -0.75           |                       | 0.75                                             | %                 |

| DIFFERENTIAL AMPLIFIER (Note 7)                                                                                |                                      |                                                                                                                   |                 |                       |                                                  |                   |

| DC Gain                                                                                                        | UG_DA                                | Unity Gain Amplifier                                                                                              |                 | 0                     |                                                  | dB                |

| Unity Gain Bandwidth                                                                                           | UGBW_DA                              | , ,                                                                                                               |                 | 5                     |                                                  | MHz               |

| V <sub>SFN+</sub> Pins Input Current                                                                           | I <sub>VSEN+</sub>                   |                                                                                                                   | 0.2             | 1.16                  | 2.5                                              | μA                |

| Maximum Source Current for Current Sharing                                                                     | IVSEN1-                              | VSEN1- Source Current for Current Sharing when parallel multiple modules each of which has its own voltage loop   |                 | 350                   |                                                  | μΑ                |

| Input Impedance                                                                                                | R <sub>VSEN+</sub> _to<br>_VSEN-     | $V_{VSEN+}/I_{VSEN+}$ , $V_{VSEN+} = 0.6V$                                                                        |                 | -500                  |                                                  | kΩ                |

| Output Voltage Swing                                                                                           |                                      |                                                                                                                   | 0               |                       | V <sub>CC</sub> - 1.8                            | ٧                 |

| Input Common Mode Range                                                                                        |                                      |                                                                                                                   | -0.2            |                       | V <sub>CC</sub> - 1.8                            | ٧                 |

| Disable Threshold                                                                                              | V <sub>VSEN-</sub>                   | V <sub>MON1</sub> = Tri-State                                                                                     |                 | V <sub>CC</sub> - 0.4 |                                                  | ٧                 |

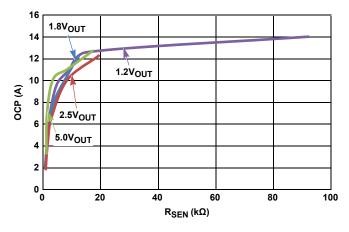

| OVERCURRENT PROTECTION (Note 7)                                                                                |                                      |                                                                                                                   |                 | +                     | <del>                                     </del> |                   |

| Channel Overcurrent Limit                                                                                      | I <sub>SOURCE</sub>                  | V <sub>CC</sub> = 2.97V to 5.6V                                                                                   |                 | 111                   |                                                  | μA                |

| Channel Overcurrent Limit                                                                                      | I <sub>SOURCE</sub>                  | $V_{CC} = 5V;$                                                                                                    | 89              | 111                   | 129                                              | μA                |

| Share Pin OC Threshold                                                                                         | V <sub>OC_ISHARE</sub>               | Comparator offset included                                                                                        | 1.16            | 1.20                  | 1.22                                             | V                 |

| CURRENT SHARE                                                                                                  |                                      |                                                                                                                   |                 | 1                     |                                                  |                   |

| External Current Share Accuracy                                                                                |                                      | Up to 3 phases                                                                                                    |                 | ±10                   |                                                  | %                 |

| POWER GOOD MONITOR (Note 7)                                                                                    |                                      |                                                                                                                   |                 | I                     | <u> </u>                                         |                   |

| Undervoltage Falling Trip Point                                                                                | V <sub>UVF</sub>                     | Percentage Below Reference Point                                                                                  | -15             | -13                   | -11                                              | %                 |

| Undervoltage Rising Hysteresis                                                                                 | V <sub>UVR_HYS</sub>                 | Percentage Above UV Trip Point                                                                                    | ·               | 4                     | -                                                | %                 |

| 5 5 7                                                                                                          | 0411_1113                            | 5 F                                                                                                               |                 |                       |                                                  |                   |

# **Electrical Specifications** Boldface limits apply over the operating temperature range, -40°C to +85°C. (Continued)

| PARAMETER                                            | SYMBOL               | TEST CONDITIONS                         | MIN<br>(Note 7) | TYP<br>(Note 6) | MAX<br>(Note 7) | UNITS |

|------------------------------------------------------|----------------------|-----------------------------------------|-----------------|-----------------|-----------------|-------|

| Overvoltage Falling Hysteresis                       | V <sub>OVF_HYS</sub> | Percentage below OV Trip Point          |                 | 4               |                 | %     |

| PGOOD Low Output Voltage                             |                      | I <sub>PGOOD</sub> = 2mA                |                 |                 | 0.35            | ٧     |

| Sinking Impedance                                    |                      | I <sub>PGOOD</sub> = 2mA                |                 |                 | 70              | Ω     |

| Maximum Sinking Current                              |                      | V <sub>PGOOD</sub> < 0.8V               |                 | 10              |                 | mA    |

| OVERVOLTAGE PROTECTION (Note 7)                      |                      |                                         |                 |                 |                 |       |

| OV Latching Trip Point                               |                      | EN = UGATE = LATCH Low, LGATE = High    | 118             | 120             | 122             | %     |

| OV Non-Latching Trip Point                           |                      | EN = Low, UGATE = Low, LGATE = High     |                 | 113             |                 | %     |

| LGATE Release Trip Point                             |                      | EN = Low/HIGH, UGATE = Low, LGATE = Low |                 | 87              |                 | %     |

| OVER-TEMPERATURE PROTECTION CON                      | TROLLER JUNCTIO      | N TEMPERATURE                           | T.              | I               | 1               |       |

| Over-Temperature Trip                                |                      |                                         |                 | 150             |                 | °C    |

| Over-Temperature Release Threshold                   |                      |                                         |                 | 125             |                 | °C    |

| INTERNAL COMPONENT VALUES                            |                      |                                         | -               |                 |                 |       |

| Internal Resistor Between PVCC and VCC pin           | R <sub>CC</sub>      |                                         |                 | 5               |                 | Ω     |

| Internal Resistor Between PHASE and OCSET Pins       | R <sub>ISEN-IN</sub> |                                         |                 | 2.2k            |                 | Ω     |

| Internal Resistor Between FSYNC_IN and PGND1 Pins    | R <sub>FS</sub>      |                                         |                 | 59k             |                 | Ω     |

| Internal Resistor Between PGOOD and VCC Pins         | R <sub>PG</sub>      |                                         |                 | <b>1</b> 0k     |                 | Ω     |

| Internal Resistor Between CLKOUT and VCC Pins        | R <sub>CLK</sub>     |                                         |                 | <b>10</b> k     |                 | Ω     |

| Internal Resistor Between PH_CNTRL and VCC Pins      | R <sub>PHC</sub>     |                                         |                 | <b>1</b> 0k     |                 | Ω     |

| Internal Resistor Between VOUT_SET and VSEN_REM- pin | R <sub>OS1</sub>     |                                         |                 | 2.2k            |                 | Ω     |

#### NOTES:

<sup>6.</sup> Parameters with TYP limits are not production tested, unless otherwise specified.

<sup>7.</sup> Parameters with MIN and/or MAX limits are 100% tested for internal IC prior to module assembly, unless otherwise specified. Temperature limits established by characterization and are not production tested.

FIGURE 5. TEST CIRCUIT FOR ALL PERFORMANCE AND DERATING GRAPHS

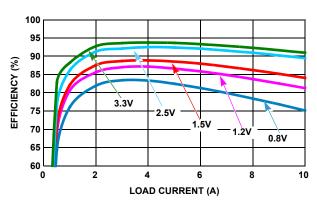

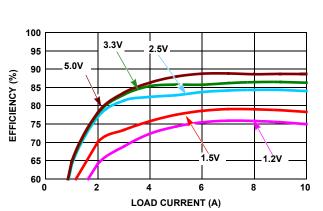

# **Typical Performance Characteristics**

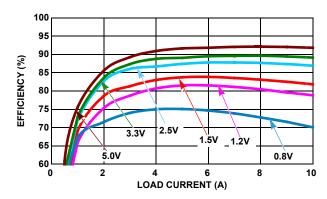

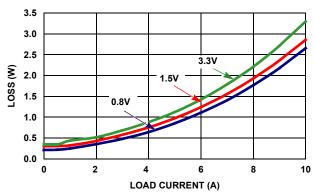

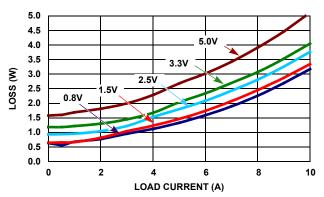

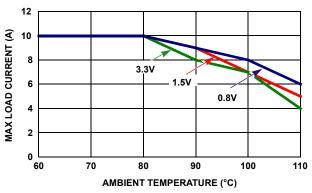

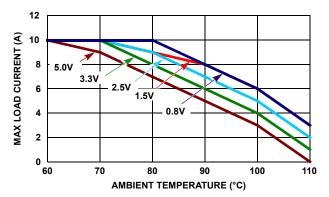

**Efficiency Performance**  $T_A = +25 \,^{\circ}\text{C}$ ,  $PV_{IN} = V_{IN}$ ,  $C_{IN} = 220 \,\mu\text{Fx1}$ ,  $10 \,\mu\text{F/Ceramic}$  x 2,  $C_{OUT} = 47 \,\mu\text{F/Ceramic}$  x 8.

FIGURE 6. EFFICIENCY vs LOAD CURRENT (5VIN)

FIGURE 8. EFFICIENCY vs LOAD CURRENT (20VIN)

FIGURE 7. EFFICIENCY vs LOAD CURRENT (12VIN)

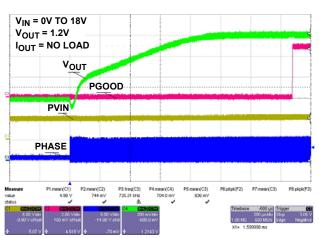

FIGURE 9. 1.2V TRANSIENT RESPONSE

# **Typical Performance Characteristics (Continued)**

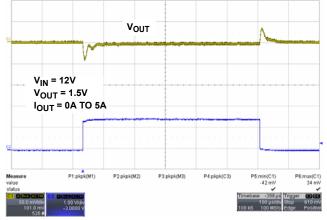

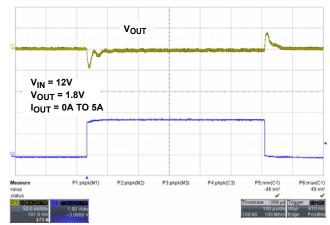

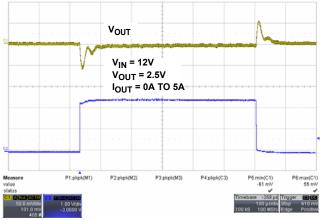

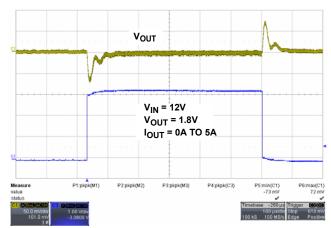

**Transient Response Performance**  $T_A = +25\,^{\circ}\text{C}$ , PV<sub>IN</sub> = V<sub>IN</sub> = 12V,  $C_{\text{IN}} = 220\,\mu\text{Fx1}$ ,  $10\,\mu\text{F/Ceramic}$  x 2,  $C_{\text{OUT}} = 47\,\mu\text{F/Ceramic}$  x 8  $I_{\text{OUT}} = 0A$  to 5A, Current slew rate = 2.5A/ $\mu$ s

FIGURE 10. 1.5V TRANSIENT RESPONSE

FIGURE 11. 1.8V TRANSIENT RESPONSE

FIGURE 12. 2.5V TRANSIENT RESPONSE

FIGURE 13. 3.3V TRANSIENT RESPONSE

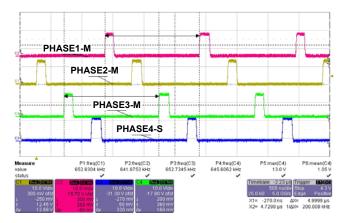

FIGURE 14. FOUR MODULE CLOCK SYNC (VIN = 12V)

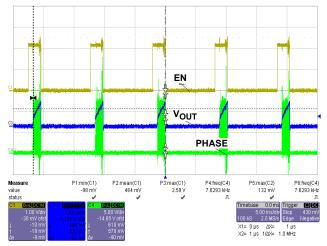

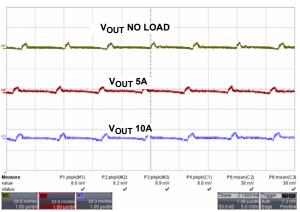

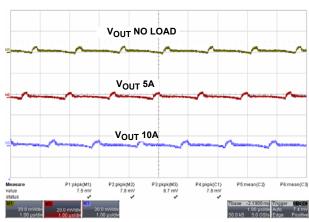

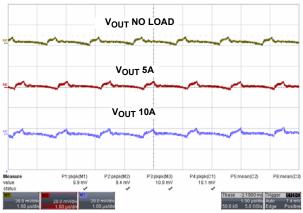

# **Typical Performance Characteristics (Continued)**

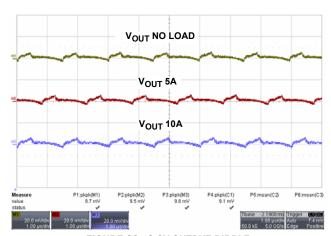

Output Ripple Performance  $T_A = +25\,^{\circ}\text{C}$ ,  $PV_{IN} = V_{IN} = 12\text{V}$ ,  $C_{IN} = 220\mu\text{Fx1}$ ,  $10\mu\text{F/Ceramic x 2}$ ,  $C_{OUT} = 100\mu\text{F/Ceramic x 6 I}_{OUT} = \text{No Load, 5, 10A}$

FIGURE 15. OVERCURRENT PROTECTION

FIGURE 16. 50% PRE-BIAS START UP

FIGURE 17. 1.2V OUTPUT RIPPLE

FIGURE 18. 1.5V OUTPUT RIPPLE

FIGURE 19. 2.5V OUTPUT RIPPLE

FIGURE 20. 3.3V OUTPUT RIPPLE

# **Applications Information**

### **Programming the Output Voltage (RSET)**

The ISL8200AM has an internal 0.6V  $\pm$  0.7% reference voltage. Programming the output voltage requires a dividing resistor (R<sub>SET</sub>) between the VOUT\_SET pin and the V<sub>OUT</sub> regulation point. The output voltage can be calculated as shown in Equation 1:

$$V_{OUT} = 0.6 \times \left(1 + \frac{R_{SET}}{R_{OS}}\right)$$

(EQ. 1)

Note: ISL8200AM has integrated  $2.2k\Omega$  resistances into the module dividing resistor for the bottom side (R<sub>OS</sub>). The resistances for different output voltages in single phase operation are listed in Table 1.

TABLE 1. VOUT - RSET

| V <sub>OUT</sub> | 0.6V | 0.8V | 1.0V   | 1.2V  |

|------------------|------|------|--------|-------|

| R <sub>SET</sub> | Ω0   | 732Ω | 1.47kΩ | 2.2kΩ |

| V <sub>OUT</sub> | 1.5V   | 1.8V   | 2.0V   | 2.5V   |

|------------------|--------|--------|--------|--------|

| R <sub>SET</sub> | 3.32kΩ | 4.42kΩ | 5.11kΩ | 6.98kΩ |

| V <sub>OUT</sub> | 3.3V | 5.0V   | 6.0V |

|------------------|------|--------|------|

| R <sub>SET</sub> | 10kΩ | 16.2kΩ | 20kΩ |

The output voltage accuracy can be improved by maintaining the impedance at V<sub>OUTSET</sub> (internal V<sub>SEN1+</sub>) at or below 1k $\Omega$  effective impedance. Note: the impedance between V<sub>SEN1+</sub> and V<sub>SEN1-</sub> is about 500k $\Omega$ .

The module has a minimum input voltage at a given output voltage, which needs to be a minimum of 1.43 times the output voltage if operating at  $F_{SW}$  = 700kHz switching frequency. This is due to the Minimum PWM OFF Time ( $t_{MIN-OFF}$ ).

The equation to determine the minimum  $PV_{IN}$  to support the required  $V_{OUT}$  is given by Equations 2 and 3; it is recommended to add 0.5V to the result to account for temperature variations.

$$PV_{IN\_MIN} = \frac{v_{OUT} \times t_{SW}}{t_{SW} - t_{MIN\_OFF}}$$

(EQ. 2)

$t_{SW}$  = switching period =  $1/F_{SW}$

for the 700kHz switching frequency = 1428ns

$$PV_{IN\ MIN} = 1.43 \times V_{OUT}$$

(EQ. 3)

For 3.3V input voltage operation, the VIN voltage is recommended to be 5V for sufficient gate drive voltage. This can be accomplished by using a voltage greater than or equal to 5V on VIN, or directly connecting the 5V source to both VIN and PVCC.

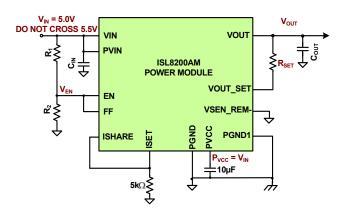

VIN is the input to the internal LDO that powers the control circuitry while PVCC is the output of the aforementioned LDO. PVIN is the power input to the power stage. Figure 21 shows a scenario where the power stage is running at 3.3V and the control circuitry is running at 5.0V; keep in mind that the PVCC pin is also at 5.0V to ensure that the LDO is not functioning. Figure 22 shows a setup where both the control circuitry and the power stage is at a 5.0V rail. It is imperative to not cross 5.5V in

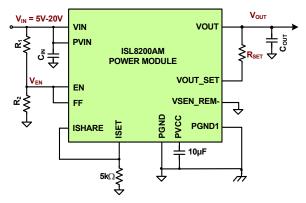

this setup as that is the voltage limit on the PVCC pin. Figure 23 is a more general setup and can accommodate VIN ranges up to 20V; PVCC is not tied to VIN and hence the control circuitry is powered by the internal LDO.

The circuit shown in Figure 24 ensures proper startup by injecting current into the ISHARE line until all phases are ready to start regulating.

FIGURE 21. 3.3V OPERATION

FIGURE 22. 5.0V OPERATION

FIGURE 23. 5V TO 20V OPERATION

#### **Selection of the Input Capacitor**

The input filter capacitor should be based on how much ripple the supply can tolerate on the DC input line. The larger the capacitor, the less ripple expected, but consideration should be taken for the higher surge current during power-up. The ISL8200AM provides the soft-start function that controls and limits the current surge. The value of the input capacitor can be calculated by Equation 4:

$$C_{IN(MIN)} = I_0 \bullet \frac{D \bullet (1-D)}{V_{P-P(MAX)} \bullet F_S}$$

(EQ. 4)

Where:

$C_{\text{IN}(\text{MIN})}$  is the minimum input capacitance (µF) required

In is the output current (A)

D is the duty cycle  $(V_0/V_{IN})$

V<sub>P-P(MAX)</sub> is the maximum peak-to-peak voltage (V)

F<sub>S</sub> is the switching frequency (Hz)

In addition to the bulk capacitance, some low Equivalent Series Inductance (ESL) ceramic capacitance is recommended to decouple between the drain terminal of the high side MOSFET and the source terminal of the low side MOSFET. This is used to reduce the voltage ringing created by the switching current across parasitic circuit elements.

#### **Output Capacitors**

The ISL8200AM is designed for low output voltage ripple. The output voltage ripple and transient requirements can be met with bulk output capacitors ( $C_{OUT}$ ) with low enough Equivalent Series Resistance (ESR); the recommended ESR is <10m $\Omega$ . When the total ESR is below  $4m\Omega$ , a capacitor ( $C_{FF}$ ) between 2.2nF-10nF is recommended;  $C_{FF}$  is placed in parallel with RSET, in between the VOUT and VOUT\_SET pin.  $C_{OUT}$  can be a low ESR tantalum capacitor, a low ESR polymer capacitor or a ceramic capacitor. The typical capacitance is  $330\mu F$  and decoupled ceramic output capacitors are used per phase. The internally optimized loop compensation provides sufficient stability margins for all ceramic capacitor applications with a recommended total value of  $300\mu F$  per phase. Additional output filtering may be needed if further reduction of output ripple or dynamic transient spike is required.

#### **Using Multiple Phases**

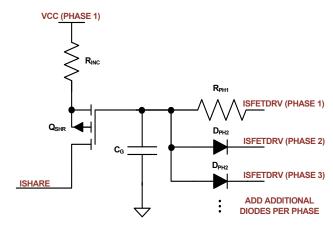

The ISL8200AM can be easily connected in parallel with other ISL8200AM modules and current share providing an additional 10A per phase. For 2 phases, simply follow the schematic shown in Figure 4. A rough summary shows that the modules share VIN, VOUT, GND and have their ISHARE pins tied together with a  $10 \mathrm{k}\Omega$  resistor to ground (per phase). When using 3 phases or more, it is recommended that you add the following circuitry (see Figure 24) to ensure proper startup. The circuit shown in Figure 24 ensures proper startup by injecting current into the ISHARE line until all phases are ready to start regulating. For additional phases, the RC time constant, using  $R_{INC}$  and  $C_G$ , might have to be adjusted to increase the turn on time of the PFET (QSHR). For 3-4 phases, these are the values,  $R_{INC}$  = 243k,  $R_{PH1}$  = 15k,  $Q_{SHR}$  = Small Signal PFET,  $C_G$  = 22nF).

FIGURE 24. STARTUP CIRCUITRY

# **Functional Description**

#### Initialization

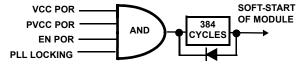

The ISL8200AM requires VCC and PVCC to be biased by a single supply. Power-On Reset (POR) circuits continually monitor the bias voltages (PVCC and VCC) and the voltage at the EN pin. The POR function initiates soft-start operation 384 clock cycles after the EN pin voltage is pulled to be above 0.8V; all input supplies exceed their POR thresholds and the PLL locking time expires. The enable pin can be used as a voltage monitor and to set desired hysteresis with an internal 30µA sinking current going through an external resistor divider. The sinking current is disengaged after the system is enabled. This feature is especially designed for applications that require higher input rail POR for better undervoltage protection. For example, in 12V applications,  $R_{UP}$  = 53.6k and  $R_{DOWN}$  = 5.23k will set the turn-on threshold (V<sub>EN RTH</sub>) to 10.6V and turn-off threshold (V<sub>EN FTH</sub>) to 9V, with 1.6V hysteresis (V<sub>EN HYS</sub>). These numbers are explained in Figure 29 on page 15.

During shutdown or fault conditions, the soft-start is quickly reset while UGATE and LGATE immediately change state (<100ns) upon the input dropping below POR.

HIGH = ABOVE POR; LOW = BELOW POR

FIGURE 25. SOFT-START INITIALIZATION LOGIC

#### **Soft-Start**

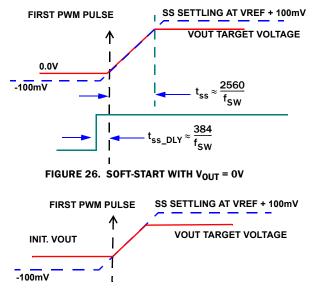

The ISL8200AM has an internal digital pre-charged soft-start circuitry, which has a rise time inversely proportional to the switching frequency and is determined by a digital counter that increments with every pulse of the phase clock. The full soft-start time from OV to 0.6V can be estimated by Equation 5.

$$t_{SS} = \frac{2560}{f_{SW}} \tag{EQ. 5}$$

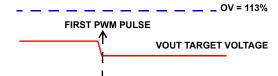

The ISL8200AM has the ability to work under a pre-charged output. The PWM outputs will not be fed to the drivers until the first PWM pulse is seen. The low side MOSFET is held low for the first clock cycle to provide charge for the bootstrap capacitor. If the pre-charged output voltage is greater than the final target level but less than the 113% setpoint, switching will not start until the output voltage is reduced to the target voltage and the first PWM pulse is generated. The maximum allowable pre-charged level is 113%. If the pre-charged level is above 113% but below 120%, the output will hiccup between 113% (LGATE turns on) and 87% (LGATE turns off) while EN is pulled low. If the pre-charged load voltage is above 120% of the targeted output voltage, then the controller will be latched off and not be able to power-up.

FIGURE 27. SOFT-START WITH V<sub>OUT</sub> < TARGET VOLTAGE

FIGURE 28. SOFT-START WITH  $V_{OUT}$  BELOW OV BUT ABOVE FINAL TARGET VOLTAGE

#### **Voltage Feedforward**

The voltage applied to the FF pin is fed to adjust the sawtooth amplitude of the channel. The amplitude the sawtooth is set to is 1.25 times the corresponding FF voltage when the module is enabled. This configuration helps to maintain a constant gain ( $G_M = V_{IN} \cdot D_{MAX}/\Delta V_{RAMP}$ ) and input voltage to achieve optimum loop response over a wide input voltage range. The sawtooth ramp offset voltage is 1V (equal to 0.8V\*1.25), and the peak of the sawtooth is limited to  $V_{CC}$ -1.4V. With  $V_{CC}$ =5.4V, the ramp has a maximum peak-to-peak amplitude of  $V_{CC}$ -2.4V (equal to 3V); so the feed-forward voltage effective range is typically 3x as the ramp amplitude ranges from 1V to 3V.

A 384 cycle delay is added after the system reaches its rising POR and prior to the soft-start. The RC timing at the FF pin should be sufficiently small to ensure that the input bus reaches its static state and the internal ramp circuitry stabilizes before soft-start. A large RC could cause the internal ramp amplitude not to synchronize with the input bus voltage during output start-up or when recovering from faults. A 1nF capacitor is recommended as a starting value for typical applications. The voltage on the FF pin needs to be above 0.8V prior to soft-start and during PWM switching to ensure reliable regulation. In a typical application, FF pin can be shorted to the EN pin.

FIGURE 29. SIMPLIFIED ENABLE AND VOLTAGE FEEDFORWARD CIRCUIT

#### **Power Good**

The Power-Good comparators monitor the voltage on the internal VMON1 pin. The trip points are shown in Figure 30. PGOOD will not be asserted until after the completion of the soft-start cycle. The PGOOD pulls low upon both EN's disabling it or the internal VMON1 pin's voltage is out of the threshold window. PGOOD will not be asserted until after the completion of the soft-start cycle. PGOOD will not pull low until the fault is present for three consecutive clock cycles.

The UV indication is not enabled until the end of soft-start. In a UV event, if the output drops below -13% of the target level due to some reason (cases when EN is not pulled low) other than OV, OC, OT, and PLL faults, PGOOD will be pulled low.

#### **Current Share**

The IAVG\_CS is the current of the module. ISHARE and ISET pins source a copy of IAVG\_CS with 15 $\mu$ A offset, i.e., the full scale will be 126 $\mu$ A.

The share bus voltage ( $V_{ISHARE}$ ) set by an external resistor ( $R_{ISHARE} = R_{ISET}/NCTRL$ ) represents the average current of all active modules. The voltage ( $V_{ISET}$ ) set by  $R_{ISET}$  represents the average current of the corresponding module and is compared with the share bus ( $V_{ISHARE}$ ). The current share error signal (ICSH\_ER) is then fed into the current correction block to adjust each module's PWM pulse accordingly. The current share function provides at least 10% overall accuracy between ICs, up to 3 phases. The current share bus works for up to 6-phase. Figure 4 further illustrates the current sharing aspects of the ISL8200AM.

FIGURE 30. POWER-GOOD THRESHOLD WINDOW

When there is only one module in the system, the ISET and ISHARE pins can be shorted together and grounded via a single resistor to ensure zero share error - a resistor value of 5k (paralleling 10k on ISET and ISHARE) will allow operation up to the OCP level.

#### **Overvoltage Protection (OVP)**

The Overvoltage (OV) protection indication circuitry monitors the voltage on the internal VMON1 pin.

OV protection is active from the beginning of soft-start. An OV condition (>120%) would latch the IC off (the high-side MOSFET to latch off permanently; the low-side MOSFET turns on immediately at the time of OV trip and then turns off permanently after the output voltage drops below 87%). The EN and PGOOD are also latched low at OV event. The latch condition can be reset only by recycling VCC.

There is another non-latch OV protection (113% of target level). At the condition of EN low and the output over 113% OV, the lower side MOSFET will turn on until the output drops below 87%. This is to protect the overall power trains in case of a single channel of a multi-module system detecting OV. The low-side MOSFET always turns on at the conditions of EN = LOW and the output voltage above 113% (all EN pins are tied together) and turns off after the output drops below 87%. Thus, in a high phase count application (multi-module mode), all cascaded modules can latch off simultaneously via the EN pins (EN pins are tied together in multiphase mode), and each IC shares the same sink current to reduce the stress and eliminate the bouncing among phases.

#### **Over-Temperature Protection (OTP)**