# EVAL-AD7091R-5SDZ User Guide

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

#### **Evaluating the EVAL-AD7091R-5SDZ 12-Bit Monitor and Control System**

#### **FEATURES**

Full featured evaluation board for the EVAL-AD7091R-5SDZ

On-board power supplies

Standalone capability

System demonstration platform (SDP) compatible (EVAL-SDP-CB1Z)

PC software for control and data analysis (download from the AD7091R-5 product page)

#### **EVALUATION KIT CONTENTS**

Evaluation board Screw/nut kit Mains power supply adapter

#### **ADDITIONAL EQUIPMENT NEEDED**

EVAL-SDP-CB1Z (must be ordered separately)

includes a USB cable

Signal source

PC running Windows® XP SP2, Windows Vista, or Windows 7

with USB 2.0 port

#### **EVALUATION BOARD DESCRIPTION**

The EVAL-AD7091R-5SDZ is a fully featured evaluation board designed to allow you to evaluate the features of the AD7091R-5 analog-to-digital converters (ADCs). Control of the evaluation board occurs via the SDP connector (J13). The SDP board (EVAL-SDP-CB1Z) enables control of the evaluation board through the USB port of a PC using the evaluation board software available for download from the product page.

On-board components include: the ADA4805-1 low power, low noise rail-to-rail amplifier, the AD8031 high speed precision rail-to-rail op amp, the AD8032 high speed precision rail-to-rail dual op amp, the ADP3303 high accuracy 200 mA low dropout linear regulator, and the REF193 3.0 V precision micropower, low dropout, low voltage reference.

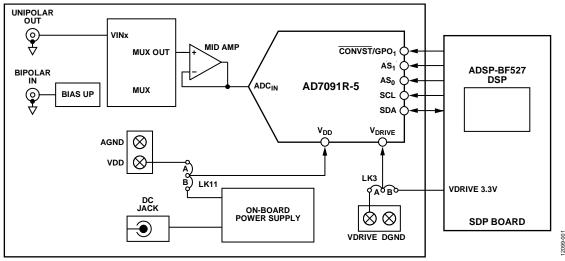

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

## EVAL-AD7091R-5SDZ User Guide

## **UG-667**

### **TABLE OF CONTENTS**

| 1 |

|---|

| 1 |

| 1 |

| 1 |

| 1 |

| 2 |

| 3 |

| 4 |

| 4 |

| 4 |

| 4 |

| 7 |

| 7 |

| 7 |

| 8 |

|   |

|   | Software instanation                   | 0    |

|---|----------------------------------------|------|

|   | Launching the Software                 | . 10 |

|   | Description of Main Window             | . 11 |

|   | Waveform Capture                       | . 12 |

|   | AC Testing—Histogram                   | . 13 |

|   | DC Testing—Histogram                   | . 13 |

|   | AC Testing—FFT Capture                 | . 14 |

|   | Summary Tab                            | . 15 |

|   | Read Register Tab                      | . 15 |

|   | Dynamic Power Scaling                  | . 16 |

|   | Saving Files                           | . 17 |

|   | Opening Files                          | . 18 |

| E | valuation Board Schematics and Artwork | . 19 |

#### **REVISION HISTORY**

7/15—Revision 0: Initial Version

#### **QUICK START GUIDE**

Follow these steps to quickly evaluate the AD7091R-5 ADC:

- Install the evaluation software from the AD7091R-5

product page. Ensure that the EVAL-SDP-CB1Z board is

disconnected from the USB port of the PC while installing

the software. The PC may need to be restarted after the

installation.

- 2. Ensure that the various link options are configured as outlined in Table 2.

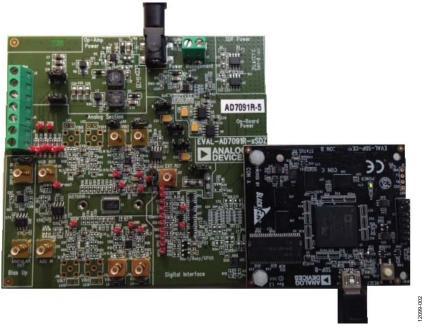

- 3. Connect the EVAL-SDP-CB1Z board to the evaluation board as shown in Figure 2. Screw the two boards together using the enclosed nylon screw/nut set to ensure that the boards connect firmly together.

- 4. Connect the power supply adapter included in the kit to Connecter J1 on the evaluation board.

- Connect the EVAL-SDP-CB1Z board to the PC via the USB cable. For Windows\* XP, you may need to search for the EVAL-SDP-CB1Z drivers. Choose to automatically search for the drivers for the EVAL-SDP-CB1Z board if prompted by the operating system.

- 6. Launch the evaluation software from the **Analog Devices** subfolder in the **Programs** menu.

- 7. Connect an input signal via either the BIPOLAR IN/ UNIPOLAR OUT connectors, J10 and J14, or any of the unipolar channel inputs, J7, J8, J18, or J19.

Figure 2. Evaluation Board (Left) Connected to the SDP Board (Right)

## EVALUATION BOARD HARDWARE DEVICE DESCRIPTION

This user guide describes the evaluation board for the AD7091R-5 ADC. The AD7091R-5 is a 12-bit, ultralow power, successive approximation ADC. The device operates from a single 2.7 V to 5.25 V power supply. This ADC features an on-chip conversion clock, an accurate reference, and an I $^2$ C interface that operates in both standard ( $f_{SCL} = 100 \text{ kHz}$ ) and fast ( $f_{SCL} = 400 \text{ kHz}$ ) modes.

The conversion process and data acquisition are controlled using the I²C interface and an internal oscillator. The AD7091R-5 interface allows for data read after the conversion, achieving a maximum 22.22 kSPS throughput rate in fast mode. This device uses advanced design and process techniques to achieve ultralow power dissipation without compromising performance. An on-chip, accurate 2.5 V reference is available.

Complete specifications for the AD7091R-5 are provided in the device data sheet, available from Analog Devices, Inc., which should be consulted in conjunction with this user guide when using the evaluation board. Full details on the EVAL-SDP-CB1Z are available online.

#### HARDWARE LINK OPTIONS

The functions of the link options are described in Table 2. The default setup is configured to operate the board with the mains power supply adapter and to interface to the EVAL-SDP-CB1Z board.

#### **POWER SUPPLIES**

Take care before applying power and signals to the evaluation board to ensure that all link positions are set according to the required operating mode. See Table 2 for the complete list of link options.

This evaluation board is supplied with a wall-mountable switching power supply that provides 9 V dc output. Connect the supply to a 100 V to 240 V ac wall outlet at 50 Hz to 60 Hz. The output from the supply is provided through a 2.0 mm inner diameter jack that connects to the evaluation board at J1. The 9 V supply is connected to the on-board 5 V linear regulator that supplies the correct bias to each of the various sections on the evaluation board and on the EVAL-SDP-CB1Z board.

When using this evaluation board with the EVAL-SDP-CB1Z board, it is necessary to power the board through the J1 connector.

If the evaluation board is used without the 9 V adapter, an external power supply in the range of 2.7 V to 5.25 V must be connected to the  $V_{DD}$  input to supply the AD7091R-5  $V_{DD}$  pin. In addition, an external supply in the range of 1.8 V to 5.25 V must be connected to the  $V_{DRIVE}$  input to supply the  $V_{DRIVE}$  pin.

Each supply is decoupled on this board using 10  $\mu F$  tantalum and 100 nF multilayer ceramic capacitors.

There are two main ground planes, AGND and DGND. These are connected at one location close to the ADC.

#### **Caution**

When the EVAL-AD7091R-5SDZ is connected to the EVAL-SDP-CB1Z, take care to ensure that, if an external voltage is supplied to the  $V_{\text{DRIVE}}$  input connector, J4, the voltage does not exceed 3.3 V. Otherwise, permanent damage may occur to the EVAL-SDP-CB1Z board.

Table 1. External Power Supplies Required

| Power Supply | Voltage Range    | Purpose                                             |

|--------------|------------------|-----------------------------------------------------|

| DC Jack      | 9 V ± 5%         | Supplies power to on-board power management devices |

| $V_{DD}$     | 2.7 V to 5.25 V  | Analog supply rail                                  |

| $V_{DRIVE}$  | 1.65 V to 5.25 V | Digital supply rail without EVAL-SDP-CB1Z connected |

|              | 3.3 V ± 5%       | Digital supply rail with EVAL-SDP-CB1Z connected    |

**Table 2. Link Options**

| Category        | Link | Default<br>Position | Function                                                                                                    |

|-----------------|------|---------------------|-------------------------------------------------------------------------------------------------------------|

| Power           | LK1  | Α                   | This link is used to select the op amp positive supply source.                                              |

| Supplies        |      |                     | In Position A, the positive supply is generated from the 9 V dc jack plug.                                  |

|                 |      |                     | In Position B, the positive supply is provided by the J3-3 connector.                                       |

|                 | LK2  | Α                   | This link is used to select the op amp negative supply source.                                              |

|                 |      |                     | In Position A, the negative supply is generated from the 9 V dc jack plug.                                  |

|                 |      |                     | In Position B, the negative supply is provided by the J3-1 connector.                                       |

|                 | LK3  | Α                   | This link is used to select the source of the V <sub>DRIVE</sub> supply for the AD7091R-5.                  |

|                 |      |                     | In Position A, the V <sub>DRIVE</sub> supply is sourced from the on-board 5 V regulator.                    |

|                 |      |                     | In Position B, the V <sub>DRIVE</sub> supply is sourced externally via the J4-1 connector.                  |

|                 | LK4  | Α                   | This link is used to select the source of the V <sub>DRIVE</sub> supply for the AD7091R-5.                  |

|                 |      |                     | In Position A, the V <sub>DRIVE</sub> supply is sourced from the on-board regulators or the J4-1 connector. |

|                 |      |                     | In Position B, the V <sub>DRIVE</sub> supply is sourced from the SDP connector J13.                         |

| Termination     | LK6  | Inserted            | Adds a 51 $\Omega$ termination resistor to AGND at VIN2.                                                    |

|                 |      |                     | Inserted—51 Ω termination on the VIN2 input.                                                                |

|                 |      |                     | Not inserted—no 51 $\Omega$ termination on the VIN2 input.                                                  |

|                 | LK7  | Inserted            | Adds a 51 $\Omega$ termination resistor to AGND at VINO.                                                    |

|                 |      |                     | Inserted—51 Ω termination on the VIN0 input.                                                                |

|                 |      |                     | Not inserted—no 51 $\Omega$ termination on the VIN0 input.                                                  |

| Power           | LK8  | В                   | This link is used to select the source of the V <sub>DRIVE</sub> supply for the AD7091R-5.                  |

| Supplies        |      |                     | In Position A, the V <sub>DRIVE</sub> supply is sourced from the on-board 5 V regulator or J9-1.            |

|                 |      |                     | In Position B, the V <sub>DRIVE</sub> supply is sourced from the on-board 3.3 V regulator.                  |

|                 | LK9  | Α                   | This link is used to select the source of the V <sub>DD</sub> supply for the AD7091R-5.                     |

|                 |      |                     | In Position A, the V <sub>DD</sub> supply is sourced from the on-board 5 V regulator.                       |

|                 |      |                     | In Position B, the V <sub>DD</sub> supply is sourced externally via the J1 connector.                       |

| Termination     | LK10 | Inserted            | Adds a 51 $\Omega$ termination resistor to AGND at BIPOLAR IN.                                              |

|                 |      |                     | Inserted—51 Ω termination on the BIPOLAR IN input.                                                          |

|                 |      |                     | Not inserted—no 51 Ω termination on the BIPOLAR IN input.                                                   |

| Power           | LK11 | В                   | This link is used to select the source of the V <sub>DD</sub> supply for the AD7091R-5.                     |

| Supplies        |      |                     | In Position A, the V <sub>DD</sub> supply is sourced from either the on-board 5 V regulator or J9-1.        |

|                 |      |                     | In Position B, the V <sub>DD</sub> supply is sourced from the on-board 3.3 V regulator.                     |

| Reference Input | LK12 | Not                 | This link is used to select the source of the reference input for the AD7091R-5.                            |

| ·               |      | Inserted            | Inserted—reference voltage is generated by REF193.                                                          |

|                 |      |                     | Not inserted—reference either generated internally by AD7091R-5 or provided by the J12                      |

|                 |      |                     | connector.                                                                                                  |

| Analog Input    | LK13 | В                   | This link is used to select the connection option for the MUX <sub>OUT</sub> pin.                           |

|                 |      |                     | In Position A, the MUX <sub>OUT</sub> pin is connected to Pin 3 of U16.                                     |

|                 |      |                     | In Position B, the MUX <sub>OUT</sub> pin is connected to Pin 3 of U15.                                     |

|                 |      |                     | In Position C, the MUX <sub>OUT</sub> pin is connected directly to LK14.                                    |

|                 | LK14 | В                   | This link is used to select the source of the ADC <sub>IN</sub> input for the AD7091R-5.                    |

|                 |      |                     | In Position A, the ADC <sub>IN</sub> pin is sourced from U16.                                               |

|                 |      |                     | In Position B, the ADC <sub>IN</sub> pin is sourced from U15.                                               |

|                 |      |                     | In Position C, the ADC <sub>IN</sub> pin is sourced directly from Position C of LK13.                       |

| Termination     | LK17 | Inserted            | Adds a 51 Ω termination resistor to AGND at VIN3.                                                           |

|                 | ,    |                     | Inserted—51 $\Omega$ termination on the VIN3 input.                                                         |

|                 |      |                     | Not inserted—no 51 $\Omega$ termination on the VIN3 input.                                                  |

|                 | LK18 | Inserted            | Adds a 51 $\Omega$ termination resistor to AGND at VIN1.                                                    |

|                 | •    |                     | Inserted—51 $\Omega$ termination on the VIN1 input.                                                         |

|                 |      |                     | Not inserted—no 51 $\Omega$ termination on the VIN1 input.                                                  |

## UG-667

|               |      | Default  |                                                                                              |

|---------------|------|----------|----------------------------------------------------------------------------------------------|

| Category      | Link | Position | Function                                                                                     |

| Analog Input  | SL1  | В        | This link is used in conjunction with SL2 to select the buffering option for the VINO input. |

|               |      |          | In Position A, the VINO input signal is buffered by U9-A.                                    |

|               |      |          | In Position B, the VINO input signal bypasses the U9-A buffer.                               |

|               | SL2  | В        | This link is used in conjunction with SL1 to select the buffering option for the VINO input. |

|               |      |          | In Position A, the VINO input signal is buffered by U9-A.                                    |

|               |      |          | In Position B, the VINO input signal bypasses the U9-A buffer.                               |

|               | SL3  | В        | This link is used in conjunction with SL4 to select the buffering option for the VIN1 input. |

|               |      |          | In Position A, the VIN1 input signal is buffered by U25-B.                                   |

|               |      |          | In Position B, the VIN1 input signal bypasses the U25-B buffer.                              |

|               | SL4  | В        | This link is used in conjunction with SL3 to select the buffering option for the VIN1 input. |

|               |      |          | In Position A, the VIN1 input signal is buffered by U25-B.                                   |

|               |      |          | In Position B, the VIN1 input signal bypasses the U25-B buffer.                              |

|               | SL5  | В        | This link is used in conjunction with SL6 to select the buffering option for the VIN2 input. |

|               |      |          | In Position A, the VIN2 input signal is buffered by U9-B.                                    |

|               |      |          | In Position B, the VIN2 input signal bypasses the U9-B buffer.                               |

|               | SL6  | В        | This link is used in conjunction with SL5 to select the buffering option for the VIN2 input. |

|               |      |          | In Position A, the VIN2 input signal is buffered by U9-B.                                    |

|               |      |          | In Position B, the VIN2 input signal bypasses the U9-B buffer.                               |

|               | SL7  | В        | This link is used in conjunction with SL8 to select the buffering option for the VIN3 input. |

|               |      |          | In Position A, the VIN3 input signal is buffered by U25-A.                                   |

|               |      |          | In Position B, the VIN3 input signal bypasses the U25-A buffer.                              |

|               | SL8  | В        | This link is used in conjunction with SL7 to select the buffering option for the VIN3 input. |

|               |      |          | In Position A, the VIN3 input signal is buffered by U25-A.                                   |

|               |      |          | In Position B, the VIN3 input signal bypasses the U25-A buffer.                              |

| Digital Input | SL17 | Α        | This link determines the logic value of AS <sub>1</sub> .                                    |

|               |      |          | In Position A, AS <sub>1</sub> has a logic value of 0.                                       |

|               |      |          | In Position B, AS <sub>1</sub> has a logic value of 1.                                       |

|               | SL18 | В        | This link determines the logic value of AS <sub>0</sub> .                                    |

|               |      |          | In Position A, AS₀ has a logic value of 1.                                                   |

|               |      |          | In Position B, AS₀ has a logic value of 0.                                                   |

#### SOCKETS/CONNECTORS

The connectors and sockets on the EVAL-AD7091R-5SDZ are outlined in Table 3.

Table 3. On-Board Connectors

| Connector | Function                                                 |

|-----------|----------------------------------------------------------|

| J1        | 9 V, 2.0 mm dc jack connector                            |

| J2        | External PWR_IN and GND power connector                  |

| J3        | External OP_AMP_POS, OP_AMP_NEG, and GND power connector |

| J4        | External VDRIVE and GND power connector                  |

| J7        | VIN2 analog input signal                                 |

| J8        | VINO analog input signal                                 |

| J9        | External VDD and GND power connector                     |

| J10       | BIPOLAR IN analog input signal to bias up circuit        |

| J11       | MUX <sub>OUT</sub> signal from output of multiplexer     |

| J12       | External reference voltage connector                     |

| J13       | 120-way connector for EVAL-SDP-CB1Z interface            |

| J14       | UNIPOLAR OUT analog signal from bias up circuit          |

| J15       | ADC <sub>IN</sub> analog input signal                    |

| J18       | VIN3 analog input signal                                 |

| J19       | VIN1 analog input signal                                 |

The default interface to this evaluation board is via the 120-way connector, which connects the EVAL-AD7091R-5SDZ to the EVAL-SDP-CB1Z board.

#### **TEST POINTS**

There are numerous test points on the EVAL-AD7091R-5SDZ boards. These test points provide easy access to the signals from the evaluation board for probing, evaluation, and debugging.

It is also possible to access the AD7091R-5 devices via the test points to operate the evaluation board in standalone mode without the need for the EVAL-SDP-CB1Z board.

#### BASIC HARDWARE SETUP

The EVAL-AD7091R-5SDZ connects to the EVAL-SDP-CB1Z system demonstration platform (SDP) board. The EVAL-SDP-CB1Z board is the controller board, which is the communication link between the PC and the main evaluation board.

Figure 2 shows a photograph of the connections between the EVAL-AD7091R-5SDZ daughter board and the EVAL-SDP-CB1Z board.

The analog input range to the AD7091R-5 devices is 0 V to  $V_{\text{REF}}$  and should not be exceeded. When using the on-chip reference,  $V_{\text{REF}}$  is 2.5 V. Connect an input signal in the range of 2.5 V p-p to the evaluation board via any analog input connector.

If an input signal is bipolar, it should be connected to BIPOLAR IN, the J10 connector. This signal is biased to  $V_{\text{REF}}/2$  via the bias up circuitry on the EVAL-AD7091R-5SDZ. The signal source should be a low impedance source. Connection of the properly biased signal to any unipolar analog input occurs by connecting UNIPOLAR OUT, the J14 connector, to any connector (J7, J8, J18, or J19). On-board unity gain amplifiers buffer the signal to the ADC. This is the default configuration on the evaluation board.

A unipolar input signal directly connects to any multiplexer input, VIN0 to VIN3, the J7, J8, J18, or J19 connectors. Onboard unity gain amplifiers buffer the signal to the AD7091R-5.

Before connecting power, connect the EVAL-AD7091R-5SDZ to Connector A on the EVAL-SDP-CB1Z board. A nylon screw/nut set is included in the evaluation kit and can be used to ensure that the evaluation board and the EVAL-SDP-CB1Z boards are connected firmly together.

Ensure that the link options are in the default positions as outlined in Table 2.

After the EVAL-AD7091R-5SDZ and the EVAL-SDP-CB1Z board are securely linked, connect the power to the evaluation board. The evaluation board requires an external power supply adapter, which is included in the evaluation board kit. Connect this power supply to Connector J1 on the evaluation board. For further details on the required power supply connections and options, see the Power Supplies section.

Before connecting the EVAL-SDP-CB1Z board to your PC, ensure installation of the evaluation software. Details of the full software installation procedure are located in the Evaluation Board Software section.

Finally, connect the EVAL-SDP-CB1Z board to the PC via the USB cable enclosed in the EVAL-SDP-CB1Z kit. If using a Windows XP platform, you may need to search for the EVAL-SDP-CB1Z drivers. Choose to automatically search for the drivers for the EVAL-SDP-CB1Z board if prompted by the operating system.

## EVALUATION BOARD SOFTWARE SOFTWARE INSTALLATION

The EVAL-AD7091R-5SDZ kit includes software available for download from the AD7091R-5 product page.

- Start the Windows operating system and download the evaluation software from the AD7091R-5 product page.

- 2. Unzip the downloaded file.

- 3. Double-click the **setup.exe** file to run the install. The default location for the software is

- C:\Program Files\Analog Devices\AD7091R-5\

- Power up the evaluation board as described in the Power Supplies section.

- 5. Connect the evaluation board and the EVAL-SDP-CB1Z board to the USB port of the PC to ensure that the evaluation system is correctly recognized when connected to the PC.

- When the software detects the evaluation board, proceed through any dialog boxes that appear to finalize the installation.

There are two parts to the installation:

- EVAL-AD7091R-5SDZ evaluation software installation

- EVAL-SDP-CB1Z system demonstration platform board drivers installation

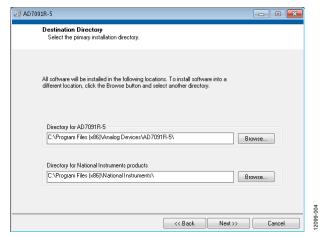

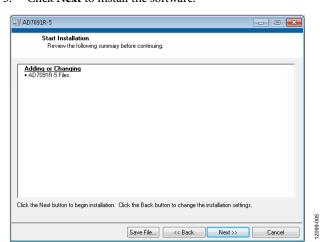

Follow Step 1 to Step 4 (see Figure 3 to Figure 6) to install the evaluation board software. Follow Step 5 to Step 8 (see Figure 7 to Figure 10) to install the EVAL-SDP-CB1Z drivers. Proceed through all of the installation steps, allowing the software and drivers to be placed in the appropriate locations. Connect the EVAL-SDP-CB1Z board to the PC only after the software and drivers have been installed.

1. Click **Yes** to begin the installation process.

Figure 3. Evaluation Software Installation—User Account Control

Select the installation directory. Click Next.

Figure 4. Evaluation Software Installation—Destination Directory

3. Click **Next** to install the software.

Figure 5. Evaluation Software Installation—Start Installation

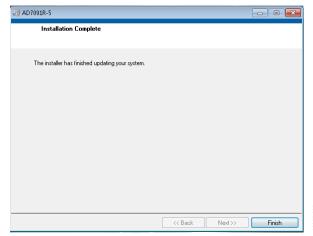

4. The installation of the evaluation software completes. Click **Finish** to proceed with the installation of the drivers.

Figure 6. Evaluation Software Installation—Installation Complete

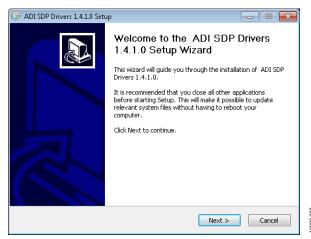

The setup wizard opens. Click **Next** to begin the driver installation process.

Figure 7. EVAL-SDP-CB1Z Drivers Installation—Setup Wizard

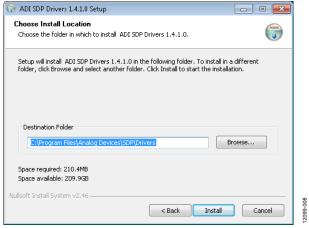

Select a destination folder for the SDP drivers, and click Install.

Figure 8. EVAL-SDP-CB1Z Drivers Installation—Choose Install Location

7. Click **Install** to proceed with the installation.

Figure 9. EVAL-SDP-CB1Z Drivers Installation—Windows Security

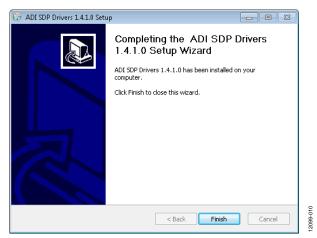

Click Finish.

Figure 10. EVAL-SDP-CB1Z Drivers Installation—Complete

After the evaluation software installation is complete, connect the EVAL-AD7091R-5SDZ board to the EVAL-SDP-CB1Z board as described in the Evaluation Board Hardware section.

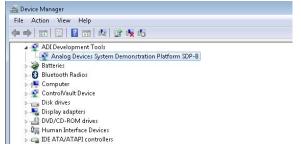

When you first plug in the EVAL-SDP-CB1Z board via the USB cable provided, allow the Found Hardware Wizard to run. After the drivers are installed, you can check that the board is connected correctly by looking at the Device Manager of the PC. The Device Manager can be found by right-clicking My Computer > Manage > Device Manager from the list of System Tools as shown in Figure 11.

The EVAL-SDP-CB1Z SDP-B board should appear under **ADI Development Tools**. This completes the installation.

Figure 11. Device Manager

#### **LAUNCHING THE SOFTWARE**

After the evaluation board and EVAL-SDP-CB1Z board are correctly connected to your PC, the evaluation software can be launched.

From the **Start** menu, select **Programs** > **Analog Devices** > **AD7091R-5.** The main window of the software then opens (see Figure 13).

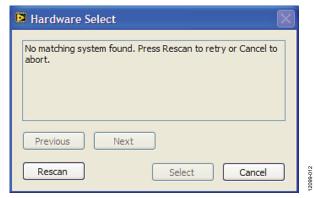

If the evaluation board is not connected to the USB port via the EVAL-SDP-CB1Z when the software is launched, a connectivity error displays (see Figure 12). Connect the evaluation board to the USB port of the PC, wait a few seconds, click **Rescan**, and follow the instructions.

Figure 12. Connectivity Error Alert

Figure 13. Evaluation Software Main Window

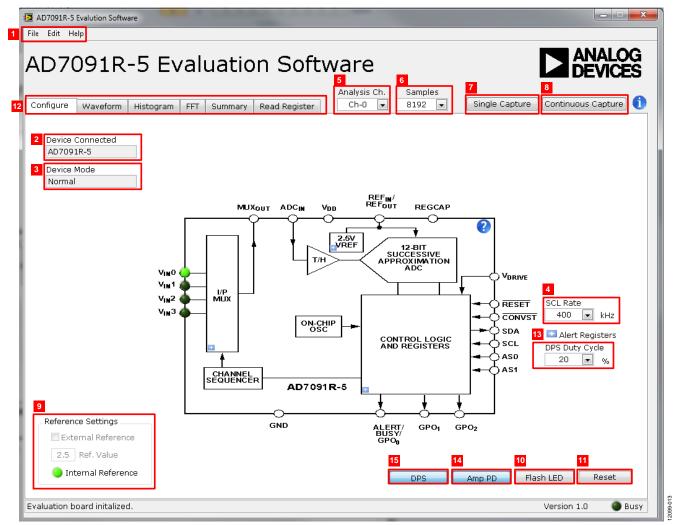

#### **DESCRIPTION OF MAIN WINDOW**

The following tools allow user control of the different chart displays. When the software is launched, the main software window opens (see Figure 13).

The user software panel as shown in Figure 13 has the following features:

- Menu bar

- Control buttons

- Configuration display

- Data capture display

- Register read

#### Menu Bar

The menu bar, labeled 1 in Figure 13, consists of the **File**, **Edit**, and **Help** menus.

#### File Menu

**Open.** Loads previously captured data in comma separated values (.csv) format for analysis.

**Save Analysis Data.** Saves captured data in .csv format for future analysis.

Save Picture. Saves captured data images as a .jpeg file.

**Save Register Configuration**. Saves current device configuration for later use.

Exit. Exits the program.

#### **Edit Menu**

**Reinitialize to default**. Places the evaluation board in a known default state.

#### Help Menu

**Context Help.** Turns on context sensitive help.

User Guide. Opens the evaluation kit user guide.

About. Provides evaluation kit information.

#### Control Buttons, Drop-Down Boxes, and Indicators

The evaluation software includes the following control buttons, drop-down boxes, and indicators.

The **Device Connected** box (labeled 2 in Figure 13) indicates which model of the AD7091R-5 has been detected.

The **Device Mode** box (labeled 3 in Figure 13) indicates the operating mode of the ADC. In **Normal** mode, the ADC is ready to acquire samples. In **Sleep** mode, the device enters power-down mode with sampling disabled.

The **SCL Rate** box (labeled 4 in Figure 13) selects the SCL clock rate. Standard mode is 100 kHz. Fast mode is 400 kHz. Fast mode is the default configuration.

The **Analysis Ch** box (labeled 5 in Figure 13) selects the channel analyzed and the channel whose parametric performance data is displayed in the plot analysis blocks.

The **Samples** box (labeled 6 in Figure 13) selects the number of samples to be completed in a single acquisition.

The **Single Capture** box (labeled 7 in Figure 13) initiates the sampling and readback of the defined number of measurements.

The **Continuous Capture** box (labeled 8 in Figure 13) performs a continuous capture from the ADC. Click a second time to stop sampling.

The **Reference Settings** box (labeled 9 in Figure 13) indicates current reference setting. If **External Reference** is selected, you have the option to provide an off-board external reference. If this option is selected, the supplied reference value must be entered in **Ref. Value**.

The **Flash LED** box (labeled 10 in Figure 13) causes the orange **LED1A** on the SDP board to flash, which can be a useful debugging tool.

The **Reset** box (labeled 11 in Figure 13) resets the ADC and places the default configuration in the control register.

The **DPS Duty Cycle** box (labeled 13 in Figure 13) selects the duty cycle of the dynamic power-scaling signal controlling the power consumption of the ADA4805-1ARJZ amplifier connected between  $MUX_{OUT}$  and  $ADC_{IN}$ .

The **Amp PD** box (labeled 14 in Figure 13) places the ADA4805-1ARJZ amplifier in power-down mode when enabled. The default configuration is power-down enabled.

The **DPS** box (labeled 15 in Figure 13) selects the state of the dynamic power scaling (DPS) feature of the ADA4805-1ARJZ amplifier connected between MUX $_{

m OUT}$  and ADC $_{

m IN}$ . The default configuration is DPS enabled.

#### **Configuration Buttons**

There are four configuration register buttons contained within the block diagram on the **Configure** tab. Selecting these blue buttons, , produces pop-up boxes that allow you to configure the respective section of the block diagram.

The four buttons control the enabled channels (I/P MUX), the source of the reference input (2.5V VREF), the CONTROL LOGIC AND REGISTERS, and the Alert Registers. Refer to the AD7091R-5 data sheet for details on available configuration options.

Note that the light emitting diode (LED), D3, can be used to indicate an alert to the evaluation board user. Refer to the AD7091R-5 data sheet for instructions on configuring the control logic and registers so that a high state of the alert pin on the ADC enables the LED, D3.

#### **Data Capture Display**

While the main software window shows six tabs, only four tabs display the conversion data in different formats: **Waveform**, **Histogram**, **FFT**, and **Summary** (labeled 12 in Figure 13). These tabs are only active in command mode. The **Configure** and **Read Register** tabs are always active.

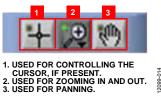

The tools shown in Figure 14 allow user control of the different chart displays within the four tabs.

Figure 14. Chart Tools

#### **WAVEFORM CAPTURE**

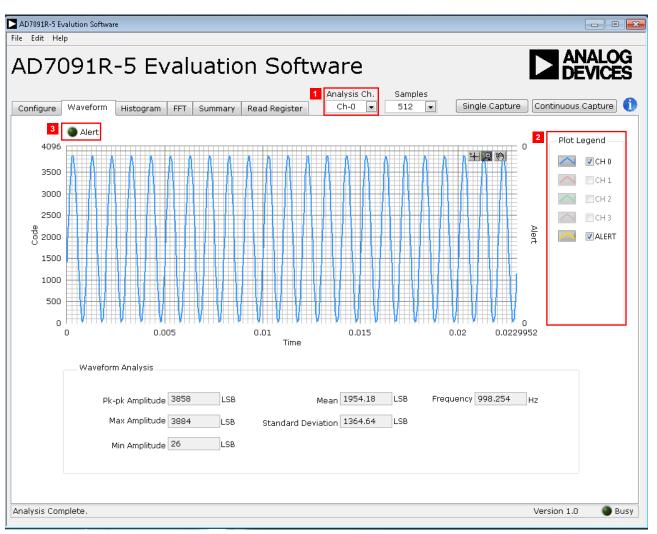

Figure 15 shows the Waveform tab.

The waveform analysis reports the amplitudes recorded from the captured signal as well as the frequency of the signal tone. The analysis report is generated for the channel selected via the **Analysis Ch** drop-down menu (labeled 1 in Figure 15).

All enabled channels can be shown in the waveform plot. It is possible to remove any undesired channel(s) from the plot by deselecting that channel within the **Plot Legend** (labeled 2 in Figure 15). If an alert is generated, the **Alert** indicator (labeled 3 in Figure 15) on the waveform panel illuminates.

Figure 15. Waveform Capture Tab

#### **AC TESTING—HISTOGRAM**

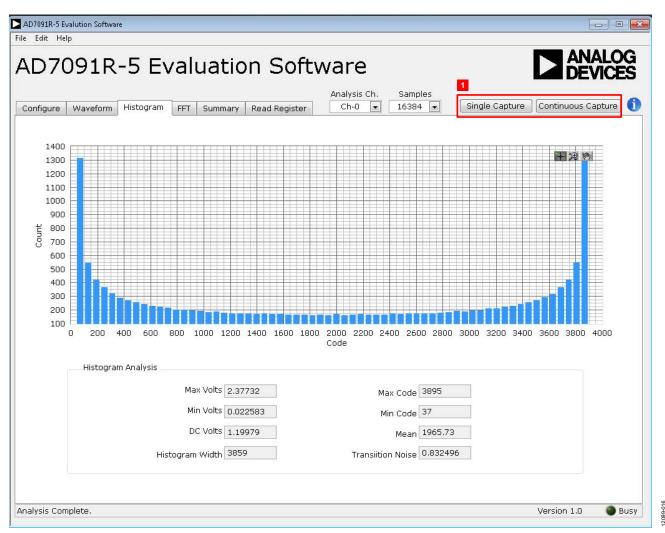

Figure 16 shows the **Histogram** capture tab. This tests the ADC for the code distribution for the ac input and computes the mean and standard deviation, or transition noise of the converter, and displays the results.

Raw data is captured and passed to the PC for statistical computations. To perform a histogram test, select the **Histogram** tab in the evaluation software main window and click the **Single Capture** or **Continuous Capture** button (labeled 1 in Figure 16).

Note that an ac histogram requires a quality signal source applied to the input BIPOLAR IN or VINx connectors.

#### DC TESTING—HISTOGRAM

The histogram is more commonly used for dc testing. Similar to ac testing, this tests the ADC for the code distribution for the dc input and computes the mean and standard deviation, or transition noise of the converter, and displays the results.

Raw data is captured and passed to the PC for statistical computations. To perform a histogram test, ensure the AD7091R-5 is in command mode, select the **Histogram** tab in the evaluation software main window and click the **Single Capture** or **Continuous Capture** button (labeled 1 in Figure 16).

Figure 16. Histogram Capture Tab

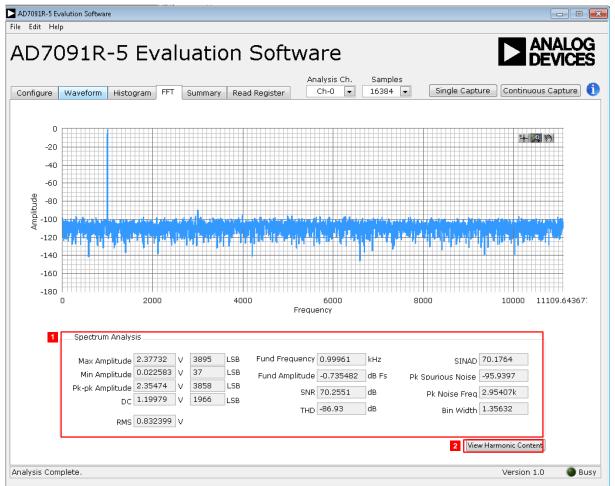

#### AC TESTING—FFT CAPTURE

Figure 17 shows the **FFT** capture tab. This tests the traditional ac characteristics of the converter and displays a fast Fourier transform (FFT) of the results. As in the histogram test, raw data is captured and passed to the PC where the FFT is performed, displaying SNR, SINAD, and THD.

To perform an ac test, apply either a bipolar sinusoidal signal to the evaluation board at the BIPOLAR IN input (J10). Then, connect the UNIPOLAR OUT connector (J14) to any input multiplexer channel connector (J7, J8, J18, or J19) or apply a unipolar sinusoidal signal directly to any of these channel connectors. Low distortion, better than 115 dB, is required to allow true evaluation of the part. One possibility is to filter the input signal from the ac source. There is no suggested bandpass filter, but take consideration in the choice. Furthermore, if using a low frequency band-pass filter when the full-scale input range is more than a few volts peak-to-peak, it is recommended to use the on-board amplifiers to amplify the signal, thus preventing the filter from distorting the input signal.

Optional on-board antialias filtering can be implemented by populating RC filters connected to the noninverting inputs of channel buffers.

Figure 17 displays the spectral analysis results of the captured data.

- The plot is the FFT image of the analysis channel selected.

- The Spectrum Analysis panel displays the performance data: SNR, THD, SINAD, dynamic range, and noise performance along with the input signal characteristics (labeled 1 in Figure 17).

- Select the **View Harmonic Content** button to switch the panel to display the frequency and amplitude of the fundamental in addition to the second to fifth harmonics (labeled 2 in Figure 17).

Figure 17. FFT Capture Tab

#### **SUMMARY TAB**

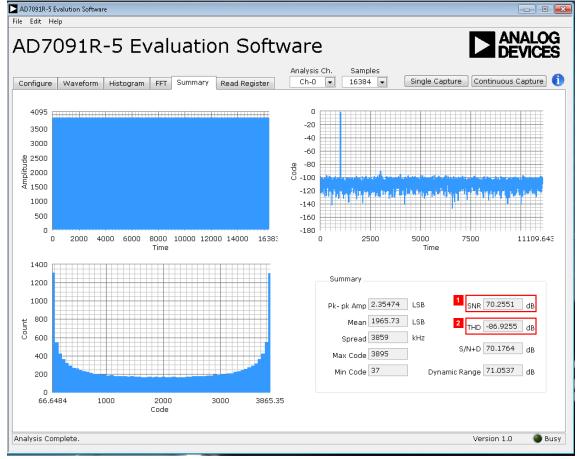

Figure 19 shows the **Summary** tab. This tab captures and displays all of the information in one panel with a synopsis of the information, including key performance parameters, such as **SNR** and **THD**, labeled 1 and 2, respectively in Figure 19.

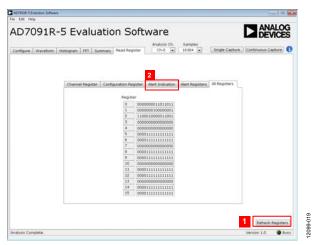

#### **READ REGISTER TAB**

All indicators within the **Read Register** tab are automatically updated when this tab is selected. In addition, this tab features a **Refresh Registers** button (labeled 1 in Figure 18) that is useful for monitoring the **Alert Indication** subtab while performing data captures and viewing the **Read Register** panel.

The **Read Register** tab as shown in Figure 18 offers the following subtabs:

- The Channel Register tab indicates the current enable/disable state of all channels available on the AD7091R-5.

- The **Configuration Register** tab indicates the configuration state of the AD7091R-5.

- The **Alert Indication** tab (labeled 2 in Figure 18) indicates the current high and low alert status of individual

- channels. This allows you to service an alert that has been triggered.

- The Alert Registers tab indicates the current high, low, and hysteresis alert register values that are programmed into the AD7091R-5 control registers.

- The All Registers tab displays all current register values contained within the AD7091R-5.

Figure 18. Read Register Tab

Figure 19. Summary Tab

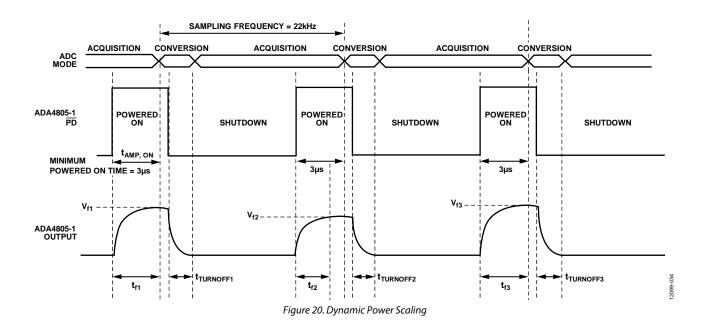

#### DYNAMIC POWER SCALING

Figure 20 shows the dynamic power scaling (DPS) features available to the board user. This feature can only be accessed when LK13 and LK14 are in the B position. This places U15 between the MUX<sub>OUT</sub> and ADC<sub>IN</sub> pins of the AD7091R-5. As well, place LK2 in the B position and provide a voltage of between –2 V and 0 V to the J3-1 input header. If the DPS features are utilized, it is recommended to not use the J10 and J14 connectors. One of the merits of a SAR ADC is that its power scales with the sampling rate. This power scaling makes SAR ADCs very power efficient, especially when running at a low sampling frequency. However, the ADC driver used with the SAR ADC traditionally consumes constant power regardless of the sampling frequency.

DPS is a method by which the quiescent power of the ADC driver can be dynamically scaled with the sampling rate of the system. By providing properly timed signals to the  $\overrightarrow{PD}$  pin of the ADC driver, both the AD7091R-5 and the ADC driver can be run at optimum efficiency.

Figure 20 illustrates the relative signal timing for power scaling the ADC driver and the ADC. To prevent any degradation in the performance of the ADC, the ADC driver must have a fully settled output into the ADC before the start of the conversion period. In this example, the amplifier is switched to full power mode 3  $\mu s$  prior to the start of conversion. The  $\overline{PD}$  pin of the ADC driver is pulled low when the ADC input is inactive in between samples. The quiescent current of the amplifier typically falls to 10% of the normal operating value within 0.9  $\mu s$  at  $V_S=5$  V. While in shut down mode, the ADC driver output impedance is high.

Without power scaling, the amplifier consumes constant power regardless of the sampling frequency, as shown in the following equation.

$$P_Q = I_Q \times V_S$$

With power scaling, the quiescent power becomes proportional to the ratio between the amplifier on time,  $t_{AMP,\,ON}$ , and the sampling time,  $t_s$ :

$$P_Q = I_Q \times V_S \times \frac{t_{AMP,ON}}{t_S}$$

Thus, by dynamically switching the ADC Driver between shut down and full power modes between consecutive samples, the quiescent power of the driver scales with the sampling rate.

#### **SAVING FILES**

The software can save the current captured data for future analysis. The software has the ability to capture the current plot images and the current device configuration, as well as the raw waveform data, histogram data, and ac spectrum data.

#### Saving Data

To save data, go to the **File** menu, click **Save Analysis Data**, and select the desired data type to be saved.

- The Waveform Data saves the raw data captured as seen in the Waveform tab.

- The Histogram Data generates a file that contains two columns, one that contains the codes captured and the other containing the number of times each code was observed in the current capture.

- The **Spectrum Analysis** saves all the information that would be required for you to recreate the spectral analysis.

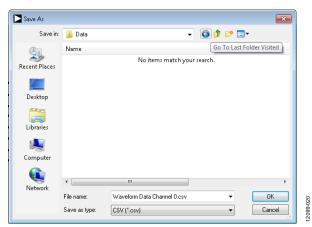

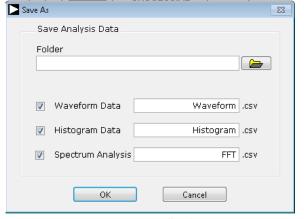

- The Save All Analysis Data option produces a pop-up box that allows you to save all of the analysis types to a specific folder location. For the individual saves, the Save As dialog box in Figure 21 opens. Save to an appropriate folder location. For the save all option, the dialog box in Figure 22 opens.

Figure 21. Save File Dialog Box

Figure 22. Save All Dialog Box

#### **Saving Plot Images**

To save plot images, go to the **File** menu, click **Save Picture** and select the desired plot image to be saved.

- The Waveform option saves the image from the waveform panel.

- The **Histogram** options save the image from the histogram panel.

- The **FFT** option saves the image from the FFT panel.

The images are saved in JPEG format and do not contain any raw data information. Saved plots cannot be loaded back into the evaluation environment. To save images, the **Save As** dialog box in Figure 23 opens. Save the images to an appropriate location.

Figure 23. Save Image Dialog Box

#### **Saving Device Configurations**

To save the current device configuration in XML format, go to the **File** menu and click **Save Register Configuration**.

To save the current device configuration, the **Save As** dialog box in Figure 24 opens. Save to an appropriate location.

Figure 24. Save As Register Configuration Dialog Box

#### **OPENING FILES**

#### **Loading Captured Data**

The software can load previously captured data for analysis.

Go to the **File** menu, click **Open**, and select **Waveform Data**. Only the previously captured waveform data can be opened, not a histogram or spectral analysis file. The waveform data is a raw data capture that rebuilds the histogram and ac spectrum analyses upon being loaded into the evaluation platform.

When **Waveform Data** is selected, the **Open** file dialog box in Figure 25 opens for loading an appropriate file. The evaluation software expects that a previously generated waveform file is in .csv format.

Figure 25. Open File Dialog Box

#### **Loading Device Configurations**

The software can load a previously utilized device configuration.

Go to the **File** menu, click **Open**, and select **Register Configuration**. The software loads all previously used device settings to the ADC and updates the evaluation platform appropriately. When **Register Configuration** is selected, the **Open** file dialog box in Figure 26 opens. Load an appropriate .XML file.

Figure 26. Open Configuration Dialog Box

## **EVALUATION BOARD SCHEMATICS AND ARTWORK**

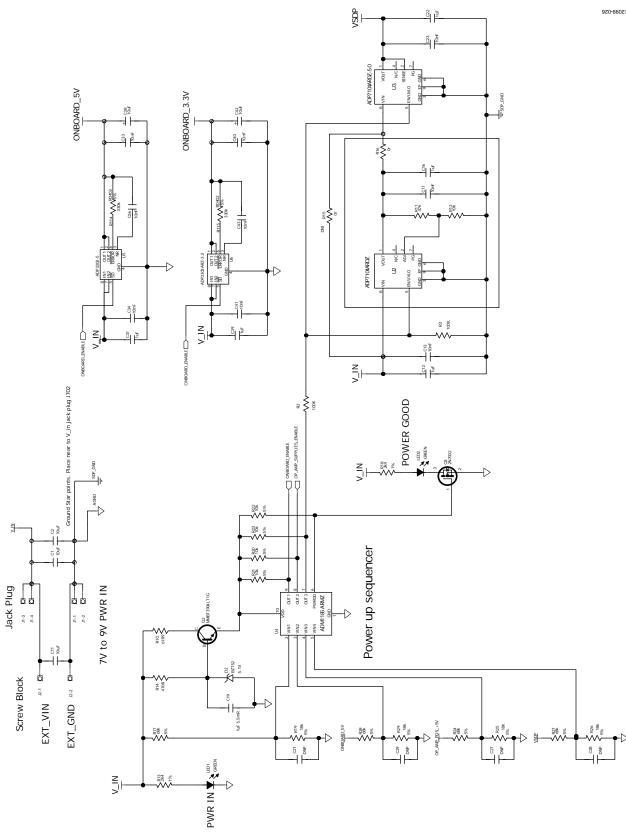

Figure 27. Schematic Page 1

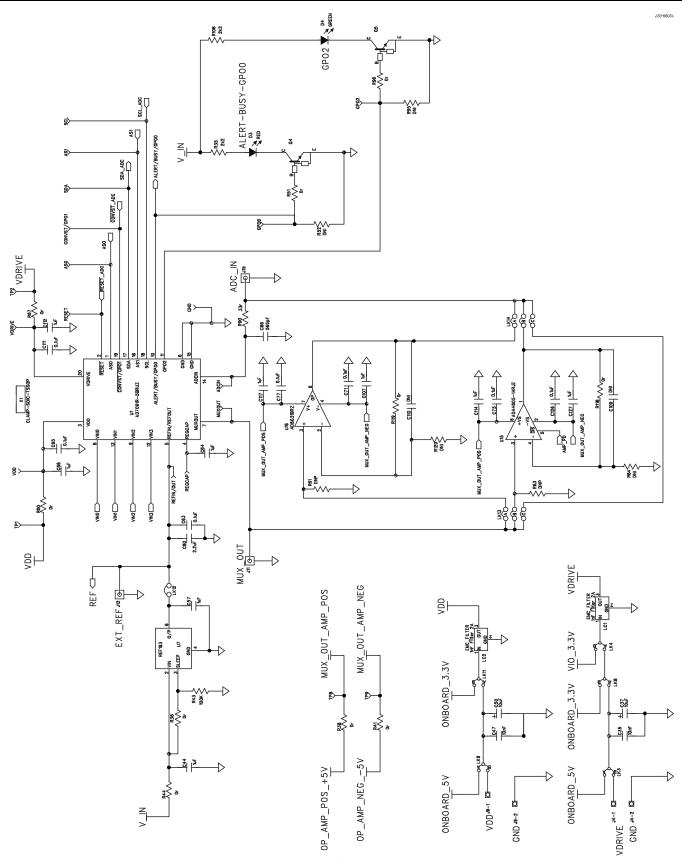

Figure 28. Schematic Page 2

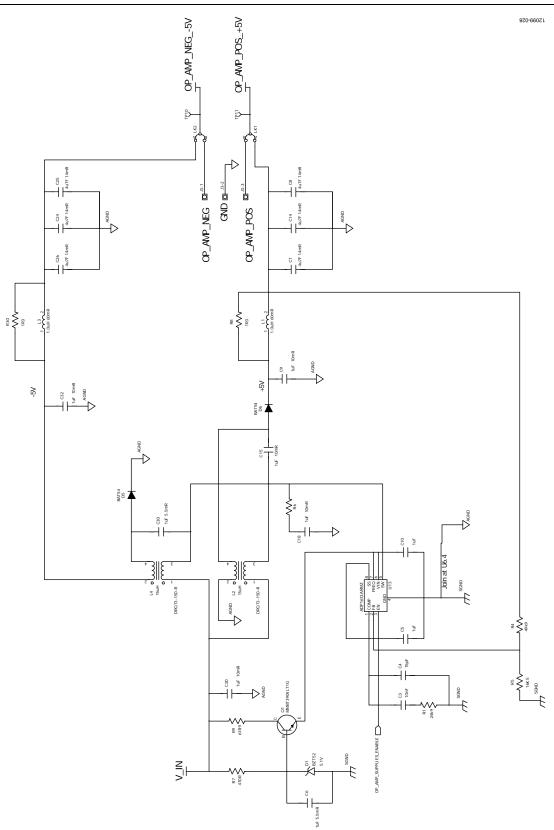

Figure 29. Schematic Page 3

15099-059 UNIPOLAR OUT BIAS\_UP\_AMP\_POS BIAS\_UP\_AMP\_NEG \$ ₹ ₹ OP\_AMP\_POS\_+5V OP\_AMP\_NEG\_-5V BIPOLAR IN Input buffer power supply 0P\_AMP\_P0S\_+5V

Figure 30. Schematic Page 4

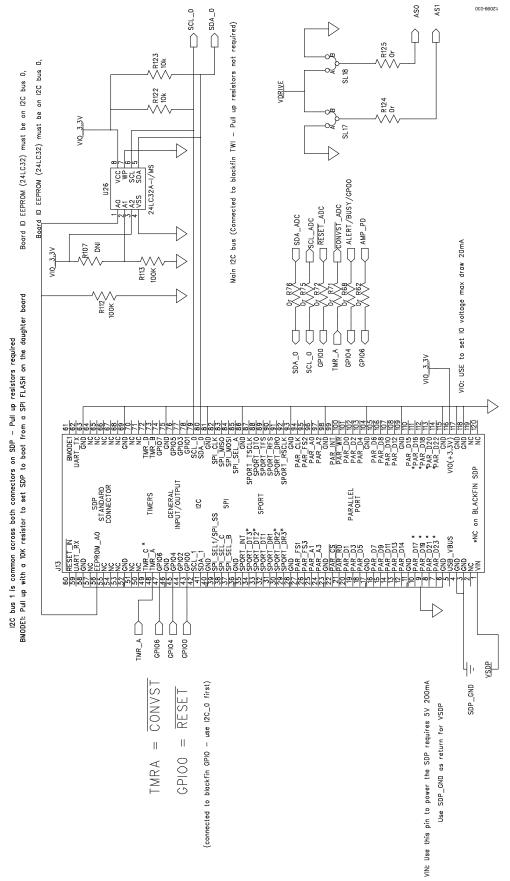

Figure 31. Schematic Page 5 Rev. 0 | Page 23 of 27

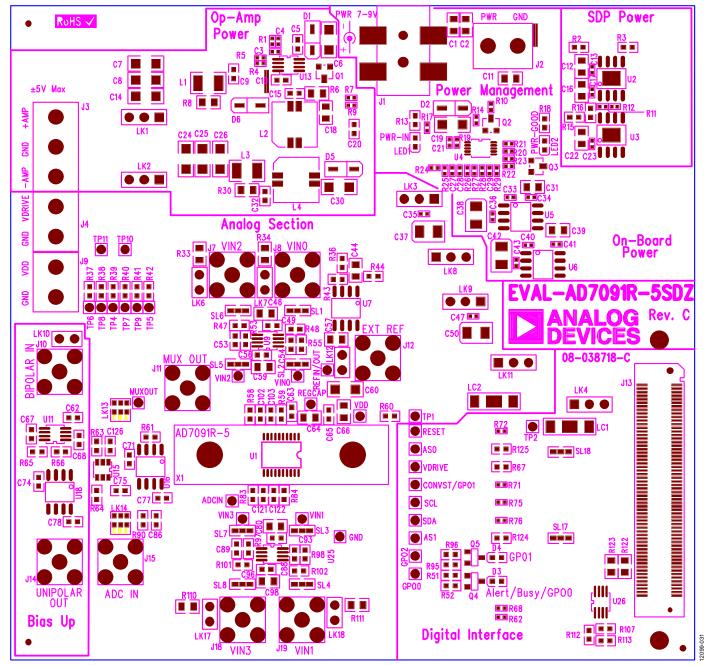

Figure 32. EVAL-AD7091R-5SDZ Top-Side Silkscreen

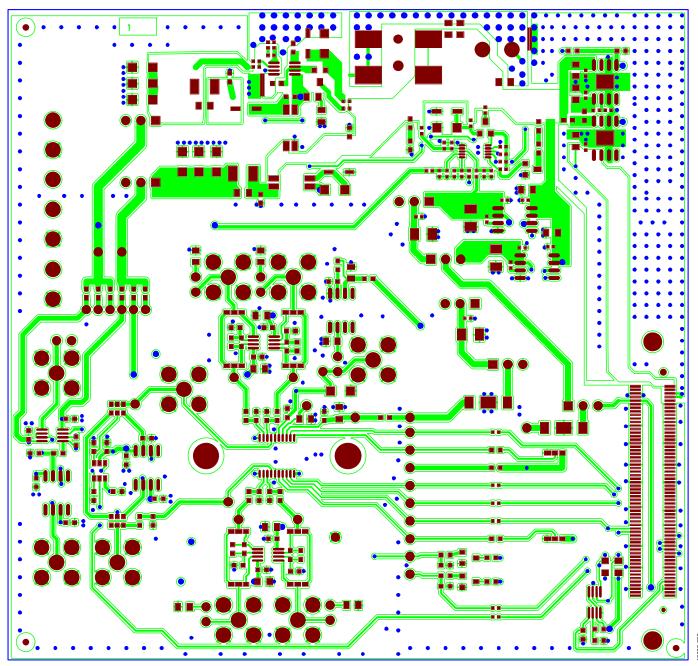

Figure 33. EVAL-AD7091R-5SDZ Top Layer

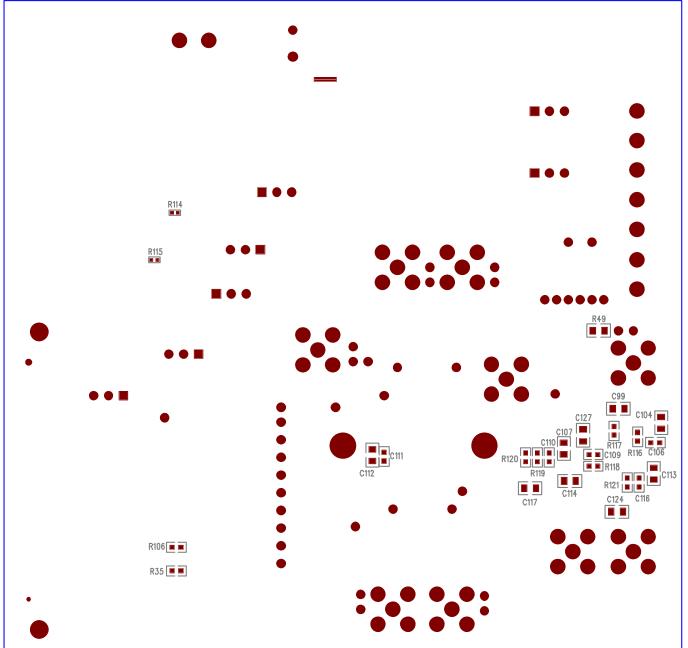

Figure 34. EVAL-AD7091R-5SDZ Bottom-Side Silkscreen

00.033

#### **NOTES**

#### **ESD Caution**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### **Legal Terms and Conditions**

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED AS IS AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

UG12099-0-7/15(0)

www.analog.com

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: <u>org@eplast1.ru</u>

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.