19-4190; Rev 0; 7/08

EVALUATION KIT

# AVAILABLE **Dual SMPS Outputs, LDO, and Dual Charge** Pumps with I<sup>2</sup>C Interface for OLED

# **General Description**

The MAX17065 provides the power-supply rails for activematrix, organic light-emitting diode (OLED) displays.

The MAX17065 includes a step-up DC-DC converter, an inverting DC-DC converter, a regulated positive charge pump, a regulated negative charge pump, and a low-dropout linear regulator (LDO). Synchronous rectifiers are integrated into the IC, eliminating the need for external power components. An I<sup>2</sup>C interface is used to program the switching frequency, the operating mode, and the cycle-by-cycle current limit of the noninverting and step-up converters, as well as the output voltages of the inverting converter and the charge pumps. Efficiency of 94% can be achieved for the step-up and 83% for the inverting converter.

The MAX17065 is packaged into a space-efficient 28-pin, 4mm x 4mm TQFN package with an exposed backside pad (EP) to enhance thermal characteristics.

**Applications**

**Cell Phones Digital Still Cameras** MP3 Players

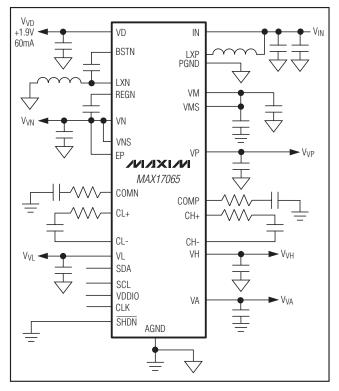

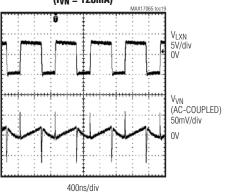

# Minimal Operating Circuit

# **Features**

- ♦ 2.3V to 4.5V Input Voltage Supply Range

- Fixed +5.35V Step-Up DC-DC Converter

- ♦ Adjustable -0.5V to -5.0V Inverting DC-DC Converter

- Adjustable 450mA/700mA Cycle-by-Cycle Current Limit for DC-DC Converters

- ♦ Selectable SKIP or Forced-PWM Mode for DC-DC Converters

- ♦ 600kHz/1.2MHz Selectable Fixed-Switching Frequency

- ♦ +5.5V to +9.0V Adjustable Positive-Regulated Charge Pump

- ♦ -5.0V to -0.5V Adjustable Negative-Regulated Charge Pump

- +1.9V 60mA LDO

- Integrated Synchronous Rectifiers

- ♦ True Shutdown<sup>™</sup>

- Output Undervoltage Shutdown with 100ms Timer

- Startup Sequence with 4ms Soft-Start

- ♦ 3µA (typ) Shutdown Supply Current

- Thermal Shutdown with 15ms Timer

- I<sup>2</sup>C Interface Control

- Greater than 90% Efficiency

- Small, 4mm x 4mm, 28-Pin Thin QFN

## **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX17065ETI+ | -40°C to +85°C | 28 Thin QFN |

|              |                | 1           |

+Denotes a lead-free/RoHS-compliant package.

#### Pin Configuration appears at end of data sheet.

True Shutdown is a trademark of Maxim Integrated Products, Inc.

Maxim Integrated Products 1

X17065

#

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| IN, SDA, SCL, VMS, VDDIO to AGND0.3V to +6V                              | BSTN to LXN0.3V to +6V                                |

|--------------------------------------------------------------------------|-------------------------------------------------------|

| $\overline{\text{SHDN}}$ , CLK to AGND                                   | VH to PGND0.3V to +14V                                |

| COMP, COMN to AGND0.3V to (V <sub>VMS</sub> + 0.3V)                      | CH- to PGND0.3V to (V <sub>VM</sub> + 0.3V)           |

| VD to $\overrightarrow{AGND}$ 0.3V to $(\overrightarrow{V_{IN}} + 0.3V)$ | CH+ to PGND0.3V to $(V_{VH} + 6V)$                    |

| LXP to PGND0.3V to (V <sub>VM</sub> + 0.3V)                              | VL to PGND6V to +0.3V                                 |

| VM to PGND0.3V to +6V                                                    | CL+ to PGND0.3V to (V <sub>VM</sub> + 0.3V)           |

| VP to PGND(VvM - 6V) to (VvM + 6V)                                       | CL- to PGND(VvL - 0.3V) to +0.3V                      |

| VA to PGND0.3V to $(V_{VM} + 0.3V)$                                      | VD to AGND Short CircuitContinuous                    |

| PGND to AGND0.3V to +0.3V                                                | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| VN to PGND9V to +0.3V                                                    | 28-Pin TQFN (derate 20.8mW/°C above +70°C)1667mW      |

| VNS to VN0.3V to +0.3V                                                   | Operating Temperature Range40°C to +85°C              |

| LXN to VN0.3V to (V <sub>IN</sub> + 0.3V)                                | Junction Temperature+150°C                            |

| REGN to VN0.3V to +6V                                                    | Storage Temperature Range65°C to +160°C               |

| BSTN to VNVREGN - 0.3V) to +18V                                          | Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1, VP, VN, VL, VH enabled, default output values set according to Tables 7, 8, 9, skip mode enabled, VVM = 5.5V, VVN, VVH, VVL set 50mV beyond their regulation points (not switching), VIN = 3.3V, TA = 0°C to +85°C, unless otherwise noted.)

| PARAMETER                                           | CONDITIONS                                                                                                                  | MIN  | ТҮР  | MAX  | UNITS |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| IN Input Voltage Range                              |                                                                                                                             | 2.3  |      | 4.5  | V     |  |

| IN Shutdown Supply Current<br>+ LXP Leakage Current | $\label{eq:shdd} \begin{array}{l} \overline{SHDN} = low \ , \ V_{IN} = 4.5 V, \ VD \ off, \\ T_A = +25^\circ C \end{array}$ |      | 3    | 7    | μA    |  |

| IN Standby Supply Current                           | VP, VN, VL, VH disabled, VD enabled, V <sub>IN</sub> = 2.3V to 4.5V                                                         |      | 300  | 600  | μA    |  |

| IN Undervoltage-Lockout (UVLO) Threshold            | V <sub>IN</sub> rising, typical hysteresis is 50mV                                                                          | 2.00 | 2.10 | 2.20 | V     |  |

| VD REGULATOR                                        |                                                                                                                             |      |      |      |       |  |

| VD Output Voltage                                   | $V_{IN} = 2.3V$ to 4.5V, 0 < $I_{LOAD}$ < 60mA                                                                              | 1.8  | 1.9  | 1.95 | V     |  |

| VD Undervoltage-Lockout Threshold                   | V <sub>VD</sub> rising, typical hysteresis is 60mV                                                                          | 1.3  | 1.4  | 1.5  | V     |  |

| VD Short-Circuit Current                            |                                                                                                                             | 70   |      | 160  | mA    |  |

| STEP-UP REGULATOR                                   |                                                                                                                             |      |      |      |       |  |

| VM Regulation Voltage                               | V <sub>IN</sub> = 2.3V to 4.5V                                                                                              | 5.25 | 5.35 | 5.45 | V     |  |

| VM Load Regulation                                  | 0 < I <sub>LOAD</sub> < 120mA                                                                                               |      | 0.1  |      | %     |  |

| VM Transconductance                                 | $\Delta I = \pm 2.5 \mu A$ at COMP, $V_{VM} = 5.35 V$                                                                       | 20   | 35   | 70   | μS    |  |

| LXP Current-Sense Transresistance                   |                                                                                                                             | 0.5  | 0.75 | 1.0  | V/A   |  |

| VP-to-PGND Discharge Resistance                     | VP discharge mode                                                                                                           |      | 100  | 200  | Ω     |  |

| LXP-to-PGND On-Resistance                           | V <sub>VM</sub> = 5.35V                                                                                                     |      | 0.25 | 0.5  | Ω     |  |

| LXP-to-VM On-Resistance                             | V <sub>VM</sub> = 5.35V                                                                                                     |      | 0.5  | 1    | Ω     |  |

| LXP Current Limit                                   | VSW register bit $5 = 1$ (high value), duty = 38%                                                                           | 0.6  | 0.7  | 0.8  |       |  |

| LXP Current Limit                                   | VSW register bit $5 = 0$ (low value), duty = $38\%$                                                                         | 0.36 | 0.45 | 0.54 | A     |  |

| LXP-to-VM Zero-Crossing Threshold                   | Skip mode only                                                                                                              |      | 25   |      | mA    |  |

| LXP-to-IN Damping Switch Resistance                 | Skip mode, $V_{VM} = 5.5V$                                                                                                  |      | 100  |      | Ω     |  |

MAX17065

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, VP, VN, VL, VH enabled, default output values set according to Tables 7, 8, 9, skip mode enabled,  $V_{VM} = 5.5V$ , VVN, VVH, VVL set 50mV beyond their regulation points (not switching),  $V_{IN} = 3.3V$ , **TA** = 0°C to +85°C, unless otherwise noted.)

| PARAMETER                             | COND                                                                                                 | DITIONS                                    | MIN  | ТҮР  | MAX  | UNITS |

|---------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------|------|------|------|-------|

| LXP Negative Current Limit            | Forced PWM only; it is<br>average value is (LXP<br>limit - I <sub>RIPPLE</sub> /2)                   |                                            |      | -0.3 |      | А     |

| VM-to-VP On-Resistance                | V <sub>VM</sub> = 5.35V                                                                              |                                            |      | 0.4  | 0.8  | Ω     |

| VM-to-VA On-Resistance                | $V_{VM} = 5.35V$                                                                                     |                                            |      | 3    | 6    | Ω     |

| VP Leakage Current                    | $V_{VP} = +8V$ , VM in regulated test mode, $T_A = +25^{\circ}$                                      |                                            |      |      | 10   | μΑ    |

| VM Soft-Start Time                    |                                                                                                      |                                            | 3    | 4    | 5    | ms    |

| VP Soft-Start Time                    |                                                                                                      |                                            | 3    | 4    | 5    | ms    |

| VA-to-PGND Discharge Resistance       |                                                                                                      |                                            |      | 100  | 200  | Ω     |

| VM-to-VA Impedance at Startup         |                                                                                                      |                                            |      | 100  | 200  | Ω     |

| VM-to-VA Delay to Low Impedance       |                                                                                                      |                                            |      |      | 1    | ms    |

| INVERTING REGULATOR                   |                                                                                                      |                                            |      |      |      |       |

|                                       |                                                                                                      | $V_{VN} = -0.5V$                           | -7   |      | +7   |       |

| /N Regulation Voltage Accuracy        | V <sub>VN</sub> Table 9 voltage                                                                      | V <sub>VN</sub> = -1.0V, -1.5V<br>or -2.0V | -4   |      | +4   | %     |

|                                       |                                                                                                      | $V_{VN} \le -2.5V$                         | -2   |      | +2   |       |

| VN Load Regulation                    | 0 < I <sub>LOAD</sub> < 120mA                                                                        |                                            |      | 0.1  |      | %     |

| VN Transconductance                   | $\Delta I = \pm 2.5 \mu A$ at COMN                                                                   | , V <sub>VN</sub> = -4.5V                  | 20   | 35   | 70   | μS    |

| LXN Current-Sense Transresistance     |                                                                                                      |                                            | 0.3  | 0.6  | 0.9  | V/A   |

| VN-to-PGND Discharge Resistance       | VN discharge mode                                                                                    |                                            |      | 120  | 250  | Ω     |

| LXN-to-IN On-Resistance               | V <sub>VM</sub> = 5.35V, V <sub>BSTN</sub> - '                                                       | $V_{LXN} = 4.5V$                           |      | 0.5  | 1    | Ω     |

| LXN-to-VN On-Resistance               | V <sub>VM</sub> = 5.35V                                                                              |                                            |      | 0.5  | 1    | Ω     |

|                                       | VSW register bit 4 = 1 (                                                                             | high value), duty = 80%                    | 0.6  | 0.7  | 0.8  |       |

| LXN Current Limit                     | VSW register bit $4 = 0$ (                                                                           | low value), duty = 80%                     | 0.36 | 0.45 | 0.54 | A     |

| LXN-to-VN Zero Crossing               | Skip mode only                                                                                       |                                            |      | 20   |      | mA    |

| LXN Negative Current Limit            | Forced PWM only; it is a peak value;<br>average value is (LXN negative current<br>limit - IRIPPLE/2) |                                            |      | -0.3 |      | A     |

| VN + VNS Leakage Current              | $V_{VN} = V_{VNS} = -8V$ , test mode,<br>T <sub>A</sub> = +25°C (Note 1)                             |                                            |      |      | 20   | μA    |

| LXN-to-PGND Damping Switch Resistance |                                                                                                      |                                            |      | 100  |      | Ω     |

| VN Soft-Start Time                    |                                                                                                      |                                            | 3    | 4    | 5    | ms    |

| OSCILLATOR                            | -                                                                                                    | -                                          |      |      |      |       |

| LXN, LXP Switching Frequency          | V <sub>IN</sub> = 3.3V                                                                               | FSET = 1                                   | 1080 | 1200 | 1320 | kHz   |

| VNL VD Movimum Duty Ovela             |                                                                                                      | FSET = 0                                   | 540  | 600  | 660  | 0/    |

| LXN, LXP Maximum Duty Cycle           |                                                                                                      |                                            | 80   | 85   | 90   | %     |

| CLx, CHx Switching Frequency          | $V_{VH} = +6V, V_{VL} = -4V, FSET = 0$                                                               |                                            | 270  | 300  | 330  | kHz   |

|                                       | $V_{VH} = +6V, V_{VL} = -4V, FSET = 1$                                                               |                                            | 540  | 600  | 660  |       |

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, VP, VN, VL, VH enabled, default output values set according to Tables 7, 8, 9, skip mode enabled,  $V_{VM} = 5.5V$ ,  $V_{VN}$ ,  $V_{VH}$ ,  $V_{VL}$  set 50mV beyond their regulation points (not switching),  $V_{IN} = 3.3V$ ,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted.)

| PARAMETER                                                     | CONDITIONS                                                |                                   | MIN   | ТҮР  | MAX  | UNITS |

|---------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------|-------|------|------|-------|

| CHARGE PUMPS                                                  | ł                                                         |                                   |       |      |      |       |

| VH Adjustable Voltage Range                                   | See Table 7 for outp                                      | ut settings                       | 5.5   |      | 9.0  | V     |

| VL Adjustable Voltage Range                                   | See Table 8 for outp                                      | ut settings (Note 3)              | -5.0  |      | -0.5 | V     |

| CH-, CL+ to VM, CH-, CL+ to PGND<br>On-Resistance             |                                                           |                                   |       | 4    | 8    | Ω     |

| CH+ to VM, CH+ to VH, CL- to VL,<br>CL- to PGND On-Resistance |                                                           |                                   |       | 10   | 25   | Ω     |

| VH Voltage-Regulation Threshold                               | With respect to the V<br>V <sub>VM</sub> = $5.35V$        | / <sub>VH</sub> Table 7 voltage,  | -2    |      | +2   | %     |

|                                                               | With respect to the                                       | V <sub>VL</sub> = -0.5V           | -10   |      | +10  |       |

| VI Valtage Degulation Threshold                               | V <sub>VL</sub> Table 8                                   | V <sub>VL</sub> = -1.0V           | -5    |      | +5   | 0/    |

| VL Voltage-Regulation Threshold                               | voltage, V <sub>VM</sub> =                                | V <sub>VL</sub> = -1.5V or -2     | -4    |      | +4   | %     |

|                                                               | 5.35V                                                     | V <sub>VL</sub> ≤ -2.5V           | -2    |      | +2   |       |

| VL Discharge Resistance                                       |                                                           |                                   |       | 100  | 200  | Ω     |

| VH Discharge Resistance                                       |                                                           |                                   |       | 100  | 200  | Ω     |

| VH Leakage Current                                            | $V_{VH} = +9V$ , test mode, $T_A = +25^{\circ}C$ (Note 1) |                                   |       |      | 10   | μΑ    |

| VL Leakage Current                                            | $V_{VL}$ = -5.0V, test mod                                | de, $T_A = +25^{\circ}C$ (Note 1) |       |      | 10   | μΑ    |

| VH Soft-Start Time                                            |                                                           |                                   | 3     | 4    | 5    | ms    |

| VL Soft-Start Time                                            |                                                           |                                   | 3     | 4    | 5    | ms    |

| PROTECTION                                                    |                                                           |                                   |       |      |      |       |

| VMS UVP Threshold Voltage                                     | VMS falling, V <sub>VMS</sub> >                           | V <sub>IN</sub>                   | 4     | 4.2  | 4.4  | V     |

| VA UVP Threshold Voltage                                      | V <sub>A</sub> falling                                    |                                   | 4.15  | 4.37 | 4.59 | V     |

| VMS-to-VIN Disable Threshold Voltage                          | VMS rising, typical h                                     | nysteresis is 90mV                | -0.35 | -0.2 | -0.1 | V     |

|                                                               | With respect to the                                       | $V_{VN} = -0.5V$ to $-1.5V$       | 27    | 60   | 90   | %     |

| VNS UVP Threshold-Voltage Tolerance                           | regulation voltage,<br>VNS rising                         | V <sub>VN</sub> ≤ -2.0V           | 74    | 80   | 85   | 70    |

| VH UVP Threshold-Voltage Tolerance                            | With respect to the regulation voltage,<br>VH falling     |                                   | 75    | 80   | 85   | %     |

| VL UVP Threshold-Voltage Tolerance                            | With respect to the                                       | $V_{VL} = -0.5V$ to $-1.5V$       | 27    | 60   | 90   | 0/    |

|                                                               | regulation voltage,<br>VL rising                          | $V_{VL} \leq -2.0V$               | 74    | 80   | 85   | %     |

| UVP Shutdown Delay                                            |                                                           |                                   | 100   | 120  | 145  | ms    |

| Thermal Shutdown                                              | Hysteresis = 20°C                                         |                                   |       | 160  |      | °C    |

| Thermal-Shutdown Delay                                        |                                                           |                                   | 12    | 15   | 18   | ms    |

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, VP, VN, VL, VH enabled, default output values set according to Tables 7, 8, 9, skip mode enabled,  $V_{VM} = 5.5V$ , VVN, VVH, VVL set 50mV beyond their regulation points (not switching),  $V_{IN} = 3.3V$ , **TA** = 0°C to +85°C, unless otherwise noted.)

| PARAMETER                               | CONDITIONS                          | MIN                      | ТҮР | МАХ                      | UNITS |

|-----------------------------------------|-------------------------------------|--------------------------|-----|--------------------------|-------|

| LOGIC INPUTS (SDA, SCL)                 |                                     |                          |     |                          |       |

| I <sup>2</sup> C Frequency Range        |                                     | 10                       |     | 100                      | kHz   |

| SDA, SCL Input Logic-High Voltage       |                                     | 0.7 x<br>V <sub>VD</sub> |     |                          | V     |

| SDA, SCL Input Logic-Low Voltage        |                                     |                          |     | 0.3 x<br>V <sub>VD</sub> | V     |

| SDA, SCL Pullup Resistance to VD        |                                     | 5                        | 10  | 20                       | kΩ    |

| SDA Pulldown Current                    | $V_{SDA} = 0.4V$                    | 10                       |     |                          | mA    |

| VDDIO Operating Voltage Range           | $V_{SDA} = 0.4V$                    | 1.6                      |     | 5.5                      | V     |

| VDDIO UVLO Threshold Voltage            |                                     | 1.2                      | 1.4 | 1.6                      | V     |

| VDDIO Bias Current                      | $V_{CLK} = 0$ or VDDIO, SHDN = open |                          |     | 2                        | μA    |

| SHDN, CLK Input Logic-High Voltage      |                                     | 0.7 x<br>Vvddio          |     |                          | V     |

| SHDN, CLK Logic Input Logic-Low Voltage |                                     |                          |     | 0.3 x<br>Vvddio          | V     |

| SHDN Pulldown Resistance                |                                     | 50                       | 100 | 200                      | kΩ    |

# **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1, VP, VN, VL, VH enabled, default output values set according to Tables 7, 8, 9, skip mode enabled,  $V_{VM} = 5.5V$ ,  $V_{VN}$ ,  $V_{VH}$ ,  $V_{VL}$  set 50mV beyond their regulation points (not switching),  $V_{IN} = 3.3V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                                                          | CONDITIONS                                                          | MIN  | TYP | MAX  | UNITS |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|-----|------|-------|

| IN Input Voltage Range                                                             |                                                                     | 2.3  |     | 4.5  | V     |

| IN Standby Supply Current                                                          | VP, VN, VL, VH disabled, VD enabled, V <sub>IN</sub> = 2.3V to 4.5V |      |     | 600  | μA    |

| IN Undervoltage-Lockout Threshold V <sub>IN</sub> rising, typical hysteresis is 50 |                                                                     | 2.05 |     | 2.20 | V     |

| VD REGULATOR                                                                       |                                                                     |      |     |      |       |

| VD Output Voltage                                                                  | $V_{IN} = 2.3V$ to 4.5V, 0 < $I_{LOAD}$ < 60mA                      | 1.8  |     | 1.95 | V     |

| VD Undervoltage-Lockout Threshold                                                  | V <sub>VD</sub> rising, typical hysteresis is 60mV                  | 1.25 |     | 1.6  | V     |

| VD Short-Circuit Current                                                           |                                                                     | 55   |     | 180  | mA    |

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, VP, VN, VL, VH enabled, default output values set according to Tables 7, 8, 9, skip mode enabled,  $V_{VM} = 5.5V$ ,  $V_{VN}$ ,  $V_{VH}$ ,  $V_{VL}$  set 50mV beyond their regulation points (not switching),  $V_{IN} = 3.3V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                         | COND                                                                                         | ITIONS                                     | MIN   | ТҮР | MAX  | UNITS |

|-----------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------|-------|-----|------|-------|

| STEP-UP REGULATOR                 | •                                                                                            |                                            |       |     |      | •     |

| VM Regulation Voltage             | $V_{IN} = 2.3V$ to 4.5V                                                                      |                                            | 5.25  |     | 5.45 | V     |

| VM Transconductance               | $\Delta I = \pm 2.5 \mu A$ at COMF                                                           | P, V <sub>VM</sub> = 5.35V                 | 20    |     | 70   | μS    |

| LXP Current-Sense Transresistance |                                                                                              |                                            | 0.5   |     | 1.0  | V/A   |

| VP-to-PGND Discharge Resistance   | VP discharge mode                                                                            |                                            |       |     | 200  | Ω     |

| LXP-to-PGND On-Resistance         | V <sub>VM</sub> = 5.35V                                                                      |                                            |       |     | 0.5  | Ω     |

| LXP-to-VM On-Resistance           | V <sub>VM</sub> = 5.35V                                                                      |                                            |       |     | 1    | Ω     |

|                                   | VSW register bit 5 = 1 (                                                                     | high value), duty = 38%                    | 0.6   |     | 0.8  | ^     |

| LXP Current Limit                 | VSW register bit $5 = 0$ (                                                                   | low value), duty = 38%                     | 0.36  |     | 0.54 | A     |

| LXP Negative Current Limit        | Forced PWM only; it is a peak value;<br>average value is (LXP negative limit -<br>IRIPPLE/2) |                                            | -0.3  |     | -0.1 | А     |

| VM-to-VP On-Resistance            | $V_{VM} = 5.35V$                                                                             |                                            |       |     | 0.8  | Ω     |

| VM-to-VA On-Resistance            | V <sub>VM</sub> = 5.35V                                                                      |                                            | 3     |     | 6    | Ω     |

| VM Soft-Start Time                |                                                                                              |                                            | 3     |     | 5    | ms    |

| VP Soft-Start Time                |                                                                                              |                                            | 3     |     | 5    | ms    |

| VA-to-PGND Discharge Resistance   |                                                                                              |                                            | 100   |     | 200  | Ω     |

| VM-to-VA Impedance at Startup     |                                                                                              |                                            | 100   |     | 200  | Ω     |

| VM-to-VA Delay to Low Impedance   |                                                                                              |                                            |       |     | 1    | ms    |

| INVERTING REGULATOR               |                                                                                              |                                            |       |     |      |       |

|                                   | $V_{IN} = 2.3V$ to 4.5V                                                                      | $V_{VN} = -0.5V$                           | -7    |     | +7   |       |

| VN Regulation Voltage Accuracy    | with respect to the V <sub>VN</sub> Table 9 voltage                                          | V <sub>VN</sub> = -1.0V, -1.5V<br>or -2.0V | -4    |     | +4   | %     |

|                                   |                                                                                              | $V_{VN} \leq -2.5V$                        | -2    |     | +2   |       |

| VN Transconductance               | $\Delta I = \pm 2.5 \mu A at COMM$                                                           | V, V <sub>VN</sub> = -4.5 V                | 20    |     | 70   | μS    |

| LXN Current-Sense Transresistance |                                                                                              |                                            | 0.3   |     | 0.9  | V/A   |

| VN-to-PGND Discharge Resistance   | VN discharge mode                                                                            |                                            |       |     | 250  | Ω     |

| LXN-to-IN On-Resistance           | $V_{VM} = 5.35V, V_{BSTN} - V_{LXN} = 4.5V$                                                  |                                            |       |     | 1    | Ω     |

| LXN-to-VN On-Resistance           | V <sub>VM</sub> = 5.35V                                                                      |                                            |       |     | 1    | Ω     |

| LXN Current Limit                 | VSW register bit $4 = 1$ (                                                                   | high value), duty = 80%                    | 0.6   |     | 0.8  | ^     |

|                                   | VSW register bit $4 = 0$ (low value), duty = 80%                                             |                                            | 0.345 |     | 0.54 | A     |

| VN Soft-Start Time                |                                                                                              |                                            | 3     |     | 5    | ms    |

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, VP, VN, VL, VH enabled, default output values set according to Tables 7, 8, 9, skip mode enabled, V<sub>VM</sub> = 5.5V, V<sub>VN</sub>, V<sub>VH</sub>, V<sub>VL</sub> set 50mV beyond their regulation points (not switching), V<sub>IN</sub> = 3.3V, **T<sub>A</sub>** = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                                     | CONDITIONS                                    |                                         | MIN   | ТҮР  | MAX  | UNITS |  |

|---------------------------------------------------------------|-----------------------------------------------|-----------------------------------------|-------|------|------|-------|--|

| OSCILLATOR                                                    |                                               |                                         |       |      |      |       |  |

| LVN LVD Switching Frequency                                   | V(n = 2, 2)/                                  | FSET = 1                                | 1080  |      | 1320 |       |  |

| LXN, LXP Switching Frequency                                  | V <sub>IN</sub> = 3.3V                        | FSET = 0                                | 540   |      | 660  | – kHz |  |

| LXN, LXP Maximum Duty Cycle                                   |                                               |                                         | 80    |      | 90   | %     |  |

| CLx, CHx Switching Frequency                                  | $V_{VH} = 6V, V_{VL} = -4V,$                  | FSET = 0                                | 270   |      | 330  | - kHz |  |

| CEX, CHX Switching Frequency                                  | $V_{VH} = 6V, V_{VL} = -4V,$                  | FSET = 1                                | 540   |      | 660  | KITZ  |  |

| CHARGE PUMPS                                                  |                                               |                                         |       |      |      |       |  |

| VH Adjustable Range                                           | See Table 7 for output                        | it settings                             | 5.5   |      | 9.0  | V     |  |

| VL Adjustable Range                                           | See Table 8 for output                        | it settings (Note 3)                    | -5.0  |      | -0.5 | V     |  |

| CH-, CL+ to VM, CH-, CL+ to PGND<br>On-Resistance             |                                               |                                         |       |      | 8    | Ω     |  |

| CH+ to VM, CH+ to VH, CL- to VL,<br>CL- to PGND On-Resistance |                                               |                                         |       |      | 25   | Ω     |  |

| VH Voltage-Regulation Threshold                               | Typical values as pe                          | r Table 7, V <sub>VM</sub> = 5.35V      | -2    |      | +2   | %     |  |

| VL Voltage-Regulation Threshold                               |                                               | V <sub>VL</sub> = -0.5V                 | -10   |      | +10  | %     |  |

|                                                               | With respect to the $V_{VL}$ Table 8 voltage, | V <sub>VL</sub> = -1                    | -5    |      | +5   |       |  |

|                                                               | $V_{VM} = 5.35V$                              | V <sub>VL</sub> = -1.5V or -2           | -4    |      | +4   |       |  |

|                                                               |                                               | $V_{VL} = -2.5V \text{ or } -4.5$       | -2    |      | +2   |       |  |

| VL Discharge Resistance                                       |                                               |                                         |       |      | 200  | Ω     |  |

| VH Discharge Resistance                                       |                                               |                                         |       |      | 200  | Ω     |  |

| VH Soft-Start Time                                            |                                               |                                         | 3     |      | 5    | ms    |  |

| VL Soft-Start Time                                            |                                               |                                         | 3     |      | 5    | ms    |  |

| PROTECTION                                                    |                                               |                                         |       |      |      |       |  |

| VMS UVP Threshold Voltage                                     | VMS falling, $V_{VMS} > 1$                    | VIN                                     | 4.2   |      | 4.4  | V     |  |

| VA UVP Threshold Voltage                                      | VA falling                                    |                                         | 4.15  |      | 4.59 | V     |  |

| VMS-to-IN Disable Threshold Voltage                           | VMS rising, typical h                         | ysteresis is 90mV                       | -0.35 | -0.2 | -0.1 | V     |  |

|                                                               | With respect to the                           | $V_{VN} = -0.5V$ to $-1.5V$             | 27    |      | 90   |       |  |

| VNS UVP Threshold-Voltage Tolerance                           | regulation voltage,<br>VNS rising             | $V_{VN} \leq -2.0V$                     | 74    |      | 85   | - %   |  |

| VH UVP Threshold-Voltage Tolerance                            | With respect to the re<br>VH falling          | With respect to the regulation voltage, |       |      | 85   | %     |  |

| VL UVP Threshold-Voltage Tolerance                            | With respect to the regulation voltage,       | $V_{VL} = -0.5V$ to $-1.5V$             | 27    |      | 90   | %     |  |

|                                                               | VL rising                                     | $V_{VL} \leq -2.0V$                     | 74    |      | 85   |       |  |

| UVP Shutdown Delay                                            |                                               |                                         | 100   |      | 145  | ms    |  |

| Thermal-Shutdown Delay                                        |                                               |                                         | 12    |      | 18   | ms    |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, VP, VN, VL, VH enabled, default output values set according to Tables 7, 8, 9, skip mode enabled,  $V_{VM} = 5.5V$ ,  $V_{VN}$ ,  $V_{VH}$ ,  $V_{VL}$  set 50mV beyond their regulation points (not switching),  $V_{IN} = 3.3V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                          | CONDITIONS                                      | MIN                      | ТҮР | MAX                      | UNITS |

|------------------------------------|-------------------------------------------------|--------------------------|-----|--------------------------|-------|

| LOGIC INPUTS (SDA, SCL)            | · · ·                                           | •                        |     |                          |       |

| I <sup>2</sup> C Frequency Range   |                                                 | 10                       |     | 100                      | kHz   |

| SDA, SCL Input Logic-High Voltage  |                                                 | 0.7 x<br>V <sub>VD</sub> |     |                          | V     |

| SDA, SCL Input Logic-Low Voltage   |                                                 |                          |     | 0.3 x<br>V <sub>VD</sub> | V     |

| SDA, SCL Pullup Resistance to VD   |                                                 | 5                        |     | 20                       | kΩ    |

| SDA Pulldown Current               | $V_{SDA} = 0.4V$                                | 10                       |     |                          | mA    |

| VDDIO Voltage Range                |                                                 | 1.6                      |     | 5.5                      | V     |

| VDDIO UVLO Threshold Voltage       | VDDIO falling, typical hysteresis is 50mV       | 1.2                      |     | 1.6                      | V     |

| VDDIO Bias Current                 | $V_{CLK} = 0$ or $V_{VDDIO}$ , SHDN unconnected |                          |     | 2                        | μA    |

| SHDN, CLK Input Logic-High Voltage |                                                 | 0.7 x<br>Vvddio          |     |                          | V     |

| SHDN, CLK Input Logic-Low Voltage  |                                                 |                          |     | 0.3 x<br>Vvddio          | V     |

| SHDN Pulldown Resistance           |                                                 | 50                       |     | 200                      | kΩ    |

**Note 1:** The 10µA leakage current at VN, VP, VH, VL is guaranteed only when the switching regulators are disabled. See Table 12. **Note 2:** The  $T_A = -40^{\circ}$ C specifications are guaranteed by design, not production tested.

Note 3: VL output current cannot exceed 1mA when VL is set at -5V.

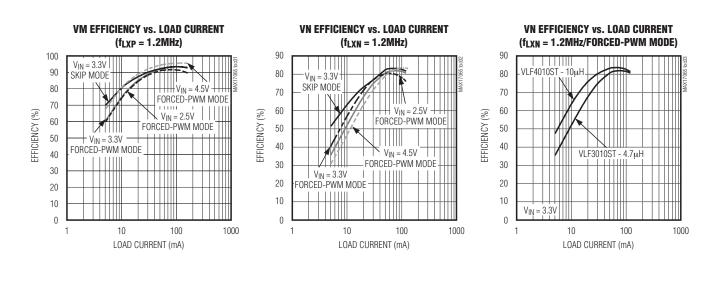

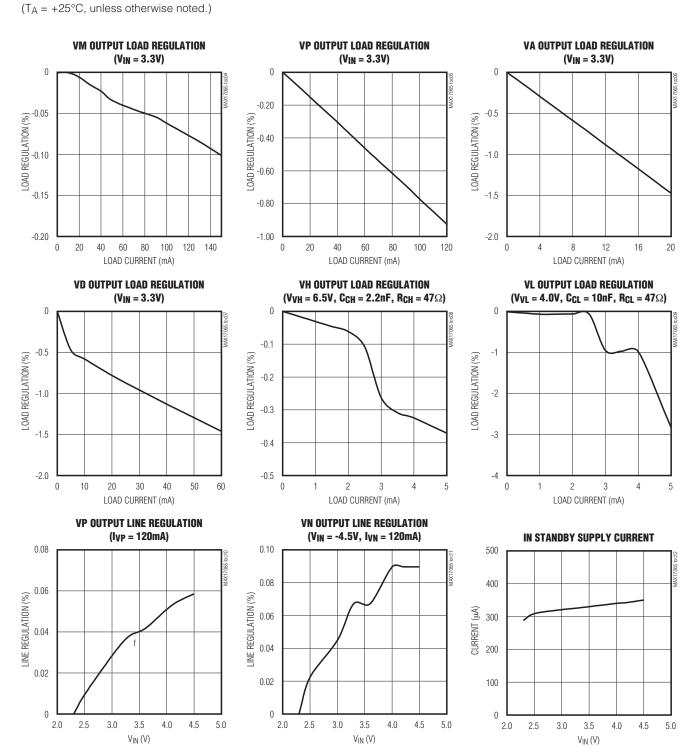

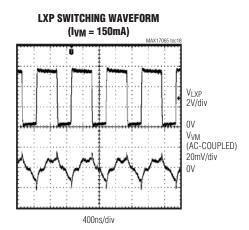

$(T_A = +25^{\circ}C, unless otherwise noted.)$

# **Typical Operating Characteristics**

M/IXI/N

# \_Typical Operating Characteristics (continued)

MAX17065

#### **Typical Operating Characteristics (continued)** $(T_A = +25^{\circ}C, unless otherwise noted.)$ VM, VA, VH, AND VL STARTUP VH, VL, VP, AND VN STARTUP IN SHUTDOWN SUPPLY CURRENT (0N1 = 1)(0N2 = 1)MAY17065 5 ON2 = 1 $\mathsf{V}_{\mathsf{V}\mathsf{M}}$ 5V/div 4 VVP 2V/div 0V 0V 3 5V/div 0V $V_{VA}$ $V_{VN}$ 0V 5V/div 2 Vvh 0V 5V/div 5V/div VVL 0V VVH 0V 1 0V 5V/div $V_{\text{VL}}$ 5V/div ON1 = 1 0 2.5 3.0 4.0 4.5 2.0 3.5 5.0 1ms/div 2ms/div $V_{IN}(V)$ VM, VA, VH, AND VL SHUTDOWN VH, VL, VP, AND VN SHUTDOWN (0N1 = 1)(0N2 = 1)MAN17005 4--17 AAV17000 $V_{\text{VM}}$ 2V/div ON1 = 1 ON2 = 1 $V_{VP}$ 5V/div 0V 0V 0V VVA $V_{VN}$ 5V/div 0V 5V/div VVH 5V/div 5V/div $V_{VH}$ 0V 0V $\mathsf{V}_{\mathsf{VL}}$ 0V 0V VVL 5V/div 5V/div 1ms/div 1ms/div

M/XI/M

**MAX17065**

CURRENT (µA)

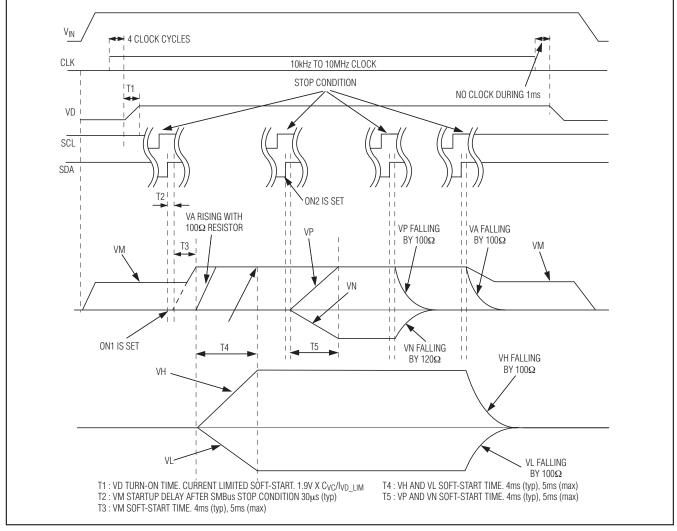

**Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                   |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SDA   | I <sup>2</sup> C-Compatible Serial Bidirectional Data Line. Internally connected to VD with a 10k $\Omega$ resistor.                                                                                                                                                                                                       |

| 2   | CLK   | External Wake-Up CMOS Oscillator. The fourth rising CLK pulse edge starts the IC. The CLK input frequency range is 10kHz to 10MHz.                                                                                                                                                                                         |

| 3   | VDDIO | Supply Voltage for CLK and SHDN Input Logic                                                                                                                                                                                                                                                                                |

| 4   | VD    | 1.9V Low-Dropout Linear Regulator Output. Connect a 4.7µF capacitor to AGND.                                                                                                                                                                                                                                               |

| 5   | AGND  | Analog GND                                                                                                                                                                                                                                                                                                                 |

| 6   | SHDN  | Shutdown Control Input. Connect $\overline{\text{SHDN}}$ to VDDIO to force VD to be always on. This pin is internally pulled down to AGND through a 100k $\Omega$ resistor. Connect $\overline{\text{SHDN}}$ to AGND or open for shutdown. The MAX17065 can exit from the shutdown after the fourth rising CLK pulse edge. |

| 7   | COMN  | Compensation Pin for the Inverting Converter Error Amplifier. Connect a series RC from COMN to AGND. Typical values are $33k\Omega$ and $470pF$ .                                                                                                                                                                          |

| 8   | VNS   | Inverting Converter Voltage Sense. Connect to the VN output capacitor.                                                                                                                                                                                                                                                     |

| 9   | REGN  | Regulated Supply that Provides $V_{VN}$ + 5V for the Synchronous DMOS of the Inverting Converter.<br>Bypass with a 0.1µF capacitor to VN.                                                                                                                                                                                  |

| 10  | VN    | Inverting Converter Output. Connect a 4.7µF capacitor to PGND for 1.2MHz operating frequency.                                                                                                                                                                                                                              |

| 11  | BSTN  | Boost Supply that Provides $V_{LXN}$ + 5V for the DMOS of the Inverting Converter. Bypass with a 0.1 $\mu$ F capacitor to LXN.                                                                                                                                                                                             |

| 12  | LXN   | Inverting Converter Switching Node. Connect inductor here and minimize trace area for lowest EMI.                                                                                                                                                                                                                          |

| 13  | IN    | Supply Pin. Bypass IN with a minimum 10µF ceramic capacitor directly to PGND.                                                                                                                                                                                                                                              |

| 14  | PGND  | Power GND                                                                                                                                                                                                                                                                                                                  |

| 15  | N. C. | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                   |

| 16  | LXP   | Step-Up Converter Switching Node. Connect inductor here and minimize trace area for lowest EMI.                                                                                                                                                                                                                            |

| 17  | VM    | Step-Up Converter Output. Connect a 4.7µF capacitor to PGND for 1.2MHz frequency operation.                                                                                                                                                                                                                                |

| 18  | VMS   | Step-Up Converter Voltage Sense. Connect to the VM output capacitor. VMS also provides a clean power supply for internal precision circuitry. Bypass VMS to AGND with a 0.1µF capacitor.                                                                                                                                   |

| 19  | VP    | OLED Anode Voltage Supply. Powered from VM through an internal 0.4 $\Omega$ MOSFET.                                                                                                                                                                                                                                        |

| 20  | VA    | Anode Voltage Supply. Powered from VM through an internal 3 $\Omega$ MOSFET.                                                                                                                                                                                                                                               |

| 21  | COMP  | Compensation Pin for the Step-Up Converter Error Amplifier. Connect a series RC from COMP to AGND. Typical values are $33k\Omega$ and $470pF$ .                                                                                                                                                                            |

| 22  | VL    | Negative Charge-Pump Output. Connect a 1µF capacitor to PGND.                                                                                                                                                                                                                                                              |

| 23  | CL-   | Negative Charge-Pump Flying Capacitor Terminal. Connect $10nF + 100\Omega$ between CL+ and CL- for typical application. See the Charge Pumps section in the <i>Electrical Characteristics</i> table for the capacitor selection.                                                                                           |

| 24  | CL+   | Negative Charge-Pump Flying Capacitor Terminal. Connect $10nF + 100\Omega$ between CL+ and CL- for typical application. See the Charge Pumps section in the <i>Electrical Characteristics</i> table for the capacitor selection.                                                                                           |

| 25  | CH-   | Positive Charge-Pump Flying Capacitor Terminal. Connect 2.2nF + $100\Omega$ between CH+ and CH- for typical application. See the Charge Pumps section in the <i>Electrical Characteristics</i> table for the capacitor selection.                                                                                          |

| 26  | CH+   | Positive Charge-Pump Flying Capacitor Terminal. Connect 2.2nF + $100\Omega$ between CH+ and CH- for typical application. See the Charge Pumps section in the <i>Electrical Characteristics</i> table for the capacitor selection.                                                                                          |

| 27  | VH    | Positive Charge-Pump Output. Connect a 1µF capacitor to PGND.                                                                                                                                                                                                                                                              |

| 28  | SCL   | I <sup>2</sup> C-Compatible Clock Input and Output. Internally connected to VD with a 10k $\Omega$ resistor.                                                                                                                                                                                                               |

| _   | EP    | Exposed Backside Pad. To ensure low thermal resistance, solder the backside pad to a copper plane that is <b>electrically connected to VN</b> . See the <i>PCB Layout and Grounding</i> section.                                                                                                                           |

MAX17065

Figure 1. MAX17065 Typical Operating Circuit

# Table 1. Component List

| DESIGNATION                                    | DESCRIPTION                                                                                                  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| CIN                                            | 10μF ±10%, 6.3V X5R ceramic<br>capacitor (0603)<br>TDK C1608X5R0J106K<br>Murata GRM188R60J106M               |

| L <sub>N</sub>                                 | 4.7μH, 0.75A, 0.15 <b>Ω</b> inductor<br>TDK VLF3010ST-4R7MR70                                                |

| Lp                                             | 4.7μH, 0.75A, 0.15Ω inductor<br>TDK VLF3010ST-4R7MR70<br>10μH, 0.8A, 0.25Ω inductor<br>TDK VLF4010ST-100MR80 |

| C <sub>MOUT,</sub><br>C <sub>NOUT,</sub> CDOUT | 4.7µF ±10%, 10V X5R ceramic<br>capacitors (0805)<br>Murata GRM219R61A475K<br>TDK C2012X5R1A475K              |

# Table 2. Component Suppliers

| SUPPLIER                                        | PHONE        | WEBSITE                     |

|-------------------------------------------------|--------------|-----------------------------|

| Murata<br>Electronics<br>North<br>America, Inc. | 770-436-1300 | www.murata-northamerica.com |

| TDK Corp.                                       | 847-803-     | www.component.tdk.com       |

# **Typical Operating Circuit**

The typical operating circuit of Figure 1 provides the power-supply rails for active-matrix OLED displays. Table 1 lists recommended components and Table 2 lists contact information for component suppliers.

## **Detailed Description**

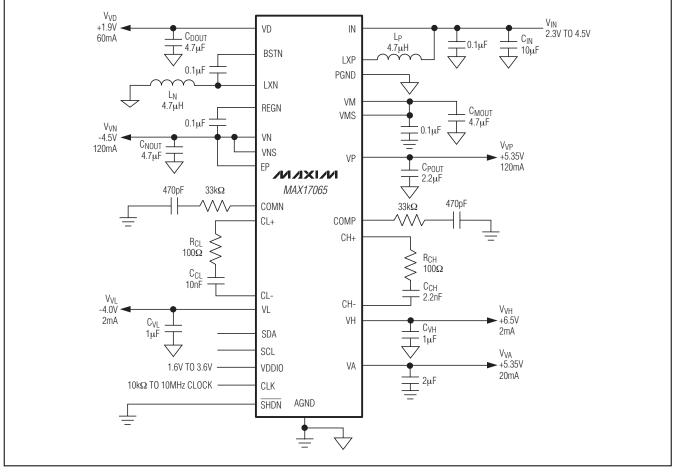

The MAX17065 provides all the power-supply rails for active-matrix OLED displays. It includes a step-up DC-DC converter, an inverting DC-DC converter, a regulated positive charge pump, a regulated negative charge pump, and a low-dropout linear regulator (LDO). Synchronous rectifiers are integrated into the device to minimize the number of external components, and to save circuit board space. Figure 2 is the MAX17065 functional diagram.

Figure 2. MAX17065 Functional Diagram

### Step-Up Converter (VM)

The step-up converter provides a fixed output voltage of +5.35V and provides up to 150mA of output current used to power the anode voltage supply (VP), the analog voltage supply (VA), the positive charge pump (VH), the negative charge pump (VL), and some of the IC's internal circuitry through the step-up converter's output-voltage sense pin (VMS).

The I<sup>2</sup>C interface is used to select the switching frequency (600kHz or 1.2MHz), the operating mode (SKIP or forced PWM), and the cycle-by-cycle current limit (450mA or 700mA) of the step-up converter. Efficiency of 94% can be achieved. Because of the slope compensation used to stabilize the feedback loop, the inductor current limit depends on the duty cycle. The current limit is determined by the following equation:

### $I_{LP(LIM)} = I_{LP(LIM)\_EC} + 0.2A \times (0.38 - Duty)$

where I<sub>LP(LIM)\_EC</sub> is the current limit specified at 38% duty cycle (see the *Electrical Characteristics*). The current-limit comparator delay is 60ns (typ) and the actual peak inductor current is increased by the delay.

#### Anode Voltage Supply (VP)

The anode voltage supply is created by connecting the output of the step-up converter VM directly to VP through an internal 0.4 $\Omega$  (typ) MOSFET. VP can deliver up to 120mA to the OLED's anode.

#### Analog Voltage Supply (VA)

The analog voltage supply is created by connecting the output of the step-up converter VM directly to VA through an internal  $3\Omega$  (typ) MOSFET. The VA voltage is kept within 100mV from the VM regulated output. VA can deliver up to 20mA.

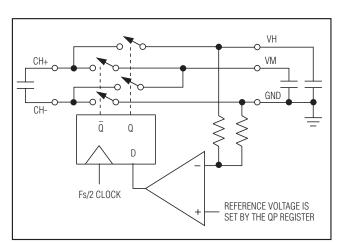

Figure 3. Positive Charge-Pump Regulator Control Block Diagram

#### **Inverting Converter (VN)**

The inverting converter can be adjusted to provide an output voltage range of -5.0V to -0.5V and can deliver an output current up to 120mA. The I<sup>2</sup>C interface is used to set the output voltage, the switching frequency (600kHz or 1.2MHz), the operating mode (SKIP or forced PWM), and the cycle-by-cycle current limit (450mA or 700mA). An efficiency of 84% can be achieved. Because of the slope compensation used to stabilize the feedback loop, the inductor current limit depends on the duty cycle. The current limit is determined by the following equation:

### $I_{LN(LIM)} = I_{LN(LIM)}EC + 0.25A \times (0.8 - Duty)$

where I<sub>LN(LIM)\_EC</sub> is the current limit specified at 80% duty cycle (see the *Electrical Characteristics*). The current-limit comparator delay is 60ns (typ) and the actual peak inductor current is increased by the delay.

### **Positive Charge-Pump Regulator (VH)**

The positive charge-pump regulator is programmable through the I<sup>2</sup>C interface to provide an output voltage range of +5.0V to +9.0V and can provide an output current up to 2mA. The positive charge-pump regulator has an on-demand switching architecture to save power loss at light-load current. Figure 3 is the positive charge-pump regulator control block diagram.

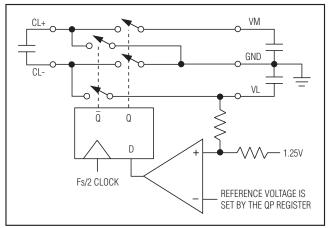

#### **Negative Charge-Pump Regulator (VL)**

The negative charge-pump regulator is programmable through the I<sup>2</sup>C interface to provide an output voltage range of -5.0V to -0.5V and can provide an output current up to 2mA. Like the positive charge-pump regulator, the negative charge-pump regulator has an on-demand switching architecture to save power loss at light-load current as well. Figure 4 shows the negative charge-pump regulator control block diagram.

Figure 4. Negative Charge-Pump Regulator Block Diagram

#### Low-Dropout Linear Regulator (VD)

The LDO provides a fixed output voltage of 1.9V and can deliver up to 60mA. The LDO is active whenever the input voltage is higher than the input UVLO threshold if SHDN is connected to VDDIO. If SHDN is connected to AGND or left unconnected, the LDO is started only when activity on the CLK pin is detected.

#### **True Shutdown**

The MAX17065 completely disconnects the VA, VP, and VN loads from the input when the outputs are turned off. For most step-up converters, the external rectifying diode and inductor form a DC current path from the battery to the output. This can drain the battery even in shutdown if a load remains connected at the step-up converter output. The MAX17065 internal switches shut off, disconnecting the load from the battery. This load disconnect is referred to as True Shutdown.

**Output Undervoltage Fault Protection**

The MAX17065 provides output undervoltage fault protection (UVP) for all outputs. When a UVP fault is detected for one of the outputs VA, VN, VH, and VL for 120ms (typ), all outputs except VD latch off. The fault status is set in the status register, which can be read through the I<sup>2</sup>C interface. When a VM UVP fault is detected, the VM-VP switch latches off after a 30µs delay. If the VM UVP condition continues for a period longer than 120ms (typ), all remaining outputs except VD are latched off. For all UVP faults except a VD UVP fault, the fault latch can be cleared by writing zero for ON1 and ON2 to the control register. Since the I<sup>2</sup>C bus is pulled up to VD through a  $10k\Omega$  resistor, a VD UVP fault cannot be cleared by writing to the control register and can only be cleared by cycling the input power (below the VIN - UVLO falling threshold) or by removing the CLK signal with  $\overline{SHDN} = Iow$ .

#### **Thermal-Overload Protection**

The thermal-overload protection prevents excessive power dissipation from overheating the device. When the junction temperature exceeds  $T_J = +160^{\circ}C$ , a thermal sensor activates the fault-protection latch after 15ms (typ), which shuts down all outputs including VD, allowing the device to cool down. For continuous operation, do not exceed the absolute maximum junction temperature rating of  $T_J = +150^{\circ}C$ .

Since VD is latched off during a thermal-overload protection fault, the fault cannot be cleared through the I<sup>2</sup>C bus since the I<sup>2</sup>C bus is pulled up to VD through a 10k $\Omega$  resistor. The fault is cleared by either cycling the input power (below the V<sub>IN</sub> - UVLO falling threshold) or by removing the CLK signal with  $\overline{SHDN}$  = low. See Table 3.

# Table 3. Status of Each Output Due to aFault Condition

| F.                   | -     | ION AFTER<br>FAULT   |     |                  |

|----------------------|-------|----------------------|-----|------------------|

| OVER-<br>TEMPERATURE | VD    | ANY OTHER<br>OUTPUTS | VD  | OTHER<br>OUTPUTS |

| Fault                | Х     | х                    | Off | Off              |

| Good                 | Fault | х                    | Off | Off              |

| Good                 | Goo   | Fault                | On  | Off              |

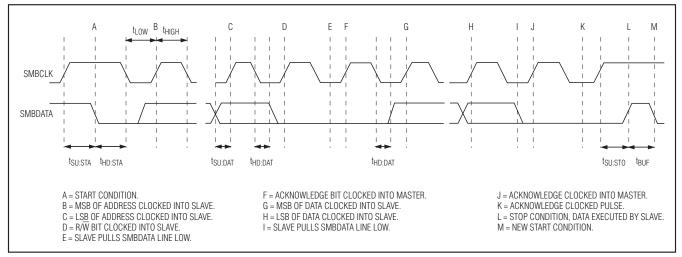

### I<sup>2</sup>C Interface (SDA, SCL)

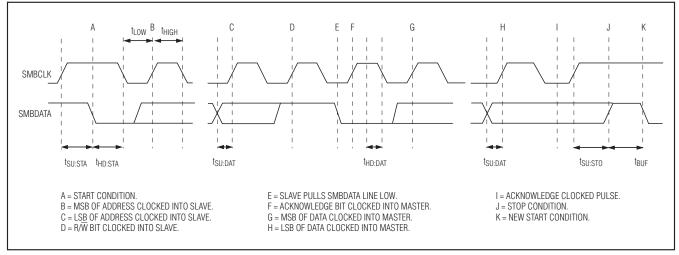

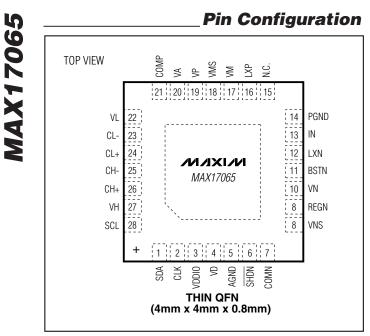

The MAX17065 supports an I<sup>2</sup>C-compatible, 2-wire digital interface. SDA is the bidirectional data line and SCL is the clock line of the 2-wire interface corresponding, respectively, to SDA and SDL lines of the I<sup>2</sup>C bus. The MAX17065 uses the write-byte and read-byte protocols (Figures 5 and 6). The I<sup>2</sup>C protocols are documented in the I<sup>2</sup>C-bus specification and user manual and are available at http://www.nxp.com/. The MA17065 is a slave-only device and responds to the 7-bit address 0b0100111. The read and write commands can be distinguished by adding 1 more bit (R/W bit) to the end of the 7-bit slave address, with one indicating read, and zero indicating write. The MAX17065 has six registers: a device control register (0x00), a VQP register (0x01), a VSW register (0x02), a status register (0x03), an MFG register (0x04), and an IREG register (0x05).

| WRITE BYTE FORMAT |                  |      |     |         |     |        |         |    |      |        |     |      |

|-------------------|------------------|------|-----|---------|-----|--------|---------|----|------|--------|-----|------|

| SI                | r addf           | RESS | WR  | ACK     | CC  | MMAND  | ACK     | D  | ATA  | ACK    |     | STOP |

|                   | 7 b              | oits |     |         |     | 8 bits |         | 8  | bits |        |     |      |

| READ              | READ BYTE FORMAT |      |     |         |     |        |         |    |      |        |     |      |

| ST                | ADDRESS          | WR   | ACK | COMMAND | ACK | RST    | ADDRESS | RD | ACK  | DATA   | /// | STOP |

|                   | 7 bits           |      |     | 8 bits  |     |        | 7 bits  | 1  |      | 8 bits |     |      |

Figure 5. I<sup>2</sup>C Protocols

MIXIM

15

**MAX17065**

Communication starts with the master signaling the beginning of a transmission with a START condition, which is a high-to-low transition on SDA while SCL is high. When the master has finished communicating with the slave, the master issues a STOP condition, which is a low-to-high transition on SDA while SCL is high. The bus is then free for another transmission. Figures 6 and 7 show the timing diagrams for signals on the 2-wire interface. The address byte, command byte, and data byte are transmitted between the START and STOP conditions. The SDA state is allowed to change only while SCL is low, except for the START and STOP conditions. Data is transmitted in 8-bit words and is sampled on the rising edge of SCL. Nine clock cycles are required to transfer each byte in or out of the MAX17065 since either the master or the slave acknowledges the receipt of the correct byte during the ninth clock. If the MAX17065 receives its correct slave address followed by R/W = 0, it expects to receive 1 or 2 bytes of information (depending on the protocol). If the device detects a START or STOP condition prior to clocking in the bytes of data, it considers this an error condition and disregards all the data. If the transmission is completed correctly, the registers are updated immediately after a STOP (or RESTART) condition. If the MAX17065 receives its correct slave address followed by R/W = 1, it expects to clock out the register data selected by the previous command byte.

(Table 6).

### **I<sup>2</sup>C Register Definitions**

All MAX17065 registers are byte wide and accessible through the read/write byte protocols mentioned in the previous section. Their bit assignments are provided in the following sections with reserved bits containing a default value of zero. Table 4 summarizes the register assignments. During shutdown, the serial interface remains fully functional.

#### Control Register (0x00)

The control register enables and disables the VA, VH, VL, VP, and VN outputs. Also, the operating frequency and the mode of operation for the step-up and inverting converters are controlled by this register.

**Output Enable and Fault Latch Reset**

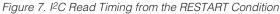

Setting ON1 to 1 enables VM to start up and the VA, VH, and VL outputs begin their soft-start procedures. Setting ON1 to 0 triggers a VA, VH, and VL shutdown sequence. Toggling ON1 to 0 has no effect if ON1 was previously set to 1 for less than 6ms or if ON2 is currently set to 1.

Setting ON2 to 1 enables the VP and VN soft-start procedure. Setting ON2 to 0 triggers the VP and VN shutdown

### **Table 4. Commands Description**

sequence. Toggling ON2 to 0 has no effect if ON2 was previously set to 1 for less than 6ms. See Table 5. Setting both ON1 and ON2 to 0 clears the fault latches

(see the *Status Register (0x03)* section). **Step-Up and Inverting Converter Operating Mode** Set SKIP/PWM to 0 for forced PWM or to 1 for skipmode operation of the step-up and inverting converters (VM and VN regulated outputs). If no value is written to

SKIP/PWM, forced-PWM mode is selected by default

Step-Up and Inverting Converter Operating Frequency Selection

Setting the FSET bit chooses the switching frequency for the step-up and inverting converters (VM and VN regulated outputs). Set FSET to 0 for 600kHz operation or to 1 for 1.2MHz operation. If no value is written to FSET, the 600kHz frequency is selected by default. See Table 7.

#### VQP Register (0x01)

The VQP register is used to set both VL and VH output regulation voltages.

| 00111110                      | DEGIOTED         | DATA-REGISTER BIT ASSIGNMENT |         |             |         |          |          |                |          |

|-------------------------------|------------------|------------------------------|---------|-------------|---------|----------|----------|----------------|----------|

| COMMAND REGISTER<br>BYTE NAME | BIT 7<br>(MSB)   | BIT 6                        | BIT 5   | BIT 4       | BIT 3   | BIT 2    | BIT 1    | BIT 0<br>(LSB) |          |

| 0x00                          | Control register | Reserve                      | FSET    | SKIP<br>PWM | Reserve | Reserve  | Reserve  | ON2            | ON1      |

| 0x01                          | VQP register     | VL3                          | VL2     | VL1         | VL0     | Reserve  | VH2      | VH1            | VH0      |

| 0x02                          | VSW register     | TEST1                        | TEST0   | IMAXP       | IMAXN   | VN3      | VN2      | VN1            | VN0      |

| 0x03                          | Status register  | VA fault                     | Reserve | Reserve     | Reserve | VL fault | VH fault | VN fault       | VM fault |

| 0xFE                          | MFG register     | 0                            | 1       | 0           | 0       | 1        | 1        | 0              | 1        |

| 0xFF                          | IDREG            | 0                            | 1       | 0           | 0       | 1        | 1        | 1              | 1        |

### Table 5. ON2 and ON1

| ON2 | ON1 | VA OUTPUT | VH, VL OUTPUTS | VP, VN OUTPUT | NOTES                                                         |

|-----|-----|-----------|----------------|---------------|---------------------------------------------------------------|

| 0   | 0   | OFF       | OFF            | OFF           | Clears fault latch.                                           |

| 0   | 1   | ON        | ON             | OFF           | —                                                             |

| 1   | 0   | ON        | ON             | ON            | VP/VN are turned on after when VH/VL soft-start is completed. |

| 1   | 1   | ON        | ON             | ON            | VP/VN are turned on after when VH/VL soft-start is completed. |

### Table 6. SKIP/PWM

| SKIP/PWM | OPERATING MODE | NOTES             |

|----------|----------------|-------------------|

| 0        | Forced PWM     | Default condition |

| 1        | SKIP           |                   |

### Table 7. FSET

| FSET | OPERATING<br>FREQUENCY (MHz) | NOTES             |

|------|------------------------------|-------------------|

| 0    | 0.6                          | Default condition |

| 1    | 1.2                          |                   |

**Positive Charge-Pump Regulation Voltage (VH)** Set the VH bits to program the VH regulation voltage according to Table 8.

### Table 8. VH[2:0]

| VH[2:0] | VH REGULATION<br>VOLTAGE (V) | NOTES             |

|---------|------------------------------|-------------------|

| 0b000   | 5.5                          | Default condition |

| 0b001   | 6.0                          | —                 |

| 0b010   | 6.5                          | —                 |

| 0b011   | 7.0                          | —                 |

| 0b100   | 7.5                          | —                 |

| 0b101   | 8.0                          | —                 |

| 0b110   | 8.5                          | —                 |

| 0b111   | 9.0                          | _                 |

**Negative Charge-Pump Regulation Voltage (VL)** Set the VL bits to program the VL regulation voltage according to Table 9.

### Table 9. VL[3:4]

| VN REGULATION<br>VOLTAGE (V) | NOTES                                                                      |  |  |  |  |

|------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| -0.5                         | Default condition                                                          |  |  |  |  |

| -1.0                         | —                                                                          |  |  |  |  |

| -1.5                         | —                                                                          |  |  |  |  |

| -2.0                         | —                                                                          |  |  |  |  |

| -2.5                         | —                                                                          |  |  |  |  |

| -3.0                         | —                                                                          |  |  |  |  |

| -3.5                         | —                                                                          |  |  |  |  |

| -4.0                         | —                                                                          |  |  |  |  |

| -4.5                         | —                                                                          |  |  |  |  |

| -5.0                         | _                                                                          |  |  |  |  |

|                              | VOLTAGE (V)   -0.5   -1.0   -1.5   -2.0   -2.5   -3.0   -3.5   -4.0   -4.5 |  |  |  |  |

### VSW Register (0x02)

The VSW register sets the VN regulation voltage and sets the maximum current limit for LXP and LXN. Also, this register can be programmed to disable the VH, VL, VP, and VN outputs such that they can be driven by external voltage sources.

### VN Regulation Voltage

Set the VN bits to program the output voltage of VN according to Table 10.

### LXN Peak Current Limit

The IMAXN bit is used to select the peak LXN current for the inverting converter. Setting IMAXN to 0 selects an LXN peak current limit of 450mA (typ), while setting

### Table 10. VN[3:0]

| <u> </u> |                              |                   |  |  |  |  |

|----------|------------------------------|-------------------|--|--|--|--|

| VN[3:0]  | VN REGULATION<br>VOLTAGE (V) | NOTES             |  |  |  |  |

| 0b0000   | -0.5                         | Default condition |  |  |  |  |

| 0b0001   | -1.0                         | —                 |  |  |  |  |

| 0b0010   | -1.5                         | —                 |  |  |  |  |

| 0b0011   | -2.0                         | —                 |  |  |  |  |

| 0b0100   | -2.5                         | —                 |  |  |  |  |

| 0b0101   | -3.0                         | —                 |  |  |  |  |

| 0b0110   | -3.5                         | —                 |  |  |  |  |

| 0b0111   | -4.0                         | —                 |  |  |  |  |

| 0b1000   | -4.5                         |                   |  |  |  |  |

| 0b1001   | -5.0                         |                   |  |  |  |  |

IMAXN to 1 selects an LXN peak current limit of 700mA (typ). If no value is written to IMAXN, the LXN current limit is set to 450mA (typ) by default. See Table 11.

### Table 11. IMAXN

| IMAXN | OPERATING MODE<br>(mA) | NOTES             |

|-------|------------------------|-------------------|