# Ideal Diode, Reverse-Battery, and Overvoltage Protection Switch/Limiter Controllers with External MOSFETs

### **General Description**

The MAX16914/MAX16915 low-quiescent-current overvoltage and reverse-battery protection controllers are designed for automotive and industrial systems that must tolerate high-voltage transient and fault conditions. These conditions include load dumps, voltage dips, and reversed input voltages. The controllers monitor the input voltage on the supply line and control two external pFETs to isolate the load from the fault condition. The external pFETs are turned on when the input supply exceeds 4.5V and stay on up to the programmed overvoltage threshold. During high-voltage fault conditions, the controllers regulate the output voltage to the set upper threshold voltage (MAX16915), or switch to high resistance (MAX16914) for the duration of the overvoltage transient to prevent damage to the downstream circuitry. The overvoltage event is indicated through an active-low, open-drain output,  $\overline{OV}$ .

The reverse-battery pFET behaves as an ideal diode, minimizing the voltage drop when forward biased. Under reverse bias conditions, the pFET is turned off, preventing a downstream tank capacitor from being discharged into the source.

Shutdown control turns off the IC completely, disconnecting the input from the output and disconnecting TERM from its external resistor-divider to reduce the quiescent current to a minimum.

Both devices are available in a 10-pin  $\mu \text{MAX} \& \text{package}$  and operate over the automotive -40°C to +125°C temperature range.

# **Applications**

Industrial

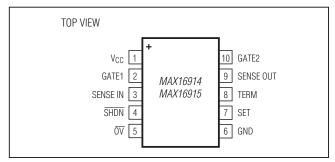

# **Pin Configuration**

μΜΑΧ is a registered trademark of Maxim Integrated Products, Inc.

#### **Benefits and Features**

- Architecture Replaces Protection Diodes Reducing the Forward Voltage, Allowing Operation During Cold-Crank Conditions

- Transient Voltage Protection Up to +44V and -75V

- Low-Voltage Drop when Used with Properly Sized External pFETs

- 4.5V to 19V Input-Voltage Operation

- Ideal Diode Reverse-Battery Protection Supports Down to -75V to Protect System During Negative-Voltage Transients

- Back-Charge Prevention Avoids Discharging Downstream Tank Capacitance

- Overvoltage Protection Enables System to Survive Up to a +44V Load Dump

- · Overvoltage Indicator

- · Thermal-Overload Protection

- Low Operating Current Meets Stringent Module Specifications While Maintaining System Protection

- · 29µA Low Operating Current

- 6µA Low Shutdown Current

Ordering Information appears at end of data sheet.

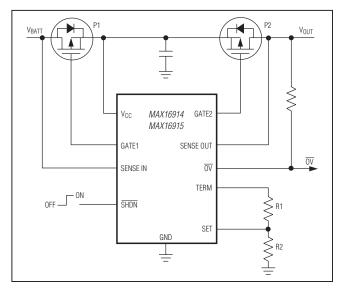

# **Typical Operating Circuit**

# Ideal Diode, Reverse-Battery, and Overvoltage Protection Switch/Limiter Controllers with External MOSFETs

### **Absolute Maximum Ratings**

| V <sub>CC</sub> , SENSE OUT, TERM, $\overline{\text{SHDN}}$ , $\overline{\text{OV}}$ to GND for $\leq$ 400ms0.3V to +44V | GATE1, GATE2 to GND0.3V to (V <sub>CC</sub> + 0.3V)<br>SET to GND0.3V to +8V |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| VCC, SENSE OUT, TERM, SHDN, OV to GND                                                                                    | Continuous Power Dissipation (TA = +70°C)                                    |

| for ≤ 90s0.3V to +28V                                                                                                    | 10-Pin $\mu$ MAX (derate 8.8mW/°C above T <sub>A</sub> = +70°C)              |

| V <sub>CC</sub> , SENSE OUT, TERM, SHDN, OV to GND0.3V to +20V                                                           | (Note 1)707mW                                                                |

| SENSE IN to GND for $\leq$ 2ms75V to +44V                                                                                | Operating Temperature Range40°C to +125°C                                    |

| SENSE IN to GND for $\leq$ 90s18V to +44V                                                                                | Junction Temperature+150°C                                                   |

| SENSE IN to GND0.3V to +20V                                                                                              | Storage Temperature Range65°C to +150°C                                      |

| GATE1, GATE2 to V <sub>CC</sub> 16V to +0.3V                                                                             | Lead Temperature (soldering, 10s)+300°C                                      |

|                                                                                                                          |                                                                              |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{CC} = 14V, C_{GATE1} = 32nF, C_{GATE2} = 32nF, \overline{SHDN} = high, T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                   | SYMBOL | COND                           | ITIONS                              | MIN  | TYP   | MAX  | UNITS |

|-------------------------------------------------------------|--------|--------------------------------|-------------------------------------|------|-------|------|-------|

| Operating Voltage Range                                     | Vcc    | (Note 3)                       |                                     | 4.5  |       | 19   | V     |

|                                                             |        |                                | T <sub>A</sub> = +25°C              |      | 6.0   | 12   |       |

| Shutdown Supply Current (ISENSE IN + ISENSE OUT + IOV +     | ISHDN  | VSENSE OUT = 0V,<br>VTERM = 0V | T <sub>A</sub> = +85°C (Note 3)     |      | 6.1   | 12   | μA    |

| ISHDN + IVCC)                                               |        |                                | $T_A = +125^{\circ}C$ (Note 3)      |      | 6.2   | 12   |       |

|                                                             |        |                                | TA = +25°C                          |      | 29    | 53   |       |

| Quiescent Supply Current<br>(ISENSE IN + ISENSE OUT + IOV + | IQ     | IQ SHDN = high                 | T <sub>A</sub> = +85°C (Note 3)     |      | 30    | 55   | μA    |

| ISHDN + IVCC)                                               |        |                                | T <sub>A</sub> = +125°C<br>(Note 3) |      | 31    | 57   |       |

| VCC Undervoltage Lockout                                    | Vuvlo  | VCC rising, VSET =             | 1V , SHDN = high                    |      | 4.06  | 4.35 | V     |

| V <sub>CC</sub> Undervoltage-Lockout<br>Hysteresis          |        |                                |                                     |      | 8     |      | %     |

| SET Threshold Voltage                                       | VSETTH | V <sub>SET</sub> rising        |                                     | -3%  | +1.20 | +3%  | V     |

| SET Threshold Voltage<br>Hysteresis                         | VSETHY |                                |                                     |      | 4     |      | %     |

| SET Input Current                                           | ISET   | V <sub>SET</sub> = 1V          |                                     |      | 0.02  | 0.2  | μA    |

| SHDN Low Threshold                                          | VSHDNL |                                |                                     |      |       | 0.4  | V     |

| SHDN High Threshold                                         | VSHDNH |                                |                                     | 1.4  |       |      | V     |

| SHDN Pulldown Current                                       | ISHDN  | VSHDN = 14V, inter             | nally pulled to GND                 |      | 0.5   | 1.0  | μΑ    |

| V <sub>CC</sub> to GATE Output Low<br>Voltage               | VGVCC1 | VCC = 14V                      |                                     | 6.25 | 7.5   | 8.5  | V     |

| VCC to GATE Clamp Voltage                                   | VGVCC2 | VCC = 42V                      |                                     |      |       | 14   | V     |

www.maximintegrated.com Maxim Integrated | 2

### **Electrical Characteristics (continued)**

$(V_{CC} = 14V, C_{GATE1} = 32nF, C_{GATE2} = 32nF, \overline{SHDN} = high, T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                | SYMBOL               | CONDITIONS                                                                      | MIN | TYP   | MAX | UNITS |

|----------------------------------------------------------|----------------------|---------------------------------------------------------------------------------|-----|-------|-----|-------|

| TERM On-Resistance                                       | RTERM                | SHDN = high                                                                     |     | 150   | 500 | Ω     |

| TERM Output Current                                      | ITERM                | SHDN = low, V <sub>TERM</sub> = 0V                                              |     |       | 1.0 | μΑ    |

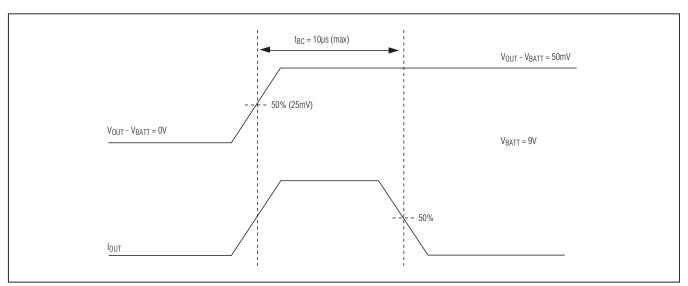

| Back-Charge Voltage Fault<br>Threshold                   | V <sub>BCTH</sub>    | VSENSE OUT = 14V (Note 4)                                                       | 18  | 25    | 32  | mV    |

| Back-Charge Voltage Threshold Hysteresis                 | V <sub>BCHY</sub>    | VSENSE OUT = 14V                                                                |     | 50    |     | mV    |

| Back-Charge Turn-Off Time (GATE1)                        | tBC                  | VCC = 9.5V, VSENSE IN = 9V,<br>VSENSE OUT stepped from 4.9V to 9.5V<br>(Note 5) |     | 6     | 10  | μs    |

| Back-Charge Recovery Time (GATE1)                        | <sup>†</sup> BCREC   | VCC = 9.5V, VSENSE IN = 9V,<br>VSENSE OUT stepped from 9.5V to 4.9V<br>(Note 6) |     | 18    | 30  | μs    |

| GATE2 Turn-Off Time                                      |                      | VCC = 9.5V, VSET rising from 1V to 1.5V (Note 7)                                |     | 3     |     | μs    |

| GATE2 Turn-On Time                                       |                      | VCC = 9.5V, VSET falling from 1.5V to 1V (Note 8)                               |     | 20    |     | μs    |

| Startup Response Time (VSHDN Rising)                     | tSTART1              | VCC = 9.5V, from VSHDN rising to VGATE_ falling (Note 9)                        |     | 100   |     | μs    |

| Startup Response Time (VCC Rising)                       | tSTART2              | VCC rising from 2V to 4.5V, SHDN = high (Note 10)                               |     | 0.150 |     | ms    |

| Reverse-Battery Voltage Turn-Off Time/UVLO Turn-Off Time | <sup>†</sup> REVERSE | VCC and VSENSE IN falling from 4.25V to 3.25V, VSENSE OUT = 4.25V (Note 11)     |     |       | 30  | μs    |

| Thermal-Shutdown Temperature                             |                      |                                                                                 |     | +170  |     | °C    |

| Thermal-Shutdown Hysteresis                              |                      |                                                                                 |     | 20    |     | °C    |

| OV Output Low Voltage                                    | Vovbl                | ISINK = 600µA                                                                   |     |       | 0.4 | V     |

| OV Open-Drain Leakage Current                            | I <sub>OVB</sub>     | V <sub>SET</sub> = 1.0V                                                         |     |       | 1.0 | μΑ    |

| SENSE IN Input Current                                   | ISENSE IN            | VSHDN = 0/14V                                                                   |     | 1     | 5   | μΑ    |

| SENSE OUT Input Current                                  | ISENSE OUT           | VSHDN = 0/14V                                                                   |     | 2     | 5   | μA    |

| SET to OV Output Low<br>Propagation Delay                | tovbpd               | VCC = 9.5V, VSET rising from 1V to 1.5V to VOV falling                          |     | 3     |     | μs    |

- **Note 2:** All parameters are production tested at T<sub>A</sub> = +25NC. Limits over the operating temperature range are guaranteed by design and characterization.

- **Note 3:** Guaranteed by design and characterization.

- Note 4: The back-charge voltage, VBC, is defined as the voltage at SENSE OUT minus the voltage at SENSE IN.

- Note 5: Defined as the time from when VBC exceeds VBCTH (25mV typ) to when VGATE1 exceeds VCC 3.5V.

- Note 6: Defined as the time from when VBC falls below VBCTH 50mV to when VGATE1 falls below VCC 3.5V.

- Note 7: Defined as the time from when VSET exceeds VSETTH (1.20V typ) to when VGATE2 exceeds VCC 3.5V.

- Note 8: Defined as the time from when VSET falls below VSETTH 5% (1.14V typ) to when VGATE2 falls below VCC 3.5V.

- Note 9: The external pFETs can turn on tSTART after the IC is powered up and all input conditions are valid.

- Note 10: Defined as the time from when VCC exceeds the undervoltage-lockout threshold (4.3V max) to when VGATE1 and VGATE2 fall below 1V.

- Note 11: Defined as the time from when V<sub>CC</sub> falls below V<sub>SENSE</sub> O<sub>UT</sub> 25mV to when V<sub>GATE1</sub> reaches V<sub>CC</sub> 1.75V.

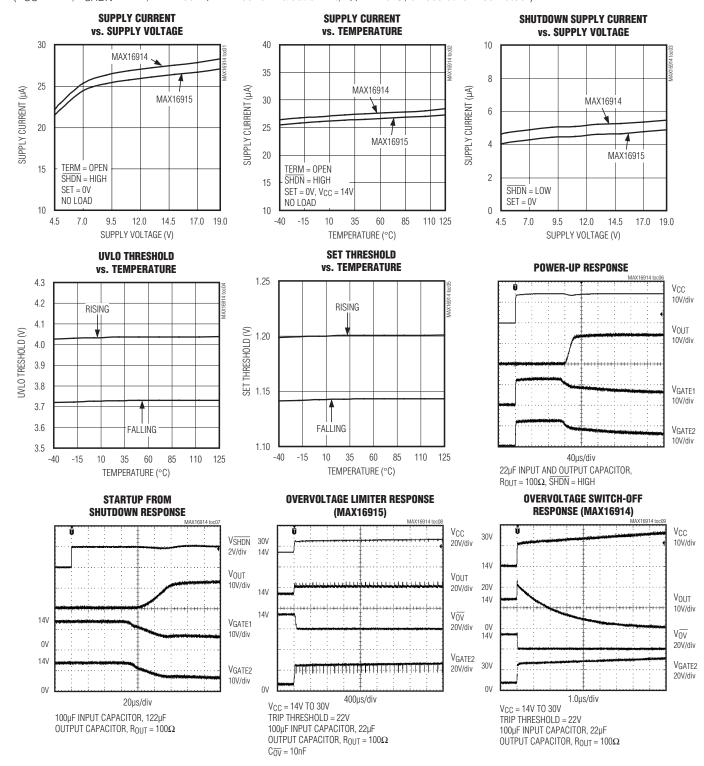

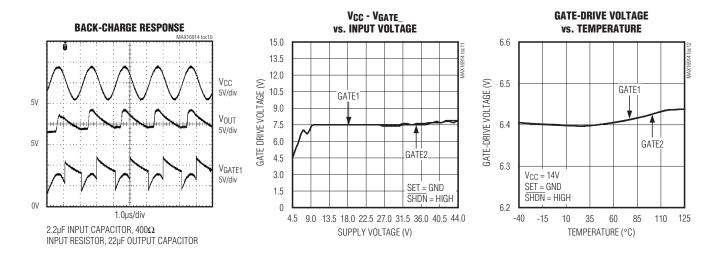

### **Typical Operating Characteristics**

(VCC = 14V, VSHDN = 14V, MAX16914/MAX16915 Evaluation Kit, TA = +25°C, unless otherwise noted.)

# **Typical Operating Characteristics (continued)**

(VCC = 14V, VSHDN = 14V, MAX16914/MAX16915 Evaluation Kit, TA = +25°C, unless otherwise noted.)

## **Pin Description**

| PIN | NAME      | FUNCTION                                                                                                                                                                                                                                               |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Vcc       | Positive Supply Input Voltage. Bypass VCC to GND with a 0.1µF or greater ceramic capacitor.                                                                                                                                                            |

| 2   | GATE1     | Gate-Driver Output. Connect GATE1 to the gate of an external p-channel FET pass switch to provide low drain-to-source voltage drop, reverse voltage protection, and back-charge prevention.                                                            |

| 3   | SENSE IN  | Differential Voltage Sense Input (Input Side of IC). Used with SENSE OUT to provide back-charge prevention when the SENSE IN voltage falls below the SENSE OUT voltage by 25mV.                                                                        |

| 4   | SHDN      | Active-Low Shutdown/Wake Input. Drive SHDN high to turn on the voltage detectors. GATE2 is shorted to VCC when SHDN is low. SHDN is internally pulled to GND through a 0.5µA current sink. Connect SHDN to VCC for always-on operation.                |

| 5   | OV        | Open-Drain Overvoltage Indicator Output. Connect a pullup resistor from $\overline{\text{OV}}$ to a positive supply such as VCC. $\overline{\text{OV}}$ is pulled low when the voltage at SET exceeds the internal threshold.                          |

| 6   | GND       | Ground                                                                                                                                                                                                                                                 |

| 7   | SET       | Controller Overvoltage Threshold Programming Input. Connect SET to the center of an external resistive divider network between TERM and GND to adjust the desired overvoltage switch-off or limiter threshold.                                         |

| 8   | TERM      | Voltage-Divider Termination Output. TERM is internally connected to SENSE OUT in the MAX16915 and to VCC in the MAX16914. TERM is high impedance when SHDN is low, forcing the current to zero in the resistor-divider connected to TERM.              |

| 9   | SENSE OUT | Differential Voltage Sense Input (Output Side Of IC). Used with SENSE IN to provide back-charge prevention when the SENSE IN voltage falls below the SENSE OUT voltage by 25mV.                                                                        |

| 10  | GATE2     | Gate-Driver Output. Connect GATE2 to the gate of an external p-channel FET pass switch. GATE2 is driven low during normal operation and quickly regulated or shorted to VCC during an overvoltage condition. GATE2 is shorted to VCC when SHDN is low. |

www.maximintegrated.com Maxim Integrated | 5

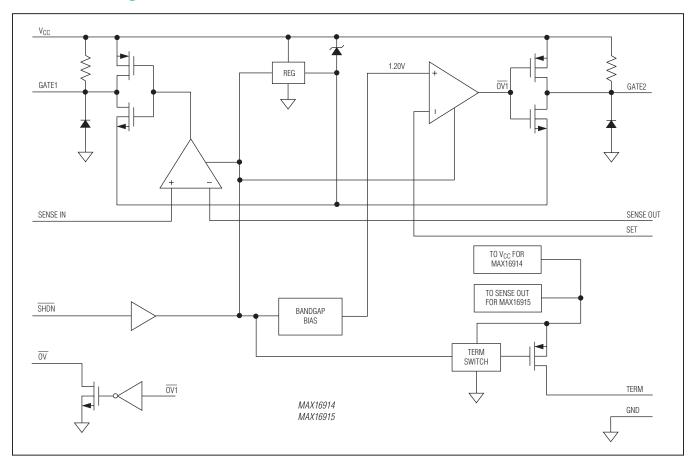

### **Functional Diagram**

### **Detailed Description**

The MAX16914/MAX16915 are ultra-small, low-quiescent, high load-current, overvoltage-protection circuits for automotive or industrial applications. These devices monitor the input and output voltages and control two p-channel MOSFETs to protect downstream loads from reverse-battery, overvoltage, and high-voltage transient conditions and prevent downstream tank capacitors from discharging into the source (back-charging).

One MOSFET (P1) eliminates the need for external diodes, thus minimizing the input voltage drop and provides back-charge and reverse-battery protection. The second MOSFET (P2) isolates the load or regulates the output voltage during an overvoltage condition. These ICs allow system designers to size the external p-channel MOSFET to their load current, voltage drop, and board size.

# Overvoltage Switch-Off Controller (MAX16914)

In the MAX16914, the input voltage is monitored (TERM is internally shorted to VCC—see the *Functional Diagram*) making the device an overvoltage switch-off controller. As the VCC voltage rises, and the programmed overvoltage threshold is tripped, the internal fast comparator turns off the external p-channel MOSFET (P2), pulling GATE2 to VCC to disconnect the power source from the load. When the monitored voltage goes below the adjusted overvoltage threshold, the MAX16914 enhances GATE2, reconnecting the load to the power source.

www.maximintegrated.com Maxim Integrated | 6

# Overvoltage Limiter Controller (MAX16915)

In the MAX16915, TERM is internally connected to SENSE OUT (see the *Functional Diagram*) allowing the IC to operate in voltage-limiter mode.

During normal operation, GATE2 is pulled low to fully enhance the MOSFET. The external MOSFET's drain voltage is monitored through a resistor-divider between TERM, SET, and GND. When the output voltage rises above the adjusted overvoltage threshold, an internal comparator pulls GATE2 to VCC turning off P2. When the monitored voltage goes below the overvoltage threshold (-4% hysteresis), the p-channel MOSFET (P2) is turned on again. During a continuous overvoltage condition, MOSFET (P2) cycles on and off (between the overvoltage threshold and the hysteresis), generating a sawtooth waveform with a frequency dependent on the load capacitance and load current. This process continues to keep the voltage at the output regulated to within approximately a 4% window. The output voltage is regulated during the overvoltage transients and MOSFET (P2) continues to conduct during the overvoltage event, operating in switched-linear mode.

Caution must be exercised when operating the MAX16915 in voltage-limiting mode for long durations due to the MOSFET's power-dissipation consideration (see the MOSFET Selection section).

#### **Shutdown**

The MAX16914/MAX16915 feature an active-low shutdown input (SHDN). Drive SHDN low to switch off FET (P2), disconnecting the input from the output, thus placing the IC in low-quiescent-current mode. Reverse-battery protection is still maintained.

#### **Reverse-Battery Protection**

The MAX16914/MAX16915 feature reverse-battery protection to prevent damage to the downstream circuitry caused by battery reversal or negative transients. The reverse-battery protection blocks the flow of current into the downstream load and allows the circuit designer to remove series-protection diodes.

#### **Back-Charge Switch-Off**

The MAX16914/MAX16915 monitor the input-to-output differential voltage between SENSE IN and SENSE OUT. It turns off the external FET (P1) when (VSENSE OUT - VSENSE IN) > 25mV (see Figure 1) to prevent discharging of a downstream tank capacitor into the battery supply during an input voltage drop, such as a cold-crank condition or during a superimposed sinusoidal voltage on top of the supply voltage. It turns on the FET (P1) again if the back-charge voltage threshold hysteresis of 50mV is satisfied.

Figure 1. Back-Charge Turn-Off Time

### Overvoltage Indicator Output (OV)

The MAX16914/MAX16915 include an active-low, open-drain overvoltage-indicator output ( $\overline{OV}$ ). For the MAX16914,  $\overline{OV}$  asserts low when VCC exceeds the programmed overvoltage threshold.  $\overline{OV}$  deasserts when the overvoltage condition is over.

For the MAX16915,  $\overline{OV}$  asserts if  $\overline{VOUT}$  exceeds the programmed overvoltage threshold.  $\overline{OV}$  deasserts when VOUT drops 4% (typ) below the overvoltage threshold level. If the overvoltage condition continues,  $\overline{OV}$  may toggle with the same frequency as the overvoltage limiter FET (P2). If the P2 device is turned on for a very short period (less than tovBPD), the  $\overline{OV}$  pin may not toggle. To obtain a logic-level output, connect a 45k $\Omega$  pullup resistor from  $\overline{OV}$  to a system voltage less than 44V. A capacitor connected from  $\overline{OV}$  to GND helps extend the time that the logic level remains low.

### **Applications Information**

#### **Load Dump**

Most automotive applications run off a multicell "12V" lead-acid battery with a nominal voltage that swings between 9V and 16V (depending on load current, charging status, temperature, battery age, etc.). The battery voltage is distributed throughout the automobile and is locally regulated down to voltages required by the different system modules. Load dump occurs when the alternator is charging the battery and the battery becomes disconnected. The alternator voltage regulator is temporarily driven out of control. Power from the alternator flows into the distributed power system and elevates the voltage seen at each module. The voltage spikes have rise times typically greater than 5ms and decays within several hundred milliseconds but can extend out to 1s or more depending on the characteristics of the charging system. These transients are capable of destroying sensitive electronic equipment on the first "fault event."

#### **Setting Overvoltage Thresholds**

TERM and SET provide an accurate means to set the overvoltage level for the MAX16914/MAX16915. Use a resistive divider to set the desired overvoltage condition (see the *Typical Operating Circuit*). VSET has a rising 1.20V threshold with a 4% falling hysteresis. Begin by selecting the total end-to-end resistance:

$$RTOTAL = R1 + R2$$

For high accuracy, choose R<sub>TOTAL</sub> to yield a total current equivalent to a minimum 100 x I<sub>SET</sub> where I<sub>SET</sub> is the input bias current at SET.

For example:

With an overvoltage threshold (Vov) set to 20V, R<sub>TOTAL</sub> < 20V/(100 x ISET), where ISET = 1 $\mu$ A (max).

RTOTAL <

$$200k\Omega$$

Use the following formula to calculate R2:

where V<sub>TH</sub> is the 1.20V SET rising threshold and V<sub>OV</sub> is the desired overvoltage threshold.

Then,  $R2 = 12.0k\Omega$ .

Use the nearest standard-value resistor lower than the calculated value. A lower value for total resistance dissipates more power but provides slightly better accuracy.

To determine R1:

$$RTOTAL = R2 + R1$$

Then, R1 =  $188k\Omega$ .

Use the nearest standard-value resistor lower than the calculated value. A lower value for total resistance dissipates more power but provides slightly better accuracy.

#### **MOSFET Selection**

#### Output p-Channel MOSFET (P2)

Select the external output MOSFET according to the application current level. The MOSFET's on-resistance (RDS(ON)) should be chosen low enough to have a minimum voltage drop at full load to limit the MOSFET power dissipation. Determine the device power rating to accommodate an overvoltage fault when operating the MAX16915 in overvoltage-limiting mode. During normal operation for either IC, the external MOSFET dissipates little power. The power dissipated in the MOSFET during normal operation is:

$$PNORM = ILOAD^2 \times RDS(ON)$$

where P<sub>NORM</sub> is the power dissipated in the MOSFET in normal operation, I<sub>LOAD</sub> is the output load current, and R<sub>DS(ON)</sub> is the drain-to-source resistance of the MOSFET. Worst-case power dissipation in the output MOSFET occurs during a prolonged overvoltage event when operating the MAX16915 in voltage-limiting mode. The power dissipated across the MOSFET is as follows:

where POVLO is the power dissipated in the MOSFET in overvoltage-limiting operation, VDS is the voltage across the MOSFET's drain and source, and ILOAD is the load current.

# Ideal Diode, Reverse-Battery, and Overvoltage Protection Switch/Limiter Controllers with External MOSFETs

#### **Reverse-Polarity Protection MOSFET (P1)**

Most battery-powered applications must include reverse-voltage protection. Many times this is implemented with a diode in series with the battery. The disadvantage in using a diode is the forward-voltage drop of the diode, which reduces the operating voltage available to downstream circuits (VLOAD = VBATTERY - VDIODE).

The MAX16914/MAX16915 include high-voltage GATE1 drive circuitry allowing users to replace the high-voltage drop series diode with a low-voltage-drop MOSFET device (as shown in the *Typical Operating Circuit*). The forward-voltage drop is reduced to ILOAD x RDS(ON) of P1. With a suitably chosen MOSFET, the voltage drop can be reduced to millivolts.

In normal operating mode, internal GATE1 output circuitry enhances P1. The constant enhancement ensures P1 operates in a low  $R_{DS(ON)}$  mode, but the gate-source junction is not overstressed during high battery-voltage applications or transients (many MOSFET devices specify a  $\pm 20V$  VGS absolute maximum). As VCC drops below

### **Chip Information**

PROCESS: BICMOS

## **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| MAX16914AUB+ | -40°C to +125°C | 10 μMAX     |

| MAX16915AUB+ | -40°C to +125°C | 10 μMAX     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

10V, GATE1 is limited to GND, reducing P1 VGS to VCC. In normal operation, the P1 power dissipation is very low:

$$P1 = ILOAD^2 \times RDS(ON)$$

During reverse-battery conditions, GATE1 is limited to GND and the P1 gate-source junction is reverse biased. P1 is turned off and neither the MAX16914/MAX16915 nor the load circuitry is exposed to the reverse-battery voltage. Care should be taken to place P1 (and its internal drain-to-source diode) in the correct orientation for proper reverse-battery operation.

#### **Thermal Shutdown**

The MAX16914/MAX16915 thermal-shutdown feature turns off both MOSFETs if the IC junction temperature exceeds the maximum allowable thermal dissipation. When the junction temperature exceeds  $T_J = +170^{\circ}\text{C}$ , the thermal sensor signals the shutdown logic, turning off both GATE1 and GATE2 outputs and allowing the device to cool. The thermal sensor turns GATE1 and GATE2 on again after the IC's junction temperature cools by 20°C. For continuous operation, do not exceed the absolute maximum junction-temperature rating of  $T_J = +150^{\circ}\text{C}$ .

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE        | LAND        |

|---------|---------|----------------|-------------|

| TYPE    | CODE    | NO.            | PATTERN NO. |

| 10 μMAX | U10+2   | <u>21-0061</u> | 90-0330     |

# Ideal Diode, Reverse-Battery, and Overvoltage Protection Switch/Limiter Controllers with External MOSFETs

# **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                          | PAGES<br>CHANGED |

|--------------------|---------------|--------------------------------------------------------------------------------------|------------------|

| 0                  | 9/09          | Initial release                                                                      | _                |

| 1                  | 4/13          | Added commercial-grade OPNs to Ordering Information                                  | 1                |

| 2                  | 10/14         | Removed automotive reference from Applications and /V OPNs from Ordering Information | 1                |

| 3                  | 2/15          | Updated the Benefits and Features section                                            | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.