# **TMC2084**

# Standalone Mode CircLink<sup>TM</sup> Controller

#### **Datasheet**

#### **PRODUCT FEATURES**

- Low Power CMOS, 3.3 Volt Power Supply with 5 Volt Tolerant I/O

- Enhanced Token Passing Protocol from ARCNET

- Maximum 15 node per network

- Token Retry Mechanism

- 64/128 Byte Per Packet

- Consecutive Node ID Assignment

- Memory Mirror

- Shared Memory Within Network

- Network Standard Time

- Network Time Synchronization

- Automatic Time Stamping

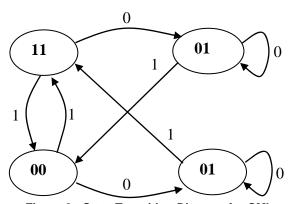

- Coded Mark Inversion

- Intelligent 1-Bit Error Correction

- Magnetic Saturation Prevention

- Standalone I/O Mode Operates without MCU

- Supports 16 Bit Input and 16 Bit Output

- Up to 14 Intelligent Remote I/O Ports:

- Programmable with 8-bit basis (16 to 32 outputs; 0 to 16 inputs)

- Selectable output type (push-pull or open-drain)

- The part of port is definable as strobe outputs and/or external trigger inputs

- The anti-chatter circuit on the input port can be set in ON/OFF

- The sampling frequency of the anti-chatter circuit can be set (19.1Hz/1.22KHz)

- Feature Rich Transmit Trigger:

- After receiving OUTPUT DATA packet or expiring onchip timer

- Continuous transmission

- External trigger input

- Flexible Transceiver Interface:

- RS-485 transceiver + twist pair cable

- RS-485 transceiver + pulse transformer + twist pair cable

- Hybrid transceiver (HYC4000 or HYC2000 from SMSC Japan)

- Fiber Optics also supported

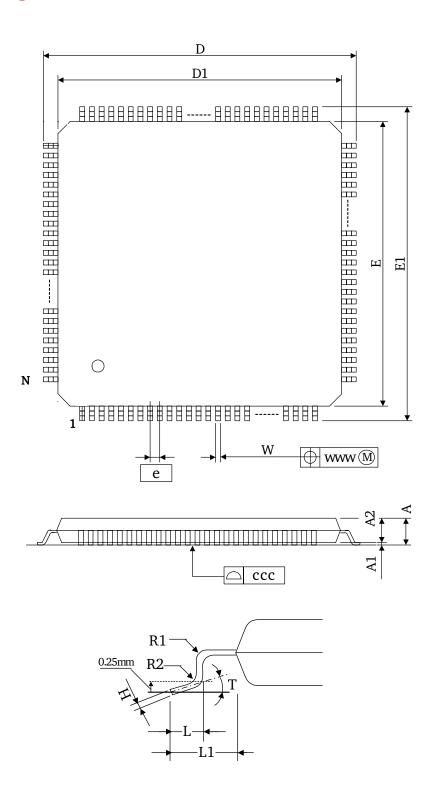

- 48-Pin, TQFP Lead-Free RoHS Compliant Package

- Body size: 7 × 7mm; pitch: 0.5mm

- Temperature Range from 0 to 70 degrees C

#### ORDERING INFORMATION

Order Number(s):

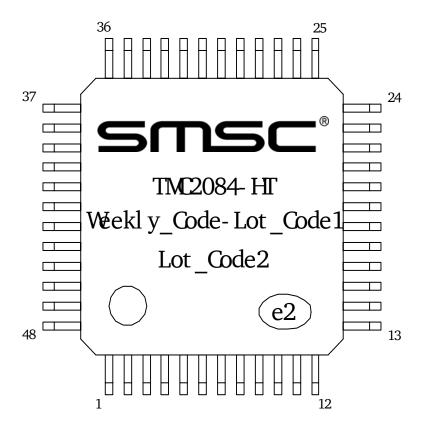

TMC2084-HT for 48 pin, TQFP Lead-Free RoHS Compliant Package

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright @ 2008 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| Cha             | apter 1        | General Description                              | 5        |

|-----------------|----------------|--------------------------------------------------|----------|

| 1.1             | Abou           | t CircLink                                       | 5        |

| 1.2             | Abou           | t TMC2084                                        | <u>5</u> |

| 1.3             |                | Diagram                                          |          |

| 1.4             |                | ist                                              |          |

| 1.5             |                | ut                                               |          |

| 1.5             | 1 11100        | ut                                               |          |

| Cha             | apter 2        | Functional Description                           |          |

| 2.1             |                | ork Configuration                                |          |

|                 | 2.1.1          | General                                          |          |

|                 | 2.1.2          | Configuration Examples                           |          |

|                 |                | Configuration                                    |          |

|                 | 2.2.1          | Configuration Using Shared Pins                  |          |

|                 | 2.2.2          | Configuration Through the Network                |          |

|                 | 2.2.3          | Returning Configuration Data                     |          |

|                 | -              | s of Packets                                     |          |

|                 | 2.3.1          | Packets TMC2084 Can Receive                      | 30       |

|                 | 2.3.2          | Packets TMC2084 Can Transmit                     |          |

|                 |                | mand Packets                                     |          |

| 2.7             | 2.4.1          | Format of COMMAND Packets                        |          |

| 25              |                | PUT PORTs                                        |          |

| 2.0             | 2.5.1          | Format of OUTPUT DATA Packets                    | -رد      |

|                 | 2.5.2          | Configuring I/O Port Directions                  |          |

|                 | 2.5.3          | Open-Drain Mode                                  |          |

|                 | 2.5.4          | Initializing OUTPUT PORTs                        |          |

|                 | 2.5.5          | Switching Timing In OUTPUT PORTs                 | 36       |

|                 |                | T PORT                                           |          |

|                 | 2.6.1          | Format of Input Data Packets                     |          |

|                 |                | OUTPUT                                           |          |

| ,               | 2.7.1          | Flag Descriptions                                |          |

|                 | 2.7.2          | Pulse Level Width Of Each Output Flag            |          |

| 2.8             |                | s Bits                                           |          |

|                 |                | Time Stamps                                      |          |

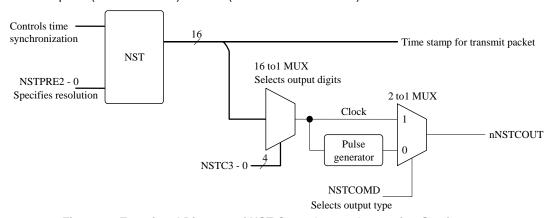

|                 | 2.9.1          | Time Synchronization                             |          |

|                 | 2.9.2          | Carry Output                                     |          |

| 2.10            |                | Il Coding                                        |          |

| 2.1             |                | M Image On Host Side                             |          |

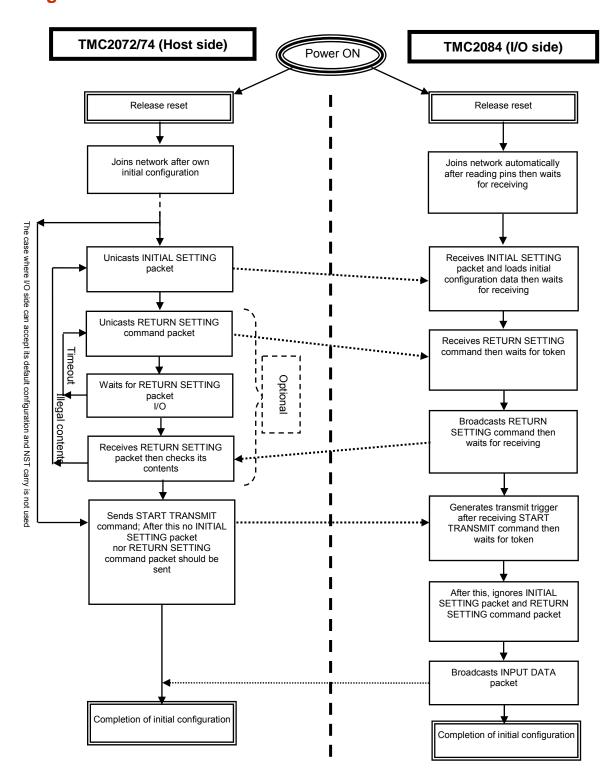

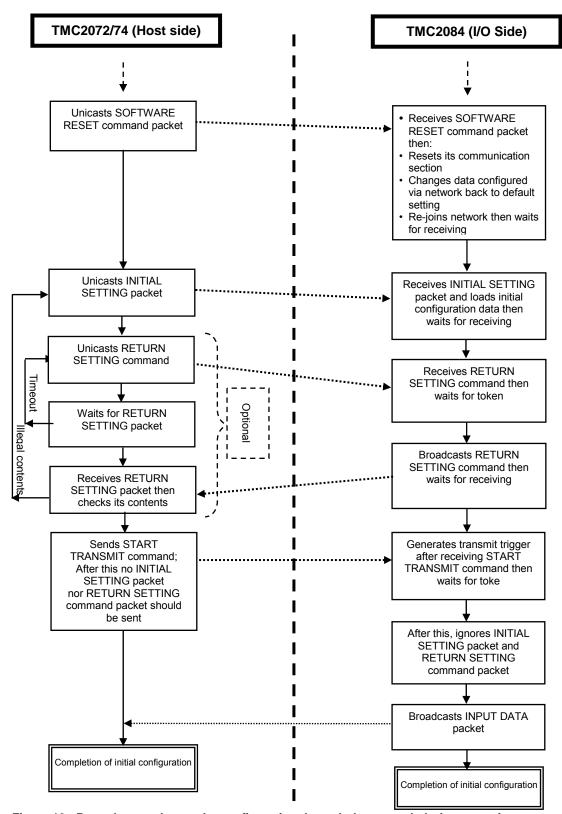

| 2.12            |                | nfiguration Flow                                 |          |

| ۷. ۱۷           | 2 001          | illiguration Flow                                |          |

| Cha             | apter 3        | Operating Conditions                             | 53       |

| 3.1             |                | lute Maximum Ratings                             |          |

|                 |                | al Operating Conditions                          | 53       |

| 3.3             |                | Characteristics                                  |          |

| 3.4             |                | haracteristics                                   |          |

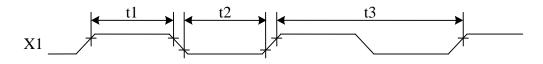

| J. <del>4</del> |                | Timing Measurement Points                        |          |

|                 | 3.4.1<br>3.4.2 | CMI Transmit And Receive Waveforms (nCMIBYP = H) |          |

|                 | 3.4.2          | RZ Transmit And Receive Waveforms (nCMIBYP = L)  |          |

|                 | 3.4.4          | External Trigger Input                           |          |

|                 | 3.4.5          | Other Timing Specifications                      | 57<br>58 |

| 3.5             |                | age Outline                                      |          |

| 3.6             |                | ee Marking                                       |          |

|                 |                |                                                  |          |

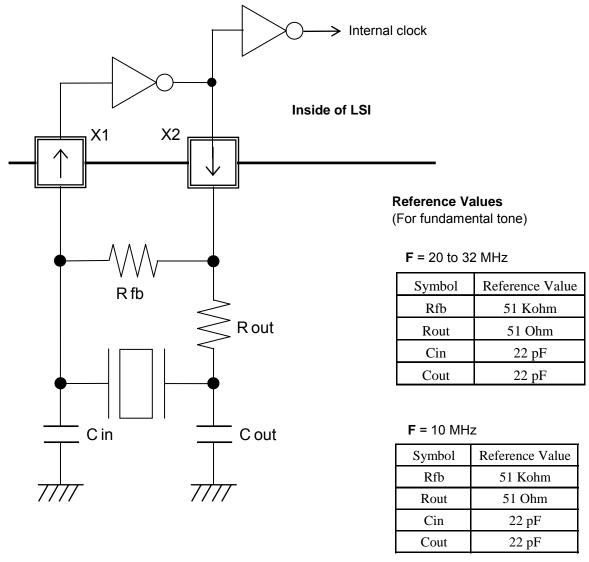

| 3.7<br>3.8      |                | lator Circuit                                    |          |

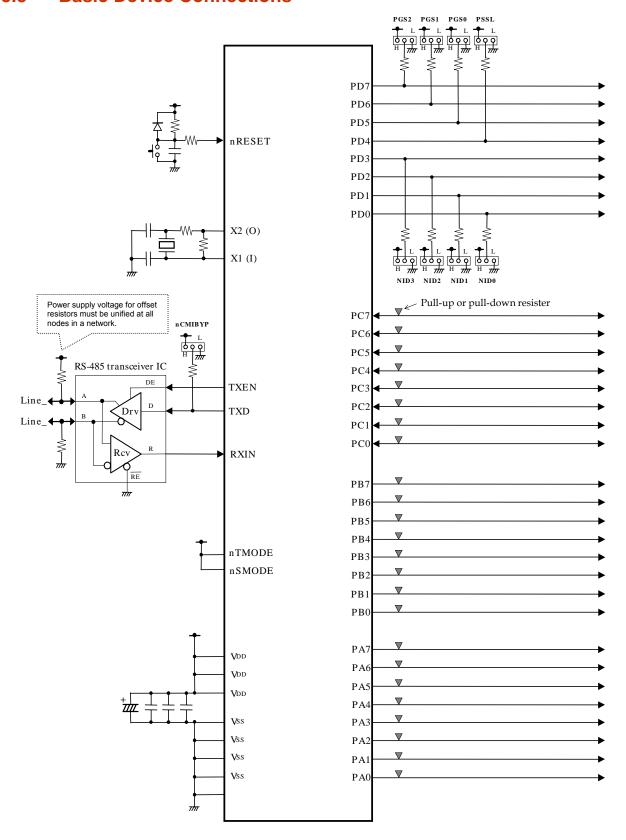

| ວ.ດ             | Dasic          | Device Connections                               |          |

| Chapter 4                                                                                                                                  | APPENDIX                                                               | 64 |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----|

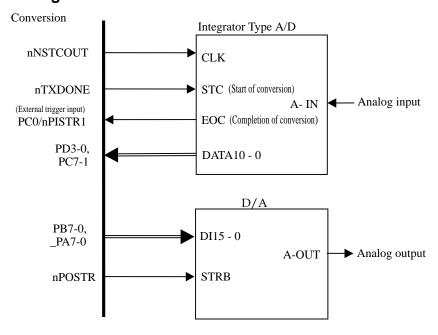

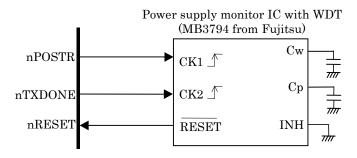

|                                                                                                                                            | lication Circuit Examples                                              |    |

| 4.1.1                                                                                                                                      | Connecting A/D and D/A                                                 |    |

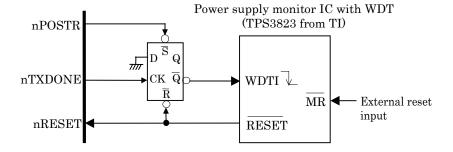

| 4.1.2                                                                                                                                      | Connecting Watchdog Timer                                              |    |

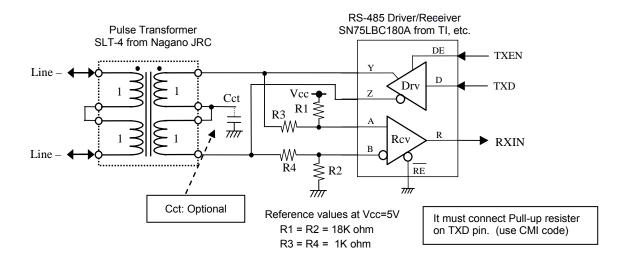

| 4.1.3                                                                                                                                      | Using SLT4 Plus RS485                                                  |    |

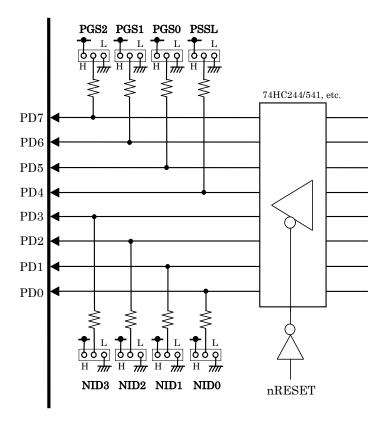

| 4.1.4                                                                                                                                      | Considerations for Shared Pins When Port D is Configured as INPUT PORT |    |

| 4.1.5                                                                                                                                      | Case Where Port A and B are Unused                                     |    |

| 4.1.6                                                                                                                                      | Case Where Port C is Unused                                            | 68 |

| 4.1.7                                                                                                                                      | Case Where Port D is Unused                                            |    |

| 4.1.8                                                                                                                                      | Initial Configuration for OUTPUT PORT (LED Display Example)            | 69 |

| 4.1.9                                                                                                                                      | Width of Reset Signal                                                  | 70 |

| 4.2 Out                                                                                                                                    | out Current from Shared Pins                                           | 72 |

| 4.3 Valu                                                                                                                                   | es of Pull-Up and Pull-Down Resisters                                  | 73 |

| Figure 2 -<br>Figure 3 -<br>Figure 4 -<br>Figure 5 -<br>Figure 6 -<br>Figure 7 -<br>Figure 8 -<br>Figure 9 -<br>Figure 10 -<br>Figure 11 - | TMC2084 Pin Configuration                                              |    |

| List of Table 1 - Table 2 -                                                                                                                | Truth Table Of Bits FOSL3 - 0                                          | 46 |

| Table 3 -                                                                                                                                  | Bits NSTC3 – 0 vs. Carry Output Bit                                    |    |

| Table 4 -                                                                                                                                  | CircLink Controller Comparison Table                                   |    |

# **Chapter 1 General Description**

## 1.1 About CircLink

The CircLink networking controller was developed for small control-oriented local network data communication based on ARCNET's token-passing protocol that guarantees message integrity and calculatable maximum delivery times.

In a CircLink network, when a node receives the token it becomes the temporary master of the network for a fixed, short period of time. No node can dominate the network since token control must be relinquished when transmission is complete. Once a transmission is completed the token is passed on to the next node (logical neighbor), allowing it to be come the master.

Because of this token passing scheme, maximum waiting time for network access can be calculated and the time performance of the network is predictable or deterministic. Industrial network applications require predictable performance to ensure that controlled events occur when required.

However, reconfiguration of a regular ARCNET network becomes necessary when the token is missed due to electronic and magnetic noise. In these cases, the maximum wait time for sending datagrams can not be guaranteed and the real-time characteristic is impaired. CircLink makes several modification to the original ARCNET protocol (such as maximum and consecutive node ID assignment) to avoid token missing as much as possible and reduce the network reconfiguration time.

CircLink implements other enhancements to the ARCNET protocol including a smaller-sized network , shorter packet size, and remote buffer mode operation that enable more efficient and reliable small, control-oriented LANs. In addition, CircLink introduces several unique features for reducing overall system cost while increasing system reliability.

CircLink can operate under a special mode called "Standalone" or "I/O" mode. In this mode, CircLink does not need an administrating CPU for each node. Only one CPU is needed to manage a CircLink network composed of several nodes, reducing cost and complexity.

In a CircLink network, the data sent by the source node is received by all other nodes in the network and stored according to node source ID. For the target node the received data is executed per ARCNET flow control and the data is stored in its buffer RAM. The receiving node processes the data while the remaining nodes on the network discard the data when the receiving node has completed. This memory-mirroring function assures higher reliability and significantly reduces network traffic.

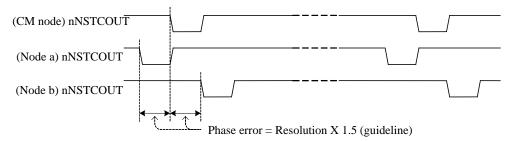

Network Standard Time (NST) is also a unique CircLink feature. NST is realized by synchronizing the individual local time on each network node to the clock master in the designated node from which the packet is sent. CircLink also uses CMI code for transmitting signals, rather than the dipulse or bipolar signals that are the standard ARCNET signals. Since CMI encoding eliminates the DC element, a simple combination of a standard RS485 IC and a pulse transformer can be used to implement a transformer-coupled network.

# 1.2 About TMC2084

The TMC2084 is CircLink's standalone mode controller acting as an intelligent remote I/O controller that uses the enhanced token passing protocol. TMC2084 I/O nodes are controlled by the Host node (TMC2074/72) via the network. Thus, TMC2084 enables a single-processor with multi-remote I/O controllers environment at reasonable cost.

The TMC2084 has thirty-two I/O port lines featuring programmable direction, with 8-bit basis (output: 16 to 32 bit; input: 0 to 16 bit). The maximum number of nodes per network is fifteen, including the host node. This configuration enables a processor to control a total of  $448 (14 \times 32)$  remote I/O lines.

The Output Port type is selectable from either open-drain or push-pull, while one part of the I/O ports is definable as either output pins for network status monitoring, strobe output pins to handshake with AD or DA converter, or input pins for external trigger.

TMC2084 also has additional functions including the function to notify the host of its status, the states of its Output Ports and settings, the function to send packets with timestamp, and the function to synchronize the on-chip timer to the host.

This rich feature set is contained in a single 48-pin TQFP package.

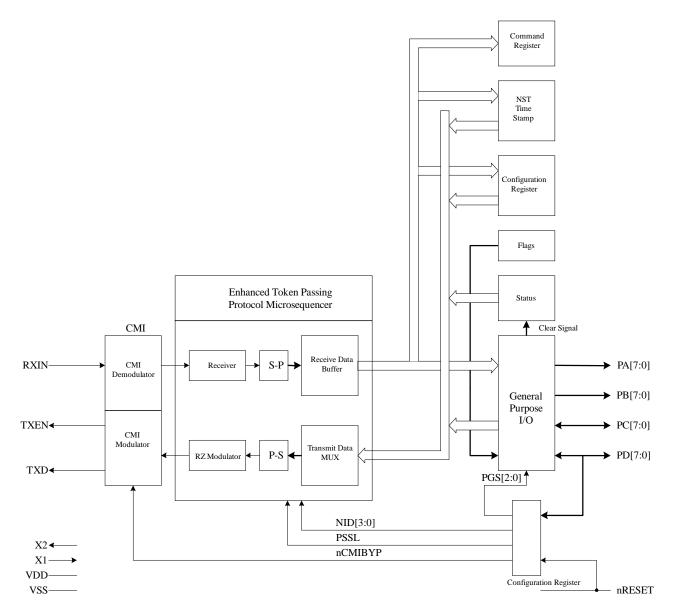

# 1.3 Block Diagram

Figure 1 - TMC2084 Block Diagram

# 1.4 Pin List

| PIN<br>NO.      | SIGNAL NAME                       | PIN NAME   | BUFFER<br>TYPE BY<br>FUNCTION | DETAILED DESCRIPTION                                                                                                                                                                                                                                                                                                             |

|-----------------|-----------------------------------|------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                                   | General Pu | rpose I/O Group               | A                                                                                                                                                                                                                                                                                                                                |

| 2 - 9           | Port A bit 0 - 7<br>(output-only) | PA0 - 7    | O42/OD4                       | General Purpose I/O Port A. An output-only port. The type of output can be selected using the PAOD bit, configured through the network. PAOD = 0 selects push-pull; PAOD = 1 selects open-drain (default).                                                                                                                       |

|                 |                                   | General Pu | rpose I/O Group               | В                                                                                                                                                                                                                                                                                                                                |

| 10-11,<br>14-19 | Port B bit 0 - 7<br>(output-only) | PB0 - 7    | O42/OD4                       | General Purpose I/O Port B. An output-only port. The type of output can be selected using PBOD bit, configured through the network. PBOD = 0 selects push-pull; PBOD = 1 selects open-drain (default).                                                                                                                           |

|                 |                                   | General Pu | rpose I/O Group               |                                                                                                                                                                                                                                                                                                                                  |

| 20              | Port C bit 0                      | PC0        | IT/O42/OD4                    | General Purpose I/O Port Bit 0. A bi-directional port. The port direction can be specified using the shared pin PGS0. PGS0 = L specifies input; PGS0 = H specifies output. The type of output can be selected using PCOD bit, configured through the network. PCOD = 0 selects push-pull; PCOD = 1 selects open-drain (default). |

|                 | External Trigger Input 1          | nPISTR1    | IT                            | External Trigger Input 1 The input pin for external trigger signal. If the shared pin PGS0 is set to L while "6h" or "7" is set using TXTRG3 - 0 bits that are configured through network then this port is configured for the external trigger input.                                                                           |

| 21-23,<br>26-29 | Port C bit 1 - 7                  | PC1 - 7    | IT/O42/OD4                    | General Purpose I/O port C bit 1 to 7. A bi-directional port. The direction of port and the type of output are configured using the same way as PC0.                                                                                                                                                                             |

|     |                               |          | BUFFER          |                                                                                                                                                                                                                                                                                                    |

|-----|-------------------------------|----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | SIGNAL NAME                   | PIN NAME | TYPE BY         | DETAILED DESCRIPTION                                                                                                                                                                                                                                                                               |

| NO. |                               |          | FUNCTION        |                                                                                                                                                                                                                                                                                                    |

|     | I.B. (B.) (C.)                |          | rpose I/O Group |                                                                                                                                                                                                                                                                                                    |

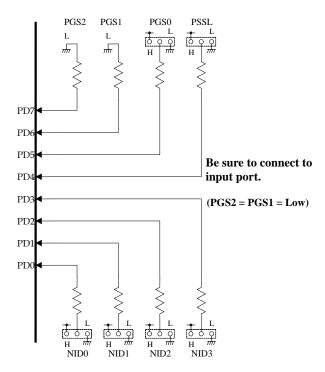

| 30  | Port D bit 0                  | PD0      | IT/O42          | The bit 0 of Port D.  A bi-directional port. The port direction can be specified using the shared pin PGS1.  PGS1 = L specifies input; PGS1 = H specifies output.                                                                                                                                  |

|     | External Trigger Input 2      | nPISTR2  | IT              | External Trigger Input 2 The input port of external trigger signal. If the shared pins PGS0 and PGS1 are set to L and H respectively while either "6h" or "7h" is set using TXTRG3 – 0 bits that are configured through network, then this port is configured for the external trigger input port. |

|     | (Node ID Configuration Bit 0) | (NID0)   | (IT)            | The configuration bit 0 of the own node ID. For detailed information, see the section on Configuration Using Shared Pins.                                                                                                                                                                          |

| 31  | Port D bit 1                  | PD1      | IT/O42          | The bit 1 of Port D. A bi-directional port. The port direction is configured using the same way as PD0.                                                                                                                                                                                            |

|     | (Node ID Configuration Bit 1) | (NID1)   | (IT)            | The configuration bit 1 of the own node ID For detailed information, see the section on Configuration Using Shared Pins.                                                                                                                                                                           |

| 32  | Port D bit 2                  | PD2      | IT/O42          | The bit 2 of Port D. A bi-directional port. The port direction is configured using the same way as PD0.                                                                                                                                                                                            |

|     | (Node ID Configuration Bit 2) | (NID2)   | (IT)            | The configuration bit 2 of the own node ID For detailed information, see the section on Configuration Using Shared Pins.                                                                                                                                                                           |

| 33  | Port D bit 3                  | PD3      | IT/O42          | The bit 3 of Port D. A bi-directional port. The port direction is configured using the same way as PD0.                                                                                                                                                                                            |

|     | (Node ID Configuration Bit 3) | (NID3)   | (IT)            | The configuration bit 3 of the own node ID For detailed information, see the section on Configuration Using Shared Pins.                                                                                                                                                                           |

| 34  | Port D bit 4                  | PD4      | IT/O42          | The bit 4 of Port D.  A bi-directional port. The port direction can be specified using the shared pin PGS1.  PGS1 = L specifies input; PGS1 = H specifies output. PGS2 should be set to L.                                                                                                         |

|     | FLAG OUTPUT bit0              | FO0      | O42             | The bit0 of FLAG OUTPUT. A bi-directional port. Setting the shared pin PGS2 to H configures FLAG OUTPUT mode. For detailed information of the flag, see the section on Configuration Through Network.                                                                                              |

|     | (Page Size Selection)         | (PSSL)   | (IT)            | Page Size Selection. For detailed information, see the section on Configuration Using Shared Pins.                                                                                                                                                                                                 |

| PIN<br>NO. | SIGNAL NAME                            | PIN NAME  | BUFFER<br>TYPE BY     | DETAILED DESCRIPTION                                                                                                                                                               |

|------------|----------------------------------------|-----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                        |           | FUNCTION              |                                                                                                                                                                                    |

| 35         | Port D bit 5                           | PD5       | IT/O42                | The bit 5 of Port D. A bi-directional port. The port direction is configured using the same way as PD4.                                                                            |

|            | FLAG OUTPUT bit1                       | FO1       | O42                   | The bit1 of FLAG OUTPUT. The FLAG OUTPUT mode is configured using the same way as PD4. For detailed information of the flag, see the section on Configuration Through Network.     |

|            | (Port Direction Configuration - bit 0) | (PGS0)    | (IT)                  | Configuration bit 0 of port direction. For detailed information, see the section on Configuration Using Shared Pins.                                                               |

| 37         | Port D bit6                            | PD6       | IT/O42                | The bit 6 of Port D.                                                                                                                                                               |

|            |                                        |           |                       | A bi-directional port. The port direction is configured using the same way as PD4.                                                                                                 |

|            | FLAG OUTPUT bit2                       | FO2       | O42                   | The bit2 of FLAG OUTPUT. The FLAG OUTPUT mode is configured using the same way as PD4. For detailed information of the flag, see the section on Configuration Through the Network. |

|            | (Port Direction Configuration - bit 1) | (PGS1)    | (IT)                  | Configuration bit 1 of port direction. For detailed information, see the section on Configuration Using Shared Pins.                                                               |

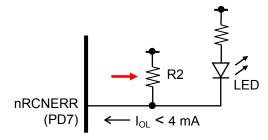

| 38         | Port D bit 7                           | PD7       | IT/O42                | The bit 7 of Port D. A bi-directional port. The port direction is configured using the same way as PD4.                                                                            |

|            | Network Status<br>Monitoring output    | nRCNERR   | O42                   | Network Status Monitoring output. The FLAG OUTPUT mode is configured using the same way as PD4. For detailed information see the section on Configuration Through the Network.     |

|            | (Port Direction Configuration - bit 2) | (PGS2)    | (IT)                  | The configuration bit 2 of port direction. For detailed information, see the section on Configuration Using Shared Pins.                                                           |

|            |                                        |           | t and Clock           |                                                                                                                                                                                    |

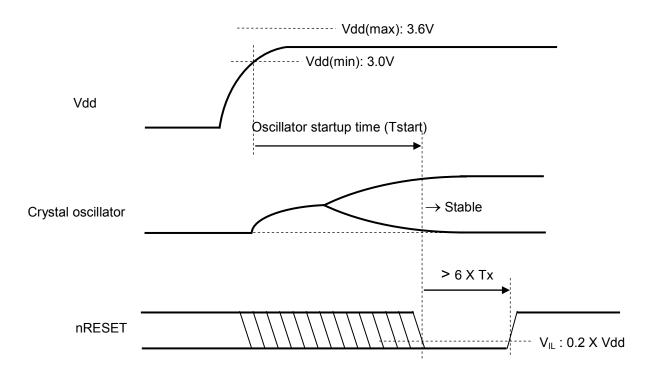

| 41         | Reset Input                            | nRESET    | ICS                   | The input for the reset signal.  The signal for hardware reset is connected to this active low pin.                                                                                |

| 43         | Oscillator/<br>External Clock Input    | X1        | IC                    | This pin functions as the input for either the oscillator or the external clock.                                                                                                   |

| 44         | Oscillator Output                      | X2        | OX<br>eiver Interface | Oscillator output.                                                                                                                                                                 |

| 46         | Transmit Enable Output                 | TXEN      | O42                   | Transmit enable output (active high)                                                                                                                                               |

| 47         | Transmit Data Output                   | TXD       | O42                   | Transmit data output.                                                                                                                                                              |

|            | (CMI bypass configuration)             | (nCMIBYP) | (IT)                  | Specifies bypassing of CMI encoder/decoder. For detailed information, see the section on Configuration Using Shared Pins.                                                          |

#### Datasheet

| PIN<br>NO.                    | SIGNAL NAME        | PIN NAME         | BUFFER<br>TYPE BY<br>FUNCTION | DETAILED DESCRIPTION                                                        |

|-------------------------------|--------------------|------------------|-------------------------------|-----------------------------------------------------------------------------|

| 48                            | Receive Data Input | RXIN             | IT                            | Receive data input.                                                         |

|                               |                    |                  | Test Pin                      |                                                                             |

| 39,<br>40                     | Test Mode          | nTMODE<br>nSMODE | IT_PU                         | Test mode. This pin must be tied to Vdd.                                    |

|                               |                    | Powe             | r Supply Pin                  |                                                                             |

| 13,<br>25,<br>42              | Power Supply       | Vdd              | -                             | Power supply pin. This pin is connected to the power supply voltage (3.3V). |

| 1,<br>12,<br>24,<br>36,<br>45 | Ground             | Vss              | -                             | Ground pin. This pin is connected to the ground level (0V).                 |

# **Description of buffer types:**

IC Input, CMOS Level

IT Input, TTL Level

IT\_PU Input, TTL Level with pull-up

ICS Input, CMOS Level with Schmitt Trigger

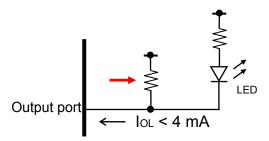

O42 Output,  $I_{OL} = 4 \text{ mA}$ ,  $I_{OH} = -2 \text{ mA}$

OD4 Open-drain Output, I<sub>OL</sub> = 4 mA

OX Oscillator Output

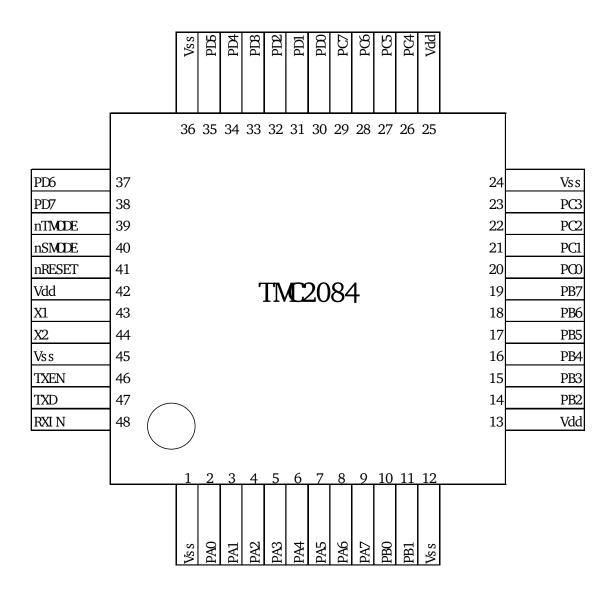

# 1.5 Pinout

Figure 2 - TMC2084 Pin Configuration

# **Chapter 2 Functional Description**

# 2.1 Network Configuration

#### 2.1.1 General

#### **Host Node and I/O Node**

A CircLink network can consist of a single host node/multi I/O node, or multiple host nodes/single I/O, or multiple host nodes and multiple I/O nodes. The host node is directly connected to the system (external) CPU, which controls all communications to or from it. The device that can be used for the host node should be a TMC2072/74 that is configured to operate in Peripheral mode; the TMC2084 is dedicated for the use as an I/O node only (Standalone mode). The I/O nodes do not require the CPU and they are controlled indirectly via the network by the CPU through the host node.

The CircLink network allows a combination of host nodes and I/O nodes up to 15 nodes total. Every CircLink network must have at least one host node.

The host node controls the following I/O node functions:

- Input and output activities on a port (sending and receiving data and initializing the port)

- Setting various configuration data

- Request for configuration data

- Activation of transmission activity

- Software reset

These functions are controlled through the network.

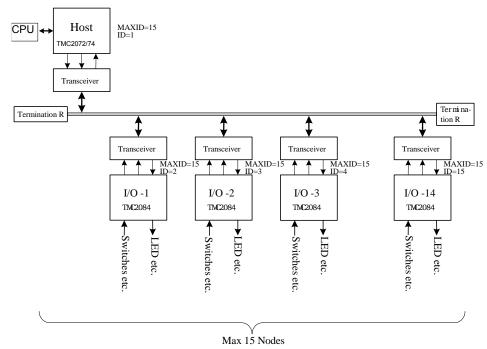

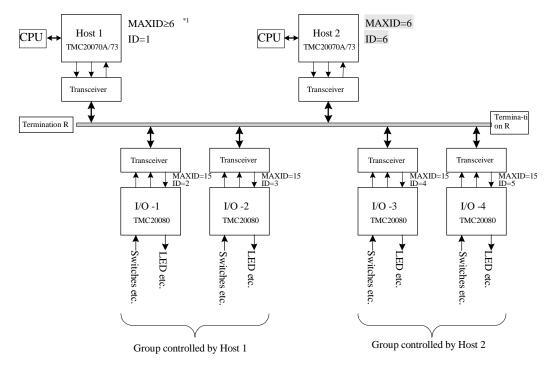

Section 2.1.2 shows two examples: network configuration example 1 (single host) that includes one host node and fourteen I/O nodes, and network configuration example 2 (dual host) that includes two host nodes and four I/O nodes. When multiple hosts are used, I/O nodes should be grouped so that each host can control its corresponding group as shown in network configuration example 2: Host 1 controls both I/O-1 and -2; Host 2 controls both I/O-3 and -4.

#### Node ID

Any node that belongs to a network should have a unique identification number (ID). The ID is configured using shared pins NID3 - 0. When shared pin PSSL is set to L, the allowable range of the node ID is 1 trough 7; it is 1 through 15 when the PSSL pin is set to H. 0 is not allowed for any node ID.

Consecutive node ID numbers (beginning with 1) are assigned to nodes in a network. Consecutive node ID numbers should be used, because each unused ID number between 2 working node IDs causes a latency of 93.6 µs (2.5 Mbps operation) every time a token is sent and thus degrades overall network performance.

#### MAXID

The MAXID defines the maximum node ID of the network and is configured through the network using the MAXID3 - 0 bits. Configuring the MAXID for the network when the number of nodes is less than the upper limit that is defined as 7 for PSSL = L and 15 for PSSL = H in the protocol enables tokens to circulate only among the existing nodes. The allowable MAXID range is 2 through 7 for PSSL = L and 2 through 15 for PSSL = H. Both 0 and 1 are not allowed. The node ID should be assigned consecutively starting with 1 and the MAXID should be equal to the number of nodes.

Typically, all nodes should have the same value for MAXID. However, the node that requires MAXID is the node that has the largest ID number in the network and the remaining nodes can be left to use the default value: 7 for PSSL = L and 15 for PSSL = H (in this case the maximum ID is assigned to the host node). In the case where configuration items other than MAXID also can use their corresponding default values, configuration through the network is not required.

#### **Transmission Rate**

Transmission Rate defines a common rate for all nodes. The transmission rate for TMC2072/74 is configured using either an internal register or an external pin; for TMC2084, it is configured by the value that is equal to one eighth of the input clock.

| TRANSMISSION RATE | CLOCK<br>FREQUENCY | CLOCK SOURCE                        |  |  |

|-------------------|--------------------|-------------------------------------|--|--|

| 5 Mbps            | 40 MHz             | External clock only                 |  |  |

| 4 Mbps            | 32 MHz             | External clock or crystal resonator |  |  |

| 2.5 Mbps          | 20 MHz             | External clock or crystal resonator |  |  |

| 2 Mbps 16 MHz     |                    | External clock or crystal resonator |  |  |

| 1.25 Mbps         | 10 MHz             | External clock or crystal resonator |  |  |

| 1 Mbps            | 8 MHz              | External clock only                 |  |  |

| 625 Kbps          | 5 MHz              | External clock only                 |  |  |

| 500 Kbps          | 4 MHz              | External clock only                 |  |  |

| 312.5 Kbps        | 2.5 MHz            | External clock only                 |  |  |

The acceptable frequency of an external crystal resonator is limited to the range of 10 MHz to 32 MHz due to the limitation of the onchip oscillator's performance. Please use the external clock module if a frequency other than the above is needed.

# 2.1.2 Configuration Examples

Figure 3 - Network Configuration Example 1: S Single Host and 15 Nodes

$<sup>^{*1}</sup>$  Because a token is still passed to node 6 even if nodes 2 to 5 are off.

Figure 4 - Network Configuration Example 2: Dual Hosts and 6 Nodes

# 2.2 Initial Configuration

Initial configuration can be performed two ways: through shared pins or through the network.

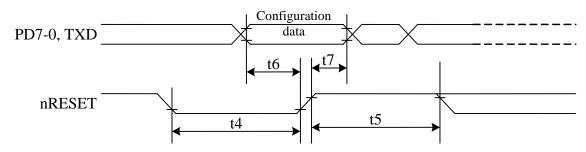

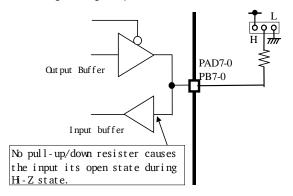

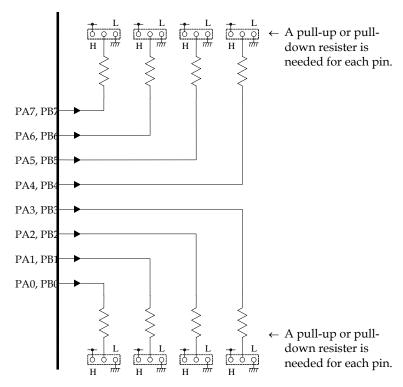

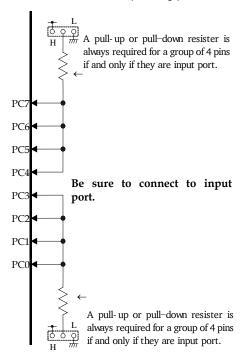

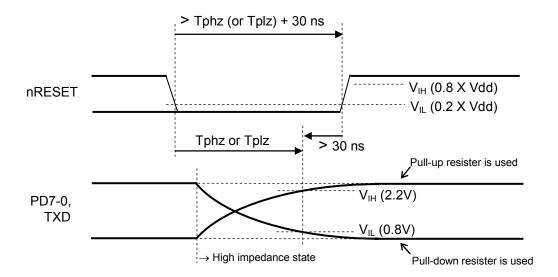

# 2.2.1 Configuration Using Shared Pins

Basic items related to communication are configured using the shared pins. The configuration is performed after reading the states of pins PD7 - 0 and TXD at the rising edge of the reset signal. Since these pins remain in their high-impedance states (input states) during reset, connecting pull-up resisters to them causes High level input and connecting pull-down resisters to them causes Low level input. The items configured here are essential to send or receive packets within the network. Additional detail items may be configured if necessary using configuration through the network as described below.

**nCMIBYP** This pin specifies whether CMI coding is bypassed.

(Shared with TXD) Low: the CMI coding is bypassed (RZ coding for HYC4000/2000)

High: the CMI coding is not bypassed. (CMI coding for RS-485/CAN transceiver)

NID3 - 0 These three pins specify the node ID within the range 1 through 15.

(Shared with PD3 - 0) NID3 and NID0 correspond to MSB and LSB respectively. Low causes 0; High

causes 1. When PSSL is set to Low, NID3 causes 0.

**Note**: DO NOT set low level for all pins.

**PSSL** This pin selects the page size.

(Shared with PD4) Low: 128 bytes/page (the maximum number of nodes = 7): All of the NID3,

MAXID3 and CMID3 bits are fixed to 0.

Burst Transmission Period =  $1.07 \text{ ms} \times 2.5/R$  (R = Transmission Rate in Mbps)

High: 64 bytes/page (the maximum number of nodes = 15)

Burst Transmission Period =  $0.79 \text{ ms} \times 2.5/\text{R}$  (R = Transmission Rate in Mbps)

Two types of page sizes out of the four types that TMC2072/74 supports can be configured for TMC2084: 64-byte and 128-byte modes. A common page size must be configured for all nodes including host nodes. The data size that TMC2084 can send to or receive from the host in all modes is only the 8 bytes that are taken from the page; 64 bytes or 128 bytes of data can be transmitted only between host nodes.

**PGS2 - 0** These three pins specify I/O port direction as shown in the table below.

(Shared with PD7 - 5)

| DCS2                                                              | DCS4 | PGS0   | Push-p  | ull only      | 0       | .D / Push-pull |         | Input Pins<br>for External |         |

|-------------------------------------------------------------------|------|--------|---------|---------------|---------|----------------|---------|----------------------------|---------|

| PGSZ                                                              | PGST | F G 30 | PD7 - 4 | PD3 - 0       | PC7 - 0 | PB7 - 0        | PA7 - 0 | Trigger                    |         |

| L                                                                 | L    | L      | Input   | Input         | Input   |                |         | nPISTR1                    |         |

| L                                                                 | L    | Н      | IIIput  | input input   | Output  | Output         | Output  | nPISTR2                    |         |

| L                                                                 | Н    | L      | Output  | Output Output |         |                |         | Input                      | nPISTR1 |

| L                                                                 | Н    | Н      |         | Output        | Output  |                |         | -                          |         |

| Н                                                                 | L    | L      |         | lanut         | Input   | Output         |         | nPISTR1                    |         |

| Н                                                                 | L    | Н      | FLAG    | Input         | Output  |                |         | nPISTR2                    |         |

| Н                                                                 | Н    | L      | OUTPUT  | Outeut        | Input   |                |         | nPISTR1                    |         |

| Н                                                                 | Н    | Н      |         | Output        | Output  |                |         | -                          |         |

| L: Low; H: High O.D: Open-drain. The pins PA7 – 0 and PB7 – 0 are |      |        |         |               |         |                |         | re output-only.            |         |

#### **Port D Considerations**

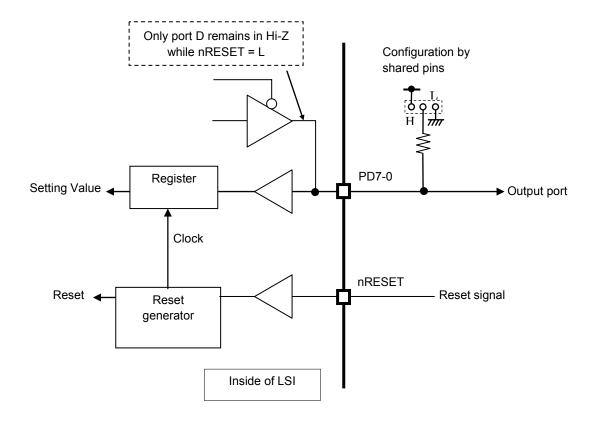

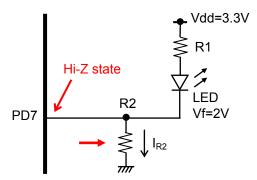

Example 1: Configuring Port D as OUTPUT PORT or FLAG OUTPUT - The case where the configuration by the shared pins is the same as the initial data from the OUTPUT PORT configured

The figure below shows the case where the initial data from the OUTPUT PORT does not conflict with the configuration by shared pins even if port D is configured as the OUTPUT PORT or FLAG OUTPUT. Port D remains in high-impedance state while the reset signal (nRESET) remains low. OUTPUT PORT remains in high-impedance state during the period from the falling edge of reset to the beginning of the first output data received. During these high-impedance periods, each input to port D is defined by the external pull-up (High) or pull-down (Low) resister. When port D is configured as FLAG OUTPUT, it starts driving right after the deassertion of the reset signal.

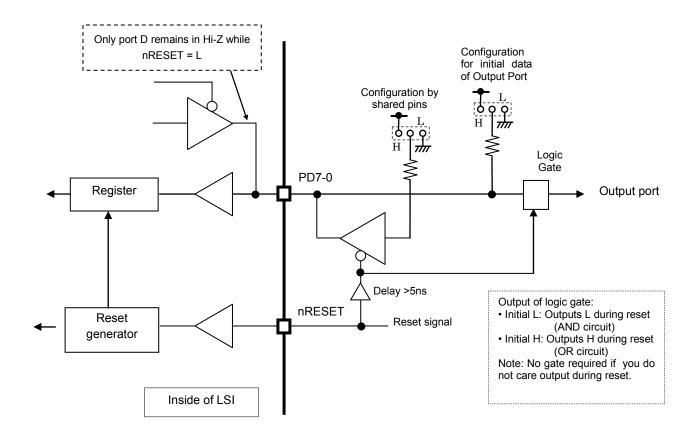

**Example 2: Configuring Port D as OUTPUT PORT -** The case where the configuration by the shared pins is different from the initial data from the OUTPUT PORT configured.

The figure below shows the case where the initial data from the OUTPUT PORT <u>does</u> conflict with the configuration by shared pins when port D is configured as an OUTPUT PORT. Port D remains in high-impedance state while the reset signal (nRESET) remains low. Also, the OUTPUT PORT remains in high-impedance state during the period from the falling edge of reset to the beginning of the first output data received.

During reset, the external tri-state buffer is enabled and the values configured by the shared pins are inputted to port D. After the reset signal is deasserted, the tri-state buffer is disabled and the initial data from the OUTPUT PORT is defined by an external pull-up (High) or pull-down (Low) resister. If initial data from the OUTPUT PORT is needed during the reset, use an external gate as shown in the figure below to define the data from OUTPUT PORT while the nRESET remains at low level.

A hold time greater than 5 ns is required to retrieve the data configured by the shared pins and place it in the onchip memory. Thus, a buffer is added to provide a delay time for the control signal of an external tristate buffer.

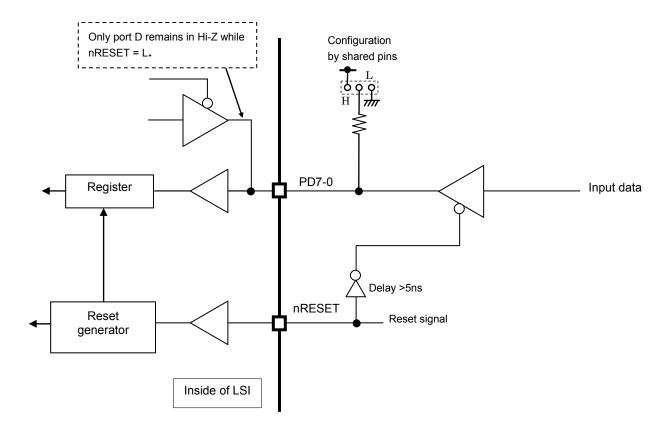

#### **Example 3: Configuring Port D as an INPUT PORT**

The figure below shows the case where the port D is configured as INPUT PORT. The port D remains in high impedance state while the reset signal (reset) remains low level. During this high-impedance state, data defined by an external pull-up (High) or pull-down (Low) resister must be inputted to port D and any external input data to port D should be inhibited to avoid conflict. This requires the external tri-state buffer to inhibit input data during the reset period.

A hold time greater than 5 ns is required to retrieve the data configured by the shared pins and place it on the onchip memory. Thus, the buffer is added to provide a delay time for the control signal of the external tri-state buffer.

# 2.2.2 Configuration Through the Network

Additional items configured using this feature. The configuration is performed with an INITIAL SETTING packet received from the host node.

If the default is acceptable for all items that require configuration via the network and the NST carry output (i.e. nNSTCOUT described later) is not used, then configuration by the INITIAL SETTING packet is unnecessary. The configuration by INITIAL SETTING packet is valid only before receiving the START TRANSMIT command (described later). After receiving the START TRANSMIT command, the INITIAL SETTING packet is ignored.

#### Format of INITIAL SETTING Packet

From host node (transmit) to I/O node (receive)

| Name  | Adrs. * | Bit 7                   | Bit 6           | Bit 5       | Bit 4            | Bit 3                | Bit 2        | Bit 1  | Bit 0 | Initial value |

|-------|---------|-------------------------|-----------------|-------------|------------------|----------------------|--------------|--------|-------|---------------|

| SID   | 00h     |                         |                 | -           | Host n           | ode ID               | -            |        |       |               |

| DID   | 01h     |                         |                 |             |                  | ode ID<br>oadcasted) |              |        |       |               |

| C.P   | 02h     |                         | C.P = 38h/78h * |             |                  |                      |              |        |       |               |

|       | :       |                         | <b>:</b>        |             |                  |                      |              |        |       |               |

|       |         | PA                      | CKET ID co      | ode         |                  |                      |              |        |       |               |

| DATA0 | 38h/78h | 0                       | 1               | 0           |                  |                      | 0            |        |       |               |

| DATA1 | 39h/79h | 0                       | PCOD            | PBOD        | PAOD             | BSTSEN<br>D          | CMIERR<br>MD | EMGYMD | BRE   | 7Fh           |

| DATA2 | 3Ah/7Ah | POSTRM<br>D             | POSTRD<br>LY    | ACHTBY<br>P | 0                |                      | MAXI         | D3 - 0 |       | 0Fh           |

| DATA3 | 3Bh/7Bh |                         | FOSI            | _3 - 0      |                  |                      | TXTR         | G3 - 0 |       | 00h           |

| DATA4 | 3Ch/7Ch | NSTCOM<br>D             | ACHTFR<br>Q     | 0           | 0                | NSTC3 - 0            |              |        |       |               |

| DATA5 | 3Dh/7Dh | NSTPRE2 - 0 0 CMID3 - 0 |                 |             |                  |                      |              | 00h    |       |               |

| NST-L | 3Eh/7Eh | NST7 - 0                |                 |             |                  |                      |              |        |       |               |

| NST-H | 3Fh/7Fh |                         |                 |             | NST <sup>2</sup> | 15 - 8               |              |        |       |               |

Note: \*Addresses in 64-byte mode/Addresses in 128-byte mode

#### Register Description (DATA1: Various Configurations)

| Name  | Drs.    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3       | Bit 2        | Bit 1  | Bit 0 |

|-------|---------|-------|-------|-------|-------|-------------|--------------|--------|-------|

| DATA1 | 39h/79h | 0     | PCOD  | PBOD  | PAOD  | BSTSEN<br>D | CMIERR<br>MD | EMGYMD | BRE   |

**BRE**

Enables or disables receiving broadcast

- 0: Receiving broadcast is disabled.

- 1: Receiving broadcast is enabled (default).

When the broadcast packet is received by the BRE=0 setting, it is disregarded. (It doesn't become a receiving error.)

#### **EMGYMD**

Configures emergency mode (Assertion of MYRECON causes dropping from network).

- 0: Does not initialize OUTPUT PORT (high-impedance state) when MYRECON is asserted.

- 1: Initializes OUTPUT PORT (high-impedance state) when MYRECON is asserted (default).

#### **CMIERRMD**

Configures the CMI error mode.

- 0: Does not discard the packet when CMIECC is asserted in it.

- 1: Discards the packet when CMIECC is asserted in it (default)

#### **BSTSEND**

Configures Recon-burst signal transmit (Assertion of MYRECON causes dropping from network).

- 0: Does not transmit Recon-burst signal when MYRECON is asserted.

- 1: Transmits Recon-burst signal when MYRECON is asserted (default).

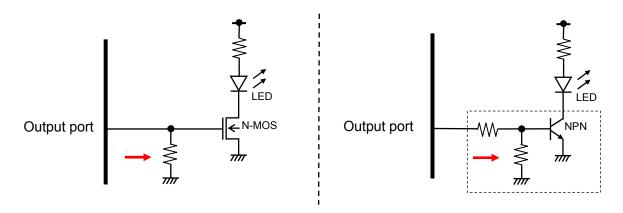

#### **PAOD**

Configures port A pins (PA7 - 0) as open-drain outputs.

- 0: Configures port A pins (PA7 0) as push-pull outputs (totem pole).

- 1: Configures port A pins (PA7 1) as open-drain outputs (default).

#### **PBOD**

Configures port B pins (PB7 - 0) as open-drain outputs.

- 0: Configures port B pins (PB7 0) as push-pull output (totem pole).

- 1: Configures port B pins (PB7 1) as open-drain outputs (default).

#### **PCOD**

Configures port D pins (PD7 - 0) as open-drain outputs.

- 0: Configures port D pins (PD7 0) as push-pull output (totem pole).

- 1: Configures port D pins (PD7 1) as open-drain outputs (default).

#### Register Description (DATA2: MAXID and nPOSTR Related)

| Name  | Adrs.   | Bit 7       | Bit 6        | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|---------|-------------|--------------|-------------|-------|-------|-------|-------|-------|

| DATA2 | 3Ah/7Ah | POSTRM<br>D | POSTRD<br>LY | ACHTBY<br>P | 0     |       | C     | )     |       |

**MAXID3 - 0** Configure the maximum ID number with range 1 to 15 (MAXID4 is fixed to 0)

MAXID3: MSB; MAXID0: LSB

Configuring PSSL = Low causes MAXID3 to be fixed to 0.

Default: MAXID3 - 0 = 1111

**ACHTBYP** Configures the bypass or not for Anti-chatter circuit on input ports.

0: Enable the anti-chatter circuit (default)

1: Bypass (Disable) the anti-chatter circuit

**Note:** When the transmit trigger (TXTRG3-0) setting is set to "By the external trigger", bypass is automatic.

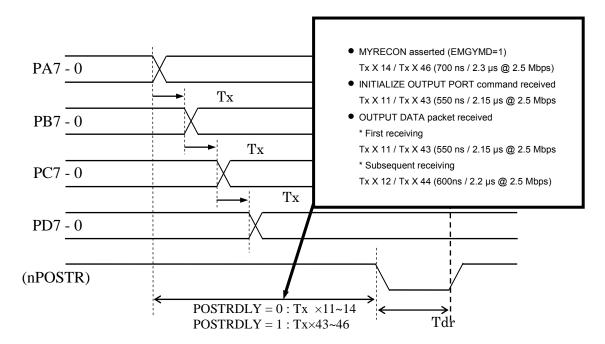

**POSTRDLY** Configures delay time for the OUTPUT PORT strobe (nPOSTR).

0: From the transition of port A to the falling edge of strobe at least 11 times of Tx (default)

1: From the transition of port A to the falling edge of strobe at least 43 times of Tx.

Note: Tx = Period of input clock (11 × Tx = 550 ns and  $43 \times Tx = 2.15 \mu s$  @20 MHz input)

**POSTRMD** Configures output mode for the OUTPUT PORT strobe signal (nPOSTR).

0: Asserts OUTPUT PORT strobe signal after initializing OUTPUT PORT and after receiving the OUTPUT DATA packet (default).

1: Asserts only after receiving the OUTPUT DATA packet.

**Note:** Initializing OUTPUT PORT means Initialization by both the INITIALIZE OUTPUT PORT command and the assertion of MYRECON in emergency mode (EMGYMD = 1).

SMSC TMC2084 Page 23 Revision 0.2 (10-23-08)

#### Register Description (DATA3: This register selects the transmit trigger in FLAG OUTPUT.)

| Name  | Adrs.   | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

|-------|---------|-------|-------|--------|-------|-------|-------|--------|-------|

| DATA3 | 3Bh/7Bh |       | FOSI  | _3 - 0 |       |       | TXTR  | G3 - 0 |       |

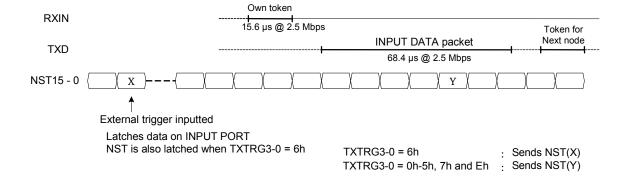

**TXTRG3 - 0** These bits select the transmit trigger.

The trigger condition to send the INPUT DATA packet is configured. The transmit trigger is enabled after receiving the START TRANSMIT command.

|   | TXT | RG |   | The transmit trigger to send the INPUT DATA                           |

|---|-----|----|---|-----------------------------------------------------------------------|

| 3 | 2   | 1  | 0 | packet is generated upon                                              |

| 0 | 0   | 0  | 0 | Receiving the OUTPUT DATA packet                                      |

| 0 | 0   | 0  | 1 | Receiving the OUTPUT DATA packet or expiring on-chip timer (3.3 ms)   |

| 0 | 0   | 1  | 0 | Receiving the OUTPUT DATA packet or expiring on-chip timer (6.6 ms)   |

| 0 | 0   | 1  | 1 | Receiving the OUTPUT DATA packet or expiring on-chip timer (13.1 ms)  |

| 0 | 1   | 0  | 0 | Receiving the OUTPUT DATA packet or expiring on-chip timer (26.2 ms)  |

| 0 | 1   | 0  | 1 | Receiving the OUTPUT DATA packet or expiring on-chip timer (104.8 ms) |

| 0 | 1   | 1  | 0 | By the external trigger (with NST latch)                              |

| 0 | 1   | 1  | 1 | By the external trigger (without NST latch)                           |

| 1 | 0   | 0  | 0 | Reserved (unused)                                                     |

| 1 | 0   | 0  | 1 | Reserved (unused)                                                     |

| 1 | 0   | 1  | 0 | Reserved (unused)                                                     |

| 1 | 0   | 1  | 1 | Reserved (unused)                                                     |

| 1 | 1   | 0  | 0 | Reserved (unused)                                                     |

| 1 | 1   | 0  | 1 | Reserved (unused)                                                     |

| 1 | 1   | 1  | 0 | Receiving own token                                                   |

| 1 | 1   | 1  | 1 | Receiving the COMMAND packet                                          |

#### **Receiving the OUTPUT DATA packet:**

A single transmit trigger is generated after receiving the OUTPUT DATA packet that is destined for this node or broadcasted is received. The INPUT DATA packet is transmitted after receiving the token (i.e., the token destined for this node).

#### Receiving the OUTPUT DATA packet or expiring on-chip timer:

A single transmit trigger is generated after either receiving the OUTPUT DATA packet that is destined for this node or broadcasted, or expiring on-chip timer. The INPUT DATA packet is then transmitted after receiving the token.

Note:

This on-chip timer is cleared by an of three events: receiving the START TRANSMIT command; receiving the INITIALIZE OUTPUT PORT command; or transmitting an INPUT DATA packet after receiving a data packet.

#### By the external trigger:

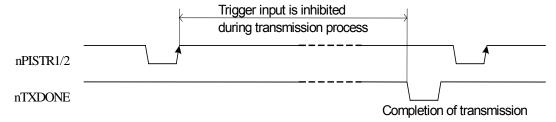

The rising edge on the external trigger input pin (nPISTR1 or nPISTR2) latches the input data and generates the trigger. The INPUT DATA packet is then transmitted after receiving the token.

Either nPISTR1 or nPISTR2 is selected as the external trigger input pin depending on the I/O port direction configured by pins PGS2 - 0. If all of ports are configured as OUTPUT PORTs by the configuration feature for I/O port direction, then this external trigger cannot be used.

When the NST value latch is used, both the NST value and input data are latched simultaneously and the latched NST value is transmitted. When the NST value latch is not used, the last NST value is transmitted regardless to latching the input data.

#### (Both the input data and NST value latches are cleared to zero by hardware at initialization.)

Receiving the token allows the actual transmission of packets. Thus, the delay time from the trigger to the actual transmission can vary. If two consecutive external triggers are inputted, it can not be determined which trigger caused the data transmission since it depends on when the token was received.

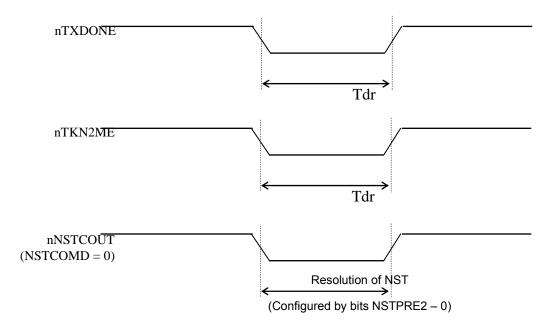

Using nTXDONE (transmit completion flag) of the FLAG OUTPUT allows an easy handshake.

#### Whenever the token is received:

With this condition, the trigger is always generated. The INPUT DATA packet is transmitted whenever own token is received.

#### **Receiving COMMAND packet:**

A single transmit trigger is generated whenever either the START TRANSMIT or INITIALIZE OUTPUT PORT command that is destined for this node or broadcasted is received. The INPUT DATA packet is then transmitted upon receiving the token (The transmit trigger caused by the INITIALIZE OUTPUT PORT command is valid after receiving the START TRANSMIT command).

Note that the Return Setting and SOFTWARE RESET commands do not cause any transmit trigger. For detail information on each command, see section 2.4 COMMAND packet.

**NOTE**: A single transmit trigger is generated each time the START TRANSMIT command is received regardless of the configuration for the transmit trigger. Additionally, a single transmit trigger is generated at the time the INITIALIZE OUTPUT PORT command is received after receiving the START TRANSMIT command.

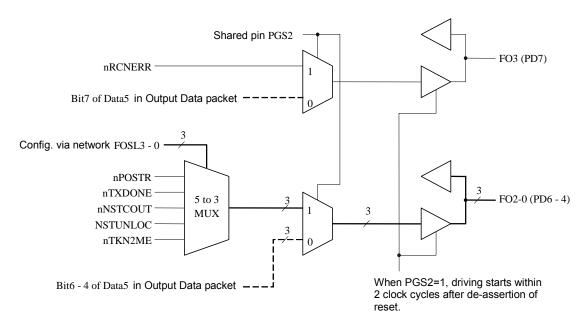

#### FOSL3 - 0 Select FLAG OUTPUT.

These bits select the flags that are outputted to the upper 4 bits of port D. For detailed information, see section of  $2.7\ FLAG\ OUTPUT$ .

Default

|      |   | FO | SL |   | FO3 (PD7)   | FO2 (PD6)         | FO1 (PD5)         | FO0 (PD4)         |  |

|------|---|----|----|---|-------------|-------------------|-------------------|-------------------|--|

|      | 3 | 2  | 1  | 0 | FO3 (FD1)   | FOZ (FD0)         | FOT (FD3)         | FO0 (FD4)         |  |

| lt [ | 0 | 0  | 0  | 0 |             |                   |                   | nNSTCOUT          |  |

|      | 0 | 0  | 0  | 1 |             |                   | nTXDONE           | NSTUNLOC          |  |

|      | 0 | 0  | 1  | 0 |             | nPOSTR            |                   | nTKN2ME           |  |

|      | 0 | 0  | 1  | 1 |             | 111 0311          | nNSTCOUT          | NSTUNLOC          |  |

|      | 0 | 1  | 0  | 0 |             |                   | 1110310001        | nTKN2ME           |  |

|      | 0 | 1  | 0  | 1 |             |                   | NSTUNLOC          | ITTKINZIVIE       |  |

|      | 0 | 1  | 1  | 0 |             |                   | nNSTCOUT          | NSTUNLOC          |  |

|      | 0 | 1  | 1  | 1 | nRCNERR     | nTXDONE           | 1110310001        |                   |  |

|      | 1 | 0  | 0  | 0 | HINGINEININ |                   | NSTUNLOC          | nTKN2ME           |  |

| L    | 1 | 0  | 0  | 1 |             | nNSTCOUT          | NOTONLOC          |                   |  |

| L    | 1 | 0  | 1  | 0 |             |                   |                   |                   |  |

| L    | 1 | 0  | 1  | 1 |             |                   |                   |                   |  |

|      | 1 | 1  | 0  | 0 |             | (Fixed to High)   | (Fixed to High)   | (Fixed to High)   |  |

|      | 1 | 1  | 0  | 1 |             | (Fixed to Flight) | (Fixed to Flight) | (Fixed to Flight) |  |

|      | 1 | 1  | 1  | 0 |             |                   |                   |                   |  |

|      | 1 | 1  | 1  | 1 |             |                   |                   |                   |  |

#### Register Description (DATA4: NST carry-related configuration)

| Name  | Adrs.   | Bit 7       | Bit 6       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

|-------|---------|-------------|-------------|-------|-------|-------|-------|--------|-------|

| DATA4 | 3Ch/7Ch | NSTCOM<br>D | ACHTFR<br>Q | 0     | 0     |       | NSTC  | C3 – 0 |       |

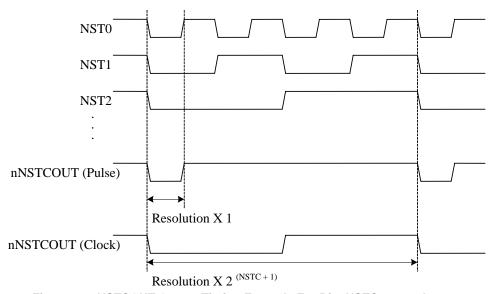

**NSTC3 - 0** These bits select the NST carry (default: NSTC3 - 0 = 0000)

0000: 1<sup>st</sup> digit (carry period = NST resolution X 2^1)

0001: 2<sup>nd</sup> digit (carry period = NST resolution X 2<sup>2</sup>)

0010: 3<sup>rd</sup> digit (carry period = NST resolution X 2^3)

0011: 4<sup>th</sup> digit (carry period = NST resolution X 2<sup>4</sup>)

:: :

1110: 15<sup>th</sup> digit (carry period = NST resolution X 2^15)

1111: 16<sup>th</sup> digit (carry period = NST resolution X 2^16)

**ACHTFRQ** Configures the sampling frequency for Anti-chatter circuit on input ports.

0: Sampling frequency is 1.22 kHz (default)

1: Sampling frequency is 19.1Hz (52 ms period)

**NOTE:** When the transmit trigger (TXTRG3-0) setting is set to "By the external trigger", bypass is automatic. The above-mentioned sampling frequency is the value when the input clock is 20 MHz. The sampling frequency doubles when the input clock is 40 MHz, and half when the input clock is 10 MHz.

NSTCOMD Configures the output mode of NST carry (NST carry is outputted via nNSTCOUT)

- 0: Active low pulse output with the pulse Level Width resolution selected by the bits  ${\sf NSTPRE2-0}$

- 1: Clock output with the duty ratio 50% (default)

#### Register Description (DATA5: Clock master ID and NST resolution)

| Name  | Adrs.   | Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

|-------|---------|-------|-----------|-------|-------|-------|-------|--------|-------|

| DATA5 | 3Dh/7Dh | ١     | NSTPRE2 - | 0     | 0     |       | CMIE  | 03 - 0 |       |

**CMID3 - 0** These bits define the clock master ID in the range of 1 to 15 (CMID4 is fixed to 0)

CMID3: MSB; CMID0: LSB

PSSL = Low causes CMID3 = 0.

Default: CMID3 - 0 = 0000 (Asynchronous to NST: free running)

If a non-zero value is set in bits CMID3 – 0, the synchronization to NST begins when a packet is received from the next CMID.

**NSTPRE2 - 0** These bits define the NST resolution (default: NSTPRE2 - 0 = 000)

000: 1.6 μs (Maximum period = 104.9 ms) 001: 3.2 μs (Maximum period = 209.7 ms) 010: 6.4 μs (Maximum period = 419.4 ms) 011: 12.8 μs (Maximum period = 838.9 ms) 100: 25.6 μs (Maximum period = 1.68 s) 101: 51.2 μs (Maximum period = 3.35 s)110: 102.4 μs (Maximum period = 6.71 s)111: 204.8 μs (Maximum period = 13.42 s)

**NOTE:** The above data are for 20 MHz input.

(For 40 MHz input they are half; for 10 MHz input they double)

# 2.2.3 Returning Configuration Data

When the RETURN SETTING command is received before receiving the START TRANSMIT command, the RETURN SETTING packet is broadcasted upon receiving the next own token. Items configured using the INITIAL SETTING packet are transmitted as the RETURN SETTING packet.

After receiving the START TRANSMIT command, any RETURN SETTING command is ignored. For detail information on each command, see the section of 2.4 COMMAND packets.

#### Format of the RETURN SETTING Packet

| From I/C | o node (tra | nsmit) to ho            | st node (re    | ceive)      |            |             |              |             |       |  |  |

|----------|-------------|-------------------------|----------------|-------------|------------|-------------|--------------|-------------|-------|--|--|

| Name     | Adrs. *     | Bit 7                   | Bit 6          | Bit 5       | Bit 4      | Bit 3       | Bit 2        | Bit 1       | Bit 0 |  |  |

| SID      | 00h         |                         | ID of I/O node |             |            |             |              |             |       |  |  |

| DID      | 01h         |                         |                | 00          | 0h (always | broadcaste  | d)           |             |       |  |  |

| C.P      | 02h         |                         |                |             | C.P = 3    | 8h/78h *    |              |             |       |  |  |

|          | :           |                         | <b>:</b>       |             |            |             |              |             |       |  |  |

|          |             | PA                      | CKET ID co     | ode         |            | Ţ.          | Į.           |             |       |  |  |

| DATA0    | 38h/78h     | 0                       | 1              | 1           | 0          | 0           | 00           | 00 / PGS2-0 | *2    |  |  |

| DATA1    | 39h/79h     | 0                       | PCOD           | PBOD        | PAOD       | BSTSEN<br>D | CMIERR<br>MD | EMGYMD      | BRE   |  |  |

| DATA2    | 3Ah/7Ah     | POSTRM<br>D             | POSTRD<br>LY   | ACHTBY<br>P | 0          |             | (            | 0           |       |  |  |

| DATA3    | 3Bh/7Bh     |                         | FOSI           | _3 - 0      |            |             | TXTR         | G3 - 0      |       |  |  |

| DATA4    | 3Ch/7Ch     | NSTCOM<br>D             | ACHTFR<br>Q    | 0           | 0          | NSTC3 - 0   |              |             |       |  |  |

| DATA5    | 3Dh/7Dh     | NSTPRE2 - 0 0 CMID3 - 0 |                |             |            |             |              |             |       |  |  |

| NST-L    | 3Eh/7Eh     | NST7 - 0                |                |             |            |             |              |             |       |  |  |

| NST-H    | 3Fh/7Fh     |                         | NST15 - 8      |             |            |             |              |             |       |  |  |

<sup>\*</sup> Addresses in 64-byte mode/Addresses in 128-byte mode

PGS2-0 sets status of the I/O ports direction for the configuration using shared pins.

<sup>\*2 &</sup>quot;000" or "PGS2-0" is selected using the RETURN SETTING command.

# 2.3 Types of Packets

# 2.3.1 Packets TMC2084 Can Receive

TMC2084 can receive the three types of packets from the host node: the Initial Setting, Command and OUTPUT DATA packets. The packet is identified using the packet ID code included in the first data byte (DATA0) of it and any packet that has undefined code is discarded.

Packet's RAM image on the host node is shown below.

| Adrs. *1 | Name  | INITIAL SETTING Packet                                              | COMMAND Packet                      | OUTPUT DATA Packet                      |  |  |  |

|----------|-------|---------------------------------------------------------------------|-------------------------------------|-----------------------------------------|--|--|--|

| 00h      | SID   |                                                                     |                                     |                                         |  |  |  |

| 01h      | DID   |                                                                     | ID of I/O node or 00h (broadcasted) |                                         |  |  |  |

| 02h      | C.P   |                                                                     | C.P = 38h/78h *1                    |                                         |  |  |  |

|          |       |                                                                     | :                                   |                                         |  |  |  |

| 38h/78h  | DATA0 | PACKET ID code = 010                                                | PACKET ID code = 100                | PACKET ID code = 000,<br>OPICDONE clear |  |  |  |

| 39h/79h  | DATA1 | Various configuration data                                          | 0                                   | Status clear                            |  |  |  |

| 3Ah/7Ah  | DATA2 | MAXID, nPOSTR-related                                               | Command code                        | Port A output data                      |  |  |  |

| 3Bh/7Bh  | DATA3 | Transmit trigger , FLAG OUTPUT selection                            | 0                                   | Port B output data                      |  |  |  |

| 3Ch/7Ch  | DATA4 | NST carry -related                                                  | Command code                        | Port C output data                      |  |  |  |

| 3Dh/7Dh  | DATA5 | Clock master ID, NST resolution 0 Port D output data                |                                     |                                         |  |  |  |

| 3Eh/7Eh  | NST-L | Lower byte of NST (for the time synchronization use <sup>*2</sup> ) |                                     |                                         |  |  |  |

| 3Fh/7Fh  | NST-H | Upper byte of NST (for the time synchronization use *2)             |                                     |                                         |  |  |  |

<sup>\*1</sup> Addresses in 64-byte mode/Addresses in 128-byte mode

<sup>&</sup>lt;sup>\*2</sup> In the case where the originator of the packet is the clock master (CM) node. If the originator of the packet is not the clock master (CM) node, then the time synchronization is not used.

#### 2.3.2 Packets TMC2084 Can Transmit

TMC2084 can send two types of packets: the Return Setting and INPUT DATA packets. It sends the RETURN SETTING packet during the period from the deassertion of reset signal to receiving the START TRANSMIT command. After receiving the START TRANSMIT command it sends INPUT DATA packets. For more information, see section of 2.4 COMMAND packets.

Packet's RAM image on the host node is shown below.

| Adrs. * | Name  | RETURN SETTING Packet INPUT DATA Packet                                                      |                                                                     |  |  |  |  |

|---------|-------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|

| 00h     | SID   | ID of I/O node                                                                               |                                                                     |  |  |  |  |

| 01h     | DID   | 00h (always                                                                                  | broadcasted)                                                        |  |  |  |  |

| 02h     | C.P   | C.P = 3                                                                                      | 8h/78h <sup>*</sup>                                                 |  |  |  |  |

|         |       |                                                                                              |                                                                     |  |  |  |  |

| 38h/78h | DATA0 | PACKET ID code = 011                                                                         | PACKET ID code = 001, OPICDONE, configuration data of PGS2 - 0 pins |  |  |  |  |

| 39h/79h | DATA1 | Various configuration data                                                                   | Status                                                              |  |  |  |  |

| 3Ah/7Ah | DATA2 | MAXID, nPOSTR-related configuration data                                                     | Port A OUTPUT PORT data                                             |  |  |  |  |

| 3Bh/7Bh | DATA3 | Transmit trigger,<br>FLAG OUTPUT selections                                                  | Port B OUTPUT PORT data                                             |  |  |  |  |

| 3Ch/7Ch | DATA4 | NST carry-related configurations                                                             | Port C input data or port C OUTPUT PORT data                        |  |  |  |  |

| 3Dh/7Dh | DATA5 | Clock master ID, Port D input data  NST resolution configurations or port D OUTPUT PORT data |                                                                     |  |  |  |  |

| 3Eh/7Eh | NST-L | Lower byte of NST (time stamp)                                                               |                                                                     |  |  |  |  |

| 3Fh/7Fh | NST-H | Upper byte of NST (time stamp)                                                               |                                                                     |  |  |  |  |

<sup>\*</sup> Addresses in 64-byte mode/Addresses in 128-byte mode

# 2.4 Command Packets

# 2.4.1 Format of COMMAND Packets

From host node (transmit) to I/O node (receive)

| Name  | Adrs. * | Bit 7                                 | Bit 6           | Bit 5 | Bit 4   | Bit 3                | Bit 2 | Bit 1 | Bit 0 |  |

|-------|---------|---------------------------------------|-----------------|-------|---------|----------------------|-------|-------|-------|--|

| SID   | 00h     |                                       | ID of host node |       |         |                      |       |       |       |  |

| DID   | 01h     |                                       |                 |       |         | O node<br>padcasted) |       |       |       |  |

| C.P   | 02h     |                                       |                 |       | C.P = 3 | 8h/78h <sup>*</sup>  |       |       |       |  |

|       | :       |                                       | •               |       |         |                      |       |       |       |  |

|       |         | PA                                    | PACKET ID code  |       |         |                      |       |       |       |  |

| DATA0 | 38h/78h | 1                                     | 0               | 0     |         |                      | 0     |       |       |  |

| DATA1 | 39h/79h |                                       |                 |       | 00      | 0h                   |       |       |       |  |

| DATA2 | 3Ah/7Ah |                                       |                 |       | СМІ     | D7 - 0               |       |       |       |  |

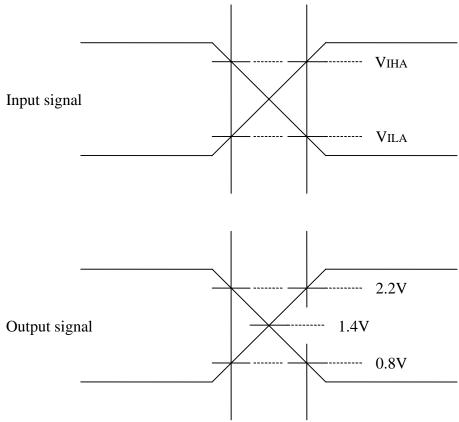

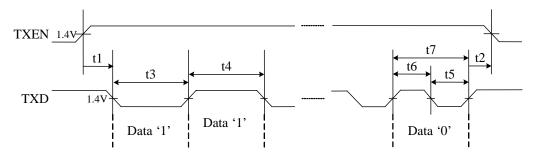

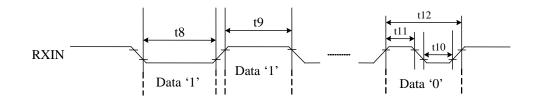

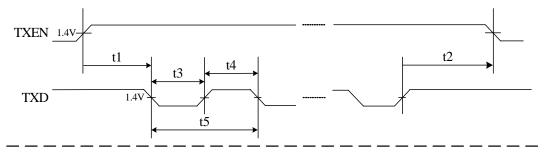

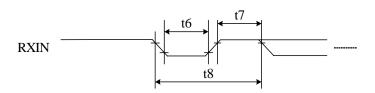

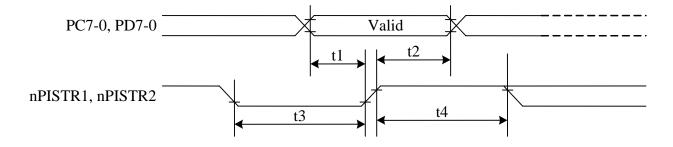

| DATA3 | 3Bh/7Bh |                                       |                 |       | 00      | 0h                   |       |       |       |  |