September 1999

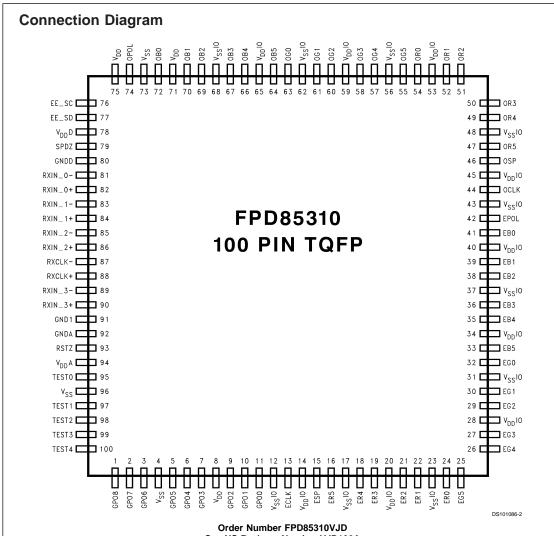

# FPD85310 Panel Timing Controller

## **General Description**

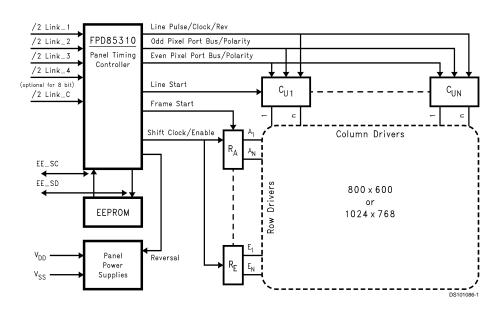

The FPD85310 Panel Timing Controller is an integrated FPD-Link based TFT-LCD timing controller. It resides on the flat panel display and provides the interface signal routing and timing control between graphics or video controllers and a TFT-LCD system. FPD-Link is a low power, low electromagnetic interference interface used between this controller and the host system.

The FPD85310 chip links the panel's system interface to the display via a ten wire LVDS data bus. That data is then routed to the source and gate display drivers. XGA and SVGA resolutions are supported.

The FPD85310 is programmable via an optional external serial EEPROM. Reserved space in the EEPROM is available for display identification information. The system can access the EEPROM to read the display identification data or program initialization values used by the FPD85310.

## **Features**

- FPD-Link System Interface utilizes Low Voltage Differential Signaling (LVDS).

- System programmable via EEPROM

- Suitable for notebook and monitor applications

- 8-bit or 6-bit system interface

- XGA or SVGA capable

- Supports single or dual port column drivers

- Programmable outputs provide customized control for standard or in-house column drivers and row drivers

- Fail-safe operation prevents panel damage with system clock failure

- Programmable skew rate controlled outputs on CD interface for reduced EMI

- Polarity pin reduces CD data bus switching

- CMOS circuitry operates from a 3.3V supply

## **System Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

4.1V Supply Voltage (V<sub>DD</sub>) DC Input Voltage (V<sub>IN</sub>) -0.5V to  $V_{\rm DD}$  +0.5V –0.5V to  $V_{\rm DD}$  +0.5V DC Output Voltage (V<sub>OUT</sub>) Storage Temperature Range (T<sub>STG</sub>)  $-65^{\circ}$ C to  $+150^{\circ}$ C Lead Temperature (T<sub>L</sub>) (Soldering 10 sec.)

260°C

ESD Rating:  $(C_{ZAP} = 120 \text{ pF}, R_{ZAP} = 1500\Omega)$ MM = 200V, HBM = 2000V

## **Operating Conditions**

|                                         | Min | Max | Units |

|-----------------------------------------|-----|-----|-------|

| Supply Voltage (V <sub>DD</sub> )       | 3.0 | 3.6 | V     |

| Operating Temp. Range (T <sub>A</sub> ) | 0   | 70  | °C    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

# **DC Electrical Characteristics** $T_A$ = 0°C to 70°C, $V_{DD}$ = 3.3V $\pm$ 0.3V (unless otherwise specified)

| Symbol          | Parameter                                | Conditions                                     | Min  | Max  | Units |

|-----------------|------------------------------------------|------------------------------------------------|------|------|-------|

| V <sub>OH</sub> | Minimum High Level Output Voltage        | V <sub>DD</sub> = 3.0V, I <sub>OH</sub> = 1 mA | 2.4  |      | V     |

| V <sub>OL</sub> | Maximum Low Level Output Voltage         | V <sub>DD</sub> = 3.0V, I <sub>OL</sub> = 1 mA |      | 0.4  | V     |

| V <sub>IH</sub> | Minimum High Level Input Voltage         |                                                | 2.0  |      | V     |

| V <sub>IL</sub> | Maximum Low Level Input Voltage          |                                                |      | 0.8  | V     |

| I <sub>IN</sub> | Input Current                            | $V_{IN} = V_{DD}$                              |      | 10   | μA    |

| l <sub>oz</sub> | Maximum TRI-STATE Output Leakage Current | $V_{IN} = V_{DD}, V_{IN} = V_{SS}$             |      | 10   | μА    |

| I <sub>DD</sub> | Average Supply Current                   | f = 65 MHz, C <sub>LOAD</sub> = 50 pF          |      | 312  | mA    |

| $V_{THH}$       | Differential Input High<br>Threshold     | Common Mode Voltage = +1.2V                    |      | +100 | mV    |

| $V_{THL}$       | Differential Input Low<br>Threshold      | Common Mode Voltage = +1.2V                    | -100 |      | mV    |

## **Device Specifications** $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{DD} = 3.3V$ (unless otherwise specified)

| Symbol | Parameter                             | Conditions | Min | Max | Units |

|--------|---------------------------------------|------------|-----|-----|-------|

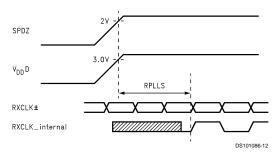

| RPLLS  | Receiver Phase Lock Loop Set Time     |            |     | 10  | ms    |

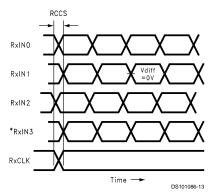

| RCCS   | RxIN Channel-to-Channel Skew (Note 2) |            |     | 700 | ps    |

Note 2: This limit assumes a maximum cable skew of 350 ps. Actual automated test equipment limit is 400 ps due to tester accuracy.

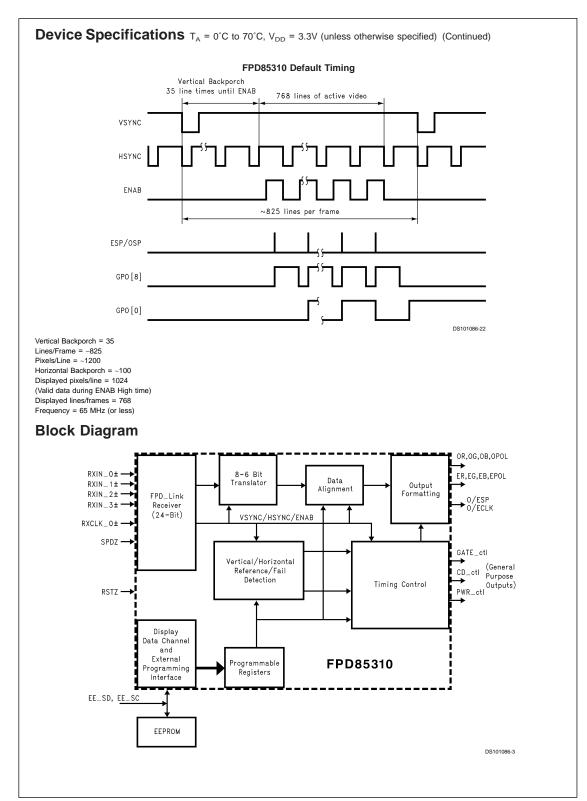

FIGURE 1. FPD85310 (Receiver) Phase Lock Loop Set Time

# **Device Specifications** $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{DD} = 3.3V$ (unless otherwise specified) (Continued)

Note 3: Measurements at V<sub>DIFF</sub> = 0V

Note 4: RCCS measured between earliest and latest LVDS edges

Note 5: \*RxIN3 pair (RxIN\_3±) is option for 24-bit color depth

FIGURE 2. FPD85310 (Receiver) Channel-to-Channel Skew and Pulse Width

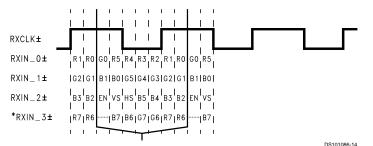

FIGURE 3. FPD85310's (Receiver) Format of the Input Data

| Symbol    | Parameter                     | Conditions            | Min | Max | Units |

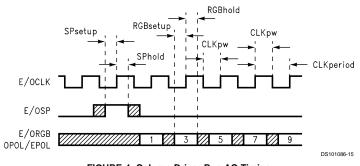

|-----------|-------------------------------|-----------------------|-----|-----|-------|

| SPsetup   | E/OSP from E/OCLK             | 65 MHz Video (Note 6) | 8   |     | ns    |

| SPhold    | E/OSP from E/OCLK             | 65 MHz Video (Note 6) | 8   |     | ns    |

| RGBsetup  | ER/EG/EB/OR/OG/OB from E/OCLK | 65 MHz Video (Note 6) | 8   |     | ns    |

| RGBhold   | ER/EG/EB/OR/OG/OB from E/OCLK | 65 MHz Video (Note 6) | 8   |     | ns    |

| CLKpw     | E/OCLK pulsewidth             | 65 MHz Video (Note 6) | 11  |     | ns    |

| CLKperiod | E/OCLK period                 | 65 MHz Video (Note 6) | 25  |     | ns    |

Note 6: Timing applies to Dual Bus output modes.

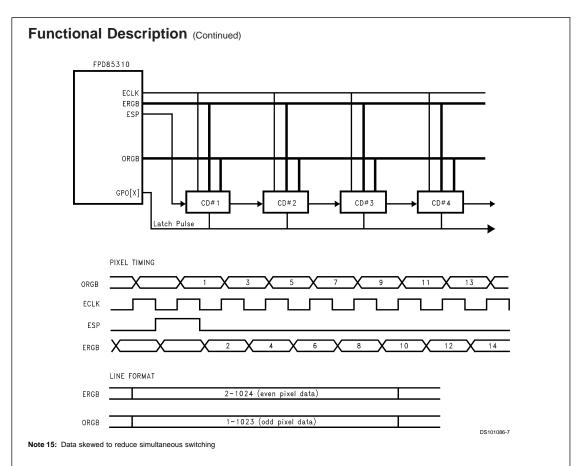

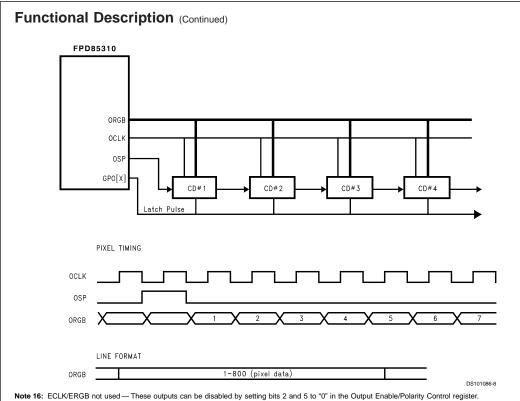

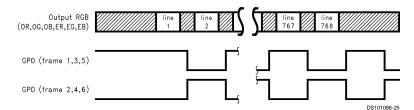

FIGURE 4. Column Driver Bus AC Timing

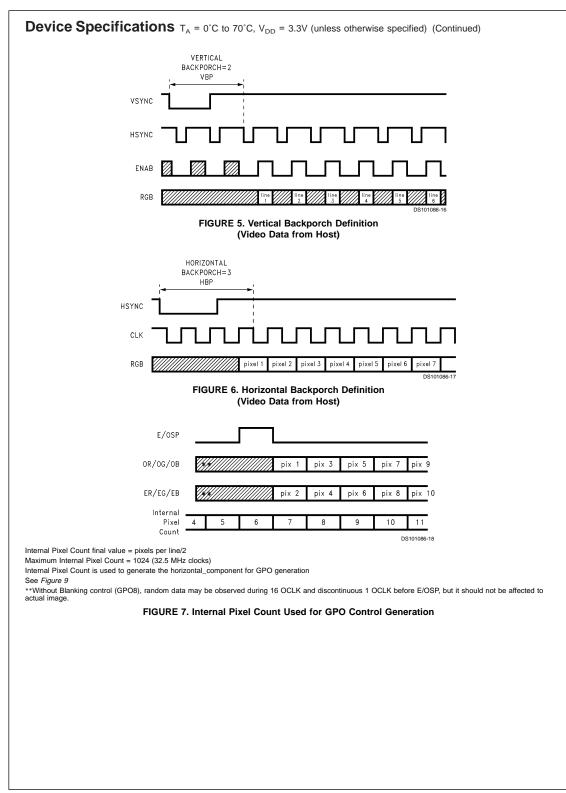

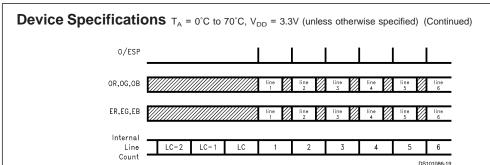

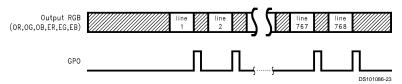

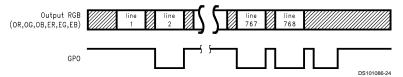

LC = lines per frame count, LCmax = 2048 lines Internal Line Count is used to generate the vertical component for GPO generation See *Figure 9*

FIGURE 8. Internal Line Count Used for GPO Control Generation

## **GPO** Generation Internal Line Count vertical\_start Vertical Component Internal Line Count vertical\_start + vertical\_duration Internal Pixel Count $horizontal\_start$ Horizontal Internal Pixel Count Component GPO[n]\_CONTROL[1:0] horizontal\_start + pixel\_duration toggle flop for REV generation DS101086-20

GPO Combination Select

GPO\*[n]

a a \* b 01

GPO[n]

GPO[n]

GPO[n]

GPO Combination Select)

VSYNC

DS101086-21

FIGURE 9. GPO Control Generation

## **Functional Description**

### **FPD-LINK RECEIVER**

The LVDS based FPD-Link Receiver receives inputs video data and control timing. Four LVDS channels plus clock provide 24-bit color. Three LVDS channels can be used for 18-bit color.

The video data is regenerated to a parallel data stream and routed to the 8 to 6 Bit Translator. When SPDZ is active (low) the FPD85310 is placed in a power down mode. The General Purpose Outputs (GPOs) continue outputting the programmed control sequence at a reduced frame rate. RSTZ initialized the chip with the default register values. EEPROM configuration data is loaded if EEPROM is detected. (EEPROM address 80H = "00").

#### 8 to 6 Bit Translator

8-bit data is reduced to a 6-bit data path via a time multiplexed dithering technique or a simple truncation of the LSBs. This function is enabled via the Input Control Register bits 4 and 3. See *Table 2* Input Format Control register.

## DATA ALIGNMENT

This function delays and aligns data to match the CD/panel architect. The following programmable selections in the Output Format Control Register bits 0 and 1 provide support for various panel architectures. See *Figures 10, 11, 12, 13, 14* for additional explanation.

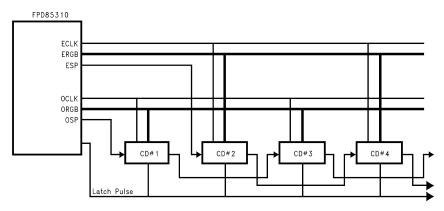

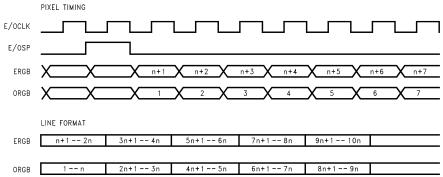

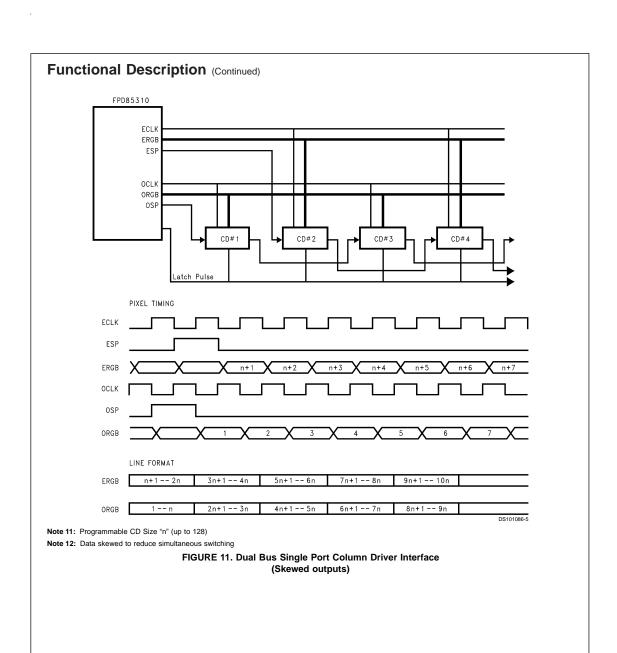

## **Dual Bus, Single Port CD Interface**

When interfacing two busses to a bank of single port column drivers, the RGB data must be aligned/delayed with respect to the size of the column drivers being used. The CD Size register is programmed to support single port column drivers of up to 384 outputs (128 pixels).

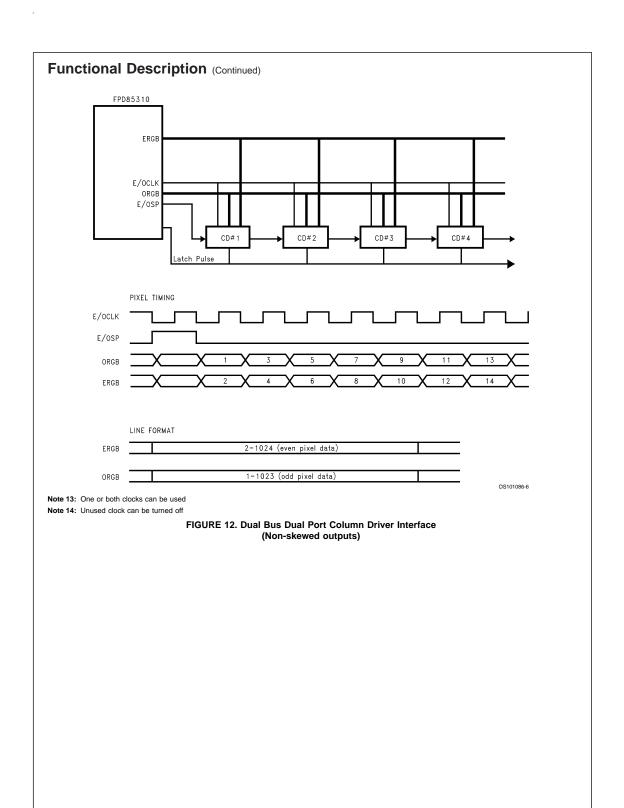

### **Dual Bus, Dual Port CD Interface**

When interfacing with dual port column drivers, data is simply output with odd and even data on separate outputs.

### Single Bus, Single Port CD Interface

The single bus, single port column driver interface provides support of existing SVGA systems. All data is output on a single bus. The second bus can be turned off when using this configuration.

### **Output Formatting**

The output formatting function provides several capabilities to reduce noise EMI and to generate customized timing. These capabilities are selectable/programmable via the Output Format Control, Output Enable/Polarity Control, and Output Drive Control Registers. See *Table 2* for specific bit definitions

### **Data Bus Skewing**

This function aligns the two output channels in either a nonskewed data format (simultaneous switching) or a skewed data format. The skewed format delays the even channel data and control by ½ clock. This reduces the number of outputs which switch simultaneously. See *Figures 10, 11, 12, 13, 14.* Data Bus Skewing is enabled by setting bit 2 in the Output Format Control register.

#### **Programmable Skew Rates**

Programmable edge rates allow the Data, Polarity, Start Pulse, and Clock outputs to be adjusted for better impedance matching for noise and EMI reduction. Bits [7:6] of the Output Enable/Polarity Control Register control OSP and ESP outputs. The Output Drive Control register control the OCLK, ECLK, ORGB/OPOL, ERGB/EPOL outputs.

#### **Polarity Generation**

When enabled, a polarity indication is output for each data bus. If the number of transitions from pixel to pixel exceed 18 bits from 36 bits, the data is inverted and a polarity indication corresponding to that bus is set active. This requires the use of a CD with a polarity input and in "SKEWED" mode, OPOL and EPOL are separated for each skewing then two port CD need to be two polarity inputs. Polarity Generation is not supported in the single bus/single port CD configuration (SVGA configuration). The polarity function is enabled by setting bit 6 of the Output Format Control register (EEPROM address D2). The OCLK and ECLK polarity is also programmable. Inversion and TRI-STATE control of OCLK and ECLK is provided by bits [3:0] of the Output Enable/Polarity Control Register. The ERGB/ESP/EPOL and ORGB/OSP/OPAL outputs can be disabled (TRI-STATE) using bits [5:4] of the Output Enable/Polarity Control register.

### **Programmable Positioning of CD Start Pulse**

The position of the CD Start Pulse is programmable. This allows use with column drivers having non-standard start pulse timing. The CD Start Pulse position is determined by bits [3:0] of the Output Format Control Register (EEPROM address D3).

## **Data Blanking**

Data, Polarity, Start Pulse and Clock can be blanked (forced to "0") during horizontal and/or vertical blanking periods. GPO [8] is programmed to correspond to display periods. When GPO [8] is low, outputs are forced to "0". This reduces amount of switching over the frame time thus reducing power. See GPO programming procedure in APPENDIX A: GPO Programming Examples.

#### Line Inversion

When enabled (Bit 3 of the Output Format Register), the polarity of the output data is determined by GPO [0]. Bit 4 defines the relationship between GPO [0] and the output data. Bit 5 provides a variation of this where the Odd and Even data is of different polarity. This could be used in a system with CDs on both top and bottom of the panel in which dot inversion is desired.

#### White Data

The White Data function generates all "1" data beginning at line 769 and continuing until the beginning of the next frame. This function is controlled via D6 Register Bit 7.

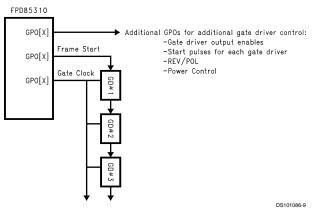

## Timing Control

The Timing Control function generates control to column drivers, row drivers, and power supply. The programmable GPOs provide for CD latch pulse, REV, and gate driver control generation. The GPOs allow the user to generate control anywhere within the frame data. Standard gate driver inter-

face or custom gate interfaces can be implemented with the nine GPOs. Note that GPO [8] must be used for output blanking control.

Five registers provide the timing definition for each GPO. The Horizontal Start register defines the output pixel number for which the GPO output goes active. The Horizontal duration register determines how many clocks the output will remain active during the line. The Vertical Start register defines at what line # the output becomes active, and the Vertical duration register defines how many lines the output remains active. Each output has a control register (bit 0) which defines the GPO polarity (active high or low). Another bit in the control register (bit 1) enables the "toggle" mode. This mode is useful in REV generation when alternating polarity is required from line. Frame to Frame polarity changes are made by programming an odd # in the vertical duration register when in "toggle" mode.

Two of the General Purpose Outputs have additional capabilities. GPO [8] controls output blanking and must be used for this purpose. If output blanking is not desired, this register must be programmed to always be active. White data generation (all "1" data) at the end of each frame is generated when D6 register bit 7 is set. When this bit is set, white data is output after line #768 if GPO [8] is active. GPO [0] is capable of performing line inversion on the output data. Bits [5:3] of the Output Format Control register provides control for this function.

See APPENDIX A: GPO Programming Examples.

#### SERIAL EEPROM INTERFACE

The Serial EEPROM Interface controls the FPD85310 initialization. If the EEPROM is not present (EESD and EESC are pulled high), or if EEPROM address 80H is not "00", the internal default values are used to initialize all programmable functions of the FPD85310.

At power-up, the FPD85310 configures the internal programmable registers with data from the EEPROM. After the FPD85310 is initialized, the EEPROM can be accessed by the system in which display configuration and manufacturing information can be obtained. The EEPROM can be programmed "in system" providing quick evaluation of different display timing.

External access to the EEPROM must be preceded by applying a "1" to pin TEST [2] in order to interrupt the FPD85310 download.

The FPD85310 initialization data begins at EEPROM address 80H. The first 128 bytes (0-7F) are reserved for display identification data.

A power-up delay can be programmed using bits [6:5] of the Input Format Control Register. This delays outputting (driving) of the data and control for up to 5 frame times after reset. The TEST [2] pin must be low for a power-up delay to occur.

# VERTICAL/HORIZONTAL REFERENCE GENERATOR AND FAILURE DETECTION

This block provides Vertical and Horizontal Reference points for the Timing Control Function. VSYNC, HSYNC and ENAB along with programmable control from the input control register bits 0 and 1 (FIX HORIZONTAL and FIX VERTICAL) are used to determine when the video from the host is valid. Three input modes are supported. See *Table 1*.

#### Fixed Vertical, Fixed Horizontal

The horizontal timing is fixed and determined by the Horizontal Backporch register. The vertical timing is also fixed and determined by the Vertical Backporch register. ENAB is ignored and is not necessary.

#### Fixed Vertical, ENAB Controlled Horizontal

The horizontal timing is controlled by the ENAB timing. The vertical timing is fixed and determined by the Vertical Backporch register.

#### **ENAB Only**

In ENAB Only timing, VSYNC and HSYNC are ignored. All timing is derived from the ENAB signal.

#### **Failure Detection**

The FPD85310 detects the loss of (necessary) control from the system. VSYNC, HSYNC, ENAB, and CLK are monitored for failure conditions. Failure condition is detected whenever the input clock stops or when control necessary for the operational mode is inactive. Failure conditions result in outputting a default video stream to the panel. Depending on the mode, loss of CLK, ENAB, HSYNC and/or VSYNC will result in fail condition output timing. The FPD85310 has an internal oscillator used for input clock failure detection. If the input clock quits toggling, the internal oscillator generates the control timing to the column drivers and row drivers. The internal ring oscillator is disabled when a "1" is applied to the TEST [3] pin. This will, of course, disable the clock failure detection capability of the FPD85310. Further description of the failure detection modes is given in *Table 4*.

## TABLE 1. Input Mode Definition

| INPUT FORMAT FIXED VERTICAL, FIXED HORIZONTAL determined by the INPUT CONTROL REGISTER bits [1:0] | HORIZONTAL<br>DATA START                               | VERTICAL<br>DATA START                                                      |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------|

| FIXED VERTICAL, FIXED HORIZONTAL (FIX VERTICAL = 1, FIX HORIZONTAL = 1)                           | Programmable from HSYNC Falling Edge<br>(# INPUT CLKS) | Programmable from VSYNC<br>Falling Edge<br>(# HSYNC PERIODS)                |

| FIXED VERTICAL, ENAB HORIZONTAL (FIXED VERTICAL = 1, FIXED HORIZONTAL = 0)                        | Data Valid during ENAB high (HSYNC is IGNORED)         | Programmable from VSYNC<br>Falling Fdge<br>(# HSYNC PERIODS)                |

| ENAB ONLY<br>(FIXED VERTICAL = 0,<br>FIXED HORIZONTAL = 0)                                        | Data Valid during ENAB High (HSYNC is IGNORED)         | First ENAB after ENAB low for greater than one line time (VSYNC is IGNORED) |

Note: INPUT CONTROL REGISTER bit[2] "Enab Detection" provides for "auto-detection" of ENAB. When "1" and Enab is not toggling, the controller will automatically set the input mode to Fixed Vertical, Fixed Horizontal.

## PROGRAMMABLE REGISTERS

At power-up, data is read from an external EEPROM. If anything other than 00H is read back on the first EEPROM access (indicating EEPROM not present), the internal default

values are used. The following parameters are initialized at power up. Pullups must be used on EE\_SD and EE\_SC nins

TABLE 2. FPD85310 Programmable Register Definition

| Control       | EEPROM  |          |                                                                                     |

|---------------|---------|----------|-------------------------------------------------------------------------------------|

| Registers     | Address | The conf | trol registers provide mode setting information to the input and output interfaces. |

| Output Format | D2      | [1:0]    | "00" = Dual Bus, Single port CD interface                                           |

| Control       |         | ,        | "01" = Dual Bus, Dual port CD interface                                             |

|               |         |          | "10" = Single Bus, Single port CD interface                                         |

|               |         |          | "11" = Not implemented (defaults to "10")                                           |

|               |         | [2]      | "0" = Non-Skewed outputs                                                            |

|               |         |          | "1" = Skewed outputs                                                                |

|               |         | [3]      | "0" = Data inversion is disabled                                                    |

|               |         |          | "1" = Data inversion is enabled                                                     |

|               |         | [4]      | "0" = Data inversion when GPO[0] is "0"                                             |

|               |         |          | "1" = Data inversion when GPO[0] is "1"                                             |

|               |         | [5]      | "0" = Even and Odd data inversion when data inversion is enabled                    |

|               |         |          | "1" = Odd data inversion determined by bit[4], Even data opposite of Odd data       |

|               |         | [6]      | "0" = Polarity Function disabled                                                    |

|               |         |          | "1" = Polarity Function enabled                                                     |

|               |         | [7]      | "0" = OPOL/EPOL = 0 when data is inverted                                           |

|               |         |          | "1" = OPOL/EPOL = 1 when data is inverted                                           |

|               | D3      | [1:0]    | Odd Start Pulse Offset                                                              |

|               |         |          | "00" = Start pulse 0 clocks before data                                             |

|               |         |          | "01" = Start pulse 1 clock before data                                              |

|               |         |          | "10" = Start pulse 2 clocks before data                                             |

|               |         |          | "11" = Start pulse 3 clocks before data                                             |

|               |         | [3:2]    | Even Start Pulse Offset                                                             |

|               |         |          | "00" = Start pulse 0 clocks before data                                             |

|               |         |          | "01" = Start pulse 1 clock before data                                              |

|               |         |          | "10" = Start pulse 2 clocks before data                                             |

|               |         |          | "11" = Start pulse 3 clocks before data                                             |

|               |         | [7:4]    | Unused Pixels                                                                       |

|               |         |          | "0000" = no unconnected pixels at beginning of first CD                             |

|               |         |          | "0001" = 1 unconnected pixel at beginning of first CD                               |

|               |         |          | "0010" = 2 unconnected pixels at beginning of first CD                              |

|               |         |          |                                                                                     |

|               |         |          |                                                                                     |

|               |         |          | "1111" = 15 unconnected pixels at beginning of first CD                             |

TABLE 2. FPD85310 Programmable Register Definition (Continued)

| Control<br>Registers | EEPROM<br>Address | The control registers provide mode setting information to the input and output interfaces. |                                                                                                                                                                                                                                                                   |                   |                  |                                             |  |  |

|----------------------|-------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|---------------------------------------------|--|--|

| Output               | DB                | [0]                                                                                        | OCLK Enal                                                                                                                                                                                                                                                         | ole (1-On, 0-T    | RI-STATE)        |                                             |  |  |

| Enable/Polarity      |                   | [1]                                                                                        | OCLK Pola                                                                                                                                                                                                                                                         | rity (1-Per Da    | tasheet, 0-Inv   | erted)                                      |  |  |

| Control              |                   | [2]                                                                                        | 2] ECLK Enable (1-On, 0-TRI-STATE)                                                                                                                                                                                                                                |                   |                  |                                             |  |  |

|                      |                   | [3]                                                                                        | ECLK Polarity (1-Per Datasheet, 0-Inverted)                                                                                                                                                                                                                       |                   |                  |                                             |  |  |

|                      |                   | [4]                                                                                        | ORGB/OSP/OPOL Enable (1-On, 0-TRI-STATE)                                                                                                                                                                                                                          |                   |                  |                                             |  |  |

|                      |                   | [5]                                                                                        | ERGB/ESP/EPOL Enable (1-On, 0-TRI-STATE)                                                                                                                                                                                                                          |                   |                  |                                             |  |  |

|                      |                   | [7:6]                                                                                      | OSP/ESP Control                                                                                                                                                                                                                                                   |                   |                  |                                             |  |  |

|                      |                   | ` '                                                                                        | [7,6] Output                                                                                                                                                                                                                                                      |                   |                  |                                             |  |  |

|                      |                   |                                                                                            |                                                                                                                                                                                                                                                                   | west Drive        |                  |                                             |  |  |

|                      |                   |                                                                                            | 0,1                                                                                                                                                                                                                                                               |                   |                  |                                             |  |  |

|                      |                   |                                                                                            | 1,0                                                                                                                                                                                                                                                               |                   |                  |                                             |  |  |

|                      |                   |                                                                                            | ,                                                                                                                                                                                                                                                                 | hest Drive        |                  |                                             |  |  |

| Output Drive         | D4                | [1:0]                                                                                      | OCLK Cont                                                                                                                                                                                                                                                         |                   |                  |                                             |  |  |

| Control              | 04                | [3:2]                                                                                      | ECLK Cont                                                                                                                                                                                                                                                         |                   |                  |                                             |  |  |

|                      |                   |                                                                                            |                                                                                                                                                                                                                                                                   |                   |                  |                                             |  |  |

|                      |                   |                                                                                            | [5:4] ORGB/OPOL Control [7:6] ERGB/EPOL Control                                                                                                                                                                                                                   |                   |                  |                                             |  |  |

|                      |                   | [7:6]                                                                                      |                                                                                                                                                                                                                                                                   |                   |                  |                                             |  |  |

|                      |                   |                                                                                            |                                                                                                                                                                                                                                                                   | Output            |                  |                                             |  |  |

|                      |                   |                                                                                            | 0,0 Lowest Drive                                                                                                                                                                                                                                                  |                   |                  |                                             |  |  |

|                      |                   |                                                                                            | 0,1                                                                                                                                                                                                                                                               |                   |                  |                                             |  |  |

|                      |                   |                                                                                            | 1,0                                                                                                                                                                                                                                                               |                   |                  |                                             |  |  |

| CD Size              | D5                | [7:0]                                                                                      | 1,1 H<br>= # Data/C                                                                                                                                                                                                                                               | ighest Drive      |                  |                                             |  |  |

|                      |                   |                                                                                            | This number defines how many contiguous pixels are output on the odd and even data channels for the single port CD interface. CD sizes of up to 128 pixel (384 channel) are supported. A minimum value of 20H must be programmed regardless of CD interface used. |                   |                  |                                             |  |  |

| Input Format         | D6                | [0]                                                                                        | Fix Vertical                                                                                                                                                                                                                                                      |                   |                  |                                             |  |  |

| Control              |                   |                                                                                            | "0" = Vertic                                                                                                                                                                                                                                                      | al position der   | pendent on fir   | st ENAB from VSYNC                          |  |  |

|                      |                   |                                                                                            |                                                                                                                                                                                                                                                                   |                   |                  | ertical Backporch Register                  |  |  |

|                      |                   | [1]                                                                                        | Fix Horizon                                                                                                                                                                                                                                                       |                   | Jonaoni on vi    | Stribal Backpoton (togloto)                 |  |  |

|                      |                   | 1.,1                                                                                       |                                                                                                                                                                                                                                                                   | ontal position    | denendent on     | FNAB                                        |  |  |

|                      |                   |                                                                                            |                                                                                                                                                                                                                                                                   |                   |                  | Horizontal Backporch Register               |  |  |

|                      |                   |                                                                                            |                                                                                                                                                                                                                                                                   | 1 for valid mo    |                  |                                             |  |  |

|                      |                   | [2]                                                                                        | Enab detec                                                                                                                                                                                                                                                        |                   | de combinati     | 013.                                        |  |  |

|                      |                   | ا ادا                                                                                      |                                                                                                                                                                                                                                                                   | detection off     |                  |                                             |  |  |

|                      |                   |                                                                                            |                                                                                                                                                                                                                                                                   |                   | detecto if Fra   | b in toggling)                              |  |  |

|                      |                   |                                                                                            |                                                                                                                                                                                                                                                                   | detection on (    |                  | 00 0,                                       |  |  |

|                      |                   |                                                                                            |                                                                                                                                                                                                                                                                   | switching whe     |                  |                                             |  |  |

|                      |                   |                                                                                            | Fix<br>Vertical                                                                                                                                                                                                                                                   | Fix<br>Horizontal | Enab<br>Toggling | Operating Mode                              |  |  |

|                      |                   |                                                                                            | 0                                                                                                                                                                                                                                                                 | 0                 | Yes              | ENAB ONLY                                   |  |  |

|                      |                   |                                                                                            | 0                                                                                                                                                                                                                                                                 | 0                 | No               | FV/FH                                       |  |  |

|                      |                   |                                                                                            | 1                                                                                                                                                                                                                                                                 | 0                 | Yes              | FV/ENAB HORIZ                               |  |  |

|                      |                   |                                                                                            | 1                                                                                                                                                                                                                                                                 | 0                 | No               | FV/FH                                       |  |  |

|                      |                   |                                                                                            | 1                                                                                                                                                                                                                                                                 | 1                 | Х                | FV/FH                                       |  |  |

|                      |                   | Note: In<br>Mode"                                                                          | put sync. need                                                                                                                                                                                                                                                    | d to be procee    | eded before R    | STZ goes "high" to determine the "Operating |  |  |

| Address                   | The control registers provide mode setting information to the input and output interfaces.  [3] Enable/Disable Virtual 8-bit (8-bit input only)  "0" = Virtual 8-bit enabled  "1" = Virtual 8-bit disabled (Truncate LSBs)  [4] Eight/Six Bit Video  "0" = Six Bit Video  "1" = Eight Bit Video  [6:5] Power-up Delay (TEST2 must be "0")  "00" = Outputs active after second VSYNC |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | "0" = Virtual 8-bit enabled "1" = Virtual 8-bit disabled (Truncate LSBs)  [4] Eight/Six Bit Video "0" = Six Bit Video "1" = Eight Bit Video  [6:5] Power-up Delay (TEST2 must be "0")                                                                                                                                                                                               |

| -                         | "1" = Virtual 8-bit disabled (Truncate LSBs)  [4] Eight/Six Bit Video "0" = Six Bit Video "1" = Eight Bit Video  [6:5] Power-up Delay (TEST2 must be "0")                                                                                                                                                                                                                           |

| _                         | [4] Eight/Six Bit Video  "0" = Six Bit Video  "1" = Eight Bit Video  [6:5] Power-up Delay (TEST2 must be "0")                                                                                                                                                                                                                                                                       |

|                           | "0" = Six Bit Video "1" = Eight Bit Video  [6:5] Power-up Delay (TEST2 must be "0")                                                                                                                                                                                                                                                                                                 |

|                           | "1" = Eight Bit Video [6:5] Power-up Delay (TEST2 must be "0")                                                                                                                                                                                                                                                                                                                      |

|                           | [6:5] Power-up Delay (TEST2 must be "0")                                                                                                                                                                                                                                                                                                                                            |

|                           |                                                                                                                                                                                                                                                                                                                                                                                     |

|                           | "00" = Outputs active after second VSYNC                                                                                                                                                                                                                                                                                                                                            |

|                           |                                                                                                                                                                                                                                                                                                                                                                                     |

|                           | "01" = Outputs active after third VSYNC                                                                                                                                                                                                                                                                                                                                             |

|                           | "10" = Outputs active after fourth VSYNC                                                                                                                                                                                                                                                                                                                                            |

|                           | "11" = Outputs active after fifth VSYNC                                                                                                                                                                                                                                                                                                                                             |

|                           | [7] White Data Generation                                                                                                                                                                                                                                                                                                                                                           |

|                           | "0" = No white data generation                                                                                                                                                                                                                                                                                                                                                      |

|                           | "1" = Enables white data generation during vertical blanking                                                                                                                                                                                                                                                                                                                        |

| DA, D9                    | # of HSYNCS from VSYNC falling edge until start of video                                                                                                                                                                                                                                                                                                                            |

| .                         |                                                                                                                                                                                                                                                                                                                                                                                     |

|                           |                                                                                                                                                                                                                                                                                                                                                                                     |

| 08, D7                    | # of 65 MHz clocks after the falling edge of HSYNC until start of video                                                                                                                                                                                                                                                                                                             |

|                           |                                                                                                                                                                                                                                                                                                                                                                                     |

|                           |                                                                                                                                                                                                                                                                                                                                                                                     |

| Table 3                   | The GPO registers provide complete control over placement of control edges/strobes within the data frame. The GPO timing registers (Vertical Start, Vertical Duration, Horizontal Start, and                                                                                                                                                                                        |

| EEPROM  <br>Memory<br>Map | Horizontal Duration) define the control timing relative to the internal line and pixel counters. The line counter corresponds to the line being displayed. The pixel counter corresponds to the pixel output each line. The Control Register provides polarity selection and/or generation of a line to                                                                             |

|                           | line frame-to-frame alternating signal (REV). Each General Purpose Output can be uniquely configured. See the GPO programming examples for details.                                                                                                                                                                                                                                 |

|                           | - GPO $\left[0\right]$ provides for the data inversion function enabled by bit 3 of the Output Format Control Register                                                                                                                                                                                                                                                              |

|                           | - GPO [8] provides programmable data and clock blanking                                                                                                                                                                                                                                                                                                                             |

| Γ                         | Line # at which GPO [X] control generation begins                                                                                                                                                                                                                                                                                                                                   |

| L                         |                                                                                                                                                                                                                                                                                                                                                                                     |

|                           | # lines GPO [X] control generation continues                                                                                                                                                                                                                                                                                                                                        |

|                           | (if "0", Vertical component is always on)                                                                                                                                                                                                                                                                                                                                           |

|                           |                                                                                                                                                                                                                                                                                                                                                                                     |

|                           | Internal count (pixel counter) at which GPO [X] goes active to be triggered on rising edge of the                                                                                                                                                                                                                                                                                   |

|                           | OCLK  Note: If control register [1] = "1" start position will be moved by 1 pixel clock                                                                                                                                                                                                                                                                                             |

| -                         | Note: If control register [1] = "1", start position will be moved by 1 pixel clock                                                                                                                                                                                                                                                                                                  |

|                           | # Pixel Clocks/2 GPO [X] is active after Horizontal Start (if "0", Horizontal component is always on)                                                                                                                                                                                                                                                                               |

|                           | (ii o , i ionzoniai component is aiways on)                                                                                                                                                                                                                                                                                                                                         |

| S .                       | 8, D7  ee able 3 EPROM                                                                                                                                                                                                                                                                                                                                                              |

TABLE 2. FPD85310 Programmable Register Definition (Continued)

|                  |         | IADLE 2.  | repossio Programmable Register Definition (Continued)                                                                                                                                                                 |

|------------------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control          | EEPROM  | The con   | trol registers provide mode setting information to the input and output interfaces.                                                                                                                                   |

| Registers        | Address | THE COIL  | inor registers provide mode setting information to the input and output interfaces.                                                                                                                                   |

| Control Register |         | [0]. Outp | out polarity - defines active high or active low output                                                                                                                                                               |

| (5 bits)         |         |           | "0" = normal output (active high)                                                                                                                                                                                     |

|                  |         |           | "1" = inverted output (active low)                                                                                                                                                                                    |

|                  |         | [1]. Togg | gle circuit enable/disable                                                                                                                                                                                            |

|                  |         |           | "0" = Normal GPO output; Toggle circuitry disabled                                                                                                                                                                    |

|                  |         |           | "1" = Toggle circuitry enabled; output transitions after 1 clock (pixel counter) whenever programmed rising edge of GPO occurs.                                                                                       |

|                  |         |           | When "toggle circuit" is enable, the value of "Horizontal Duration" register programming determine; "001h"~'1 H-line-1' = 1 H-line toggling, '1 H-line'~'2 H-line-1' = 2 H-line toggling, etc. up to 11 bits are set. |

|                  |         | [2].      | Automatic Frame Size Detection                                                                                                                                                                                        |

|                  |         |           | GPO [0:1]                                                                                                                                                                                                             |

|                  |         |           | "0" = Normal Operation                                                                                                                                                                                                |

|                  |         |           | "1" = Used with toggle circuitry to create a "continuous" REV signal. NOTE: The value of the vertical duration register is overwritten.                                                                               |

|                  |         |           | GPO [2:8]                                                                                                                                                                                                             |

|                  |         |           | "0" = Normal Operation                                                                                                                                                                                                |

|                  |         |           | "1" = Early Start capability (Vertical Duration = "00" is N/A, See Table 5)                                                                                                                                           |

|                  |         |           | The value in the Vertical Start Register is subtracted from the total number of lines/frame (auto-detected) to determine the Vertical Start position.                                                                 |

|                  |         |           | (It needs a full frame after RSTZ, then started with 1 frame delayed to compare to the other GPOs)                                                                                                                    |

|                  |         | [4:3]     | GPO [0:8] Combination Select* (Two GPOs or multi GPOs)                                                                                                                                                                |

|                  |         |           | "00" = Select GPO# as programmed. (no combination function)                                                                                                                                                           |

|                  |         |           | "01" = Select GPO# "ANDed" with GPO#-1                                                                                                                                                                                |

|                  |         |           | "10" = Select GPO# "ORed" with GPO#-1                                                                                                                                                                                 |

|                  |         |           | "11" = Select GPO# and GPO#-1 on alternating frames                                                                                                                                                                   |

|                  |         |           | (*If the transition of GPO#-1 effect the combined result, it should be delayed 1 OCLK, and GPO0 cannot be programmed by non-existing of "GPO-1")                                                                      |

|                  |         | (Example  | es) GPO#-1 AND GPO#, (GPO#-2 and GPO#-1) OR GPO# and etc.                                                                                                                                                             |

## TABLE 3. EEPROM Memory Map

| Address | Data (# bits)                            | Default Values |

|---------|------------------------------------------|----------------|

| 0-7F    | DDC VESA DATA                            | (HEX)          |

| 80      | programmed to 00H for EEPROM auto detect | 00             |

|         |                                          |                |

| 82,81   | gpo [8]_pstart_reg (10)                  | 00,01          |

| 84,83   | gpo [8]_pcount_reg (11)                  | 02,2D          |

| 86,85   | gpo [8]_lstart_reg (11)                  | 00,01          |

| 88,87   | gpo [8]_lcount_reg (11)                  | 03,02          |

| 89      | gpo [8]_cont_reg (5)                     | 00             |

|         |                                          |                |

| 8B,8A   | gpo [7]_pstart_reg (10)                  | 00,14          |

| 8D,8C   | gpo [7]_pcount_reg (11)                  | 01,E0          |

| 8F,8E   | gpo [7]_lstart_reg (11)                  | 00,02          |

| 91,90   | gpo [7]_lcount_reg (11)                  | 03,00          |

| 92      | gpo [7]_cont_reg (5)                     | 01             |

|         |                                          |                |

## TABLE 3. EEPROM Memory Map (Continued)

| Address        | Data (# bits)                                    | Default Values |

|----------------|--------------------------------------------------|----------------|

| 94,93          | gpo [6]_pstart_reg (10)                          | 00,01          |

| 96,95          | gpo [6]_psunt_reg (11)                           | 02,9F          |

| 98,97          | gpo [6]_Istart_reg (11)                          | 02,91<br>01,FD |

| 9A,99          | gpo [6]_lcount_reg (11)                          | 00,01          |

| 9B             |                                                  | 00,01          |

| 96             | gpo [6]_cont_reg (5)                             | 01             |

| 9D,9C          | gpo [5]_pstart_reg (10)                          | 00,01          |

| 9F,9E          | gpo [5]_pcount_reg (11)                          | 02,9F          |

| A1,A0          | gpo [5]_lstart_reg (11)                          | 00,FD          |

| A3,A2          | gpo [5]_lcount_reg (11)                          | 00,01          |

| A4             | gpo [5]_cont_reg (5)                             | 01             |

|                |                                                  |                |

| A6,A5          | gpo [4]_pstart_reg (10)                          | 00,01          |

| A8,A7          | gpo [4]_pcount_reg (11)                          | 02,9F          |

| AA,A9          | gpo [4]_lstart_reg (11)                          | 03,22          |

| AC,AB          | gpo [4]_lcountreg (11)                           | 00,01          |

| AD             | gpo [4]_cont_reg (5)                             | 01             |

| AF,AE          | gpo [3]_pstart_reg (10)                          | 01,E0          |

| B1,B0          | gpo [3]_pount_reg (11)                           | 00,28          |

| B3,B2          | gpo [3]_Istart_reg (11)                          | 00,01          |

| B5,B4          | gpo [3]_lcount_reg (11)                          | 00,00          |

| B6             | gpo [3]_cont_reg (5)                             | 01             |

|                |                                                  | -              |

| B8,B7          | gpo [2]_pstart_reg (10)                          | 02,0B          |

| BA,B9          | gpo [2]_pcount_reg (11)                          | 00,14          |

| BC,BB          | gpo [2]_lstart_reg (11)                          | 00,01          |

| BE,BD          | gpo [2]_lcount_reg (11)                          | 03,00          |

| BF             | gpo [2]_cont_reg (5)                             | 00             |

| 04.00          | M1 (40)                                          | 00.00          |

| C1,C0          | gpo [1]_pstart_reg (10)                          | 02,0D          |

| C3,C2          | gpo [1]_pcount_reg (11)                          | 00,0A          |

| C5,C4<br>C7,C6 | gpo [1]_lstart_reg (11)  gpo [1]_lcount_reg (11) | 00,01          |

|                |                                                  | 03,01          |

| C8             | gpo [1]_cont_reg (5)                             | 03             |

| CA,C9          | gpo [0]_pstart_reg (10)                          | 02,0D          |

| CC,CB          | gpo [0]_pcount_reg (11)                          | 00,0A          |

| CE,CD          | gpo [0]_lstart_reg (11)                          | 00,01          |

| D0,CF          | gpo [0]_lcount_reg (11)                          | 03,01          |

| D1             | gpo [0]_cont_reg (5)                             | 02             |

|                |                                                  |                |

| D3,D2          | output_format (16)                               | 00,00          |

| D4             | output_drive (8)                                 | AA             |

| D5             | cd_size (8)                                      | 67             |

| D6             | input_format (8)                                 | 01             |

TABLE 3. EEPROM Memory Map (Continued)

| Address | Data (# bits)                      | Default Values |

|---------|------------------------------------|----------------|

| D8,D7   | hbp_reg (11)                       | 00,94          |

| DA,D9   | vbp_reg (11)                       | 00,23          |

| DB      | output_enable/polarity_control (8) | BF             |

| FF-DC   | not used/not loaded                | _              |

DS101086

Note 7: Programmable CD Size "n" (up to 128)

Note 8: One or both clocks can be used

Note 9: Unused clocks can be turned off

Note 10: E/OCLK polarity is programmable

FIGURE 10. Dual Bus Single Port Column Driver Interface (Non-skewed outputs)

FIGURE 13. Dual Bus Dual Port Column Driver Interface (Skewed outputs)

Note 17: Start pulse offset\* (D3 [1:0]) is defined as below only in this mode.

"00" - Start pulse 1 clock after 1st data

"01" - Start pulse 1 clock before 1st data

"10" - Start pulse 3 clocks before 1st data

"11" - Start pulse 5 clocks before 1st data

\*Start pulse position can be adjusted precisely by unused pixels register (D3 [7:4])

Note 18: The Pcount and Pstart registers are programmed by 2 OCLK only in this mode. (Example) Pcount Register = "02":4 OCLK duration

FIGURE 14. Single Port Single Bus Column Driver Interface (SVGA Application)

Note 19: Total of eight GPOs for REV, LP, and Gate Driver Control (GPO [8] dedicated to blanking function)

Note 20: GPO resolution is video clock/2

FIGURE 15. Standard or Custom Gate Driver Interface

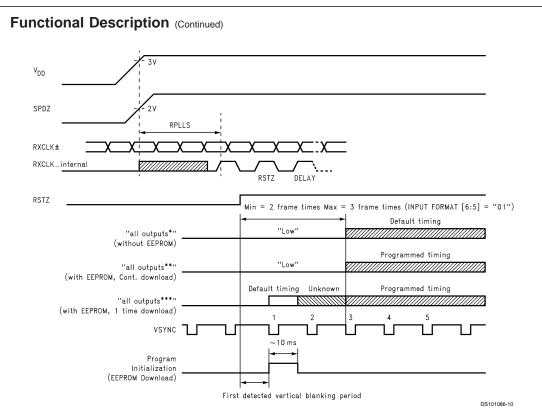

Note 21: RSTZ transition Low-to-High occurs at the completion of the RPLLS delay or later as shown above.

Note 22: All outputs\* forced low in default timing of FPD85310 during power-up delay time.

Note 23: All outputs\*\* forced low in continuous download (every two frame) mode.

Note 24: All outputs\*\*\* generate the signal for default values in FPD85310 and unknown values when use the EEPROM values during power-up delay time. Then NS recommend to use the continuous download mode.

Note 25: EEPROM download occurs at first detected vertical blanking period.

Note 26: Active outputs depends on INPUT FORMAT register bits [5:6].

| INPUT<br>FORMAT<br>[5:6] | VSYNC# at which outputs go active |

|--------------------------|-----------------------------------|

| 00                       | Second VSYNC                      |

| 01                       | Third VSYNC                       |

| 10                       | Fourth VSYNC                      |

| 11                       | Fifth VSYNC                       |

Note 27: When configured in ENAB Only Mode (EOM), VSYNC signals are unused except for timing EEPROM DownLoad Sequences. When configured with default values in Fixed Vertical mode, the VSYNC signal is generated any time ENAB remains low for more than 2 horizontal periods.

During Power Up, before Reset has propagated, the EEPROM may receive spurious addressing that initiates a down load sequence, but the output data is often not captured for lack of timing alignment with VSYNC. In the case where EEPROM data is not captured during the initial (automatic) Reset or Power Up DownLoad sequence, Timing Controller outputs are indeterminate until the EEPROM data is successfully loaded, which always begins and is executed at the next VSYNC valid (low) cycle.

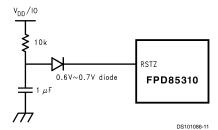

Note 28: During Power Up sequences, false RSTZ signals are possible due to instability of the power supply level, typically within the 10 ms of operation. To avoid this situation, implementation of the circuit in Figure 17, or other functional equivalent, is recommended, (Figure 17).

FIGURE 16. Power-up Sequence (INPUT FORMAT[6:5] = "01")

FIGURE 17. Delay Circuit for Stable RSTZ

### **FAILURE DETECTION**

TABLE 4. FPD85310 Failure Detection

| Mode                         | No<br>Clock | No<br>VSYNC | No<br>HSYNC | No<br>ENAB |

|------------------------------|-------------|-------------|-------------|------------|

| Fix Vertical/Horizontal      | (1)         | (2)         | (3)         | _          |

| Fix Vertical/ENAB Horizontal | (1)         | (2)         | _           | (4)        |

| ENAB Only Mode               | (1)         | _           | _           | (5)        |