# 2 Mb / 4 Mb Single Operating Voltage Serial Flash Memory With 104 MHz Dual or 100MHz Quad-Output SPI Bus Interface

#### **FEATURES**

- Single Power Supply Operation

- Low voltage range: 2.3 V 3.6 V

- Memory Organization

- IS25LQ020: 256K x 8 (2 Mbit)

- IS25LQ040: 512K x 8 (4 Mbit)

- Cost Effective Sector/Block Architecture

- 2Mb / 4Mb : Uniform 4KByte sectors / sixteen uniform 64KByte blocks

- Serial Peripheral Interface (SPI) Compatible

- Supports single-, dual- or quad-output

- Supports SPI Modes 0 and 3

- Maximum 33 MHz clock rate for normal read

- Maximum 104 MHz clock rate for fast read

- Maximum 208MHz clock rate equivalent Dual SPI

- Maximum 400MHz clock rate equivalent Quad SPI

- Byte Program Operation

- Typical 10 us/Byte

- Page Program (up to 256 Bytes) Operation

- Maximum 0.7ms per page program

- Sector, Block or Chip Erase Operation

- Sector Erase (4KB) → 150ms (Typ)

- Block Erase (64KB)→500ms (Typ)

- Chip Erase →0.5s (2Mb)

- Chip Erase → 1s (4Mb)

#### PRELIMINARY DATASHET

- Low Power Consumption

- Max 12 mA active read current

- Max 20 mA program/erase current

- Max 50 uA standby current

- Hardware Write Protection

- Protect and unprotect the device from write operation by Write Protect (WP#) Pin

- Software Write Protection

- The Block Protect (BP3, BP2, BP1, BP0) bits allow partial or entire memory to be configured as read-only

- High Product Endurance

- Guaranteed 100,000 program/erase cycles per single sector

- Minimum 20 years data retention

- Industrial Standard Pin-out and Package

- 8-pin SOIC 208mil

- 8-pin SOIC 150mil

- 8-pin VVSOP 150mil

- 8-pin WSON (5x6mm)

- 8-pin USON (2x3mm)

- KGD (Call Factory)

- Lead-free (Pb-free) package

- Automotive Temperature Ranges Available

- Additional 256-byte Security information onetime programmable (OTP) area

- Special protect function

- Safe guard function (Appendix 1)

- Sector unlock function (Appendix

#### **GENERAL DESCRIPTION**

The IS25LQ020/040 is 2 Mbit / 4 Mbit Serial Peripheral Interface (SPI) Flash memories, providing single-, dual or quad-output. The devices are designed to support a 33 MHz fclock rate in normal read mode, and 104 MHz in fast read (Quad output is 100MHz), the fastest in the industry. The devices use a single low voltage power supply, ranging from 2.3 Volt to 3.6 Volt, to perform read, erase and program operations. The devices can be programmed in standard EPROM programmers.

The IS25LQ020/040 are accessed through a 4-wire SPI Interface consisting of Serial Data Input/Output (SI), Serial Data Output (SO), Serial Clock (SCK), and Chip Enable (CE#) pins. The devices support page program mode, where 1 to 256 bytes data can be programmed into the memory in one program operation. These devices are divided into uniform 4 KByte sectors or uniform 64 KByte blocks.

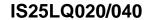

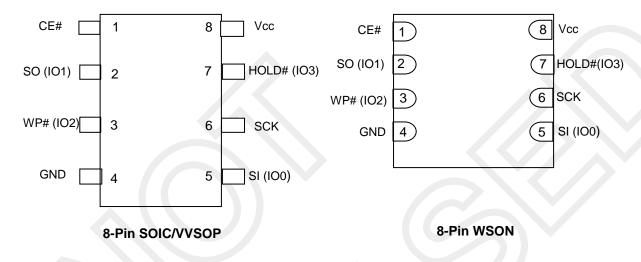

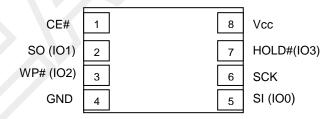

The IS25LQ020/040 are offered in 8-pin SOIC 208mil, 8-pin VVSOP, 8-pin WSON and 8-pin USON.

# **CONNECTION DIAGRAMS**

8-Pin USON

# **PIN DESCRIPTIONS**

| SYMBOL         | TYPE         | DESCRIPTION                                                                                                                            |

|----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|

| OF#            | INDUT        | Chin Fachla, CF# law astivates the devices internal circuitains for                                                                    |

| CE#            | INPUT        | Chip Enable: CE# low activates the devices internal circuitries for device operation. CE# high deselects the devices and switches into |

|                |              | standby mode to reduce the power consumption. When a device is not                                                                     |

|                |              | selected, data will not be accepted via the serial input pin (SI), and the                                                             |

|                |              | serial output pin (SO) will remain in a high impedance state.                                                                          |

| SCK            | INPUT        | Serial Data Clock                                                                                                                      |

| SI (IO0)       | INPUT/OUTPUT | Serial Data Input/Output                                                                                                               |

| SO (IO1)       | INPUT/OUTPUT | Serial Data Input/Output                                                                                                               |

| GND            |              | Ground                                                                                                                                 |

| Vcc            |              | Device Power Supply                                                                                                                    |

| WP#            | INPUT/OUTPUT | Write Protect/Serial Data Output: A hardware program/erase protection for all or                                                       |

| (IO2)          |              | part of a memory array. When the WP# pin is low, memory array write-protection                                                         |

|                |              | depends on the setting of BP3, BP2, BP1 and BP0 bits in the Status Register.                                                           |

|                |              | When the WP# is high, the status register are not write-protected.                                                                     |

|                |              | When the QE bit of is set "1", the /WP pin (Hardware Write Protect) function is                                                        |

| HOLD#          | INDUT/OUTDUT | not available since this pin is used for IO2                                                                                           |

| HOLD#<br>(IO3) | INPUT/OUTPUT | Hold: Pause serial communication by the master device without resetting the serial sequence.                                           |

| (103)          |              | When the QE bit of Status Register is set for "1", the function is Serial Data                                                         |

|                |              |                                                                                                                                        |

|                |              | Input & Output (for 4xI/O read mode)                                                                                                   |

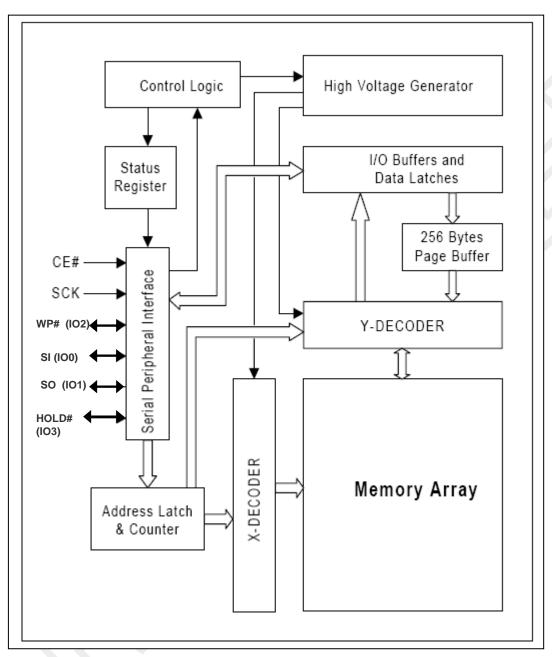

# **BLOCK DIAGRAM**

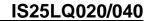

#### **SPI MODES DESCRIPTION**

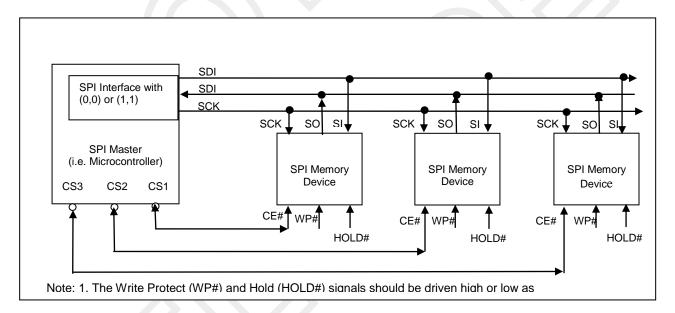

Multiple IS25LQ020/040 devices can be connected on the SPI serial bus and controlled by a SPI Master, i.e. microcontroller, as shown in Figure 1. The devices support either of two SPI modes:

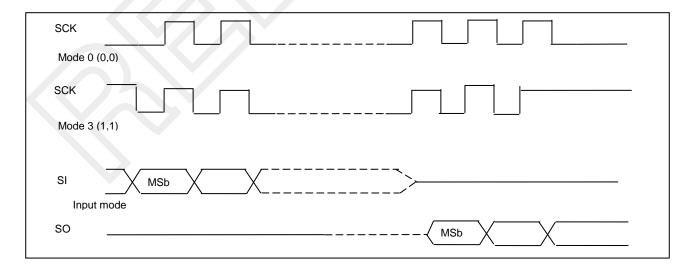

> Mode 0 (0, 0) Mode 3 (1, 1)

The difference between these two modes is the clock polarity when the SPI master is in Stand-by mode: the serial clock remains at "0" (SCK = 0) for Mode 0 and the clock remains at "1" (SCK = 1) for Mode 3. Please refer to Figure 2. For both modes, the input data is latched on the rising edge of Serial Clock (SCK), and the output data is available from the falling edge of SCK.

Figure 1. Connection Diagram among SPI Master and SPI Slaves (Memory Devices)

Figure 2. SPI Modes Supported

### **SYSTEM CONFIGURATION**

The IS25LQ020/040 devices are designed to interface directly with the synchronous Serial Peripheral Interface (SPI) of the Motorola MC68HCxx series of microcontrollers or any SPI interface-equipped system controllers. The devices have two superset features that can be enabled through specific software instructions and the Configuration Register:

1. Configurable sector size: The memory array of IS25LQ020/040 is divided into uniform 4 KByte sectors or uniform 64 KByte blocks (a block consists of sixteen adjacent sectors).

Table 1 illustrates the memory map of the devices.

Table 1. Block/Sector Addresses of IS25LQ020

| Memory Density | Block No.<br>(64Kbyte) | Sector No. | Sector<br>Size<br>(KBytes) | Address Range     |

|----------------|------------------------|------------|----------------------------|-------------------|

|                |                        | Sector 0   | 4                          | 000000h - 000FFFh |

|                | Block 0                | Sector 1   | 4                          | 001000h - 001FFFh |

|                | DIOCK U                | :          | :                          |                   |

|                |                        | Sector 15  | 4                          | 00F000h - 00FFFFh |

| 2Mbit          |                        | Sector 16  | 4                          | 010000h - 010FFFh |

|                | Diagrafia 4            | Sector 17  | 4                          | 011000h - 011FFFh |

|                | Block 1                | :          | :                          | :                 |

|                |                        | Sector 31  | 4                          | 01F000h - 01FFFFh |

|                |                        | :          | :                          | :                 |

|                | Block 3                | Sector 63  | 4                          | 03F000h - 03FFFFh |

Table 2. Block/Sector Addresses of IS25LQ040

| Memory Density | Block No.<br>(64Kbyte) | Sector No. | Sector<br>Size<br>(KBytes) | Address Range     |

|----------------|------------------------|------------|----------------------------|-------------------|

|                |                        | Sector 0   | 4                          | 000000h - 000FFFh |

|                | Block 0                | Sector 1   | 4                          | 001000h - 001FFFh |

|                | DIOCK U                | ••         | •                          | :                 |

|                |                        | Sector 15  | 4                          | 00F000h - 00FFFFh |

| 4Mbit          | Block 1                | Sector 16  | 4                          | 010000h - 010FFFh |

|                |                        | Sector 17  | 4                          | 011000h - 011FFFh |

|                |                        | :          | :                          | :                 |

|                |                        | Sector 31  | 4                          | 01F000h - 01FFFFh |

|                | :                      | :          | :                          | :                 |

|                | Block 7                | Sector 127 | 4                          | 070000h – 07FFFFh |

# REGISTERS (CONTINUED)

#### STATUS REGISTER

Refer to Tables 5 and 6 for Status Register Format and Status Register Bit Definitions.

The BP0, BP1, BP2, BP3 and SRWD are non-volatile memory cells that can be written by a Write Status Register (WRSR) instruction. The default value of the BP2, BP1, BP0, and SRWD bits were set to "0" at factory. The Status Register can be read by the Read Status Register (RDSR). Refer to Table 10 for Instruction Set.

The function of Status Register bits are described as follows:

WIP bit: The Write In Progress (WIP) bit is read-only, and can be used to detect the progress or completion of a program or erase operation. When the WIP bit is "0", the device is ready for a write status register, program or erase operation. When the WIP bit is "1", the device is busy.

WEL bit: The Write Enable Latch (WEL) bit indicates the status of the internal write enable latch. When the WEL is "0", the write enable latch is disabled, and all write operations, including write status register, write configuration register, page program, sector erase, block and chip erase operations are inhibited. When the WEL bit is "1", write operations are allowed. The WEL bit is set by a Write Enable (WREN) instruction. Each write register, program and erase instruction must be preceded by a WREN instruction. The WEL bit WARNING: The QE bit should never be set to a 1 can be reset by a Write Disable (WRDI) instruction. It will automatically be the reset after the completion of a write instruction.

BP3, BP2, BP1, BP0 bits: The Block Protection (BP3, BP2, BP1 and BP0) bits are used to define the portion of the memory area to be protected. Refer to Tables 7, 8 and 9 for the Block Write Protection bit settings. When a defined combination of BP3, BP2, BP1 and BP0 bits are set, the corresponding memory area is protected. Any program or erase operation to that area will be inhibited. Note: a Chip Erase (CHIP\_ER) instruction is executed only if all the Block Protection Bits are set as "0"s.

**SRWD bit**: The Status Register Write Disable (SRWD) bits operates in conjunction with the Write Protection (WP#) signal to provide a Hardware Protection Mode. When the SRWD is set to "0", the Status Register is not write-protected. When the SRWD is set to "1" and the WP# is pulled low (VIL), the bits of Status Register (SRWD, BP3, BP2, BP1, BP0) become read-only, and a WRSR instruction will be ignored. If the SRWD is set to "1" and WP# is pulled high (V<sub>IH</sub>), the Status Register can be changed by a WRSR instruction.

QE bit: The Quad Enable (QE) is a non-volatile bit in the status register that allows Quad operation. When the QE bit is set to "0".the pin WP# and HOLD# are enable. When the QE bit is set to "1", the pin IO2 and IO3 are enable.

during standard SPI or Dual SPI operation if the WP# or HOLD# pins are tied directly to the power supply or ground.

**Table 5. Status Register Format**

|                     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|

|                     | SRWD  | QE    | BP3   | BP2   | BP1   | BP0   | WEL   | WIP   |

| Default (flash bit) | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

<sup>\*</sup> The default value of the BP3, BP2, BP1, BP0, and SRWD bits were set to "0" at factory.

# REGISTERS (CONTINUED) Table 6. Status Register Bit Definition

| Bit   | Name | Definition                                                                                                                                                                        | Read-<br>/Write | Non-Volatile bit |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|

| Bit 0 | WIP  | Write In Progress Bit: "0" indicates the device is ready "1" indicates a write cycle is in progress and the device is busy                                                        | R               | No               |

| Bit 1 | WEL  | Write Enable Latch: "0" indicates the device is not write enabled (default) "1" indicates the device is write enabled                                                             | R/W             | No               |

| Bit 2 | BP0  | Disale Protection Dity (Con Tables 7, 0 and 0 for datails)                                                                                                                        |                 |                  |

| Bit 3 | BP1  | Block Protection Bit: (See Tables 7, 8 and 9 for details) "0" indicates the specific blocks are not write-protected (default)                                                     | R/W             | Yes              |

| Bit 4 | BP2  | "1" indicates the specific blocks are not write-protected (default)                                                                                                               | FC/VV           | 162              |

| Bit 5 | BP3  | i indicates the specific blocks are write-protected                                                                                                                               |                 |                  |

| Bit 6 | QE   | Quad Enable bit: "0" indicates the Quad output function disable (default) "1" indicates the Quad output function enable                                                           | R/W             | Yes              |

| Bit 7 | SRWD | Status Register Write Disable: (See Table 10 for details) "0" indicates the Status Register is not write-protected (default) "1" indicates the Status Register is write-protected | R/W             | Yes              |

Table 9. Block Write Protect Bits for IS25LQ020/040

| Status Register Bits |     |     |     | Protected M                     | emory Area                    |

|----------------------|-----|-----|-----|---------------------------------|-------------------------------|

| BP3                  | BP2 | BP1 | BP0 | 2 Mbit                          | 4 Mbit                        |

| 0                    | 0   | 0   | 0   | None                            | None                          |

| 0                    | 0   | 0   | 1   | (1 block : 7th)                 | (1 block : 7th):              |

| 0                    | 0   | 1   | 0   | (2 blocks :6th to 7th)          | (2 blocks :6th to 7th)        |

| 0                    | 0   | 1   | 1   |                                 | (4 blocks :4th to 7th)        |

| 0                    | 1   | 0   | 0   |                                 |                               |

| 0                    | 1   | 0   | 1   |                                 |                               |

| 0                    | 1   | 1   | 0   |                                 |                               |

| 0                    | 1   | 1   | 1   | All blocks ( 2 blocks : 0 to 2) | All blocks (Oblocks + O to 7) |

| 1                    | 0   | 0   | 0   | All blocks (3 blocks: 0 to 3)   | All blocks (8blocks : 0 to 7) |

| 1                    | 0   | 0   | 1   |                                 |                               |

| 1                    | 0   | 1   | 0   |                                 |                               |

| 1                    | 0   | 1   | 1   |                                 |                               |

| 1                    | 1   | 0   | 0   |                                 | (4 blocks :0th to 3th)        |

| 1                    | 1   | 0   | 1   | (2 blocks :0th to 1th)          | (2 blocks :0th to 1th):       |

| 1                    | 1   | 1   | 0   | (1 blocks :0th)                 | (1 blocks :0th)               |

| 1                    | 1   | 1   | 1   | None                            | None                          |

# REGISTERS (CONTINUED)

#### **PROTECTION MODE**

The IS25LQ020/040 have two types of write-protection mechanisms: hardware and software. These are used to prevent irrelevant operation in a possibly noisy environment and protect the data integrity.

#### HARDWARE WRITE-PROTECTION

The devices provide two hardware write-protection features:

- a. When inputting a program, erase or write status register instruction, the number of clock pulse is checked to determine whether it is a multiple of eight before the executing. Any incomplete instruction command sequence will be ignored.

- b. Write inhibit is 2.0V, all write sequence will be ignored when Vcc drop to 2.0V and lower.

- c. The Write Protection (WP#) pin provides a hardware write protection method for BP3, BP2, BP1, BP0 and SRWD in the Status Register. Refer to the STATUS REGISTER description.

The IS25LQ020/040 also provides two software write protection features:

- a. Before the execution of any program, erase or write status register instruction, the Write Enable Latch (WEL) bit must be enabled by executing a Write Enable (WREN) instruction. If the WEL bit is not enabled first, the program, erase or write register instruction will be ignored.

- b. The Block Protection (BP3, BP2, BP1, BP0) bits allow part or the whole memory area to be write-protected.

Table 10. Hardware Write Protection on Status Register

|   | SRWD | RWD WP# Status Register |           |

|---|------|-------------------------|-----------|

|   | 0    | Low                     | Writable  |

|   | 1    | Low                     | Protected |

|   | 0    | High                    | Writable  |

| \ | 1    | High                    | Writable  |

#### SOFTWARE WRITE PROTECTION

#### **DEVICE OPERATION**

The IS25LQ020/040 utilize an 8-bit instruction register. Refer to Table 11 Instruction Set for details of the Instructions and Instruction Codes. All instructions, addresses, and data are shifted in with the most significant bit (MSB) first on Serial Data Input (SI). The input data on SI is latched on the rising edge of Serial Clock (SCK) after Chip Enable (CE#) is driven low ( $V_{IL}$ ). Every instruction sequence starts with a one-byte

instruction code and is followed by address bytes, data bytes, or both address bytes and data bytes, depending on the type of instruction. CE# must be driven high  $(V_{IH})$  after the last bit of the instruction sequence has been shifted in.

The timing for each instruction is illustrated in the following operational descriptions.

**Table 11. Instruction Set**

| Instruction Name        | Hex<br>Code | Operation                                               | Comman d Cycle    | Maximum<br>Frequency |

|-------------------------|-------------|---------------------------------------------------------|-------------------|----------------------|

| RDID                    | ABh         | Read Manufacturer and Product ID                        | 4 Bytes           | 104 MHz              |

| JEDEC ID READ           | 9Fh         | Read Manufacturer and Product ID by JEDEC ID Command    | 1 Byte            | 104 MHz              |

| RDMDID                  | 90h         | Read Manufacturer and Device ID                         | 4 Bytes           | 104 MHz              |

| WREN                    | 06h         | Write Enable                                            | 1 Byte            | 104 MHz              |

| WRDI                    | 04h         | Write Disable                                           | 1 Byte            | 104 MHz              |

| RDSR                    | 05h         | Read Status Register                                    | 1 Byte            | 104 MHz              |

| WRSR                    | 01h         | Write Status Register                                   | 2 Bytes           | 104 MHz              |

| READ                    | 03h         | Read Data Bytes from Memory at Normal Read Mode         | 4 Bytes           | 33 MHz               |

| FAST_READ               | 0Bh         | Read Data Bytes from Memory at Fast Read Mode           | 5 Bytes           | 104 MHz              |

| FRDO                    | 3Bh         | Fast Read Dual Output                                   | 5 Bytes           | 104 MHz              |

| FRDIO                   | BBh         | Fast Read Dual I/O                                      | 3 Bytes           | 104MHz               |

| FRQO                    | 6Bh         | Fast Read Quad Output                                   | 5 Bytes           | 100 MHz              |

| FRQIO                   | EBh         | Fast Read Quad I/O                                      | 2 Bytes           | 100MHz               |

| MR                      | FFh         | Mode Reset                                              | 2 Byte            | 104MHz               |

| PAGE_ PROG              | 02h         | Page Program Data Bytes Into Memory                     | 4 Bytes<br>+ 256B | 104 MHz              |

| SECTOR_ER               | D7h/<br>20h | Sector Erase                                            | 4 Bytes           | 104 MHz              |

| BLOCK_ER (64KB)         | D8h         | Block Erase 64K byte                                    | 4 Bytes           | 104 MHz              |

| CHIP_ER                 | C7h/<br>60h | Chip Erase                                              | 1 Byte            | 104 MHz              |

| Quad page program       | 32h         | Page Program Data Bytes Into Memory with Quad interface | 4 Bytes<br>+ 256B |                      |

| Program/Erase suspend   | 75h         | Suspend during the program/erase                        |                   | 104MHz               |

| Program/Erase resume    | 7Ah         | Resume program/erase                                    |                   | 104MHz               |

| Program information Raw | B1h         | Program 256 bytes of Security area                      | 4 Bytes           | 104 MHz              |

| Read information<br>Raw | 4Bh         | Read 256 bytes of Security area                         | 4 Bytes           | 33 MHz               |

#### **HOLD OPERATION**

HOLD# is used in conjunction with CE# to select the IS25LQ020/040. When the devices are selected and a serial sequence is underway, HOLD# can be used to pause the serial communication with the master device without resetting the serial sequence. To pause, HOLD# is brought low while the SCK signal is low. To resume serial communication, HOLD# is brought high while the SCK signal is low (SCK may still toggle during HOLD). Inputs to SI will be ignored while SO is in the high impedance state.

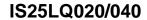

# RDID COMMAND (READ PRODUCT IDENTIFICATION)/ Release Power-down OPERATION

The Release from Power-down or High performance Mode / Device ID instruction is a multi-purpose instruction. The Read Product Identification (RDID) instruction is for reading out the old style of 8-bit Electronic Signature, whose values are shown as table of ID Definitions. This is not same as RDID or JEDEC ID instruction. It's not recommended to use for new design. For new design, please use RDID or JEDEC ID instruction.

The RDES instruction code is followed by three dummy bytes, each bit being latched-in on SI during the rising edge of SCK. Then the Device ID is shifted out on SO with the MSB first, each bit been shifted out during the falling edge of SCK. The RDES instruction is ended by CE# goes high. The Device ID outputs repeatedly if continuously send the additional clock cycles on SCK while CE# is at low.

To release the device from the power-down state Mode, the instruction is issued by driving the CE# pin low,

shifting the instruction code "ABh" and driving CE# high as shown in figure 3.

Release from power-down will take the time duration of tRES1 before the device will resume normal operation and other instructions are accepted. The CE# pin must remain high during the tRES1 time duration. If the Release from Power-down / RDID instruction is issued while an Erase, Program or Write cycle is in process (when BUSY equals 1) the instruction is ignored and will not have any effects on the current cycle

**Table 12. Product Identification**

| Product Identifica | Data        |            |

|--------------------|-------------|------------|

| Manufacturer ID    | First Byte  |            |

| Wanulacturer ID    | Second Byte | 7Fh        |

| Device ID:         | Device ID1  | Device ID2 |

| IS25LQ020          | 11h         | 42h        |

| IS25LQ040          | 12h         | 43h        |

Figure 3. Read Product Identification Sequence

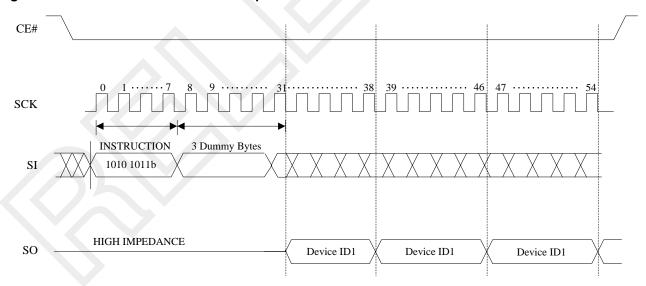

# JEDEC ID READ COMMAND (READ PRODUCT IDENTIFICATION BY JEDEC ID) OPERATION

The JEDEC ID READ instruction allows the user to read the manufacturer and product ID of devices. Refer to Table 10 Product Identification for pFlash Manufacturer ID and Device ID. After the JEDEC ID READ command is input, the Manufacturer ID1 is shifted out on SO with the MSB first, followed by the

first Device ID1and the Device ID2, in the case of the, each bit shifted out during the falling edge of SCK. If CE# stays low after the last bit of the Device ID is shifted out, the Manufacturer ID and Device ID will loop until CE# is pulled high.

Figure 4. Read Product Identification by JEDEC ID READ Sequence

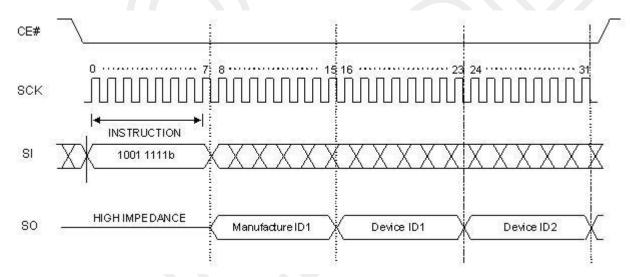

# RDMDID COMMAND (READ DEVICE MANUFACTURER AND DEVICE ID) OPERATION

The Read Product Identification (RDID) instruction allows the user to read the manufacturer and product ID of the devices. Refer to Table 12 Product Identification for pFLASH™ manufacturer ID and device ID. The RDID instruction code is followed by two dummy bytes and one byte address (A7~A0), each bit being latched-in on SI during the rising edge of SCK. If one byte address is initially set to A0 = 0, then the first manufacturer ID (9Dh) is shifted out on SO with

the MSB first, the device ID1 and the second manufacturer ID (7Fh), each bit been shifted out during the falling edge of SCK. If one byte address is initially set to A0 = 1, then device ID1 will be read first, then followed by the first manufacture ID (9Dh) and then second manufacture ID (7Fh). The manufacture and device ID can be read continuously, alternating from one to the others. The instruction is completed by driving CE# high.

Figure 5. Read Product Identification by RDMDID READ Sequence

#### Note:

(1) ADDRESS A0 = 0, will output the 1st manufacture ID (9Dh) first -> device ID1 -> 2nd manufacture ID (7Fh) ADDRESS A0 = 1, will output the device ID1 -> 1st manufacture ID (9D) -> 2nd manufacture ID (7Fh)

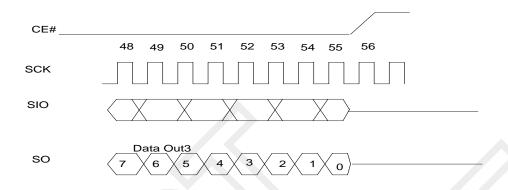

#### WRITE ENABLE OPERATION

The Write Enable (WREN) instruction is used to set the Write Enable Latch (WEL) bit. The WEL bit of the IS25LQ016 is reset to the write –protected state after power-up. The WEL bit must be write enabled before any write operation, including sector, block erase, chip

erase, page program, write status register, and write configuration register operations. The WEL bit will be reset to the write-protect state automatically upon completion of a write operation. The WREN instruction is required before any above operation is executed.

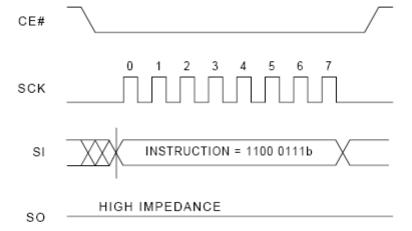

Figure 6. Write Enable Sequence

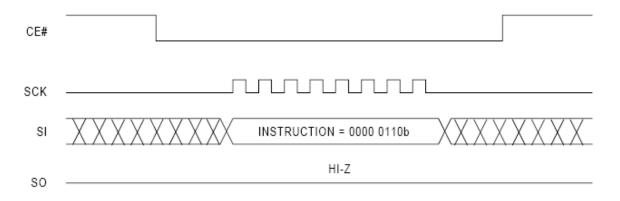

#### WRDI COMMAND (WRITE DISABLE) OPERATION

The Write Disable (WRDI) instruction resets the WEL bit and disables all write instructions. The WRDI

instruction is not required after the execution of a write instruction, since the WEL bit is automatically reset.

Figure 7. Write Disable Sequence

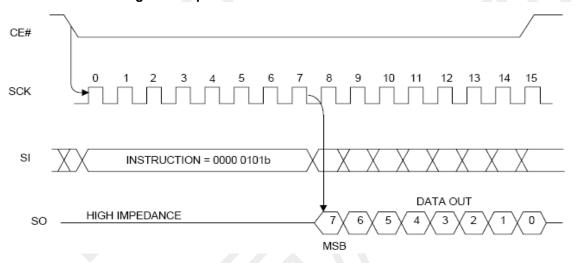

#### RDSR COMMAND (READ STATUS REGISTER) OPERATION

The Read Status Register (RDSR) instruction provides access to the Status Register. During the execution of a program, erase or write status register operation, all other instructions will be ignored except the RDSR

instruction, which can be used to check the progress or completion of an operation by reading the WIP bit of Status Register.

Figure 8. Read Status Register Sequence

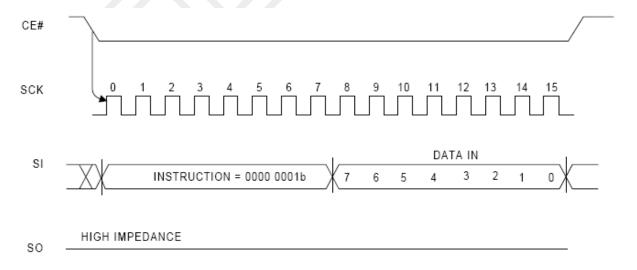

#### WRSR COMMAND (WRITE STATUS REGISTER) OPERATION

The Write Status Register (WRSR) instruction allows the user to enable or disable the block protection and status register write protection features by writing "0"s or "1"s into the non-volatile BP3, BP2, BP1, BP0 and SRWD bits.

Figure 9. Write Status Register Sequence

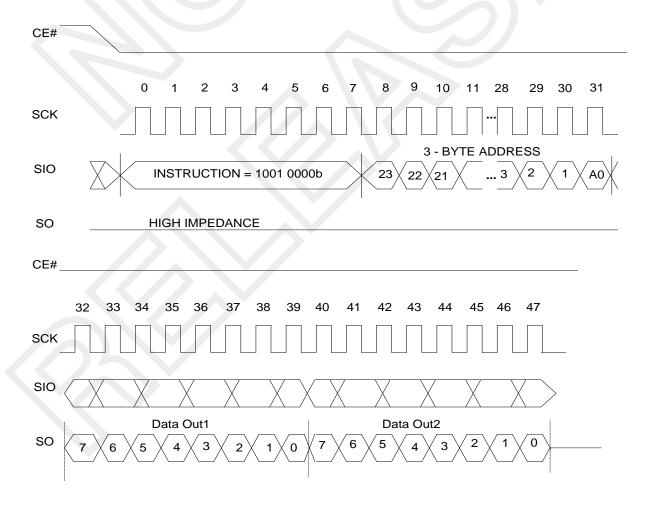

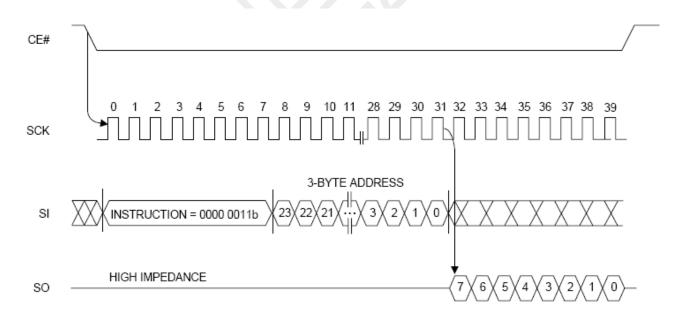

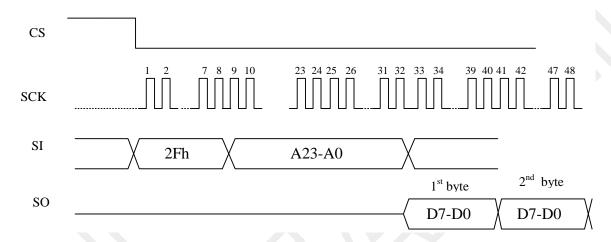

#### **READ COMMAND (READ DATA) OPERATION**

The Read Data (READ) instruction is used to read memory data of a IS25LQ020/040under normal mode running up to 33 MHz.

The READ instruction code is transmitted via the SI line, followed by three address bytes (A23 - A0) of the first memory location to be read. A total of 24 address bits are shifted in, but only  $A_{\rm MS}$  (most significant address) - A0 are decoded. The remaining bits (A23 –  $A_{\rm MS}$ ) are ignored. The first byte addressed can be at any memory location. Upon completion, any data on the SI will be ignored. Refer to Table 13 for the related Address Key.

The first byte data (D7 - D0) addressed is then shifted

out on the SO line, MSb first. A single byte of data, or up to the whole memory array, can be read out in one READ instruction. The address is automatically incremented after each byte of data is shifted out. The read operation can be terminated at any time by driving CE# high (VIH) after the data comes out. When the highest address of the devices is reached, the address counter will roll over to the 000000h address, allowing the entire memory to be read in one continuous READ instruction.

If a Read Data instruction is issued while an Erase, Program or Write cycle is in process (BUSY=1) the instruction is ignored and will not have any effects on the current cycle

Table 13. Address Key

| Address             | IS25LQ020/040 |

|---------------------|---------------|

| $A_N(A_{MS}-A_{0)}$ | A19 - A0      |

| Don't Care Bits     | A23 – A20     |

Figure 12. Read Data Sequence

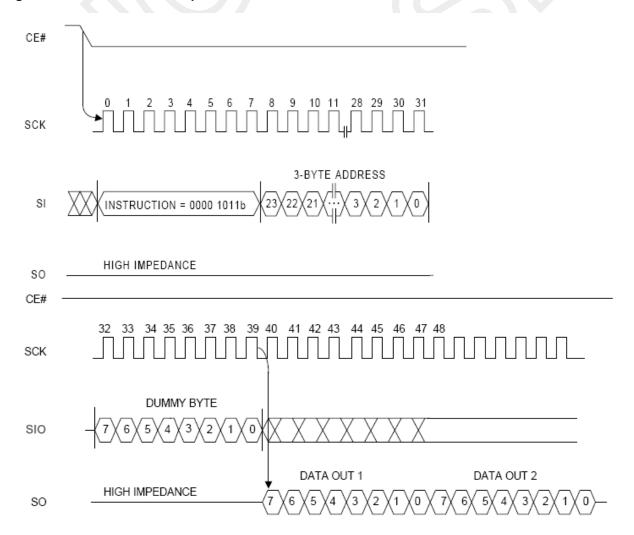

#### FAST READ COMMAND (FAST READ DATA) OPERATION

The FAST\_READ instruction is used to read memory data at up to a 104 MHz clock.

The FAST\_READ instruction code is followed by three address bytes (A23 - A0) and a dummy byte (8 clocks), transmitted via the SI line, with each bit latched-in during the rising edge of SCK. Then the first data byte addressed is shifted out on the SO line, with each bit shifted out at a maximum frequency  $f_{\text{CT}},$  during the falling edge of SCK.

The first byte addressed can be at any memory location. The address is automatically incremented after each byte of data is shifted out. When the highest address is reached, the address counter will roll over to the 000000h address, allowing the entire memory to be read with a single FAST\_READ instruction. The FAST\_READ instruction is terminated by driving CE# high (VIH). If a Fast Read Data instruction is issued while an Erase, Program or Write cycle is in process (BUSY=1) the instruction is ignored and will not have any effects on the current cycle

Figure 13. Fast Read Data Sequence

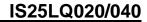

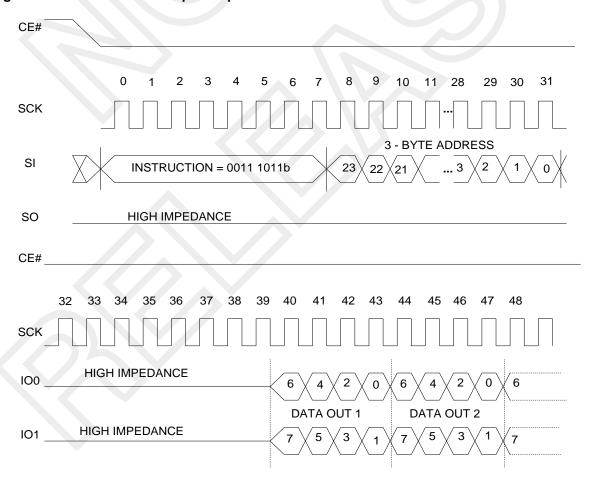

#### FRDO COMMAND (FAST READ DUAL OUTPUT) OPERATION

The FRDO instruction is used to read memory data on two output pins each at up to a 104 MHz clock.

The FRDO instruction code is followed by three address bytes (A23 – A0) and a dummy byte (8 clocks), transmitted via the SI line, with each bit latched-in during the rising edge of SCK. Then the first data byte addressed is shifted out on the SO and SIO lines, with each pair of bits shifted out at a maximum frequency  $f_{CT}$ , during the falling edge of SCK. The first bit (MSb) is output on SO, while simultaneously the second bit is output on SIO.

The first byte addressed can be at any memory location. The address is automatically incremented after each byte of data is shifted out. When the highest address is reached, the address counter will roll over to the 00000h address, allowing the entire memory to be read with a single FRDO instruction. FRDO instruction is terminated by driving CE# high (VIH). If a FRDO instruction is issued while an Erase, Program or Write cycle is in process (BUSY=1) the instruction is ignored and will not have any effects on the current cycle

Figure 14. Fast Read Dual-Output Sequence

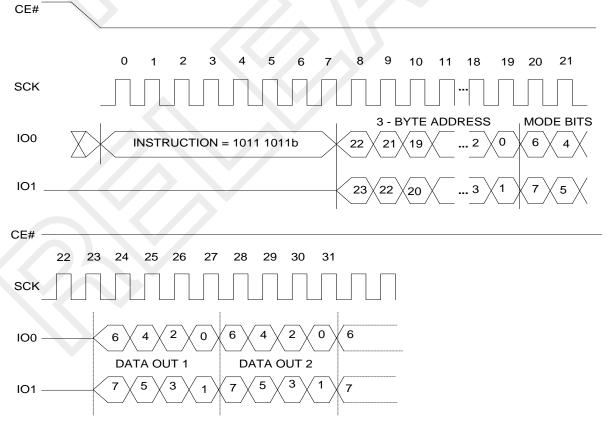

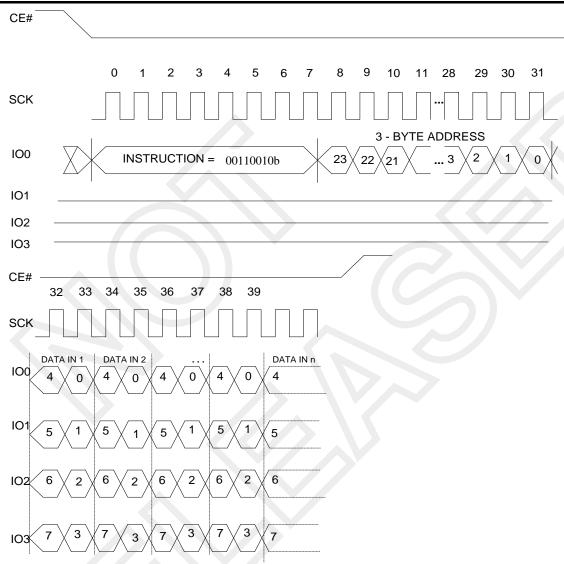

#### FRDIO COMMAND (FAST READ DUAL I/O) OPERATION

The FRDIO instruction is similar to the FRDO instruction, but allows the address bits to be input two bits at a time. This may allow for code to be executed directly from the SPI in some applications.

The FRDIO instruction code is followed by three address bytes (A23 – A0) and a mode byte, transmitted via the IO0 and IO1 lines, with each pair of bits latched-in during the rising edge of SCK. The address MSb is input on IO1, the next bit on IO0, and continues to shift in alternating on the two lines. The mode byte contains the value Ax, where x is a "don't care" value. Then the first data byte addressed is shifted out on the IO1 and IO0 lines, with each pair of bits shifted out at a maximum frequency fcT, during the falling edge of SCK. The MSb is output on IO1, while simultaneously the second bit is output on IO0. Figure 15 illustrates the timing sequence.

The first byte addressed can be at any memory location. The address is automatically incremented after each byte of data is shifted out. When the highest address is reached, the address counter will roll over to the 000000h address, allowing the entire memory to be read with a single FRDIO instruction. FRDIO instruction is terminated by driving CE# high (VIH).

The device expects the next operation will be another FRDIO. It remains in this mode until it receives a Mode Reset (FFh) command. In subsequent FRDIO execution, the command code is not input, saving timing cycles as described in Figure 16. If a FRDIO instruction is issued while an Erase, Program or Write cycle is in process (BUSY=1) the instruction is ignored and will not have any effects on the current cycle

Figure 15. Fast Read Dual I/O Sequence (with command decode cycles)

Figure 16. Fast Read Dual I/O Sequence (without command decode cycles)

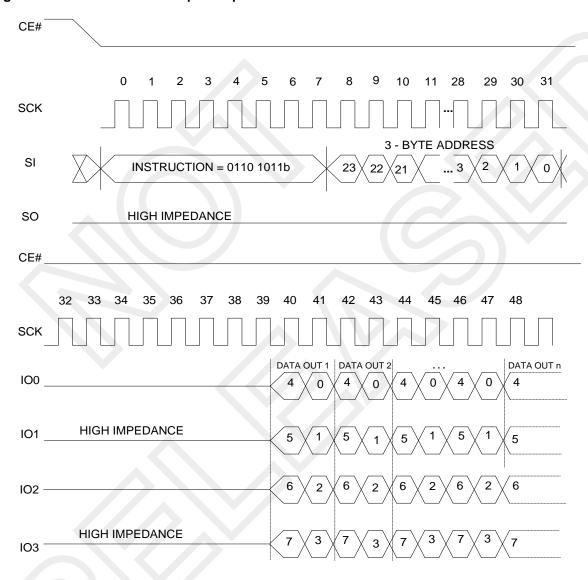

#### FRQO COMMAND (FAST READ QUAD OUTPUT) OPERATION

The FRQO instruction is used to read memory data on four output pins each at up to a 100 MHz clock.

The FRQO instruction code is followed by three address bytes (A23 – A0) and a dummy byte (8 clocks), transmitted via the SI line, with each bit latched-in during the rising edge of SCK. Then the first data byte addressed is shifted out on the IO3, IO2, IO1 and IO0 lines, with each group of four bits shifted out at a maximum frequency  $f_{\text{CT}}$ , during the falling edge of SCK. The first bit (MSb) is output on IO3, while

simultaneously the second bit is output on IO2, the third bit is output on IO1, etc.

The first byte addressed can be at any memory location. The address is automatically incremented after each byte of data is shifted out. When the highest address is reached, the address counter will roll over to the 00000h address, allowing the entire memory to be read with a single FRQO instruction. FRQO instruction is terminated by driving CE# high (VIH). If a FRQO instruction is issued while an Erase, Program or Write cycle is in process (BUSY=1) the instruction is ignored and will not have any effects on the current cycle

Figure 17. Fast Read Quad-Output Sequence

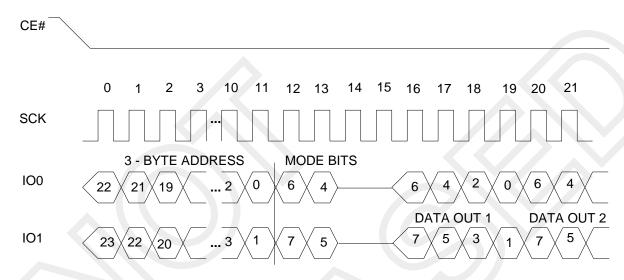

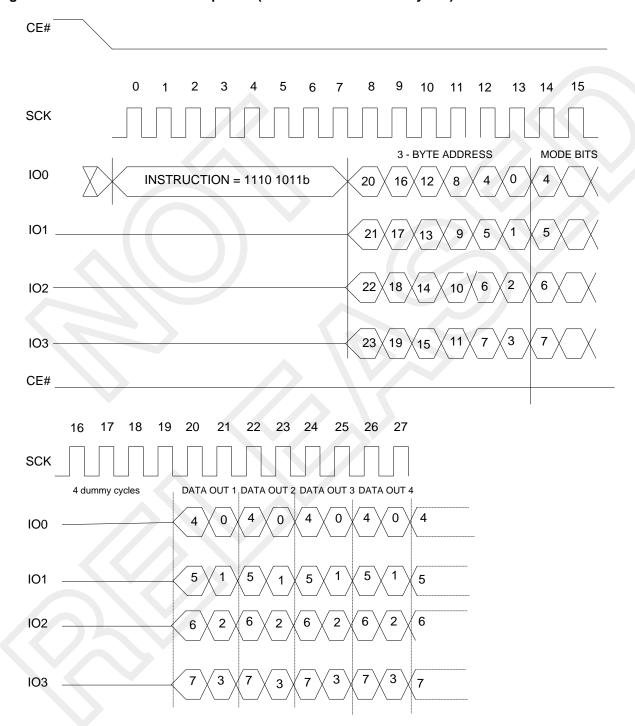

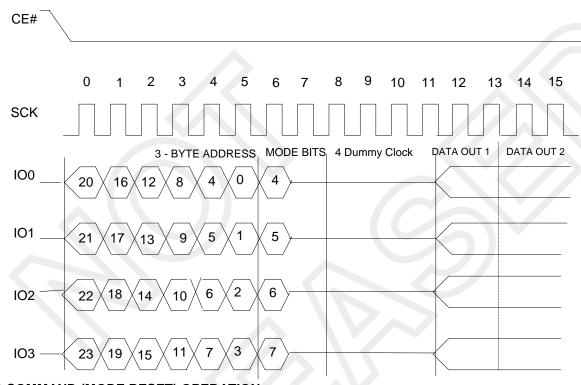

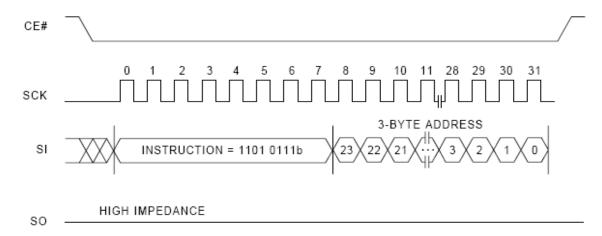

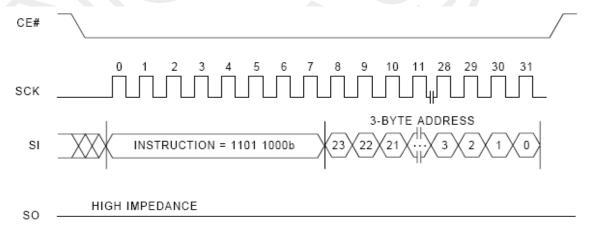

#### FRQIO COMMAND (FAST READ QUAD I/O) OPERATION

The FRQIO instruction is similar to the FRQO instruction, but allows the address bits to be input four bits at a time. This may allow for code to be executed directly from the SPI in some applications.

The FRQIO instruction code is followed by three address bytes (A23 – A0) and a mode byte, transmitted via the IO3, IO2, IO0 and IO1 lines, with each group of four bits latched-in during the rising edge of SCK. The address MSb is input on IO3, the next bit on IO2, the next bit on IO1, the next bit on IO0, and continue to shift in alternating on the four. The mode byte contains the value Ax, where x is a "don't care" value. After four dummy clocks, the first data byte addressed is shifted out on the IO3, IO2, IO1 and IO0 lines, with each group of four bits shifted out at a maximum frequency  $f_{\text{CT}}$ , during the falling edge of SCK. The first bit (MSb) is output on IO3, while simultaneously the second bit is output on IO2, the

third bit is output on IO1, etc. Figure 18 illustrates the timing sequence.

The first byte addressed can be at any memory location. The address is automatically incremented after each byte of data is shifted out. When the highest address is reached, the address counter will roll over to the 000000h address, allowing the entire memory to be read with a single FRQIO instruction. FRQIO instruction is terminated by driving CE# high (VIH).

The device expects the next operation will be another FRQIO. It remains in this mode until it receives a Mode Reset (FFh) command. In subsequent FRDIO execution, the command code is not input, saving cycles as described in Figure 19. If a FRQIO instruction is issued while an Erase, Program or Write cycle is in process (BUSY=1) the instruction is ignored and will not have any effects on the current cycle

Figure 18. Fast Read Quad I/O Sequence (with command decode cycles)

Figure 19. Fast Read Quad I/O Sequence (without command decode cycles)

### MR COMMAND (MODE RESET) OPERATION

The Mode Reset command is used to conclude subsequent FRDIO and FRQIO operations. It resets the Mode bits to a value that is not Ax. It should be executed after an FRDIO or FRQIO operation, and is recommended also as the first

command after a system reset. The timing sequence is different depending whether the MR command is used after an FRDIO or FRQIO, as shown in Figure 20.

Figure 20, Mode Reset Command

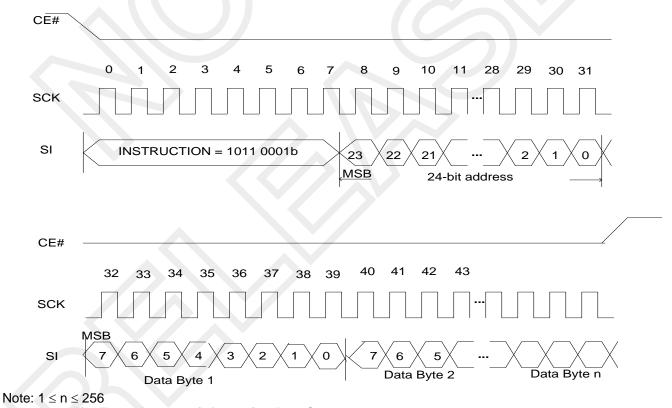

#### PAGE\_PROG COMMAND (PAGE PROGRAM) OPERATION

The Page Program (PAGE\_PROG) instruction allows up to 256 bytes data to be programmed into memory in a single operation. The destination of the memory to be programmed must be outside the protected memory area set by the Block Protection (BP2, BP1, BP0) bits. A PAGE\_PROG instruction which attempts to program into a page that is write-protected will be ignored. Before the execution of PAGE\_PROG instruction, the Write Enable Latch (WEL) must be enabled through a Write Enable (WREN) instruction.

The PAGE\_PROG instruction code, three address bytes and program data (1 to 256 bytes) are input via the SI line. Program operation will start immediately after the CE# is brought high, otherwise the PAGE\_PROG instruction will not be executed. The internal control logic automatically handles the programming voltages and timing. During a program operation, all instructions will be ignored except the RDSR instruction. The progress or completion of the program operation can be determined by reading the

WIP bit in Status Register via a RDSR instruction. If the WIP bit is "1", the program operation is still in progress. If WIP bit is "0", the program operation has completed.

If more than 256 bytes data are sent to a device, the address counter rolls over within the same page, the previously latched data are discarded, and the last 256 bytes data are kept to be programmed into the page. The starting byte can be anywhere within the page. When the end of the page is reached, the address will wrap around to the beginning of the same page. If the data to be programmed are less than a full page, the data of all other bytes on the same page will remain unchanged.

Note: A program operation can alter "1"s into "0"s, but an erase operation is required to change "0"s back to "1"s. A byte cannot be reprogrammed without first erasing the whole sector or block.

Figure 21. Page Program Sequence

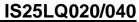

#### **Quad Input Page Program operation**

The Quad Input Page Program instruction allows up to 256 bytes data to be programmed into memory in a single operation with four pins (IO0, IO1, IO2 and IO3). The destination of the memory to be programmed must be outside the protected memory area set by the Block Protection (BP3, BP2, BP1, BP0) bits. A Quad Input Page Program instruction which attempts to program into a page that is write-protected will be ignored. Before the execution of Quad Input Page Program instruction, the QE bit in the status register must be set to "1" and the Write Enable Latch (WEL) must be enabled through a Write Enable (WREN) instruction.

The Quad Input Page Program instruction code, three address bytes and program data (1 to 256 bytes) are input via the four pins (IO0, IO1, IO2 and IO3). Program operation will start immediately after the CE# is brought high, otherwise the Quad Input Page Program instruction will not be executed. The internal control logic automatically handles the programming voltages and timing. During a program operation, all instructions will be ignored except the

RDSR instruction. The progress or completion of the program operation can be determined by reading the WIP bit in Status Register via a RDSR instruction. If the WIP bit is "1", the program operation is still in progress. If WIP bit is "0", the program operation has completed.

If more than 256 bytes data are sent to a device, the address counter rolls over within the same page, the previously latched data are discarded, and the last 256 bytes data are kept to be programmed into the page. The starting byte can be anywhere within the page. When the end of the page is reached, the address will wrap around to the beginning of the same page. If the data to be programmed are less than a full page, the data of all other bytes on the same page will remain unchanged.

Note: A program operation can alter "1"s into "0"s, but an erase operation is required to change "0"s back to "1"s. A byte cannot be reprogrammed without first erasing the whole sector or block.

#### **ERASE OPERATION**

The memory array of the IS25LQ020/040 is organized into uniform 4 Kbyte sectors or 64 Kbyte uniform blocks (a block consists of sixteen adjacent sectors).

Before a byte can be reprogrammed, the sector or block that contains the byte must be erased (erasing sets bits to "1"). In order to erase the devices, there are three erase instructions available: Sector Erase (SECTOR\_ER), Block Erase (BLOCK\_ER) and Chip Erase (CHIP\_ER). A sector erase operation allows any individual sector to be erased without affecting the data in other sectors. A block erase operation erases any individual block. A chip erase operation erases the whole memory array of a device. A sector erase, block erase or chip erase operation can be executed prior to any programming operation.

# SECTOR\_ER COMMAND (SECTOR ERASE) OPERATION

A SECTOR\_ER instruction erases a 4 Kbyte sector Before the execution of a SECTOR\_ER instruction, the Write Enable Latch (WEL) must be set via a Write Enable (WREN) instruction. The WEL bit is reset automatically after the completion of sector an erase operation.

A SECTOR\_ER instruction is entered, after CE# is pulled low to select the device and stays low during the entire instruction sequence The SECTOR\_ER instruction code, and three address bytes are input via SI. Erase operation will start immediately after CE# is pulled high. The internal control logic automatically handles the erase voltage and timing. Refer to Figure 22 for Sector Erase Sequence.

During an erase operation, all instruction will be ignored except the Read Status Register (RDSR) instruction. The progress or completion of the erase

operation can be determined by reading the WIP bit in the Status Register using a RDSR instruction. If the WIP bit is "1", the erase operation is still in progress. If the WIP bit is "0", the erase operation has been completed.

# BLOCK\_ER COMMAND (BLOCK ERASE) OPERATION

A Block Erase (BLOCK\_ER) instruction erases a 64 Kbyte block of the IS25LQ016. Before the execution of a BLOCK\_ER instruction, the Write Enable Latch (WEL) must be set via a Write Enable (WREN) instruction. The WEL is reset automatically after the completion of a block erase operation.

The BLOCK\_ER instruction code and three address bytes are input via SI. Erase operation will start immediately after the CE# is pulled high, otherwise the BLOCK\_ER instruction will not be executed. The internal control logic automatically handles the erase voltage and timing. Refer to Figure 23 for Block Erase Sequence.

#### CHIP ER COMMAND (CHIP ERASE) OPERATION

A Chip Erase (CHIP\_ER) instruction erases the entire memory array of a IS25LQ016. Before the execution of CHIP\_ER instruction, the Write Enable Latch (WEL) must be set via a Write Enable (WREN) instruction. The WEL is reset automatically after completion of a chip erase operation.

The CHIP\_ER instruction code is input via the SI. Erase operation will start immediately after CE# is pulled high, otherwise the CHIP\_ER instruction will not be executed. The internal control logic automatically handles the erase voltage and timing. Refer to Figure 24 for Chip Erase Sequence.

Figure 22. Sector Erase Sequence

Figure 23. Block Erase Sequence

Figure 24. Chip Erase Sequence

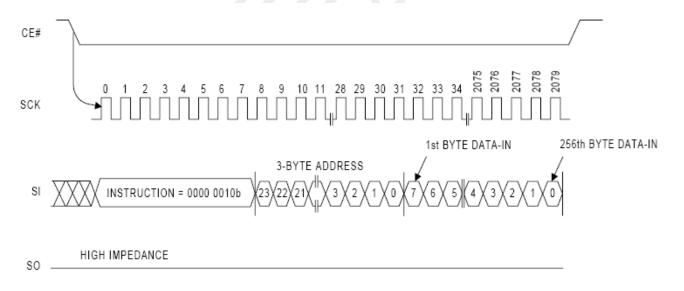

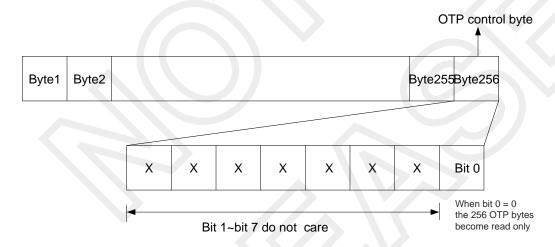

#### **Program Security Information Row Instruction (PSIR)**

The PSIR instructions can read and programmed (Erase) using three dedicated instructions. The program information Raw instruction is used to program at most 256 bytes to the security memory area (by changing bits from '1' to '0', only). Before it can be accepted, a write enable (WREN) instruction must previously have been executed. After the write enable (WREN) instruction has been decoded, the device sets the write enable latch (WEL) bit. The program information Row instruction is entered by driving CE# pin Low, followed by the instruction code, three address bytes and at least one data byte on serial data input (SI). CE# pin must be driven High after the eighth bits of the last data byte has been latched in, otherwise the Program information Row instruction is not executed. If more than 256 bytes data are sent to a device, the address counter can not roll over.

After CE# pin is driven High, the self-timed page program cycle (whose duration is t<sub>potp</sub>) is initiated. While the program OTP cycle is in progress, the status register may be read to check the value of the write in progress (WIP) bit. The write in progress (WIP) bit is 1 during the self-timed program cycle, and it is 0 when it is completed. At some unspecified time before the cycle is complete, the write enable latch (WEL) bit is reset.

Figure 30. Program information Raw Sequence

Note: 1. The SIR address is from 000000h to 0000FFh. 2. The SIR protection bit is in the address 000100h.

# **DEVICE OPERATION (CONTINUED)**

#### To lock the OTP memory:

Bit 0 of the OTP control byte, that is byte 256, is used to permanently lock the OTP memory array.

- □When bit 0 of byte 256 = '1', the 256 bytes of the OTP memory array can be programmed.

- □When bit 0 of byte 256 = '0', the 256 bytes of the OTP memory array are read-only and cannot be programmed anymore.

Once a bit of the OTP memory has been programmed to '0', it can no longer be set to '1'. Therefore, as soon as bit 0 of byte 256 (control byte) is set to '0', the 256 bytes of the OTP memory array become read-only in a permanent way.

Any program OTP (POTP) instruction issued while an erase, program or write cycle is in progress is rejected without having any effect on the cycle that is in progress

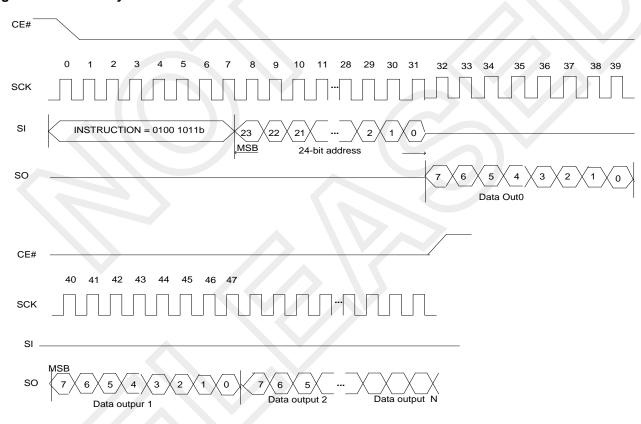

#### Read Security Information Row (RSIR)

The RSIR instruction read the security information Row. There is no rollover mechanism with the read OTP (ROTP) instruction. This means that the read OTP (ROTP) instruction must be sent with a maximum of 256 bytes to read, since once the 256<sup>th</sup> byte has been read, the same (256<sup>th</sup>) byte keeps being read on the SO pin.

Fig 33. Read Security information Row instruction

#### **Program/Erase Suspend Resume**

The device allows the interruption of Sector-Erase, Block-Erase or Page-Program operations and will conduct other operations.

To enter the suspend/ resume mode: issuing 75h/B0h for suspend; 7Ah/30h for resume Suspend to suspend ready timing: 20us.

Resume to another suspend timing: 1ms.

\*Note: It takes 500ns delay time to go from write command to suspend command

#### Program/Erase Suspend During Sector-Erase or Block-Erase

After erase suspend, WEL bit will be clear, only read related and resume command can be accepted. (03h, 0Bh, BBh, EBh, 05h, ABh, 9Fh, 90h, 4Bh)

To execute a Program/Erase Suspend operation, the host drives CE# low, sends the Program/Erase Suspend command cycle (75H/B0h), then drives CE# high. The device will not accept another command until it is ready. To determine when the device will accept a new command, poll the WIP bit in the Status register or wait Tws.

#### **Program/Erase Suspend During Page Programming**

Program suspend allows the interruption of all program operations.

After program suspend, WEL bit will be cleared, only read related and resume command can be accepted. (03h, 0Bh, BBh, EBh, 05h, ABh, 9Fh, 90h, 4Bh)

To execute a Program/Erase Suspend operation, the host drives CE# low, sends the Program/Erase Suspend command cycle (75H/B0h), then drives CE# high. The device will not accept another command until it is ready. To determine when the device will accept a new command, poll the WIP bit in the Status register or wait Tws.

#### Program/Erase Resume

Program/Erase Resume restarts a Program/Erase command that was suspended. To execute a Program/Erase Resume operation, the host drives CE# low, sends the Program/Erase Resume command cycle (7AH/30h), then drives CE# high. To determine if the internal, self-timed Write operation completed, poll the WIP bit in the Status register, or wait the specified time Tse, Tbe or Tpp for Sector- Erase, Block-Erase, or Page-Programming, respectively. The total write time before suspend and after resume will not exceed the uninterrupted write times Tse, Tbe or Tpp.

# ABSOLUTE MAXIMUM RATINGS (1)

| Storage Temperature                           | -55°C to +125°C       |                 |

|-----------------------------------------------|-----------------------|-----------------|

| Surface Mount Lead Soldering Temperature      | Standard Package      | 240°C 3 Seconds |

| Surface Mount Lead Soldering Temperature      | Lead-free Package     | 260°C 3 Seconds |

| Input Voltage with Respect to Ground on All F | -0.5 V to VCC + 0.5 V |                 |

| All Output Voltage with Respect to Ground     | -0.5 V to VCC + 0.5 V |                 |

| VCC (2)                                       | -0.5 V to +6.0 V      |                 |

#### Notes:

- 1. Applied conditions greater than those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. The functional operation of the device conditions that exceed those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating condition for extended periods may affect device reliability.

- 2. Maximum DC voltage on input or I/O pins is Vcc + 0.5 V. During voltage transitions, input or I/O pins may overshoot Vcc by + 2.0 V for a period of time not to exceed 20 ns. Minimum DC voltage on input or I/O pins is -0.5 V. During voltage transitions, input or I/O pins may undershoot GND by -2.0 V for a period of time not to exceed 20 ns.

# DC AND AC OPERATING RANGE

| Part Number                                  | IS25LQ020/040  |

|----------------------------------------------|----------------|

| Operating Temperature (Extended Grade)       | -40°C to 105°C |

| Operating Temperature (Industrial Grade)     | -40°C to 85°C  |

| Operating Temperature (Automotive, A1 Grade) | -40°C to 85°C  |

| Operating Temperature (Automotive, A2 Grade) | -40°C to 105°C |

| Operating Temperature (Automotive, A3 Grade) | -40°C to 125°C |

| Vcc Power Supply                             | 2.3 V – 3.6 V  |

### DC CHARACTERISTICS

Applicable over recommended operating range from:

$T_{AC} = -40$ °C to +125°C,  $V_{CC} = 2.3$  V to 3.6 V (unless otherwise noted).

| Symbol           | Parameter                 | Condition                                                           |                           | Min                   | Ty<br>p               | Max    | Units |

|------------------|---------------------------|---------------------------------------------------------------------|---------------------------|-----------------------|-----------------------|--------|-------|

| I <sub>CC1</sub> | Vcc Active Read Current   | $V_{CC} = 3.6V \text{ at } 33 \text{ M}$                            |                           | 10                    | 12                    | mA     |       |

| I <sub>CC2</sub> | Vcc Program/Erase Current | $V_{CC} = 3.6V \text{ at } 33 \text{ M}$                            |                           | 15                    | 20                    | mA     |       |

| I <sub>SB1</sub> | Vcc Standby Current CMOS  | $V_{CC} = 3.6V, CE\# = 3.6V$                                        |                           | 10                    | 30                    | μΑ     |       |

| I <sub>SB3</sub> | Vcc Standby Current TTL   | $V_{CC}$ = 3.6V, CE# = $V_{IH}$ to $V_{CC}$                         |                           |                       |                       | 3      | mA    |

| ILI              | Input Leakage Current     | $V_{IN} = 0V \text{ to } V_{CC}$                                    |                           |                       |                       | 1      | μΑ    |

| I <sub>LO</sub>  | Output Leakage Current    | $V_{IN} = 0V$ to $V_{CC}$ , $T_{AC} = 0^{\circ}C$ to $130^{\circ}C$ |                           |                       |                       | 1      | μΑ    |

| V <sub>IL</sub>  | Input Low Voltage         |                                                                     |                           | -0.5                  |                       | 0.3Vcc | V     |

| V <sub>IH</sub>  | Input High Voltage        |                                                                     |                           | 0.7V <sub>CC</sub>    | V <sub>CC</sub> + 0.3 |        | V     |

| V <sub>OL</sub>  | Output Low Voltage        | 2 2 1/2 1/2 2 6 1/2                                                 | I <sub>OL</sub> = 2.1 mA  |                       |                       | 0.45   | V     |

| V <sub>OH</sub>  | Output High Voltage       | $2.3V < V_{CC} < 3.6V$                                              | I <sub>OH</sub> = -100 μA | V <sub>CC</sub> - 0.2 |                       |        | V     |

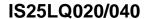

# **AC CHARACTERISTICS**

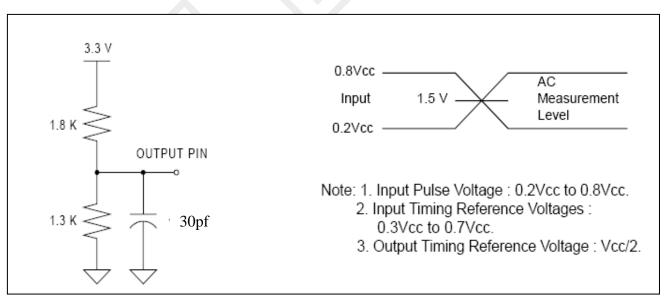

Applicable over recommended operating range from  $T_A = -40$ °C to +125°C,  $V_{CC} = 2.3$  V to 3.6 V  $C_L = 1$  TTL Gate and 30 pF (unless otherwise noted).

| Symbol            | Parameter                          | Min | Тур  | Max | Units |

|-------------------|------------------------------------|-----|------|-----|-------|

| fст               | Clock Frequency for fast read mode | 0   |      | 104 | MHz   |

| fc                | Clock Frequency for read mode      | 0   |      | 33  | MHz   |

| trı               | Input Rise Time                    |     |      | 8   | ns    |

| tFI               | Input Fall Time                    |     |      | 8   | ns    |

| tскн              | SCK High Time                      | 4   |      |     | ns    |

| tckl              | SCK Low Time                       | 4   |      |     | ns    |

| tceh              | CE# High Time                      | 25  |      |     | ns    |

| tcs               | CE# Setup Time                     | 10  |      |     | ns    |

| tсн               | CE# Hold Time                      | 5   |      |     | ns    |

| tos               | Data In Setup Time                 | 2   |      |     | ns    |

| tDH               | Data in Hold Time                  | 2   |      |     | ns    |

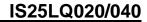

| ths               | Hold Setup Time                    | 15  |      |     | ns    |

| thd               | Hold Time                          | 15  |      |     | ns    |

| tv                | Output Valid                       |     |      | 8   | ns    |

| tон               | Output Hold Time Normal Mode       | 0   |      |     | ns    |

| tLZ               | Hold to Output Low Z               |     |      | 200 | ns    |

| tHZ               | Hold to Output High Z              |     |      | 200 | ns    |

| tois              | Output Disable Time                |     |      | 100 | ns    |

| tec               | Secter Erase Time                  |     | 120  | 300 | ms    |

|                   | Block Erase Time(64Kbyte)          |     | 0.25 | 1   | S     |

|                   | Chip Erase Time (2Mb)              |     | 0.75 | 1.5 | S     |

|                   | Chip Erase Time (4Mb)              |     | 1.5  | 3   | S     |

| <b>t</b> PP       | Page Program Time                  |     | 0.5  | 1   | ms    |

| t <sub>res1</sub> | Release from Power-Down            |     |      | 3   | μs    |

| t <sub>dp</sub>   | Deep Power Down                    |     |      | 3   | μs    |

| t <sub>w</sub>    | Write Status Register time         |     | 2    | 10  | ms    |

| Tws               | Suspend time                       |     |      | 20  | μs    |

## **AC CHARACTERISTICS (CONTINUED)**

### SERIAL INPUT/OUTPUT TIMING (1)

Note: 1. For SPI Mode 0 (0,0)

# **AC CHARACTERISTICS (CONTINUED)**

#### **HOLD TIMING**

PIN CAPACITANCE (f = 1 MHz, T = 25°C)

|      | Тур | Max | Units | Conditions |

|------|-----|-----|-------|------------|

| CIN  | 4   | 6   | pF    | Vin = 0 V  |

| Соит | 8   | 12  | pF    | Vout = 0 V |

Note: These parameters are characterized but not 100% tested.

#### **OUTPUT TEST LOAD**

#### INPUT TEST WAVEFORMS AND MEASUREMENT LEVEL

#### **POWER-UP AND POWER-DOWN**

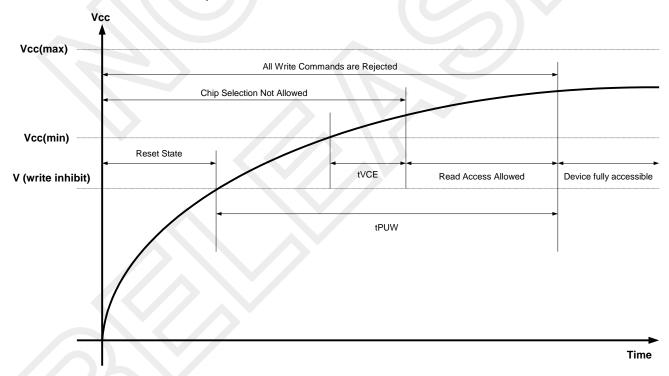

At Power-up and Power-down, the device must not be selected (CE# must follow the voltage applied on Vcc) until Vcc reaches the correct value:

- Vcc(min) at Power-up, and then for a further delay of tVCF

- Vss at Power-down

Usually a simple pull-up resistor on CE# can be used to insure safe and proper Power-up and Power-down. To avoid data corruption and inadvertent write operations during power up, a Power On Reset (POR) circuit is included. The logic inside the device is held reset while Vcc is less than the POR threshold value (Vwi) during power up, the device does not respond to any instruction until a time delay of tPUW has elapsed after the moment that Vcc rised above the VWI threshold. However, the correct operation of the device

is not guaranteed if, by this time, Vcc is still below Vcc(min). No Write Status Register, Program or Erase instructions should be sent until the later of:

- tPUW after Vcc passed the VWI threshold

- tVCE after Vcc passed the Vcc(min) level

At Power-up, the device is in the following state:

- The device is in the Standby mode

- The Write Enable Latch (WEL) bit is reset

At Power-down, when Vcc drops from the operating voltage, to below the Vwi, all write operations are disabled

and the device does not respond to any write instruction.

| Symbol                                              | Parameter                                | Min. | Max. | Unit |

|-----------------------------------------------------|------------------------------------------|------|------|------|

| t <sub>VCE</sub> *1                                 | Vcc(min) to CE# Low                      | 150  |      | us   |

| t <sub>PUW</sub> *1                                 | Power-Up time delay to Write instruction | 1    | 10   | ms   |

| V <sub>WI</sub> <sup>*1</sup> Write Inhibit Voltage |                                          | 2.0  |      | V    |

| Note: *1. T                                         | hese parameters are characterized only.  |      |      |      |

## PROGRAM/ERASE PERFORMANCE

| Parameter               | Unit | Тур  | Max  |

|-------------------------|------|------|------|

| Sector Erase Time       | ms   | 120  | 300  |

| Block Erase Time (64KB) | ms   | 250  | 1000 |

| Chip Erase Time (2Mb)   | S    | 0.75 | 1.5  |

| Chip Erase Time (4Mb)   | S    | 1.5  | 3    |

| Page Programming Time   | ms   | 0.5  | 1    |

| Byte Program            | μs   | 8    | 25   |

Note: These parameters are characterized and are not 100% tested.

### **RELIABILITY CHARACTERISTICS**

| Parameter              | Min        | Unit   | Test Method         |

|------------------------|------------|--------|---------------------|

| Endurance              | 100,000    | Cycles | JEDEC Standard A117 |

| Data Retention         | 20         | Years  | JEDEC Standard A103 |

| ESD – Human Body Model | 2,000      | Volts  | JEDEC Standard A114 |

| ESD – Machine Model    | 200        | Volts  | JEDEC Standard A115 |

| Latch-Up               | 100 + Icc1 | mA     | JEDEC Standard 78   |

Note: These parameters are characterized and are not 100% tested.

## **PACKAGE TYPE INFORMATION**

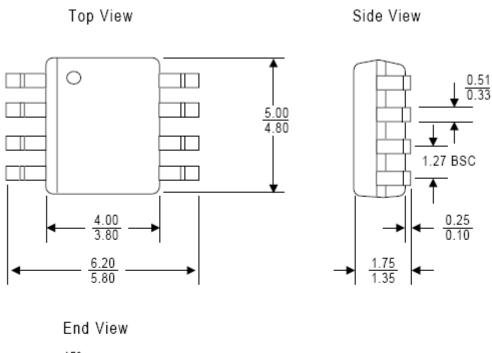

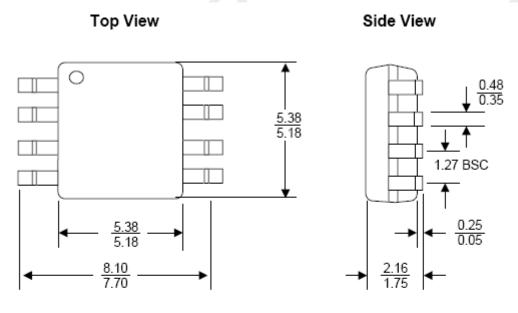

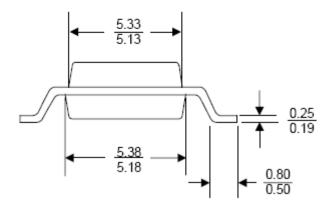

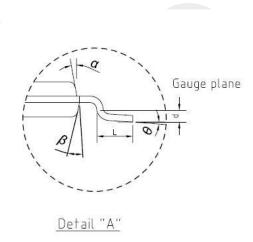

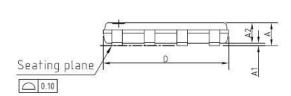

### JN 8-Pin JEDEC 150mil Broad Small Outline Integrated Circuit (SOIC) Package (measure in millimeters)

### JB 8-Pin JEDEC 208mil Broad Small Outline Integrated Circuit (SOIC) Package (measure in millimeters)

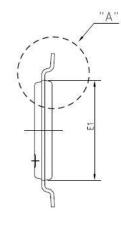

### **End View**

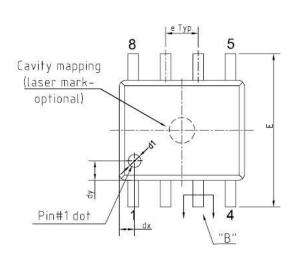

# JV 8-pin VVSOP 150mil

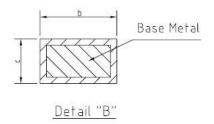

| SYMBOL | [    | DIMENSIO<br>(MM) | N     | DIMENSION<br>(MIL) |         |         |  |

|--------|------|------------------|-------|--------------------|---------|---------|--|

|        | MIN. | NOM.             | MAX.  | MIN.               | NOM.    | MAX     |  |

| Α      | 222  | (222             | 0.88  | 202                | 2004    | 34.6    |  |

| A1     | 0.05 |                  | 0.14  | 2.0                |         | 5.5     |  |

| A2     | 0.63 | 3222             | 0.74  | 24.8               | 222     | 29.1    |  |

| b      | 0.33 | 0.41             | 0.51  | 13.0               | 16.1    | 20.1    |  |

| С      | 0.13 | 1222             | 0.18  | 5.1                | 222     | 7.1     |  |

| D      | 4.80 | 4.90             | 5.00  | 189.0              | 192.9   | 196.9   |  |

| d      | 2520 | 0.25             | 94446 | 2427               | 10.0    |         |  |

| d1     | 202  | 0.50typ          | 2000  | 5000               | 19.7†yp | 1127151 |  |

| dx     |      | 0.60†yp          |       |                    | 23.6†yp |         |  |

| dy     |      | 0.76typ          |       |                    | 29.9typ |         |  |

| E      | 5.80 | 6.00             | 6.20  | 228.3              | 236.2   | 244.1   |  |

| E1     | 3.80 | 3.90             | 4.00  | 149.6              | 153.5   | 157.5   |  |

| е      |      | 1.27             |       |                    | 50.0    |         |  |

| L      | 0.41 | 0.71             | 1.27  | 16.1               | 28.0    | 50.0    |  |

| α      | 100  | 10°              | 57.73 | -55%               | 10°     | 8555    |  |

| β      |      | 10°              |       |                    | 10°     |         |  |

| θ      | 0°   |                  | 10°   | 0°                 | 555     | 10°     |  |

### NOTES:

- 1. MOLD BODY DIMENSION DOES NOT INCLUDE END FLASH.

- 2. THE MOLDED END FLASH IS MAX. 0.15 mm.

- 3. LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION / INTRUSION.

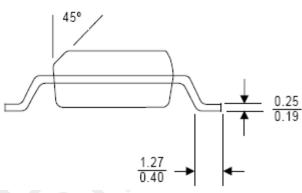

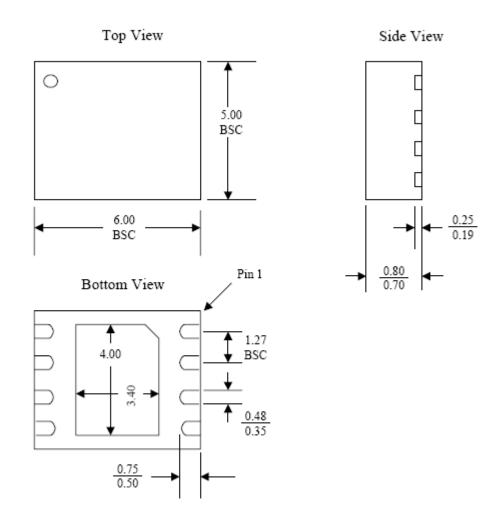

JK 8-Pin Ultra-Thin Small Outline No-Lead (WSON) Package (measure in millimeters)

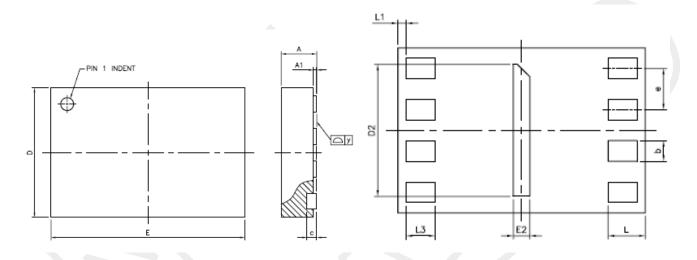

JU 8-pin USON Package (measure in millimeters)

| evannoi e | DIMENSIC | INS IN MIL | LIMETERS |

|-----------|----------|------------|----------|

| SYMBOLS   | MIN      | NOM        | MAX      |

| A         | 0.50     | 0.55       | 0.60     |

| A1        | 0.00     | 0.02       | 0.05     |

| b         | 0.20     | 0.25       | 0.30     |

| С         |          | 0.15 REF.  |          |

| D         | 1.90     | 2.00       | 2.10     |

| D2        | 1.55     | 1.60       | 1.65     |

| E         | 2.90     | 3.00       | 3.10     |

| E2        | 0.15     | 0.20       | 0.25     |

| е         |          | 0.50       |          |

| L         | 0.40     | 0.45       | 0.50     |

| L1        |          | 0.10       |          |

| L3        | 0.30     | 0.35       | 0.40     |

| у         | 0.00     |            | 0.075    |

### **Appendix1: Safe Guard function**

Safe Guard function is a security function for customer to protect by sector (4Kbyte).

Every sector has one bit register to decide if it is under safe guard protect or not. ("0" means protect and "1" means not protect by safe guard.)

IS25LQ020 (sector 0~sector 63)

IS25LQ040 (sector 0~sector 127)

## Mapping table for safe guard register

|            | Address | D7 | D6 |   | D5 |   | D4 | D3 | D2 | D1 | D0 |

|------------|---------|----|----|---|----|---|----|----|----|----|----|

| Sector 0   | 000h    |    | 1  | 1 | 1  | 1 | 1  | 1  | 1  | 1  | 0  |

| Sector 1   | 000h    | •  | 1  | 1 | 1  | 1 | 1  | 1  | 1  | 0  | 1  |

| Sector 2   | 000h    |    | 1  | 1 | 1  | 1 | 1  | 1  | 0  | 1  | 1  |

| Sector 3   | 000h    | •  | 1  | 1 | •  | 1 | 1  | 0  | 1  | 1  | 1  |

| Sector 4   | 000h    | •  | 1  | 1 | ,  | 1 | 0  | 1  | 1  | 1  | 1  |

| Sector 5   | 000h    |    | 1  | 1 | (  | C | 1  | 1  | 1  | 1  | 1  |

| Sector 6   | 000h    |    | 1  | 0 | 1  | 1 | 1  | 1  | 1  | 1  | 1  |

| Sector 7   | 000h    | O  | )  | 1 | ,  | 1 | 1  | 1  | 1  | 1  | 1  |

| :          | :       | :  | :  |   | :  |   | :  | :  | :  |    | :  |

| Sector 56  | 006h    |    | 1  | 1 | -  | 1 | 1  | 1  | 1  | 1  | 0  |

| Sector 57  | 006h    |    | 1  | 1 | -  | 1 | 1  | 1  | 1  | 0  | 1  |

| Sector 58  | 006h    |    | 1  | 1 | 1  | 1 | 1  | 1  | 0  | 1  | 1  |

| Sector 59  | 006h    |    | 1  | 1 | 1  | 1 | 1  | 0  | 1  | 1  | 1  |

| Sector 60  | 006h    | ,  | 1  | 1 | 1  | 1 | 0  | 1  | 1  | 1  | 1  |

| Sector 61  | 006h    |    | 1  | 1 | (  | C | 1  | 1  | 1  | 1  | 1  |

| Sector 62  | 006h    |    | 1  | 0 | 1  | 1 | 1  | 1  | 1  | 1  | 1  |

| Sector 63  | 006h    | (  | )  | 1 | 1  | 1 | 1  | 1  | 1  | 1  | 1  |

| :          | ÷       | :  | :  |   | :  |   | :  | :  |    | :  | :  |

| Sector 120 | 00Fh    | •  | 1  | 1 | 1  | 1 | 1  | 1  | 1  | 1  | 0  |

| Sector 121 | 00Fh    |    | 1  | 1 | 1  | 1 | 1  | 1  | 1  | 0  | 1  |

| Sector 122 | 00Fh    | ,  | 1  | 1 | 1  | 1 | 1  | 1  | 0  | 1  | 1  |

| Sector 123 | 00Fh    |    | 1  | 1 | 1  | 1 | 1  | 0  | 1  | 1  | 1  |

| Sector 124 | 00Fh    |    | 1  | 1 | 1  | 1 | 0  | 1  | 1  | 1  | 1  |

| Sector 125 | 00Fh    | •  | 1  | 1 | (  | C | 1  | 1  | 1  | 1  | 1  |

| Sector 126 | 00Fh    | •  | 1  | 0 | 1  | 1 | 1  | 1  | 1  | 1  | 1  |

| Sector 127 | 00Fh    | (  | )  | 1 | 1  | 1 | 1  | 1  | 1  | 1  | 1  |

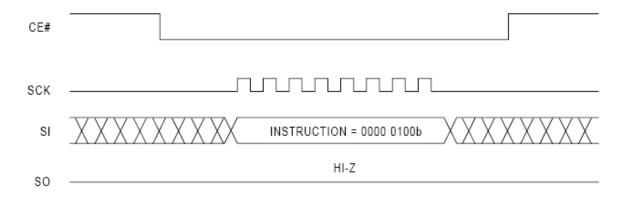

#### Read Safe Guard register

The READ Safe Guard instruction code is transmitted via the SIO line, followed by three address bytes (A23 - A0) of the first register location to be read. The first byte data (D7 - D0) addressed is then shifted out on the SO line, MSb first. The address is automatically incremented after each byte of data is shifted out. The read operation can be terminated at any time by driving CE# high (VIH) after the data comes out.

Fig a. Timing waveform of Read Safe guard register

#### **Erase Safe Guard register**

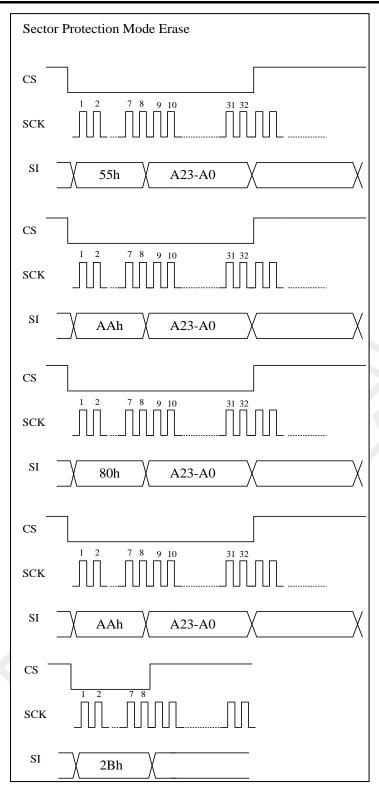

If we want to erase the safe guard register to let the flash into unprotect status, it needs five continuous instructions. If any instruction is wrong, the erase command will be ignored. Erase wait time follow product erase timing spec.

Fig b. shows the complete steps for Erase safe guard register.

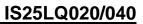

#### **Program Safe Guard register**

If we want to erase the safe guard register to let the flash into unprotect status, it needs five continuous instructions. If any instruction is wrong, the program command will be ignored. The Program safe guard instruction allows up to 256 bytes data to be programmed into memory in a single operation. Program wait time follow product program timing spec.

Fig c. shows the complete steps for program safe guard register.

Fig b. Erase safe guard register

Fig c. program safe guard register

#### **Appendix2: Sector Unlock function**

| Instruction Name | Hex  | Operation     | Command | Maximum   |

|------------------|------|---------------|---------|-----------|

|                  | Code |               | Cycle   | Frequency |

| SECT_UNLOCK      | 26h  | Sector unlock | 4 Bytes | 100 MHz   |

| SECT_LOCK        | 24h  | Sector lock   | 1 Byte  | 100 MHz   |

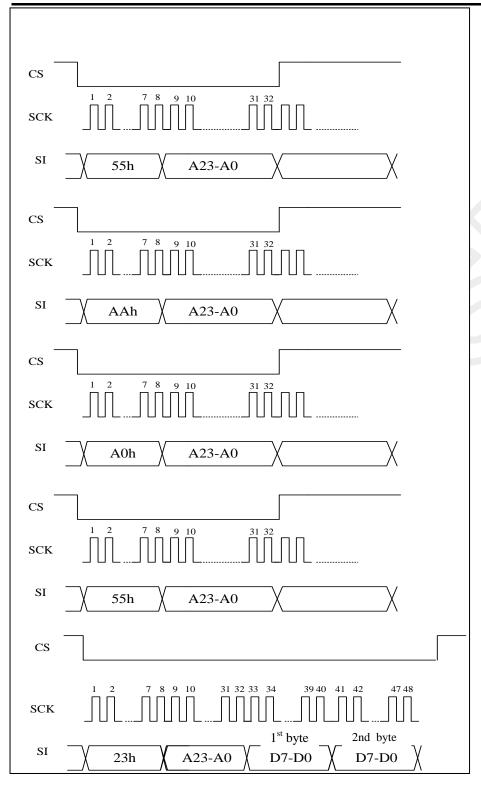

#### SEC\_UNLOCK COMMAND OPERATION

The Sector unlock command allows the user to select a specific sector to allow program and erase operations. This instruction is effective when the blocks are designated as write-protected through the BP0, BP1, BP2 and BP3 bits in the status register. Only one sector can be enabled at any time. To enable a different sector, a previously

enabled sector must be disabled by executing a Sector Lock command. The instruction code is followed by a 24-bit address specifying the target sector, but A0 through A11 are not decoded. The remaining sectors within the same block remain in read-only mode.

Figure d. Sector Unlock Sequence

Note: 1.If the clock number will not match 8 clocks(command)+ 24 clocks (address), it will be ignored. 2.It must be executed write enable (06h) before sector unlock instructions.

#### SECT\_LOCK COMMAND OPERATION

The Sector Lock command reverses the function of the Sector Unlock command. The instruction code does not require an address to be specified, as only one sector can be enabled at a time. The remaining sectors within the same block remain in read-only mode.

Figure e. Sector Lock Sequence

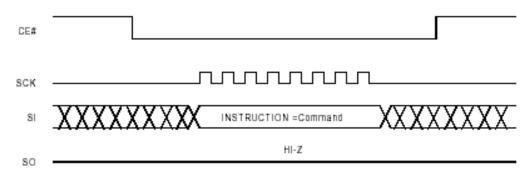

### **PRODUCT ORDERING INFORMATION**

| Flash Product Family                                                                | SPI Interface                                                                | Package Type                                                                                                                                          | Lead-Free Package                                                                                                                                                     |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI = 25                                                                            | D = x2 output                                                                | JN = 8 pin SOIC 150mil                                                                                                                                | All flash products are lead free                                                                                                                                      |

|                                                                                     | Q = x4 output                                                                | JB = 8 pin SOIC 208mil                                                                                                                                |                                                                                                                                                                       |

| SPI Operating Voltage Range<br>L = 2.30V-3.60V<br>W = 1.65V-1.95V<br>C = 2.70-3.60V | Density<br>025 = 256Kb<br>512 = 512Kb<br>010 = 1Mb<br>020 = 2Mb<br>040 = 4Mb | JM = 16 pin SOIC 300mil JD = 8 pin TSSOP JE = 48 pin TSSOP JT = 56 pin TSSOP JK = 8 pin WSON (5x6 mm) JL = 8 pin WSON (6x8mm) JU = 8 pin USON (2x3mm) | Temperature Grade E = Extended grade (-40C to +105C) A1 = Automotive grade (-40C to +85C) A2 = Automotive grade (-40C to +105C) A3 = Automotive grade (-40C to +125C) |

|                                                                                     | 080 = 8Mb                                                                    | JF = 8 pin VSOP 208mil                                                                                                                                |                                                                                                                                                                       |

|                                                                                     | 016 = 16Mb                                                                   | JV = 8 pin VVSOP 150mil                                                                                                                               |                                                                                                                                                                       |

|                                                                                     | 032 = 32Mb                                                                   | JG = 24 ball (BGA 6x8mm) (Call                                                                                                                        | **                                                                                                                                                                    |

|                                                                                     | 064 = 64Mb                                                                   | JH = 48 ball (BGA 6x8mm) (Call                                                                                                                        | **                                                                                                                                                                    |