#### **Features**

- Pin-programmable Mode

- Supply Voltage Range 1.55V to 3.6V

- PHY IC USB1.0 Downstream Port

- Bridge USB2.0 Section 7 to IC\_USB1.0

- Bridge IC\_USB1.0 to USB2.0 Section 7

- 3.3V Voltage Reference

- Two 70mA LDO Voltage Regulators

- Less Than 5µA Static Current on Each Supply

- Slew Rate Control to Minimize Radiated EMI

- ESD 4kV Compliant with USB UICC

- Applications:

- Mobile USB UICC (ETSI 102 600), PC USB UICC, Token USB

## **Description**

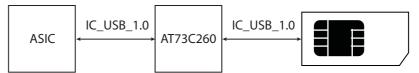

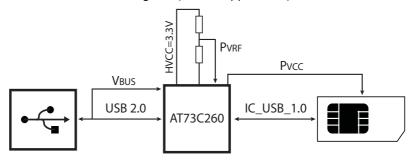

The AT73C260 is an Inter Chip USB transceiver fully compliant with the Universal Serial Bus Specification, and more specifically with the IC\_USB1.0 supplement. The AT73C260 is a bidirectional differential interface. The AT73C260 is ideal for applications in mobile devices, PCs and USB tokens making use of an USB UICC.

The AT73C260's upstream facing port may be connected to three different interfaces:

- Digital

- USB2.0 section 7 with or without cable

- IC USB1.0

The AT73C260's downstream port complies with IC\_USB1.0. The AT73C260's mode is selected by three pins. When PVCC is powered by 3.3V and pull down resistors are added on PDM and PDP, the AT73C260's downstream port complies with USB2.0 section 7.

The AT73C260 includes a 3.5V Supply Monitor, a Low Power Band-Gap, a 3.3V 70mA Linear Voltage Regulator and a 1.8V-3.0V 70mA Linear Voltage Regulator SIM FTA compliant Test 27.17.2.1.

The AT73C260 is specified over the industrial temperature range - 40°C to +85°C.

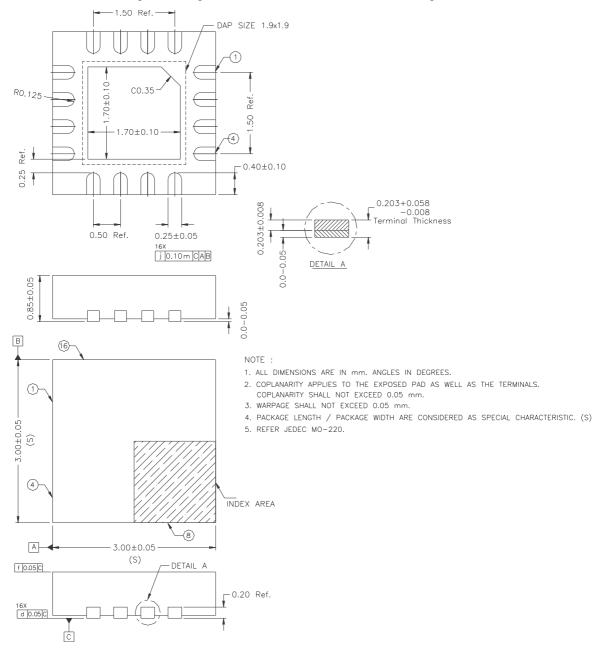

The AT73C260 is available in a 3 X 3 mm, 0.5mm pitch, QFN16 package.

Power

Management

and Analog

Companions

(PMAAC)

AT73C260

Interchip USB Transceiver

(PHY - IC\_USB1.0, Voltage Class Converter, USB2.0 - IC\_USB1.0 Bridges)

**Preliminary**

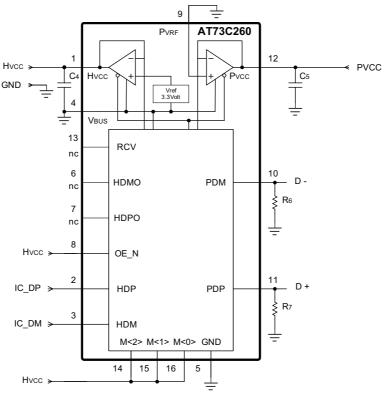

# 1. Block Diagram

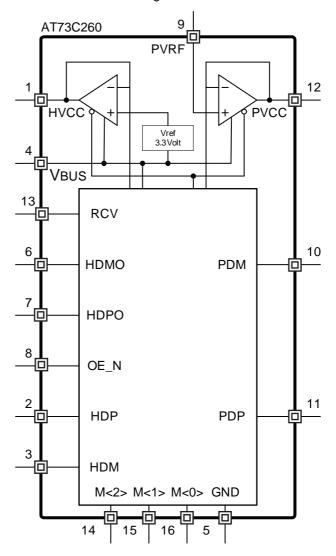

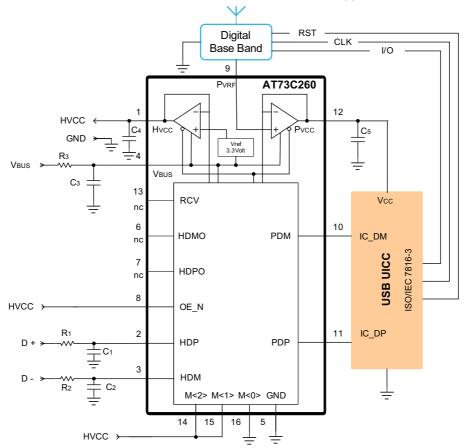

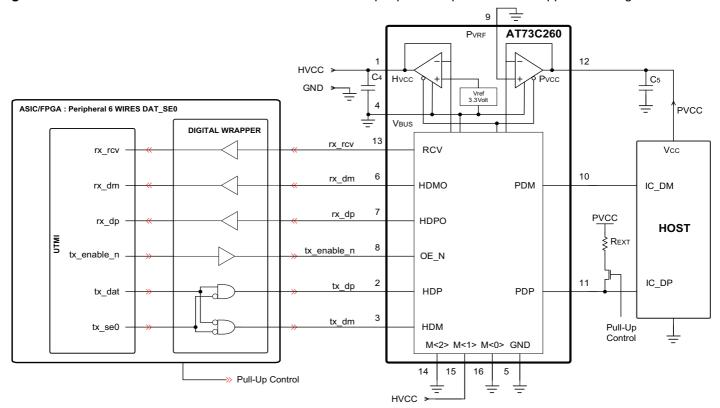

Figure 1-1. AT73C260 functional block diagram

## 2. Package and Pinout

Figure 2-1. AT73C260 QFN16 package pinout - top view

# 3. Pin Description

Table 3-1.AT73C260 Pin Description

| Pin Name | I/O    | Pin Number | Туре    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HVCC     | Output | 1          | Analog  | Host Side VCC     •When pin 4 (VBUS) is grounded. The LDO on pin HVCC is in standby and its output is isolated. The Host supplies HVCC with the appropriate voltage to the AT73C260's upstream transceiver.     •When pin 4 (VBUS) is connected to a voltage source the internal voltage reference 3.3V and both LDO are activated. The LDO on pin 1 provides power at 3.3V to the AT73C260's upstream transceiver and it may source up to 70mA. |

| HDP      | I/O    | 2          | Digital | Bidirectional                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HDM      | I/O    | 3          | Digital | Bidirectional                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VBUS     | Input  | 4          | Analog  | Supply, provides power to the LDOs on pin 1 and 12                                                                                                                                                                                                                                                                                                                                                                                               |

| GND      | Ground | 5          | Analog  | GND Ground for Digital and I/Os                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HDMO     | Output | 6          | Digital | Output                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| HDPO     | Output | 7          | Digital | Output                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OE_N     | Input  | 8          | Digital | Input                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PVRF     | Input  | 9          | Analog  | PVCC LDO input reference                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PDM      | I/O    | 10         | Digital | Bidirectional pad                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PDP      | I/O    | 11         | Digital | Bidirectional pad                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PVCC     | Input  | 12         | Analog  | Peripheral Side VCC  •When pin 4 (VBUS) is grounded. The LDO on pin PVCC is in standby and its output is isolated. The application supplies PVCC with the appropriate voltage to the AT73C260's downstream transceiver.  •When pin 4 (VBUS) is connected to a voltage source, the LDO on pin PVCC follows the voltage on pin PVRF. The LDO on pin PVCC provides power to the AT73C260's downstream transceiver and it may source up to 70mA.     |

| RCV      | Output | 13         | Digital | Output                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| M<2>     | Input  | 14         | Digital | Input. For mode configuration                                                                                                                                                                                                                                                                                                                                                                                                                    |

| M<1>     | Input  | 15         | Digital | Input. For mode configuration                                                                                                                                                                                                                                                                                                                                                                                                                    |

| M<0>     | Input  | 16         | Digital | Input. For mode configuration                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND      | Ground | 17         | Analog  | Analog Ground. Thermal Pad. Shall be connected to GND for electrical and power dissipation reasons.                                                                                                                                                                                                                                                                                                                                              |

## 4. Absolute Maximum Ratings

Table 4-1. Absolute Maximum Ratings

| Operating Temperature (Industrial)40°C to + 85°C <sup>(1)</sup> |

|-----------------------------------------------------------------|

| Storage Temperature55°C to + 150°C                              |

| Power Supply Input on H <sub>VCC</sub> 0.3V to + 3.6V           |

| Power Supply Input on VBUS0.3V to + 5.5V                        |

| Digital I/O Input Voltage0.3V to + 3.6V                         |

| All Other Pins0.3V to + 3.6V                                    |

| ESD (all pins)4 KV HBM                                          |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Notes: 1. Refer to Power Dissipation Rating section)

## 5. Recommended Operating Conditions

Table 5-1.

Recommended Operating Conditions

| Parameter                                    | Condition        | Min  | Max | Units |

|----------------------------------------------|------------------|------|-----|-------|

| Operating Ambient Temperature <sup>(1)</sup> |                  | -40  | 85  | °C    |

| Power Supply Output                          | P <sub>VCC</sub> | 1.55 | 3.6 | V     |

| Power Supply Input                           | H <sub>VCC</sub> | 1.55 | 3.6 | V     |

| Power Supply Input                           | VBUS             | 4.0  | 5.5 | V     |

Note: 1. Refer to Power Dissipation Rating section

## 6. Power Dissipation Ratings

**Table 6-1.** Recommended Operating Conditions

| Parameter                         | Condition                                      | Min | Тур | Max | Units |

|-----------------------------------|------------------------------------------------|-----|-----|-----|-------|

| Maximum Junction Temperature      |                                                | -40 |     | 125 | °C    |

| R <sub>THjA</sub> <sup>(1)</sup>  | Package thermal junction to ambient resistance |     |     | 90  | °C/W  |

| Maximum On-chip Power Dissipation | Ambient temperature = 85°C                     |     |     | 400 | mW    |

Note: 1. According to specification JESD51-5

### 7. Electrical Characteristics

### 7.1 I/Os DC Characteristics Referred to H<sub>VCC</sub>

**Table 7-1.** H<sub>VCC</sub> Referred I/Os: HDP, HDM, RCV, HDMO, HDPO, OE\_N and M<2:0>

| Symbol                          | Parameter                                 | Comments                                                                                             | Min                        | Тур | Max                        | Units |

|---------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| H <sub>VCC</sub>                | Host Side Supply Voltage                  | 220nF ceramic capacitor (1)                                                                          | 1.55                       |     | 3.6                        | V     |

| I <sub>HVCC</sub>               | Operating H <sub>VCC</sub> Supply Current | Full Speed Transceiver / Receiver at 12Mbps, C <sub>LOAD</sub> = 18pF on HDP and HDM during transmit |                            |     | 2                          | mA    |

| V <sub>IH</sub>                 | Input High-Level Voltage                  | V <sub>OH</sub> > V <sub>OH_MIN</sub>                                                                | 0.65 x<br>H <sub>VCC</sub> |     | H <sub>VCC</sub> + 0.3     | V     |

| V <sub>IL</sub>                 | Input Low-Level Voltage                   | V <sub>OH</sub> < V <sub>OL_MAX</sub>                                                                | -0.3                       |     | 0.35 x<br>H <sub>VCC</sub> | V     |

| V <sub>OH</sub>                 | Output High-Level Voltage                 | I <sub>OH</sub> = - 2mA                                                                              | H <sub>VCC</sub> -<br>0.45 |     |                            | V     |

| V <sub>OL</sub>                 | Output Low-Level Voltage                  | I <sub>OL</sub> = 2mA                                                                                |                            |     | 0.45                       | V     |

| R <sub>PDP</sub>                | Pull-Down Resistors on HDP,<br>HDM        | All Cases                                                                                            | 30                         |     | 80                         | kΩ    |

| R <sub>PU1</sub> <sup>(2)</sup> | Upstream Pull-Up Resistors on HDP         | M<0> = 0<br>M<2:1> = connected to HVCC                                                               | 0.9                        |     | 3.09                       | kΩ    |

| R <sub>PU2</sub> <sup>(3)</sup> | Upstream Pull-Up Resistors on HDP         | M<2:0> = connected to H <sub>VCC</sub>                                                               | 1                          |     | 150                        | kΩ    |

Notes:

- 1. A 220nF ceramic capacitor is connected between the pin H<sub>VCC</sub> and the pin GND and closest to H<sub>VCC</sub> pin.

- 2.  $R_{PU1}$  Pull Up resistor is as per the ECN "Pull-up/pull-down resistors" published by the USB-IF.  $R_{PU1}$  value is between  $900\Omega$  and  $1575\Omega$  when the bus is idle and between  $1425\Omega$  and  $3090\Omega$  when the upstream device is transmitting

- 3.  $R_{PU2}$  Pull Up resistor is as per the IC\_USB1.0 published by the USB-IF.  $R_{PU2}$  value is between  $1k\Omega$  and  $3k\Omega$  to attach and between  $30k\Omega$  and  $150k\Omega$  during idle.

## 7.2 I/Os DC Characteristics Referred to P<sub>VCC</sub>

**Table 7-2.** P<sub>VCC</sub> Referred I/Os: PDP, PDM

| Symbol            | Parameter                                 | Comments                                                                                             | Min                        | Тур | Max                        | Units |

|-------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| P <sub>VCC</sub>  | Peripheral Side Supply Voltage            | 220nF ceramic capacitor (1)                                                                          | 1.55                       |     | 3.6                        | V     |

| I <sub>PVCC</sub> | Operating P <sub>VCC</sub> Supply Current | Full Speed Transceiver / Receiver at 12Mbps, C <sub>LOAD</sub> = 18pF on PDP and PDM during transmit |                            |     | 2                          | mA    |

| V <sub>IH</sub>   | Input High-Level Voltage                  | V <sub>OH</sub> > V <sub>OH_MIN</sub>                                                                | 0.65 x<br>P <sub>VCC</sub> |     | P <sub>VCC</sub> + 0.3     | V     |

| $V_{IL}$          | Input Low-Level Voltage                   | V <sub>OH</sub> < V <sub>OL_MAX</sub>                                                                | -0.3                       |     | 0.35 x<br>P <sub>VCC</sub> | ٧     |

| $V_{OH}$          | Output High-Level Voltage                 | I <sub>OH</sub> = - 2mA                                                                              | P <sub>VCC</sub> - 0.45    |     |                            | V     |

| V <sub>OL</sub>   | Output Low-Level Voltage                  | I <sub>OL</sub> = 2mA                                                                                |                            |     | 0.45                       | V     |

| R <sub>PDH</sub>  | Pull-Down Resistors                       | All Cases for PDP, PDM                                                                               | 30                         |     | 80                         | kΩ    |

Notes: 1. A 220nF ceramic capacitor is connected between the pin  $P_{VCC}$  and the pin GND and closest to  $P_{VCC}$  pin.

### 7.3 Timing Characteristics Table

Table 7-3. Timing Table

| Symbol                | Parameter                                   | Comments                                                  | Min | Тур                          | Max | Units |

|-----------------------|---------------------------------------------|-----------------------------------------------------------|-----|------------------------------|-----|-------|

| т                     | Dropogotion Doloy Time                      | $H_{VCC}$ = 3.3V and $P_{VCC}$ = 3.0V                     |     | 37                           |     | ns    |

| T <sub>DELAY</sub>    | Propagation Delay Time                      | $H_{VCC}$ = 3.3V and $P_{VCC}$ = 1.8V                     |     | 42                           |     | ns    |

| _                     | Clay Data Diag Time on DDD                  | 10%-90%, C <sub>LOAD</sub> =33pF, P <sub>VCC</sub> =3.0V  |     | 5.7                          |     |       |

| T <sub>SLEW_R_P</sub> | Slew Rate, Rise Time on PDP                 | 10%-90%, C <sub>LOAD</sub> =33pF, P <sub>VCC</sub> =1.8V  |     | 10.5                         |     |       |

| _                     | Clay Data Diag Time on DDM                  | 10%-90%, C <sub>LOAD</sub> =33pF, P <sub>VCC</sub> =3.0V  |     | 5.6                          |     |       |

| T <sub>SLEW_R_M</sub> | Slew Rate, Rise Time on PDM                 | 10%-90%, C <sub>LOAD</sub> =33pF, P <sub>VCC</sub> =1.8V  |     | 10.6                         |     |       |

| _                     | 01 0 5 5 11 7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 10%-90%, C <sub>LOAD</sub> =33pF, P <sub>VCC</sub> =3.0V  |     | 6.1                          |     | ns    |

| T <sub>SLEW_F_P</sub> | Slew Rate, Fall Time on PDP                 | 10%-90%, C <sub>LOAD</sub> =33pF, P <sub>VCC</sub> =1.8V  |     | 7.6                          |     |       |

| _                     | Class Data Fall Time on DDM                 | 10%-90%, C <sub>LOAD</sub> =33pF, P <sub>VCC</sub> =3.0V  |     | 6.1                          |     |       |

| T <sub>SLEW_F_M</sub> | Slew Rate, Fall Time on PDM                 | 10%-90%, C <sub>LOAD</sub> =33pF, P <sub>VCC</sub> =1.8V  |     | 42 5.7 10.5 5.6 10.6 6.1 7.6 |     |       |

| T <sub>ATTACH</sub>   | Attachment Transit Time                     | $M < 2:0 > = 110$ , $H_{VCC} = 3.3V$ and $P_{VCC} = 3.0V$ |     | 400                          |     | ns    |

| T <sub>ATTACH</sub>   | Attachment Transit Time                     | $M < 2:0 > = 111$ , $H_{VCC} = 1.8V$ and $P_{VCC} = 3.3V$ |     | 400                          |     | ns    |

Notes: 1. External Capacitor is a  $1\mu F$  or higher ceramic capacitor connected between the pin  $V_{BUS}$  and the pin GND and closest to  $V_{BUS}$  pin

### 7.4 V<sub>BUS</sub> Supply Characteristics

**Table 7-4.** V<sub>BUS</sub> Supply Monitor

| Symbol           | Parameter                  | Comments                             | Min  | Тур  | Max  | Units |

|------------------|----------------------------|--------------------------------------|------|------|------|-------|

| V <sub>BUS</sub> | Input Supply Voltage Range | 1μF ceramic capacitor <sup>(1)</sup> | 4.0  | 5.0  | 5.5  | V     |

| V <sub>TP</sub>  | Positive Threshold         |                                      | 3.36 | 3.5  | 3.64 | V     |

| $V_{TN}$         | Negative Threshold         |                                      | 3.02 | 3.15 | 3.28 | V     |

| V <sub>HYS</sub> | Hysteresis                 |                                      | 348  | 361  | 374  | mV    |

Notes: 1. External Capacitor is a  $1\mu F$  or higher ceramic capacitor connected between the pin  $V_{BUS}$  and the pin GND and closest to  $V_{BUS}$  pin

**Table 7-5.** V<sub>BUS</sub> Current Consumption

| Symbol            | Parameter                       | Comments                                                                                                                                                                                                            | Min | Тур | Max | Units |

|-------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| V <sub>BUS</sub>  | Input Supply Voltage Range      | 1µF ceramic capacitor (1)                                                                                                                                                                                           | 4.0 | 5.0 | 5.5 | V     |

| I <sub>VBUS</sub> | V <sub>BUS</sub> Supply Current | $V_{\text{BUS}} \text{ active}$ $\bullet \text{ H}_{\text{VCC}} = 3.3 \text{V nominal}$ $\bullet 1.55 \text{V} < \text{P}_{\text{VRF}} < 3.6 \text{V}$ $\bullet \text{ Loads} = 0 \text{mA}$ $\bullet \text{ Idle}$ |     | 100 | 150 | μА    |

Notes: 1. External Capacitor is a  $1\mu F$  or higher ceramic capacitor connected between the pin  $V_{BUS}$  and the pin GND and closest to  $V_{BUS}$  pin.

### 7.5 H<sub>VCC</sub> and P<sub>VCC</sub> Supplies Characteristics

### 7.5.1 H<sub>VCC</sub> and P<sub>VCC</sub> Current Consumption

**Table 7-6.**  $P_{VCC}$  and  $H_{VCC}$  Current Consumption

| Symbol           | Parameter                       | Comments                                                                                                                              | Min  | Тур | Max | Units |

|------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| H <sub>VCC</sub> | Host Supply Voltage             |                                                                                                                                       | 1.55 |     | 3.6 | V     |

| P <sub>VCC</sub> | Peripheral Supply Voltage       |                                                                                                                                       | 1.55 |     | 3.6 | V     |

| I <sub>vcc</sub> | X <sub>VCC</sub> Supply Current | V <sub>BUS</sub> = 0V, P <sub>VRF</sub> = 0V • Loads = 0mA • Idle • H <sub>VCC</sub> forced at 3.6V • P <sub>VCC</sub> forced at 3.3V |      |     | 5   | μА    |

### 7.5.2 3.3V Supplied on H<sub>VCC</sub>

When  $V_{\text{BUS}}$  is greater than 3.5V nominal, an internal LDO voltage regulator provides a 3.3V nominal voltage source on pin  $H_{\text{VCC}}$ .

**Table 7-7.** H<sub>VCC</sub> LDO Characteristics

| Symbol                          | Parameter               | Comments                                                                                                                                             | Min | Тур      | Max | Units |

|---------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|-------|

| H <sub>VCC</sub> <sup>(1)</sup> | Output Voltage          | <ul> <li>Enabled when V<sub>BUS</sub> is greater than 3.5V typical.</li> <li>Disabled when V<sub>BUS</sub> goes below 3.15V typical</li> </ul>       | 3.0 | 3.3      | 3.6 | V     |

| Io                              | Output Current          |                                                                                                                                                      | 0   |          | 70  | mA    |

|                                 | Static Load Regulation  | • V <sub>BUS</sub> > 4.5V<br>• I <sub>O</sub> = 10% to 90%                                                                                           |     |          | 10  | mV    |

| $\Delta_{VDD\_IL}$              | Dynamic Load Regulation | <ul> <li>V<sub>BUS</sub> &gt; 4.5V</li> <li>I<sub>O</sub> = 10% to 90%</li> <li>T<sub>RISE</sub> = T<sub>FALL</sub> = 5μs</li> </ul>                 |     | 50       |     | mV    |

|                                 | Ctatic Line Degulation  | • V <sub>BUS</sub> from 4.3V to 5.5V<br>• I <sub>O</sub> = Max                                                                                       |     |          | 20  | mV    |

| $\Delta_{VDD\_VIN}$             | Static Line Regulation  | • V <sub>BUS</sub> from 4.0V to 5.5V<br>• I <sub>O</sub> = 7 mA                                                                                      |     | 20<br>20 | 20  | mV    |

| T <sub>START</sub>              | Start-up Time           | <ul> <li>V<sub>BUS</sub> From 0V to 5.0V</li> <li>T<sub>RISE</sub> = 10μs</li> <li>I<sub>O</sub> = 0mA</li> <li>V<sub>OUT</sub> &gt; 3.0V</li> </ul> |     |          | 60  | μs    |

Notes: 1. When  $V_{BUS}$  is present and greater than  $V_{TP}$ ,  $10k\Omega$  pull down is removed on  $H_{VCC}$  and on  $P_{VCC}$  and LDO are started. When  $V_{BUS}$  goes below  $V_{TP}$ , a  $10k\Omega$  pull down is connected on  $H_{VCC}$  and  $P_{VCC}$  and LDO are disabled. When  $V_{BUS} = 0V$  and  $H_{VCC}$  and  $P_{VCC}$  within their normal range the  $10k\Omega$  pull down are disconnected.

### 7.5.3 Voltage Supplied on P<sub>VCC</sub>

When  $V_{\text{BUS}}$  is greater than 3.5V nominal, an internal LDO Follower provides a voltage source on pin  $P_{VCC}$ . The voltage on pin  $P_{VCC}$  is equal to the voltage on pin  $P_{VRF}$ .

$P_{\text{VCC}}$  LDO is in accordance with FTA Test 3GPP - 27.17.2.1 dedicated for Subscriber Identity Module (SIM) application.

**Table 7-8.** P<sub>VCC</sub> LDO Characteristics

| Symbol                           | Parameter               | Comments                                                                                                                                                                                     | Min  | Тур | Max                            | Units |

|----------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------------------|-------|

| V <sub>BUS</sub>                 | Supply Input Voltage    | On pin V <sub>BUS</sub>                                                                                                                                                                      | 4.0  | 5.0 | 5.5                            | V     |

| P <sub>VCC</sub> <sup>(1)</sup>  | Output Voltage          | <ul> <li>Enabled when V<sub>BUS</sub> is greater than 3.5V typical.</li> <li>Disabled when V<sub>BUS</sub> goes below 3.15V typical</li> <li>1.55V &lt; P<sub>VRF</sub> &lt; 3.6V</li> </ul> | 1.55 |     | 3.6                            | V     |

| V <sub>OFF</sub>                 | Follower Offset Voltage | P <sub>VCC</sub> - P <sub>VRF</sub>                                                                                                                                                          | -40  |     | 40                             | mV    |

| Io                               | Output Current          |                                                                                                                                                                                              | 0    |     | 70                             | mA    |

|                                  | Static Load Regulation  | • V <sub>BUS</sub> > 4.5V<br>• I <sub>O</sub> = 10% to 90%                                                                                                                                   |      |     | 10                             | mV    |

| $\Delta_{\text{VDD\_IL}}$        | Dynamic Load Regulation | <ul> <li>V<sub>BUS</sub> &gt; 4.5V</li> <li>I<sub>O</sub> = 10% to 90%</li> <li>T<sub>RISE</sub> = T<sub>FALL</sub> = 5μs</li> </ul>                                                         |      | 30  |                                | mV    |

|                                  | Static Line Regulation  | • V <sub>BUS</sub> from 4.3V to 5.5V<br>• I <sub>O</sub> = Max                                                                                                                               |      |     | 20                             | mV    |

| $\Delta_{VDD\_VIN}$              |                         | • V <sub>BUS</sub> from 4.0V to 5.5V<br>• I <sub>O</sub> = 7 mA                                                                                                                              |      |     | 20                             | mV    |

| _                                |                         | <ul> <li>V<sub>BUS</sub> is set at 5.0V</li> <li>P<sub>VRF</sub> 0V to 1.8V with T<sub>RISE</sub> = 5μs</li> <li>I<sub>O</sub> = 10mA</li> <li>V<sub>OUT</sub> &gt; 1.62V</li> </ul>         |      | 20  | 35                             | μs    |

| T <sub>START</sub>               | Start-up Time           | <ul> <li>V<sub>BUS</sub> is set at 5.0V</li> <li>P<sub>VRF</sub> 0V to 3.0V with T<sub>RISE</sub> = 5μs</li> <li>I<sub>O</sub> = 10mA</li> <li>V<sub>OUT</sub> &gt; 2.7V</li> </ul>          |      | 32  | 40<br>70<br>10<br><br>20<br>20 | μs    |

| т (2)                            | Power Off Time          | • $V_{BUS}$ is set at 5.0V<br>• $P_{VRF}$ 3.0V to 0V with $T_{FALL}$ = 5 $\mu$ s<br>• $R_{LOAD}$ = 1 $K\Omega$ . $C_{OUT}$ =220 $n$ F/ X5R<br>• $V_{OUT}$ < 0.4V                             |      |     | 525                            | μs    |

| T <sub>STOP</sub> <sup>(2)</sup> | Power-Off Time          | • $V_{BUS}$ is set at 5.0V<br>• $P_{VRF}$ 3.0V to 0V with $T_{FALL}$ = 5 $\mu$ s<br>• $I_{O}$ = 7mA. $C_{OUT}$ =220nF/ X5R<br>• $V_{OUT}$ < 0.4V                                             |      |     | 225                            | μs    |

Notes: 1. When  $V_{BUS}$  is present and greater than  $V_{TP}$ ,  $10k\Omega$  pull down is removed on  $H_{VCC}$  and on  $P_{VCC}$  and LDO are started. When  $V_{BUS}$  goes below  $V_{TP}$ , a  $10k\Omega$  pull down is connected on  $H_{VCC}$  and  $P_{VCC}$  and LDO are disabled. When  $V_{BUS}$  = 0V and  $H_{VCC}$  and  $P_{VCC}$  within their normal range the  $10k\Omega$  pull down are disconnected.

<sup>2.</sup> Off time is described in Section 9.3.4 on page 16. To reduce T<sub>STOP</sub> time an external reisitor is recommended. This value depends on C<sub>OUT</sub> and load applied on the system.

# 8. Components List.

Table 8-1.

AT73C260 External Components List

| Component Name                  | Component Type        | Value / Tol.  | Reference                        | Reference         |

|---------------------------------|-----------------------|---------------|----------------------------------|-------------------|

| R <sub>1</sub> , R <sub>2</sub> | Resistor              | 33 Ω +/- 5%   | CRG04                            | 02J33R            |

| R <sub>3</sub>                  | Resistor              | 10 Ω +/- 5%   | CRG06                            | 03J10R            |

| R <sub>4</sub>                  | Resistor              | 10kΩ +/- 1%   | CPF0402                          | 2F10KE1           |

| R <sub>5</sub>                  | Resistor              | 100kΩ +/- 1%  | CPF0603                          | F100KC1           |

| R <sub>6</sub> , R <sub>7</sub> | Resistor              | 22kΩ +/- 5%   | CRG04                            | 02J22K            |

| C <sub>1</sub> , C <sub>2</sub> | Ceramic Capacitor COG | 22pF +/- 20%  | C1005COG1H220J                   | GRM1555C1H220JZ01 |

| C <sub>3</sub>                  | Ceramic Capacitor X5R | 1µF +/- 20%   | C1005X5R0J105K GRM155R60J105KE1  |                   |

| C <sub>4</sub>                  | Ceramic Capacitor X5R | 220nF +/- 20% | C1005X5R1C224KT GRM155R60J224KE0 |                   |

| C <sub>5</sub>                  | Ceramic Capacitor X5R | 220nF +/- 20% | C1005X5R1C224KT                  | GRM155R60J224KE01 |

### 9. Functional Description

### 9.1 AT73C260's Upstream and Downstream Ports

This section relates to either upstream or downstream ports with digital, IC\_USB1.0 or USB2.0 section 7 electrical characteristics.

Table 9-1 shows the configuration of the upstream and downstream ports based on pins 14, 15 and 16 voltages.

- 0 is when the pin is connected to GND.

- 1 is when the pin is connected to H<sub>VCC</sub>.

**Table 9-1.** Upstream and Downstream Ports

| M<2><br>Pin 14 | M<1><br>Pin 15 | M<0><br>Pin 16 | Upstream<br>Port | Downstream<br>Port        |

|----------------|----------------|----------------|------------------|---------------------------|

| 0              | 0              | 0              | Digital          | IC_USB1.0                 |

| 0              | 0              | 1              | Digital          | IC_USB1.0                 |

| 0              | 1              | 0              | Digital          | IC_USB1.0                 |

| 0              | 1              | 1              | Digital          | IC_USB1.0                 |

| 1              | 0              | 0              | Not Used         | Not Used                  |

| 1              | 0              | 1              | Digital          | IC_USB1.0                 |

| 1              | 1              | 0              | Section 7        | IC_USB1.0                 |

| 1              | 1              | 1              | IC_USB1.0        | Section 7 (1) / IC_USB1.0 |

Notes: 1.  $P_{VCC}$  is set to 3.3V and external pull down resistors of  $22k\Omega \pm 5\%$  are connected, one between PDP and GND and the other between PDM and GND.

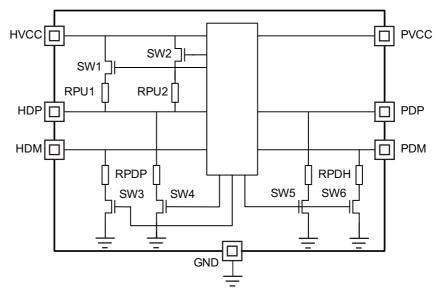

### 9.2 AT73C260 Pull Up and Pull Down Resistors

Pull down resistors  $R_{PDP}$  and  $R_{PDH}$  values and behaviors comply with the IC\_USB1.0 specification published by the USB-IF.

### 9.2.1 AT73C260 Upstream Port Connectivity ( $H_{VCC}$ , $H_{DP}$ , $H_{DM}$ ):

The host, IC\_USB1.0 or USB2.0 section 7, is connected to the AT73C260's upstream port.

- When in IC\_USB 1.0 R<sub>PU2</sub> is selected.

- When in USB2.0 section 7 R<sub>PU1</sub> is selected.

### 9.2.2 AT73C260 Downstream Port Connectivity ( $P_{VCC}$ , $P_{DP}$ , $P_{DM}$ ):

The peripheral, IC\_USB1.0 or USB2.0 section 7, is connected to the AT73C260's downstream port.

- An IC\_USB1.0 peripheral is connected to the AT73C260's downstream port.

- An USB2.0 section 7 peripheral is connected to the AT73C260's downstream port with external pull down resistors as per precedent note (1) (See Table 9-1 on page 11).

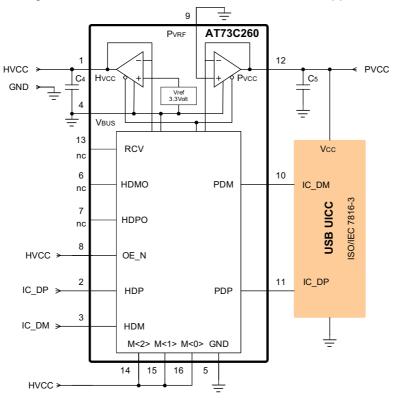

Figure 9-1. AT73C260 Downstream and Upstream Ports

### 9.3 Theory Of Operation

#### 9.3.1 Remote Wake Up

The AT73C260 does not support remote wake up.

#### 9.3.2 Slew Rate Control

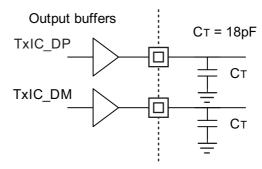

When the AT73C260 drives an IC\_USB bus section the output buffer on each line (Figure 9-2) drives the pin with a slew rate control to minimize radiated EMI.

Figure 9-2. AT73C260 Output Buffer

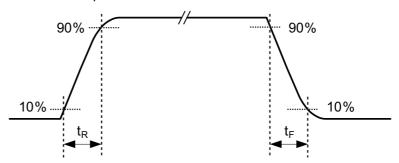

Figure 9-3. AT73C260 Output Buffer Slew Rate

Note: See Table 7-3 on page 7 for timing values.

#### 9.3.3 Attach

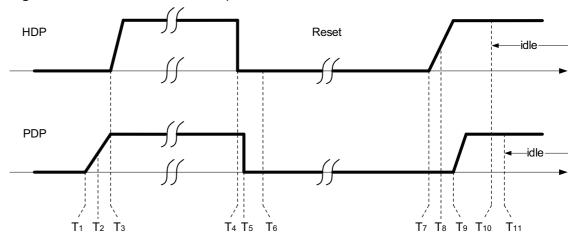

Figure 9-4. AT73C260 Attach Sequence

In the following paragraphs, two different attach sequences are described according the mode selected. Mode VCC and Mode S7\_ICC\_TK are explained.

#### 9.3.3.1 Attach Sequence "Mode VCC"

The following sequence describes the AT73C260 with an IC\_USB upstream connection and an IC\_USB downstream connection (**Mode VCC**). For hardware connection refers to "Mode: Voltage Class Converter: VCC" on page 34.

- H<sub>VCC</sub> and P<sub>VCC</sub> are present and are in their dedicated voltage range.

- R<sub>PU1</sub> is not used (SW1 always open). (For more information about switches, refers to Figure 9-1 on page 12)

- Before T<sub>1</sub>, R<sub>PDP</sub> and R<sub>PDH</sub> are connected. R<sub>PU2</sub> is disconnected. (For more information about resistors, refers to Figure 9-1 on page 12)

- T<sub>1</sub>: Peripheral event.

Beyond T<sub>1</sub>, PDP is driven high by the IC\_USB peripheral's pull-up resistor.

- T<sub>2</sub>: AT73C260 event.

The signal is above  $V_{IH}$ . The AT73C260 verifies that the condition PDP is high lasts more than 200ns nominal. This information is passed to the AT73C260's Host side.

• **T**<sub>3</sub>: AT73C260 event.

Beyond T<sub>3</sub>, R<sub>PU2</sub> (2k nominal) is connected while R<sub>PDP</sub> on HDP is disconnected.

• T₄: Host event.

From T<sub>4</sub> the host drives the reset with SE0.

• T<sub>5</sub>: AT73C260 event.

It takes 40 ns nominal beyond T<sub>4</sub> for PDP to be driven low.

• **T**<sub>6</sub>: AT73C260 event.

During reset the AT73C260 detects a SE0 for more than  $1\mu s$  nominal. Beyond  $T_6$  both  $R_{PDH}$  are disconnected.

14

• T7: Host event.

Host stops driving SE0. The AT73C260 with its 2k nominal resistor, pulls-up HDP.

• T<sub>8</sub>: AT73C260 event.

The signal is above V<sub>IH</sub>.(on HDP)

• **T**<sub>9</sub>: AT73C260 event.

40ns nominal after  $T_8$ . From  $T_9$ , the AT73C260 drives high until  $V_{IH}$  (on PDP) is reached plus 100ns nominal until  $T_{11}$ .

• T<sub>10</sub>: AT73C260 event.

Between  $T_7$  and  $T_{10}$ . HDP is pulled-up with 2k nominal until  $V_{IH}$  (on HDP) is reached plus 100ns. At  $T_{10}$  R<sub>PU2</sub> becomes 50k nominal.

#### 9.3.3.2 Attach Sequence Mode S7\_ICC\_TK

The following sequence describes the AT73C260 with an USB2.0 section 7 upstream connection and an IC\_USB downstream connection (**Mode S7\_ICC\_TK**). For hardware connection refers to "Mode: USB2.0 section 7 to IC\_USB1.0 with PVCC fixed by PVRF: S7\_ICC\_TK" on page 38.

- $H_{VCC}$  = 3.3V and  $P_{VCC}$  are present and are in their dedicated voltage range.

- R<sub>PU2</sub> is not used (SW2 always open). R<sub>PDP</sub> are not used (SW3 and SW4 always open). (For more information about switches, refers to Figure 9-1 on page 12)

- Before T<sub>1</sub>, R<sub>PDH</sub> are connected. R<sub>PU2</sub> is disconnected. (For more information about resistors, refers to Figure 9-1 on page 12)

- T<sub>1</sub>: Peripheral event.

Beyond T<sub>1</sub>, PDP is driven high by the IC\_USB peripheral's pull-up resistor.

• T2: AT73C260 event.

The signal is above  $V_{IH}$ . The AT73C260 verifies that the condition PDP is high lasts more than 200ns nominal. This information is passed to the AT73C260's Host side.

• T<sub>3</sub>: AT73C260 event.

Beyond T<sub>3</sub>, R<sub>PU1</sub> 1.2k nominal, is connected.

• T4: Host event.

From  $T_4$  the host drives the reset with SE0.

• T<sub>5</sub>: AT73C260 event.

$R_{PU1}$  becomes 2.2k nominal. It takes 40 ns nominal beyond  $T_4$  for PDP to be driven low.

• T<sub>6</sub>: AT73C260 event.

During reset the AT73C260 detects a SE0 for more than  $1\mu s$  nominal. Beyond  $T_6$  both  $R_{PDH}$  are disconnected.

• T<sub>7</sub>: Host event.

Host stops driving SE0. The AT73C260 with its 2k nominal resistor, pulls-up HDP.

• T<sub>8</sub>: AT73C260 event.

The signal is above V<sub>IH</sub>.(on HDP)

• T<sub>9</sub>: AT73C260 event.

40ns nominal after  $T_8$ . From  $T_9$ , the AT73C260 drives high until  $V_{IH}$  (on PDP) is reached plus 100ns nominal until  $T_{11}$ .

• **T**<sub>10</sub>: AT73C260 event.

Between  $T_7$  and  $T_{10}$ . HDP is pulled-up with 2.2k nominal until  $V_{IH}$  (on HDP) is reached plus 100ns. At  $T_{10}$   $R_{PU1}$  becomes 1.2k nominal.

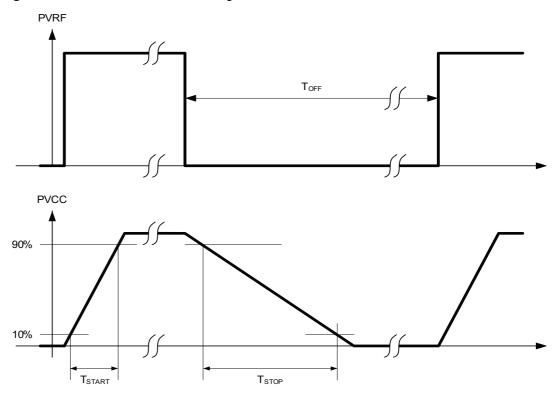

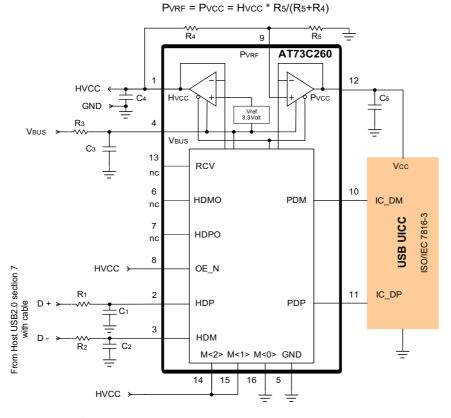

#### 9.3.4 PVRF Driving PVCC

Figure 9-5. AT73C260 PVRF driving PVCC

When  $V_{BUS}$ , pin 4, is providing power to the USB UICC via the LDOs, the voltage on  $P_{VCC}$  (pin 12) is following the voltage on  $P_{VRF}$  (pin 9).

T<sub>START</sub> is mostly related to the capacitive load on P<sub>VCC</sub> and the strength of the LDO's PMOS.

T<sub>START</sub> as mentioned in Table 7-8 on page 9 is less than 50μs.

T<sub>STOP</sub> is mostly related to the load on P<sub>VCC</sub> since the LDO's PMOS is off when starts T<sub>OFF</sub>.

Certain applications may require  $P_{VCC}$  to fall below a minimum voltage in less than  $T_{OFF}$  and guarantee a Power On Reset sequence in the USB UICC when  $P_{VCC}$  is set again. For these applications an extra load, such as a resistor across  $P_{VCC}$  and GND in parallel with the USB UICC and the decoupling capacitor C5 may be required.

As an example, for  $T_{OFF} = 0.4$ ms, a decoupling capacitor C5 of 220nF and an USB UICC in standby (less than 100µA) the extra resistor shall be less than 1k $\Omega$ .

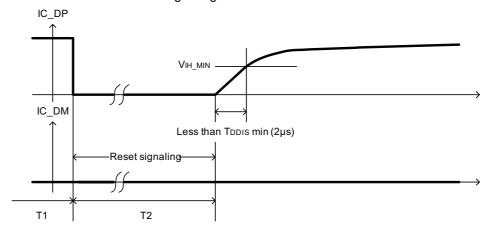

#### 9.3.5 Reset Signaling

At the end of the Reset signaling on AT73C260's host side and peripheral sides the pulled up data line voltage has to reach  $V_{\text{IH\_MIN}}$  in less than  $T_{\text{DDIS}}$ , see Figure 9-6. If it is not the case, the host may see a disconnect condition.

Reset is forced during T2.

If a  $100 \text{k}\Omega$  pull up resistor is used while the capacitive load is more than 20 pF, the time constant is greater than 2 µs. To avoid any disconnect condition, the AT73C260 pulls up the appropriate data line during about one bit duration with extra strength making the disconnect condition unlikely.

Figure 9-6. AT73C260 Reset Signaling

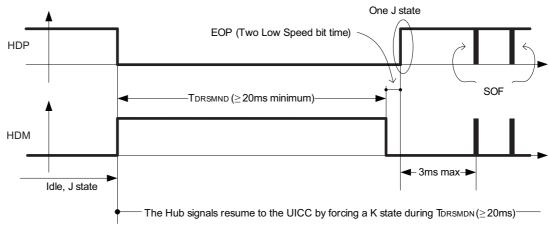

#### 9.3.6 Resume Signaling

The AT73C260 supports resume signaling. The timings on IC\_DP and IC\_DM are those on HDP and HDM delayed by 40ns nominal.

Figure 9-7. AT73C260 Resume Signaling

Notes: 1. J state means that HDP = 1 and HDM = 0.

- 2. K state means that HDP = 0 and HDM = 1.

- 3. SOF = Start Of Frame

#### 9.4 **General Description**

The AT73C260 covers four main functions:

- PHY (described in Section 9.4.3 on page 20)

- Bridge (described in Section 9.4.4 on page 30)

- IC\_USB1.0 Voltage Class Converter (described in Section 9.4.5 on page 34)

- Bridge with LDOs for two specific applications (described in Section 9.4.6 on page 36),

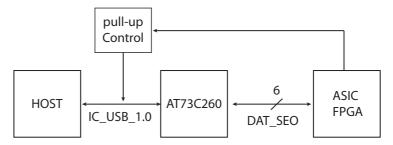

and one extra function from many described as an example where the AT73C260 is an interchip PHY in a digital implementation (FPGA) of a peripheral.

#### 9.4.1 **Application Modes**

The following Table 9-2 lists the applications and pin settings.

**Table 9-2.** AT73C260 Application Modes (4)

| Mode       | Application                                                                               | M<2><br>Pin 14 | M<1><br>Pin 15 | M<0><br>Pin 16 | Function                      |

|------------|-------------------------------------------------------------------------------------------|----------------|----------------|----------------|-------------------------------|

| PHY_6_SE0  | Digital six wires unidirectional DAT_SE0 to IC_USB1.0                                     | 0              | 0              | 0              | PHY                           |

| PHY_4_SE0  | Digital four wires bidirectional DAT_SE0 to IC_USB1.0                                     | 0              | 0              | 1              | PHY                           |

| PHY_6_DPDM | Digital six wires unidirectional DP_DM to IC_USB1.0                                       | 0              | 1              | 0              | PHY                           |

| PHY_4_DPDM | Digital four wires bidirectional DP_DM to IC_USB1.0                                       | 0              | 1              | 1              | PHY                           |

| PHY_3_ULPI | Digital three wires bidirectional (DAT, SE0, OE_N) to IC_USB1.0                           | 1              | 0              | 1              | PHY                           |

| S7_ICC     | USB2.0 section 7 without cable to IC_USB1.0                                               | 1              | 1              | 0              | Bridge                        |

| S7_ICC_DBB | USB2.0 section 7 with cable to IC_USB1.0, LDOs ON VCC driven by the Digital Base Band (2) |                | 1              | 0              | Bridge with LDOs              |

| S7_ICC_TK  | USB2.0 section 7 with cable to IC_USB1.0, LDOs ON VCC fixed by PVRF (3)                   |                | 1              | 0              | Bridge with LDOs              |

| ICC_S7     | IC_USB1.0 to USB2.0 section 7 <sup>(1)</sup>                                              | 1              | 1              | 1              | Bridge                        |

| vcc        | IC_USB1.0 to IC_USB1.0                                                                    | 1              | 1              | 1              | Voltage<br>Class<br>Converter |

- Notes: 1.  $22k\Omega$  Pull down on pins 10 and 11

- 2. PC with Digital Base Band

- 3. Token

- 4. M<2:0> code"100" is not used

#### 9.4.2 Function Descriptions

#### 9.4.2.1 Downstream Port PHY:

A set of digital signals generated by an FPGA or an ASIC with I/O powered by a first power supply drive the AT73C260 which converts these signals into analog signals IC\_DP and IC\_DM as per IC\_USB1.0 powered by a second power supply.

#### 9.4.2.2 Bridge:

Two cases are supported: USB2.0 section 7 to IC\_USB1.0 and IC\_USB1.0 to USB2.0 section 7.

USB2.0 section 7 to IC\_USB1.0

Downstream D+ and D- signals drive the AT73C260 which converts these signals into analog signals IC\_DP and IC\_DM as per IC\_USB1.0.

IC\_USB1.0 to USB2.0 section 7

Downstream IC\_USB1.0 signals drive the AT73C260 which converts these signals into analog signals D+ and D- as per USB2.0 section 7.

#### 9.4.2.3 Voltage Class Converter:

The following applications enable communications between an IC\_USB1.0 compliant down-stream port with a first voltage class  $V_1$  and an IC\_USB1.0 compliant peripheral with a second voltage class  $V_{CC}$ .

The range of the supplies, respectively Host and Device, are:  $H_{VCC}$  (1.55V - 3.6V) and  $P_{VCC}$  (1.55V - 3.6V)

#### 9.4.2.4 Bridge with LDOs:

Two cases are supported: one for PC with embedded Digital Base Band and one for Token.

PC with embedded Digital Base Band

The AT73C260 provides up to 70mA from  $V_{BUS}$  to the UICC under the  $V_{CC}$  required by the DBB.

Also the AT73C260 converts D+ and D- signals into analog signals IC\_DP and IC\_DM as per IC\_USB1.0.

Token

The AT73C260 provides up to 70mA from  $V_{BUS}$  to the UICC under  $V_{CC}$ .

This voltage is generated by  $P_{VCC}$  LDO and set by an external resistor bridge supplied by 3.3V voltage reference ( $H_{VCC}$ ).

Also the AT73C260 converts D+ and D- signals into analog signals IC\_DP and IC\_DM as per IC\_USB1.0.

#### 9.4.3 Downstream Port PHY

In mobile applications, the USB UICC is handled by the user and special care should be taken in the ESD protection on the downstream port facing the USB UICC. The AT73C260 downstream port is protected against 4kV ESD.

Also, the host and the USB UICC may not be located on the same board with a flex connecting the two PCBs. The AT73C260 should be located next to the host. The flex is between the AT73C260's downstream port and the USB UICC upstream port. The AT73C260 downstream port has slew rate control on both  $P_{DM}$  and  $P_{DP}$  to minimize the radiated EMI.

Pins  $V_{BUS}$  and  $P_{VRF}$  are connected to GND and LDO outputs are isolated and in standby.

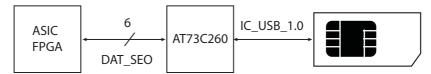

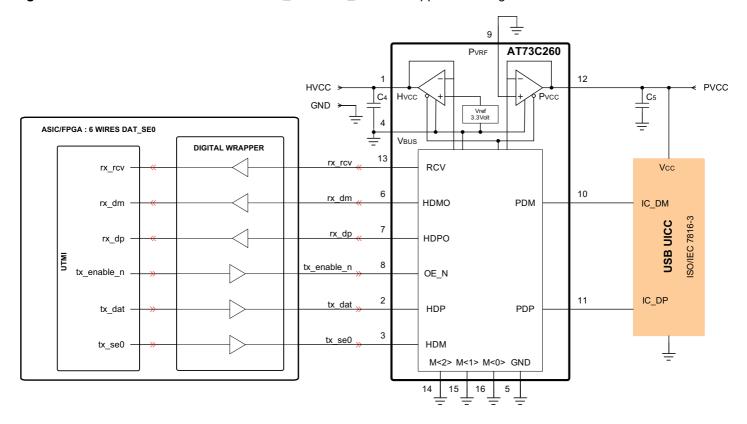

#### 9.4.3.1 Mode: Digital six wires unidirectional DAT\_SE0 to IC\_USB1.0: PHY\_6\_SE0

#### Description

This application allows a Host, ASIC or FPGA, with the digital unidirectional Philips PDIUSBP11A (MODE pin = 0) six wires interface to drive an IC\_USB downstream port.

Figure 9-8. PHY\_6\_SE0 Block Diagram

#### Hardware Configuration

**Table 9-3.** AT73C260 Hardware Configuration

|    | Mode     | M<2><br>Pin 14 | M<1><br>Pin 15 | M<0><br>Pin 16 | Application                                           |

|----|----------|----------------|----------------|----------------|-------------------------------------------------------|

| PI | HY_6_SE0 | 0              | 0              | 0              | Digital six wires unidirectional DAT_SE0 to IC_USB1.0 |

**Table 9-4.** AT73C260 Pin description and configuration

| Pin Number | Pin Name    | I/O Type | Polarity | Function                                     |

|------------|-------------|----------|----------|----------------------------------------------|

| 1          | HVCC        | A-Power  |          | Supply by ASIC FPGA I/O Ring (1.55V to 3.6V) |

| 2          | TX_DAT      | D-Input  |          | Unidirectional Transmit Data                 |

| 3          | TX_SEO      | D-Input  |          | Unidirectional Transmit Single Ended 0       |

| 4          | VBUS        | A-Input  |          | Not Used and Connected to Ground             |

| 6          | RX_DM       | D-Output |          | Unidirectional Receiving DM                  |

| 7          | RX_DP       | D-Output |          | Unidirectional Receiving DP                  |

| 8          | TX_ENABLE_N | D-Input  | Low      | Tx Enable N                                  |

| 9          | PVRF        | A-Input  |          | Connected to Ground                          |

| 10         | PDM         | D-I/O    |          | Downstream Port for USB Device               |

Table 9-4. AT73C260 Pin description and configuration

| Pin Number | Pin Name | I/O Type | Polarity | Function                                        |

|------------|----------|----------|----------|-------------------------------------------------|

| 11         | PDP      | D-I/O    |          | Downstream Port for USB Device                  |

| 12         | PVCC     | A-Power  |          | Same as peripheral's power (1.8V or 3V typical) |

| 13         | RX_RCV   | D-Output |          | Unidirectional Receiving RCV                    |

| 14, 15, 16 | M<2:0>   | D-Inputs | Low      | Connected to Ground                             |

In the following figure, the hardware configuration is described.

Figure 9-9. AT73C260: PHY - 6 wires DAT\_SE0 to IC\_USB1.0 - application diagram

Note: All external components are defined in component list Table 8-1 on page 10

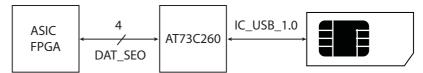

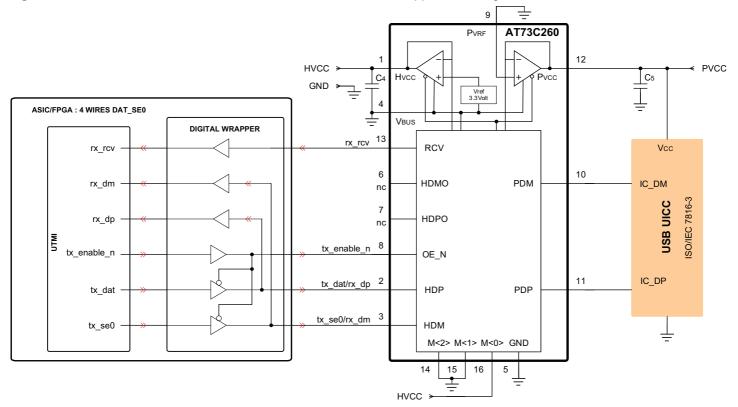

#### 9.4.3.2 Mode: Digital four wires bidirectional DAT\_SE0 to IC\_USB1.0: PHY\_4\_SE0

#### Description

This application allows a Host, ASIC or FPGA, with the digital bidirectional UTMIfs, DAT\_SE0, four wires interface to drive an IC\_USB downstream port.

Figure 9-10. PHY\_4\_SE0 Block Diagram

#### Hardware Configuration

Table 9-5.

AT73C260 Hardware Configuration

| Mode      | M<2><br>Pin 14 | M<1><br>Pin 15 | M<0><br>Pin 16   | Application                                           |

|-----------|----------------|----------------|------------------|-------------------------------------------------------|

| PHY_4_SE0 | 0              | 0              | H <sub>VCC</sub> | Digital four wires bidirectional DAT_SE0 to IC_USB1.0 |

**Table 9-6.** AT73C260 Pin description and configuration

| Pin Number | Pin Name     | I/O Type | Polarity | Function                                        |

|------------|--------------|----------|----------|-------------------------------------------------|

| 1          | HVCC         | A-Power  |          | Supply by ASIC FPGA I/O Ring (1.55V to 3.6V)    |

| 2          | TX_DAT/RX_DP | D-I/O    |          | Bidirectional Rx_Dp/Tx_Data                     |

| 3          | TX_SE0/RX_DM | D-I/O    |          | Bidirectional Rx_DM/Tx_Single Ended 0           |

| 4          | VBUS         | A-Input  |          | Not Used and Connected to Ground                |

| 6          | HDMO         | D-Output | HiZ      | Not Connected                                   |

| 7          | HDPO         | D-Output | HiZ      | Not Connected                                   |

| 8          | TX_ENABLE_N  | D-Input  | Low      | Tx Enable N                                     |

| 9          | PVRF         | A-Input  |          | Connected to Ground                             |

| 10         | PDM          | D-I/O    |          | Downstream Port for USB Device                  |

| 11         | PDP          | D-I/O    |          | Downstream Port for USB Device                  |

| 12         | PVCC         | A-Power  |          | Same as peripheral's power (1.8V or 3V typical) |

| 13         | RX_RCV       | D-Output |          | Unidirectional Receiving RCV                    |

| 14, 15     | M<2:1>       | D-Inputs | Low      | Connected to Ground                             |

| 16         | M<0>         | D-Input  | High     | Connected to H <sub>VCC</sub>                   |

In the following figure, the hardware configuration is described.

Figure 9-11. AT73C260: PHY - 4 wires DAT\_SE0 to IC\_USB1.0 - application diagram

Note: All external components are defined in component list Table 8-1 on page 10

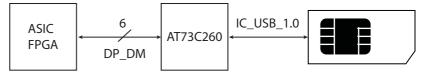

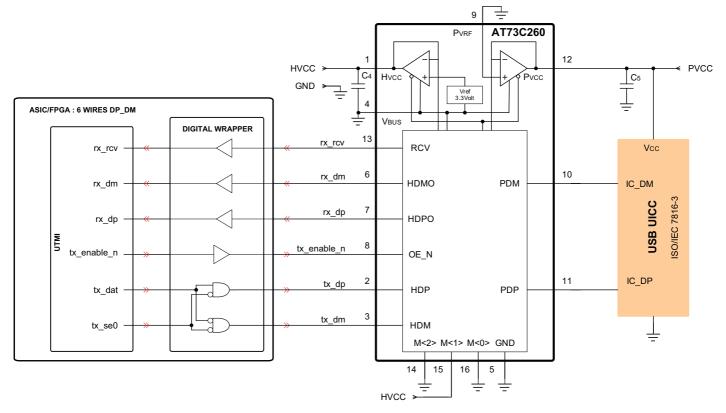

#### 9.4.3.3 Mode: Digital six wires unidirectional DP\_DM to IC\_USB1.0: PHY\_6\_DPDM

#### Description

This application allows a Host, ASIC or FPGA, with the digital unidirectional Philips PDIUSBP11A (MODE pin = 1) six wires interface to drive an IC\_USB downstream port.

Figure 9-12. PHY\_6\_DPDM Block Diagram

#### Hardware Configuration

Table 9-7.

AT73C260 Hardware Configuration

| Мо    | de    | M<2><br>Pin 14 | M<1><br>Pin 15   | M<0><br>Pin 16 | Application                                         |

|-------|-------|----------------|------------------|----------------|-----------------------------------------------------|

| PHY_6 | _DPDM | 0              | H <sub>VCC</sub> | 0              | Digital six wires unidirectional DP_DM to IC_USB1.0 |

**Table 9-8.** AT73C260 Pin description and configuration

| Pin Number | Pin Name    | I/O Type | Polarity | Function                                        |

|------------|-------------|----------|----------|-------------------------------------------------|

| 1          | HVCC        | A-Power  |          | Supply by ASIC FPGA I/O Ring (1.55V to 3.6V)    |

| 2          | TX_DP       | D-Input  |          | Unidirectional Tx DP                            |

| 3          | TX_DM       | D-Input  |          | Unidirectional Tx DM                            |

| 4          | VBUS        | A-Input  |          | Not Used and Connected to Ground                |

| 6          | RX_DM       | D-Output |          | Unidirectional Rx DM                            |

| 7          | RX_DP       | D-Output |          | Unidirectional Rx DP                            |

| 8          | TX_ENABLE_N | D-Input  | Low      | Tx Enable N                                     |

| 9          | PVRF        | A-Input  |          | Connected to Ground                             |

| 10         | PDM         | D-I/O    |          | Downstream Port for USB Device                  |

| 11         | PDP         | D-I/O    |          | Downstream Port for USB Device                  |

| 12         | PVCC        | A-Power  |          | Same as peripheral's power (1.8V or 3V typical) |

| 13         | RX_RCV      | D-Output |          | Unidirectional Receiving RCV                    |

| 14         | M<2>        | D-Input  | Low      | Connected to Ground                             |

| 15         | M<1>        | D-Input  | High     | Connected to H <sub>VCC</sub>                   |

| 16         | M<0>        | D-Input  | Low      | Connected to Ground                             |

In the following figure, the hardware configuration is described.

Figure 9-13. AT73C260: PHY - 6 wires DP\_ DM to IC\_USB1.0 - application diagram

Note: All external components are defined in component list Table 8-1 on page 10

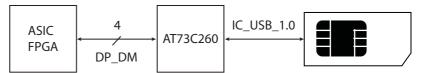

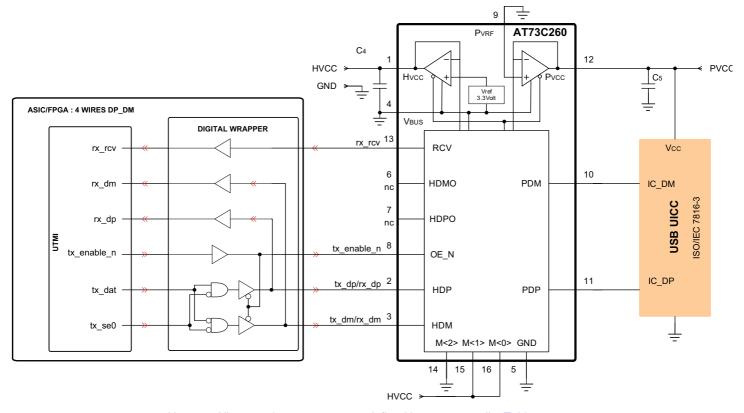

#### 9.4.3.4 Mode: Digital four wires bidirectional DP\_DM to IC\_USB1.0: PHY\_4\_DPDM

#### Description

This application allows a Host, ASIC or FPGA, with the digital bidirectional UTMIfs, DP\_DM, four wires interface to drive an IC\_USB downstream port.

Figure 9-14. PHY\_4\_DPDM Block Diagram

#### Hardware Configuration

**Table 9-9.** AT73C260 Hardware Configuration

| Mode       | M<2><br>Pin 14 | M<1><br>Pin 15   | M<0><br>Pin 16   | Application                                         |

|------------|----------------|------------------|------------------|-----------------------------------------------------|

| PHY_4_DPDM | 0              | H <sub>VCC</sub> | H <sub>VCC</sub> | Digital four wires bidirectional DP_DM to IC_USB1.0 |

**Table 9-10.** AT73C260 Pin description and configuration

| Pin Number | Pin Name    | I/O Type | Polarity | Function                                        |

|------------|-------------|----------|----------|-------------------------------------------------|

| 1          | HVCC        | A-Power  |          | Supply by ASIC FPGA I/O Ring (1.55V to 3.6V)    |

| 2          | TX_DP/RX_DP | D-I/O    | -        | Bidirectional Tx_Dp/Dx_DP                       |

| 3          | TX_DM/RX_DM | D-I/O    |          | Bidirectional Tx_Dm/Dx_DM                       |

| 4          | VBUS        | A-Input  |          | Not Used and Connected to Ground                |

| 6          | HDMO        | D-Output | HiZ      | Not Connected                                   |

| 7          | HDPO        | D-Output | HiZ      | Not Connected                                   |

| 8          | TX_ENABLE_N | D-Input  | Low      | Tx Enable N                                     |

| 9          | PVRF        | A-Input  |          | Connected to Ground                             |

| 10         | PDM         | D-I/O    |          | Downstream Port for USB Device                  |

| 11         | PDP         | D-I/O    |          | Downstream Port for USB Device                  |

| 12         | PVCC        | A-Power  |          | Same as peripheral's power (1.8V or 3V typical) |

| 13         | RX_RCV      | D-Output |          | Unidirectional Receiving RCV                    |

| 14         | M<2>        | D-Input  | Low      | Connected to Ground                             |

| 15,16      | M<1:0>      | D-Inputs | High     | Connected to H <sub>VCC</sub>                   |

In the following figure, the hardware configuration is described.

Figure 9-15. AT73C260: PHY - 4 wires DP\_ DM to IC\_USB1.0 - application diagram

Note: All external components are defined in component list Table 8-1 on page 10

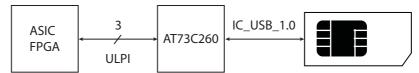

#### 9.4.3.5 Mode: Digital three wires bidirectional (DAT, SE0, OE\_N) to IC\_USB1.0: PHY\_3\_ULPI

#### Description

This application allows a Host, ASIC or FPGA, with the digital bidirectional ULPI serial support, DAT, SE0, and OE\_N, three wires interface to drive an IC\_USB downstream port.

Figure 9-16. PHY\_3\_ULPI Block Diagram

#### Hardware Configuration

Table 9-11.

AT73C260 Hardware Configuration

| Mode       | M<2><br>Pin 14   | M<1><br>Pin 15 | M<0><br>Pin 16   | Application                                                   |

|------------|------------------|----------------|------------------|---------------------------------------------------------------|

| PHY_3_ULPI | H <sub>VCC</sub> | 0              | H <sub>VCC</sub> | Digital three wires bidirectional DAT, SE0, OE_N to IC_USB1.0 |

**Table 9-12.** AT73C260 Pin description and configuration

| Pin Number | Pin Name      | I/O Type | Polarity | Function                                        |

|------------|---------------|----------|----------|-------------------------------------------------|

| 1          | HVCC          | A-Power  |          | Supply by ASIC FPGA I/O Ring (1.55V to 3.6V)    |

| 2          | RX_RCV/TX_DAT | D-I/O    |          | Bidirectional Rx_RCV / Tx_Data                  |

| 3          | RX_SE0/TX_SE0 | D-I/O    |          | Bidirectional Rx_SE0/Tx_SE0                     |

| 4          | VBUS          | A-Input  |          | Not Used and Connected to Ground                |

| 6          | HDMO          | D-Output | HiZ      | Not Connected                                   |

| 7          | HDPO          | D-Output | HiZ      | Not Connected                                   |

| 8          | TX_ENABLE_N   | D-Input  | Low      | Tx Enable N                                     |

| 9          | PVRF          | A-Input  |          | Connected to Ground                             |

| 10         | PDM           | D-I/O    |          | Downstream Port for USB Device                  |

| 11         | PDP           | D-I/O    |          | Downstream Port for USB Device                  |

| 12         | PVCC          | A-Power  |          | Same as peripheral's power (1.8V or 3V typical) |

| 13         | RCV           | D-Output | HiZ      | Not Connected                                   |

| 14         | M<2>          | D-Input  | High     | Connected to H <sub>VCC</sub>                   |

| 15         | M<1>          | D-Inputs | Low      | Connected to Ground                             |

| 16         | M<0>          | D-Inputs | High     | Connected to H <sub>VCC</sub>                   |

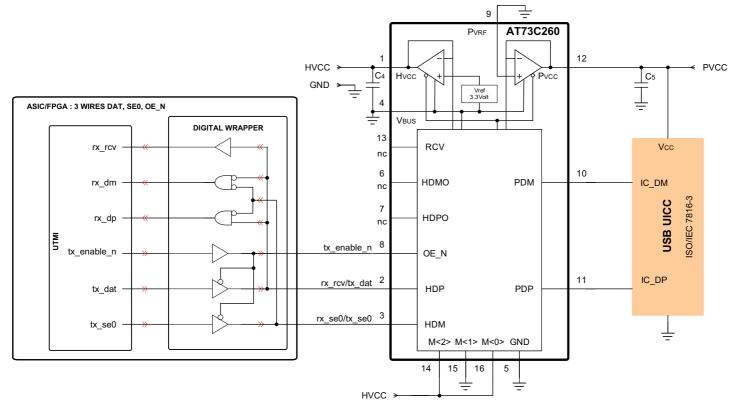

In the following figure, the hardware configuration is described.

Figure 9-17. AT73C260: PHY - 3 wires DAT, SE0, OE\_N to IC\_USB1.0 - application diagram

Note: All external components are defined in component list Table 8-1 on page 10

#### 9.4.4 Bridge

Pins  $V_{BUS}$  and  $P_{VRF}$  are connected to GND and LDO outputs are isolated and in standby.

Pin OE\_N is connected to H<sub>VCC</sub>.

The following applications enable communications between.

- **S7\_ICC**: an USB2.0 section 7 compliant downstream port and an IC\_USB1.0 compliant peripheral

- ICC\_S7: an IC\_USB1.0 compliant downstream port and an USB2.0 section 7 compliant peripheral

#### 9.4.4.1 Mode: USB2.0 section 7 downstream port to IC\_USB1.0 peripheral: S7\_ICC

#### Description

This application establishes a communication path between an USB2.0 section 7 downstream port and an IC\_USB peripheral.

An external 3.3V voltage source is applied on  $H_{VCC}$ . AT73C260's D+ and D- input pins are compliant with USB2.0 core specification.

This application is particularly well suited for mobile devices where the host may not have an IC\_USB1.0 downstream port.

Figure 9-18. S7\_ICC Block Diagram

#### Hardware Configuration

Table 9-13. AT73C260 Hardware Configuration

| Mode   | M<2><br>Pin 14   | M<1><br>Pin 15   | M<0><br>Pin 16 | Application                                              |

|--------|------------------|------------------|----------------|----------------------------------------------------------|

| S7_ICC | H <sub>VCC</sub> | H <sub>VCC</sub> | 0              | USB2.0 section 7 downstream port to IC_USB1.0 peripheral |

**Table 9-14.** AT73C260 Pin description and configuration

| Pin Number | Pin Name | I/O Type | Polarity | Function                         |

|------------|----------|----------|----------|----------------------------------|

| 1          | HVCC     | A-Power  |          | Supplied by host at 3.3V         |

| 2          | D+       | D-I/O    |          | Bidirectional D+                 |

| 3          | D-       | D-I/O    |          | Bidirectional D-                 |

| 4          | VBUS     | A-Input  |          | Not Used and Connected to Ground |

| 6          | HDMO     | D-Output | HiZ      | Not Connected                    |

| 7          | HDPO     | D-Output | HiZ      | Not Connected                    |

| 8          | OE_N     | D-Input  | High     | Connected to H <sub>VCC</sub>    |

| <b>Table 9-14.</b> AT73C260 Pin description and configurat |

|------------------------------------------------------------|

|------------------------------------------------------------|

| Pin Number | Pin Name | I/O Type | Polarity | Function                                        |

|------------|----------|----------|----------|-------------------------------------------------|

| 9          | PVRF     | A-Input  |          | Connected to Ground                             |

| 10         | PDM      | D-I/O    |          | Downstream Port for USB Device                  |

| 11         | PDP      | D-I/O    |          | Downstream Port for USB Device                  |

| 12         | PVCC     | A-Power  |          | Same as peripheral's power (1.8V or 3V typical) |

| 13         | RCV      | D-Output | HiZ      | Not Connected                                   |

| 14         | M<2>     | D-Input  | High     | Connected to H <sub>VCC</sub>                   |

| 15         | M<1>     | D-Inputs | High     | Connected to H <sub>VCC</sub>                   |

| 16         | M<0>     | D-Inputs | Low      | Connected to Ground                             |

In the following figure, the hardware configuration is described.

Figure 9-19. AT73C260: Bridge - USB2.0 section 7 downstream port to IC\_USB1.0 -application diagram

Note: All external components are defined in component list Table 8-1 on page 10

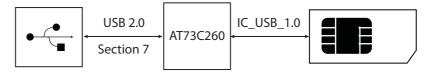

#### 9.4.4.2 Mode: IC\_USB1.0 downstream port to USB2.0 section 7 peripheral: ICC\_S7

#### Description

This application establishes a communication path between an IC\_USB1.0 downstream port and an USB2.0 section 7 peripheral.

Figure 9-20. ICC\_S7 Block Diagram

#### Hardware Configuration

Table 9-15.

AT73C260 Hardware Configuration

| Mode   | M<2><br>Pin 14   | M<1><br>Pin 15   | M<0><br>Pin 16   | Application                                              |

|--------|------------------|------------------|------------------|----------------------------------------------------------|

| ICC_S7 | H <sub>VCC</sub> | H <sub>VCC</sub> | H <sub>VCC</sub> | IC_USB1.0 downstream port to USB2.0 section 7 peripheral |

**Table 9-16.** AT73C260 Pin description and configuration

| Pin Number | Pin Name | I/O Type | Polarity | Function                                         |

|------------|----------|----------|----------|--------------------------------------------------|

| 1          | HVCC     | A-Power  |          | Same as host I/O Ring Power (1.8V to 3V typical) |

| 2          | IC_DP    | D-I/O    |          | Bidirectional IC_DP                              |

| 3          | IC_DM    | D-I/O    |          | Bidirectional IC_DM                              |

| 4          | VBUS     | A-Input  |          | Not Used and Connected to Ground                 |

| 6          | HDMO     | D-Output | HiZ      | Not Connected                                    |

| 7          | HDPO     | D-Output | HiZ      | Not Connected                                    |

| 8          | OE_N     | D-Input  | High     | Connected to H <sub>VCC</sub>                    |

| 9          | PVRF     | A-Input  |          | Connected to Ground                              |

| 10         | D-       | D-I/O    |          | Downstream Port for USB Device                   |

| 11         | D+       | D-I/O    |          | Downstream Port for USB Device                   |

| 12         | PVCC     | A-Power  |          | Supplied at 3.3V                                 |

| 13         | RCV      | D-Output | HiZ      | Not Connected                                    |

| 14         | M<2>     | D-Input  | High     | Connected to H <sub>VCC</sub>                    |

| 15         | M<1>     | D-Inputs | High     | Connected to H <sub>VCC</sub>                    |

| 16         | M<0>     | D-Inputs | High     | Connected to H <sub>VCC</sub>                    |

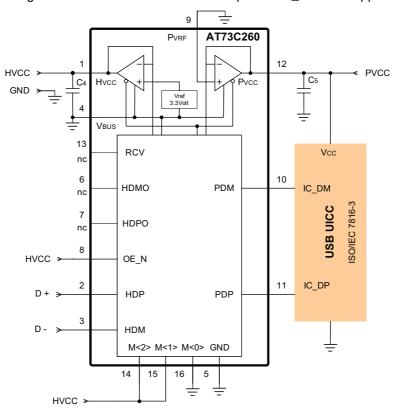

In the following figure, the hardware configuration is described.

Figure 9-21. AT73C260: Bridge - IC\_USB1.0 downstream port to USB2.0 section 7 - application diagram

Note: R<sub>6</sub> and R<sub>7</sub> are defined in component list Table 8-1 on page 10

#### 9.4.5 Mode: Voltage Class Converter: VCC

#### Description

Pins  $V_{BUS}$  and  $P_{VRF}$  are connected to GND and LDO outputs are isolated and in standby.

Pin OE\_N is connected to H<sub>VCC</sub>.

The following applications enable communications between an IC\_USB1.0 compliant downstream port with a first voltage class  $H_{VCC}$  and an IC\_USB1.0 compliant peripheral with a second voltage class  $P_{VCC}$ .

Figure 9-22. Voltage Class Converter Block Diagram

#### Hardware Configuration

**Table 9-17.** AT73C260 Hardware Configuration

|      | M<2>             | M<1>             | M<0>             |                                                |

|------|------------------|------------------|------------------|------------------------------------------------|

| Mode | Pin 14           | Pin 15           | Pin 16           | Application                                    |

| VCC  | H <sub>VCC</sub> | H <sub>VCC</sub> | H <sub>VCC</sub> | IC_USB1.0 to IC_USB1.0 Voltage Class Converter |

**Table 9-18.** AT73C260 Pin description and configuration

| Pin Number | Pin Name | I/O Type | Polarity | Function                                         |

|------------|----------|----------|----------|--------------------------------------------------|

| 1          | HVCC     | A-Power  |          | Same as host I/O Ring Power (1.8V to 3V typical) |

| 2          | IC_DP    | D-I/O    |          | Bidirectional IC_DP                              |

| 3          | IC_DM    | D-I/O    |          | Bidirectional IC_DM                              |

| 4          | VBUS     | A-Input  |          | Connected to Ground                              |

| 6          | HDMO     | D-Output | HiZ      | Not Connected                                    |

| 7          | HDPO     | D-Output | HiZ      | Not Connected                                    |

| 8          | OE_N     | D-Input  | High     | Connected to H <sub>VCC</sub>                    |

| 9          | PVRF     | A-Input  |          | Connected to Ground                              |

| 10         | PDM      | D-I/O    |          | Downstream Port for USB Device                   |

| 11         | PDP      | D-I/O    |          | Downstream Port for USB Device                   |

| 12         | PVCC     | A-Power  |          | Same as peripheral's power (1.8V or 3V typical)  |

| 13         | RCV      | D-Output | HiZ      | Not Connected                                    |

| 14         | M<2>     | D-Input  | High     | Connected to H <sub>VCC</sub>                    |

| 15         | M<1>     | D-Inputs | High     | Connected to H <sub>VCC</sub>                    |

| 16         | M<0>     | D-Inputs | High     | Connected to H <sub>VCC</sub>                    |

In the following figure, the hardware configuration is described.

Figure 9-23. AT73C260: Voltage Class Converter - IC\_USB1.0 to IC\_USB1.0 - application diagram

Note: All external components are defined in component list Table 8-1 on page 10

#### 9.4.6 Bridge With LDOs

LDOs are enabled.

AT73C260's pin  $V_{BUS}$  is connected to the USB signal  $V_{BUS}$  through a low pass filter.

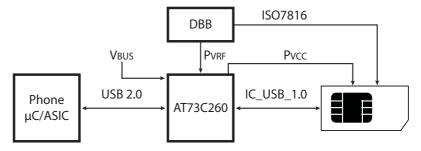

## 9.4.6.1 Mode: PC's USB2.0 section 7 to IC\_USB1.0 with VCC driven by the DBB: S7\_ICC\_DBB

#### Description

The PC's Digital Base Band may not provide enough power to a USB UICC with mass storage.

The  $V_{BUS}$  power supply voltage will make available that extra power, up to 70mA, through the AT73C260's LDO if needed by the USB UICC.

The PC's Digital Base Band supplies on pin 9 the power sequence required by ETSI. The AT73C260 buffers the signal on  $P_{VRF}$  to  $P_{VCC}$ .  $P_{VCC}$  sources power from  $V_{BUS}$  to  $V_{CC}$ .

On the Host side  $H_{\text{VCC}}$  generates 3.3V from  $V_{\text{BUS}}.$

Figure 9-24. S7\_ICC\_DBB Block Diagram

#### Hardware Configuration

**Table 9-19.** AT73C260 Hardware Configuration

| Mode       | M<2><br>Pin 14   | M<1><br>Pin 15   | M<0><br>Pin 16 | Application                                                           |

|------------|------------------|------------------|----------------|-----------------------------------------------------------------------|

| S7_ICC_DBB | H <sub>VCC</sub> | H <sub>VCC</sub> | 0              | PC's USB2.0 section 7 to IC_USB1.0 with V <sub>CC</sub> driven by DBB |

Table 9-20. AT73C260 Pin description and configuration

| Pin Number | Pin Name | I/O Type | Polarity | Function                                |

|------------|----------|----------|----------|-----------------------------------------|

| 1          | HVCC     | A-Output |          | Delivered by AT73C260 from VBUS at 3.3V |

| 2          | D+       | D-I/O    |          | Bidirectional D +                       |

| 3          | D-       | D-I/O    |          | Bidirectional D -                       |

| 4          | VBUS     | A-Input  |          | Supplied by USB Power Line              |

| 6          | HDMO     | D-Output | HiZ      | Not Connected                           |

| 7          | HDPO     | D-Output | HiZ      | Not Connected                           |

| 8          | OE_N     | D-Input  | High     | Connected to H <sub>VCC</sub>           |

| 9          | PVRF     | A-Input  |          | Control by Digital Base Band            |

| Table 9-20. | AT73C260 Pin description and configuration |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Pin Number | Pin Name | I/O Type | Polarity | Function                                           |

|------------|----------|----------|----------|----------------------------------------------------|