## ISL55141, ISL55142, ISL55143

High-Speed 18V CMOS Comparators

FN6230 Rev 4.00 August 13, 2015

ISL55141, ISL55142, ISL55143 integrated circuits are high-speed, wide input common-mode range comparators. They provide three-state window comparators in a high voltage CMOS process (18V). Each comparator has dual receive thresholds,  $\text{CV}_{\text{A}}$  and  $\text{CV}_{\text{B}}$ , for establishing minimum 1-V $_{\text{IH}}$  and maximum 0-V $_{\text{IL}}$  voltage levels. These devices can accept inputs from a number of logic families, such as TTL, ECL, CMOS, LVCMOS, LVDS and CML. Two bits of output per comparator provide the test controller with qualification of a comparator input into three states. The two output bits work with a separate user supply to establish  $\text{V}_{\text{OH}}$ ,  $\text{V}_{\text{OL}}$  levels compatibility with the system's controller logic levels.

Fast propagation delay (9.5ns typical at ±50mV overdrive) makes this family compatible with high-speed digital test systems. The 18V range enables the comparator input to operate over a wide input range. Two references per input enable and three state digitalization of input with voltage swings of up to 13V common mode. The operating frequency of these devices is typically 65MHz.

High voltage CMOS process makes these devices ideal for large voltage swing applications, such as special test voltages levels associated with Flash devices or power supervision applications and may avoid the need for test bus isolation relay(s).

#### **Features**

- · 18V I/O Range

- · 65MHz Operation

- · 9.5ns Typical Propagation Delay

- · Programmable Input Thresholds

- · User Defined Comparator OutputLlevels

- · Common-Mode Range Includes Negative Rails

- Small Footprints in QFN Packages

- Power-Down Current <10µA</li>

- · Pb-Free (RoHS compliant)

## **Applications**

- · Burn in ATE

- Low Cost ATE

- · Fast Supervisory Power Control

- Instrumentation

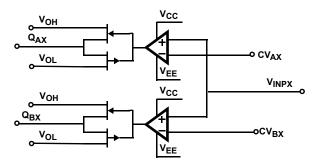

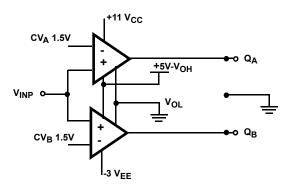

#### **DUAL LEVEL COMPARATOR - RECEIVERS**

Note: x denotes 1, 2 or 4 channels for ISL55141, ISL55142 and ISL55143, respectively

FIGURE 1. FUNCTIONAL BLOCK DIAGRAM

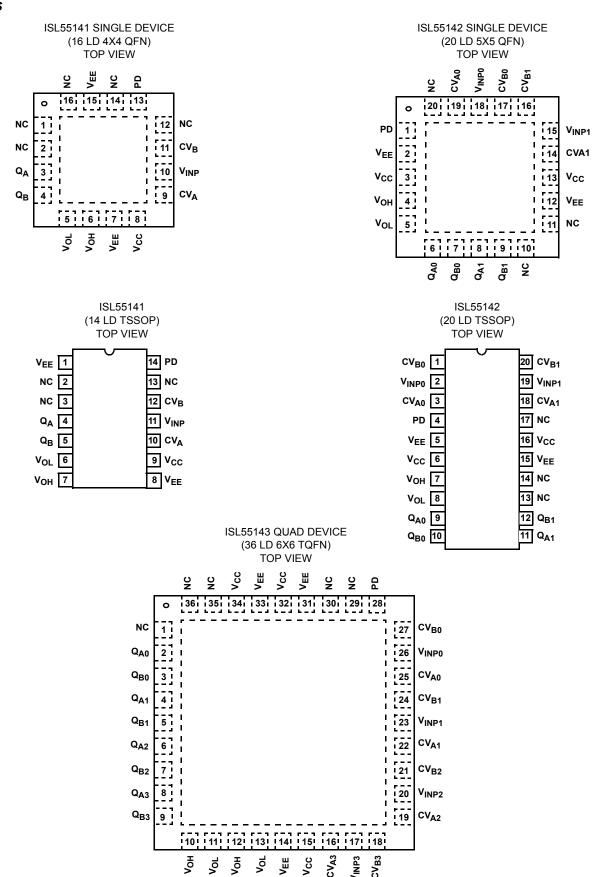

## **Pinouts**

## Pin Descriptions

| PIN               | FUNCTION                                                                                                                           |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>EE</sub>   | Negative supply input                                                                                                              |

| $Q_{AX}$          | Channel A, CV <sub>AX</sub> reference driven. Comparator output.                                                                   |

| $Q_{BX}$          | Channel B, CV <sub>BX</sub> reference driven. Comparator output.                                                                   |

| V <sub>OL</sub>   | Comparator output logic low supply. Unbuffered analog input that sets all Q <sub>AX</sub> , Q <sub>BX</sub> "low" voltage level.   |

| V <sub>OH</sub>   | Comparator output logic high supply. Unbuffered analog input that sets all Q <sub>AX</sub> , Q <sub>BX</sub> "high" voltage level. |

| VCC               | Positive supply input.                                                                                                             |

| CV <sub>AX</sub>  | Channel A comparator reference analog input.                                                                                       |

| V <sub>INPX</sub> | Window comparator input. Common to both Channel Ax and Channel Bx.                                                                 |

| CV <sub>BX</sub>  | Channel B comparator reference analog input.                                                                                       |

| PD                | Power-down logic input (connect to V <sub>EE</sub> if not used for power-down).                                                    |

| NC                | No internal connection.                                                                                                            |

## TABLE 1. $CV_A$ - $Q_A$ AND $CV_B$ - $Q_B$ BASIC COMPARATOR TRUTH TABLE

| INF                                                                               | PUT                 | OUTPUTS*                           |                 |  |  |  |

|-----------------------------------------------------------------------------------|---------------------|------------------------------------|-----------------|--|--|--|

| V <sub>II</sub>                                                                   | NPX                 | Q <sub>AX</sub>                    | Q <sub>BX</sub> |  |  |  |

| <cv<sub>AX</cv<sub>                                                               | <cv<sub>BX</cv<sub> | 0                                  | 0               |  |  |  |

| <cv<sub>AX</cv<sub>                                                               | >CV <sub>BX</sub>   | 0                                  | 1               |  |  |  |

| >CV <sub>AX</sub>                                                                 | <cv<sub>BX</cv<sub> | 1                                  | 0               |  |  |  |

| >CV <sub>AX</sub>                                                                 | >CV <sub>BX</sub>   | 1                                  | 1               |  |  |  |

|                                                                                   | * When C            | AX/QBX = 1, Output is connect to V | ОН              |  |  |  |

| * When Q <sub>AX</sub> /Q <sub>BX</sub> = 0, Output is connect to V <sub>OL</sub> |                     |                                    |                 |  |  |  |

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3)                 | PART MARKING | TEMP. RANGE (°C) | PACKAGE<br>(Pb-Free) | PKG. DWG. # |

|------------------------------------------------|--------------|------------------|----------------------|-------------|

| ISL55141IRZ (No longer available or supported) | 55 141IRZ    | -40 to +85       | 16 Ld QFN            | L16.4X4A    |

| ISL55141IVZ (No longer available or supported) | 55141 IVZ    | -40 to +85       | 14 Ld TSSOP          | M14.173     |

| ISL55142IRZ (No longer available or supported) | 55142 IRZ    | -40 to +85       | 20 Ld QFN            | L20.5x5     |

| ISL55142IVZ (No longer available or supported) | 55142 IVZ    | -40 to +85       | 20 Ld TSSOP          | M20.173     |

| ISL55143IRZ                                    | 55143 IRZ    | -40 to +85       | 36 Ld TQFN           | L36.6X6     |

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil

Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL55141, ISL55142, ISL55143. For more information on MSL please see techbrief TB363.

#### **Absolute Maximum Ratings** Thermal Information Thermal Resistance (Typical, Note 8) $\theta_{JA}$ (°C/W) $\theta_{JC}$ (°C/W) Input Voltages 16 Ld QFN Package (Notes 6, 7)..... 3 $\mathsf{PD},\,\mathsf{CV}_{\mathsf{AX}},\,\mathsf{CV}_{\mathsf{BX}},\,\mathsf{V}_{\mathsf{INPX}},\,\mathsf{V}_{\mathsf{OH}},\,\mathsf{V}_{\mathsf{OL}}$ 14 Ld TSSOP Package (Notes 4, 5) . . 100 31 ..... (V<sub>EE</sub> -0.5V) to (V<sub>CC</sub> +0.5V) 20 Ld QFN Package (Notes 6, 7). . . . . 31 1.4 Output Voltage 20 Ld TSSOP Package (Notes 4, 5) . . 76 25 $Q_{AX}$ , $Q_{BX}$ ..... ( $V_{OL}$ -0.5V) to ( $V_{OH}$ +0.5V) 36 Ld TQFN Package (Notes 6, 7). . . . 29 0.75 Maximum Junction Temperature (Plastic Plackage) . . 150° Maximum Storage Temperature Range . . . . . . . . -65°C to 150°C Pb-Free Reflow Profile. . . . . . . . . . . . . . . . . see link below http://www.intersil.com/pbfree/Pb-FreeReflow.asp

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 5. For  $\theta_{JC}$ , the "case temp" location is taken at the package top center.

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 7. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 8. Device temperature is closely tied to data-rates, driver loads and overall pin activity. Review "Power Dissipation Considerations" on page 6 for more information.

## **Recommended Operating Conditions**

| PARAMETER                       | SYMBOL                           | MIN                  | TYP | MAX                  | UNITS |

|---------------------------------|----------------------------------|----------------------|-----|----------------------|-------|

| Device Power                    | V <sub>CC</sub> -V <sub>EE</sub> | 10                   | 15  | 18                   | V     |

| Comparator Output High Rail     | V <sub>OH</sub>                  | V <sub>EE</sub> +1   |     | V <sub>CC</sub> -0.5 | V     |

| Comparator Output Low Rail      | V <sub>OL</sub>                  | V <sub>EE</sub> +0.5 |     | V <sub>EE</sub> +6   | V     |

| Common Mode Input Voltage Range | V <sub>CM</sub>                  | V <sub>EE</sub>      |     | V <sub>CC</sub> -5   | V     |

| Ambient Temperature             | T <sub>A</sub>                   | -40                  | 27  | +85                  | °C    |

| Junction Temperature            | TJ                               |                      |     | +125                 | °C    |

# **Electrical Specifications** Test Conditions: $V_{CC} = 12V$ , $V_{EE} = -3V$ , $V_{OH} = 5V$ , $V_{OL} = 0V$ , $PD = V_{EE}$ , $C_{LOAD} = 15pF$ , $T_A = 25^{\circ}C$ , unless otherwise specified.

| PARAMETER                   | SYMBOL              | TEST CONDITIONS                                        | MIN<br>(Note 13) | TYP | MAX<br>(Note 13) | UNITS |  |  |

|-----------------------------|---------------------|--------------------------------------------------------|------------------|-----|------------------|-------|--|--|

| DC CHARACTERISTICS          |                     |                                                        |                  |     |                  |       |  |  |

| Input Offset Voltage        | Vos                 | CV <sub>AX</sub> = CV <sub>BX</sub> = 1.5V             | -50              |     | 50               | mV    |  |  |

| Input Bias Current          | I <sub>BIAS</sub>   | $V_{INPX}$ - $CV_{(A/B)X}$ = ±5V                       |                  | 10  | 25               | nA    |  |  |

| Power-down Current          | I <sub>PD</sub>     | PD = V <sub>CC</sub>                                   |                  | 8   | 25               | μΑ    |  |  |

| Power-down Time (Note 11)   | t <sub>PD</sub>     |                                                        |                  | 10  |                  | μs    |  |  |

| Power-up Time (Note 11)     | t <sub>PU</sub>     |                                                        |                  | 15  |                  | μs    |  |  |

| TIMING CHARACTERISTICS      | <u> </u>            |                                                        |                  |     |                  |       |  |  |

| Propagation Delay           | t <sub>pd</sub>     |                                                        | 4.0              | 9.5 | 15               | ns    |  |  |

| Rise Time (Note 11)         | t <sub>r</sub>      |                                                        |                  | 1.4 |                  | ns    |  |  |

| Fall Time (Note 11)         | t <sub>f</sub>      |                                                        |                  | 1.5 |                  | ns    |  |  |

| Propagation Delay Mismatch  | $\Delta t_{\sf pd}$ |                                                        |                  | 0.5 | 2                | ns    |  |  |

| Maximum Operating Frequency | F <sub>MAXR</sub>   | Symmetry 50%                                           |                  | 65  |                  | MHz   |  |  |

| Min Pulse Width             | t <sub>WIDR</sub>   |                                                        |                  | 7.7 |                  | ns    |  |  |

| COMPARATOR INPUT            | COMPARATOR INPUT    |                                                        |                  |     |                  |       |  |  |

| Input Current               | I <sub>IN</sub>     | V <sub>INPX</sub> = V <sub>CC</sub> or V <sub>EE</sub> | -100             | 0   | 100              | nA    |  |  |

# **Electrical Specifications** Test Conditions: V<sub>CC</sub> = 12V, V<sub>EE</sub> = -3V, V<sub>OH</sub> = 5V, V<sub>OL</sub> = 0V, PD = V<sub>EE</sub>, C<sub>LOAD</sub> = 15pF, T<sub>A</sub> = 25°C, unless otherwise specified. **(Continued)**

| PARAMETER                                         | SYMBOL                            | TEST CONDITIONS                                 | MIN<br>(Note 13) | TYP   | MAX<br>(Note 13) | UNITS |  |

|---------------------------------------------------|-----------------------------------|-------------------------------------------------|------------------|-------|------------------|-------|--|

| Input Capacitance (Note 11)                       | C <sub>IN</sub>                   |                                                 |                  | 2.5   |                  | pF    |  |

| DIGITAL OUTPUTS Q <sub>AX</sub> , Q <sub>BX</sub> |                                   |                                                 |                  |       |                  |       |  |

| Output Resistance                                 | RoutR                             |                                                 | 18               | 27    | 37               | Ω     |  |

| Output Logic High Voltage                         | V <sub>OH</sub>                   | V <sub>OH</sub> = 5V, I <sub>SOURCE</sub> = 1mA | 4.9              | 4.95  | 5.0              | V     |  |

| Output Logic Low Voltage                          | V <sub>OL</sub>                   | V <sub>OL</sub> = 0V, I <sub>SINK</sub> = 1mA   | 0.00             | 0.05  | 0.1              | V     |  |

| POWER SUPPLIES, STATIC CONDITION                  | POWER SUPPLIES, STATIC CONDITIONS |                                                 |                  |       |                  |       |  |

| Positive Supply DC Current/Comparator             | Icc                               | No input data                                   |                  | +8.25 | 12.5             | mA    |  |

| Negative Supply Current/Comparator                | I <sub>EE</sub>                   | No input data                                   | -12.5            | -8.25 |                  | mA    |  |

| Total Power Dissipation/Comparator                | P (Note 12)                       | Input data at 40MHz                             |                  | 670   |                  | mW    |  |

#### NOTES:

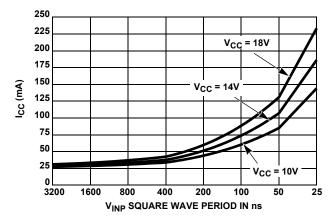

- 9. Lab characterization, room temperature, timing parameters matched stimulus/loads, channel-to-channel skew < 500ps, 1ns maximum by design

- 10. Note about I<sub>CC</sub> measurement input can approach 140mA (single comparator) at maximum pattern rates

- 11. Limits should be considered typical and are not production tested.

- 12. Total Power dissipation per comparator can be approximately calculated from the following:

P = (V<sub>CC</sub>-V<sub>EE</sub>)\*8.25mW + 90pF\*(V<sub>CC</sub>-V<sub>EE</sub>)\*2\*f + C<sub>L</sub>\*(V<sub>CC</sub>-V<sub>EE</sub>)\*2\*f, where f is the operating frequency and C<sub>L</sub> is the load capacitance.

Because the ISL55142 has two comparators, the power dissipation would be twice of P calculated from this equation. The ISL55143 would be four times P

- 13. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

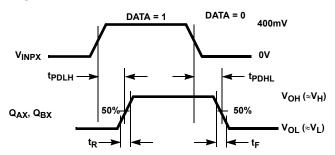

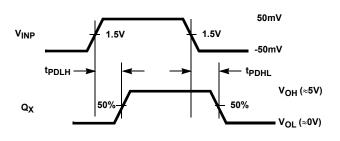

## Test Circuits and Waveforms

FIGURE 2. COMPARATOR PROPAGATION DELAY AND TRANSITION TIME MEASUREMENT POINTS

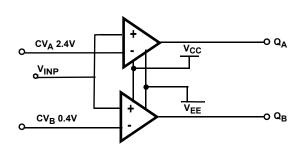

Although there is no electrical difference between the  $\text{CV}_A$  and  $\text{CV}_B$  Inputs, if one defines  $\text{CV}_A$  as being the high threshold and  $\text{CV}_B$  being the low threshold, it becomes easier to understand the utilization of a dual threshold comparator. Essentially this enables the qualification of an incoming signal into three states. In Figure 3, the three states are Valid Low <0.4V, No-man's-land (between 0.4 and 2.4V), Valid High >2.4V. Table 2 shows how the  $\text{Q}_A/\text{Q}_B$  truth table would be utilized in the real world.

TABLE 2. Q<sub>A</sub>/Q<sub>B</sub> TRUTH TABLE

| V <sub>INP</sub> | $Q_A$ | Q <sub>B</sub> | COMMENT |

|------------------|-------|----------------|---------|

| <0.4V            | 0     | 0              | Valid 0 |

| >0.4 and <2.4V   | 0     | 1              | Invalid |

| >2.4V            | 1     | 1              | Valid 1 |

FIGURE 3. THREE-STATE WINDOW COMPARATOR FUNDAMENTALS

## Test Circuits and Waveforms (Continued)

FIGURE 4. tpD RECEIVER SWITCHING TEST CIRCUIT

## Application Information

The ISL55141, ISL55142, ISL55143 provide 1, 2 and 4 dual threshold, three-state window comparator(s) in TSSOP or QFN footprints. They offer a combination of speed (10ns Tpd and wide voltage range (18V). This product directly addresses the need for unique common-mode characteristics while supplying a power-down feature.

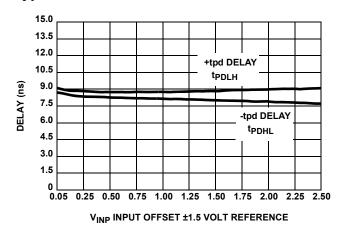

Figures 4 and 5 show the stimulus setup and measurement points for an example propagation delay measurement. Typical room temperature results are displayed in Figure 12.

Figure 5 shows a  $V_{\mbox{\footnotesize{INP}}}$  range of 50mV. In Figure 12 the offset is increased in the horizontal axis from 50mV above and below the reference (1.5V) up to 2.5V above and below the 1.5V reference.

Two lines are displayed in Figure 12. One represents the rising-to-rising delay ( $t_{PDLH}$ ) and the other the falling-to-falling delay ( $t_{PDHL}$ ).

#### Comparator Features

These three-state window comparators feature high output current capability, and user defined high and low output levels to interface with a wide variety of logic families. Each receiver comprises two comparators and each comparator has an independent threshold level input, making it easy to implement (Minimum1-V $_{IH}$ )/(Maximum 0-V $_{IL}$ ) logic level comparator functions. The CV $_{AX}$  and CV $_{BX}$  pins set the threshold levels of the A and B comparators respectively. V $_{OH}$  and V $_{OL}$  set all the comparator output levels, and V $_{OH}$  must be more positive than V $_{OL}$ . These two inputs are unbuffered supply pins, so the sources driving these pins must provide adequate current for the expected load. V $_{OH}$  and V $_{OL}$  typically connect to the power supplies of the logic device driven by the comparator outputs.

FIGURE 5. tpD RECEIVER PROPAGATION DELAY MEASUREMENT POINTS

The truth table for the receivers is given in Table 1. Receiver outputs are not tri-statable, and do not incorporate any on-chip short circuit current protection. Momentary short circuits to GND, or any supply voltage, will not cause permanent damage, but care must be taken to avoid longer duration short circuits. If tolerable to the application, current limiting resistors can be inserted in series with the  $Q_{AX}$  and  $Q_{BX}$  outputs to protect the receiver outputs from damage due to overcurrent conditions.

#### Power-down Features

The ISL55141, ISL55142, ISL55143 PD pin provides a means of reducing current consumption when the device is not in use. Supply currents fall from ~7mA to less than 10µA in the power-down mode. The device requires approximately 10µs to power-down and 15µs to power-up.

# Power Supply Bypassing and Printed Circuit Board Layout

As with any high frequency device, good printed circuit board layout is necessary for optimum performance. Ground plane construction is highly recommended, lead lengths should be as short as possible, and the power supply pins must be well bypassed to reduce the risk of oscillation. For normal single supply operation, where the  $V_{EE}$  pin is connected to ground, one  $0.1\mu F$  ceramic capacitor should be placed from the  $V_{CC}$  pin to ground. A  $4.7\mu F$  tantalum capacitor should then be connected from the  $V_{CC}$  pin to ground. This same capacitor combination should be placed at each supply pin to ground if split supplies are to be used.

#### **Power Dissipation Considerations**

Specifying continuous data rates, driver loads and driver level amplitudes are key in determining power supply requirements as well as dissipation/cooling necessities. Driver output patterns also impact these needs. The faster the pin activity, the greater the need to supply current and remove heat.

The maximum power dissipation allowed in a package is determined according to Equation 1.

$$P_{DMAX} = \frac{T_{JMAX} - T_{AMAX}}{\Theta_{JA}}$$

(EQ. 1)

#### where:

- T<sub>JMAX</sub> = Maximum junction temperature

- T<sub>AMAX</sub> = Maximum ambient temperature

- $\theta_{JA}$  = Thermal resistance of the package

- P<sub>DMAX</sub> = Maximum power dissipation in the package

## Approximate Power Dissipation

(Typ)  $P = N^*[(V_{CC}-V_{EE})^*8.25mW + 90pF^*(V_{CC}-V_{EE})^*2^*f + CL^*(V_{OH}-V_{OL})^*2^*f]$

#### where:

N is the number of comparators in the chip (1 for ISL55141, 2 for ISL55142 and 4 for ISL55143). (f) is the operating frequency. CL is the load capacitor.

The power dissipation calculated from the above formula may have an error of ±20 to 25%.

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the loads. Power also depends on the number of channels changing state and frequency of operation. The extent of continuous active pattern generation/reception will greatly affect dissipation requirements.

The user should evaluate various heat sink/cooling options in order to control the ambient temperature part of the equation. This is especially true if the user's applications require continuous, high-speed operation.

Note: The reader is cautioned against assuming the same level of thermal performance in actual applications. A careful inspection of conditions in your application should be conducted.

### **Power Supply Information**

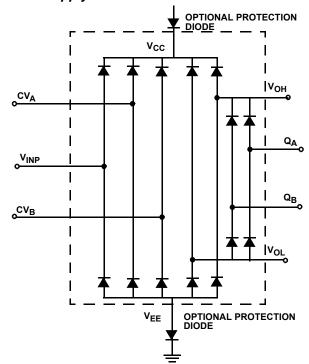

Circuit design must always take into account the internal EOS/ESD protection structure of the device.

**Important Note:** The QFN package metal plane is used for heat sinking of the device. It is electrically connected to the negative supply potential (VEE). If VEE is tied to ground, the thermal pad can be connected to ground. Otherwise, the thermal pad (VEE) must be isolated from other power planes.

#### **Power Supply Sequencing**

The ISL55141, ISL55142, ISL55143 reference every supply with respect to V<sub>EE</sub>. Therefore, apply V<sub>EE</sub>, V<sub>OL</sub> then V<sub>CC</sub> followed by the CV<sub>A</sub> and CV<sub>B</sub> supplies. The comparator V<sub>INP</sub> pin should not exceed V<sub>EE</sub> or V<sub>CC</sub> during power-up.

In cases where inputs may exceed voltage rails during power-up, series resistance should be employed to safeguard EOS to the ESD protection diodes.

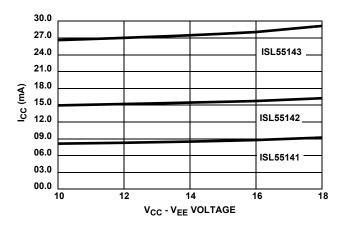

# Typical Performance Curves Device installed on Intersil ISL55141, ISL55142, ISL55143 Evaluation Boards.

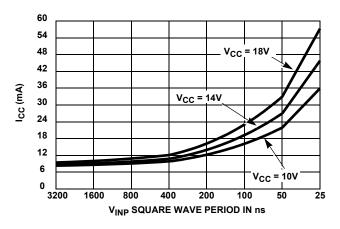

FIGURE 6. ISL55141, ISL55142, ISL55143 QUIESCENT CURRENT

FIGURE 7. ISL55141 I<sub>CC</sub> vs FREQUENCY @ 10V, 14V, AND 18V

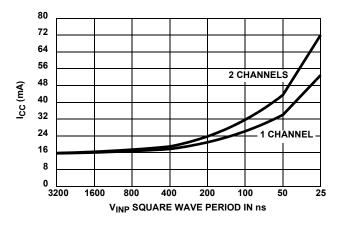

FIGURE 8. ISL55142 I<sub>CC</sub> 1 AND 2 CHANNELS ACTIVE

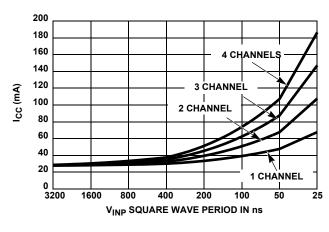

FIGURE 9. ISL55143 I<sub>CC</sub> 1, 2, 3, 4 CHANNELS ACTIVE

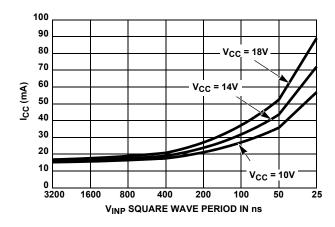

FIGURE 10. ISL55142 2-CHANNEL I<sub>CC</sub> @ 10V, 14V, AND 18V

FIGURE 11. ISL55143 4-CHANNEL I<sub>CC</sub> @ 10V, 14V, AND 18V

## Typical Performance Curves Device installed on Intersil ISL55141, ISL55142, ISL55143 Evaluation Boards. (Continued)

V<sub>CC</sub> 15.0 V<sub>EE</sub> -3.0

FIGURE 12. PROPAGATION DELAY @ 14V V<sub>CC</sub>-V<sub>EE</sub>

FIGURE 13. MINIMUM PULSE WIDTH RESPONSE

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE            | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 13, 2015 | FN6230.4 | Moved Ordering Information to page 3 and fixed page 1 layout.  Updated Ordering Information table on page 3.  Added Revision History and About Intersil sections.  Updated Package Outline Drawing (POD) L16.4X4A to the latest revision changes are as follows:  Updated to new POD format by removing table listing dimensions and moving dimensions onto drawing.  Added Typical Recommended Land Pattern. Removed package option. |

## About Intersil

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com">www.intersil.com</a>.

You may report errors or suggestions for improving this datasheet by visiting <a href="www.intersil.com/ask">www.intersil.com/ask</a>.

Reliability reports are also available from our website at www.intersil.com/support

© Copyright Intersil Americas LLC 2006-2015. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

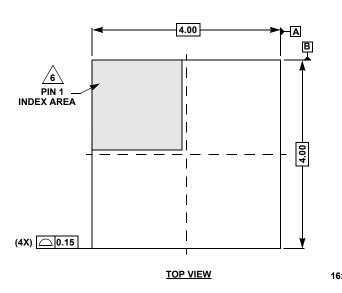

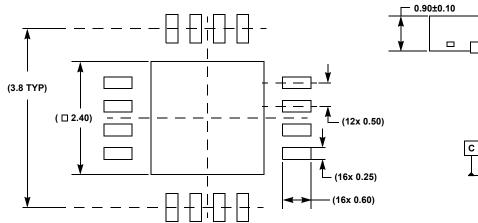

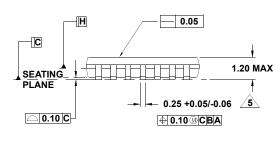

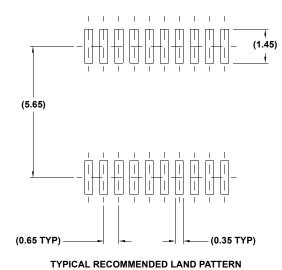

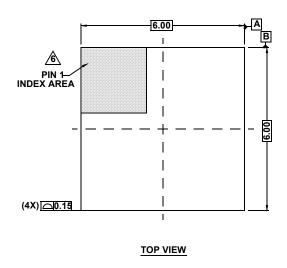

## L16.4x4A

16 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

Rev 3, 03/15

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

DETAIL "X"

- 3. Unless otherwise specified, tolerance: Decimal  $\pm 0.05$

- Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 1 Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

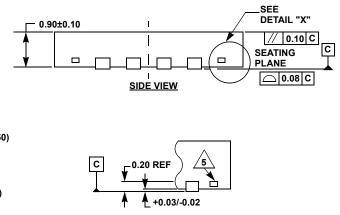

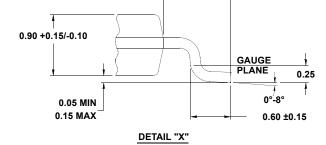

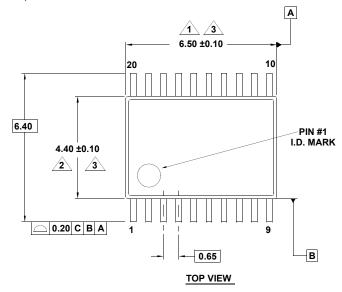

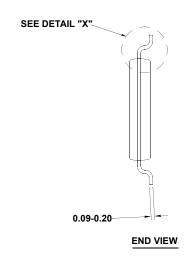

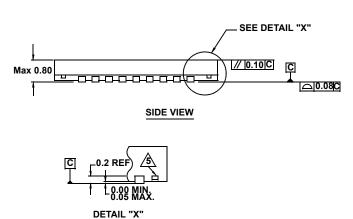

M14.173

14 LEAD THIN SHRINK SMALL OUTLINE PACKAGE (TSSOP) Rev 3, 10/09

-- 1.00 REF --

TYPICAL RECOMMENDED LAND PATTERN

- Dimension does not include mold flash, protrusions or gate burrs.

Mold flash, protrusions or gate burrs shall not exceed 0.15 per side.

- Dimension does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25 per side.

- 3. Dimensions are measured at datum plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- Dimension does not include dambar protrusion. Allowable protrusion shall be 0.80mm total in excess of dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm.

- 6. Dimension in ( ) are for reference only.

- 7. Conforms to JEDEC MO-153, variation AB-1.

## Quad Flat No-Lead Plastic Package (QFN) Micro Lead Frame Plastic Package (MLFP)

L20.5x5

20 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

|        | MILLIMETERS |                |      |       |  |

|--------|-------------|----------------|------|-------|--|

| SYMBOL | MIN         | NOMINAL        | MAX  | NOTES |  |

| Α      | 0.80        | 0.90           | 1.00 | -     |  |

| A1     | -           | 0.02           | 0.05 | -     |  |

| A2     | -           | 0.65           | 1.00 | 9     |  |

| A3     |             | 0.20 REF       |      | 9     |  |

| b      | 0.23        | 0.30           | 0.38 | 5, 8  |  |

| D      |             | 5.00 BSC       |      | -     |  |

| D1     |             | 4.75 BSC       |      | 9     |  |

| D2     | 2.95        | 2.95 3.10 3.25 |      | 7, 8  |  |

| E      |             | 5.00 BSC       |      |       |  |

| E1     |             | 4.75 BSC       |      | 9     |  |

| E2     | 2.95        | 3.10           | 3.25 | 7, 8  |  |

| е      |             | 0.65 BSC       |      | -     |  |

| k      | 0.20        | -              | -    | -     |  |

| L      | 0.35        | 0.60           | 0.75 | 8     |  |

| N      | 20          |                |      | 2     |  |

| Nd     | 5           |                |      | 3     |  |

| Ne     |             | 5              |      |       |  |

| Р      | -           | 0.60           |      |       |  |

| θ      | -           | 12             |      |       |  |

Rev. 4 11/04

- 1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

- 2. N is the number of terminals.

- 3. Nd and Ne refer to the number of terminals on each D and E.

- 4. All dimensions are in millimeters. Angles are in degrees.

- 5. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- Dimensions D2 and E2 are for the exposed pads which provide improved electrical and thermal performance.

- 8. Nominal dimensions are provided to assist with PCB Land Pattern Design efforts, see Intersil Technical Brief TB389.

- Features and dimensions A2, A3, D1, E1, P & θ are present when Anvil singulation method is used and not present for saw singulation.

- Compliant to JEDEC MO-220VHHC Issue I except for the "b" dimension.

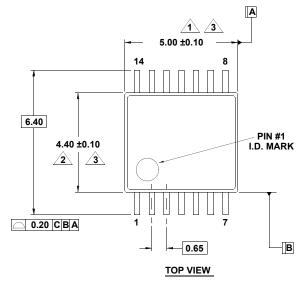

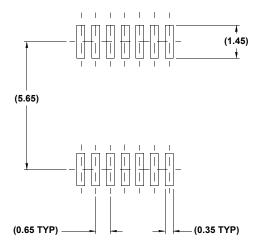

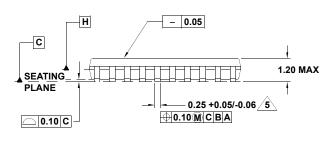

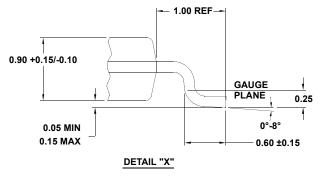

## M20.173

20 LEAD THIN SHRINK SMALL OUTLINE PACKAGE (TSSOP) Rev 2, 5/10

SIDE VIEW

- 1. Dimension does not include mold flash, protrusions or gate burrs.

Mold flash, protrusions or gate burrs shall not exceed 0.15 per side.

- 2. Dimension does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25 per side.

- 3. Dimensions are measured at datum plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 5. Dimension does not include dambar protrusion. Allowable protrusion shall be 0.08mm total in excess of dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm.

- 6. Dimension in ( ) are for reference only.

- 7. Conforms to JEDEC MO-153.

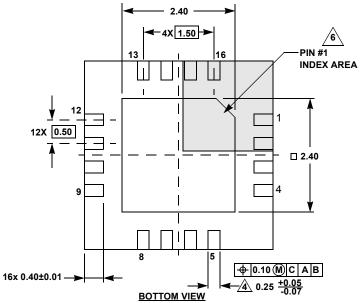

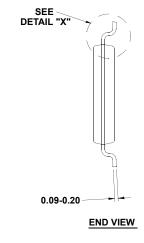

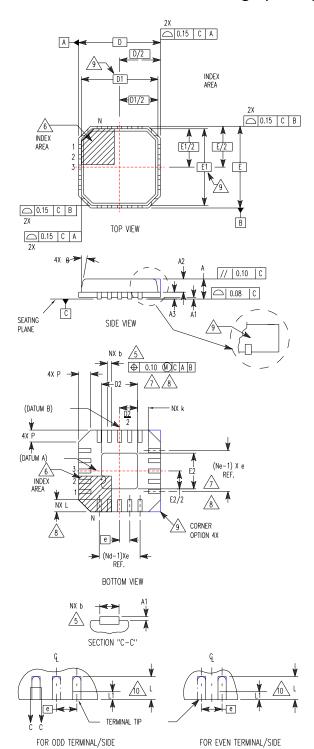

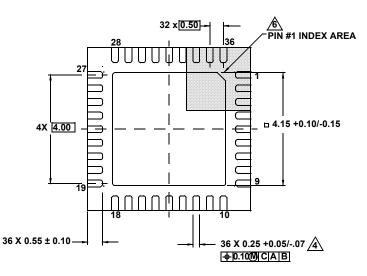

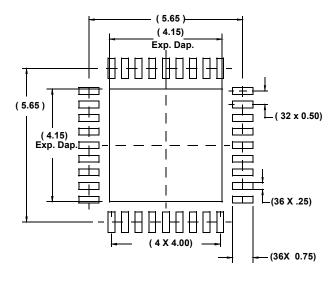

## L36.6x6

36 LEAD THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 5, 08/08

**BOTTOM VIEW**

TYPICAL RECOMMENDED LAND PATTERN

- 1. Dimensions are in millimeters.

- 2. Dimensioning and tolerancing conform to AMSEY14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 indentifier may be either a mold or mark feature.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

## Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: <u>org@eplast1.ru</u>

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.