# MP2930

4-Phase PWM Controller With 8-Bit DAC code for VR10 and VR11

The Future of Analog IC Technology

### DESCRIPTION

The MP2930 is a 4-phase, synchronous buck switching regulator controller for regulating microprocessor core voltage. MP2930 also uses dual edge PWM mode to realize fast load transient with fewer capacitors.

For meeting the requirement of microprocessor output voltage drops tightly as load current increases, output current is sensed to realize voltage droop function. Accurate current balancing is included in MP2930 to provide current balance for each channel.

8-bit ID input with selectable VR11 code and extended VR10 code can set output voltage dynamically.

The MP2930 also provides accurate and reliable over current protection and over voltage protection.

### FEATURES

- 2-, 3- or 4-phase Operation

- Channel-Current Balancing

- Voltage Droop vs. Load Current

- Precision Resistor or DCR Current Sensing

- 8-Bit ID Input with Selectable Between VR11 and VR10 Code at 6.25mV Per Bit

- Adjustable Switching Frequency

- Over Current Protection

- Over Voltage Protection

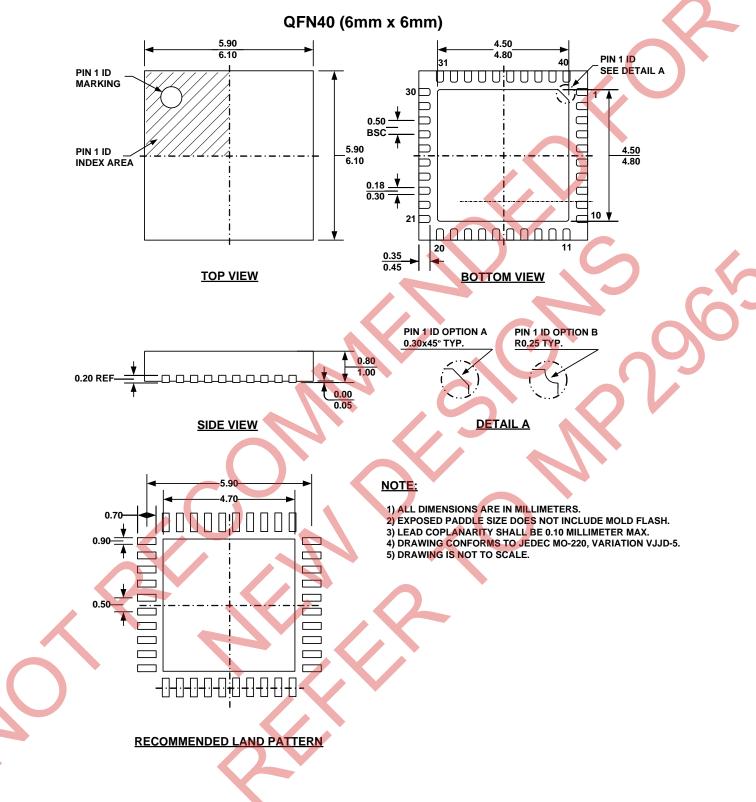

- Available in a 40-pin QFN6x6 Package

### APPLICATIONS

- Power Modules

- Desktop, Server, Core Voltage

- POLs (Memory)

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

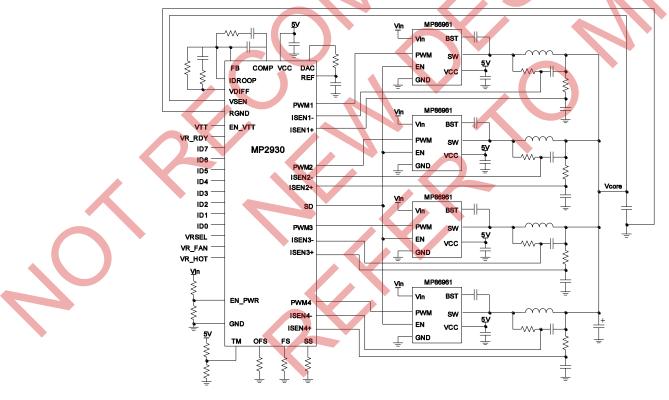

## **TYPICAL APPLICATION (4-PHASE BUCK CONVERTER)**

1 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2013 MPS. All Rights Reserved.

### ORDERING INFORMATION

| Part Number* | Package       | Top Marking | Free Air Temperature (T,) | 2 |

|--------------|---------------|-------------|---------------------------|---|

| MP2930GQK    | QFN (6 x 6mm) | MP2930GQK   | -40°C to +125°C           |   |

\* For Tape & Reel, add suffix -Z (e.g. MP2930GQK-Z);

For RoHS compliant packaging, add suffix -LF; (e.g. MP2930GQK -LF-Z)

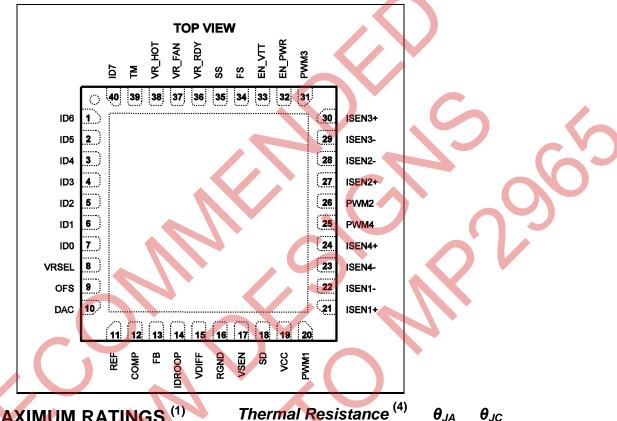

### PACKAGE REFERENCE

#### ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage VCC                                        |   |

|-----------------------------------------------------------|---|

| Continuous Power Dissipation $(T_A = +25^{\circ}C)^{(2)}$ |   |

|                                                           |   |

| Junction Temperature 150°C                                | K |

| Storage Temperature65°C to +150°C                         |   |

| ESD Rating                                                |   |

| Human Body Model2kV                                       |   |

| Machine Model200V                                         |   |

| Charged Device Model1.5kV                                 |   |

| -                                                         |   |

### Recommended Operating Conditions <sup>(3)</sup>

Supply Voltage VCC ......+5V ±5% Operating Junction Temp. (T<sub>1</sub>). -40°C to +125°C

## Thermal Resistance<sup>(4)</sup>

$\theta_{JC}$

#### Notes: 1)

Exceeding these ratings may damage the device.

- The maximum allowable power dissipation is a function of the 2) maximum junction temperature T<sub>J (MAX)</sub>, the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_{D (MAX)} = (T_{J (MAX)})^{-1}$  $T_A$ ) / $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2013 MPS. All Rights Reserved.

### **ELECTRICAL CHARACTERISTICS**

| Parameter                                                      | Test conditions                                                      | Min                                              | Тур      | Max   | Units |

|----------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------|----------|-------|-------|

| V <sub>cc</sub> Supply Current                                 |                                                                      | <u>.</u>                                         | <u>I</u> |       |       |

| Nominal Supply                                                 | VCC=5VDC; EN_PWR=5VDC;<br>RT=100kΩ,<br>ISEN1=ISEN2=ISEN3=ISEN4=-70uA |                                                  | 18       | 26    | mA    |

| Shutdown Supply                                                | VCC=5VDC; EN_PWR=0VDC;<br>RT=100 kΩ                                  |                                                  | 14       | 21    | mA    |

| Power-on Reset and Enable                                      |                                                                      |                                                  |          |       |       |

|                                                                | VCC Rising                                                           | 4.3                                              | 4.5      | 4.7   | V     |

| POR Threshold                                                  | VCC Falling                                                          | 3.7                                              | 3.9      | 4.2   | V     |

|                                                                | Rising                                                               | 0.850                                            | 0.88     | 0.910 | V     |

| EN_PWR Threshold                                               | Hysteresis                                                           |                                                  | 130      | -     | mV    |

|                                                                | Falling                                                              | 0.71                                             | 0.745    | 0.78  | V     |

|                                                                | Rising                                                               | 0.850                                            | 0.88     | 0.910 | V     |

| EN_VTT Threshold                                               | Hysteresis                                                           | -                                                | 130      |       | mV    |

|                                                                | Falling                                                              | 0.71                                             | 0.745    | 0.78  | V     |

| Reference Voltage and DAC                                      |                                                                      |                                                  |          |       |       |

| System Accuracy of MP2930<br>(ID =1V to 1.6V, TJ=0°C to +70°C) |                                                                      | -0.5                                             | 7 -      | 0.5   | %ID   |

| System Accuracy of MP2930<br>(ID =0.5V to 1V, TJ=0°C to +70°C) |                                                                      | -0.9                                             |          | 0.9   | %ID   |

| ID Pull-Up                                                     |                                                                      | -60                                              | -40      | -20   | μA    |

| ID Input Low Level                                             |                                                                      | -                                                | F.       | 0.4   | V     |

| ID Input High Level                                            |                                                                      | 0.8                                              |          | -     | V     |

| VRSEL Input Low Level                                          |                                                                      | -                                                |          | 0.4   | V     |

| VRSEL Input High Level                                         |                                                                      | 0.8                                              | -        | -     | V     |

| DAC Source Current                                             |                                                                      |                                                  | 4        | 7     | mA    |

| DAC Sink Current                                               |                                                                      | -                                                | -        | 320   | μA    |

| Pin-adjustable Offset                                          |                                                                      |                                                  |          |       |       |

|                                                                | Offset resistor connected to ground                                  | 380                                              | 400      | 420   | mV    |

| Voltage at OFS Pin                                             | Voltage below VCC, offset resistor<br>connected to VCC               | 1.55                                             | 1.600    | 1.65  | V     |

| Oscillators                                                    |                                                                      |                                                  |          |       |       |

| Accuracy of Switching Frequency setting                        | RT=100kΩ                                                             | 225                                              | 250      | 275   | kHz   |

| Adjustment Range of Switching<br>Frequency                     |                                                                      | 0.08                                             | -        | 1.0   | MHz   |

| Soft-Start Ramp Rate                                           | RS=150kΩ                                                             | -                                                | 1.563    | -     | mV/µs |

| Adjustment Range of Soft-Start Ramp Rage                       |                                                                      | 0.625                                            | -        | 6.25  | mV/µs |

| Error Amplifier                                                |                                                                      | <del>,                                    </del> | ,        |       | 1     |

| Maximum Output Voltage                                         |                                                                      | 3.8                                              | 4.2      | 4.6   | V     |

| Output High Voltage @ 2mA                                      |                                                                      | 3.6                                              | <u> </u> |       | V     |

MP2930 Rev. 1.01 10/30/2013 MF

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2013 MPS. All Rights Reserved.

# **ELECTRICAL CHARACTERISTICS** (continued) Operating conditions: $V_{CC} = 5V$ , unless otherwise noted.

| Parameter                                     | Test conditions                                     | Min   | Тур   | Max   | Unit |

|-----------------------------------------------|-----------------------------------------------------|-------|-------|-------|------|

| Remote-sense Amplifier                        |                                                     |       |       |       |      |

| Bandwidth                                     |                                                     | -     | 20    | -     | MHz  |

| Output High Current                           | VSEN-RGND=2.5V                                      | -100  | -     | 100   | μA   |

| Output High Current                           | VSEN-RGND=0.6                                       | -100  | -     | 100   | μA   |

| PWM Output                                    |                                                     |       |       |       |      |

| PWM Output Voltage Low<br>Threshold           | ILOAD=±500µA                                        |       | -     | 0.5   | V    |

| PWM Output Voltage High<br>Threshold          | ILOAD=±500µA                                        | 4.3   |       | -     | V    |

| <b>Current Sense and Over-current</b>         | Protection                                          |       |       |       |      |

| Sensed Current<br>Tolerance(IDROOP)           | ISEN1=ISEN2=ISEN3=ISEN4=50µA                        | 47    | 50    | 53    | μA   |

| Overcurrent Trip level for<br>Average Current |                                                     | 72    | 85    | 98    | μA   |

| Peak Current Limit for Individual<br>Channel  |                                                     |       | 120   |       | μA   |

| Thermal Monitoring and Fan Cor                | htrol                                               |       |       | 1     |      |

| TM Input Voltage for VR_FAN<br>TRIP           |                                                     | 1.55  | 1.65  | 1.75  | V    |

| TM Input Voltage for VR_FAN<br>Reset          |                                                     | 1.85  | 1.95  | 2.05  | V    |

| TM Input Voltage for VR_HOT<br>Trip           |                                                     | 1.3   | 1.4   | 1.5   | V    |

| TM Input Voltage for VR_HOT<br>Reset          | MPth actions all second and                         | 1.55  | 1.65  | 1.75  | V    |

| Leakage current of VR_FAN                     | With externally pull-up resisto<br>connected to VCC | r _   |       | 30    | μA   |

| VR_RAN Low Voltage                            | IVR_FAN=4mA                                         | -     | -     | 0.4   | V    |

| Leakage Current of VR_HOT                     | With externally pull-up resisto<br>connected to VCC | r _   | -     | 30    | μA   |

| VR_HOT Low Voltage                            | IVR_HOT=4mA                                         | -     | -     | 0.4   | V    |

| VR Ready and Protection Monito                |                                                     |       | 1     |       |      |

| Leakage Current of VR_RDY                     | With externally pull-up resisto<br>connected to VCC | r -   | -     | 30    | μA   |

| VR_RDY Low Voltage                            | IVR_RDY=4mA                                         | -     | -     | 0.4   | V    |

| Undervoltage Threshold                        | VDIFF Falling                                       | 48    | 50    | 52    | %ID  |

| VR_RDY Reset Voltage                          | VDIFF Rising                                        | 58    | 60    | 62    | %ID  |

| Overvoltage Protection                        | Before Valid ID                                     | 1.250 | 1.275 | 1.300 | V    |

| Threshold                                     | After valid ID, the voltage above ID                | 150   | 175   | 200   | Μv   |

| Overvoltage Protection Reset<br>Hysteresis    | $\langle \rangle$                                   | -     | 100   | -     | mV   |

### **PIN FUNCTIONS**

| Pin # | Name   | Description                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1     | ID6    |                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 2     | ID5    |                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 3     | ID4    |                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 4     | ID3    | ID inputs from microprocessor. These codes determine output regulation voltage.                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 5     | ID2    |                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 6     | ID1    |                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 7     | ID0    |                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 8     | VRSEL  | Select internal ID code. When it is tied to GND, the extended VR10 is selected. When it's floated or tied to high, VR11 code is selected.                                                                                                                                                                    |  |  |  |  |  |  |  |

| 9     | OFS    | Offset between REF and DAC program pin. The OFS pin can be used to program a DC offset current which will generate a DC offset voltage between the REF and DAC pins. The polarity of the offset is selected by connecting the resistor to GND or VCC. For no offset, the OFS pin should be left unconnected. |  |  |  |  |  |  |  |

| 10    | DAC    | Internal DAC reference output determined by ID codes                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 11    | REF    | Error amplifier input. A capacitor 0.1uF is used between REF and GND to smooth the voltage transition during Dynamic ID operations.                                                                                                                                                                          |  |  |  |  |  |  |  |

| 12    | COMP   | Error amplifier output pin. Tie to compensation network                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 13    | FB     | Output voltage feedback pin.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 14    | IDROOP | Current proportional to load current is flowed out through this pin                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| 15    | VDIFF  | Remote sense amplifier output. VDIFF-GND=VSEN-RGND                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 16    | RGND   | Remote sense amplifier input. Remote output GND                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 17    | VSEN   | Remote sense amplifier input. Remote output.                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 18    | SD     | Shutdown Intelli-phase @ Hiz state. MP2930 cooperates with MPS Intelli-phase MP86961 and SD pin is connected to the EN of MP86961.                                                                                                                                                                           |  |  |  |  |  |  |  |

| 19    | VCC    | Power supply. Connect this pin directly to a +5V supply.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 20    | PWM1   | Phase 1 PWM output.                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| 21    | ISEN1+ | Discont aurorate and life differential insult                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 22    | ISEN1- | Phase 1 current sense amplifier differential input                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 23    | ISEN4+ |                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 24    | ISEN4- | Phase 4 current sense amplifier differential input                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 25    | PWM4   | Phase 4 PWM output. Connect PWM4 to VCC to configure for 3-phase operation.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 26    | PWM2   | Phase 2 PWM output.                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| 27    | ISEN2+ | Phase 1 current sense amplifier differential input                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 28    | ISEN2- | Phase i current sense ampliner diretential input                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 29    | ISEN3- | Dhoop 2 ourrent concer emplifier differential input                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| 30    | ISEN3+ | Phase 3 current sense amplifier differential input                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 31    | PWM3   | Phase 3 PWM output. Connect PWM3 to VCC to configure for 2-phase operation.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 32    | EN_PWR | Enable pin. It is used to synchronize power-up of the controller and MOSFET driver ICs.                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 33    | EN_VTT | Enable pin. It is controlled by output of VTT voltage regulator in the mother board.                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Pin # | Name   | Description                                                                                                                                                                                                                         |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34    | FS     | PWM frequency set pin. A resistor from FS to GND will set the switching frequency.                                                                                                                                                  |

| 35    | SS     | Soft start oscillator frequency set pin. A resistor from SS to GND will set up the soft-<br>start ramp rate.                                                                                                                        |

| 36    | VR_RDY | Open drain logic output. When soft start completed and output voltage is regulated in the value determined by ID setting, VR_RDY is logic high.                                                                                     |

| 37    | VR_FAN | Open drain logic output. It is open when VR temperature reaches certain value                                                                                                                                                       |

| 38    | VR_HOT | Open drain logic output. It is open when VR temperature reaches certain value                                                                                                                                                       |

| 39    | ТМ     | NTC resistor in this pin is used to monitor inductor temperature. Connect this pin through an NTC thermistor to GND and a resistor to VCC of the controller. The voltage at this pin is reverse proportional to the VR temperature. |

| 40    | ID7    | ID input                                                                                                                                                                                                                            |

### PIN FUNCTIONS (continued)

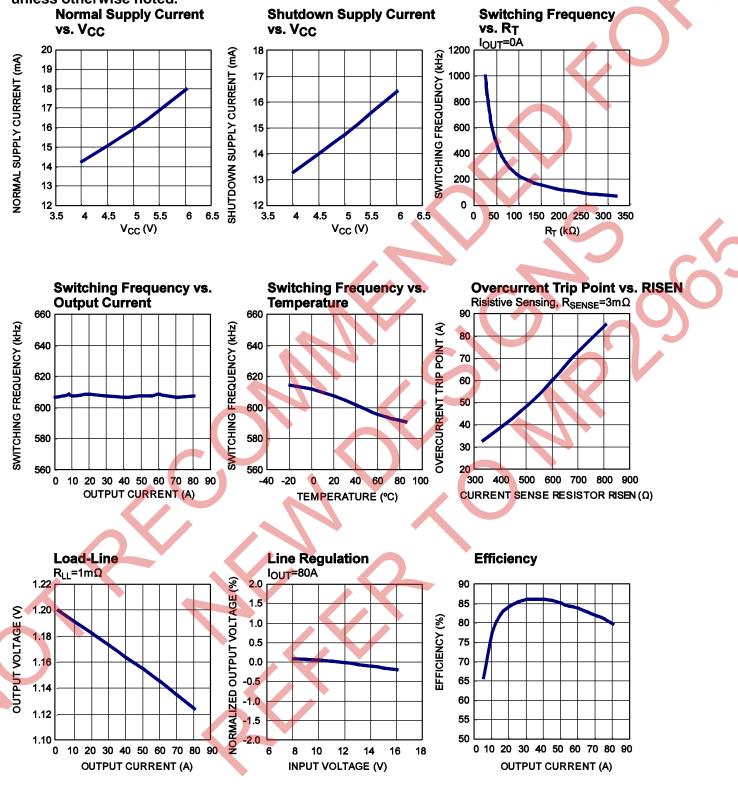

### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$ =12V, VID =1.2V, L=0.3µH, Fsw=600kHz, Inductor DCR Sensing, 4-Phase Operation, T<sub>A</sub>=+25°C, unless otherwise noted.

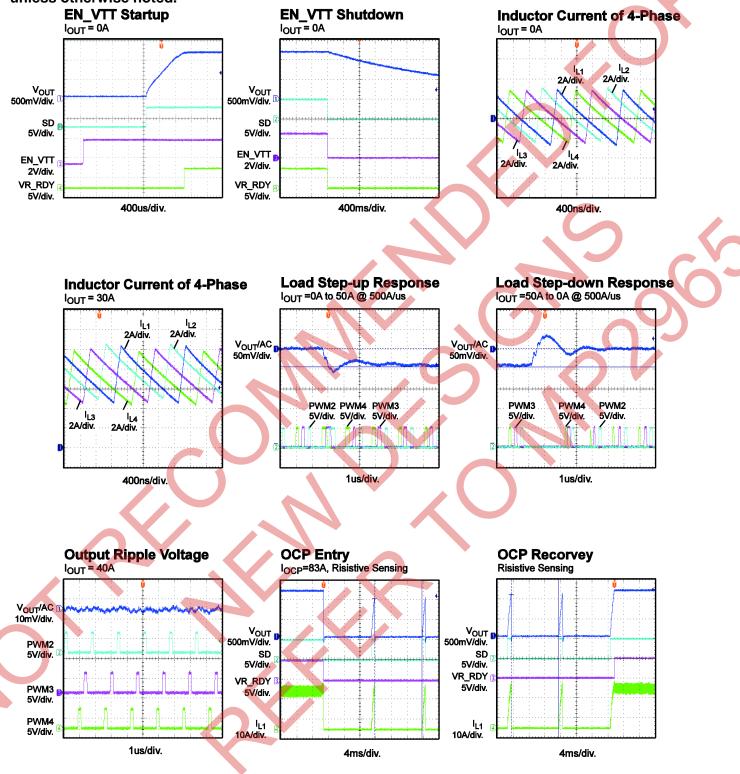

### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$ =12V, VID =1.2V, L=0.3µH, Fsw=600kHz, Inductor DCR Sensing, 4-Phase Operation, T<sub>A</sub>=+25°C, unless otherwise noted.

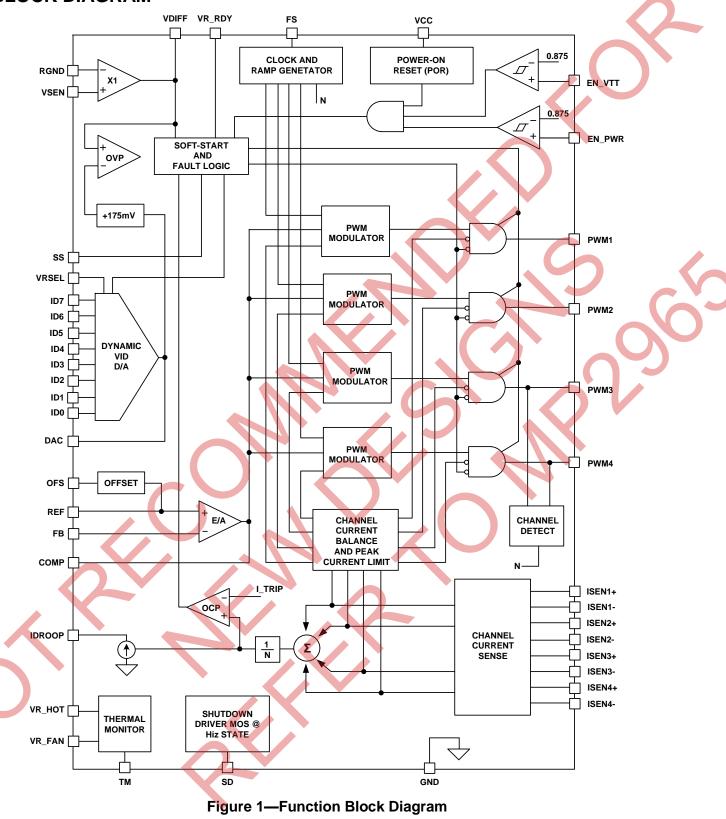

### **BLOCK DIAGRAM**

### **OPERATION**

#### Multiphase Power Conversion

The MP2930 is a multiphase regulators and it can be programmed for 2-, 3- or 4-channel operation for microprocessor core. The switching of each channel in a multiphase converter is timed to be symmetrically out-ofphase with each of the other channels. The interleaving work of each phase can help to reduce of ripple current amplitude and to reduce input ripple current.

#### **PWM Operation**

Under steady state conditions the operation of the MP2930 appears to be that of a conventional trailing edge modulator. Conventional analysis and design methods can be used for steady state and small signal operation.

Under load transition condition, the MP2930 can turn on all phase together to improve the load transient. It can achieve excellent transient performance and reduce the demand on the output capacitors.

The default channel setting for the MP2930 is four and the timing of each channel is set by the number of active channels. The cycle time of the pulse signal is the inverse of the switching frequency set by the resistor between the FS pin and GND.

For 4-channel operation, the channel firing order is 4-3-2-1: PWM3 pulse happens 1/4 of a cycle after PWM4, PWM2 output follows another 1/4 of a cycle after PWM3, and PWM1 delays another 1/4 of a cycle after PWM2. For 3-channel operation, the channel firing order is 3-2-1.

Connecting PWM4 to VCC selects 3-phase operation and the pulse times are spaced in 1/3 cycle increments. If PWM3 is connected to VCC, 2-phase operation is selected and the PWM2 pulse happens 1/2 of a cycle after PWM pulse.

#### Switching Frequency

The MP2930 switching frequency is set by the external resistor  $R_T$  between the FS pin and GND. The resistor  $R_T$  can be estimated by: Equation (1).

$$R_{T} = \frac{2.5 \times 10^{10}}{F_{SW}}$$

(1)

Where  $F_{sw}$  is the switching frequency of each phase.

#### Current Sensing

MP2930 has cycle by cycle current sense for fast response. MP2930 adopts inductor DCR sensing, or resistive sensing techniques. The sense current,  $I_{SEN}$ , is proportional to the inductor current. The sensed current is used for current balance, load-line regulation, and overcurrent protection.

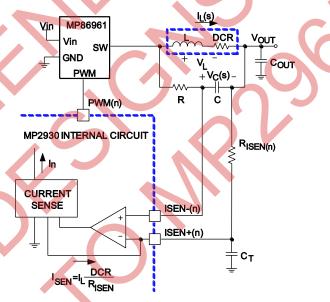

#### Inductor DCR Sensing

The MP2930 can adopt a lossless current sensing scheme, commonly referred to as inductor DCR sensing, as shown in Figure 2.

#### Figure 2–DCR Sensing Configuration

Equation (2) shows the s-domain equivalent voltage across the inductor  $V_L$ .

$$V_{L} = I_{L} \cdot (s \cdot L + DCR)$$

(2)

A simple RC network across the inductor extracts the DCR voltage, as shown in Figure 2.

The voltage on the capacitor  $V_C$  is proportional to the channel current  $I_L$ , see Equation (3).

$$V_{C} = \frac{\left(s \cdot \frac{L}{DCR} + 1\right) \cdot \left(DCR \cdot I_{L}\right)}{\left(s \cdot RC + 1\right)}$$

(3)

If the RC network components are selected such that the RC time constant (= $R^*C$ ) matches the inductor time constant (=L/DCR), the voltage across the capacitor V<sub>C</sub> is equal to the voltage drop across the DCR, i.e., proportional to the channel current.

Therefore, the current out of ISEN+ pin ( $I_{SEN}$ ), is proportional to the inductor current and it can be seen form Equation (4).

$$I_{\text{SEN}} = I_{\text{L}} \cdot \frac{DCR}{R_{\text{ISEN}}}$$

(4)

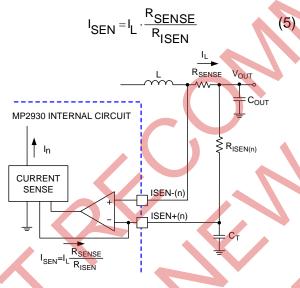

#### **Resistive Sensing**

For accurate current sense, a current-sense resistor  $R_{SENSE}$  in series with each output inductor can serve as the current sense element (see Figure 3). This technique is more accurate, but reduces overall converter efficiency due to the additional power loss on the current sense resistor  $R_{SENSE}$ .

Equation (5) shows the ratio of the channel current to the sensed current  $I_{\text{SEN}}$ .

#### Figure 3—Sense Resistor in Series with Inductors

The inductor DCR value will increase as the temperature increases. Therefore the sensed current will increase as the temperature of the current sense element increases. In order to compensate the temperature effect on the sensed current signal, a Positive Temperature Coefficient (PTC) resistor can be selected for the sense resistor  $R_{ISEN}$ .

#### **Channel-Current Balance**

The sensed current  $I_n$  from each active channel is summed together and divided by the number of active channels. The resulting average current ( $I_{AVG}$ ) provides a measure of the total load current. Channel current balance is achieved by comparing the sensed current of each channel to the average current to make an appropriate adjustment to the PWM duty cycle of each channel.

Channel current balance is essential in achieving the thermal advantage of multiphase operation. With good current balance, the power loss is equally dissipated over multiple devices and a greater area.

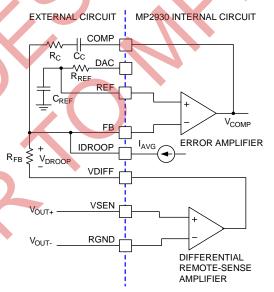

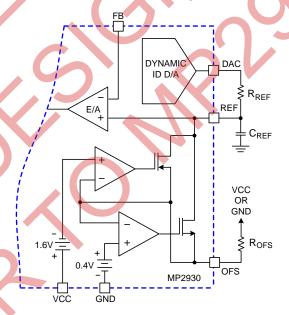

#### Voltage Regulation

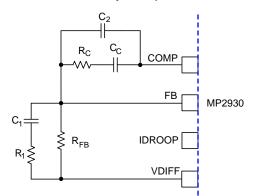

The compensation network shown in Figure 4 assures that the steady-state error in the output voltage is limited only to the error in the reference voltage (output of the DAC) and offset errors in the OFS current source, remote-sense and error amplifiers.

The typical open-loop gain of error amplifier is no less than 80dB, and the typical open-loop bandwidth is no less than 20MHz.

#### Figure 4—Output Voltage and Load-line Regulation with Offset Adjustment

The output of the error amplifier ( $V_{COMP}$ ) is compared to sawtooth waveforms to generate the PWM signals. The PWM signals control the timing of the MP86961 and regulate the converter output to the specified reference voltage. The internal and external circuitry, which control voltage regulation are shown in Figure 4.

The MP2930 incorporates an internal differential remote-sense amplifier in the feedback path, which results in a more accurate means of sensing output voltage. Connect the microprocessor sense pins to the non-inverting input (VSEN) and inverting input (RGND) of the remote-sense amplifier. The remote-sense output (VDIFF) is connected to the inverting input of the error amplifier through an external resistor.

Each ID input offers a 45µA pull-up to an internal 2.5V source for use with open-drain outputs. The pull-up current diminishes to zero above the logic threshold to protect voltage-sensitive output devices. External pull-up resistors can augment the pull-up current sources if case leakage into the driving device is greater than 45µA.

#### **Load-Line Regulation**

As the load current increases from zero, the output voltage will drop from the ID table value by an amount proportional to load current to achieve the load-line.

Adding a Droop can help to reduce the output voltage spike that result from fast load-current demand changes.

As shown in Figure 4, a current proportional to the average current of all active channels ( $I_{AVG}$ ) flows from FB through a load-line regulation resistor  $R_{FB}$ . The voltage drop across  $R_{FB}$  is proportional to the output current. It can be derived from Equation (6):

### VDROOP<sup>=I</sup>AVG<sup>R</sup>FB

The regulated output voltage is reduced by the droop voltage  $V_{DROOP}$ . The output voltage is a function a load current, it's derived by combining Equation (6) with the appropriate sensing current expression defined by the current sense method employed in Equation (7).

$$V_{OUT} = V_{REF} - V_{OFS} - \left(\frac{I_{OUT}}{N} \frac{R_X}{R_{ISEN}} R_{FB}\right)$$

(7)

Where  $V_{REF}$  is the reference voltage,  $V_{OFS}$  is the programmed offset voltage,  $I_{OUT}$  is the total output current of the converter,  $R_{ISEN}$  is the sense resistor connected to the ISEN+ pin, and  $R_{FB}$  is the feedback resistor, N is the active channel number, and  $R_X$  is the DCR, or  $R_{SENSE}$  depending on the sensing method.

Therefore the equivalent load-line impedance (Droop impedance), can be derived from Equation (8):

$$LL = \frac{R_{FB}}{N} \frac{R_{X}}{R_{ISEN}}$$

(8)

#### **Output Voltage Offset Programming**

R

In Figure 5, OFS pin is used to generate noload offset. A resistor RREF between DAC and REF is selected, and the product ( $I_{OFS} \times R_{OFS}$ ) is equal to the desired offset voltage.

#### Figure 5—Output Voltage Offset Programming

Connect a resistor  $R_{OFS}$  between OFS to VCC to generate a positive offset. The voltage across it is regulated to 1.6V. This causes a proportional current ( $I_{OFS}$ ) to flow into OFS. The positive offset is:

$$V_{\text{OFFSET}} = \frac{\frac{1.6 \times R_{\text{REF}}}{R_{\text{OFS}}}$$

(9)

(6)

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2013 MPS. All Rights Reserved.

Connect a resistor  $R_{OFS}$  between OFS to GND to generate a negative offset. The voltage across it is regulated to 0.4V, and  $I_{OFS}$  flows out of OFS. The negative offset is:

$$V_{\text{OFFSET}} = \frac{0.4 \times R_{\text{REF}}}{R_{\text{OFS}}}$$

(10)

The maximum Negative Offset for MP2930 is 150mV.

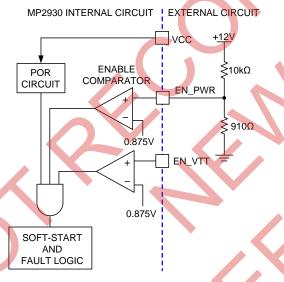

#### **Enable and Disable**

While in shutdown mode, the PWM outputs are held in a Hi-Z state, and the SD signal is pulled low to assure the Intelli-phase remain off. The following input conditions must be met to start MP2932.

- 1. VCC must reach the internal power-on reset (POR) rising threshold.

- EN\_PWR is used to coordinate the power sequencing between VCC and another voltage rail. The enable comparator holds the MP2932 in shutdown until the voltage at EN\_PWR rises above 0.875V.

- 3. The voltage on EN\_VTT must be higher than 0.875V to enable the controller. This pin is typically connected to the output of VTT VR.

#### Figure 6—Power Sequencing Using Threshold Sensitive Enable (EN) Function

When all conditions are satisfied, MP2930 begins the soft-start and ramps the output voltage to 1.1V first. After remaining at 1.1V for

some time, MP2930 reads the ID code at ID input pins. If the ID code is valid, MP2930 will regulate the output to the final ID setting. If the ID code is OFF code, MP2930 will shutdown, and cycling VCC, EN\_PWR or EN\_VTT is needed to restart.

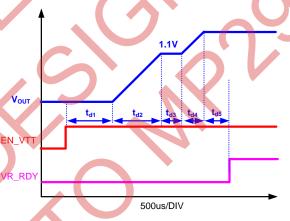

#### Soft-Start

MP2930 based VR has 4 periods during softstart as shown in Figure 7. After VCC, EN\_VTT reach their EN PWR **POR/enable** and thresholds, the controller will have fixed delay period t<sub>d1</sub>. After this delay period, the VR will begin first soft-start ramp until the output voltage reaches 1.1V voltage. Then, the controller will regulate the VR voltage at 1.1V for another fixed period  $t_{d3}$ . At the end of  $t_{d3}$ period, MP2930 reads the ID signals. If the ID code is valid, MP2930 will initiate the second soft-start ramp until the voltage reaches the ID voltage minus offset voltage.

#### Figure 7—Soft-Start Waveforms

The soft-start time is the sum of the 4 periods, as shown in Equation (12):

$$t_{SS} = t_{d1} + t_{d2} + t_{d3} + t_{d4}$$

(12)

$t_{d1}$  is a fixed delay with the typical value as 1.36ms.  $t_{d3}$  is determined by the fixed 85µs plus the time to obtain valid ID voltage. If the ID is valid before the output reaches the 1.1V, the minimum time to validate the ID input is 500ns. Therefore the minimum  $t_{d3}$  is about 86µs.

During  $t_{d2}$  and  $t_{d4}$ , MP2930 digitally controls the DAC voltage change at 6.25mV per step. The time for each step is determined by the frequency of the soft-start oscillator which is

defined by the resistor  $R_{SS}$  from SS pin to GND. The second soft-start ramp time  $t_{d2}$  and  $t_{d4}$  can be calculated based on Equations (13) and (14):

$$t_{d2} = \frac{2}{3} \times \frac{1.1 \times R_{SS}}{6.25 \times 25} (us)$$

(13)

$$t_{d4} = \frac{2}{3} \times \frac{(V_{VID} - 1.1) \times R_{SS}}{6.25 \times 25} (us)$$

(14)

For example, when ID is set to 1.5V and the  $R_{SS}$  is set at 100k $\Omega$ , the first soft-start ramp time  $t_{d2}$  will be 469µs and the second soft-start ramp time  $t_{d4}$  will be 171µs.

After the DAC voltage reaches the final ID setting, VR\_RDY will be set to high with the fixed delay  $t_{d5}$ . The typical value for  $t_{d5}$  is 85µs.

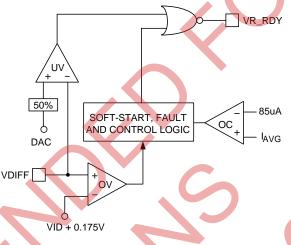

#### **Fault Monitoring and Protection**

The MP2930 actively monitors output voltage and current to detect fault conditions. One common power good indicator is provided for linking to external system monitors. The schematic in Figure 8 outlines the interaction between the fault monitors and the VR\_RDY signal.

#### VR\_RDY Signal

The VR\_RDY pin is an open-drain logic output to indicate that the soft-start period has completed and the output voltage is within the regulated range. VR\_RDY is pulled low during shutdown and releases high after a successful soft-start and a fixed delay  $t_{d5}$ . VR\_RDY will be pulled low when an under-voltage or overvoltage condition is detected, or the controller is disabled by a reset from EN\_PWR, EN\_VTT, POR, or ID OFF-code.

#### **Under-voltage Detection**

The undervoltage threshold is set at 50% of the ID code. When the output voltage at VSEN is below the undervoltage threshold, VR\_RDY is pulled low.

#### **Over-voltage Protection**

Regardless of the VR being enabled or not, the MP2930 over-voltage protection (OVP) circuit will be active after its POR. The OVP thresholds are different at different operation conditions. When VR is not enabled and during the softstart intervals  $t_{d1}$ ,  $t_{d2}$  and  $t_{d3}$ , the OVP threshold is 1.275V. Once the controller detects valid ID

input, the OVP trip point will be changed to DAC + 175mV.

Two actions are taken by the MP2930 to protect the microprocessor load when an over-voltage condition occurs.

#### Figure 8—VR\_RDY and Protection Circuitry

At the beginning of an over-voltage event, all PWM outputs are commanded low instantly (>20ns). This causes the MP86961 to turn on the lower MOSFETs and pull the output voltage below a level to avoid damaging the load. When the VDIFF voltage falls below the DAC + 75mV, PWM signals enter a high-impedance state, and the SD pin is pulled low to turn off the MP86961.

Once an over-voltage condition is detected, normal PWM operation ceases until the MP2930 is reset. Cycling the voltage on EN\_PWR, EN\_VTT or VCC below the PORfalling threshold will reset the controller. Cycling the ID codes will not reset the controller.

#### **Over-current Protection**

MP2930 has two levels of over-current protection. Each phase is protected from a sustained over-current condition by limiting its peak current, while the combined phase currents are protected on an instantaneous basis.

In instantaneous protection mode, the MP2930 utilizes the sensed average current  $I_{AVG}$  to detect an over-current condition. The average current is continually compared with a constant 85µA reference current, as shown in Figure 8.

© 2013 MPS. All Rights Reserved.

Once the average current exceeds the reference current, a comparator triggers the converter to shutdown.

At the beginning of over-current shutdown, the controller places all PWM signals in a highimpedance state within 20ns to turn off the MP86961. The system remains in this state about 12ms. If the controller is still enabled at the end of this wait period, it will attempt a softstart. If the fault remains, the hiccup mode will continue indefinitely until either controller is disabled or the fault is cleared. Note that the energy delivered during hiccup mode is much less than during full-load operation, so there is no thermal hazard during this kind of operation.

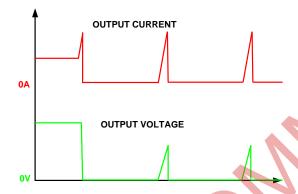

#### Figure 9—Over-current Behavior in HICCUP Mode. FSW = 600kHz

For the individual channel over-current protection, the MP2930 continuously compares the sensed current signal of each channel with the 120µA reference current. If one channel current exceeds the reference current, MP2930 will pull PWM signal of this channel to low for the rest of the switching cycle. This PWM signal can be turned on next cycle if the sensed channel current is less than the 120µA reference current. The peak current limit of individual channel will not trigger the converter to shutdown.

#### Thermal Monitoring (VR\_HOT/VR\_FAN)

There are two thermal signals to indicate the temperature status of the voltage regulator: VR\_HOT and VR\_FAN. Both VR\_FAN and VR\_HOT pins are open-drain outputs, and external pull-up resistors are required. Those signals are valid after the controller is enabled.

The VR FAN signal indicates that the temperature of the voltage regulator is high and more cooling airflow is needed. The VR HOT signal can be used to inform the system that the temperature of the voltage regulator is too high and the CPU should reduce its power consumption.

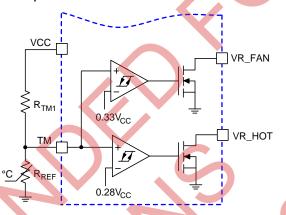

#### Figure 10—Block Diagram of Thermal **Monitoring Function**

The diagram of thermal monitoring function block is shown in Figure 10. One NTC resistor should be placed close to the power stage of the voltage regulator to sense the operational temperature, and one pull-up resistor is needed to form the voltage divider for the TM pin. As the temperature of the power stage increases, the resistance of the NTC will reduce, resulting in the reduced voltage at the TM pin.

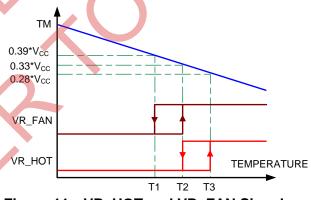

#### Figure 11—VR HOT and VR FAN Signal vs. TM Voltage

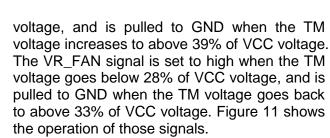

There are two comparators with hysteresis to compare the TM pin voltage to the fixed thresholds for VR FAN and VR HOT signals respectively. The VR FAN signal is set to high when the TM voltage is lower than 33% of VCC

#### **Current Sense Output**

The current from the IDROOP pin is the sensed average current. In typical application, the IDROOP pin is connected to the FB pin for the application where load line is required.

When load line function is not needed, the IDROOP pin can be used to obtain the load current information: with one resistor from the IDROOP pin to GND, the voltage at the IDROOP pin will be proportional to the load current in Equation (15):

$$V_{\text{IDROOP}} = \frac{R_{\text{IDROOP}}}{N} \frac{R_{X}}{R_{\text{ISEN}}} I_{\text{LOAD}}$$

(15)

Where  $V_{IDROOP}$  is the voltage at the IDROOP pin, R<sub>IDROOP</sub> is the resistor between the IDROOP pin and GND, I<sub>LOAD</sub> is the total output current of the converter, R<sub>ISEN</sub> is the sense resistor connected to the ISEN+ pin, N is the active channel number, and R<sub>X</sub> is the resistance of the current sense element, either the DCR of the inductor or R<sub>SENSE</sub> depending on the sensing method.

R<sub>IDROOP</sub> should be chosen to ensure that the voltage at the IDROOP pin is less than 2V under the maximum load current.

If the IDROOP pin is not used, tie it to GND.

### **APPLICATION INFORMATION**

#### **Current Sensing Resistor**

The resistors connected to the ISEN+ pins determine the gains in the load-line regulation loop and the channel-current balance loop as well as setting the over-current trip point. Select values for these resistors by using Equation (16):

$$R_{ISEN} = \frac{R_X}{85 \times 10^{-6}} \frac{I_{OCP}}{N}$$

(16)

Where  $R_{ISEN}$  is the sense resistor connected to the ISEN+ pin, N is the active channel number,  $R_X$  is the resistance of the current sense element, either the DCR of the inductor or  $R_{SENSE}$  depending on the sensing method, and  $I_{OCP}$  is the desired over-current trip point. Typically,  $I_{OCP}$  can be chosen to be 1.3x the maximum load current of the specific application.

#### Load-Line Regulation Resistor

The load-line regulation resistor is labeled R<sub>FB</sub> in Figure 4. Its value depends on the desired load-line requirement of the application.

The desired load-line can be calculated by using Equation (17):

$$R_{LL} = \frac{V_{DROOP}}{I_{FL}}$$

(17)

Where  $I_{FL}$  is the full load current of the specific application, and  $V_{RDROOP}$  is the desired voltage droop under the full load condition.

Based on the desired load-line  $R_{LL}$ , the load-line regulation resistor can be calculated by using Equation (18):

$$R_{FB} = \frac{NR_{ISEN}R_{LL}}{R_{X}}$$

Where N is the active channel number,  $R_{ISEN}$  is the sense resistor connected to the ISEN+ pin, and  $R_X$  is the resistance of the current sense, either the DCR of the inductor or  $R_{SENSE}$ depending on the sensing method.

#### Compensation

There are two distinct methods for achieving the compensation.

# Compensating Load-Line Regulated Converter

The load-line regulated converter behaves in a similar manner to a peak-current mode controller because the two poles at the output-filter L-C resonant frequency split with the introduction of current information into the control loop. The final location of these poles is determined by the system function, the gain of the current signal, and the value of the compensation components,  $R_c$  and  $C_c$ .

Treating the system as though it were a voltage-mode regulator by compensating the L-C poles and the ESR zero of the voltage-mode.

#### Figure 12— Compensation Circuit for MP2930 with Load-line Regulation

The feedback resistor,  $R_{FB}$ , has already been chosen as outlined in "Load-Line Regulation Resistor". Select a target bandwidth for the compensated system,  $f_0$ . The target bandwidth must be large enough to assure adequate transient performance, but smaller than 1/3 of the per-channel switching frequency. The values of the compensation components depend on the relationships of  $f_0$  to the L-C pole frequency and the ESR zero frequency.

The optional capacitor  $C_2$ , (22pF to 150pF) is sometimes needed to bypass noise away from the PWM comparator (see Figure 12).

www.MonolithicPower.com

(18)

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2013 MPS. All Rights Reserved.

#### **Compensation without Load-Line** Regulation

The non load-line regulated converter is accurately modeled as а voltage-mode regulator with two poles at the L-C resonant frequency and a zero at the ESR frequency. A type-III controller, as shown in Figure 13, provides the necessary compensation.

#### Figure 13—Compensation Circuit for MP2930 without Load-line Regulation

The first step is to choose the desired bandwidth,  $f_0$ , of the compensated system. Choose a frequency high enough to assure adequate transient performance but not higher than 1/3 of the switching frequency. The type-III compensator has an extra high-frequency pole,  $f_{HF}$ . A good general rule is to choose  $f_{HF}=10f_0$ , but it can be higher if desired. Choosing  $f_{HF}$  to be lower than  $10f_0$  can cause problems with too much phase shift below the system bandwidth.

#### **Designing the Output Filter**

The output inductors and the output capacitor bank together to form a low-pass filter responsible for smoothing the pulsating voltage at the phase nodes. The output filter also must provide the transient energy until the regulator can respond.

In high-speed converters, the output capacitor bank is usually the most costly (and often the largest) part of the circuit. The critical load parameters in choosing the output capacitors are the maximum size of the load step,  $\Delta I$ ; the load-current slew rate, di/dt; and the maximum allowable output voltage deviation under transient loading,  $\Delta V_{MAX}$ . Capacitors are

characterized according to their capacitance, ESR, and ESL (equivalent series inductance).

At the beginning of the load transient, the output capacitors supply all of the transient current. The output voltage will initially deviate by an amount approximated by the voltage drop across the ESL. As the load current increases, the voltage drop across the ESR increases linearly until the load current reaches its final value. The capacitors selected must have sufficiently low ESL and ESR so that the total output voltage deviation is less than the allowable maximum. Neglecting the contribution of inductor current and regulator response, the output voltage initially deviates by an amount in Equation (19):

$$\Delta V \approx (ESL) \frac{dI}{dt} + (ESR) \Delta I$$

(19)

The filter capacitor must have sufficiently low ESL and ESR so that  $\Delta V < \Delta V_{MAX}$ .

The ESR of the bulk capacitors also creates the majority of the output voltage ripple. As the bulk capacitors sink and source the inductor AC ripple current, a voltage develops across the bulk-capacitor ESR. Thus, once the output capacitors are selected, the maximum allowable ripple voltage, V<sub>P-P(MAX)</sub> determines the lower limit on the inductance.

$$L \ge (ESR) \frac{|V_{IN} - NV_{OUT}|V_{OUT}|}{f_{s} V_{IN} V_{P} - P(MAX)}$$

(20)

Since the capacitors are supplying a decreasing portion of the load current while the regulator recovers from the transient, the capacitor voltage becomes slightly depleted. The output inductors must be capable of assuming the entire load current before the output voltage decreases more than  $\Delta V_{MAX}$ . This places an upper limit on inductance.

#### Selecting the Switching Frequency

There are a number of variables to consider when choosing the switching frequency, as there are considerable effects on the upper-MOSFET loss calculation. The lower limit is established by the requirement for fast transient response and small output voltage ripple as outlined in "Output Filter Design". Choose the

lowest switching frequency that allows the regulator to meet the transient-response requirements.

#### Selecting the Input Capacitor

The input capacitors are responsible for sourcing the AC component of the input current flowing into the upper MOSFETs. Their RMS current capacity must be sufficient to handle the AC component of the current drawn by the upper MOSFETs which is related to duty cycle and the number of active phases.

Low capacitance, high-frequency ceramic capacitors are needed in addition to the bulk capacitors to suppress leading and falling edge voltage spikes. Select low ESL ceramic capacitors and place one as close as possible to each upper MOSFET drain to minimize board parasitic impedances and maximize suppression.

#### **PC Board Layout**

For best performance of the MP2930, the following guidelines should be strictly followed:

Within the allotted implementation area, place the switching components first. Switching component placement should take into account power dissipation. Align the output inductors and MOSFETs such that space between the components is minimized while creating the PHASE plane. If possible, duplicate the same placement of these components for each phase.

Next, place the input and output capacitors. Position one high frequency ceramic input capacitor next to each upper MOSFET drain. Place the input capacitors as close to the upper MOSFET drains as dictated by the component size and dimensions. Locate the output capacitors between the inductors and the load, while keeping them in close proximity to the microprocessor socket.

#### Table 1—VR10 ID Table (with 6.25mV Extension)

| ID4<br>400mV | ID3<br>200mV | ID2<br>100mV | ID1<br>50mV | ID0<br>25mV | ID5<br>12.5mV | ID6<br>6.25mV | VOLTAGE<br>(V) |

|--------------|--------------|--------------|-------------|-------------|---------------|---------------|----------------|

| 0            | 1            | 0            | 1           | 0           | 1             | 1             | 1.60000        |

| 0            | 1            | 0            | 1           | 0           | 1             | 0             | 1.59375        |

| 0            | 1            | 0            | 1           | 1           | 0             | 1             | 1.58750        |

| 0            | 1            | 0            | 1           | 1           | 0             | 0             | 1.58125        |

| 0            | 1            | 0            | 1           | 1           | 1             | 1             | 1.57500        |

| 0            | 1            | 0            | 1           | 1           | 1             | 0             | 1.56875        |

| 0            | 1            | 1            | 0           | 0           | 0             | 1             | 1.56250        |

| 0            | 1            | 1            | 0           | 0           | 0             | 0             | 1.55625        |

| 0            | 1            | 1            | 0           | 0           | 1             | 1             | 1.55000        |

| 0            | 1            | 1            | 0           | 0           | 1             | 0             | 1.54375        |

| 0            | 1            | 1            | 0           | 1           | 0             | 1             | 1.53750        |

| 0            | 1            | 1            | 0           | 1           | 0             | 0             | 1.53125        |

| 0            | 1            | 1            | 0           | 1           | 1             | 1             | 1.52500        |

| 0            | 1            | 1            | 0           | 1           | 1             | 0             | 1.51875        |

| 0            | 1            | 1            | 1           | 0           | 0             | 1             | 1.51250        |

| 0            | 1            | 1            | 1           | 0           | 0             | 0             | 1.50625        |

| 0            | 1            | 1            | 1           | 0           | 1             | 1             | 1.50000        |

| 0            | 1            | 1            | 1           | 0           | 1             | 0             | 1.49375        |

| 0            | 1            | 1            | 1           | 1           | 0             | 1             | 1.4875         |

| 0            | 1            | 1            | 1           | 1           | 0             | 0             | 1.48125        |

| 0            | 1            | 1            | 1           | 1           | 1             | 1             | 1.47500        |

| 0            | 1            | 1            | 1           | 1           | 1             | 0             | 1.46875        |

| 1            | 0            | 0            | 0           | 0           | 0             | 1             | 1.46250        |

| 1            | 0            | 0            | 0           | 0           | 0             | 0             | 1.45625        |

| 1            | 0            | 0            | 0           | 0           | 1             | 1             | 1.45000        |

| 1            | 0            | 0            | 0           | 0           | 1             | 0             | 1.44375        |

| 1            | 0            | 0            | 0           | 1           | 0             | 1             | 1.43750        |

| 1            | 0            | 0            | 0           | 1           | 0             | 0             | 1.43125        |

| 1            | 0            | 0            | 0           | 1           | 1             | 1             | 1.42500        |

| 1            | 0            | 0            | 0           | 1           | 1             | 0             | 1.41875        |

| 1            | 0            | 0            | 1           | 0           | 0             | 1             | 1.41250        |

| 1            | 0            | 0            | 1           | 0           | 0             | 0             | 1.40625        |

| 1            | 0            | 0            | 1           | 0           | 1             | 1             | 1.40000        |

| 1            | 0            | 0            | 1           | 0           | 1             | 0             | 1.39375        |

| 1            | 0            | 0            | 1           | 1           | 0             | 1             | 1.38750        |

| 1            | 0            | 0            | 1           | 1           | 0             | 0             | 1.38125        |

| 1            | 0            | 0            | 1           | 1           | 1             | 1             | 1.37500        |

| 1            | 0            | 0            | 1           | 1           | 7             | 0             | 1.36875        |

| 1            | 0            | 1            | 0           | 0           | 0             | 1             | 1.36250        |

#### Table 1—VR10 ID Table (with 6.25mV Extension) (continued)

|              | Extension) (continued) |              |             |             |               |               |                        |  |  |  |  |  |

|--------------|------------------------|--------------|-------------|-------------|---------------|---------------|------------------------|--|--|--|--|--|

| ID4<br>400mV | ID3<br>200mV           | ID2<br>100mV | ID1<br>50mV | ID0<br>25mV | ID5<br>12.5mV | ID6<br>6.25mV | VOLTAGE<br>(V)         |  |  |  |  |  |

| 1            | 0                      | 1            | 0           | 0           | 0             | 0             | 1.35625                |  |  |  |  |  |

| 1            | 0                      | 1            | 0           | 0           | 1             | 1             | 1.350 <mark>0</mark> 0 |  |  |  |  |  |

| 1            | 0                      | 1            | 0           | 0           | 1             | 0             | 1.34375                |  |  |  |  |  |

| 1            | 0                      | 1            | 0           | 1           | 0             | 1             | 1.33750                |  |  |  |  |  |

| 1            | 0                      | 1            | 0           | 1           | 0             | 0             | 1.33125                |  |  |  |  |  |

| 1            | 0                      | 1            | 0           | 1           | 1             | 1             | 1.32500                |  |  |  |  |  |

| 1            | 0                      | 1            | 0           | 1           | 1             | 0             | 1.31875                |  |  |  |  |  |

| 1            | 0                      | 1            | 1           | 0           | 0             | 1             | 1.31250                |  |  |  |  |  |

| 1            | 0                      | 1            | 1           | 0           | 0             | 0             | 1.30625                |  |  |  |  |  |

| 1            | 0                      | 1            | 1           | 0           | 1             | 1             | 1.30000                |  |  |  |  |  |

| 1            | 0                      | 1            | 1           | 0           | 1             | 0             | 1.29375                |  |  |  |  |  |

| 1            | 0                      | 1            | 1           | 1           | 0             | 1             | 1.28750                |  |  |  |  |  |

| 1            | 0                      | 1            | 1           | 1           | 0             | 0             | 1.28125                |  |  |  |  |  |

| 1            | 0                      | 1            | 1           | 1           | 1             | 1             | 1.27500                |  |  |  |  |  |

| 1            | 0                      | 1            | 1           | 1           | 1             | 0             | 1.26875                |  |  |  |  |  |

| 1            | 1                      | 0            | 0           | 0           | 0             | 1             | 1.26250                |  |  |  |  |  |

| 1            | 1                      | 0            | 0           | 0           | 0             | 0             | 1.25625                |  |  |  |  |  |

| 1            | 1                      | 0            | 0           | 0           | 1             | 1             | 1.25000                |  |  |  |  |  |

| 1            | 1                      | 0            | 0           | 0           | 1             | 0             | 1.24375                |  |  |  |  |  |

| 1            | 1                      | 0            | 0           | 1           | 0             | 1             | 1.23750                |  |  |  |  |  |

| 1            | 1                      | 0            | 0           | 1           | 0             | 0             | 1.23125                |  |  |  |  |  |

| 1            | 1                      | 0            | 0 <         | 1           | 1             | 1             | 1.22500                |  |  |  |  |  |

| 1            | 1                      | 0            | 0           | 1           | 1             | 0             | 1.21875                |  |  |  |  |  |

| 1            | 1                      | 0            | 1           | 0           | 0             | 1             | 1.21250                |  |  |  |  |  |

| 1            | 1                      | 0            | 1           | 0           | 0             | 0             | 1.20625                |  |  |  |  |  |

| 1            | 1                      | 0            | 1           | 0           | 1             | 1             | 1.20000                |  |  |  |  |  |

| 1            | 1                      | 0            | 1           | 0           | 1             | 0             | 1.19375                |  |  |  |  |  |

| 1            | 1                      | 0            | 1           | 1           | 0             | 1             | 1.18750                |  |  |  |  |  |

| 1            | 1                      | 0            | 1           | 1           | 0             | 0             | 1.18125                |  |  |  |  |  |

| 1            | 1                      | 0            | 1           | 1           | 1             | 1             | 1.17500                |  |  |  |  |  |

| 1            | 1                      | 0            | 1           | 1           | 1             | 0             | 1.16875                |  |  |  |  |  |

| 1            | 1                      | 1            | 0           | 0           | 0             | 1             | 1.16250                |  |  |  |  |  |

| 1            | 1                      | 1            | 0           | 0           | 0             | 0             | 1.15625                |  |  |  |  |  |

| 1            | 1                      | 1            | 0           | 0           | 1             | 1             | 1.15000                |  |  |  |  |  |

| 1            | 1                      | 1            | 0           | 0           | 1             | 0             | 1.14375                |  |  |  |  |  |

| 1            | 1                      | 1            | 0           | 1           | 0             | 1             | 1.13750                |  |  |  |  |  |

| 1            | 1                      | 1            | 0           | 1           | 0             | 0             | 1.13125                |  |  |  |  |  |

| 1            | 1                      | 1            | 0           | 1           | 1             | 1             | 1.12500                |  |  |  |  |  |

| 1            | 1                      | 1            | 0           | 1           | 1             | 0             | 1.11875                |  |  |  |  |  |

|              | 1                      |              |             |             |               | 1             |                        |  |  |  |  |  |

MP2930 Rev. 1.01 10/30/2013

#### Table 1—VR10 ID Table (with 6.25mV Extension) *continued*

| ID4<br>400mV | ID3<br>200mV | ID2<br>100mV | ID1<br>50mV | ID0<br>25mV | ID5<br>12.5mV | ID6<br>6.25mV | VOLTAGE<br>(V) |

|--------------|--------------|--------------|-------------|-------------|---------------|---------------|----------------|

| 1            | 1            | 1            | 1           | 0           | 0             | 1             | 1.11250        |

| 1            | 1            | 1            | 1           | 0           | 0             | 0             | 1.10625        |

| 1            | 1            | 1            | 1           | 0           | 1             | 1             | 1.10000        |

| 1            | 1            | 1            | 1           | 0           | 1             | 0             | 1.09375        |

| 1            | 1            | 1            | 1           | 1           | 0             | 1             | OFF            |

| 1            | 1            | 1            | 1           | 1           | 0             | 0             | OFF            |

| 1            | 1            | 1            | 1           | 1           | 1             | 1             | OFF            |

| 1            | 1            | 1            | 1           | 1           | 1             | 0             | OFF            |

| 0            | 0            | 0            | 0           | 0           | 0             | 1             | 1.08750        |

| 0            | 0            | 0            | 0           | 0           | 0             | 0             | 1.08125        |

| 0            | 0            | 0            | 0           | 0           | 1             | 1             | 1.07500        |

| 0            | 0            | 0            | 0           | 0           | 1             | 0             | 1.06875        |

| 0            | 0            | 0            | 0           | 1           | 0             | 1             | 1.06250        |

| 0            | 0            | 0            | 0           | 1           | 0             | 0             | 1.05625        |

| 0            | 0            | 0            | 0           | 1           | 1             | 1             | 1.05000        |

| 0            | 0            | 0            | 0           | 1           | 1             | 0             | 1.04375        |

| 0            | 0            | 0            | 1           | 0           | 0             | 1             | 1.03750        |

| 0            | 0            | 0            | 1           | 0           | 0             | 0             | 1.03125        |

| 0            | 0            | 0            | 1           | 0           | 1             | 1             | 1.02500        |

| 0            | 0            | 0            | 1           | 0           | 1             | 0             | 1.01875        |

| 0            | 0            | 0            | 1           | 1           | 0             | 7             | 1.01250        |

| 0            | 0            | 0            | 1           | 1           | 0             | 0             | 1.00625        |

| 0            | 0            | 0            | 1           | 1           | 7             | 1             | 1.00000        |

| 0            | 0            | 0            | 1           | 1           | 1             | 0             | 0.99375        |

| 0            | 0            | 1            | 0           | 0           | 0             | 1             | 0.9875         |

| 0            | 0            | 1            | 0           | 0           | 0             | 0             | 0.98125        |

| 0            | 0            | 1            | 0           | 0           | 1             | 1             | 0.97500        |

| 0            | 0            | 1            | 0           | 0           | 1             | 0             | 0.96875        |

| 0            | 0            | 1            | 0           | 1           | 0             | 1             | 0.9625         |

| 0            | 0            | 7            | 0           | 1           | 0             | 0             | 0.95625        |

| 0            | 0            | 1            | 0           | 1           | 1             | 1             | 0.95000        |

| 0            | 0            | 1            | 0           | 1           | 1             | 0             | 0.94375        |

| 0            | 0            | 1            | 1           | 0           | 0             | 1             | 0.93750        |

| 0            | 0            | 1            | 1           | 0           | 0             | 0             | 0.93125        |

| 0            | 0            | 1            | 1           | 0           | 1             | 1             | 0.92500        |

| 0            | 0            | 1            | 1           | 0           | 1             | 0             | 0.91875        |

| 0            | 0            | 1            | 1           | 1           | 0             | 1             | 0.91250        |

| 0            | 0            | 1            | 1           | 1           | 0             | 0             | 0.90625        |

| 0            | 0            | 1            | 1           | 1           | 1             | 1             | 0.90000        |

|              |              |              | 1           |             |               | [ |                        |

|--------------|--------------|--------------|-------------|-------------|---------------|---|------------------------|

| ID4<br>400mV | ID3<br>200mV | ID2<br>100mV | ID1<br>50mV | ID0<br>25mV | ID5<br>12.5mV |   | VOLTAGE<br>(V)         |

| 0            | 0            | 1            | 1           | 1           | 1             | 0 | 0.89375                |

| 0            | 1            | 0            | 0           | 0           | 0             | 1 | 0.88750                |

| 0            | 1            | 0            | 0           | 0           | 0             | 0 | 0.88125                |

| 0            | 1            | 0            | 0           | 0           | 1             | 1 | 0.875 <mark>0</mark> 0 |

| 0            | 1            | 0            | 0           | 0           | 1             | 0 | 0.86875                |

| 0            | 1            | 0            | 0           | 1           | 0             | 1 | 0.86250                |

| 0            | 1            | 0            | 0           | 1           | 0             | 0 | 0.85625                |

| 0            | 1            | 0            | 0           | 1           | 1             | 1 | 0.85000                |

| 0            | 1            | 0            | 0           | 1           | 1             | 0 | 0.84375                |

| 0            | 1            | 0            | 1           | 0           | 0             | 1 | 0.83750                |

| 0            | 1            | 0            | 1           | 0           | 0             | 0 | 0.83125                |

### Table 2—VR11 ID 8-BIT

|   | ID7 | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 | VOLTAGE |

|---|-----|-----|-----|-----|-----|-----|-----|-----|---------|

|   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | OFF     |

| - | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | OFF     |

|   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1.60000 |

|   | Ō   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1.59375 |

|   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1.58750 |

|   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 1.58125 |

|   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 0   | 1.57500 |

|   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 7   | 1.56875 |

|   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 1.56250 |

|   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | 1.55625 |

|   | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | 1.55000 |

|   | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 1   | 1.54375 |

|   | 0   | 0   | 0   | 0   | 1   | 1   | 0   | 0   | 1.53750 |

|   | 0   | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 1.53125 |