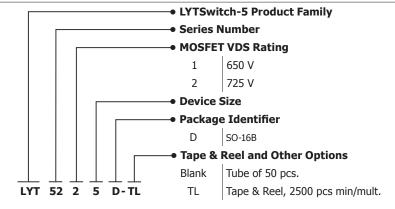

# LYT5216-5228 LYTSwitch-5 Family

Single-Stage LED Driver IC with Combined PFC and Constant Current Output in Isolated and Non-Isolated Topologies

# **Product Highlights**

# Combined Single-Stage PFC + Accurate CC Output

- Accurate CC, better than ±3%

- Power Factor >0.9

- Low THD, <10% with typical input and output conditions

- >90% efficient in optimized designs

- · High switching frequency and DCM allow compact magnetics

#### **Design Flexibility**

- Supports buck, buck-boost, tapped-buck, boost, isolated and non-isolated flyback topologies

- 2 MOSFET voltage options and 3 power levels for optimum device selection

## **Highest Reliability**

- No electrolytic bulk capacitors or optoisolators for increased lifetime

- Comprehensive protection features

- · Input and output overvoltage

- Open-loop protection

- · Advanced thermal control

- Thermal foldback allows output light delivery at abnormally high ambient temperatures

- · Hysteretic shutdown provides protection during fault conditions

# **Description**

The LYTSwitch $^{\text{TM}}$ -5 family is ideal for single-stage power factor corrected constant current LED applications – bulbs, tubes and ballasts.

Each device incorporates a high-voltage power MOSFET and discontinuous mode, variable frequency, variable on-time controller. The controller also provides fast (cycle-by-cycle) current limit, input and output OVP, plus advanced thermal management circuitry.

The combination of a low-side switching topology, cooling via electronically quiet SOURCE pins and frequency jitter ensures extremely low EMI. This reduces the size of the input filter components – greatly reducing audible noise.

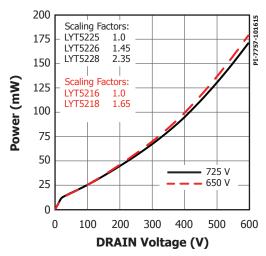

The part numbers shown in Table 1 describe 3 different power levels and two MOSFET voltage options to cost-optimize designs, while  $EcoSmart^{TM}$  switching technology ensures maximum efficiency for each device size and load condition.

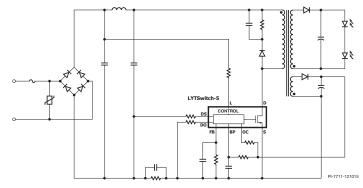

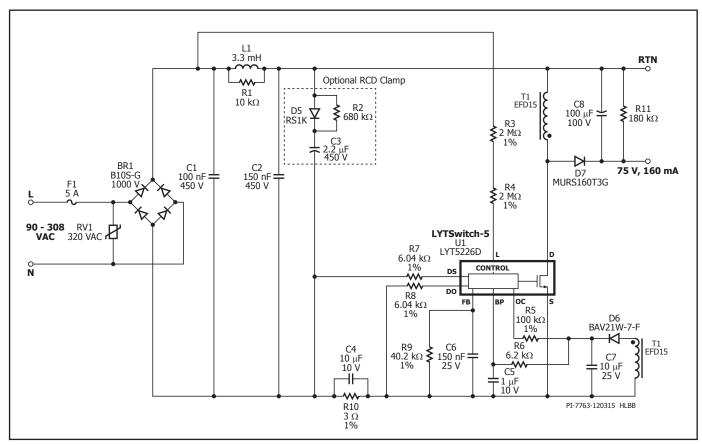

Figure 1a. Typical Application Schematic: Isolated Flyback.

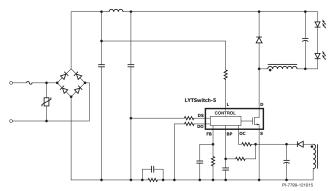

Figure 1b. Typical Application Schematic: Non-Isolated Buck.

| <b>Output P</b> | ower | <b>Table</b> |

|-----------------|------|--------------|

|-----------------|------|--------------|

| -                    |                           |

|----------------------|---------------------------|

| Draduat?             | Output Power <sup>1</sup> |

| Product <sup>2</sup> | 90-308 VAC                |

| LYT5225D             | 9 W                       |

| LYT5216D, LYT5226D   | 16 W                      |

| LYT5218D, LYT5228D   | 25 W                      |

Table 1. Output Power Table.

- Maximum practical continuous power in an open frame design with adequate heat sinking, measured at 50°C ambient (see Key Applications Considerations for more information).

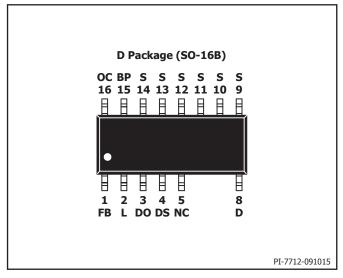

- 2. Package: D: SO-16B.

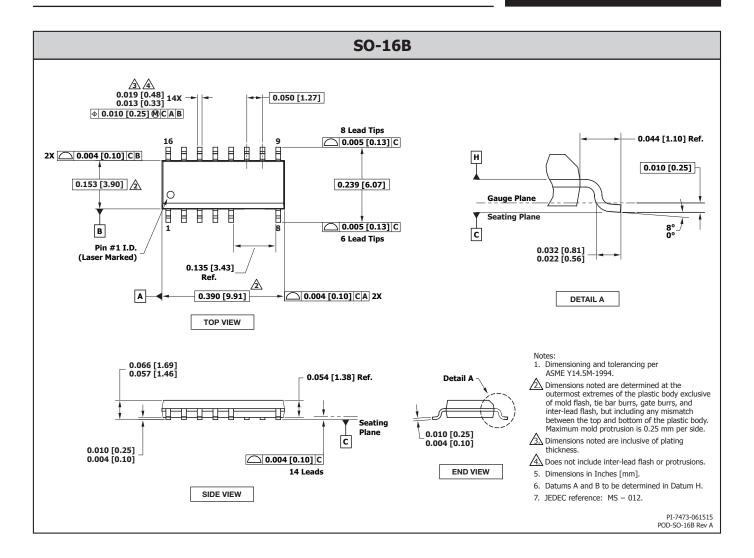

Figure 2. SO-16B (D Package).

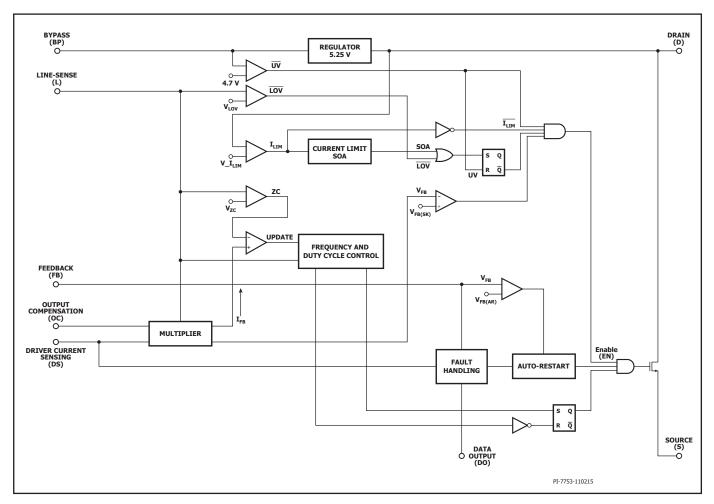

Figure 3. Block Diagram.

# **Pin Functional Description**

# LINE SENSE (L) Pin

The LINE-SENSE pin measures input voltage. Input OVP is activated when LINE-SENSE pin current exceeds the predetermined threshold.

# **DATA OUTPUT (DO) Pin**

Describes auto-restart events.

# **DRIVER CURRENT SENSE (DS) Pin**

DRIVER CURRENT SENSE pin senses the driver current. This current is used to deduce output current: it is multiplied by the input voltage and the result is then divided by the output voltage to obtain output current.

| $R_{DS}(\Omega)$ | Topology                           |  |

|------------------|------------------------------------|--|

| 6 k – 12 K       | Buck, Buck-Boost, Isolated Flyback |  |

| 24 k             | Non-Isolated Flyback               |  |

Table 2. Topology Selection Resistor.

## FEEDBACK (FB) Pin

In normal operation the preset threshold on the FEEDBACK pin is  $300\ \mbox{mV}.$

Cycle skipping is triggered when voltage on this pin exceeds 600 mV. Auto-Restart is triggered when voltage on this pin exceeds 2 V.

#### **BYPASS (BP) Pin**

5.25 V supply rail.

# **OUTPUT COMPENSATION (OC) Pin**

Output OVP for all topologies. Output voltage compensation for indirect output current sense topologies.

# DRAIN (D) Pin

High-voltage internal MOSFET (725 V or 650 V).

## **SOURCE (S) Pin:**

Power and signal ground.

Figure 4. Pin Configuration.

# **Applications Example**

# 12 W Tube Lamp Driver Accurate Regulation, High Power Factor, Low ATHD Design Example (DER-515)

Figure 5. 12 W, 75 V, 160 mA Non-Isolated Tube Lamp Driver for Wide Input Range of 90 VAC to 308 VAC using LYT5526D.

The circuit shown in Figure 5 is configured as a buck-boost power supply utilizing the LYT5526D from the LYTSwitch-5 family of ICs. This type of LED driver configuration is common for tube lamp applications where accurate regulation, high efficiency, high power factor and low ATHD are required along with low component count for high reliability. The output can drive an LED load from 70 V to 80 V with a constant output current of 160 mA  $\pm 3\%$  across input range of 90 VAC to 308 VAC and can operate in a maximum ambient temperature of 100 °C with good margin below the thermal foldback protection point. It has an efficiency of greater than 89%, very low ATHD% (less than 10%) and high power factor of greater than 0.95 measured at nominal input voltages (115 VAC and 230 VAC).

LYTSwitch-5 also can be configured in a buck topology, and has advantages where low ATHD is not a critical requirement. Buck designs can realize between 15% to 33% ATHD. Advantages of buck over buck-boost configuration are:

- Lower stress voltage on the driver MOSFET.

- Higher system efficiency.

- Potentially smaller EMI filter dependent on power, shape and size of system.

#### **Circuit Description**

The LYTSwitch-5 device (U1- LYT5526D) combines a high-voltage power MOSFET, variable frequency and on-time control engine, fast start-up, and protection functions including line and output over-

voltage into a single package, greatly reducing component count. The integrated 725 V power MOSFET provides a large drain voltage margin in universal input AC applications thus increasing reliability. A 625 V MOSFET option is also offered to reduce cost in applications where the voltage stress on the MOSFET is lower. Configured to operate as a discontinuous conduction mode buck-boost converter, U1 provides high power factor and very low ATHD via its internal control algorithm (the design also features low input capacitance to further reduce THD and increase PF). Discontinuous conduction mode inherently eliminates reverse current from the output diode when the MOSFET is in the off-state reducing high frequency noise and allowing the use of a simpler, smaller EMI filter which also improves efficiency.

# **Input Filter**

AC input power is rectified by bridge BR1. 1000 V voltage rating is recommended (the maximum clamp voltage for a typical 320 V varistor is 850 V). The rectified DC is filtered by the input capacitors C1 and C2. Too much capacitance degrades power factor and ATHD, so the values of the input capacitors were adjusted to the minimum values necessary to meet EMI with a suitable margin. Inductor L1, C1 and C2 form a  $\pi$  (pi) filter, which attenuates conducted differential and common mode EMI currents. Resistor R1 across L1 damps the Q of the filter inductor to improve filtering without reducing low frequency attenuation. F1 provides input protection against catastrophic failure such as short-circuit after the fuse. For cost

reduction, this can be replaced by a fusible resistor (typically a flame proof wire-wound type) which would need to be rated to withstand the instantaneous dissipation induced when charging the input capacitance when first connected to the input line.

Selection of fuse (F1) type and rating is dependent on input surge requirements. Typical minimum requirement for tube application is 500 V differential surges. This design meets a 3 kV surge specification, so a 5-ampere slow blow fuse was used. A fast-blow fuse with a high ampere energy (I²T) rating could also be used.

An optional RCD surge clamp circuit (D5, R2 and C3) can be employed for differential surge voltage requirement of 3 kV. Capacitor C3 can also be increased to help meet a higher surge voltage requirement.

| Input Range   | Typical Line Surge<br>Requirement                     | Protection                |

|---------------|-------------------------------------------------------|---------------------------|

| 90 to 264 VAC | 500 V Differential Surge /<br>2.5 kV Ring Wave        | 275 VAC MOV               |

| 90 to 308 VAC | 1 kV to 3 kV Differential<br>Surge / 2.5 kV Ring Wave | 320 VAC MOV,<br>RCD Clamp |

Table 3. Recommended Surge Protection.

## LYTSwitch-5 Output Regulation

In order to maintain very accurate output current regulation — within  $\pm 3\%$ , the FEEDBACK (FB) pin voltage (with an appropriately selected low-pass filter comprising R9 and C6) is compared to a preset average feedback voltage (V $_{\rm FB}$ ) of 300 mV. When the detected signal is above or below the preset average V $_{\rm FB}$  threshold voltage, the onboard averaging-engine will adjust the frequency and/or on-time to maintain regulation.

The bias winding voltage is proportional to the output voltage (controlled by the turns-ratio between the bias supply and output-main winding). This allows the output voltage to be monitored without the need for output-side feedback components. Resistor R5 converts the bias voltage into a current which is fed into the OUTPUT COMPENSATION (OC) pin of U1. The OUTPUT COMPENSATION pin current is also used to detect output overvoltage which is set to 30% above the nominal output voltage. Once the current exceeds the  $\rm I_{LOV+}$  threshold the IC will trigger a latch which disables switching which prevents the output from rising further. An AC recycle is needed to reset this protection mode once triggered.

In order to provide line input voltage information to U1 the rectified input AC voltage is fed into the LINE SENSE (L) pin of U1 as a current via R3 and R4 (4  $\mbox{M}\Omega$  total resistance). This sensed current is also used by U1 to detect input zero-crossing and set the input line overvoltage protection threshold. In a line overvoltage condition once this current exceeds the  $I_{\mbox{OOV}}$  threshold, the IC will instantaneously disable switching to protect the MOSFET from further voltage stress. The IC will start switching as soon the line voltage drops to safe levels indicated by the L pin current dropping by 5  $\mbox{\mu}\mbox{A}$ .

The primary switched current is sensed via R10 and filtered with C4. The signal is fed into the DRIVER CURRENT SENSE (DS) pin. A low ESR ceramic capacitor of at least 10  $\mu$ F is recommended for capacitor C4.

The internal frequency/on-time engine inside LYTSwitch-5 combines the OUTPUT COMPENSATION pin current, the LINE SENSE pin current and the DRIVER CURRENT SENSE pin current information to deduce the FB signal. This is compared to an internal  $V_{\rm FB}$  threshold to maintain accurate constant output current.

It is important to note that for accurate output current regulation the use of 1% tolerance for LINE SENSE pin resistors (R3 and R4) is recommended. This recommendation also applies to OUTPUT COMPENSATION pin resistor R5, FEEDBACK pin resistor R9 (capacitor C6 at least X7R type), and DRIVER CURRENT SENSE pin resistor R7 and R10.

Diode D6 and C7 provides a bias supply for U1 from an auxiliary winding on the transformer. Bias supply recommended voltage level is 12 V. Filter capacitor C7 should be sized to ensure a low ripple voltage. Capacitor C5 serves as local decoupling for the BYPASS pin of U1 which is the supply pin for the internal controller. Current via R6 is typically limited to 1 mA. During start-up, C5 is charged to  $\sim\!5.25$  V from an internal high-voltage current source internally fed from the DRAIN pin. This allows U1 to start switching. After start-up the operating supply current is provided from the bias supply via R6. The recommended value for the BYPASS pin capacitor C5 is 1  $\mu\text{F}$ . The voltage rating for the capacitor should be greater than 7 V. The capacitor can be a ceramic or electrolytic type, but tolerance should be less than 50%. The capacitor must be physically located close to BYPASS and SOURCE pins for effective noise decoupling.

## **Output Rectification**

During the switching off-state the output from the transformer main winding is rectified by D7 and filtered by C8. An ultrafast 1 A, 600 V with 35 ns reverse recovery time (trr) diode was selected for efficiency. The value of the output capacitor C8 was selected to give peak-to-peak LED ripple current equal to 30% of the mean value. For designs where lower ripple is desirable the output capacitance value can be increased unlike traditional power supplies, low ESR capacitors are not required for the output stage of LED designs.

A small output pre-load resistor R11 discharges the output capacitor when the driver is turned off, giving a relatively quick and smooth decay of the LED light. Recommended pre-load power dissipation is  $\leq 0.5\%$  of the output power.

# **Key Design Considerations**

#### **Device Selection**

The data sheet power table (Table 1) represents the maximum practical continuous output power that can be delivered in an open frame design with adequate heat sinking.

| Output Power Table   |                           |  |  |  |

|----------------------|---------------------------|--|--|--|

| Product <sup>2</sup> | Output Power <sup>1</sup> |  |  |  |

| Product <sup>2</sup> | 90-308 VAC                |  |  |  |

| LYT5225D             | 9 W                       |  |  |  |

| LYT5216D, LYT5226D   | 16 W                      |  |  |  |

| LYT5218D, LYT5228D   | 25 W                      |  |  |  |

Table 4. Output Power Table.

DER-515 is a 12 W driver. The LYT5226D IC was chosen for its higher voltage MOSFET rating of 725 V because the topology chosen was a buck-boost and the specification called for a maximum input voltage of 308 VAC. In other applications where surge and line voltage conditions allow, it may be possible to use the 650 V MOSFET option to reduce design cost without impacting reliability.

## **Magnetics Design**

The core type selected was a low profile EFD15 with ferrite core material and a wide winding window that allowed better convection cooling for the winding.

To ensure that discontinuous conduction mode (DCM) operation of LYTSwitch-5 is maintained over line input and inductance tolerance variations, and to ensure for accurate output current regulation, it is recommended that the LYTSwitch-5 PIXIs spreadsheet located at PI Expert web lab (http://piexpertweblab.power.com/site/login) should be used for magnetics calculations.

#### **EMI Considerations**

Total input capacitance affects PF and ATHD – increasing the value will degrade performance. With LYTSwitch-5, the combination of a low-side switching configuration and frequency jitter reduces EMI and enables the use of small and simple  $\pi$  (pi) filter. It also allows simple magnetic construction where the main winding can be wound continuously using the automated winding approach preferred for low-cost manufacturing. The recommended location of the EMI filter is after the bridge rectifier. This allows the use of regular film capacitors as opposed to more expensive safety rated X capacitors that would be required if the filter is placed before the bridge.

#### **Surge Immunity Consideration**

This design assumed a differential surge requirement of 3 kV which can be met easily with LYTSwitch-5 line overvoltage protection and using a RCD surge clamp circuit (D5, R2 and C3) and MOV (RV1). For lower differential surge requirement such as 1 kV, capacitor C3 can be reduced to 1  $\mu\text{F}.$

#### **Thermal and Lifetime Considerations**

Lighting applications present thermal challenges to the driver. In many cases the LED load dissipation determines the working ambient temperature experienced by the drive. Thermal evaluation should be performed with the driver inside the final enclosure. Temperature has a direct impact on driver and LED lifetime. For every 10  $^{\circ}\text{C}$  rise in temperature, component life is reduced by a factor of 2. Therefore it is important to verify and optimize the operating temperatures of all components.

# **Quick Design Checklist**

## **Maximum Drain Voltage**

Verify that the peak drain voltage stress (VDS) does not exceed maximum acceptable drain voltage under all operating conditions, including start-up and fault conditions.

### **Maximum Drain Current**

Measure the peak drain current under all operation conditions (including start-up and fault conditions). Look for transformer saturation (usually occurs at highest operating ambient temperatures). Verify that the peak current is less than the stated Absolute Maximum Rating in the data sheet.

#### **Thermal Check**

At maximum output power, for both minimum and maximum line voltage and maximum ambient temperature; verify that temperature specifications are not exceeded for the LYTSwitch-5, transformer, output diodes, output capacitors and clamp components.

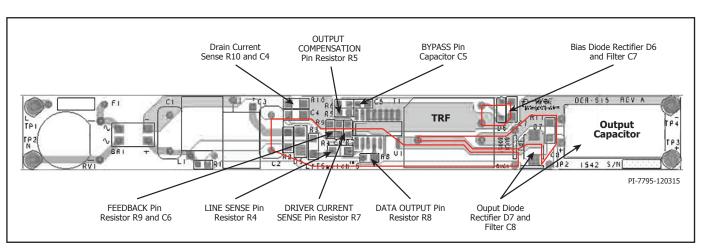

# **PCB Layout Considerations**

The EMI filter components should be located close together to improve filter effectiveness. Place the EMI filter components C1 and L1 as far away as possible from any switching nodes on the circuit board especially U1 drain node, output diode (D7) and the transformer (T1).

Care should be taken in placing the components on the layout that are used for processing input signals for the feedback loop — any high frequency noise coupled to the signal pins of U1 may affect proper system operation. The critical components in DER-515 are R5, R9, C6, R4, R7 and R8. It is highly recommended that these components be placed very close to the pins of U1 (to minimize long traces which could serve as antenna) and far away as much as possible from any high voltage and high current nodes in the circuit board to avoid noise coupling.

The bypass supply capacitor C5 should be placed directly across BYPASS pin and SOURCE pin of U1 for effective noise decoupling.

As shown in Figure 6, minimize the loop areas of the following switching circuit elements to lessen the creation of EMI.

- Loop area formed by the transformer output winding (T1), output rectifier diode (D7) and output capacitor (C8).

- Loop area formed by transformer bias winding (T1), rectifier diode (D6) and filter capacitor (C7).

- Loop area formed by input capacitor (C2), transformer (T1) main winding R10, C4 and internal MOSFET (U1).

Lastly, unlike discrete MOSFET designs where heat sinking is through the drain tab and which generates significant EMI, the LYTSwitch-5 devices employ low-side switching and the ground potential SOURCE pins are used for heat sinking. This allows the designer to maximize the copper area for good thermal management but without having the risk of increased EMI.

#### **Design Tools**

Up-to-date information on design tools can be found at the Power Integrations web site: www.power.com

LYTSwitch-5 PIXIs spreadsheet is located at PI Expert web lab: http://piexpertweblab.power.com/site/login.

Figure 6. DER-515 PCB Layout Example using SO-16B D Package. Shows the Location of Critical Components and Loop Areas on the PCB Layout.

# **Absolute Maximum Ratings**(1,3)

| DRAIN Pin Voltage:              | LYT521x     | 0.3 V to 650 V  |

|---------------------------------|-------------|-----------------|

|                                 | LYT522x     | 0.3 V to 725 V  |

| DRAIN Pin Peak Current(4)       | LYT5225     | 1.95 A (3.16 A) |

|                                 | LYT5216     | 3.25 A (4.0 A)  |

|                                 | LYT5226     | 2.64 A (4.35 A) |

|                                 | LYT5218     | 5.06 A (6.3 A)  |

|                                 | LYT5228     | 4.16 A (6.86 A) |

| BP, DO, DS, OC, L DS, FB I      | Pin Voltage | 0.3 V to 6.5 V  |

| Lead Temperature <sup>(2)</sup> |             | 260 °C          |

| Storage Temperature             |             | 65 to 150 °C    |

| Operating Junction Tempe        | erature     | 40 to 150 °C    |

Notes:

- 1. All voltages referenced to Source,  $T_A = 25$  °C.

- 2. 1/16 in. from case for 5 seconds.

- The Absolute Maximum Ratings specified may be applied, one at a time without causing permanent damage to the product. Exposure to Absolute Maximum Ratings for extended periods of time may affect product reliability.

- 4. The higher peak Drain current (in parentheses) is allowed while the Drain voltage is simultaneously less than 400 V for 725 V integrated MOSFET version, or less than 325 V for 650 V integrated MOSFET version.

#### **Thermal Resistance**

Thermal Resistance: SO-16B Package:

| $(\theta_{1A})$          | 3 °C/W <sup>(2)</sup> |

|--------------------------|-----------------------|

| $(\theta_{1\Delta})$     | 3 °C/W <sup>(3)</sup> |

| $(\theta_{10})^{(1)}$ 43 | 3 °C/W                |

Notes:

- 1. Measured per JESD 51-1, MIL-STD-883C-1012.1 and SEMI test method #G43-87.

- Soldered to 0.36 sq. inch (232 mm2) 2 oz. (610 g/m2) copper clad, with no external heat sink attached.

- 3. Soldered to 1 sq. in. (645 mm $^2$ ), 2 oz, (610 g/m $^2$ ) copper clad.

| Parameter                                            | Symbol               | Conditions  SOURCE = 0 V $T_{j} = -40  ^{\circ}\text{C}$ to +125 $^{\circ}\text{C}$ (Unless Otherwise Specified) |                     | Min   | Тур  | Max   | Units |

|------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|---------------------|-------|------|-------|-------|

| <b>Control Functions</b>                             |                      |                                                                                                                  |                     | '     |      |       | '     |

| Maximum                                              | f                    | T, = 25 °C                                                                                                       | Average             | 115.3 | 124  | 132.7 | kHz   |

| Output Frequency                                     | f <sub>MAX</sub>     | 1 <sub>3</sub> - 25 C                                                                                            | Peak-to-Peak Jitter |       | 8    |       | %     |

| Minimum                                              |                      | T 0.00 t- 135.00                                                                                                 | Average             |       | 40   |       | kHz   |

| Output Frequency                                     | f <sub>MIN</sub>     | $T_{J} = 0$ °C to 125 °C                                                                                         | Peak-to-Peak Jitter |       | 8    |       | %     |

| Frequency Jitter<br>Modulation Rate                  | f <sub>M</sub>       | See N                                                                                                            | lote A              |       | 1.76 |       | kHz   |

| Maximum On-Time                                      | T <sub>ON(MAX)</sub> | $T_{j} = 3$                                                                                                      | 25 °C               | 5.75  | 6.25 | 6.75  | μS    |

| Minimum On-Time                                      | T <sub>ON(MIN)</sub> | $T_{j} = 3$                                                                                                      | 25 °C               | 0.95  | 1.05 | 1.15  | μS    |

| FEEDBACK Pin Voltage                                 | V <sub>FB</sub>      | $T_{j} = 3$                                                                                                      | 25 °C               | 291   | 300  | 309   | mV    |

| FEEDBACK Pin Voltage<br>Triggering Cycle<br>Skipping | V <sub>FB(SK)</sub>  |                                                                                                                  |                     |       | 600  |       | mV    |

| FEEDBACK Pin<br>Overvoltage Threshold                | V <sub>FB(OV)</sub>  |                                                                                                                  |                     |       | 2000 |       | mV    |

| Feedback Pull-Up Current                             | $I_{FB}$             |                                                                                                                  |                     | -1.3  | -1.0 | -0.7  | μΑ    |

| Parameter                                                    | Symbol                 | Conditions  SOURCE = 0 V $T_{j} = -40$ °C to +125 °C  (Unless Otherwise Specified) |                          | Min   | Тур  | Max  | Units    |

|--------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------|--------------------------|-------|------|------|----------|

| Control Functions (cont.)                                    |                        | (Unless Other                                                                      | wise specified)          |       |      |      |          |

| control runctions (cont.)                                    | $I_{s_1}$              | V <sub>FB(ON)</sub> > V<br>(MOSFET no                                              | FB > V <sub>FB(SK)</sub> |       | 0.8  | 1.0  | mA       |

| DRAIN Supply Current                                         |                        | -                                                                                  | LYT5225, LYT52x6         |       | 1.1  | 1.4  |          |

| DRAIN Supply Current                                         | $I_{_{ m S2}}$         | MOSFET Switching                                                                   | LYT5218                  |       | 1.2  | 1.5  | mA       |

|                                                              |                        | at f <sub>MAX</sub>                                                                | LYT5228                  |       | 1.3  | 1.6  |          |

| BYPASS Pin<br>Charge Current                                 | I <sub>CH1</sub>       | V <sub>BP</sub> = 0 V,                                                             | T <sub>1</sub> = 25 °C   | -11.5 | -9.5 | -7.5 | mA       |

| BYPASS Pin<br>Charge Current                                 | ${\rm I}_{\rm CH2}$    | V <sub>BP</sub> = 4 V,                                                             | T <sub>3</sub> = 25 °C   | -8.8  | -6.8 | -4.8 | mA       |

| SYPASS Pin Voltage                                           | V <sub>BP</sub>        |                                                                                    |                          | 4.75  | 5.00 | 5.25 | V        |

| BYPASS Pin<br>Shunt Voltage                                  | V <sub>SHUNT</sub>     | I <sub>BP</sub> =                                                                  | 5 mA                     | 5.1   | 5.3  | 5.5  | V        |

| BYPASS Pin Power-Up<br>Reset Threshold Voltage               | V <sub>BP(RESET)</sub> |                                                                                    |                          | 4.4   | 4.6  | 4.8  | V        |

| Circuit Protection                                           |                        |                                                                                    | _                        |       | '    | ,    | <u>'</u> |

|                                                              |                        | di/dt = 974 mA/ $\mu$ s<br>T <sub>1</sub> = 25 °C                                  | LYT5225                  | 1232  | 1325 | 1418 |          |

| Current Limit                                                | I <sub>LIMIT</sub>     | di/dt = 1403 mA/ $\mu$ s<br>T <sub>3</sub> = 25 °C                                 | LYT52x6                  | 1767  | 1900 | 2033 | mA       |

|                                                              |                        | di/dt = 2239 mA/ $\mu$ s<br>T <sub>J</sub> = 25 °C                                 | LYT52x8                  | 2860  | 3075 | 3290 |          |

| eading Edge<br>Blanking Time                                 | t <sub>LEB</sub>       | $T_{j} = 3$                                                                        | 25 °C                    | 130   | 165  |      | ns       |

| Current Limit Delay                                          | T <sub>ILD</sub>       | T <sub>J</sub> = 2<br>See N                                                        | 25 °C<br>lote A          |       | 160  |      | ns       |

| Thermal Foldback<br>Temperature                              | T <sub>FB</sub>        | See N                                                                              | ote A                    | 138   | 142  | 146  | °C       |

| Thermal Shutdown<br>Temperature                              | T <sub>SD</sub>        | See N                                                                              | ote A                    | 155   | 160  | 165  | °C       |

| hermal Shutdown<br>lysteresis                                | T <sub>SD(H)</sub>     | See N                                                                              | ote A                    |       | 75   |      | °C       |

| SOA Switch ON-Time                                           | T <sub>ON(SOA)</sub>   | $T_{j} = 3$                                                                        | 25 °C                    |       | 610  | 690  | ns       |

| Auto-Restart Current<br>Threshold for Output<br>Indervoltage | I <sub>ouv</sub>       | T <sub>3</sub> = 25 °C                                                             |                          | 40    | 52   | 58   | μА       |

| Current Threshold for                                        | _                      | _                                                                                  | Threshold                | 116   | 120  | 124  |          |

| nput Voltage                                                 | $I_{\text{LOV+}}$      | T <sub>3</sub> = 25 °C                                                             | Hysteresis               |       | 5    |      | μΑ       |

| atch-Off Current<br>hreshold for Output<br>Overvoltage       | I <sub>oov</sub>       | T <sub>3</sub> = 25 °C                                                             |                          | 127   | 134  | 144  | μА       |

| INE-SENSE Pin Voltage                                        | V <sub>L</sub>         | I <sub>1</sub> = 100 μA                                                            | T = 25 °C                | 2.05  | 2.25 | 2.45 | V        |

| Parameter                                  | Symbol                                                                      | Conditions  SOURCE = 0 V  T <sub>3</sub> = -40 °C to +125 °C  (Unless Otherwise Specified) |                         | Min  | Тур  | Max  | Units |

|--------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------|------|------|------|-------|

| Output                                     |                                                                             |                                                                                            |                         |      |      |      |       |

| OUTPUT<br>COMPENSATION Pin                 | V <sub>oc</sub>                                                             | $I_{\text{OC}} = 100 \mu\text{A}$ $T_{_{1}} = 25 ^{\circ}\text{C}$                         |                         | 2.05 | 2.25 | 2.45 | V     |

|                                            |                                                                             | LYT5225                                                                                    | T <sub>1</sub> = 25 °C  |      | 3.80 | 4.35 |       |

| ON-State                                   |                                                                             | $I_D = 200 \text{ mA}$                                                                     | T <sub>J</sub> = 100 °C |      | 5.70 | 6.55 | Ω     |

|                                            |                                                                             | LYT52x6<br>I <sub>D</sub> = 300 mA                                                         | T <sub>J</sub> = 25 °C  |      | 2.75 | 3.15 |       |

| Resistance                                 | R <sub>DS(ON)</sub>                                                         |                                                                                            | T <sub>J</sub> = 100 °C |      | 4.25 | 4.90 |       |

|                                            |                                                                             | LYT52x8                                                                                    | T <sub>J</sub> = 25 °C  |      | 1.75 | 2.00 |       |

|                                            |                                                                             | $I_D = 500 \text{ mA}$                                                                     | T <sub>3</sub> = 100 °C |      | 2.70 | 3.10 |       |

| OFF-State Leakage                          | $I_{\scriptscriptstyle DSS}$                                                | $V_{BP} = 5.3 \text{ V}, V_{FB} > V_{FB}$ $T_{J} = 125$                                    | . ,                     |      |      | 200  | μА    |

| Duralida Valta na                          |                                                                             | V = 5.3 V. V > V                                                                           | LYT521x                 | 650  |      |      | V     |

| <b>Breakdown Voltage</b> BV <sub>DSS</sub> | $V_{BP} = 5.3 \text{ V}, V_{FB} > V_{FB(SK)}$ $T_{J} = 25 \text{ °C}$ LYT5. | LYT522x                                                                                    | 725                     |      |      | V    |       |

NOTES:

A. Guaranteed by design.

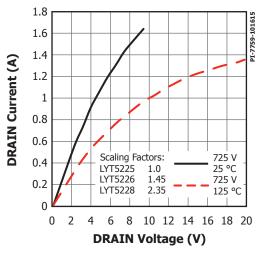

# **Typical Performance Curves**

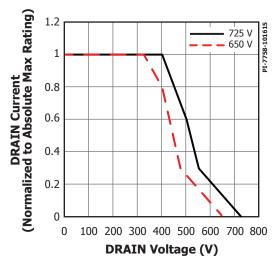

Figure 7. Power vs. Drain Voltage.

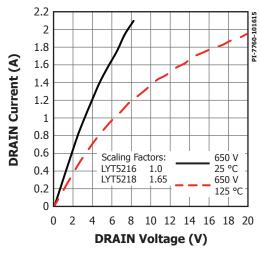

Figure 9. Drain Current vs. Drain Voltage.

Figure 8 Maximum Allowable Drain Current vs. Drain Voltage.

Figure 10. Drain Current vs. Drain Voltage.

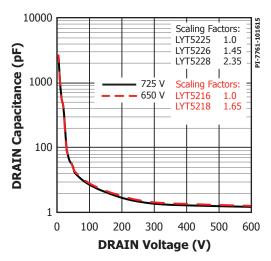

Figure 11. Drain Capacitance vs. DRAIN Pin Voltage.

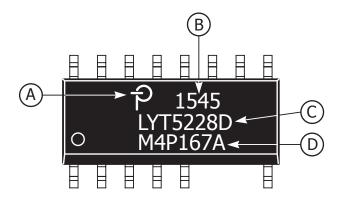

# **PACKAGE MARKING**

# **SO-16B**

- A. Power Integrations Registered Trademark

- B. Assembly Date Code (last two digits of year followed by 2-digit work week)

- C. Product Identification (Part #/Package Type)

- D. Lot Identification Code

PI-7800-111915

# **MSL Table**

| Part Number | MSL Rating |

|-------------|------------|

| LYT5225D    | 3          |

| LYT5216D    | 3          |

| LYT5226D    | 3          |

| LYT5218D    | 3          |

| LYT5228D    | 3          |

# **ESD** and Latch-Up Table

| Test                 | Conditions   | Results                                        |

|----------------------|--------------|------------------------------------------------|

| Latch-up at 125 °C   | JESD78D      | $> \pm 100$ mA or $> 2.5$ kV (max) on all pins |

| Human Body Model ESD | JESD22-A114F | > ±2000 V on all pins                          |

| Machine Model ESD    | JESD22-A115A | > ±200 V on all pins                           |

# **Part Ordering Information**

| Revision | Notes                                                                                                                                      | Date     |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|----------|

| В        | Code A Release.                                                                                                                            | 11/15    |

| В        | Made text corrections to LYTSwitch-5 Output Regulation section and PCB Layout Considerations section. Corrections made to Figures 5 and 6. | 12/03/15 |

| В        | Updated Figures 1a and 1b. Modified text in 1st paragraph of Input Filter section on page 4.                                               | 12/11/15 |

| С        | Corrected $I_{S2}$ , $T_{LEB}$ , $T_{FB}$ , $T_{SD}$ , $I_{OOV}$ parameters. Added $I_{OUV}$ and $V_L$ parameters.                         | 03/16    |

## For the latest updates, visit our website: www.power.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

#### Patent Information

The products and applications illustrated herein (including transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents, or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations patents may be found at www.power.com. Power Integrations grants its customers a license under certain patent rights as set forth at http://www.power.com/ip.htm.

### **Life Support Policy**

POWER INTEGRATIONS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF POWER INTEGRATIONS. As used herein:

- 1. A Life support device or system is one which, (i) is intended for surgical implant into the body, or (ii) supports or sustains life, and (iii) whose failure to perform, when properly used in accordance with instructions for use, can be reasonably expected to result in significant injury or death to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

The PI logo, TOPSwitch, TinySwitch, LinkSwitch, LYTSwitch, InnoSwitch, DPA-Switch, PeakSwitch, CAPZero, SENZero, LinkZero, HiperPFS, HiperTFS, HiperLCS, Qspeed, EcoSmart, Clampless, E-Shield, Filterfuse, FluxLink, StakFET, PI Expert and PI FACTS are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©2016, Power Integrations, Inc.

# **Power Integrations Worldwide Sales Support Locations**

#### **World Headquarters**

5245 Hellyer Avenue San Jose, CA 95138, USA. Main: +1-408-414-9200 Customer Service: Phone: +1-408-414-9665 Fax: +1-408-414-9765 e-mail: usasales@power.com

## China (Shanghai)

Rm 2410, Charity Plaza, No. 88 North Caoxi Road Shanghai, PRC 200030 Phone: +86-21-6354-6323 Fax: +86-21-6354-6325 e-mail: chinasales@power.com

# China (Shenzhen)

17/F, Hivac Building, No. 2, Keji Nan 8th Road, Nanshan District, Shenzhen, China, 518057 Phone: +86-755-8672-8689 Fax: +86-755-8672-8690 e-mail: chinasales@power.com

#### Germany

80337 Munich Germany Phone: +49-895-527-39110 Fax: +49-895-527-39200 e-mail: eurosales@power.com

Lindwurmstrasse 114

# India

#1, 14th Main Road Vasanthanagar Bangalore-560052 India Phone: +91-80-4113-8020 Fax: +91-80-4113-8023 e-mail: indiasales@power.com

#### Italy

Via Milanese 20, 3rd. Fl. 20099 Sesto San Giovanni (MI) Italy Phone: +39-024-550-8701

Phone: +39-024-550-8701 Fax: +39-028-928-6009 e-mail: eurosales@power.com

#### Japan

Kosei Dai-3 Bldg. 2-12-11, Shin-Yokohama, Kohoku-ku Yokohama-shi, Kanagawa 222-0033 Japan Phone: +81-45-471-1021 Fax: +81-45-471-3717

e-mail: japansales@power.com

#### Korea

RM 602, 6FL Korea City Air Terminal B/D, 159-6 Samsung-Dong, Kangnam-Gu, Seoul, 135-728, Korea Phone: +82-2-2016-6610 Fax: +82-2-2016-6630 e-mail: koreasales@power.com

## **Singapore**

51 Newton Road #19-01/05 Goldhill Plaza Singapore, 308900 Phone: +65-6358-2160 Fax: +65-6358-2015

e-mail: singaporesales@power.com

# Taiwan

5F, No. 318, Nei Hu Rd., Sec. 1 Nei Hu Dist. Taipei 11493, Taiwan R.O.C. Phone: +886-2-2659-4570 Fax: +886-2-2659-4550 e-mail: taiwansales@power.com

#### ПK

Cambridge Semiconductor, a Power Integrations company Westbrook Centre, Block 5, 2nd Floor Milton Road Cambridge CB4 1YG

Phone: +44 (0) 1223-446483 e-mail: eurosales@power.com

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

# Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

## Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.