- Single-Chip RF Transmitter for 868-MHz and 915-MHz ISM Bands

- 850-MHz to 950-MHz Operation

- FM/FSK Operation for Transmit

- 24-Bit Direct Digital Synthesizer (DDS) With 11-Bit DAC

- On-Chip Voltage-Controlled Oscillator (VCO) and Phase-Locked Loop (PLL)

- On-Chip Reference Oscillator

- Minimal External Components Required

- Low Power Consumption

- Typical Output Power of 7 dBm

- Typical Output Frequency Resolution of 230 Hz

- Ultrafast Lock Times From DDS Implementation

- Two Fully-Programmable Operational Modes

- 2.2-V to 3.6-V Operation

- Flexible Serial Interface to TI MSP430 Microcontroller

- 24-Pin Plastic Thin-Shrink Small-Outline Package (TSSOP)

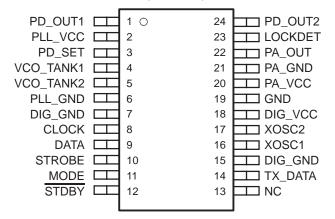

#### PW PACKAGE (TOP VIEW)

# description

The TRF4900 single-chip solution is an integrated circuit intended for use as a low cost FSK transmitter to establish a frequency-agile RF link. The device is available in a 24-lead TSSOP package and is designed to provide a fully-functional multichannel transmitter. The chip is intended for linear (FM) or digital (FSK) modulated applications in the new 868-MHz European band and the North American 915-MHz ISM band. The single chip transmitter operates down to 2.2 V and is expressly designed for low power consumption. The synthesizer has a typical channel spacing of approximately 230 Hz to allow narrow-band as well as wide-band applications. Due to the narrow channel spacing of the direct digital synthesizer (DDS), the DDS can be used to adjust the TX frequency and allows the use of inexpensive reference crystals.

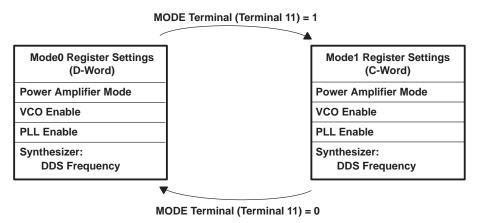

Two fully-programmable operation modes, Mode0 and Mode1, allow extremely fast switching between two preprogrammed settings (e.g., TX\_frequency\_0/TX\_frequency\_1) without reprogramming the device. Each functional block of the transmitter can be specifically enabled or disabled via the serial interface.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### ISM band standards

Europe has assigned a new unlicensed frequency band of 868 MHz to 870 MHz. This new band is specifically defined for short range devices with duty cycles from 0.1% to 100% in several sub-bands. The existing 433-MHz band for short-range devices in Europe has the great disadvantage of very high usage. The new European frequency band, due to the duty cycle assignment, allows a reliable RF link and makes many new applications possible.

The North American unlicensed ISM (industrial, scientific, and medical) band covers 902 MHz to 928 MHz (center frequency of 915 MHz) and is suitable for short range RF links.

#### transmitter

The transmitter consists of an integrated VCO, a complete fully-programmable direct digital synthesizer, and a power amplifier. The internal VCO can be used with an external tank circuit or an external VCO. The divider, prescaler, and reference oscillator require only the addition of an external crystal and a loop filter to provide a complete DDS with a typical frequency resolution of 230 Hz.

The 8-bit FSK frequency deviation register determines the frequency deviation in FSK mode. The modulation itself is done in the direct digital synthesizer, hence no additional external components are necessary.

Since the typical RF output power is approximately 7 dBm, no additional external RF power amplifier is necessary in most applications.

The TRF4900 RF transmitter is suitable for use in applications that include the TRF6900 RF transceiver.

#### baseband interface

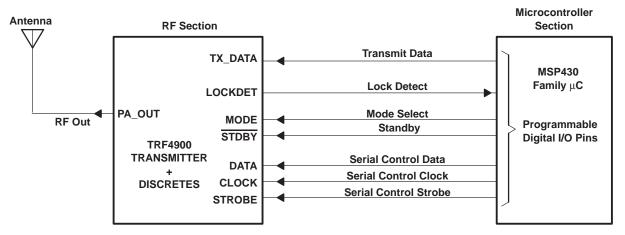

The TRF4900 can easily be interfaced to a baseband processor such as the Texas Instruments MSP430 ultralow-power microcontroller (see Figure 1). The TRF4900 serial control registers are programmed by the MSP430 and the MSP430 performs baseband operations in software.

Figure 1. System Block Diagram for Interfacing to the MSP430 Microcontroller

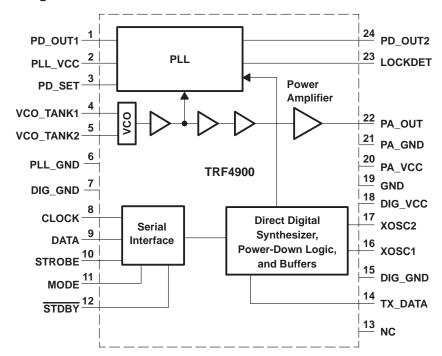

# functional block diagram

# **Terminal Functions**

| TERMIN    | IAL   |     |                                                                                                                                                                             |

|-----------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.   | 1/0 | DESCRIPTION                                                                                                                                                                 |

| CLOCK     | 8     | I   | Serial interface clock signal                                                                                                                                               |

| DATA      | 9     | I   | Serial interface data signal                                                                                                                                                |

| DIG_GND   | 7, 15 |     | Digital ground                                                                                                                                                              |

| DIG_VCC   | 18    |     | Digital supply voltage                                                                                                                                                      |

| GND       | 19    |     | Ground                                                                                                                                                                      |

| LOCKDET   | 23    | 0   | PLL lock detect output, active high. PLL locked when LOCKDET = 1.                                                                                                           |

| MODE      | 11    | I   | Mode select input. The functionality of the device in Mode0 or Mode1 can be programmed via the A-, B-, C-, and D-words of the serial control interface.                     |

| NC        | 13    |     | No connection                                                                                                                                                               |

| PA_GND    | 21    |     | Power amplifier ground                                                                                                                                                      |

| PA_OUT    | 22    | 0   | Power amplifier output, open collector                                                                                                                                      |

| PA_VCC    | 20    |     | Power amplifier supply voltage                                                                                                                                              |

| PD_OUT1   | 1     | 0   | Charge pump output – PLL in locked condition                                                                                                                                |

| PD_OUT2   | 24    | 0   | Charge pump output – PLL in unlocked condition                                                                                                                              |

| PD_SET    | 3     |     | Charge pump current setting terminal. An external resistor, R <sub>PD</sub> , is connected to this terminal to set the nominal charge pump current.                         |

| PLL_GND   | 6     |     | PLL ground                                                                                                                                                                  |

| PLL_VCC   | 2     |     | PLL supply voltage                                                                                                                                                          |

| STDBY     | 12    | I   | Standby control for the TRF4900, active low. While STDBY = 0, the contents of the control registers are still valid and can be programmed via the serial control interface. |

| STROBE    | 10    | I   | Serial interface strobe signal                                                                                                                                              |

| TX_DATA   | 14    | I   | Digital modulation buffered input for FSK/FM modulation of the carrier, active high                                                                                         |

| VCO_TANK1 | 4     | I   | VCO tank circuit connection. Should be left open if an external VCO is used.                                                                                                |

| VCO_TANK2 | 5     | I   | VCO tank circuit connection. May also be used to input an external VCO signal.                                                                                              |

| XOSC1     | 16    | 0   | Reference crystal oscillator connection                                                                                                                                     |

| XOSC2     | 17    | I   | Reference crystal oscillator connection. May be used as a single-ended clock input if an external crystal is not used.                                                      |

SLWS092G - JULY 2000 - REVISED FEBRUARY 2005

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

#### recommended operating conditions

|                                                                                      | MIN                  | TYP | MAX | UNIT |

|--------------------------------------------------------------------------------------|----------------------|-----|-----|------|

| Supply voltage, PA_VCC, PLL_VCC, DIG_VCC, DDS_VCC, VCC                               | 2.2                  |     | 3.6 | V    |

| Operating temperature                                                                | -20                  |     | 60  | °C   |

| High-level input voltage, VIH (DATA, CLOCK, STROBE, TX_DATA, MODE, STDBY)            | V <sub>CC</sub> -0.5 |     |     | V    |

| Low-level input voltage, V <sub>IL</sub> (DATA, CLOCK, STROBE, TX_DATA, MODE, STDBY) |                      |     | 0.5 | V    |

| High-level output voltage, V <sub>OH</sub> (LOCKDET); I <sub>OH</sub> = 0.5 mA       | V <sub>CC</sub> -0.5 |     |     | V    |

| Low-level output voltage, V <sub>OL</sub> (LOCKDET); I <sub>OL</sub> = 0.5 mA        |                      |     | 0.5 | V    |

electrical characteristics over full range of operating conditions, (typical values are at PA\_VCC, PLL\_VCC, DIG\_VCC, VCC = 3 V,  $T_A = 25^{\circ}\text{C}$ ) (unless otherwise noted)

#### supply current consumption in each mode

| MODE                      |                   | ACTIVE STAGES     | MIN | TYP | MAX  | UNIT |

|---------------------------|-------------------|-------------------|-----|-----|------|------|

| Power down (standby mode) |                   | None              |     | 0.5 |      | μΑ   |

|                           | PA STATE          |                   |     |     |      |      |

|                           | 0-dB attenuation  | ]                 |     | 58  | 75   |      |

| TX                        | 10-dB attenuation | DDS, PLL, VCO, PA |     | 27  |      | mA   |

|                           | 20-dB attenuation |                   |     | 22  |      |      |

|                           | PA disabled       | 7                 |     | 10  | 12.5 |      |

#### **VCO**

| PARAMETER       | TEST CONDITIONS | MIN | TYP | MAX                    | UNIT   |

|-----------------|-----------------|-----|-----|------------------------|--------|

| Frequency range |                 | 850 |     | 950                    | MHz    |

| Phase noise     | 50-kHz offset   |     | -94 |                        | dBc/Hz |

| Tuning voltage  |                 | 0.5 |     | V <sub>C</sub> C – 0.4 | V      |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup> RF terminal 22, PA\_OUT, is not protected against voltage stress higher than 800 V HBM.

NOTE 1: All GND and VCC terminals must be connected to either ground or supply, respectively, even if the function block is not used.

SLWS092G - JULY 2000 - REVISED FEBRUARY 2005

electrical characteristics over full range of operating conditions, (typical values are at PA\_VCC, PLL\_VCC, DIG\_VCC, VCC = 3 V,  $T_A = 25^{\circ}\text{C}$ ) (unless otherwise noted) (continued)

# direct digital synthesizer (DDS)

| PARAMETER                                       | TEST CONDITIONS | MIN     | TYP                | MAX  | UNIT    |         |

|-------------------------------------------------|-----------------|---------|--------------------|------|---------|---------|

| Defendance and Helenian defendance of           | As oscillator   |         | 15                 |      | 26      | N 41 1- |

| Reference oscillator input frequency, $f_{ref}$ | As buffer       |         | 15                 |      | 26      | MHz     |

| Programmable DDS divider ratio                  |                 | 22 bits | 0                  |      | 4194303 |         |

| DDS divider resolution, $\Delta f$              |                 | N:      | $\times f$ ref ÷ 2 | 24   |         |         |

| FSK – modulation register ratio                 | 8 bits          | 0       |                    | 1020 |         |         |

| FSK – modulation resolution                     |                 | N:      | $\times f$ ref ÷ 2 | 22   |         |         |

#### **PLL**

| PARAMETER                      | TEST CONDITIONS                                                       | MIN                            | TYP | MAX | UNIT |

|--------------------------------|-----------------------------------------------------------------------|--------------------------------|-----|-----|------|

| RF input frequency             |                                                                       | 850                            |     | 950 | MHz  |

| RF input power                 | Internal VCO bypassed; external input applied to VCO_TANK2            | -10                            |     | dBm |      |

| RF input divider ratio, N      |                                                                       | 256                            |     | 512 |      |

| RF output frequency resolution |                                                                       | $N \times f_{ref} \div 2^{24}$ |     |     |      |

| Charge pump current            | Programmable with external resistor, 100 k $\Omega$ nominal, APLL = 0 | 70                             |     | μА  |      |

#### power amplifier

| PARAMETER                           | TEST CONDITIONS                         | MIN | TYP    | MAX | UNIT |

|-------------------------------------|-----------------------------------------|-----|--------|-----|------|

| Frequency range                     |                                         | 850 |        | 950 | MHz  |

|                                     | 0-dB attenuation                        |     | 7      |     |      |

| A 100 A 1 A 100                     | 10-dB attenuation                       | -3  |        |     | 15   |

| Amplifier output power (see Note 2) | 20-dB attenuation                       | -12 |        |     | dBm  |

|                                     | Amplifier off                           |     |        | -52 |      |

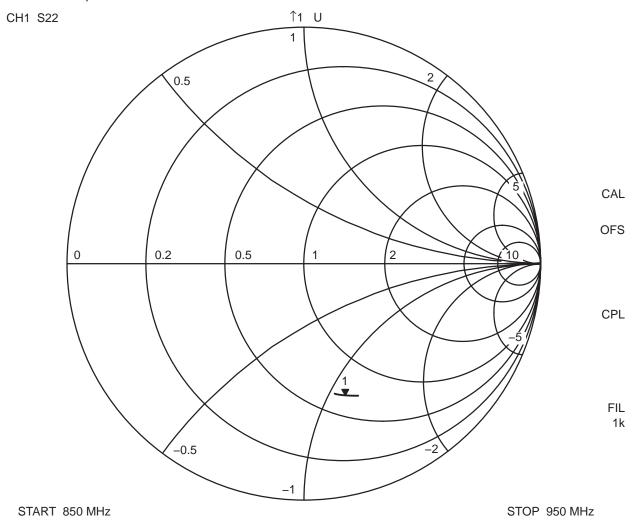

| Optimal load impedance              |                                         | See | Figure | 11  | Ω    |

| 2 <sup>nd</sup> -order harmonic     | V <sub>CC</sub> = 3 V, 0-dB attenuation | -13 |        | dBc |      |

| 3 <sup>rd</sup> -order harmonic     | V <sub>CC</sub> = 3 V, 0-dB attenuation |     | -32    |     | dBc  |

NOTE 2: The device and output matching network (see *Application Information* section) is designed to provide the output power into a 50-Ω load. The device stability was tested (no parasitic oscillations) with an output VSWR of 10:1 over all phase angles and is not tested in production.

### typical mode switching and lock times

| OPERATION                 | TEST CONDITIONS                                                               | MIN | TYP | MAX | UNIT |

|---------------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

| Standby to transmit time† | From rising edge of STDBY to valid RF signal at PA_OUT, APLL = 111b (maximum) |     | 500 |     | μs   |

<sup>†</sup> Highly dependent upon loop filter topology

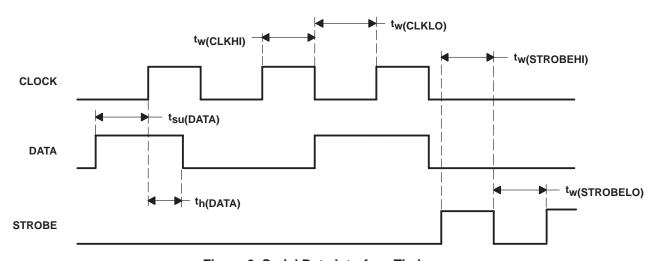

# timing data for serial interface (see Figure 2)

|                       | PARAMETER                                              | MIN | MAX | UNIT |

|-----------------------|--------------------------------------------------------|-----|-----|------|

| f(CLOCK)              | CLOCK frequency                                        |     | 20  | MHz  |

| tw(CLKHI)             | CLOCK high time pulse width, CLOCK high                | 25  |     | ns   |

| tw(CLKLO)             | CLOCK low time pulse width, CLOCK low                  | 25  |     | ns   |

| t <sub>su(DATA)</sub> | Setup time, data valid before CLOCK high               | 25  |     | ns   |

| <sup>t</sup> h(DATA)  | Hold time, data valid after CLOCK high                 | 25  |     | ns   |

| tw(STROBEHI)          | Strobe high time pulse width, STROBE high (see Note 3) | 25  |     | ns   |

| tw(STROBELO)          | Strobe low time pulse width, STROBE low                | 25  |     | ns   |

NOTE 3: CLOCK and DATA must both be low when STROBE is asserted (STROBE = 1).

Figure 2. Serial Data Interface Timing

# detailed description

#### reference oscillator

The reference oscillator provides the DDS system clock. It allows operation, with a suitable external crystal, between 15 MHz and 26 MHz.

An external oscillator can be used to supply clock frequencies between 15 MHz and 26 MHz. The external oscillator should be directly connected to XOSC2, terminal 17. The other oscillator terminal (XOSC1, terminal 16) should be left open or can be used as a buffered version of the signal applied at terminal 17 (see Figure 3). The same crystal or externally supplied oscillator signal is used to derive both the transmit and receive frequencies.

Figure 3. Applying an External Oscillator Signal

### detailed description (continued)

#### direct digital synthesizer

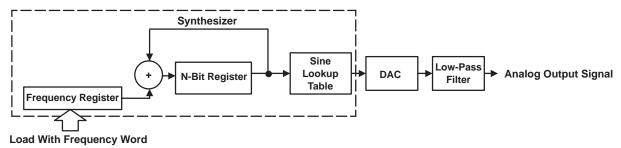

### general principles of DDS operation

In general, a direct digital synthesizer (DDS) is based on the principle of generating a sinewave signal in the digital domain. Benefits include high precision, wide frequency range, a high degree of software programmability, and extremely fast lock times.

Figure 4 shows a block diagram of a typical DDS. It generally consists of an accumulator, sine lookup table, a digital-to-analog converter, and a low-pass filter. All digital blocks are clocked by the reference oscillator.

Figure 4. Typical DDS Block Diagram

The DDS constructs an analog sine waveform using an N-bit adder counting up from 0 to 2<sup>N</sup> in steps of the frequency register whereby generating a digital ramp waveform. Each number in the N-bit output register is used to select the corresponding sine wave value out of the sine lookup table. After the digital-to-analog conversion, a low-pass filter is necessary to suppress unwanted spurious responses.

The analog output signal can be used as a reference input signal for a phase-locked loop (PLL). The PLL circuit multiplies the reference frequency by a predefined factor.

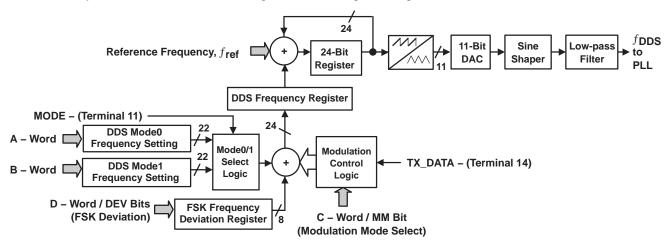

#### TRF4900 direct digital synthesizer implementation

Figure 5 shows a block diagram of the DDS implemented in the TRF4900. It consists of a 24-bit accumulator clocked by the reference oscillator along with control logic settings.

Figure 5. DDS Block Diagram as Implemented in the TRF4900

#### TRF4900 direct digital synthesizer implementation (continued)

The frequency of the reference oscillator,  $f_{ref}$ , is the DDS sample frequency, which also determines the maximum DDS output frequency. Together with the accumulator width (in bits), the frequency resolution of the DDS can be calculated. Multiplied by the divider ratio (prescaler) of the PLL, N, the minimum frequency step size of the TRF4900 is calculated as follows:

$$\Delta f = N \times \frac{f_{\text{ref}}}{2^{24}}$$

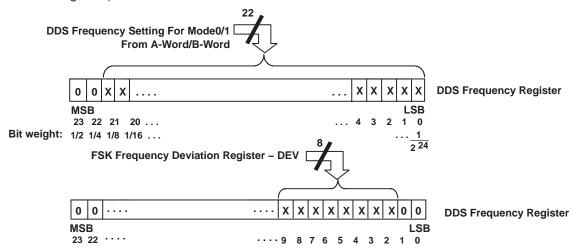

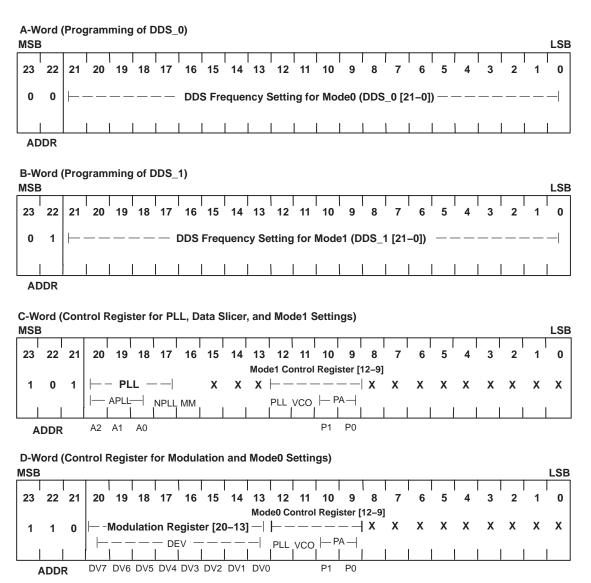

The 24-bit accumulator can be programmed via two 22-bit frequency setting registers (the A-word determines the mode0 frequency, the B-word determines the mode1 frequency) with the two MSB bits set to 0. Consequently, the maximum bit weight of the DDS system is reduced to 1/8 (see Figure 6). This bit weight corresponds to a VCO output frequency of  $(f_{\text{ref}}/8) \times \text{N}$ . Depending on the MODE terminal's (terminal 11) logic level, the internal mode select logic loads the frequency register with either the DDS\_0 or DDS\_1 frequency (see Figure 5 and Figure 6).

Figure 6. Implementation of the DDS Frequency and FSK Frequency Deviation in the DDS Frequency Register

The VCO output frequency,  $f_{\text{out}}$ , which is dependent on the DDS\_x frequency settings (DDS\_0 in the A-word or DDS\_1 in the B-word), can be calculated as follows:

$$f_{\text{out}} = \text{DDS}\_x \times N \times \frac{f_{\text{ref}}}{2^{24}} = N \times \frac{f_{\text{ref}} \times \text{DDS}\_x}{2^{24}}$$

If FSK modulation is selected (MM=0; C-Word, bit 16), then the 8-bit FSK deviation register can be used to program the frequency deviation of the 2-FSK modulation. Figure 6 illustrates where the 8 bits of the FSK deviation register map into the 24-bit DDS frequency register. Since the two LSBs are set to 0, the total FSK deviation can be determined as follows:

$$\Delta f_{2\text{-FSK}} = N \times \frac{\text{DEV} \times f_{\text{ref}}}{2^{22}}$$

Hence, the 2-FSK frequency, set by the level on the TX\_DATA is calculated as follows:

$$f_{\text{out1:TX\_DATA} = \text{Low}} = \text{N} \times \frac{f_{\text{ref}} \times \text{DDS\_x}}{2^{24}} \qquad f_{\text{out2:TX\_DATA} = \text{High}} = \text{N} \times \frac{f_{\text{ref}} \times (\text{DDS\_x} + 4 \times \text{DEV})}{2^{24}}$$

This frequency modulated output signal is used as a reference input signal for the PLL circuit. Channel width (frequency deviation) for 2-FSK modulation and channel spacing are software programmable. The minimum channel width and minimum channel spacing depend on the RF system frequency plan.

SLWS092G - JULY 2000 - REVISED FEBRUARY 2005

#### TRF4900 direct digital synthesizer implementation (continued)

Note that the frequencies  $f_{\text{out1}}$  and  $f_{\text{out2}}$  are centered about the frequency  $f_{\text{center}} = (f_{\text{out1}} + f_{\text{out2}})/2$ . When transmitting FSK,  $f_{\text{center}}$  is considered to be the effective carrier frequency and any receiver local oscillator (LO) should be set to the same  $f_{\text{center}}$  frequency  $\pm$  the receiver's IF frequency  $(f_{\text{IF}})$  for proper reception and demodulation.

For the case of low-side injection, the receiver LO would be set to  $f_{LO}$  =  $f_{center}$  –  $f_{IF}$ . Conversely, for high-side injection, the receiver LO would be set to  $f_{LO}$  =  $f_{center}$  +  $f_{IF}$ .

Since the DDS registers are static, preprogrammed values are retained during standby mode. This feature greatly reduces turnon time, reduces current consumption when coming out of standby mode, and enables fast lock-times. The PLL lock-times ultimately determine when data can be transmitted or received.

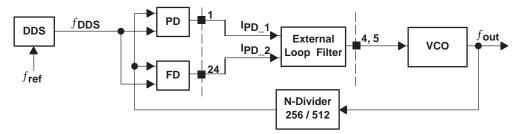

# phase-locked loop

The phase-locked loop (PLL) of the TRF4900 consists of a phase detector (PD) and a frequency acquisiton aid (FD) (including two charge pumps), an external loop filter, voltage-controlled oscillator (VCO), and a programmable fixed prescaler (N-divider) in the feedback loop (see Figure 7).

The PLL as implemented in the TRF4900 multiplies the DDS output frequency and further suppresses the unwanted spurious signals produced by the direct digital synthesizer.

Figure 7. Basic PLL Structure

#### VCO

A modified Colpitts oscillator architecture with an external resonant circuit is used for the TRF4900. The internal bias current network adjusts the signal amplitude of the VCO. This allows a wide range of Q-factors (30...60) for the external tank circuit.

The VCO can be bypassed by applying an external RF signal at VCO\_TANK2, terminal 5. To drive the internal PLL and power amplifier, a typical level of -10 dBm should be applied. When an external VCO is used, the x VCO bit should be set to 0.

#### phase detector and charge pumps

The TRF4900 contains two charge pumps for locking to the desired frequency: one for coarse tuning of the frequency differences (called the frequency acquisition aid) and one for fine tuning of the phase differences (used in conjunction with the phase detector).

The XOR phase detector and charge pumps produce a mean output current that is proportional to the phase difference between the reference frequency and the VCO frequency divided by N; N = 256 or 512. The TRF4900 generates the current pulses  $I_{PD-1}$  during normal operation (PLL locked).

An additional slip detector and acquisition aid charge pump generates current pulses at terminal PD\_OUT2 during the lock-in of the PLL. This charge pump is turned off when the PLL locks in order to reduce current consumption. The multiplication factor of the acquisition aid current  $I_{PD_2}$  can be programmed by three bits (APLL) in the C-word.

#### phase detector and charge pumps (continued)

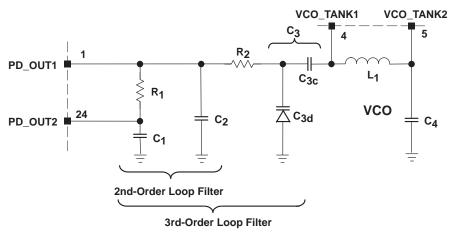

The slip detector output, PD\_OUT2, at terminal 24 should be connected directly to the loop filter capacitor  $C_1$ , as shown in Figure 10. The nominal charge pump current  $I_0$  is determined by the external resistor  $R_{PD}$ , connected to terminal 3, and can be calculated as follows:

$$I_0 = \frac{7 \, V}{R_{PD}}$$

During normal operation (PLL locked), the acquisition aid charge pump is disabled and the maximum charge pump current  $I_{PD-1}$  is determined by the nominal value  $I_0$  (see Figure 8).

Figure 8. Normal Operation Charge Pump Current, IPD 1

Each time the PLL is in an unlocked condition, the acquisition aid charge pump generates current pulses  $I_{PD_2}$ . The  $I_{PD_2}$  current pulses are APLL times larger than  $I_0$  (see Figure 9).

Figure 9. Acquisition Aid, IpD 2, and Normal Operation, IpD 1, Charge Pump Currents

### programmable divider

The internal divider ratio, N, can be set to 256 or 512 via the C-word. Since a higher divider ratio adds additional noise within the multiplication loop, the lowest divider ratio possible for the target application should be used.

#### loop filter

Loop filter designs are a balance between lock-time, noise, and spurious suppression. For the TRF4900, common loop filter design rules can be used to determine an appropriate low-pass filter. Standard formulas can be used as a first approach to calculate a basic loop filter. Figure 10 illustrates a basic 3<sup>rd</sup>-order loop filter.

Figure 10. Basic 3<sup>rd</sup>-Order Loop Filter Structure

#### loop filter (continued)

For maximum suppression of the unwanted frequency components, the loop filter bandwidth should generally be made as narrow as possible. At the same time, the filter bandwidth has to be wide enough to allow for the 2-FSK modulation and appropriate lock-time. A detailed simulation of the phase-locked loop should be performed and later verified on PCB implementations.

# power amplifier

The power amplifier (PA) can be programmed via two bits (P0 and P1 in the D-word) to provide varying output power levels. Several control loops are implemented internally to set the output power and to minimize the sensitivity of the power amplifier to temperature, load impedance, and power supply variations. The output stage of the PA usually operates in Class-C and enables easy impedance matching. PA\_OUT, terminal 22, is an open collector output terminal.

Figure 11. Power Amplifier Output Impedance (\$22) at Device Terminal 22

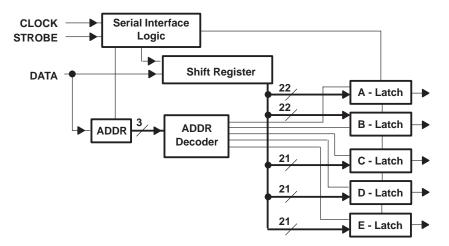

#### serial control interface

A 3-wire unidirectional serial bus (CLOCK, DATA, STROBE) is used to program the TRF4900 (see Figure 12). The internal registers contain all user programmable variables including the DDS frequency setting registers, as well as all control registers.

At each rising edge of the CLOCK signal, the logic value on the DATA terminal is written into a 24-bit shift register. Setting the STROBE terminal high loads the programmed information into the selected latch. While the STROBE signal is high, the DATA and CLOCK lines must be low (see Figure 2). Since the CLOCK and STROBE signals are asynchronous, care should be taken to ensure the signals remain free of glitches and noise.

As additional leading bits are ignored, only the least significant 24 bits are serial-clocked into the shift register. Due to the static CMOS design, the serial interface consumes virtually no current and it can be programmed in active as well as in standby mode.

Figure 12. Serial Interface Block Diagram

The control words are 24 bits in length. The first incoming bit functions as the most significant bit (MSB).

To fully program the TRF4900, four 24-bit words must be sent: the A-, B-, C-, and D-words. If individual bits within a word are to be changed, then it is sufficient to program only the appropriate 24-bit word.

Figure 13 shows the definition of the control words. Tables 1, 2, and 3 describe the function of each parameter.

The E-Latch, addressed by an ADDR equal to 111, is reserved for test purposes and should not be used. Inadvertently addressing the E-Latch activates the test modes of the TRF4900.

If the test mode has been inadvertently activated, it can only be exited by switching  $V_{CC}$  on and off or by clearing the E-Latch. The E-Latch can be cleared by addressing it and resetting its entire contents by programming 1110 0000 0000 0000 0000 0000.

As part of a proper power-up sequence, it is recommended to clear the E-Latch each time  $V_{CC}$  is applied before starting further operations with the TRF4900.

NOTE: Start programming with MSB and ensure that the CLOCK and DATA lines are low during the rising edge of the strobe signal.

Figure 13. Serial Control Word Format

Table 1. Mode0 Control Register Description (D-Word)

| 0)/440-01 | BIT      | NUMBER  | DECODINE                                                                                                                                                                                                           | INITIAL S<br>AFTER PO |                  |

|-----------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|

| SYMBOL    | LOCATION | OF BITS | DESCRIPTION                                                                                                                                                                                                        | DEFAULT<br>STATE      | DEFAULT<br>VALUE |

| 0_PA      | [10–9]   | 2       | Power amplifier mode  P1 P0  0 0 = disabled  0 1 = 10-dB attenuation, enable modulation via TX_DATA  1 0 = 20-dB attenuation, enable modulation via TX_DATA  1 1 = 0-dB attenuation, enable modulation via TX_DATA | Disabled              | 00b              |

| 0_VCO     | [11]     | 1       | During operation, this bit should always be enabled (1 = enabled), unless an external VCO is used.                                                                                                                 | Disabled              | 0b               |

| 0_PLL     | [12]     | 1       | Enable PLL (DDS system, VCO, RF divider, phase comparator and charge pump)  1 = enabled 0 = disabled                                                                                                               | Disabled              | 0b               |

# Table 2. Mode1 Control Register Description (C-Word)

| CVMDOI | BIT<br>LOCATION | NUMBER<br>OF BITS | DECORPTION                                                                                                                                                                                                         |                  | INITIAL SETTINGS<br>AFTER POWER UP |  |  |

|--------|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------|--|--|

| SYMBOL |                 |                   | DESCRIPTION                                                                                                                                                                                                        | DEFAULT<br>STATE | DEFAULT<br>VALUE                   |  |  |

| 1_PA   | [10–9]          | 2                 | Power amplifier mode  P1 P0  0 0 = disabled  0 1 = 10-dB attenuation, enable modulation via TX_DATA  1 0 = 20-dB attenuation, enable modulation via TX_DATA  1 1 = 0-dB attenuation, enable modulation via TX_DATA | Disabled         | 00b                                |  |  |

| 1_VCO  | [11]            | 1                 | During operation, this bit should always be enabled (1 = enabled), unless an external VCO is used.                                                                                                                 | Disabled         | 0b                                 |  |  |

| 1_PLL  | [12]            | 1                 | Enable PLL (DDS system, VCO, RF divider, phase comparator and charge pump)  1 = enabled 0 = disabled                                                                                                               | Disabled         | 0b                                 |  |  |

**Table 3. Miscellaneous Control Register Description**

| OVALDOL | WORD             | BIT     | NUMBER           | DESCRIPTION                                                                                                  |             | ETTINGS<br>OWER UP |

|---------|------------------|---------|------------------|--------------------------------------------------------------------------------------------------------------|-------------|--------------------|

| SYMBOL  | LOCATION OF BITS |         | DEFAULT<br>STATE | DEFAULT<br>VALUE                                                                                             |             |                    |

| DDS_0   | A-word           | [21–0]  | 22               | DDS frequency setting in Mode0                                                                               | 0           | All 0s             |

| DDS_1   | B-word           | [21–0]  | 22               | DDS frequency setting in Mode1                                                                               | 0           | All 0s             |

| DEV     | D-word           | [20-13] | 8                | FSK frequency deviation register                                                                             | 0           | All 0s             |

| APLL    | C-word           | [20–18] | 3                | Acceleration factor for the frequency acquisition aid charge pump    A2                                      | 0           | 000b               |

| NPLL    | C-word           | [17]    | 1                | PLL divider ratio 0 = divide by 256 1 = divide by 512                                                        | 256         | 0b                 |

| MM      | C-word           | [16]    | 1                | Modulation mode select. Sets the behavior of terminal TX_DATA to FSK data input.  0 = FSK/FM  1 = do not use | FSK<br>mode | 0b                 |

# operating modes

Table 4 and Table 5 illustrate operating modes and transmit frequencies as set by the STDBY, MODE, and TX\_DATA terminals used in conjunction with the DDS frequency settings.

Table 4. Transmitting Data in FSK Mode (MM bit set to 0)

|       |          | _       | •                                                                                                    |

|-------|----------|---------|------------------------------------------------------------------------------------------------------|

|       | TERMINAL | -       | TO ANOMIT EDECLIENCY                                                                                 |

| STDBY | MODE     | TX_DATA | TRANSMIT FREQUENCY                                                                                   |

| 1     | 0        | 0       | $f_{\text{out}} = f_{\text{ref}} \times N \times (DDS_0)/2^{24}$                                     |

| 1     | 0        | 1       | $f_{\text{out}} = f_{\text{ref}} \times N \times (DDS_0 + 4 \times DEV)/2^{24}$                      |

| 1     | 1        | 0       | $f_{\text{out}} = f_{\text{ref}} \times N \times (DDS_1)/2^{24}$                                     |

| 1     | 1        | 1       | $f_{\text{out}} = f_{\text{ref}} \times \text{N} \times (\text{DDS}_1 + 4 \times \text{dev})/2^{24}$ |

### operating modes (continued)

Table 5. Operating Mode Per STDBY Terminal

| STDBY | OPERATING MODE                                      |

|-------|-----------------------------------------------------|

| 0     | Standby/programming mode – Power down of all blocks |

| 1     | Operating mode and programming mode                 |

Two independent operating modes, Mode0 and Mode1, allow extremely fast switching between two preprogrammed settings by toggling the MODE terminal. Each mode can be viewed as a bank of configuration registers which store the frequency settings and the enable/disable settings for each functional block of the TRF4900. The MODE terminal is then used to asynchronously switch between Mode0 and Mode1 as shown in Figure 14. Table 6 shows several examples of operating sequences.

Figure 14. Interaction Between MODE Terminal and Preprogrammed Mode0 and Mode1 Control Registers

**Table 6. Operating Mode Examples**

| FUNCTION / DESCRIPTION                                                  | MODE0                   | MODE1                               |

|-------------------------------------------------------------------------|-------------------------|-------------------------------------|

| Transmit on two different frequencies                                   | Transmit on frequency 0 | Transmit on frequency 1             |

| Emulate FSK transmit operation using the MODE terminal for wideband FSK | Transmit on frequency 0 | Transmit on frequency 0 + deviation |

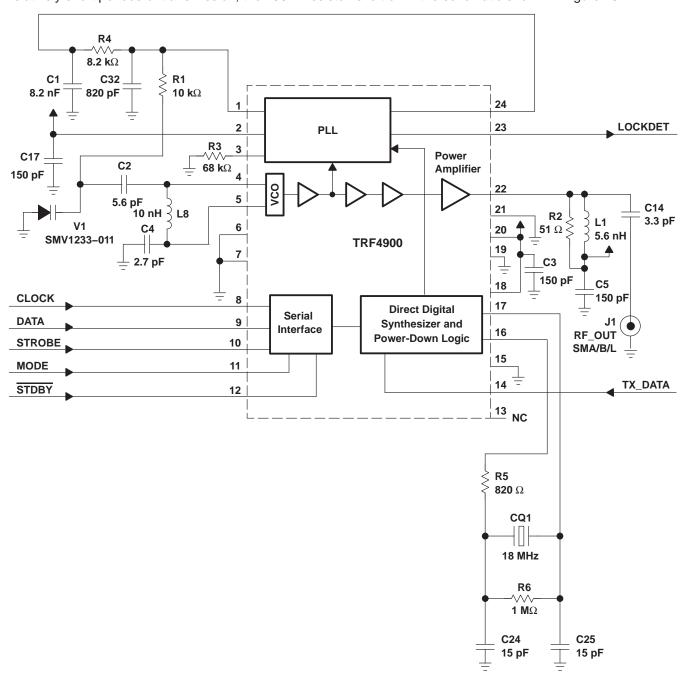

A typical application schematic for an FSK system operating in the European 868-MHz to 870-MHz ISM band is shown in Figure 15. If the TRF4900 is left on for long periods of time without going into standby mode, a  $100-\Omega$  resistor to ground should be added at terminal 4 or terminal 5 to reduce tuning voltage drift as in Figure 16. If the  $100-\Omega$  resistor is present, C2 and C4 may be changed to adjust the tuning range as needed. Since most EU applications involve relatively short periods of transmission, the  $100-\Omega$  resistor is left off in the schematic shown in Figure 15.

Figure 15. Typical Application Schematic for 868-MHz to 870-MHz European ISM Band

# external component list for Figure 15 (5% tolerance unless otherwise noted)

| DESIGNATOR | DESCRIPTION (SIZE) | VALUE       | MANUFACTURER            | PART NUMBER/COMMENTS |

|------------|--------------------|-------------|-------------------------|----------------------|

| C1         | Capacitor          | 8.2 pF      |                         |                      |

| C2         | Capacitor          | 5.6 pF      |                         |                      |

| C3         | Capacitor          | 150 pF      |                         |                      |

| C4         | Capacitor          | 2.7 pF      |                         |                      |

| C5         | Capacitor          | 150 pF      |                         |                      |

| C14        | Capacitor          | 3.3 pF      |                         |                      |

| C17        | Capacitor          | 150 pF      |                         |                      |

| C24        | Capacitor          | 15 pF       |                         |                      |

| C25        | Capacitor          | 15 pF       |                         |                      |

| C32        | Capacitor          | 820 pF      |                         |                      |

| L1         | Coil               | 5.6 nH      | Murata                  | LQN21A6N8D04         |

| L8         | Coil               | 10 nH       | Murata                  | LQW1608              |

| R1         | Resistor           | 10 kΩ       |                         |                      |

| R2         | Resistor           | 51 Ω        |                         |                      |

| R3         | Resistor           | 68 kΩ       |                         |                      |

| R4         | Resistor           | 8.2 kΩ      |                         |                      |

| R5         | Resistor           | 820 Ω       |                         |                      |

| R6         | Resistor           | 1 ΜΩ        |                         |                      |

| V1         | Varactor diode     | SMV1233-011 | Alpha Industries        |                      |

| CQ1        | Crystal            | 18 MHz      | CMAC Frequency Products | CX-1 SMI             |

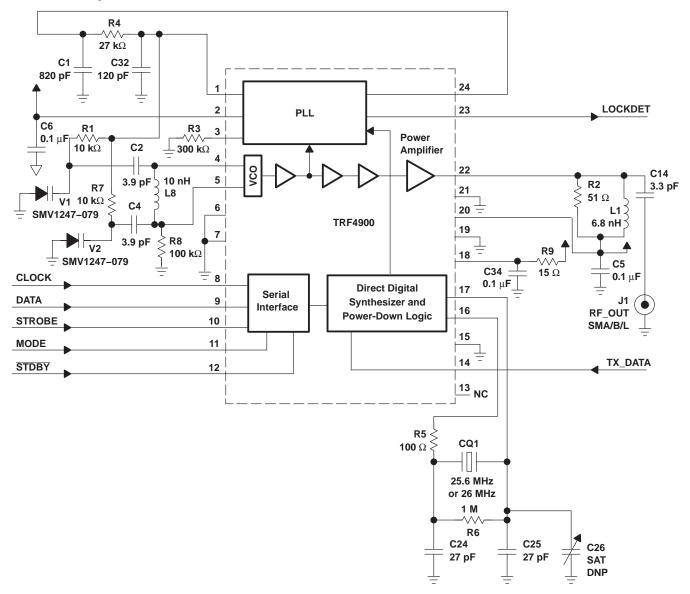

A typical application schematic for an FSK system operating in the North American 902-MHz to 928-MHz ISM band as shown in Figure 16.

Figure 16. Typical Application Schematic for 902-MHz to 928-MHz North American ISM Band

# external component list for Figure 16 (5% tolerance unless otherwise noted)

| DESIGNATOR | DESCRIPTION (SIZE) | VALUE                 | MANUFACTURER                                            | PART NUMBER/COMMENTS                     |

|------------|--------------------|-----------------------|---------------------------------------------------------|------------------------------------------|

| C1         | Capacitor          | 820 pF                |                                                         |                                          |

| C2         | Capacitor          | 3.9 pF                |                                                         |                                          |

| C4         | Capacitor          | 3.9 pF                |                                                         |                                          |

| C5         | Capacitor          | 0.1 μF                |                                                         |                                          |

| C6         | Capacitor          | 0.1 μF                |                                                         |                                          |

| C14        | Capacitor          | 3.3 pF                |                                                         |                                          |

| C24        | Capacitor          | 27 pF                 |                                                         |                                          |

| C25        | Capacitor          | 27 pF                 |                                                         |                                          |

| C26        | Capacitor          |                       |                                                         | Select at test (SAT), Do not place (DNP) |

| C32        | Capacitor          | 120 pF                |                                                         |                                          |

| C34        | Capacitor          | 0.1 μF                |                                                         |                                          |

| L1         | Coil               | 6.8 nH                | Murata                                                  | LQN21A6N8D04                             |

| L8         | Coil               | 10 nH                 | Murata                                                  | LQW1608                                  |

| R1         | Resistor           | 10 kΩ                 |                                                         |                                          |

| R2         | Resistor           | 51 Ω                  |                                                         |                                          |

| R3         | Resistor           | 300 kΩ                |                                                         |                                          |

| R4         | Resistor           | 27 kΩ                 |                                                         |                                          |

| R5         | Resistor           | 100 Ω                 |                                                         |                                          |

| R6         | Resistor           | 1 ΜΩ                  |                                                         |                                          |

| R7         | Resistor           | 10 kΩ                 |                                                         |                                          |

| R8         | Resistor           | 100 kΩ                |                                                         |                                          |

| R9         | Resistor           | 15 Ω                  |                                                         |                                          |

| V1, V2     | Varactor diode     | SMV1247-079           | Alpha Industries                                        |                                          |

| CQ1        | Crystal            | 25.6 MHz or<br>26 MHz | ICM (International Crystal Manufacturing, Incorporated) | 865842: 25.6 MHz<br>865850: 26 MHz       |

om 4-Aug-2008

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| TRF4900PW        | NRND                  | TSSOP           | PW                 | 24   | 60             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TRF4900PWG4      | NRND                  | TSSOP           | PW                 | 24   | 60             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TRF4900PWR       | NRND                  | TSSOP           | PW                 | 24   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TRF4900PWRG4     | NRND                  | TSSOP           | PW                 | 24   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

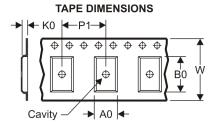

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

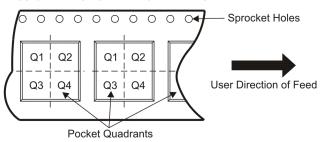

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     |       | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TRF4900PWR | TSSOP | PW                 | 24 | 2000 | 330.0                    | 16.4                     | 6.95    | 8.3     | 1.6     | 8.0        | 16.0      | Q1               |

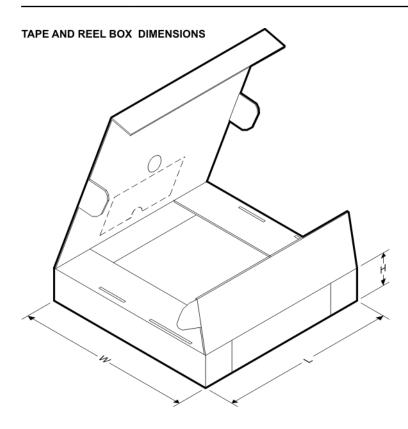

#### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TRF4900PWR | TSSOP        | PW              | 24   | 2000 | 346.0       | 346.0      | 33.0        |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: <u>org@eplast1.ru</u>

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.