# Intel® Ethernet Controller X550

### **Datasheet**

## **Ethernet Networking Division (ND)**

#### **PRODUCT FEATURES**

#### General

- Serial Flash interface

- Configurable LED operation for software or customizing OEM LED displays

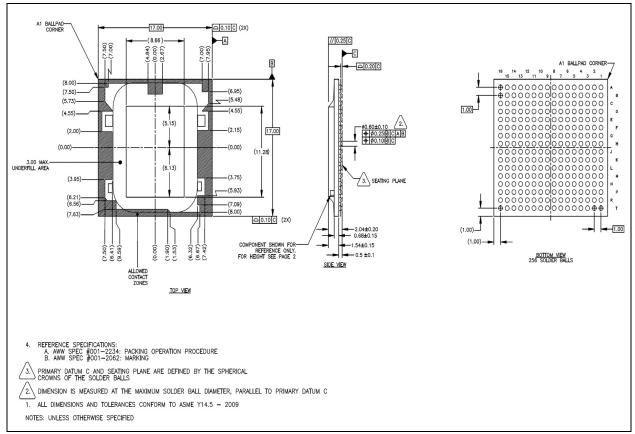

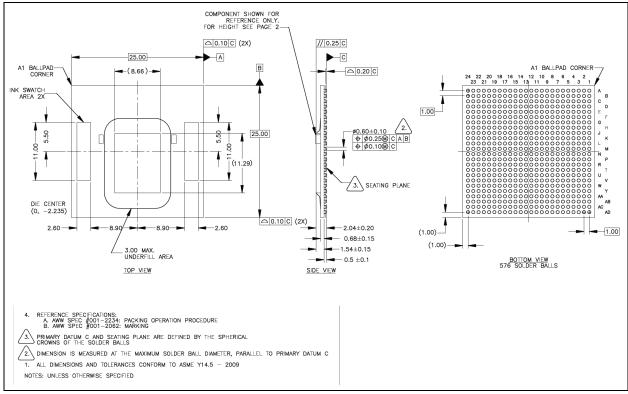

- Device disable capability Package size 25 mm x 25 mm (X550-BT2) Package size 17 mm x 17 mm (X550-AT2)

#### **Networking**

- 10 GbE/1 GbE/100 Mb/s copper PHYs integrated on-chip Support for jumbo frames of up to 15.5 KB Flow control support: send/receive pause frames and receive FLEO theoretical supports. FIFO thresholds

- Statistics for management and RMON 802.1q VLAN support TCP segmentation offload: up to 256 KB IPv6 support for IP/TCP and IP/UDP receive checksum offload

- Fragmented UDP checksum offload for packet reassembly

- Message Signaled Interrupts (MSI)

Message Signaled Interrupts (MSI-X)

Interrupt throttling control to limit maximum interrupt rate

and improve CPU usage

Flow Director (16 x 8 and 32 x 4)

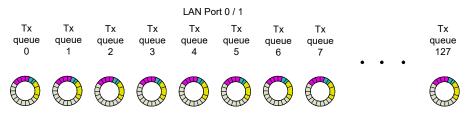

128 transmit queues

Receive packet rult bodge

- Receive packet split header Receive header replication Dynamic interrupt moderation

- TCP timer interrupts Relaxed ordering

- Support for 64 virtual machines per port (64 VMs x 2

- queues)

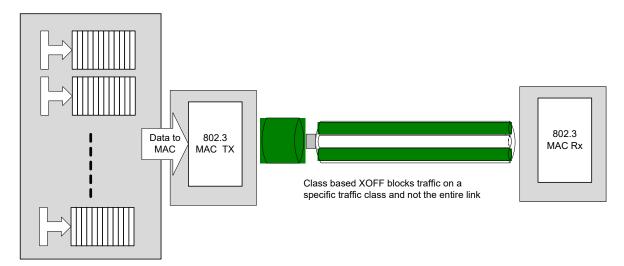

Support for Data Center Bridging (DCB);(802.1Qaz, 802.1Qbb, 802.1p)

#### **Host Interface**

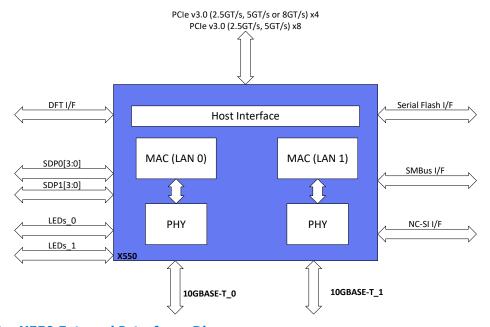

- PCIe 3.0 Base Specification

- Bus width -x1, x4, x864-bit address support for systems using more than 4 GB of physical memory

#### **MAC FUNCTIONS**

- Descriptor ring management hardware for transmit and

- ACPI register set and power down functionality supporting

- ACPT register set and power down functionality support D0 and D3 states

A mechanism for delaying/reducing transmit interrupts

Software-controlled global reset bit (resets everything except the configuration registers)

Four Software-Definable Pins (SDP) per port

Wake up

- Vake up

IPv6 wake-up filters

Configurable flexible filter (through NVM)

LAN function disable capability

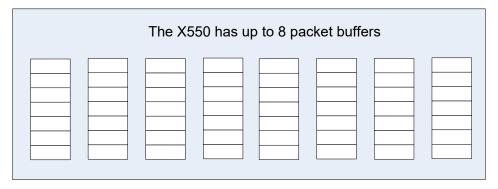

Programmable memory transmit buffers (160 KB/port)

Default configuration by NVM for all LEDs for pre-driver functionality functionality

#### Manageability

- SR-IOV support

Eight VLAN L2 filters

16 Flex L3 port filters

Four Flexible TCO filters

Four L3 address filters (IPv4)

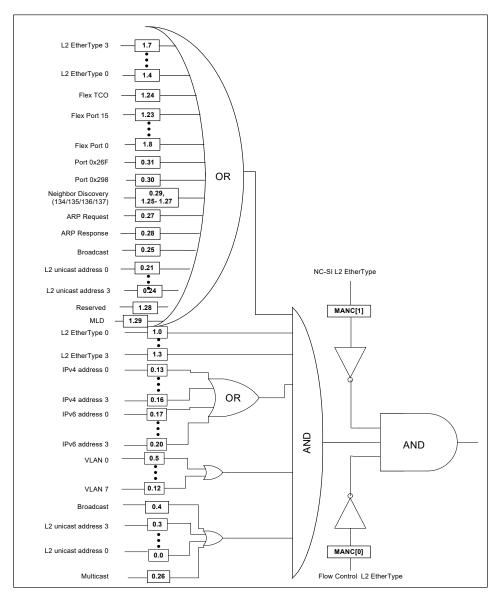

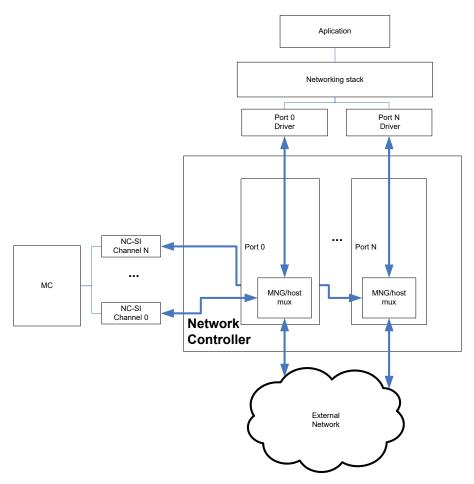

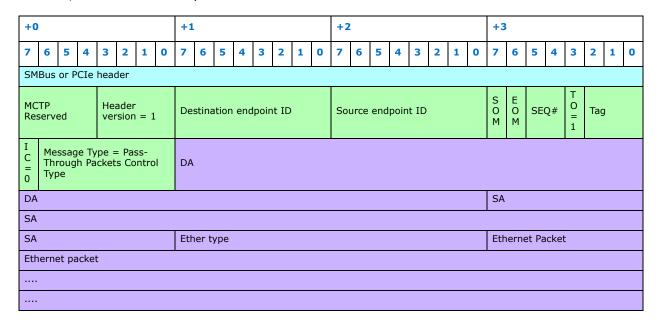

Advanced pass through-compatible management packet

transmit/receive support

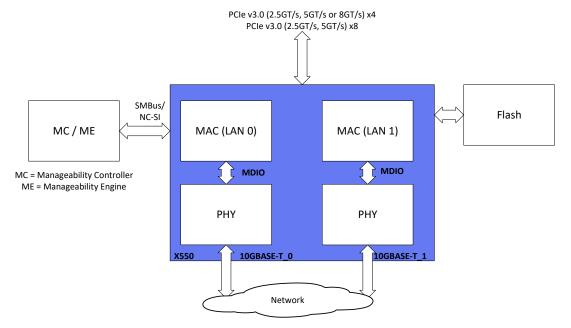

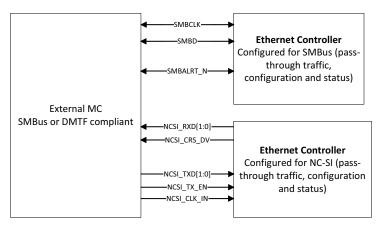

- SMBus interface to an external Manageability Controller (MC) NC-SI interface to an external MC Four L3 address filters (IPv6)

- Four L2 address filters

# **Revision History**

| Revision         | Date              | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.3              | November 19, 2018 | Updates include the following:  • Added changes related to NVM Recovery Mode:  — Section 8.2.2.20.2, "Firmware Semaphore Register - FWSM (0x00010148)" — Added Bit 5, OPERATION_MODE.  — Added Section 15.3, "NVM Recovery Mode".  • Updated Section 6.0, "Non-Volatile Memory Map".  • Updated Table 11-43, "Get MCTP Version Support Returned Value".  • Updated table in Section 12.3.10.1, "Aux Power on Peak Current Consumption".  • Updated Table 14-2, "The X550 Absolute Thermal Maximum Rating (°C)"                                                                                                                                                                                          |

| 2.2              | July 21, 2017     | Updates include the following:  • Added Section 2.2.8.1, "Pin Differences in the X550-AT Single Port Device".  • Section 11.7.6.1.3 — Added reference to list of support message types.  • Section 11.7.6.1.3.1 — Modified verbiage in "Value" column for Bytes 3:5 in Table 11-44.  • Section 12.3.9 — Added new table for X550-AT power consumption.  • Section 12.3.10.1 — Updated values in associate table.                                                                                                                                                                                                                                                                                        |

| 2.1              | May 10, 2016      | <ul> <li>Updates include the following:</li> <li>Removed EEC.FLUPD bit. No longer used for triggering Shadow RAM dump.</li> <li>Removed FLUPDATE register (0x00015F54).</li> <li>Table 3-25 — Updated description for SDP1.</li> <li>Section 9.2.3.6.7, "Link Capabilities Register (0xAC; RO)" — Changed default value for ASPM support (bits 11:10) to 10b.</li> <li>Section 11.8.3.1, "Driver Info Host Command" — Updated Table 11-49.</li> <li>Table 12-3 and Table 12-4 — Changed Device Total Power units from mW to W.</li> <li>Table 12-20 — Updated thermal diode typical ESR value to 2.77 Ω.</li> <li>Table 15-2 — Updated ID Code values.</li> <li>Other miscellaneous updates.</li> </ul> |

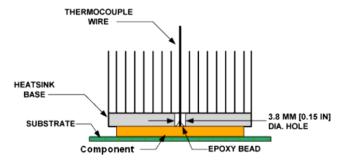

| 2.0              | January 8, 2016   | Updates include the following:  Updated PHY Registers section.  Changed Max temperature in NVM mode to 102 (Tjunction max changed 107).  Added NBASE-T information.  Removed 10BASE-T information.  Removed x2 lane width.  Updated power numbers.  Updated heat sink and other thermal information.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.9 <sup>1</sup> | October 27, 2015  | Initial release (Intel public)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

1. There were no previous versions of this document released.

# **Contents**

| 1.0 | Introd | luction                                                       | 19 |

|-----|--------|---------------------------------------------------------------|----|

| 1.1 | Scop   | pe                                                            | 19 |

| 1.2 | Prod   | luct Overview                                                 | 19 |

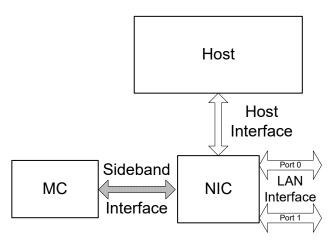

| 1   | .2.1   | System Configurations                                         | 19 |

| 1.3 | Exte   | rnal Interfaces                                               | 20 |

| 1   | .3.1   | PCIe Interface                                                | 21 |

| 1   | .3.2   | Network Interfaces                                            | 21 |

| 1   | .3.3   | Serial Flash Interface                                        | 21 |

| 1   | .3.4   | SMBus Interface                                               | 21 |

| 1   | .3.5   | NC-SI Interface                                               | 21 |

| 1   | .3.6   | Software-Definable Pins (SDP) Interface (General-Purpose I/O) | 22 |

| 1   | .3.7   | LED Interface                                                 | 22 |

| 1.4 | Feat   | ure Summary                                                   | 22 |

| 1.5 | Ove    | rview: New Capabilities Beyond the X540                       | 27 |

| 1   | .5.1   | NBASE-T Support                                               | 27 |

| 1   | .5.2   | Filtering Capabilities                                        | 27 |

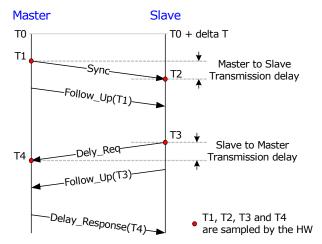

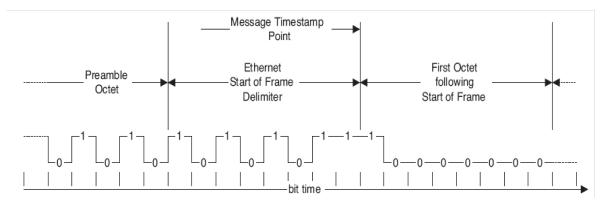

| 1   | .5.3   | IEEE 1588 Improvements                                        | 27 |

| 1   | .5.4   | Manageability                                                 | 28 |

| 1.6 | Conv   | ventions                                                      | 28 |

| 1   | .6.1   | Terminology and Acronyms                                      | 28 |

| 1   | .6.2   | Byte Ordering                                                 | 28 |

| 1.7 | Refe   | rences                                                        | 29 |

| 1.8 | Arch   | itecture and Basic Operation                                  | 31 |

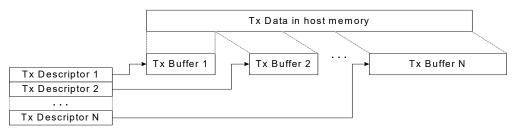

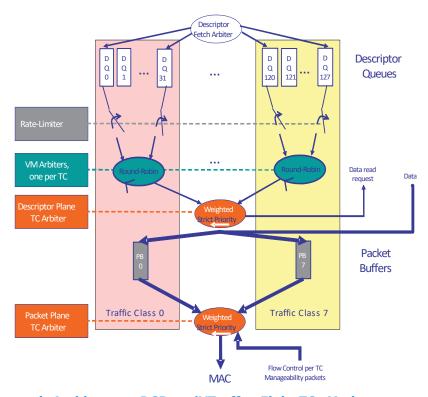

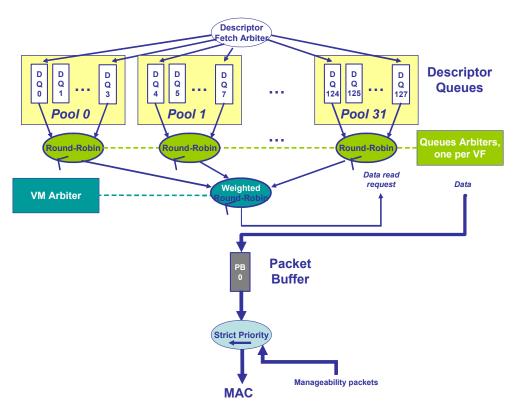

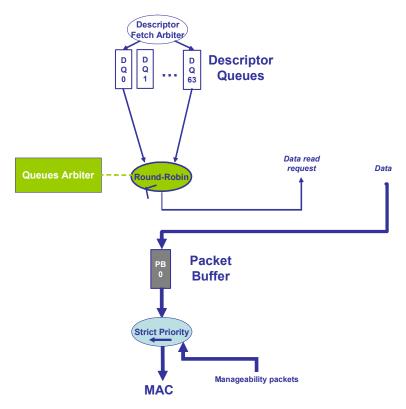

| 1   | .8.1   | Transmit (Tx) Data Flow                                       | 31 |

| 1   | .8.2   | Receive (Rx) Data Flow                                        | 32 |

| 2.0 | Pin In | terface                                                       | 33 |

| 2.1 | Sian   | al Type Definition                                            | 33 |

| 2.2 | _      | Assignments                                                   |    |

| 2   | .2.1   | PCIe                                                          |    |

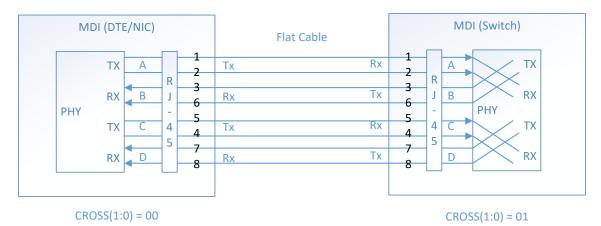

| 2   | .2.2   | MDI                                                           |    |

| 2   | .2.3   | Serial Flash                                                  |    |

| 2   | .2.4   | SMBus                                                         |    |

| 2   | .2.5   | NC-SI                                                         |    |

| 2   | .2.6   | Software Defined Pins (SDPs)                                  |    |

| 2   | .2.7   | LEDs                                                          |    |

| 2   | .2.8   | RSVD and No-Connect Pins                                      |    |

|     | .2.9   | Miscellaneous                                                 |    |

| 2   | .2.10  | JTAG                                                          |    |

| 2   | .2.11  | Power Supplies                                                | 43 |

| 2.3 | Pull-  | Up/Pull-Down Information                                      |    |

|     | .3.1   | External Pull-Ups                                             |    |

| 2.4 | Stra   | pping Options                                                 |    |

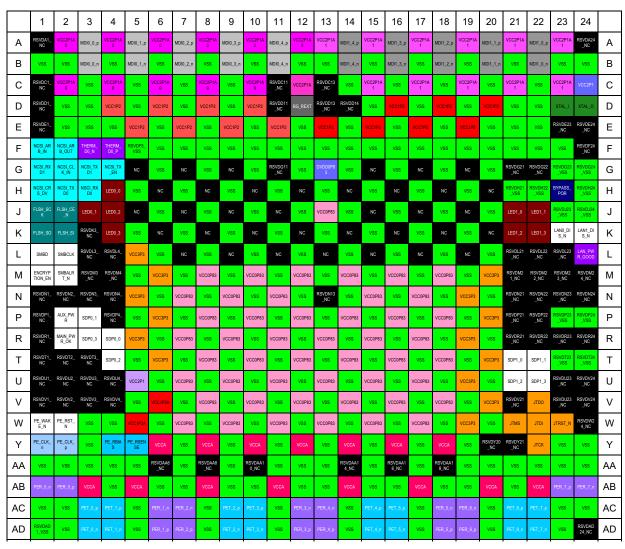

| 2.5 |        | Out — Top View Through Package                                |    |

|     |        | connects                                                      |    |

| 3.1 |        | Express (PCIe)                                                |    |

|     | .1.1   | General Overview.                                             |    |

|     | 1 2    | Transaction Layer                                             | 50 |

|            | 3.1.3          | Link Layer                                                            | . 58 |

|------------|----------------|-----------------------------------------------------------------------|------|

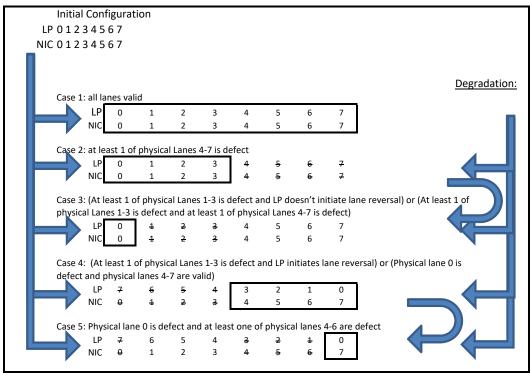

|            | 3.1.4          | Physical Layer                                                        | . 60 |

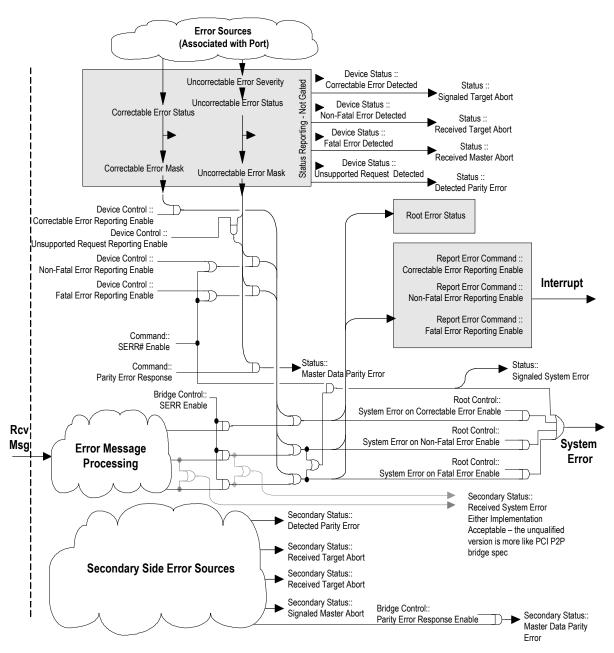

|            | 3.1.5          | Error Events and Error Reporting                                      | . 64 |

|            | 3.1.6          | Performance and Statistics Counters                                   | . 70 |

| 3.         | 2 Man          | agement Interfaces                                                    | . 78 |

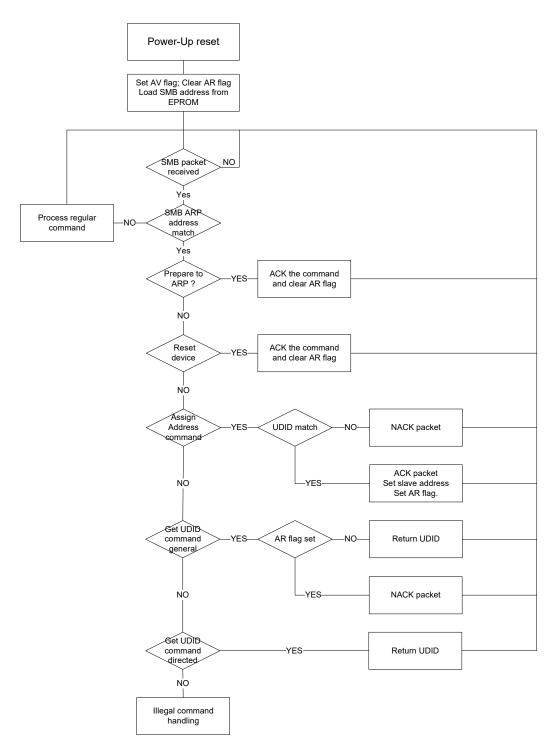

|            | 3.2.1          | SMBus                                                                 | . 78 |

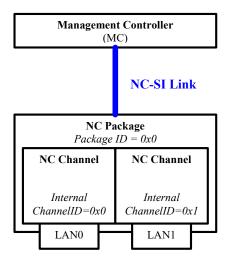

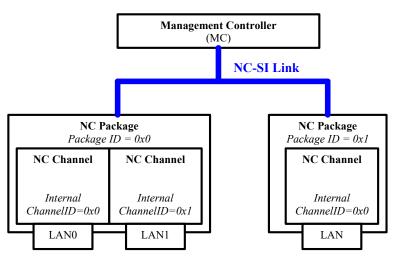

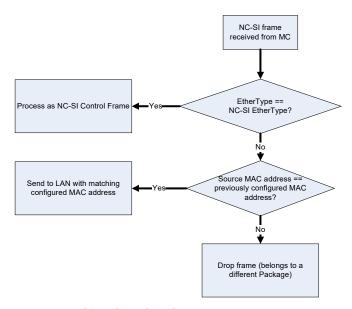

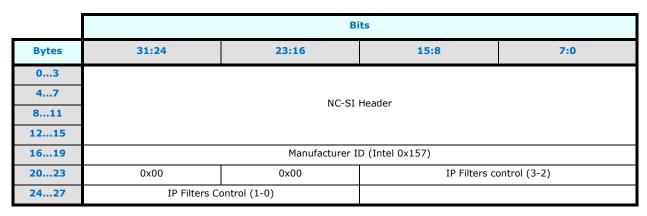

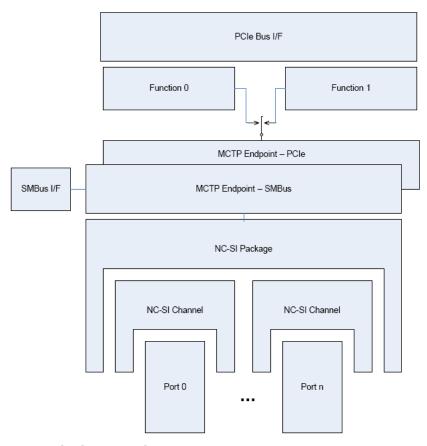

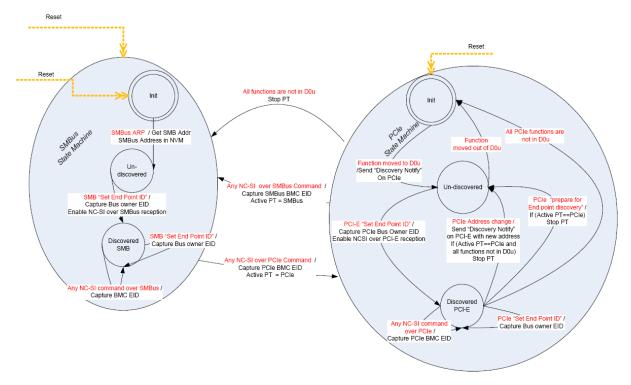

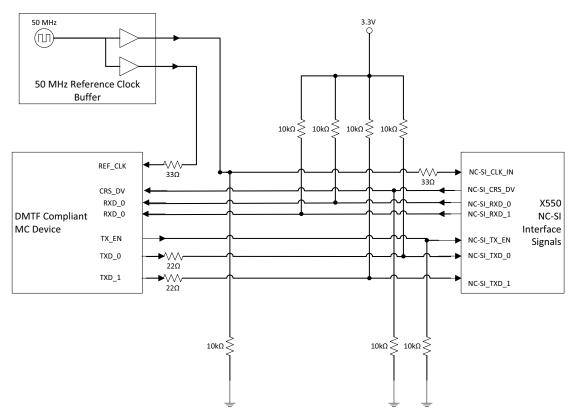

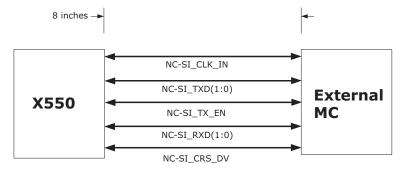

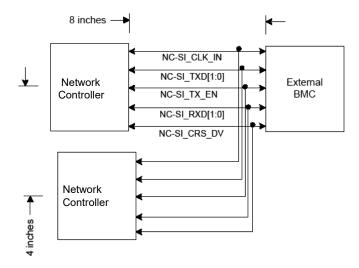

| 3.         | 3 Netv         | work Controller — Sideband Interface (NC-SI)                          | . 78 |

|            | 3.3.1          | Electrical Characteristics                                            |      |

|            | 3.3.2          | NC-SI Transactions                                                    |      |

|            | 3.3.3          | MCTP (Over PCIe or SMBus)                                             |      |

| 3.         | 4 Non          | -Volatile Memory (NVM)                                                |      |

|            | 3.4.1          | General Overview                                                      |      |

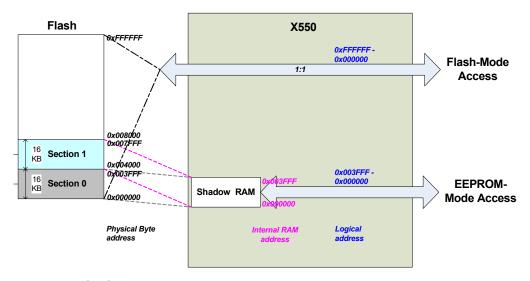

|            | 3.4.2          | Shadow RAM                                                            |      |

|            | 3.4.3          | NVM Clients and Interfaces                                            | . 81 |

|            | 3.4.4          | Flash Access Contention                                               |      |

|            | 3.4.5          | Signature Field                                                       |      |

|            | 3.4.6          | VPD Support                                                           |      |

|            | 3.4.7          | NVM Read, Write, and Erase Sequences                                  |      |

|            | 3.4.8          | Extended NVM Flows                                                    |      |

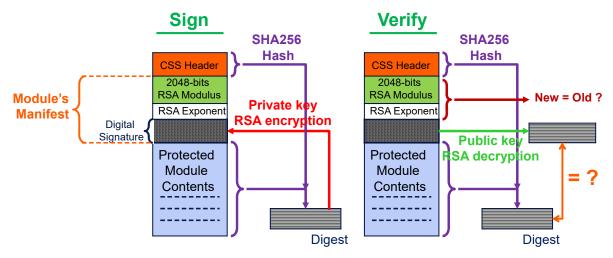

|            | 3.4.9          | NVM Authentication Procedure                                          |      |

| 3.         |                | figurable I/O Pins — Software-Definable Pins (SDPs)                   |      |

|            | 3.5.1          | I <sup>2</sup> C Over SDP                                             |      |

| 3.         |                | S                                                                     |      |

| 3.         |                | work Interface                                                        |      |

| ٥.         | 3.7.1          | Overview                                                              |      |

|            | 3.7.2          | Internal MDIO Interface                                               |      |

|            | 3.7.3          | Integrated Copper PHY Functionality                                   |      |

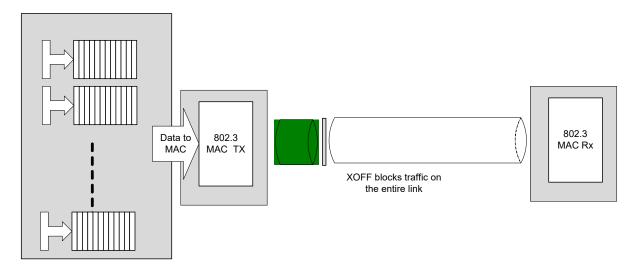

|            | 3.7.4          | Ethernet Flow Control (FC)                                            |      |

|            | 3.7.5          | Inter Packet Gap (IPG) Control and Pacing                             |      |

| <b>4</b> 0 |                | lization                                                              |      |

| 4.         |                | er Up                                                                 |      |

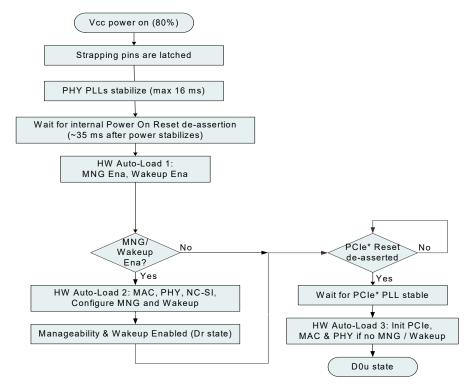

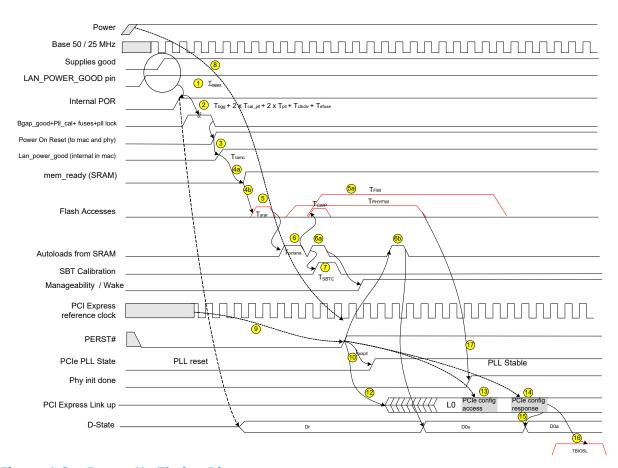

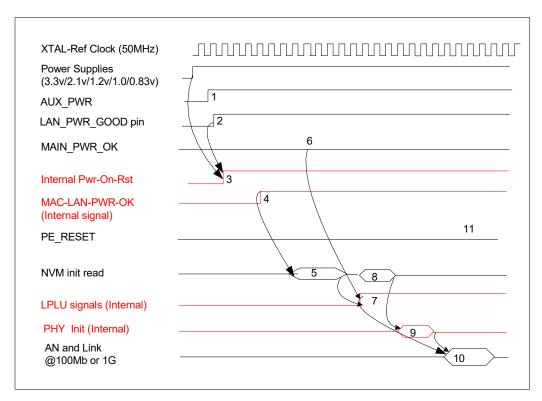

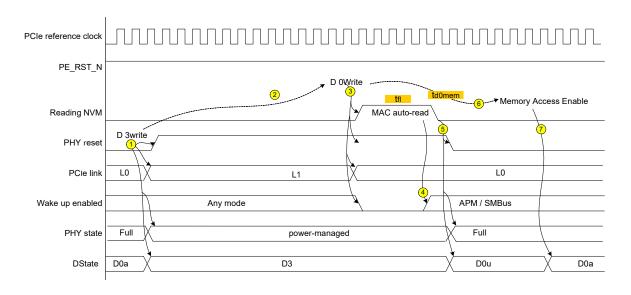

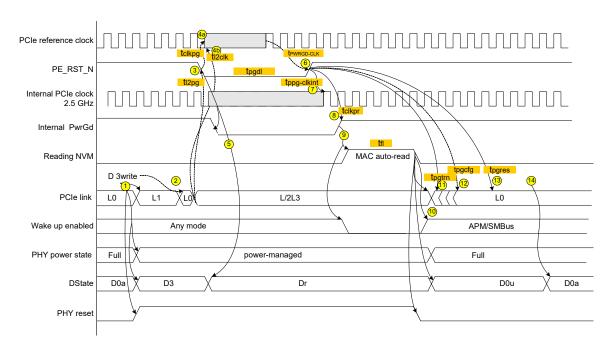

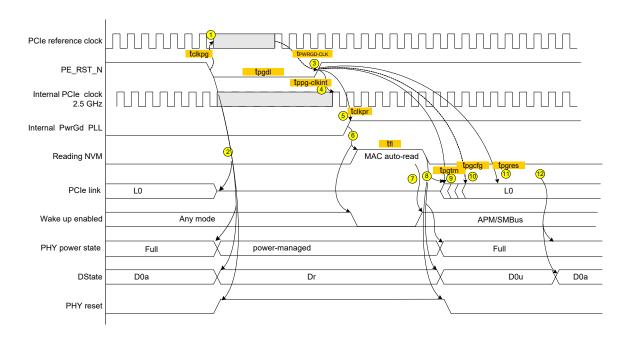

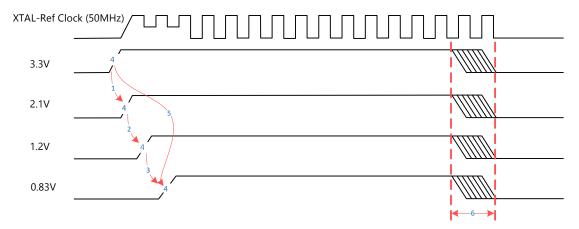

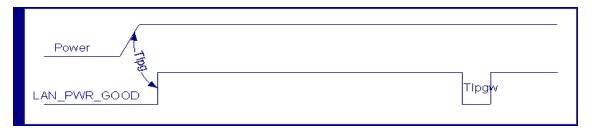

| ٦.         | 4.1.1          | Power-Up Sequence                                                     |      |

|            | 4.1.2          | Power-Up Timing Diagram                                               |      |

|            | 4.1.3          | Main-Power/Aux-Power Operation                                        |      |

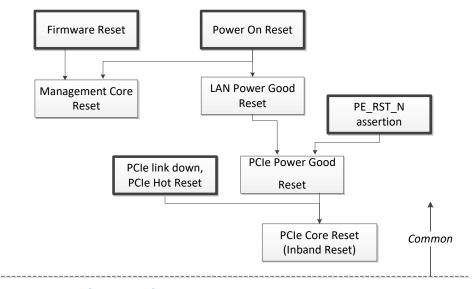

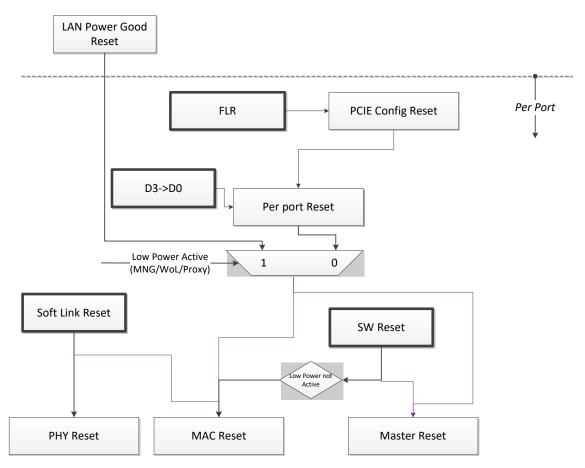

| 4.         |                | et Operation                                                          |      |

| ٦.         | 4.2.1          | Reset Sources.                                                        |      |

|            | 4.2.2          | Reset in PCI-IOV Environment                                          |      |

|            |                | Reset Effects                                                         |      |

| 4.         |                | ue Disable                                                            |      |

| 4.         |                | ction Disable                                                         |      |

| 4.         | 4.4.1          | General                                                               |      |

|            | 4.4.2          | Overview                                                              |      |

|            | 4.4.3          |                                                                       |      |

|            | 4.4.4          | Control Options  Event Flow for Enable/Disable Functions              |      |

| 4          |                | ice Disable                                                           |      |

| 4.         |                |                                                                       |      |

|            | 4.5.1<br>4.5.2 | Overview                                                              |      |

|            |                | BIOS Disable of the Device at Boot Time by Using the Strapping Option |      |

| 4.         |                | ware Initialization and Diagnostics                                   |      |

|            | 4.6.1          | Introduction                                                          |      |

|            | 4.6.2          | Power-Up State                                                        | 140  |

| 4.6.3     | Initialization Sequence                         | 141 |

|-----------|-------------------------------------------------|-----|

| 4.6.4     | 100 Mb/s, 1 GbE, and 10 GbE Link Initialization | 142 |

| 4.6.5     | Initialization of Statistics                    | 142 |

| 4.6.6     | Interrupt Initialization                        | 143 |

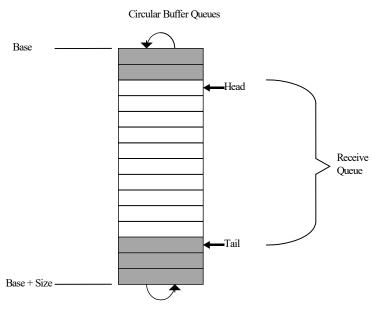

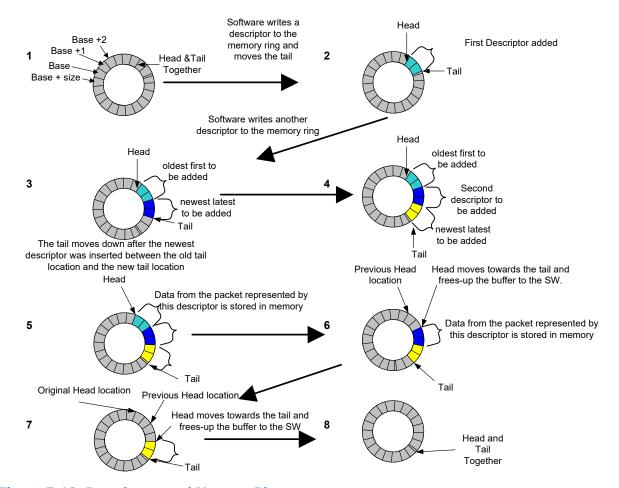

| 4.6.7     | Receive Initialization                          | 143 |

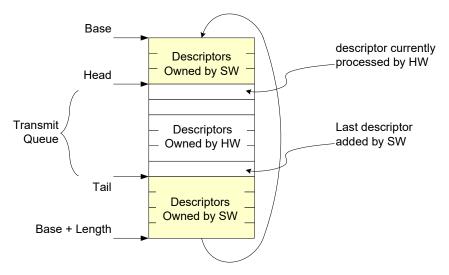

| 4.6.8     | Transmit Initialization                         | 146 |

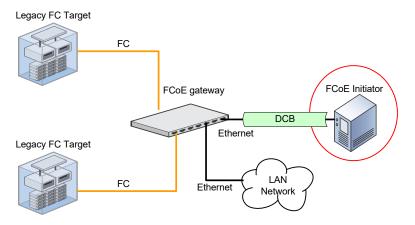

| 4.6.9     | FCoE Initialization Flow                        | 148 |

| 4.6.10    | Virtualization Initialization Flow              | 148 |

| 4.6.11    | DCB Configuration                               | 151 |

| 4.6.12    | Security Initialization                         | 161 |

| 4.6.13    | Alternate MAC Address Support                   | 162 |

| 4.7 Acce  | ess to Shared Resources                         | 163 |

| 5.0 Power | r Management and Delivery                       | 165 |

| 5.1 Pow   | er Targets and Power Delivery                   | 165 |

| 5.2 Pow   | er Management                                   | 165 |

| 5.2.1     | Introduction to X550 Power States               | 165 |

| 5.2.2     | Auxiliary Power Usage                           | 166 |

| 5.2.3     | PCIe Link Power Management                      | 166 |

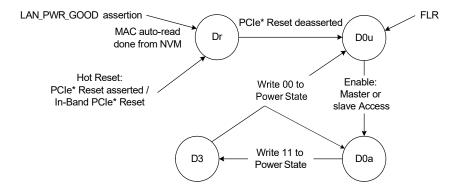

| 5.2.4     | Power States                                    | 167 |

| 5.2.5     | Timing of Power-State Transitions               | 171 |

| 5.3 Netv  | vork Interfaces Power Management                | 175 |

| 5.3.1     | PHY Power-Down State                            | 175 |

| 5.3.2     | PHY Power-Down via the PHY Register             | 176 |

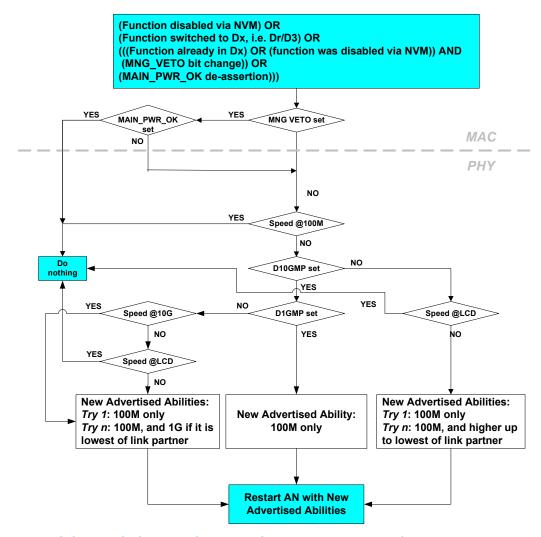

| 5.3.3     | Smart Power-Down (SPD)                          | 176 |

| 5.3.4     | Disable 10GBASE-T and/or 1000BASE-T Speeds      | 178 |

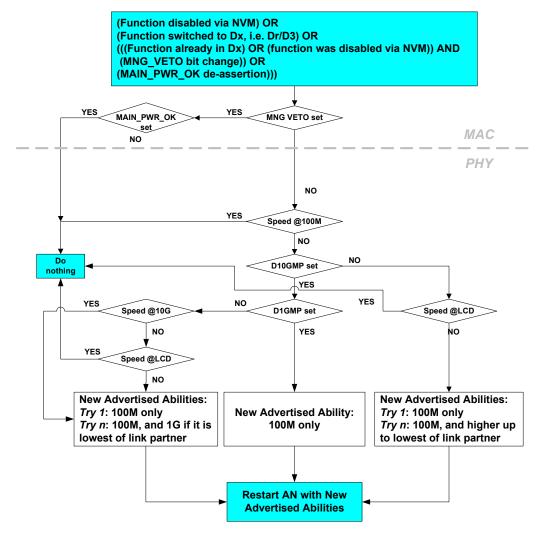

| 5.3.5     | Low Power Link Up (LPLU)                        | 178 |

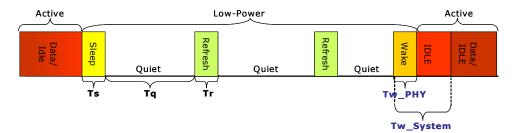

| 5.3.6     | Energy Efficient Ethernet (EEE)                 | 183 |

| 5.4 Wak   | e-Up                                            | 186 |

| 5.4.1     | Advanced Power Management Wake-Up               | 186 |

| 5.4.2     | ACPI Power Management Wake-Up                   | 186 |

| 5.4.3     | Wake-Up Packets                                 | 187 |

| 5.4.4     | Wake-Up and Virtualization                      | 191 |

| 5.5 DMA   | Coalescing                                      | 192 |

| 5.5.1     | DMA Coalescing Activation                       | 192 |

| 5.5.2     | DMA Coalescing Operating Mode                   | 193 |

| 5.5.3     | DMA Coalescing Recommended Settings             |     |

|           |                                                 |     |

| 5.6.1     | LTR Algorithm                                   | 195 |

| 5.6.2     | LTR Initialization Flow                         |     |

| 5.7 Ther  | mal Management                                  |     |

| 5.7.1     | General                                         |     |

| 5.7.2     | MC-Based Mode                                   |     |

| 5.7.3     | NVM-Based Mode                                  |     |

| 5.7.4     | Thermal Sensor Control                          |     |

| 5.7.5     | Thermal Sensor Characteristics                  |     |

|           | /olatile Memory Map                             |     |

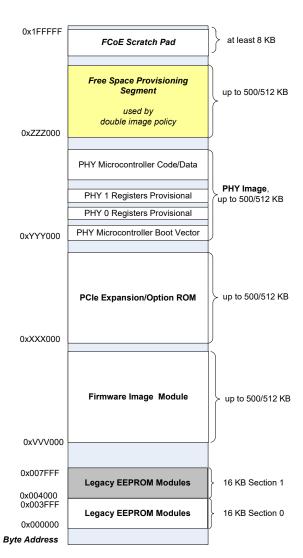

| 6.1 NVM   | l Organization                                  | 199 |

| 6.1.1     | Protected Areas                                 | 201 |

| 6.1.2     | NVM Header                                      | 202 |

| 6.1.3     | Hardware Sections                               | 204 |

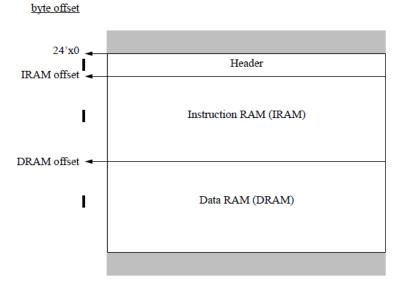

| 6.1.4   | Firmware Image Module                                             |     |

|---------|-------------------------------------------------------------------|-----|

| 6.1.5   | PCIe Expansion/Option ROM                                         | 207 |

| 6.1.6   | PHY Module                                                        | 207 |

| 6.1.7   | Register Provisional Table                                        | 210 |

| 6.2 NVM | I General Summary Table                                           | 211 |

| 6.2.1   | Init Module Section Summary Table                                 | 214 |

| 6.2.2   | MAC Module Section Summary Table                                  | 238 |

| 6.2.3   | CSR Auto Config Section Summary Table                             | 240 |

| 6.2.4   | LAN Core Module Section Summary Table                             | 241 |

| 6.2.5   | PCIe General Configuration Module Section Summary Table           | 246 |

| 6.2.6   | PCIe Configuration Space Section Summary Table                    | 255 |

| 6.2.7   | Alternate Ethernet MAC Address Section Summary Table              |     |

| 6.2.8   | FCoE Scratch Pad Header Section Summary Table                     | 258 |

| 6.2.9   | Active SAN MAC Address Section Summary Table                      |     |

| 6.2.10  | Alternate SAN MAC Address Section Summary Table                   |     |

| 6.2.11  | Boot Configuration Block Section Summary Table                    |     |

| 6.2.12  | Firmware Module Header Section Summary Table                      |     |

| 6.2.13  | Firmware Header Reserved Word Section Summary Table               |     |

| 6.2.14  | Test Configuration Module Section Summary Table                   |     |

| 6.2.15  | Common Firmware Parameters Module Section Summary Table           |     |

| 6.2.16  | Sideband Configuration Structure Section Summary Table            |     |

| 6.2.17  | Pass-Through Control Words Section Summary Table                  |     |

| 6.2.18  | Flexible TCO Filter Configuration Structure Section Summary Table |     |

| 6.2.19  | LESM Configurations (not in SGVL) Section Summary Table           |     |

| 6.2.20  | PXE VLAN Configuration Section Summary Table                      |     |

| 6.2.21  | VPD Module Section Summary Table                                  |     |

| 6.2.22  | PBA Number Module Section Summary Table                           |     |

| 6.2.23  | Mini Loader Module Section Summary Table                          |     |

| 6.2.24  | PHY Config Section Summary Table                                  |     |

| 6.2.25  | PCIe Link (LCB) Configuration Section Summary Table               |     |

| 6.2.26  | PCIe Analog Configuration Module Section Summary Table            |     |

| 6.2.27  | 2'nd Init Module Section Summary Table                            |     |

| 6.2.28  | FCoE Scratch Pad Section Summary Table                            |     |

| 6.2.29  | Firmware Module Section Summary Table                             |     |

| 6.2.30  | PXE/OROM Module Section Summary Table                             |     |

| 6.2.31  | AQ PHY Module Section Summary Table                               |     |

| 6.2.32  | Free Provisioning Module Section Summary Table                    |     |

|         | Functions                                                         |     |

|         |                                                                   |     |

|         | Pive Functionality                                                |     |

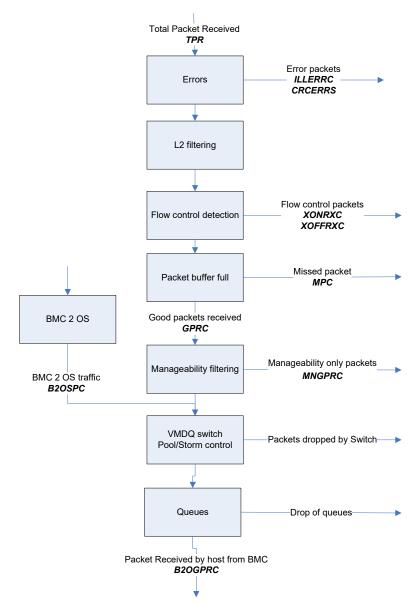

| 7.1.1   | MAC Layer - Receive                                               |     |

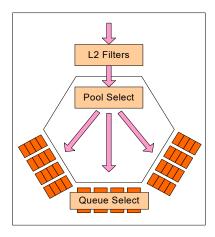

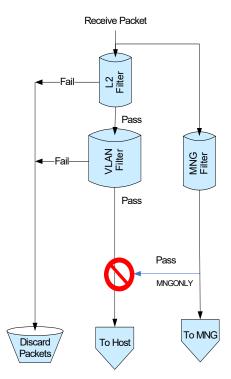

| 7.1.2   | Packet Filtering                                                  |     |

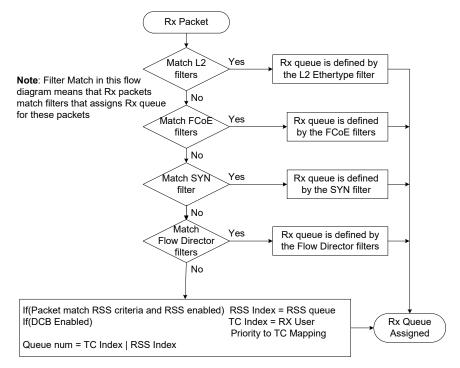

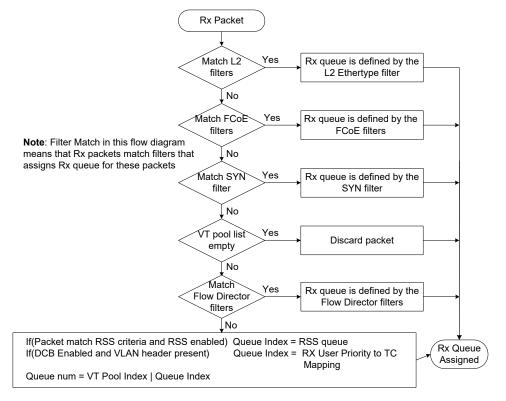

| 7.1.3   | Rx Queues Assignment                                              |     |

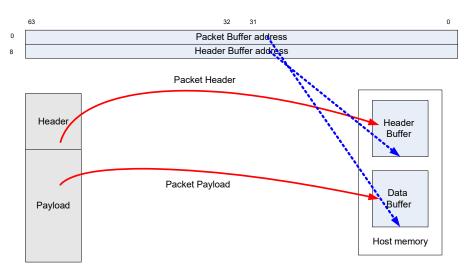

| 7.1.4   | Receive Data Storage in System Memory                             |     |

| 7.1.5   | Receive Descriptors                                               |     |

| 7.1.6   | Receive Offloads                                                  |     |

| 7.1.7   | Receive Statistics                                                |     |

|         | nsmit Functionality                                               |     |

| 7.2.1   | Packet Transmission                                               |     |

| 7.2.2   | Transmit Contexts                                                 |     |

| 7.2.3   | Transmit Descriptors                                              | 400 |

| 7.2.4          | TCP and UDP Segmentation                              | 414        |

|----------------|-------------------------------------------------------|------------|

| 7.2.5          | Transmit Checksum Offloading in Non-Segmentation Mode | 421        |

| 7.2.6          | Transmit Statistics                                   | 424        |

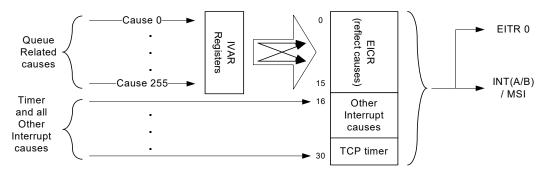

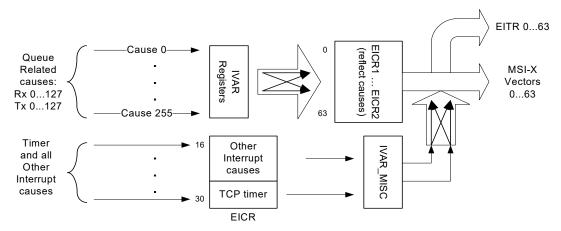

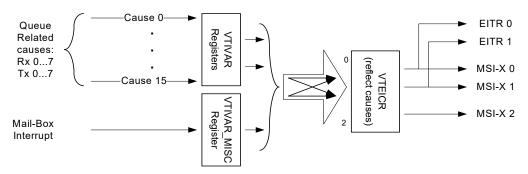

| 7.3            | Interrupts                                            | 426        |

| 7.3.1          | Interrupt Registers                                   | 426        |

| 7.3.2          | Interrupt Moderation                                  | 429        |

| 7.3.3          | TCP Timer Interrupt                                   | 431        |

| 7.3.4          | Mapping of Interrupt Causes                           | 431        |

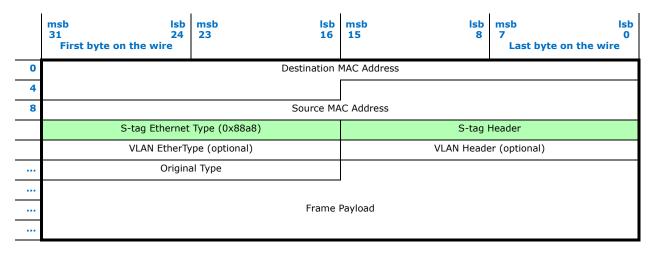

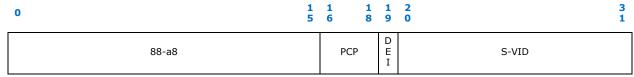

| 7.4            | 802.1q VLAN Support                                   | 438        |

| 7.4.1          | 802.1q VLAN Packet Format                             | 438        |

| 7.4.2          | 802.1q Tagged Frames                                  | 438        |

| 7.4.3          | Transmitting and Receiving 802.1q Packets             | 439        |

| 7.4.4          |                                                       |            |

| 7.4.5          | Double VLAN and Single VLAN Support                   | 440        |

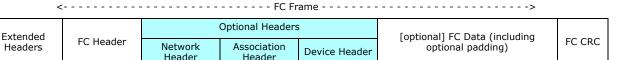

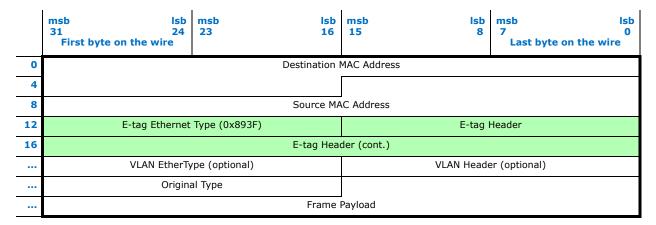

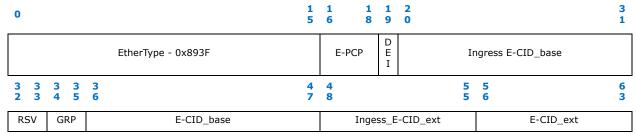

| 7.4.6          | E-tag and VLAN                                        | 442        |

| 7.5            | TLP Processing Hints (TPH)                            |            |

| 7.5.1          |                                                       |            |

| 7.6            | Data Center Bridging (DCB)                            |            |

| 7.6.1          |                                                       |            |

| 7.6.2          |                                                       |            |

| 7.6.3          | ·                                                     |            |

| 7.7            | Time SYNC (IEEE1588 and 802.1AS)                      |            |

| 7.7.1          | ,                                                     |            |

| 7.7.2          |                                                       |            |

| 7.7.3          | •                                                     |            |

| 7.7.4          |                                                       |            |

| 7.7.5          | ·                                                     |            |

| 7.7.6          | ·                                                     |            |

| 7.8            | Virtualization                                        |            |

| 7.8.1          |                                                       |            |

| 7.8.2          |                                                       |            |

| 7.8.3          | • •                                                   |            |

| 7.8.4          |                                                       |            |

| 7.8.5          | •                                                     |            |

|                | Tunneling Support                                     |            |

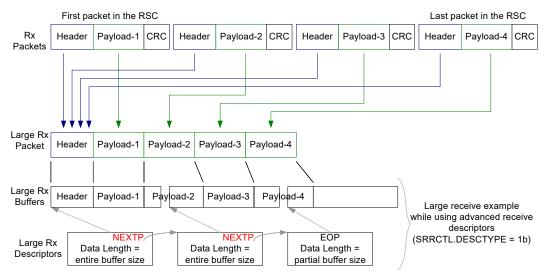

|                | Receive Side Coalescing (RSC)                         |            |

| 7.10.          |                                                       |            |

| 7.10.          | ·                                                     | 508        |

| 7.10.          | <u> </u>                                              |            |

| 7.10.          |                                                       |            |

| 7.10.          |                                                       |            |

| 7.10.          | ·                                                     |            |

|                | Fibre Channel over Ethernet (FCoE)                    |            |

| 7.11.          |                                                       |            |

| 7.11.<br>7.11. |                                                       |            |

| 7.11.<br>7.11. | ·                                                     |            |

|                |                                                       |            |

|                | Reliability                                           |            |

| 7.12.          | - · · · · · · · · · · · · · · · · · · ·               |            |

| 7.12.          |                                                       |            |

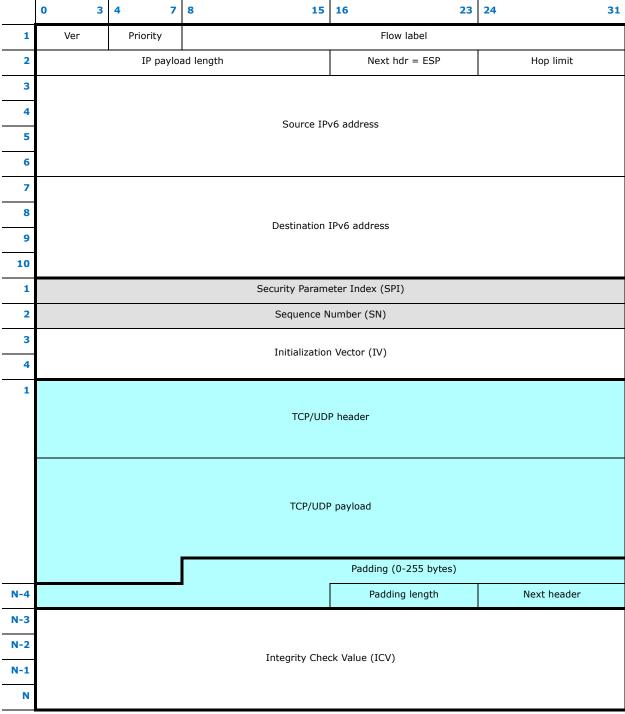

| 7.13           | IPsec Support                                         | <b>33/</b> |

| 7.13.1     | Overview                                                | 537 |

|------------|---------------------------------------------------------|-----|

| 7.13.2     | Hardware Features List                                  | 537 |

| 7.13.3     | Software/Hardware Demarcation                           | 540 |

| 7.13.4     | IPsec Formats Exchanged Between Hardware and Software   | 541 |

| 7.13.5     | Tx SA Table                                             | 545 |

| 7.13.6     | Tx Hardware Flow                                        | 546 |

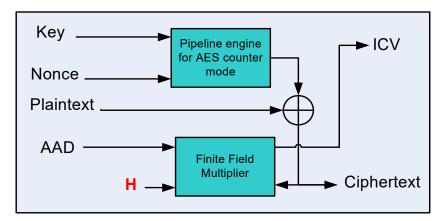

| 7.13.7     | AES-128 Operation in Tx                                 | 548 |

| 7.13.8     | Rx Descriptors                                          | 549 |

| 7.13.9     | Rx SA Tables                                            | 549 |

| 7.13.10    | Rx Hardware Flow without TCP/UDP Checksum Offload       | 551 |

| 7.13.11    | Rx Hardware Flow with TCP/UDP Checksum Offload          | 552 |

| 7.13.12    | AES-128 Operation in Rx                                 | 553 |

| 8.0 Progra | amming Interface                                        | 555 |

| 8.1 Gen    | eral                                                    | 555 |

| 8.1.1      | Memory-Mapped Access                                    | 555 |

| 8.1.2      | I/O-Mapped Access                                       |     |

| 8.1.3      | Configuration Access to Internal Registers and Memories |     |

| 8.1.4      | Register Terminology                                    |     |

| 8.1.5      | VF Registers Allocated per Queue                        |     |

| 8.1.6      | Non-Queue VF Registers                                  |     |

| 8.2 Devi   | ce Registers - PF                                       |     |

| 8.2.1      | BARO Registers Summary                                  |     |

| 8.2.2      | Detailed Register Description - PF BAR0                 |     |

| 8.2.2.2    | -                                                       |     |

| 8.2.2.3    | -                                                       |     |

| 8.2.2.4    |                                                         |     |

| 8.2.2.5    | -                                                       |     |

| 8.2.2.6    |                                                         |     |

| 8.2.2.7    | ·                                                       |     |

| 8.2.2.8    | •                                                       |     |

| 8.2.2.9    | Receive DMA Registers                                   | 633 |

| 8.2.2.1    | .0 Transmit Registers                                   | 638 |

| 8.2.2.1    | 1 DCB Registers                                         | 644 |

| 8.2.2.1    | .2 TPH Registers                                        | 651 |

| 8.2.2.1    | .3 Timers Registers                                     | 653 |

| 8.2.2.1    | 4 FCoE Registers                                        | 654 |

| 8.2.2.1    | .5 Flow Director Registers                              | 659 |

| 8.2.2.1    |                                                         |     |

| 8.2.2.1    |                                                         |     |

| 8.2.2.1    | .8 Wake-Up and Proxy Control Registers                  | 696 |

| 8.2.2.1    |                                                         |     |

| 8.2.2.2    |                                                         |     |

| 8.2.2.2    |                                                         |     |

| 8.2.2.2    |                                                         |     |

| 8.2.2.2    |                                                         |     |

| 8.2.2.2    |                                                         |     |

| 8.2.2.2    | •                                                       |     |

| 8.2.2.2    |                                                         |     |

| 8.2.3      | BAR3 Registers Summary                                  |     |

| 8.2.4      | Detailed Register Description - PF BAR3                 |     |

| 8.   | 3 De    | vice Registers - VF                                                | 750 |

|------|---------|--------------------------------------------------------------------|-----|

|      | 8.3.1   | BAR0 Registers Summary                                             | 750 |

|      | 8.3.2   | Detailed Register Description - VF BAR0                            | 752 |

|      | 8.3.3   | BAR3 Registers Summary                                             | 761 |

|      | 8.3.4   | Detailed Register Description - VF BAR3                            | 761 |

| 9.0  | PCIe    | Programming Interface                                              | 763 |

| 9.   |         | erview                                                             |     |

|      | 9.1.1   | Register Attributes                                                | 764 |

| 9.   | 2 PC    | Ie Register Map                                                    | 765 |

|      | 9.2.1   | PCIe Configuration Space Summary                                   | 765 |

|      | 9.2.2   | Mandatory PCI Configuration Registers                              | 767 |

|      | 9.2.3   | PCI Capabilities                                                   | 774 |

|      | 9.2.4   | PCIe Extended Configuration Space                                  | 798 |

|      | 9.2.5   | Driver Forward Compatibility Register (0x94; RO)                   | 819 |

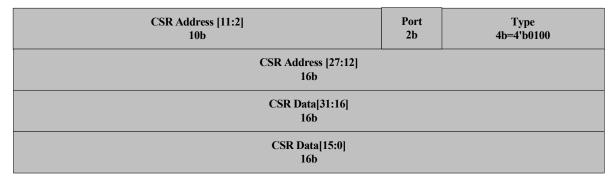

|      | 9.2.6   | CSR Access Via Configuration Address Space                         | 819 |

| 9.   | 3 Vir   | tual Functions Configuration Space                                 | 820 |

|      | 9.3.1   | Mandatory Configuration Space                                      | 822 |

|      | 9.3.2   | PCI Capabilities                                                   | 823 |

|      | 9.3.3   | PCIe Extended Capabilities                                         | 825 |

| 10.0 | ) PHY   | Registers                                                          | 827 |

| 10   | ).1 Int | roduction                                                          | 827 |

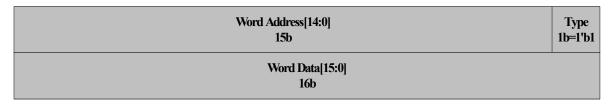

|      | 10.1.1  | PHY Register Structure                                             | 827 |

|      | 10.1.2  | Format and Nomenclature                                            | 828 |

|      | 10.1.3  | Structure                                                          | 829 |

|      | 10.1.4  | PHY Registers and Documentation                                    | 830 |

| 10   | ).2 PM  | A Registers                                                        | 831 |

|      | 10.2.1  | PMA Standard Control 1: Address 1.0                                | 831 |

|      | 10.2.2  | PMA Standard Status 1: Address 1.1                                 | 831 |

|      | 10.2.3  | PMA Standard Device Identifier 1: Address 1.2                      | 832 |

|      | 10.2.4  | PMA Standard Device Identifier 2: Address 1.3                      | 832 |

|      | 10.2.5  | PMA Standard Speed Ability: Address 1.4                            | 832 |

|      | 10.2.6  | PMA Standard Devices in Package 1: Address 1.5                     | 833 |

|      | 10.2.7  | PMA Standard Devices in Package 2: Address 1.6                     | 834 |

|      | 10.2.8  | PMA Standard Control 2: Address 1.7                                | 834 |

|      | 10.2.9  | PMA Standard Status 2: Address 1.8                                 | 834 |

|      | 10.2.10 |                                                                    |     |

|      | 10.2.11 | g · · · · · · · · · · · · · · · · · · ·                            |     |

|      | 10.2.12 | , 3                                                                |     |

|      | 10.2.13 |                                                                    |     |

|      | 10.2.14 | · · · · · · · · · · · · · · · · · · ·                              |     |

|      | 10.2.15 |                                                                    |     |

|      | 10.2.16 | ·                                                                  |     |

|      | 10.2.17 |                                                                    |     |

|      | 10.2.18 |                                                                    |     |

|      | 10.2.19 | ·                                                                  |     |

|      | 10.2.20 | ,                                                                  |     |

|      | 10.2.21 | ·                                                                  |     |

|      | 10.2.22 | ·                                                                  |     |

|      | 10.2.23 | , <del>, , , , , , , , , , , , , , , , , , </del>                  |     |

|      | 10.2.24 | PMA 10GBASE-T SNR Minimum Operating Margin Channel B: Address 1.8A | 841 |

### Intel® Ethernet Controller X550 Datasheet—Contents

| .2.25 | PMA 10GBASE-T SNR Minimum Operating Margin Channel C: Address 1.8B                                                                                                                                                                                                                                                                                                                                                                                   | 841                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .2.26 | PMA 10GBASE-T SNR Minimum Operating Margin Channel D: Address 1.8C                                                                                                                                                                                                                                                                                                                                                                                   | 841                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.27 | PMA 10GBASE-T Receive Signal Power Channel A: Address 1.8D                                                                                                                                                                                                                                                                                                                                                                                           | 842                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.28 | PMA 10GBASE-T Receive Signal Power Channel B: Address 1.8E                                                                                                                                                                                                                                                                                                                                                                                           | 842                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.29 | PMA 10GBASE-T Receive Signal Power Channel C: Address 1.8F                                                                                                                                                                                                                                                                                                                                                                                           | 842                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.30 | PMA 10GBASE-T Receive Signal Power Channel D: Address 1.90                                                                                                                                                                                                                                                                                                                                                                                           | 842                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.31 | PMA 10GBASE-T Skew Delay 1: Address 1.91                                                                                                                                                                                                                                                                                                                                                                                                             | 843                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.32 | PMA 10GBASE-T Skew Delay 2: Address 1.92                                                                                                                                                                                                                                                                                                                                                                                                             | 843                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.33 | PMA 10GBASE-T Fast Retrain Status and Control: Address 1.93                                                                                                                                                                                                                                                                                                                                                                                          | 843                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.34 | PMA TimeSync Capability: Address 1.1800                                                                                                                                                                                                                                                                                                                                                                                                              | 844                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.35 | PMA TimeSync Transmit Path Data Delay 1: Address 1.1801                                                                                                                                                                                                                                                                                                                                                                                              | 844                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.36 | PMA TimeSync Transmit Path Data Delay 2: Address 1.1802                                                                                                                                                                                                                                                                                                                                                                                              | 844                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.37 | PMA TimeSync Transmit Path Data Delay 3: Address 1.1803                                                                                                                                                                                                                                                                                                                                                                                              | 845                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| .2.38 | PMA TimeSync Transmit Path Data Delay 4: Address 1.1804                                                                                                                                                                                                                                                                                                                                                                                              | 845                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |