# **PCI IP User's Guide**

# **Table of Contents**

| Chapter 1. Introduction                                                              | 6  |

|--------------------------------------------------------------------------------------|----|

| Quick Facts                                                                          |    |

| Features                                                                             | 10 |

| Chapter 2. Functional Description                                                    |    |

| Block Diagram                                                                        |    |

| PCI Master Control                                                                   |    |

| PCI Target Control                                                                   |    |

| Local Master Interface Control                                                       |    |

| Local Target Control                                                                 |    |

| Configuration Space                                                                  |    |

| Parity Generator and Checker                                                         |    |

| Signal Descriptions                                                                  |    |

| PCI Interface Signals                                                                |    |

| Local Interface Signals                                                              |    |

| PCI Configuration Space Setup                                                        |    |

| Status Register                                                                      |    |

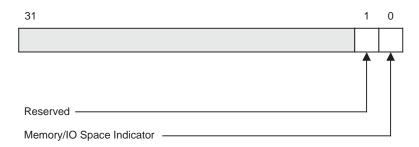

| Base Address Registers                                                               |    |

| BAR Mapped to Memory Space                                                           |    |

| Bar Mapped to I/O Space                                                              |    |

| Cache Line Size                                                                      |    |

| Latency Timer                                                                        |    |

| CardBus CIS Pointer                                                                  |    |

| Subsystem Vendor ID                                                                  |    |

| Subsystem ID                                                                         |    |

| Capabilities Pointer                                                                 |    |

| Min_Gnt                                                                              |    |

| Max_Lat                                                                              |    |

| Interrupt Line                                                                       |    |

| Interrupt Pin                                                                        |    |

| Reserved                                                                             |    |

| Lattice PCI IP core Configuration Options                                            |    |

| IPexpress User-Controlled Configurations                                             |    |

| PCI Configuration Using Core Configuration Space Port                                |    |

| Local Bus Interface                                                                  |    |

| Target Operation                                                                     |    |

| Master Operation                                                                     |    |

| Basic PCI Master Read and Write Transactions                                         |    |

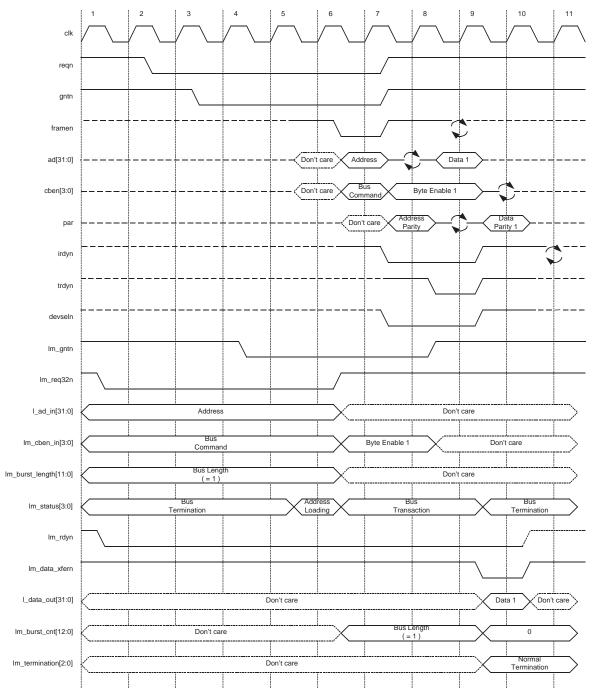

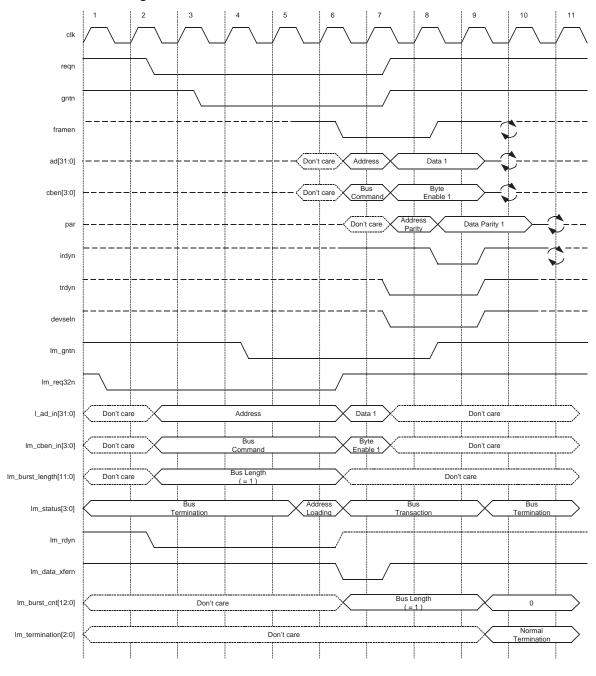

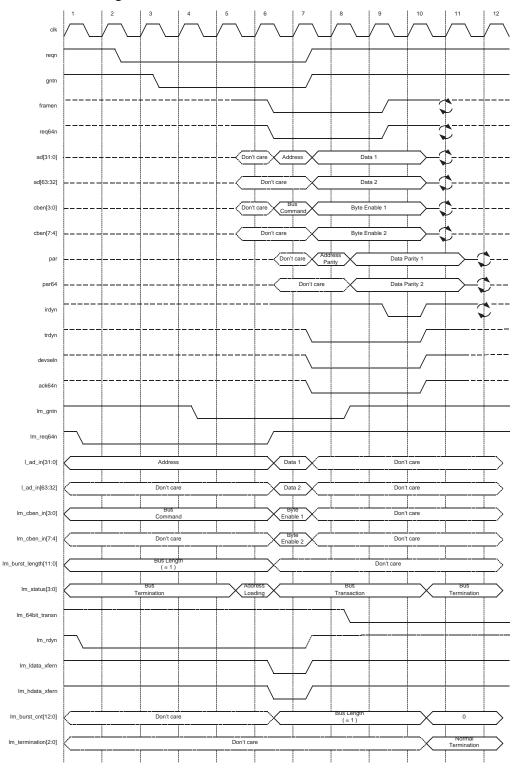

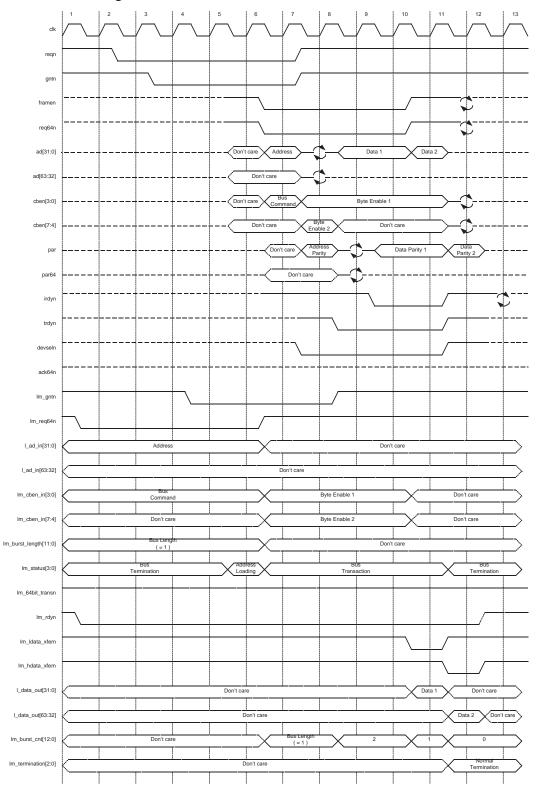

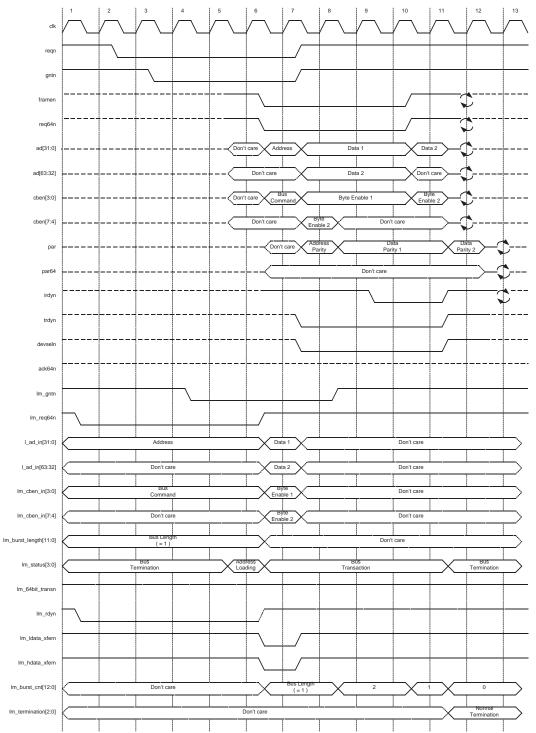

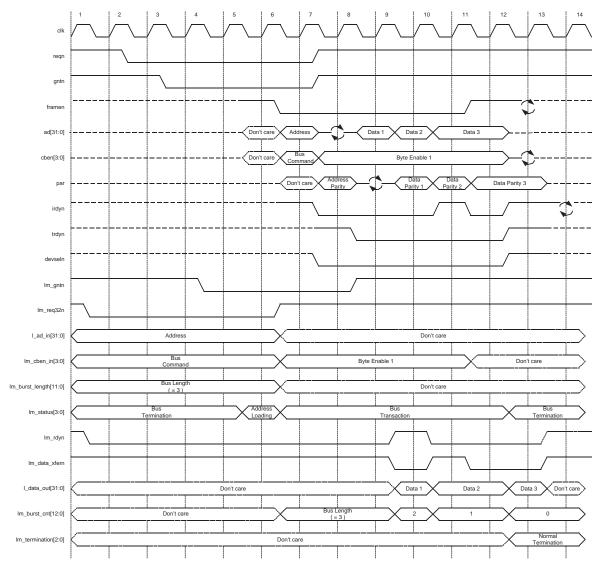

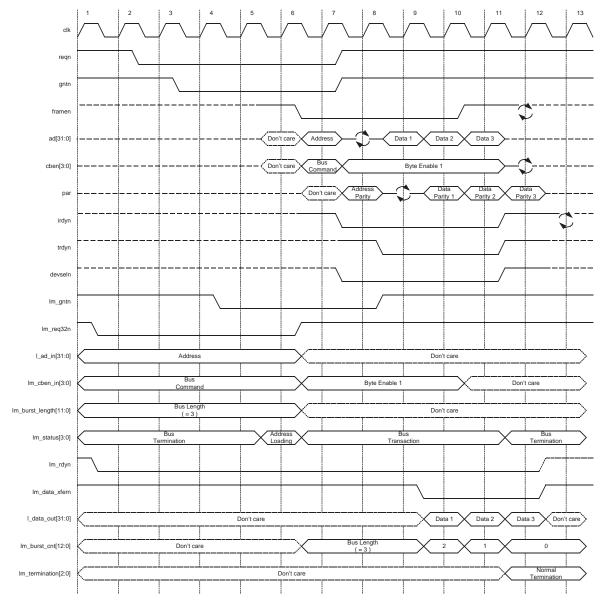

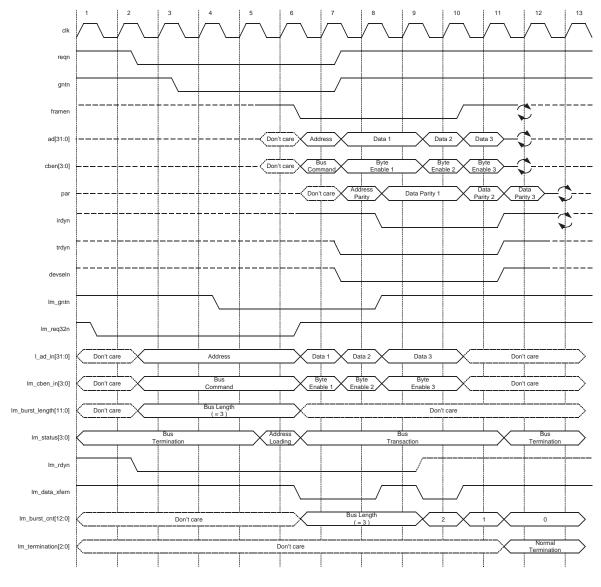

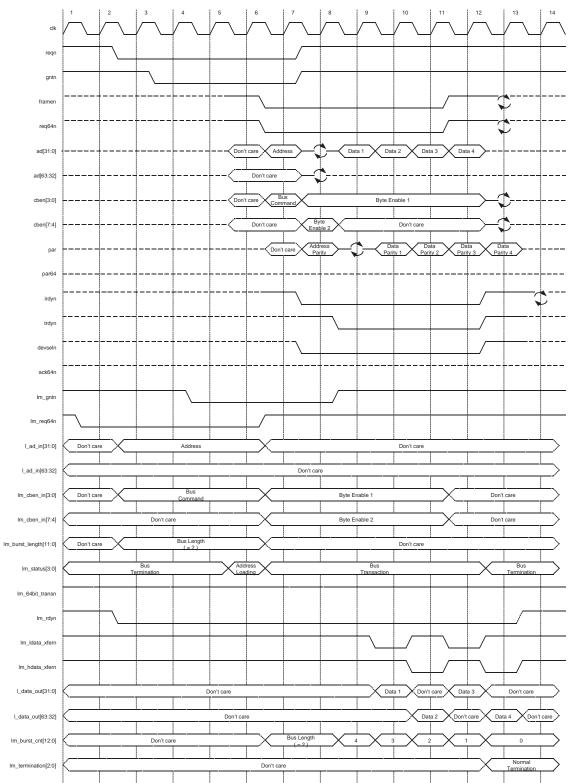

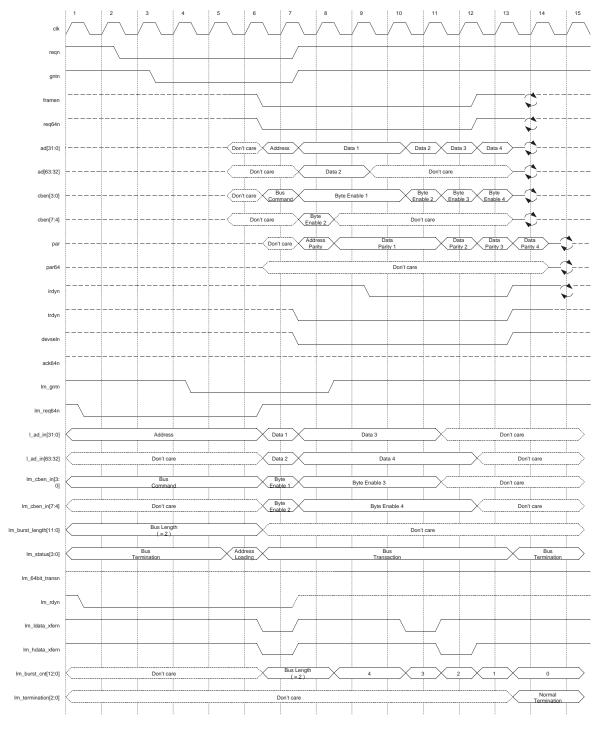

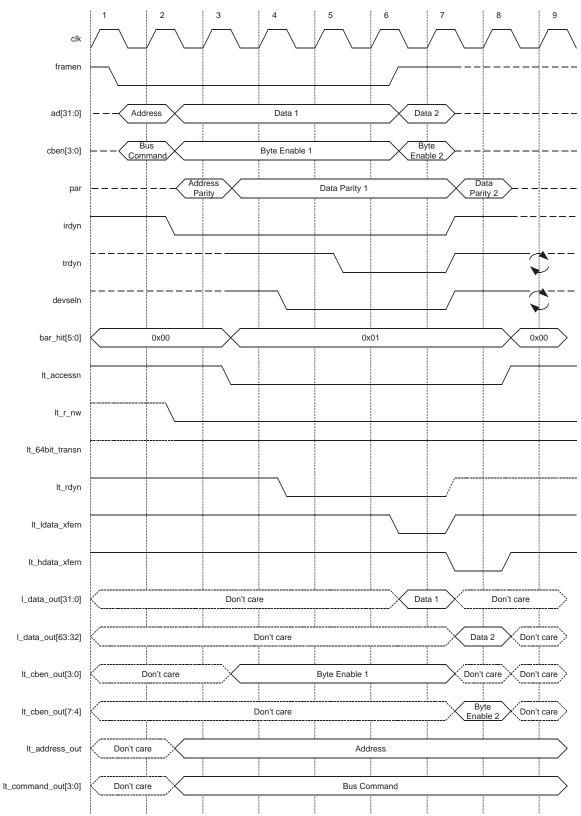

| 32-bit PCI Master with a 32-bit Local Bus                                            |    |

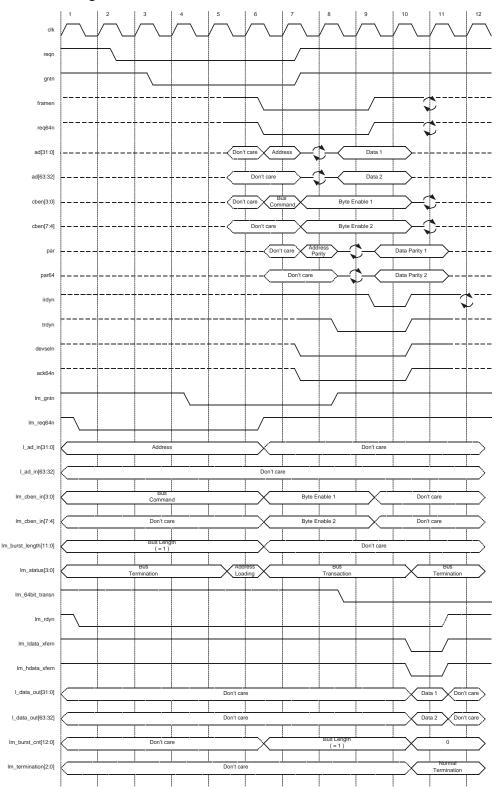

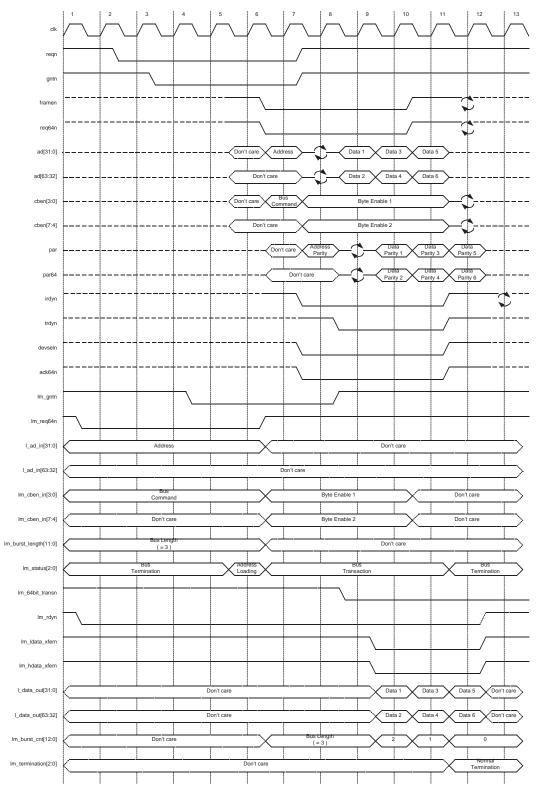

| 64-Bit PCI Master with a 64-Bit Local Bus                                            |    |

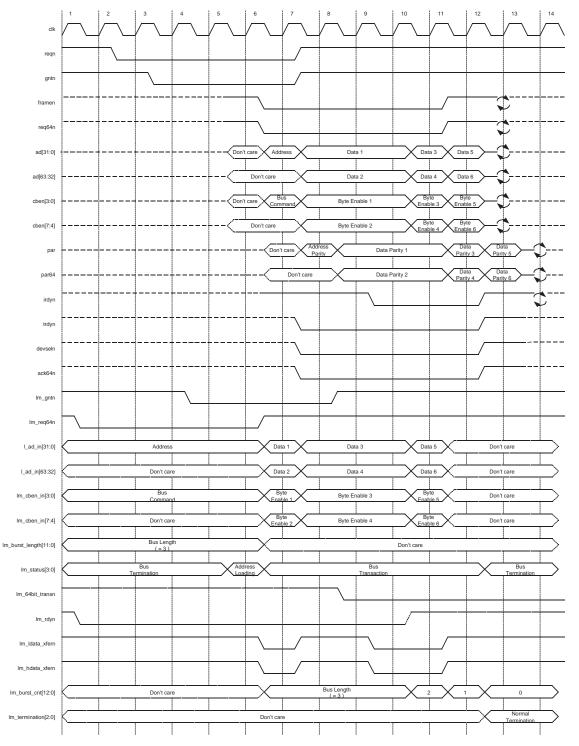

| 32-bit PCI Master with a 64-Bit Local Bus                                            |    |

|                                                                                      |    |

| Configuration Read and Write Transactions PCI Master I/O Read and Write Transactions |    |

| Advanced Master Transactions                                                         |    |

|                                                                                      |    |

| Wait States                                                                          |    |

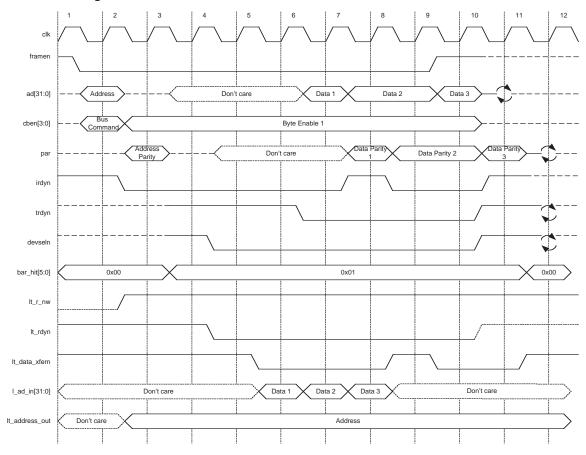

| Burst Read and Write Master Transactions                                             |    |

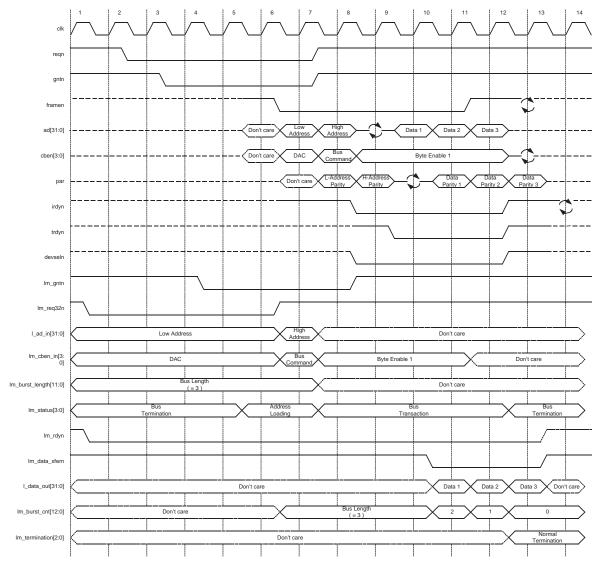

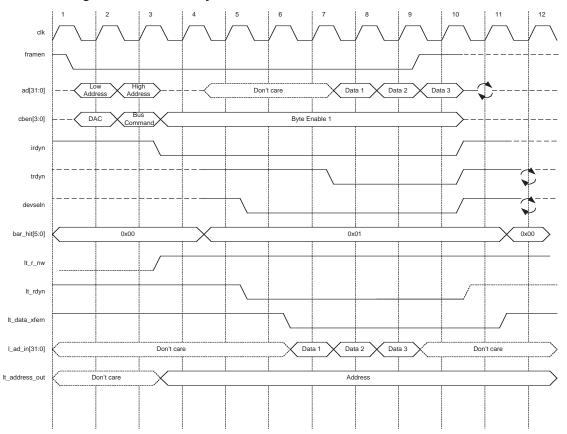

| Dual Address Cycle (DAC)                                                             |    |

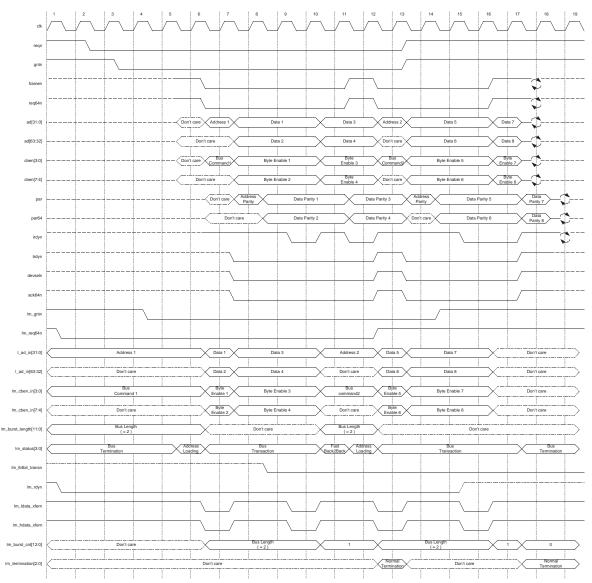

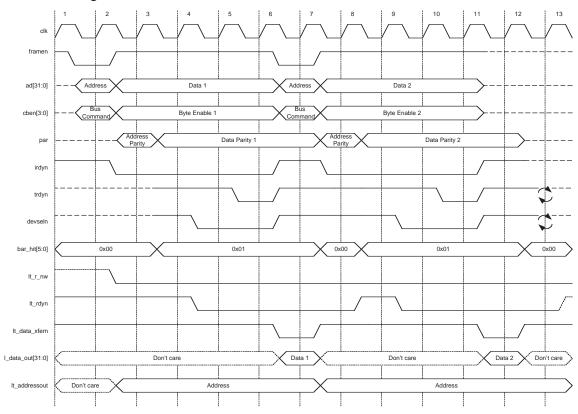

| Fast Back-to-Back Transactions                                                       |    |

| Master and Target Termination                                                        |    |

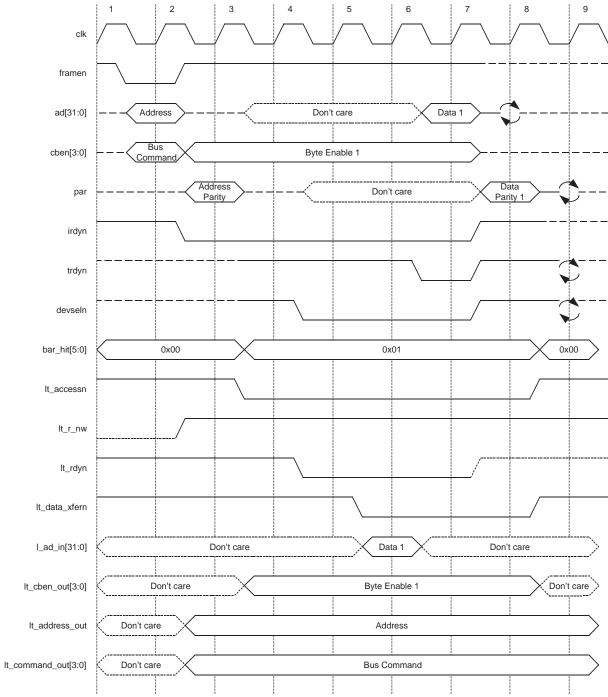

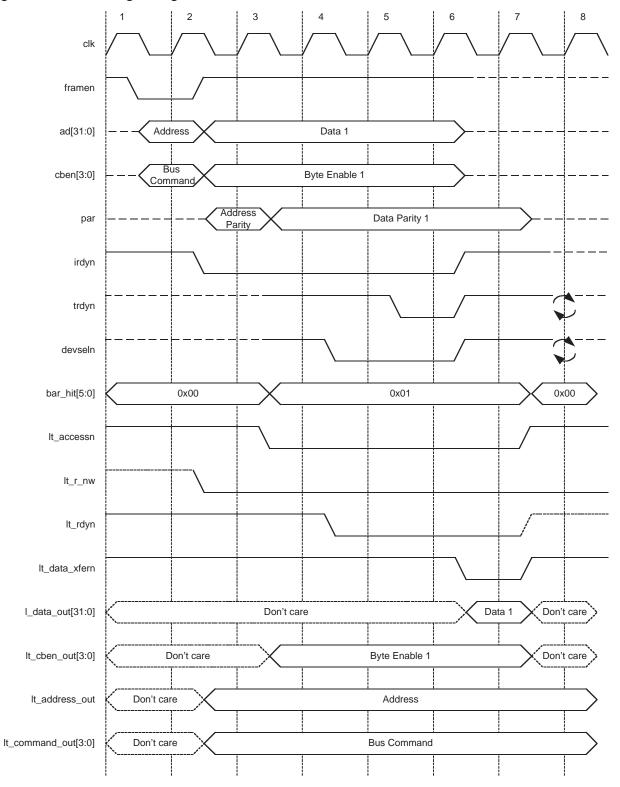

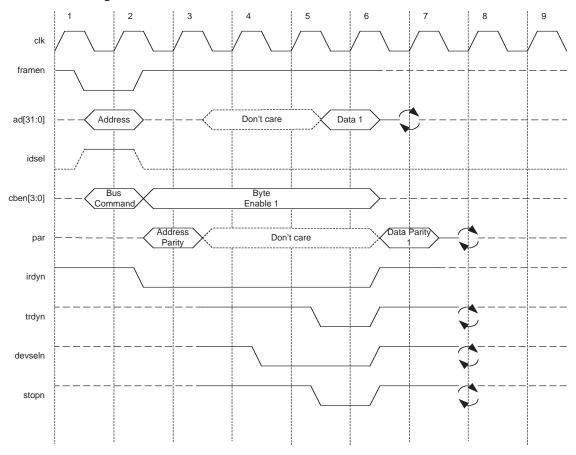

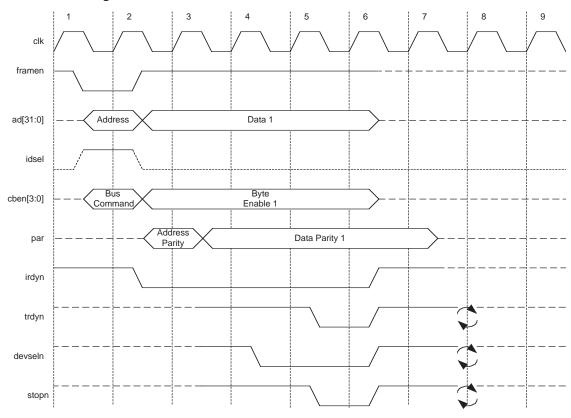

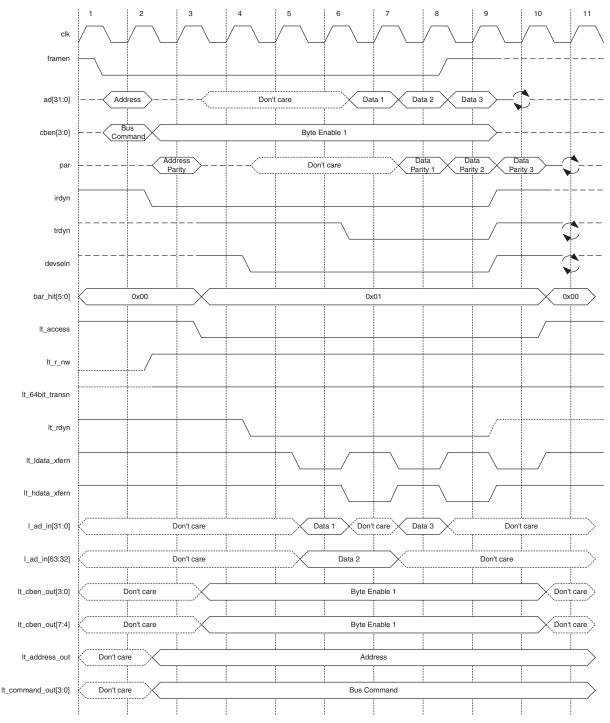

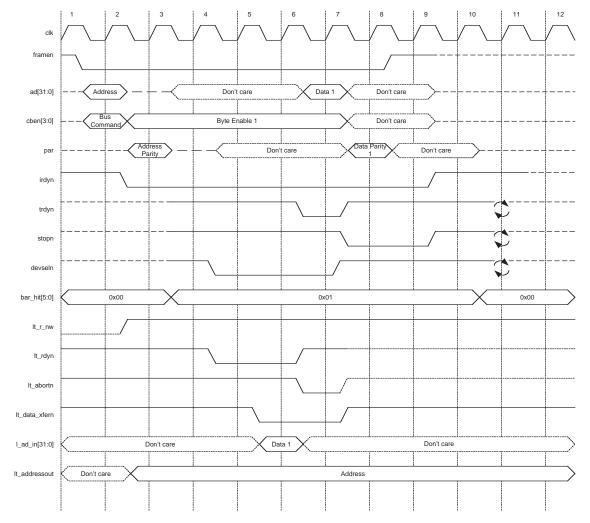

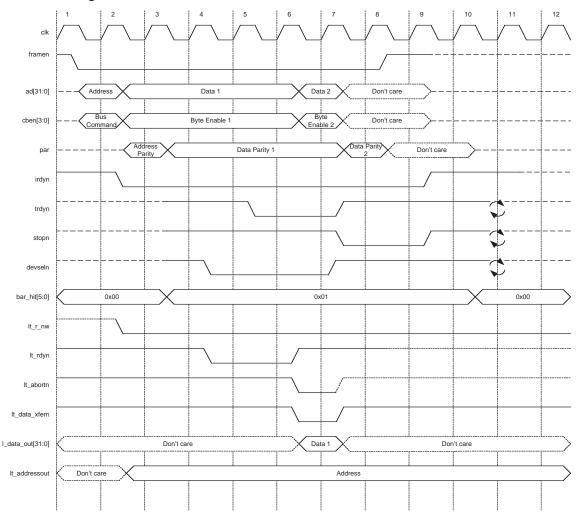

| Basic PCI Target Read and Write Transactions                                         | 81 |

© 2010 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

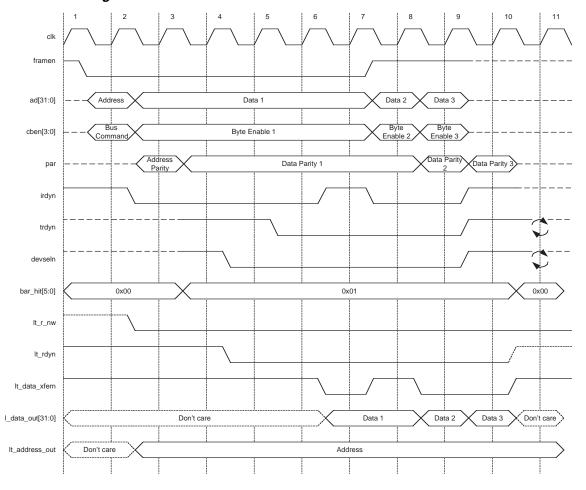

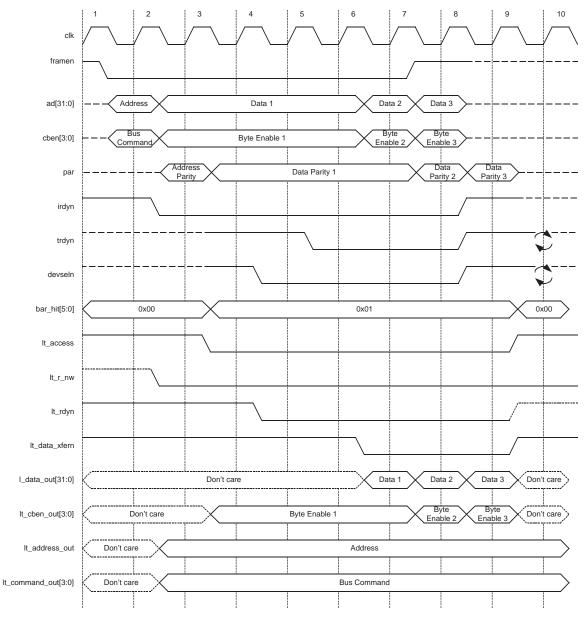

| 32-bit PCI Target with a 32-bit Local Bus Memory Transactions | 82  |

|---------------------------------------------------------------|-----|

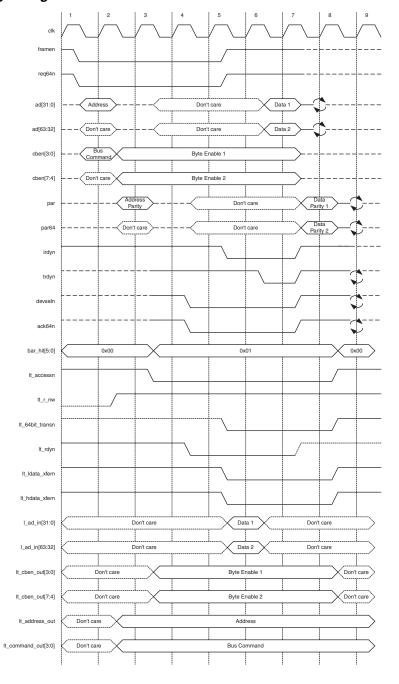

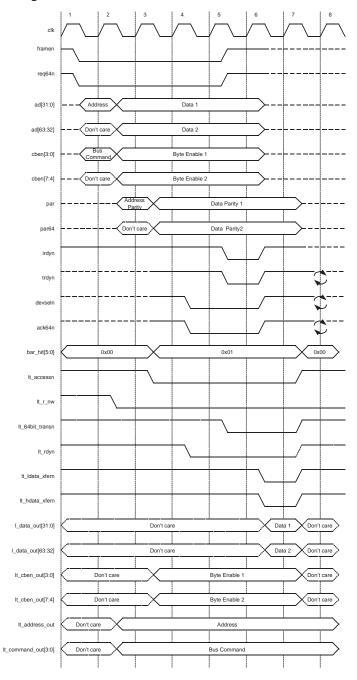

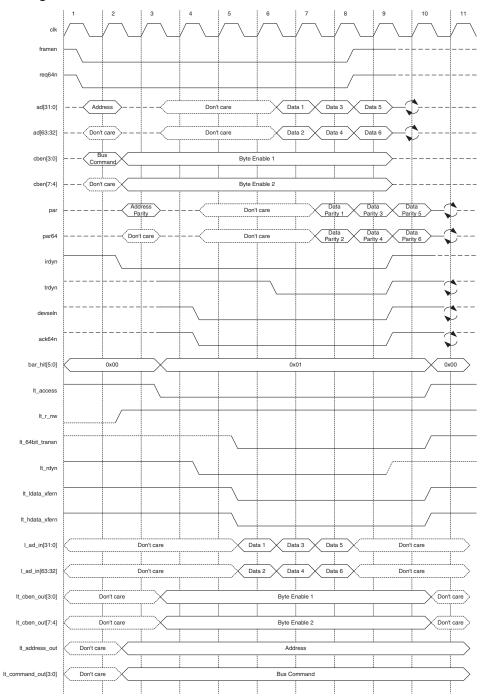

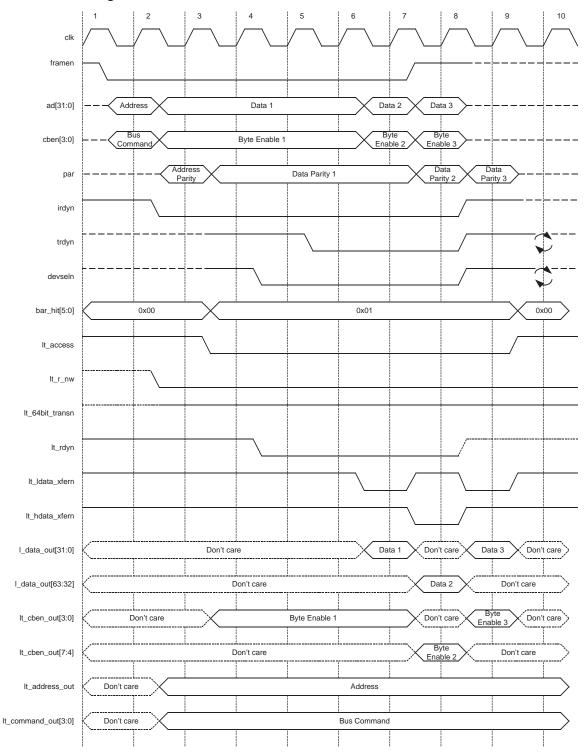

| 64-Bit PCI Target with a 64-Bit Local Bus                     | 87  |

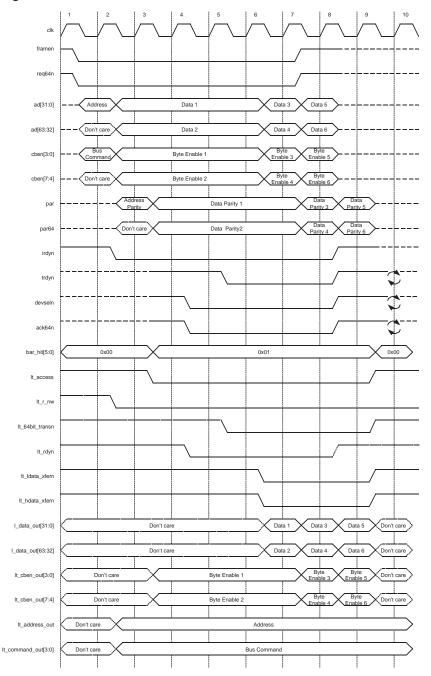

| 32-Bit PCI Target with a 64-Bit Local Bus                     | 90  |

| Configuration Read and Write Transactions                     | 94  |

| PCI Target I/O Read and Write Transactions                    | 96  |

| Advanced Target Transactions                                  | 97  |

| Wait States                                                   | 97  |

| Burst Read and Write Target Transactions                      | 100 |

| Dual Address Cycle (DAC)                                      | 115 |

| Fast Back-to-Back Transactions                                | 117 |

| Advanced Configuration Accesses                               | 120 |

| Target Termination                                            | 123 |

| Disconnect With Data                                          | 124 |

| Disconnect Without Data                                       | 127 |

| Retry                                                         | 130 |

| Target Abort                                                  | 133 |

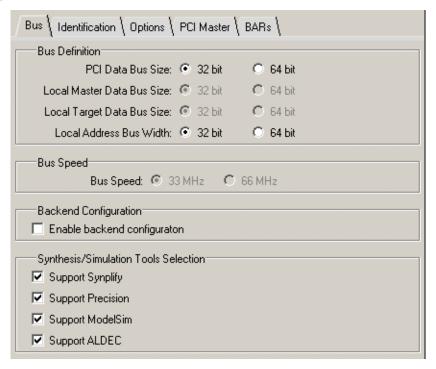

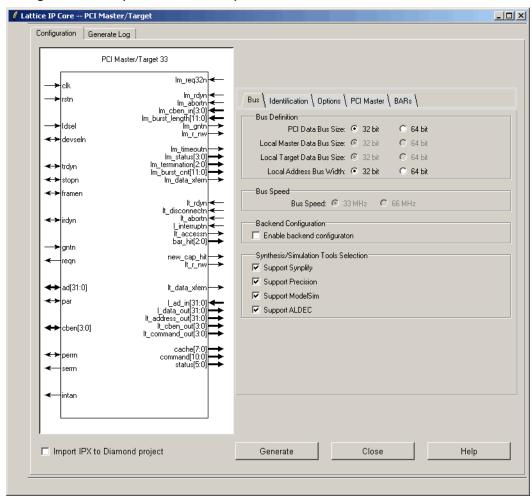

| Chapter 3. Parameter Settings                                 | 136 |

| Bus Tab                                                       |     |

| Bus Definition                                                | 137 |

| Backend Configuration                                         |     |

| Synthesis/Simulation Tools Selection                          |     |

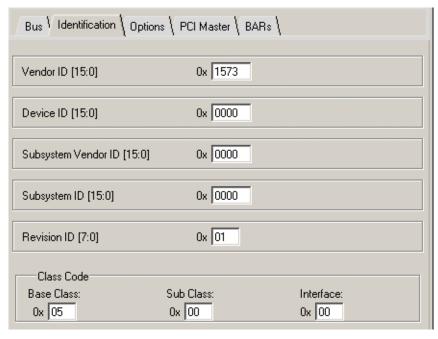

| Identification Tab                                            |     |

| Vendor ID [15:0]                                              | 139 |

| Device ID [15:0]                                              |     |

| Subsystem Vendor ID [15:0]                                    |     |

| Subsystem ID [15:0]                                           |     |

| Revision ID [15:0]                                            | 139 |

| Class Code (Base Class, Bus Class, Interface)                 | 139 |

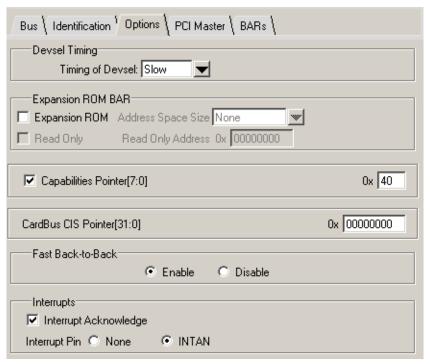

| Options Tab                                                   | 140 |

| Devsel Timing                                                 | 140 |

| Expansion ROM BAR                                             | 140 |

| Interrupts                                                    |     |

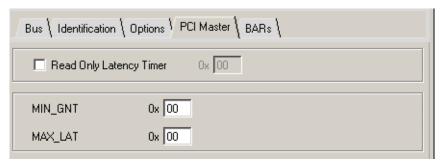

| PCI Master Tab (PCI Master/Target Cores Only)                 |     |

| Read Only Latency Timer                                       |     |

| MIN_GNT                                                       | 141 |

| MAX_LAT                                                       | 141 |

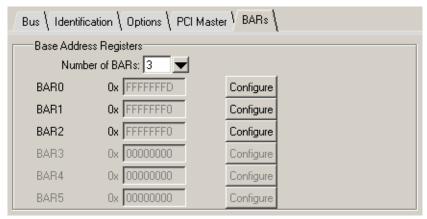

| BARs Tab                                                      |     |

| Base Address Registers                                        |     |

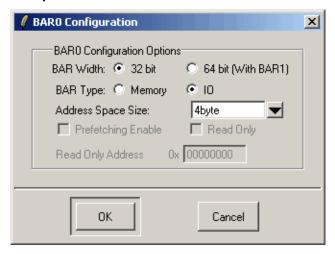

| BAR Configuration Options                                     |     |

| BAR Width                                                     |     |

| BAR Type                                                      |     |

| Address Space Size                                            |     |

| Prefetching Enable                                            |     |

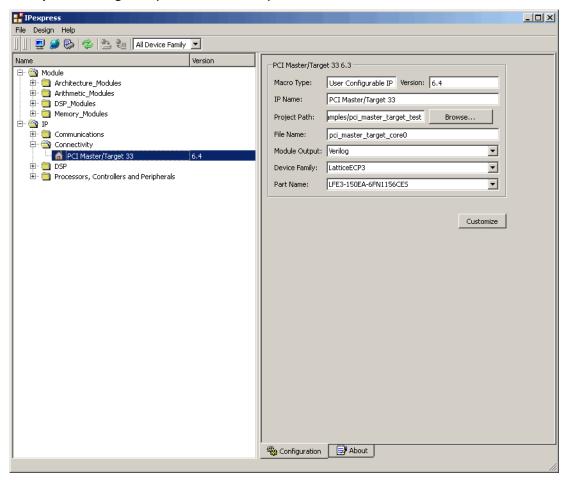

| Chapter 4. IP Core Generation                                 |     |

| Licensing the IP Core                                         | 143 |

| Getting Started                                               |     |

| IPexpress-Created Files and Top Level Directory Structure     | 146 |

| Instantiating the Core                                        |     |

| Running Functional Simulation                                 |     |

| Synthesizing and Implementing the Core in a Top-Level Design  |     |

| Hardware Evaluation                                           |     |

| Enabling Hardware Evaluation in Diamond                       |     |

| Enabling Hardware Evaluation in ispLEVER                      |     |

| Updating/Regenerating the IP Core                             | 149 |

| Regenerating an IP Core in Diamond                                 | 149 |

|--------------------------------------------------------------------|-----|

| Regenerating an IP Core in ispLEVER                                |     |

| Chapter 5. Support Resources                                       |     |

| Lattice Technical Support                                          |     |

| Online Forums                                                      |     |

| Telephone Support Hotline                                          |     |

| E-mail Support                                                     |     |

| Local Support                                                      |     |

| Internet                                                           |     |

| PCI-SIG Website                                                    |     |

| References                                                         |     |

| LatticeEC/ECP                                                      |     |

| LatticeECP2M                                                       |     |

| LatticeECP3                                                        |     |

| LatticeSC/M                                                        |     |

| LatticeSO/WLatticeSO/W                                             |     |

| LatticeXP                                                          |     |

|                                                                    |     |

| MachXO MachXO2                                                     |     |

|                                                                    | _   |

| Revision History                                                   |     |

| Appendix A. Resource Utilization                                   |     |

| LatticeECP and LatticeEC FPGAs                                     |     |

| Ordering Part Number                                               |     |

| LatticeECP2 FPGAs                                                  |     |

| Ordering Part Number                                               |     |

| LatticeECP2M FPGAs                                                 |     |

| Ordering Part Number                                               |     |

| LatticeECP3 FPGAs                                                  |     |

| Ordering Part Number                                               |     |

| LatticeXP FPGAs                                                    |     |

| Ordering Part Number                                               |     |

| LatticeXP2 FPGAs                                                   |     |

| Ordering Part Number                                               | 158 |

| MachXO FPGAs                                                       | 159 |

| Ordering Part Number                                               | 159 |

| MachXO2 FPGAs                                                      | 159 |

| Ordering Part Number                                               | 159 |

| LatticeSC FPGAs                                                    | 160 |

| Ordering Part Number                                               | 160 |

| Appendix B. Pin Assignments For Lattice FPGAs                      | 161 |

| Pin Assignment Considerations for LatticeECP and LatticeEC Devices |     |

| PCI Pin Assignments for Master/Target 33MHz 64-Bit Bus             |     |

| PCI Pin Assignments for Target 66MHz 64-Bit Bus                    |     |

| PCI Pin Assignments for Master/Target 33MHz 32-Bit Bus             |     |

| PCI Pin Assignments for Target 33MHz 32-Bit Bus                    |     |

| Pin Assignment Considerations for LatticeXP Devices                |     |

| PCI Pin Assignments for Master/Target 33MHz 32-Bit Bus             |     |

| PCI Pin Assignments for Target 33MHz 32-Bit Bus                    |     |

| PCI Pin Assignments for Master/Target 33MHz 64-Bit Bus             |     |

| Pin Assignment Considerations for MachXO Devices                   |     |

| PCI Pin Assignments for Target 33MHz 32-Bit Bus                    |     |

| PCI Pin Assignments for Target 66MHz 32-Bit Bus                    |     |

| PCI Pin Assignments for Master/Target 33MHz 32-Bit Bus             |     |

| . 5. 1 m. 1. cong. m. cond. or mactor, ranger continue of bit back | 170 |

### **Table of Contents**

| 178 |

|-----|

| 178 |

| 179 |

| 182 |

| 183 |

| 185 |

| 187 |

| 189 |

| 191 |

|     |

# Introduction

Lattice's Peripheral Component Interconnect (PCI) Intellectual Property (IP) cores provide an ideal solution that meets the needs of today's high performance PCI applications. The PCI IP cores provide a customizable, 32-bit or 64-bit PCI Master and Target or Target only solution that is fully compliant with the *PCI Local Bus Specification, Revision 3.0* for speeds up to 66MHz. The PCI cores bridge the gap between the PCI Bus and specific design applications, providing an integrated PCI solution. These cores allow designers to focus on the application rather than on the PCI specification, resulting in a faster time-to-market.

PCI is a widely accepted bus standard that is used in many applications including telecommunications, embedded systems, high performance peripheral cards, and networking. The family of PCI IP core is one of the many in Lattice's portfolio of IP cores. For more information on these and other products, refer to the Lattice web site at: <a href="http://www.latticesemi.com/products/intellectualproperty/">http://www.latticesemi.com/products/intellectualproperty/</a>.

This document covers Target only, Master and Target, 64-bit, and 32-bit PCI IP cores implemented in a number of devices. Details of Master and 64-bit operation only apply to the appropriate cores. Pin assignments for specific variations of this core are described at the end of this document.

#### **Quick Facts**

Table 1-1 through Table 1-8 give quick facts about the PCI IP core for LatticeEC<sup>™</sup>, LatticeECP<sup>™</sup>, LatticeECP<sup>™</sup>, LatticeECP<sup>™</sup>, LatticeECP<sup>™</sup>, LatticeECP<sup>™</sup>, LatticeSC<sup>™</sup>, MachXO<sup>™</sup>, MachXO<sup>™</sup>, and LatticeSCM<sup>™</sup> devices.

Table 1-1. PCI IP Core Quick Facts--PCI master/target 66MHz/64bit

|                         |                            |                                   |                               | PCI IP cor         | nfiguration                |                         |                       |  |  |  |

|-------------------------|----------------------------|-----------------------------------|-------------------------------|--------------------|----------------------------|-------------------------|-----------------------|--|--|--|

|                         |                            |                                   | PCI master/target 66MHz 64bit |                    |                            |                         |                       |  |  |  |

| Core                    | FPGA Families<br>Supported | LatticeEC<br>LatticeECP           | LatticeSC<br>LatticeSCM       |                    |                            |                         |                       |  |  |  |

| Requirements            | Minimal Device<br>Needed   | LFEC10E-<br>5F484C                | LFE2-12E-<br>6F484C           | LFXP15C-<br>5F388C | LFXP2-17E-<br>6F484C       | LFE3-35EA-<br>7FN484CES | LFSC3GA15<br>E-6F900C |  |  |  |

|                         | Data Path Width            |                                   |                               | 6                  | 4                          |                         |                       |  |  |  |

| Resource<br>Utilization | LUTs                       | 2500                              |                               |                    |                            |                         |                       |  |  |  |

|                         | Registers                  | 900                               |                               |                    |                            |                         |                       |  |  |  |

|                         | Lattice<br>Implementation  |                                   | Lattice                       | Diamond™ 1         | .0 or ispLEVE              | R <sup>®</sup> 8.1      |                       |  |  |  |

| Design Tool             | Synthesis                  |                                   | Synopsys <sup>®</sup> S       | Synplify™ Pro      | for Lattice D-             | 2009.12L-1              |                       |  |  |  |

| Support                 | Synthesis                  |                                   | Men                           | tor Graphics       | <sup>®</sup> Precision™ F  | RTL                     |                       |  |  |  |

|                         | Simulation                 |                                   | Aldec®                        | Active-HDL™        | <sup>™</sup> 8.2 Lattice E | dition                  |                       |  |  |  |

|                         | Simulation                 | Mentor Graphics ModelSim™ SE 6.3F |                               |                    |                            |                         |                       |  |  |  |

Table 1-2. PCI IP Core Quick Facts--PCI master/target 66MHz/32bit

|              |                            |                                  |                    | PCI IP co         | onfiguration         |                         |                       |  |  |  |

|--------------|----------------------------|----------------------------------|--------------------|-------------------|----------------------|-------------------------|-----------------------|--|--|--|

|              |                            |                                  | P                  | CI master/ta      | rget 66MHz 32        | 2bit                    |                       |  |  |  |

| Core         | FPGA Families<br>Supported | LatticeEC<br>LatticeECP          |                    |                   |                      |                         |                       |  |  |  |

| Requirements | Minimal Device<br>Needed   | LFEC6E-<br>5F256C                | LFE2-6E-<br>6F256C | LFXP6C-<br>5F256C | LFXP2-5E-<br>6FT256C | LFE3-17EA-<br>7FN484CES | LFSC3GA15E-<br>6F900C |  |  |  |

| Resource     | Data Path<br>Width         |                                  |                    |                   | 32                   |                         |                       |  |  |  |

| Utilization  | LUTs                       |                                  | 1600               |                   |                      |                         |                       |  |  |  |

|              | Registers                  | 700                              |                    |                   |                      |                         |                       |  |  |  |

|              | Lattice<br>Implementation  | Diamond 1.0 or ispLEVER 8.1      |                    |                   |                      |                         |                       |  |  |  |

| Design Tool  | Synthesis                  |                                  | Synopsys           | Synplify Pro      | for Lattice D-2      | 2009.12L-1              |                       |  |  |  |

| Support      | Oynthesis                  |                                  | N                  | lentor Graph      | ics Precision F      | RTL                     |                       |  |  |  |

|              | Simulation                 |                                  | Alde               | ec Active-HD      | L 8.2 Lattice E      | dition                  |                       |  |  |  |

|              | Simulation                 | Mentor Graphics ModelSim SE 6.3F |                    |                   |                      |                         |                       |  |  |  |

Table 1-3. PCI IP Core Quick Facts--PCI master/target 33MHz/64bit

|                         |                            |                                  |                                      | PCI IP co          | nfiguration             |                         |                       |  |  |  |

|-------------------------|----------------------------|----------------------------------|--------------------------------------|--------------------|-------------------------|-------------------------|-----------------------|--|--|--|

|                         |                            | PCI master/target 33MHz 64bit    |                                      |                    |                         |                         |                       |  |  |  |

| Core                    | FPGA Families<br>Supported | LatticeEC<br>LatticeECP          | Lattice ECP2<br>Lattice<br>ECP2M     | LatticeXP3         | LatticeSC<br>LatticeSCM |                         |                       |  |  |  |

| Requirements            | Minimal Device<br>Needed   | LFEC10E-<br>5F484C               | LFE2-12E-<br>6F484C                  | LFXP15C-<br>5F388C | LFXP2-17E-<br>6F484C    | LFE3-35EA-<br>7FN484CES | LFSC3GA15<br>E-6F900C |  |  |  |

| _                       | Data Path Width            | 64                               |                                      |                    |                         |                         |                       |  |  |  |

| Resource<br>Utilization | LUTs                       | 1400                             |                                      |                    |                         |                         |                       |  |  |  |

|                         | Registers                  | 800                              |                                      |                    |                         |                         |                       |  |  |  |

|                         | Lattice<br>Implementation  |                                  | [                                    | Diamond 1.0        | or ispLEVER 8.          | 1                       |                       |  |  |  |

| Design Tool             | Synthesis                  |                                  | Synopsys                             | Synplify Pro       | for Lattice D-20        | 009.12L-1               |                       |  |  |  |

| Support                 | Synthesis                  |                                  | N                                    | lentor Graphi      | cs Precision RT         | L                       |                       |  |  |  |

|                         | Simulation                 |                                  | Aldec Active-HDL 8.2 Lattice Edition |                    |                         |                         |                       |  |  |  |

|                         | Simulation                 | Mentor Graphics ModelSim SE 6.3F |                                      |                    |                         |                         |                       |  |  |  |

Table 1-4. PCI IP Core Quick Facts--PCI master/target 33MHz/32bit

|              |                                |                        |                                |                         | PCI IP config                 | guration          |                          |                         |                         |  |

|--------------|--------------------------------|------------------------|--------------------------------|-------------------------|-------------------------------|-------------------|--------------------------|-------------------------|-------------------------|--|

|              |                                |                        |                                | PCI                     | master/target                 | 33MHz 32          | 2bit                     |                         |                         |  |

| Core         | FPGA<br>Families<br>Supported  | MachXO                 | MachXO2                        | LatticeEC<br>LatticeECP | Lattice ECP2<br>Lattice ECP2M | LatticeXP         | LatticeXP2               | LatticeXP3              | LatticeSC<br>LatticeSCM |  |

| Requirements | Minimal<br>Device<br>Needed    | LCMXO1200<br>E-5FT256C | LCMXO-<br>1200HC-<br>6TG144CES | LFEC6E-<br>5F256C       | LFE2-6E-<br>6F256C            | LFXP6C-<br>5F256C | LFXP2-<br>5E-<br>6FT256C | LFE3-17EA-<br>7FN484CES | LFSC3GA1<br>5E-6F900C   |  |

| Resource     | Data Path<br>Width             |                        |                                |                         | 32                            |                   |                          |                         |                         |  |

| Utilization  | LUTs                           | 900                    |                                |                         |                               |                   |                          |                         |                         |  |

|              | Registers                      | 600                    |                                |                         |                               |                   |                          |                         |                         |  |

|              | Lattice<br>Implemen-<br>tation |                        |                                | Dia                     | amond 1.0 or is               | pLEVER 8          | 3.1                      |                         |                         |  |

| Design Tool  | Synthesis                      |                        |                                | Synopsys S              | Synplify Pro for              | Lattice D-2       | 2009.12L-1               |                         |                         |  |

| Support      | Synthesis                      |                        |                                | Me                      | ntor Graphics F               | Precision F       | RTL                      |                         |                         |  |

|              | O'mandatian                    |                        |                                | Aldec                   | Active-HDL 8.2                | 2 Lattice E       | dition                   |                         |                         |  |

|              | Simulation                     |                        |                                | Mento                   | or Graphics Mo                | delSim SE         | 6.3F                     |                         |                         |  |

Table 1-5. PCI IP Core Quick Facts--PCI target 66MHz/64bit

|                         |                            |                                  |                               | PCI IP con         | figuration           |                         |                         |  |  |

|-------------------------|----------------------------|----------------------------------|-------------------------------|--------------------|----------------------|-------------------------|-------------------------|--|--|

|                         |                            | PCI target 66MHz 64bit           |                               |                    |                      |                         |                         |  |  |

| Core                    | FPGA Families<br>Supported | LatticeEC<br>LatticeECP          | Lattice ECP2<br>Lattice ECP2M | LatticeXP          | LatticeXP2           | LatticeXP3              | LatticeSC<br>LatticeSCM |  |  |

| Requirements            | Minimal Device<br>Needed   | LFEC6E-<br>5F484C                | LFE2-12E-<br>6F484C           | LFXP10C-<br>5F388C | LFXP2-8E-<br>6FT256C | LFE3-17EA-<br>7FN484CES | LFSC3GA15<br>E-6F900C   |  |  |

| _                       | Data Path Width            |                                  |                               | 64                 | 4                    |                         |                         |  |  |

| Resource<br>Utilization | LUTs                       | 1300                             |                               |                    |                      |                         |                         |  |  |

|                         | Registers                  | 600                              |                               |                    |                      |                         |                         |  |  |

|                         | Lattice<br>Implementation  |                                  | Dia                           | amond 1.0 or       | ispLEVER 8.          | 1                       |                         |  |  |

| Design Tool             | Synthesis                  |                                  | Synopsys S                    | Synplify Pro fo    | or Lattice D-20      | 009.12L-1               |                         |  |  |

| Support                 | Synthesis                  |                                  | Me                            | ntor Graphics      | Precision R1         | ΓL                      |                         |  |  |

|                         | Simulation                 |                                  | Aldec                         | Active-HDL         | 8.2 Lattice Ed       | ition                   |                         |  |  |

|                         | Simulation                 | Mentor Graphics ModelSim SE 6.3F |                               |                    |                      |                         |                         |  |  |

Table 1-6. PCI IP Core Quick Facts--PCI target 66MHz/32bit

|                         |                            |                                                  |          | PCI IP c       | onfiguration         |                          |                       |  |  |  |

|-------------------------|----------------------------|--------------------------------------------------|----------|----------------|----------------------|--------------------------|-----------------------|--|--|--|

|                         |                            |                                                  |          | PCI targe      | t 66MHz 32bi         | i                        |                       |  |  |  |

| Core                    | FPGA Families<br>Supported | LatticeEC<br>LatticeECP                          |          |                |                      |                          |                       |  |  |  |

| Requirements            | Minimal Device<br>Needed   | LFEC3E- LFE2-6E- LFXP3C-<br>5Q208C 6F256C 5Q208C |          |                | LFXP2-5E-<br>6QN208C | LFE3-17EA-<br>7FTN256CES | LFSC3GA15<br>E-6F256C |  |  |  |

|                         | Data Path Width            |                                                  |          |                | 32                   |                          |                       |  |  |  |

| Resource<br>Utilization | LUTs                       | 900                                              |          |                |                      |                          |                       |  |  |  |

|                         | Registers                  | 500                                              |          |                |                      |                          |                       |  |  |  |

|                         | Lattice<br>Implementation  |                                                  | ı        | Diamond 1.0    | or ispLEVER          | 8.1                      |                       |  |  |  |

| Design Tool             | Synthesis                  |                                                  | Synopsys | s Synplify Pro | o for Lattice D      | -2009.12L-1              |                       |  |  |  |

| Support                 | Oynthesis                  |                                                  | N        | lentor Graph   | ics Precision        | RTL                      |                       |  |  |  |

|                         | Simulation                 |                                                  | Ald      | ec Active-HD   | L 8.2 Lattice I      | Edition                  |                       |  |  |  |

|                         | Simulation                 | Mentor Graphics ModelSim SE 6.3F                 |          |                |                      |                          |                       |  |  |  |

Table 1-7. PCI IP Core Quick Facts--PCI target 33MHz/64bit

|              |                            |                             |                     | PCI IP con         | figuration           |                         |                       |  |  |

|--------------|----------------------------|-----------------------------|---------------------|--------------------|----------------------|-------------------------|-----------------------|--|--|

|              |                            | PCI target 33MHz 64bit      |                     |                    |                      |                         |                       |  |  |

| Core         | FPGA Families<br>Supported | LatticeEC<br>LatticeECP     |                     |                    |                      |                         |                       |  |  |

| Requirements | Minimal Device<br>Needed   | LFEC6E-<br>5F484C           | LFE2-12E-<br>6F484C | LFXP10C-<br>5F388C | LFXP2-8E-<br>6FT256C | LFE3-17EA-<br>7FN484CES | LFSC3GA15E<br>-6F900C |  |  |

| Resource     | Data Path<br>Width         |                             |                     | 6-                 | 4                    |                         |                       |  |  |

| Utilization  | LUTs                       | 800                         |                     |                    |                      |                         |                       |  |  |

|              | Registers                  | 600                         |                     |                    |                      |                         |                       |  |  |

|              | Lattice<br>Implementation  | Diamond 1.0 or ispLEVER 8.1 |                     |                    |                      |                         |                       |  |  |

| Design Tool  | Synthesis                  |                             | Synopsys            | Synplify Pro fo    | or Lattice D-20      | 009.12L-1               |                       |  |  |

| Support      | Synthesis                  |                             | Me                  | entor Graphics     | s Precision RT       | L                       |                       |  |  |

|              | Simulation                 |                             | Alde                | c Active-HDL       | 8.2 Lattice Edi      | tion                    |                       |  |  |

|              | Simulation                 |                             | Men                 | tor Graphics N     | odelSim SE 6         | 5.3F                    |                       |  |  |

Table 1-8. PCI IP Core Quick Facts--PCI target 33MHz/32bit

|                     |                                |                        |                                |                         | PCI IP con                          | figuration        |                      |                          |                         |  |  |  |

|---------------------|--------------------------------|------------------------|--------------------------------|-------------------------|-------------------------------------|-------------------|----------------------|--------------------------|-------------------------|--|--|--|

|                     |                                |                        |                                | F                       | PCI target 3                        | 3MHz 32bi         | t                    |                          |                         |  |  |  |

| Core<br>Require-    | FPGA<br>Families<br>Supported  | MachXO                 | MachXO2                        | LatticeEC<br>LatticeECP | Lattice<br>ECP2<br>Lattice<br>ECP2M | LatticeXP         | LatticeXP2           | LatticeXP3               | LatticeSC<br>LatticeSCM |  |  |  |

| ments               | Minimal<br>Device<br>Needed    | LCMXO1200<br>E-5FT256C | LCMXO-<br>1200HC-<br>6TG144CES | LFEC3E-<br>5Q208C       | LFE2-6E-<br>6F256C                  | LFXP3C-<br>5Q208C | LFXP2-5E-<br>6QN208C | LFE3-17EA-<br>7FTN256CES | LFSC3GA15<br>E-6F256C   |  |  |  |

| Resource            | Data Path<br>Width             |                        |                                |                         | 3                                   | 2                 |                      |                          |                         |  |  |  |

| Utiliza-<br>tion    | LUTs                           | 600                    |                                |                         |                                     |                   |                      |                          |                         |  |  |  |

|                     | Registers                      |                        | 500                            |                         |                                     |                   |                      |                          |                         |  |  |  |

|                     | Lattice<br>Implemen-<br>tation |                        |                                | Dia                     | mond 1.0 o                          | rispLEVER         | 8.1                  |                          |                         |  |  |  |

| Design<br>Tool Sup- | Synthesis                      |                        |                                | Synopsys Sy             | ynplify Pro f                       | or Lattice D      | -2009.12L-1          |                          |                         |  |  |  |

| port                | Oynthosis                      |                        | Mentor Graphics Precision RTL  |                         |                                     |                   |                      |                          |                         |  |  |  |

|                     | Simulation                     |                        |                                | Aldec                   | Active-HDL                          | 8.2 Lattice       | Edition              |                          |                         |  |  |  |

|                     | Girialation                    |                        |                                | Mento                   | r Graphics N                        | /lodelSim S       | E 6.3F               |                          |                         |  |  |  |

### **Features**

- Available as 32/64-bit PCI bus and 32/64-bit local bus

- PCI SIG Local Bus Specification, Revision 3.0 compliant

- 64-bit addressing support (dual address cycle)

- Capabilities list pointer support

- · Parity error detection

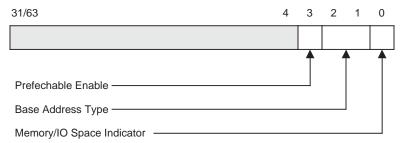

- Up to six Base Address Registers (BARs)

- · Fast back-to-back transaction support

- Supports zero wait state transactions

- Special cycle transaction support

- · Customizable configuration space

- Up to 66MHz PCI

- Fully synchronous design

# **Functional Description**

This chapter provides a functional description of the Lattice PCI IP core.

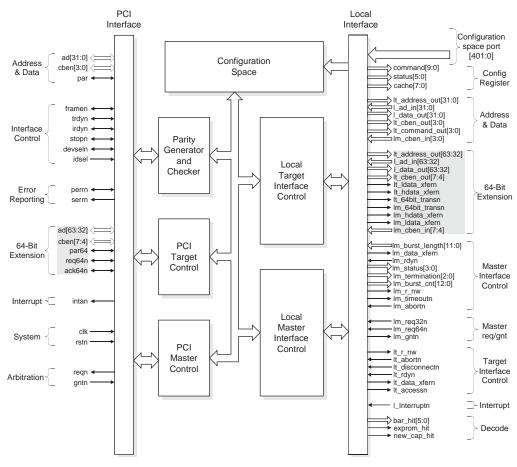

The PCI IP cores bridge the PCI bus to the back-end application. They decode transactions and pass PCI requests to the Local Interface. The back-end applications then send or receive the proper data associated with the PCI Interface via their Local Interface to respond to the PCI transactions. In the case of master versions the core executes PCI bus transactions based on back-end requests. Figure 2-1 illustrates the functional modules and internal bus structure used in the PCI IP core.

### **Block Diagram**

Figure 2-1. PCI IP core Block Diagram

Note: Signals in shaded boxes are used for 64-bit PCI Cores.

The PCI Master Target IP Core consists of multiple blocks, as shown in Figure 2-1. This section provides a detailed description of these blocks.

#### **PCI Master Control**

The PCI Master Control interfaces with the PCI bus. It supports all of the address and command signals required to execute transactions on the PCI bus for both 32-bit and 64-bit PCI applications. A list of the supported PCI signals is available in the PCI Interface Signals section of this document. Once the Local Master Interface Control is granted the bus, it passes the transaction information to the PCI Master Control using the internal bus. The PCI Master Control then requests and executes the transaction on the PCI bus. The PCI IP cores support all of the

commands specified in the PCI Local Bus Specification, Revision 3.0. Table 2-1 lists the supported PCI commands.

Table 2-1. PCI IP Core Command Support

| cben[3:0] | Command                     | Support |

|-----------|-----------------------------|---------|

| 0000      | Interrupt Acknowledge       | Yes     |

| 0001      | Special Cycle               | Yes     |

| 0010      | I/O Read                    | Yes     |

| 0011      | I/O Write                   | Yes     |

| 0100      | Reserved                    | Ignored |

| 0101      | Reserved                    | Ignored |

| 0110      | Memory Read                 | Yes     |

| 0111      | Memory Write                | Yes     |

| 1000      | Reserved                    | Ignored |

| 1001      | Reserved                    | Ignored |

| 1010      | Configuration Read          | Yes     |

| 1011      | Configuration Write         | Yes     |

| 1100      | Memory Read Multiple        | Yes     |

| 1101      | Dual Address Cycle          | Yes     |

| 1110      | Memory Read Line            | Yes     |

| 1111      | Memory Write and Invalidate | Yes     |

The PCI Master control supports data transfer requirements for both high and low throughput back-end applications. It maintains up to the maximum 528 MBytes per second (MBps) burst data transfer rate when operating at 66MHz with a 64-bit data bus. The Advanced Master Transactions section of this document describes burst data transfers in further detail. For slower applications, single data phase transactions can also be easily implemented. The Basic PCI Master Read and Write Transactions section describes these basic transactions in detail.

### **PCI Target Control**

The PCI Target control interfaces with the PCI bus. It processes the address, data, command and control signals to transfer data to and from the PCI IP core for both 32-bit and 64-bit PCI applications. A list of the supported PCI signals is available in the PCI Interface Signals section. Once the PCI Target control detects a transaction, it passes the transaction information to the Local Interface control using the internal bus. It also responds to most Configuration Space accesses with no intervention from the Local Interface. The PCI IP core supports all of the commands specified in the *PCI Local Bus Specification, Revision 3.0.* Table 2-1 lists the supported PCI commands.

When designing for a particular target application, the back-end target design may not support all the commands listed in Table 2-1. As a result, the PCI IP core does not transfer data using those commands. For cases where the back-end target application does not support all the commands, it must issue the proper termination as described in the Target Termination section of this document.

The PCI Target control supports the data transfer requirements for both high and low throughput back-end applications. It can maintain a 528 MBps transfer rate during burst transactions when operating at 66MHz with a 64-bit data bus. The Advanced Target Transactions section describes the Burst transactions in further detail. For slower applications, single data phase transactions can also be easily implemented. The Basic PCI Target Read and Write Transactions section describes the these basic transactions in detail

#### **Local Master Interface Control**

The Local Master Interface facilitates master transactions on the PCI Bus with the commands listed in Table 2-1. The Local Master Interface Control passes the local master transaction request from the user's application to the PCI Master Control which then executes the PCI bus transaction.

### **Local Target Control**

The Local Target Control responds to target transactions on the PCI bus. Fully decoded BAR select signals (bar\_hit) and new capabilities select signal (new\_cap\_hit) are provided by the Local Target Control to indicate that the PCI IP core has been selected for a transaction. Registered address and command signals are available at the Local Interface from the Local Interface Control for the back-end application to properly handle the core's request. Additionally, the Local interface also supplies Configuration Space Register signals and a local interrupt request (l\_interruptn) for users' applications. A full list of Local Interface signals and descriptions is available in the Local Interface Signals section.

### **Configuration Space**

The Configuration Space implements all the necessary Configuration Space registers required to support a single-function PCI IP core. It provides the first 64 bytes of header type 0, which is used for all device types other than PCI-to-PCI and CardBus bridges. The first 64 bytes of the predefined header region contain fields that uniquely identify the device and allow the device to be generically controlled. This predefined header portion of the Configuration Space is divided into two parts. The first 16 bytes of the header are defined the same way regardless of the type of device. The remaining bytes have different definitions depending on the functionality that the PCI IP core supports. These bytes include six Base Address Registers (BARs), the Capabilities Pointer (Cap Ptr), and the registers that control the interrupt capability. Refer to the Configuration Space Set-up section for additional information on the Configuration Space.

Accesses to the first 64 bytes of the Configuration Space are completed by the PCI IP core control with no intervention from the Local Target Interface control. Access beyond the first 64 bytes, such as the Capabilities List, is left to the Local Target Interface control. These transactions are described in the Advanced Configuration Accesses section.

### **Parity Generator and Checker**

Parity checking must occur on every PCI address and data cycle to be compliant with the *PCI Local Bus Specification, Revision 3.0.* The PCI IP core's Parity Generator and Checker module does all parity checking for the PCI device. The Parity Generator and Checker determines if the master is successful in addressing the desired target. It also verifies that data transfers occur correctly between the master and target devices. The address and byte enable signals are included in every calculation to ensure accuracy. Each address and data cycle that occurs on the PCI bus is checked for errors.

The parity check signals perrn and serrn are enabled or disabled using bit 6 and bit 8 of the PCI Command Register, which is part of the Configuration Space.

# **Signal Descriptions**

Pin Assignments for the evaluation configurations are shown "Pin Assignments For Lattice FPGAs" on page 161. Final selection of the pinouts is left to the designer to allow for maximum flexibility in the design. Pinouts are defined in the HDL source code, or as follows:.

- In Diamond, choose **View > Show Views > File List**, double-click the.lpf file, and edit the file to add pin location preferences.

- In ispLEVER, double-click **Edit Preference (ASCII)** in the Processes window, and edit the file in the Text Editor to add pin location preferences.

Refer to the Diamond or ispLEVER software help for additional information.

There are five types of signals defined in Table 2-2.

Table 2-2. Signal Types

| Signal Type | Description                                                                                                                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| in          | Input is a standard input only signal.                                                                                                                                                           |

| out         | Output is a standard output only signal.                                                                                                                                                         |

| t/s         | Tri-state is a bidirectional, tri-state input/output pin.                                                                                                                                        |

| s/t/s       | Sustained Tri-State is an active low tri-state signal owned and driven by one agent at a time.                                                                                                   |

| o/d         | <b>Open Drain</b> allows multiple devices to share as a wire-OR. A pull-up is required to sustain the inactive state until another agent drives it and must be provided by the central resource. |

## **PCI Interface Signals**

The PCI Interface signals correspond to the PCI bus specification. Table 2-3 shows the input and output signals for the PCI IP core. These are the signals required by the PCI IP core to handle PCI bus side transactions. Table 2-3 describes each signal.

In addition to the signals required by the PCI IP core, there are some signals on the PCI Bus, referred to as "Additional Signals" in the PCI specifications, which must be handled appropriately to insure proper PCI IP core functions in a system. Refer to the relevant PCI specifications for a description of those Additional Signals (which are beyond the scope of this document). Examples of this type of signal are M66EN and PRSNT [1:0].

Table 2-3. PCI IP Core Signals<sup>1</sup>

| Name         | I/O     | Polarity | Description                                                                                                                                                            |

|--------------|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI System   | )       |          |                                                                                                                                                                        |

| clk          | in      | _        | The PCI system clock provides timing for all transactions. The clock frequency operates up to 66MHz. This clock is also used to provide timing to the Local Interface. |

| rstn         | in      | low      | The asynchronous PCI system reset is used to set the PCI device to a starting known and stable state.                                                                  |

| PCI Addres   | s and D | ata      |                                                                                                                                                                        |

| ad[31:0]     | t/s     | _        | The multiplexed address and data bus.                                                                                                                                  |

| cben[3:0]    | t/s     | _        | Multiplexed command and byte enable signals.                                                                                                                           |

| par          | t/s     | _        | The par signal generates even parity for ad [31:0] and cben [3:0] signals                                                                                              |

| PCI Interfac | e Conti | rol      |                                                                                                                                                                        |

| framen       | s/t/s   | low      | The framen signal is driven by the current master and used to indicate the start of cycle and the duration of the cycle.                                               |

| irdyn        | s/t/s   | low      | The initiator ready signal indicates that the current master is ready for the data phase.                                                                              |

| trdyn        | s/t/s   | low      | The target ready signal indicates that the current target is ready for the data phase.                                                                                 |

| stopn        | s/t/s   | low      | The PCI IP core, as a target, drives this signal low requesting to stop the current transaction.                                                                       |

| idsel        | in      | _        | The initialization device select is used to select a target for configuration reads and writes.                                                                        |

| devseln      | s/t/s   | low      | Device select is actively driven by the PCI IP core to indicate that it is the target of the bus transaction.                                                          |

Table 2-3. PCI IP Core Signals<sup>1</sup> (Continued)

| Name         | I/O       | Polarity | Description                                                                           |

|--------------|-----------|----------|---------------------------------------------------------------------------------------|

| PCI Error R  | eportin   | g        |                                                                                       |

| perrn        | s/t/s     | low      | Data parity error is used to report parity errors in the data phase.                  |

| serrn        | o/d       | low      | System error is used to indicate catastrophic errors.                                 |

| PCI Interru  | pt        |          |                                                                                       |

| intan        | o/d       | low      | Interrupt A is used to request an interrupt.                                          |

| PCI Bus Ar   | bitratio  | n        |                                                                                       |

| reqn         | out       | low      | Request for the use of PCI bus.                                                       |

| gntn         | in        | low      | Grant the master's access to PCI bus.                                                 |

| PCI 64-Bit I | Extension | on       |                                                                                       |

| ad[63:32]    | t/s       | _        | The upper 32 bits of multiplexed address and data bus.                                |

| cben[7:4]    | t/s       | _        | The upper, multiplexed command and byte enable signals for 64-bit applications.       |

| par64        | t/s       | _        | The par64 signal generates even parity for ad [63:32] and cben [7:4] signals.         |

| req64n       | s/t/s     | low      | Used by the master to request a 64-bit data transaction.                              |

| ack64n       | s/t/s     | low      | Signal used to indicate the acknowledgement of a request for 64-bit data transaction. |

<sup>1.</sup> Shaded rows apply to 64-bit applications.

### **Local Interface Signals**

The Local Interface provides all the necessary address and control signals to respond to and initiate transactions associated with the PCI bus. Command and status information are also available at the Local Interface, so the back-end application logic can essentially monitor the PCI bus. Table 2-4 contains the Local Interface signals that are divided into three different categories: Local Bus Signals, Local Target Bus signals and Local Master Bus signals.

The Local Bus Signals are shared between the Local Master Interface and Local Target Interface. These signals are typically denoted with an "1\_". The Local Target Bus signals are used by the Local Target Interface and are denoted using "1t\_". The Local Master Bus signals are used by the Local Master interface and are denoted using "1m".

Table 2-4. Local Interface Signals<sup>1</sup>

| Name                   | I/O                    | Polarity | Description                                                                                                                                                                                                                                                              |  |  |  |

|------------------------|------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Local Address and Data | Local Address and Data |          |                                                                                                                                                                                                                                                                          |  |  |  |

| l_ad_in[31:0]          | in                     | -        | Local address/data input. The address input is used in Master Read/Write transactions, and the data input is used for master write/target read transactions                                                                                                              |  |  |  |

| l_data_out[31:0]       | out                    | _        | Local Data output. Local side lower DWORD data output for a master read or a target write.                                                                                                                                                                               |  |  |  |

| lt_address_out [31:0]  | out                    | _        | The local address bus for target read and write. This bus indicates the start address of the transaction. The bus, lt_address_out [31:0], is latched one clock after the framen signal is asserted on each transaction and remains unchanged until the next transaction. |  |  |  |

| lt_cben_out[3:0]       | out                    | low      | The local byte enables for target read and write. The <code>lt_cben_out[3:0]</code> determine which byte lanes of <code>l_data_out[31:0]</code> or <code>l_ad_in[31:0]</code> carry meaningful data.                                                                     |  |  |  |

| lt_command_out[3:0]    | out                    | _        | The $lt\_command\_out$ [3:0] latches the command information during the address phase of a PCI cycle. It indicates the PCI bus command for the current cycle (refer to Table 2-1).                                                                                       |  |  |  |

| lm_cben_in[3:0]        | in                     | low      | Local master command and byte enables.                                                                                                                                                                                                                                   |  |  |  |

Table 2-4. Local Interface Signals<sup>1</sup> (Continued)

| Name                   | I/O | Polarity | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|------------------------|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Local 64-Bit Extension |     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| l_ad_in[63:32]         | in  | _        | Local address/data input. The address input is used in Master Read/Write transactions, and the data input is used for master write/target read transactions.                                                                                                                                                                                                                                                                                       |  |

| 1_data_out[63:32]      | out | _        | Local Data output. Local side upper DWORD data output for a master read or a target write.                                                                                                                                                                                                                                                                                                                                                         |  |

| lt_address_out [63:32] | out | _        | The local address bus for target read and write. This bus is valid only for 64bit address bar. The 64-bit combined signal lt_address_out [63:0] indicates the start address of the transaction. The high 32bit of the bus, lt_address_out [63:32], is latched two clock cycles after the framen signal is asserted on each transaction (only for dual address cycle) and remains unchanged until the next transaction.                             |  |

| lt_cben_out[7:4]       | out | low      | The local byte enables for 64-bit target read and write. The lt_cben_out[7:4] determine which byte lanes of l_data_out[63:32] or l_ad_in[63:32] carry meaningful data.                                                                                                                                                                                                                                                                             |  |

| lt_ldata_xfern         | out | low      | This signal works same as lt_data_xfern. It applies to lower DWORD when local bus is 64bit.                                                                                                                                                                                                                                                                                                                                                        |  |

| lt_hdata_xfern         | out | low      | This signal works same as lt_data_xfern. It applies to upper DWORD when local bus is 64bit.                                                                                                                                                                                                                                                                                                                                                        |  |

| lt_64bit_transn        | out | low      | Signal to the local target that a 64-bit read or write transaction is underway on pci bus.                                                                                                                                                                                                                                                                                                                                                         |  |

| lm_ldata_xfern         | out | low      | This signal works same as lm_data_xfern. It applies to lower DWORD when local bus is 64bit.                                                                                                                                                                                                                                                                                                                                                        |  |

| lm_hdata_xfern         | out | low      | This signal works same as lm_data_xfern. It applies to upper DWORD when local bus is 64bit.                                                                                                                                                                                                                                                                                                                                                        |  |

| lm_64bit_transn        | out | low      | Signal to the local master that a 64-bit read or write transaction is underway on PCI bus.                                                                                                                                                                                                                                                                                                                                                         |  |

| lm_cben_in[7:4]        | in  | low      | Local master byte enables.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Local Interrupt        |     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| l_interruptn in low    |     | low      | The local side interrupt request indicates that the Local Interface is requesting an interrupt. This signal asserts the PCI side interrupt signal, intan, if interrupts are enabled in the Configuration Space.                                                                                                                                                                                                                                    |  |

| Config Register        |     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| cache[7:0]             | out | _        | The cache signal indicates the cache length in the cache registers defined in the Configuration Space                                                                                                                                                                                                                                                                                                                                              |  |

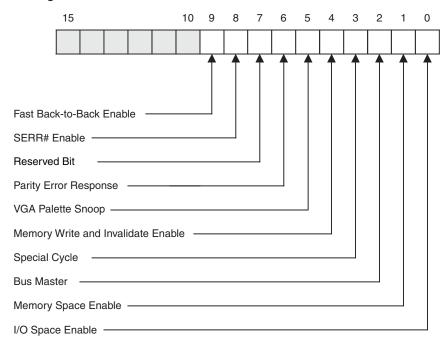

| command[9:0]           | out | _        | Command register bits from the Configuration Space. Bit 0 - I/O space enable, Command[0] Bit 1 - Memory space enable, Command[1] Bit 2 - Master enable, Command[2] Bit 3 - Special cycles enable, Command[3] Bit 4 - Memory write and invalidate enable, Command[4] Bit 5 - VGA Palette Snoop, Command[5] Bit 6 - Parity Error Response, Command[6] Bit 7 - Reserved Bit 8 - SERR# enable, Command[8] Bit 9 - Fast back-to-back enable, Command[9] |  |

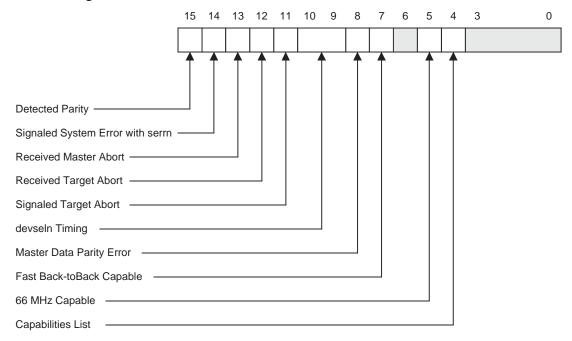

| status[5:0]            | out | _        | Status register bits from the Configuration Space. Bit 0 - Master Data Parity Error, Status[8] Bit 1 - Signaled Target Abort, Status[11] Bit 2 - Received Target Abort, Status[12] Bit 3 - Received Master Abort, Status[13] Bit 4 - Signaled System Error with SERR#, Status[14] Bit 5 - Detected Parity Error, Status[15]                                                                                                                        |  |

Table 2-4. Local Interface Signals<sup>1</sup> (Continued)

| Name                              | I/O | Polarity | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Local Target Interface            |     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| lt_abortn                         | in  | low      | Local target abort request is used to request a target abort on the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| lt_disconnectn                    | in  | low      | Local target disconnect (or retry) is used to request early termination of a bus transaction on the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                   |

| lt_rdyn                           | in  | low      | Local target ready signal indicates that the Local Interface is ready to receive or send data.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| lt_r_nw                           | out | _        | Read/Write (read/not write) to signal whether the current transaction is a read or write. 1 = read, 0 = write                                                                                                                                                                                                                                                                                                                                                                                                  |

| lt_accessn                        | out | low      | Local target can access local interface if <code>lt_accessn</code> is active. Once <code>lt_accessn</code> active, local target needs to be ready for next process based on <code>lt_command_out.lt_accessn</code> is active during either of active <code>bar_hit, exprom_hit</code> or <code>new_cap_hit</code> . It is also active during special cycle command.                                                                                                                                            |

| lt_data_xfern                     | out | low      | This signal indicates local input data (l_ad_in) being read or local output data (l_data_out) being available at current clock cycle. When lt_data_xfern is active, if core reads data from l_ad_in, back-end can update l_ad_in for next data at next clock cycle. If core writes data on l_data_out, back-end can get valid data from l_data_out. It is only used when the local bus is 32 bits.                                                                                                             |

| <b>Local Target Address Decod</b> | е   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bar_hit[5:0]                      | out | high     | The bar_hit signal indicates that the master is requesting a transaction that falls within one of the Base Address register ranges.                                                                                                                                                                                                                                                                                                                                                                            |

| new_cap_hit                       | out | high     | New Capabilities List hit. new_cap_hit indicates that the master is requesting a Configuration Space register out of internal registers (00h-3fh), that is 40h-FFh., Although the hardware associated with the New Capabilities reside in the back-end logic, logically they are part of the PCI Configuration Space.                                                                                                                                                                                          |