# High Voltage High Efficiency Power Factor Correction Controller

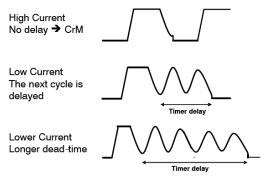

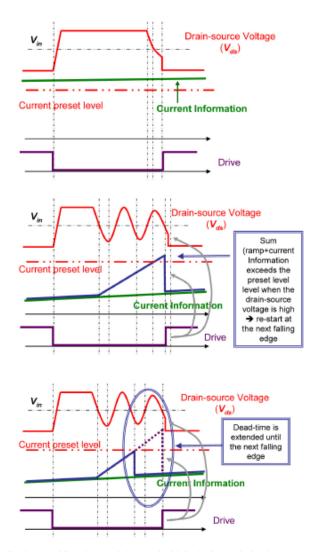

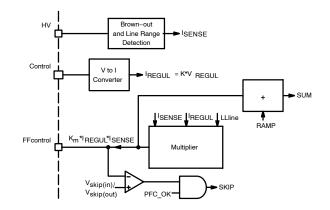

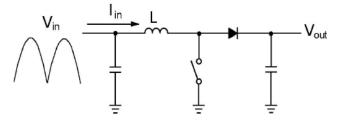

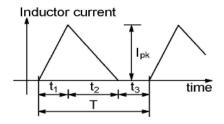

The NCP1615 is a high voltage PFC controller designed to drive PFC boost stages based on an innovative Current Controlled Frequency Foldback (CCFF) method. In this mode, the circuit operates in critical conduction mode (CrM) when the inductor current exceeds a programmable value. When the current is below this preset level, the NCP1615 linearly decays the frequency down to a minimum of about 26 kHz at the sinusoidal zero–crossing. CCFF maximizes the efficiency at both nominal and light load. In particular, the standby losses are reduced to a minimum. Innovative circuitry allows near– unity power factor even when the switching frequency is reduced.

The integrated high voltage start–up circuit eliminates the need for external start–up components and consumes negligible power during normal operation. Housed in a SOIC–14 or SOIC–16 package, the NCP1615 incorporates the features necessary for robust and compact PFC stages, with few external components.

## **General Features**

- High Voltage Start-Up Circuit with Integrated Brownout Detection

- Input to Force Controller into Standby Mode

- Restart Pin Allows Adjustment of Bulk Voltage Hysteresis in Standby Mode

- Skip Mode Near the Line Zero Crossing

- Fast Line / Load Transient Compensation

- Valley Switching for Improved Efficiency

- High Drive Capability: -500 mA/+800 mA

- Wide V<sub>CC</sub> Range: from 9.5 V to 28 V

- Input Voltage Range Detection

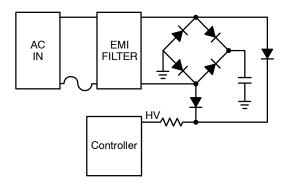

- Input X2 Capacitor Discharge Circuitry

- Power Saving Mode (PSM) Enables < 30 mW No-load Power Consumption

- This is a Pb and Halogen Free Device

#### Safety Features

- Adjustable Bulk Undervoltage Detection (BUV)

- Soft Overvoltage Protection

- Line Overvoltage Protection

- Overcurrent Protection

# **ON Semiconductor®**

http://onsemi.com

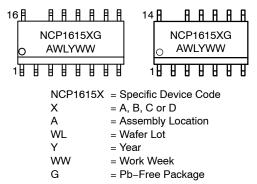

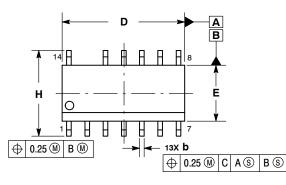

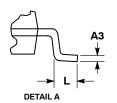

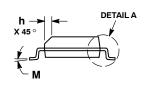

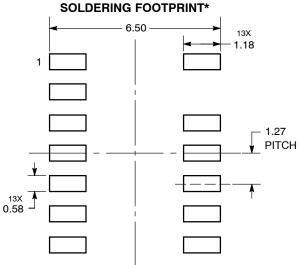

## MARKING DIAGRAMS

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.

- Open Pin Protection for FB and FOVP/BUV Pins

- Internal Thermal Shutdown

- Bi–Level Latch Input for OVP and OTP

- Bypass/Boost Diode Short Circuit Protection

- Open Ground Pin Protection

#### **Typical Applications**

- PC Power Supplies

- Off Line Appliances Requiring Power Factor Correction

- LED Drivers

- Flat TVs

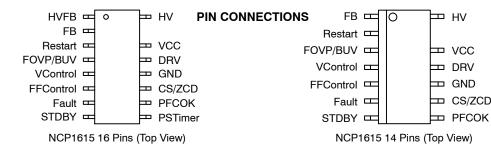

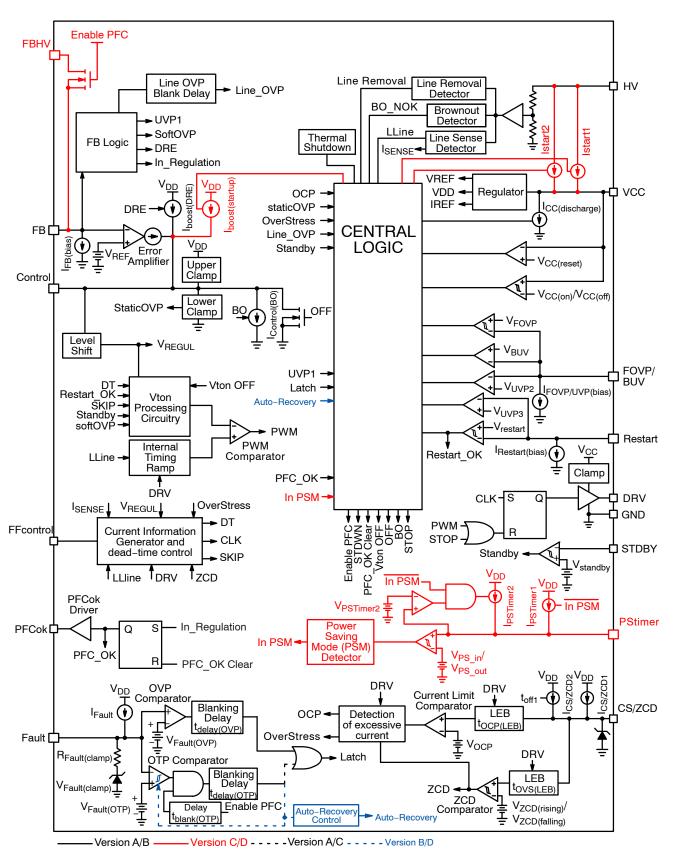

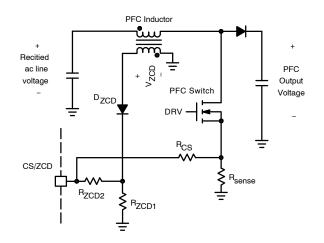

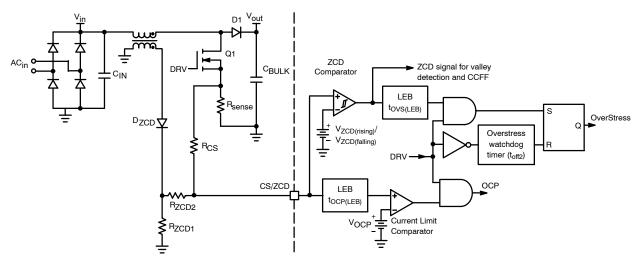

Figure 1. NCP1615C/D Typical Application Circuit

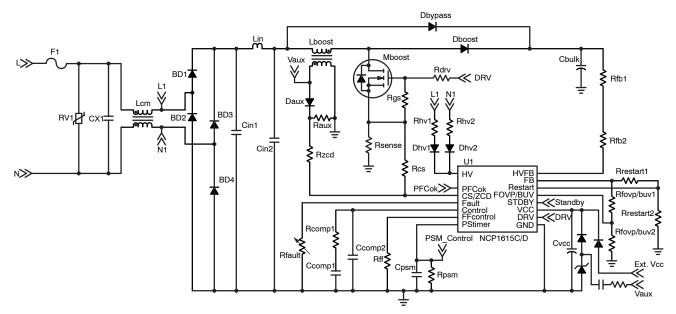

Figure 2. NCP1615A/B Typical Application Circuit

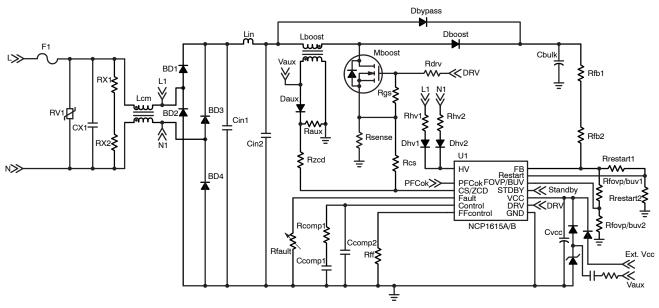

## Table 1. PIN FUNCTION DESCRIPTION

| Pin Nu     | umber      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------------|------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NCP1615C/D | NCP1615A/B | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

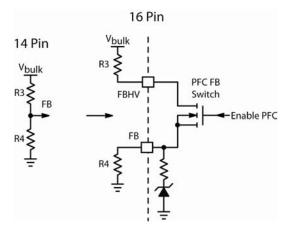

| 1          | N/A        | FBHV      | High voltage PFC feedback input. An external resistor divider is used to sense the PFC bulk voltage. The divider high side resistor chain from the PFC bulk voltage connects to this pin. An internal high–voltage switch disconnects the high side resistor chain from the low side resistor when the PFC is latched or in PSM in order to reduce input power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

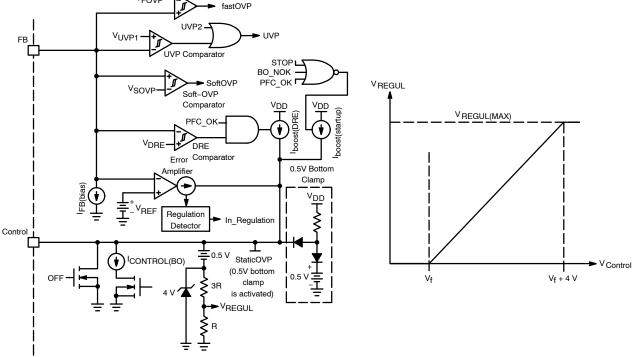

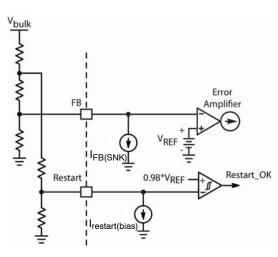

| 2          | 1          | FB        | This pin receives a portion of the PFC output voltage for the regulation and the dynamic response enhancer (DRE) that speeds up the loop response when the output voltage drops below 95.5% of the regulation level. V <sub>FB</sub> is also the input signal for the Soft–Overvoltage Comparators as well as the Undervoltage (UVP) Comparator. The UVP Comparator prevents operation as long as V <sub>FB</sub> is lower than 12% of the reference voltage (V <sub>REF</sub> ). The Soft–Overvoltage Comparator (Soft–OVP) gradually reduces the duty ratio to zero when V <sub>FB</sub> exceeds 105% of V <sub>REF</sub> . A 250 nA sink current is built–in to trigger the UVP protection and disable the part if the feedback pin is accidentally open. A dedicated comparator monitors the bulk voltage and disables the controller if a line overvoltage fault is detected.                                                                                    |  |  |  |  |

| 3          | 2          | Restart   | This pin receives a portion of the PFC output voltage for determining the restart level after entering standby mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 4          | 3          | FOVP/BUV  | Input terminal for the Fast Overvoltage (Fast–OVP) and Bulk Undervoltage (BUV)<br>Comparators. The circuit disables the driver if the $V_{FOVP/BUV}$ exceeds the $V_{FOVP}$<br>threshold which is set 2% higher than the reference for the Soft–OVP comparator<br>monitoring the FB pin. This allows the both pins to receive the same portion of the<br>output voltage. The BUV Comparator trips when $V_{FOVP/BUV}$ falls below 76% of the<br>reference voltage. A BUV fault disables the driver and grounds the PFCOK pin.<br>The BUV function has no action whenever the PFCOK pin is in low state. Once<br>the downstream converter is enabled the BUV Comparator monitors the output<br>voltage to ensure it is high enough for proper operation of the downstream con-<br>verter. A 250 nA current pulls down the pin and disable the controller if the pin is<br>accidentally open.                                                                           |  |  |  |  |

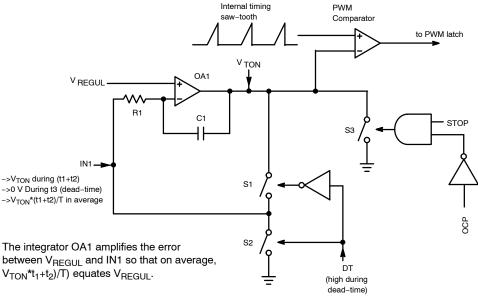

| 5          | 4          | Control   | The error amplifier output is available on this pin. The network connected between this pin and ground sets the regulation loop bandwidth. It is typically set below 20 Hz to achieve high power factor ratios. This pin is grounded when the controller is disabled. The voltage on this pin gradually increases during power up to achieve a soft-start.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

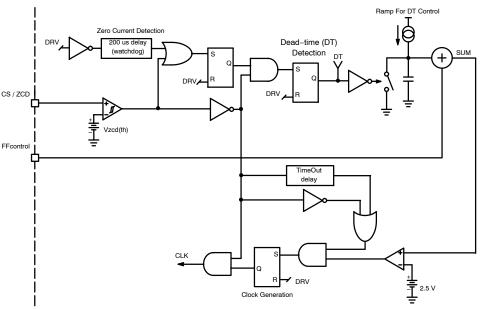

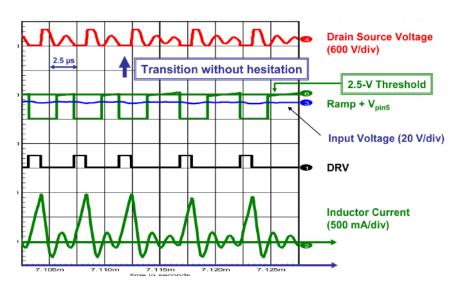

| 6          | 5          | FFcontrol | This pin sources a current representative to the line current. Connect a resistor between this pin and GND to generate a voltage representative of the line current. When this voltage exceeds the internal 2.5 V reference, the circuit operates in critical conduction mode. If the pin voltage is below 2.5 V, a dead-time is generated that approximately equates [83 $\mu$ s • (1 – (V <sub>FFcontrol</sub> /V <sub>REF</sub> ))]. By this means, the circuit increases the deadtime when the current is smaller and decreases the deadtime as the current increases. The circuit skips cycles whenever V <sub>FFcontrol</sub> is below 0.65 V to prevent the PFC stage from operating near the line zero crossing where the power transfer is particularly inefficient. This does result in a slightly increased distortion of the current. If superior power factor is required, offset the voltage on this pin by more than 0.75 V to inhibit skip operation. |  |  |  |  |

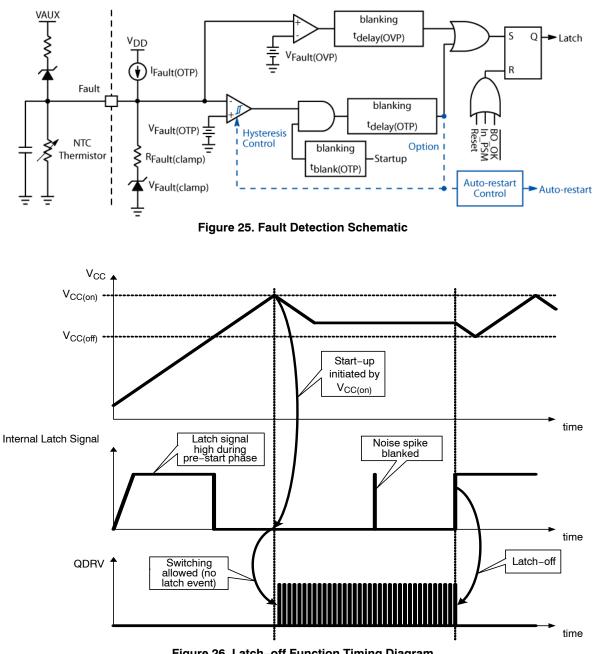

| 7          | 6          | Fault     | The controller enters fault mode if the voltage of this pin is pulled above or below the fault thresholds. A precise pull up current source allows direct interface with an NTC thermistor. Fault detection triggers a latch or auto-recovery depending on device version.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 8          | 7          | STDBY     | This pin is used to force the controller into standby mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

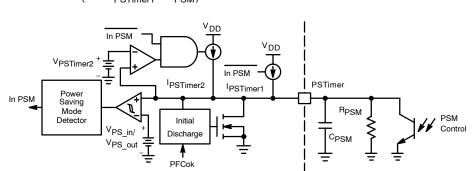

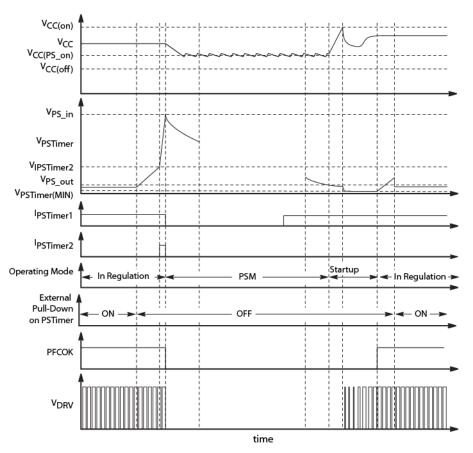

| 9          | N/A        | PSTimer   | Power saving mode (PSM) timer adjust. A capacitor between this pin and GND, $C_{PSTimer}$ , sets the delay time before the controller enters power saving mode. Once the controller enters power saving mode the IC is disabled and the current consumption is reduced to a maximum of 100 $\mu$ A. The input filter capacitor discharge function is available while in power saving mode. The device enters PSM if the voltage on this pin exceeds the PSM threshold, $V_{PS\_in}$ . A secondary side controller optocoupler pulls down on the pin to prevent the controller from entering PSM when the load is connected to the power supply. The controller is enabled once $V_{PSTimer}$ drops below $V_{PS\_out}$ .                                                                                                                                                                                                                                              |  |  |  |  |

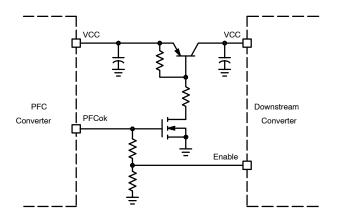

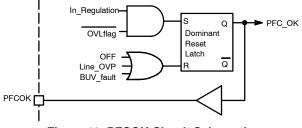

| 10         | 8          | PFCOK     | This pin is grounded until the PFC output has reached its nominal level. It is also grounded if the controller detects a fault. The voltage on this pin is 5 V once the controller reaches regulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

## Table 1. PIN FUNCTION DESCRIPTION

| Pin N      | umber      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NCP1615C/D | NCP1615A/B | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

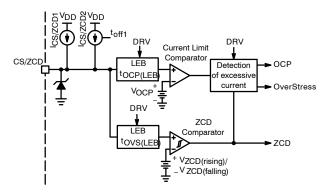

| 11         | 9          | CS/ZCD | This pin monitors the MOSFET current to limit its maximum current. This pin is also connected to an internal comparator for zero current detection (ZCD). This comparator is designed to monitor a signal from an auxiliary winding and to detect the core reset when this voltage drops to zero. The auxiliary winding voltage is to be applied through a diode to avoid altering the current sense information for the on time (see application schematic). |

| 12         | 10         | GND    | Ground reference.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 13         | 11         | DRV    | MOSFET driver. The high current capability of the totem pole gate drive (-0.5/<br>+0.8 A) makes it suitable to effectively drive high gate charge power MOSFETs.                                                                                                                                                                                                                                                                                              |

| 14         | 12         | VCC    | Supply input. This pin is the positive supply of the IC. The circuit starts to operate when $V_{CC}$ exceeds $V_{CC(on)}$ . After start–up, the operating range is 9.5 V up to 28 V.                                                                                                                                                                                                                                                                          |

| 15         | 13         |        | Removed for creepage distance.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16         | 14         | HV     | This pin is the input for the line removal detection, line level detection, and brownout detection circuits. For versions C and D, this pin is also the input for the high voltage start-up circuit.                                                                                                                                                                                                                                                          |

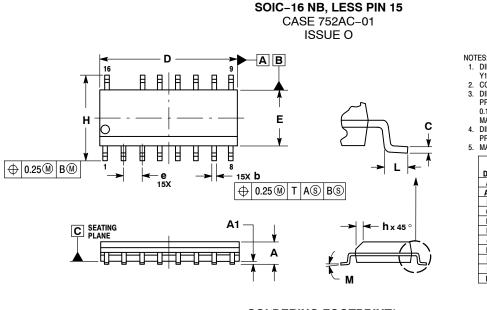

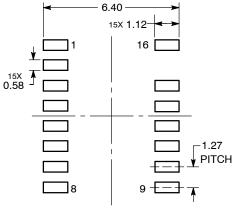

#### **Table 2. ORDERING INFORMATION**

| Part Number   | Device<br>Marking | v <sub>cc</sub> | HV<br>Start–Up | OTP Fault     | PSM | X2<br>Discharge | Brownout | Package             | Shipping <sup>†</sup> |

|---------------|-------------------|-----------------|----------------|---------------|-----|-----------------|----------|---------------------|-----------------------|

| NCP1615ADR2G  | NCP1615A          | 10.5 V          | No             | Latch         | No  | No              | 100 Vdc  | SOIC-14<br>NB, LESS | 3000 /<br>Tape & Reel |

| NCP1615BDR2G  | NCP1615B          | 10.5 V          | No             | Auto-Recovery | No  | No              | 100 Vdc  | PIN 13<br>(Pb-Free) |                       |

| NCP1615CDR2G  | NCP1615C          | 17 V            | Yes            | Latch         | Yes | Yes             | 100 Vdc  | SOIC-16             | 3000 /                |

| NCP1615C2DR2G | NCP1615C2         | 17 V            | Yes            | Latch         | Yes | Yes             | 87 Vdc   | NB, LESS<br>PIN 15  | Tape & Reel           |

| NCP1615DDR2G  | NCP1615D          | 17 V            | Yes            | Auto-Recovery | Yes | Yes             | 100 Vdc  | (Pb-Free)           |                       |

| NCP1615D2DR2G | NCP1615D2         | 17 V            | Yes            | Auto-Recovery | Yes | Yes             | 87 Vdc   |                     |                       |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

### Table 3. MAXIMUM RATINGS (Notes 3 and 4)

| Rating                                                                                                                                                                                 | Pin        | Symbol                                         | Value                             | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------|-----------------------------------|------|

| High Voltage Start-Up Circuit Input Voltage                                                                                                                                            | HV         | V <sub>HV</sub>                                | -0.3 to 700                       | V    |

| High Voltage Feedback Input Voltage                                                                                                                                                    | FBHV       | V <sub>FBHV</sub>                              | -0.3 to 700                       | V    |

| High Voltage Feedback Input Current                                                                                                                                                    | FBHV       | I <sub>FBHV</sub>                              | 0.5                               | mA   |

| Zero Current Detection and Current Sense Input Voltage (Note 5)                                                                                                                        | CS/ZCD     | V <sub>CS/ZCD</sub>                            | -0.3 to V <sub>CS/ZCD(MAX)</sub>  | V    |

| Zero Current Detection and Current Sense Input Current                                                                                                                                 | CS/ZCD     | I <sub>CS/ZCD</sub>                            | +5                                | mA   |

| Control Input Voltage (Note 6)                                                                                                                                                         | Control    | V <sub>Control</sub>                           | -0.3 to V <sub>Control(MAX)</sub> | V    |

| Supply Input Voltage                                                                                                                                                                   | VCC        | V <sub>CC(MAX)</sub>                           | -0.3 to 28                        | V    |

| Fault Input Voltage                                                                                                                                                                    | Fault      | V <sub>Fault</sub>                             | –0.3 to (V <sub>CC</sub> + 0.6)   | V    |

| PSTimer Input Voltage                                                                                                                                                                  | PSTimer    | V <sub>PSTimer</sub>                           | –0.3 to (V <sub>CC</sub> + 0.6)   | V    |

| Driver Maximum Voltage (Note 7)                                                                                                                                                        | DRV        | V <sub>DRV</sub>                               | –0.3 to V <sub>DRV</sub>          | V    |

| Driver Maximum Current                                                                                                                                                                 | DRV        | I <sub>DRV(SRC)</sub><br>I <sub>DRV(SNK)</sub> | 500<br>800                        | mA   |

| Maximum Input Voltage (Note 8)                                                                                                                                                         | Other Pins | V <sub>MAX</sub>                               | –0.3 to 7                         | V    |

| Maximum Operating Junction Temperature                                                                                                                                                 |            | TJ                                             | -40 to 150                        | °C   |

| Storage Temperature Range                                                                                                                                                              |            | T <sub>STG</sub>                               | -60 to 150                        | °C   |

| Lead Temperature (Soldering, 10 s)                                                                                                                                                     |            | T <sub>L(MAX)</sub>                            | 300                               | °C   |

| Moisture Sensitivity Level                                                                                                                                                             |            | MSL                                            | 1                                 | -    |

| Power Dissipation (T <sub>A</sub> = 70°C, 1 Oz Cu, 0.155 Sq Inch Printed Circuit<br>Copper Clad)<br>Plastic Package SOIC-14NB/SOIC-16NB                                                |            | P <sub>D</sub>                                 | 465                               | mW   |

| Thermal Resistance, Junction to Ambient 1 Oz Cu Printed Circuit<br>Copper Clad)<br>Plastic Package SOIC-14NB/SOIC-16NB                                                                 |            | $R_{	heta JA} \ R_{	heta JC}$                  | 172<br>68                         | °C/W |

| ESD Capability (Note 9)<br>Human Body Model per JEDEC Standard JESD22-A114E.<br>Machine Model per JEDEC Standard JESD22-A114E.<br>Charge Device Model per JEDEC Standard JESD22-C101E. |            |                                                | > 2000<br>> 200<br>> 500          | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. All references to Version C include Versions C/C2, unless otherwise noted.

2. All references to Version D include Versions D/D2, unless otherwise noted.

3. This device contains Latch–Up protection and exceeds  $\pm$  100 mA per JEDEC Standard JESD78.

4. Low Conductivity Board. As mounted on 80 x 100 x 1.5 mm FR4 substrate with a single layer of 50 mm<sup>2</sup> of 2 oz copper traces and heat Low Conductivity Board. As mounted on 80 x 100 x 1.5 mm FR4 substrate with a single layer of 50 mm<sup>2</sup> of 2 oz copper traces and neat spreading area. As specified for a JEDEC51–1 conductivity test PCB. Test conditions were under natural convection of zero air flow.

V<sub>CS/ZCD(MAX)</sub> is the CS/ZCD pin positive clamp voltage.

V<sub>Control(MAX)</sub> is the Control pin positive clamp voltage.

V<sub>Control(MAX)</sub> is the Control pin positive clamp voltage.

When V<sub>CC</sub> exceeds the driver clamp voltage (V<sub>DRV(high</sub>)), V<sub>DRV</sub> is equal to V<sub>DRV(high</sub>). Otherwise, V<sub>DRV</sub> is equal to V<sub>CC</sub>.

When the voltage applied to these pins exceeds 5.5 V, they sink a current about equal to (V<sub>pin</sub> – 5.5 V) / (4 kΩ). An applied voltage of 7 V geoperators a sink current of approximately 0.937 s mÅ.

generates a sink current of approximately 0.375 mA.

Pins HV, PFBHV are rated to the maximum voltage of the part, or 700 V.

| <b>Table 4. ELECTRICAL CHARACTERISTICS</b> (V <sub>CC</sub> = 15 V, V <sub>HV</sub> = 120 V, V <sub>FB</sub> = 2.4 V, R <sub>HVFB</sub> = 200 kΩ, V <sub>HVFB</sub> = 20 V, C <sub>VControl</sub> =                                     |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10 nF, V <sub>FFcontrol</sub> = 2.6 V, V <sub>ZCD/CS</sub> = 0 V, R <sub>ZCD/CS</sub> = 3 kΩ, V <sub>FOVPBUV</sub> = 2.4 V, V <sub>STDBY</sub> = 1 V, V <sub>Restart</sub> = 1 V, V <sub>PSTimer</sub> = 0 V, V <sub>Fault</sub> = open |  |

| V <sub>PFCOK</sub> = open, C <sub>DRV</sub> = 1 nF, for typical values T <sub>J</sub> = 25°C, for min/max values, T <sub>J</sub> is -40°C to 125°C, unless otherwise noted)                                                             |  |

| Characteristics                                                                                                                                     | Conditions                                                                                                                                                                                                              | Symbol                                                                                                                | Min                   | Тур                         | Max                             | Uni |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------|---------------------------------|-----|

| START-UP AND SUPPLY CIRCUITS                                                                                                                        |                                                                                                                                                                                                                         |                                                                                                                       | -                     |                             |                                 |     |

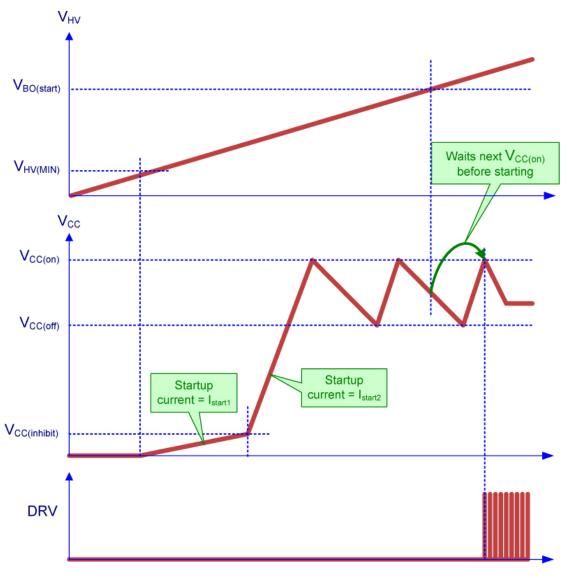

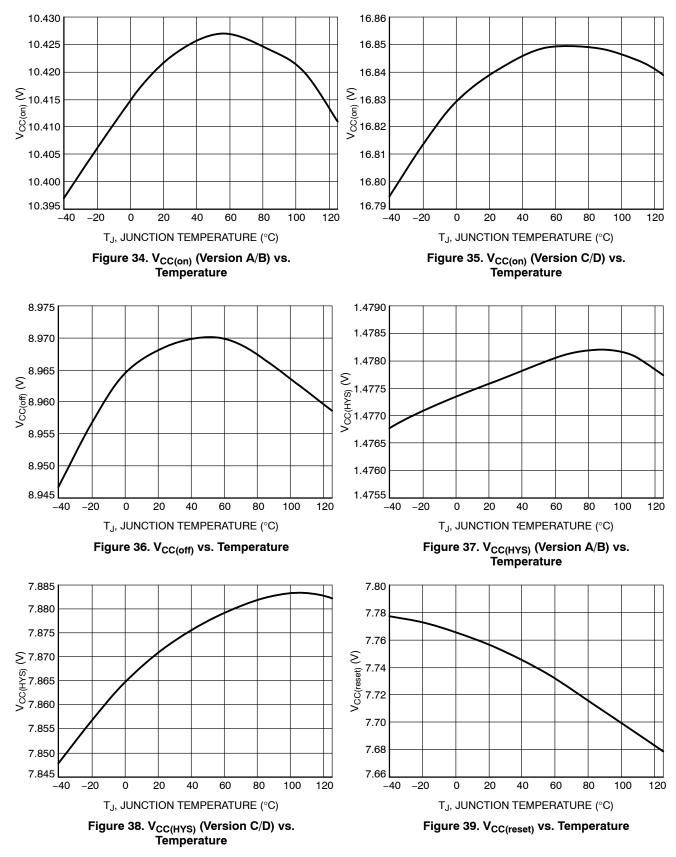

| Start–Up Threshold<br>A/B Version<br>C/D Version                                                                                                    | V <sub>CC</sub> increasing                                                                                                                                                                                              | V <sub>CC(on)</sub>                                                                                                   | 9.75<br>16.0          | 10.50<br>17.0               | 11.25<br>18.0                   | V   |

| Minimum Operating Voltage                                                                                                                           | V <sub>CC</sub> decreasing                                                                                                                                                                                              | V <sub>CC(off)</sub>                                                                                                  | 8.5                   | 9.0                         | 9.5                             | V   |

| V <sub>CC</sub> Hysteresis<br>A/B Version<br>C/D Version                                                                                            | V <sub>CC(on)</sub> – V <sub>CC(off)</sub>                                                                                                                                                                              | V <sub>CC(HYS)</sub>                                                                                                  | 1.0<br>7.0            | 1.5<br>8.0                  |                                 | V   |

| Internal Latch / Logic Reset Level                                                                                                                  | V <sub>CC</sub> decreasing                                                                                                                                                                                              | V <sub>CC(reset)</sub>                                                                                                | 7.3                   | 7.8                         | 8.3                             | V   |

| Difference Between $V_{CC(off)}$ and $V_{CC(reset)}$                                                                                                | V <sub>CC(off)</sub> - V <sub>CC(reset)</sub>                                                                                                                                                                           | $\Delta V_{CC(reset)}$                                                                                                | 0.5                   | -                           | -                               | V   |

| Regulation Level in Power Saving Mode                                                                                                               | Version C/D                                                                                                                                                                                                             | V <sub>CC(PS_on)</sub>                                                                                                | -                     | 11                          | -                               | V   |

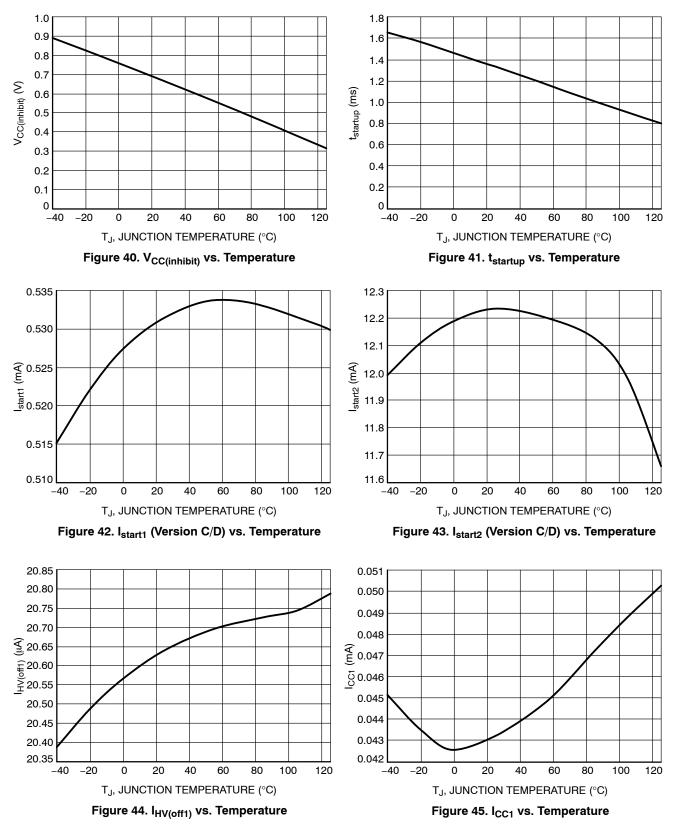

| Transition from I <sub>start1</sub> to I <sub>start2</sub><br>(C/D Version)                                                                         | $V_{CC}$ increasing, $I_{HV}$ = 650 $\mu$ A                                                                                                                                                                             | V <sub>CC(inhibit)</sub>                                                                                              | -                     | 0.8                         | -                               | V   |

| Start-Up Time (C/D Version)                                                                                                                         | $\begin{array}{c} C_{VCC} = 0.47 \ \mu\text{F}, \\ V_{CC} = 0 \ V \ \text{to} \ V_{CC(\text{on})} \end{array}$                                                                                                          | t <sub>start-up</sub>                                                                                                 | —                     | _                           | 2.5                             | m   |

| Inhibit Current Sourced from V <sub>CC</sub> Pin<br>(C/D Version)                                                                                   | V <sub>CC</sub> = 0 V, V <sub>HV</sub> = 100 V                                                                                                                                                                          | I <sub>start1</sub>                                                                                                   | 0.375                 | 0.5                         | 0.87                            | m   |

| Start–Up Current Sourced from V <sub>CC</sub> Pin<br>(C/D Version)                                                                                  | $V_{CC} = V_{CC(on)} - 0.5 V,$<br>$V_{HV} = 100 V$                                                                                                                                                                      | I <sub>start2</sub>                                                                                                   | 6.5                   | 12                          | 16.5                            | m   |

| Start-Up Circuit Off-State Leakage Current                                                                                                          | V <sub>HV</sub> = 400 V<br>V <sub>HV</sub> = 700 V                                                                                                                                                                      | I <sub>HV(off1)</sub><br>I <sub>HV(off2)</sub>                                                                        | _                     | -                           | 30<br>50                        | μ   |

| Minimum Voltage for Start–Up Circuit<br>Start–Up (C/D Version)<br>During PSM (C/D Version)                                                          | $I_{start2} = 6.5 \text{ mA}, \\ V_{CC} = V_{CC(on)} - 0.5 \text{ V} \\ I_{start2} = 6.5 \text{ mA}, V_{CC} = \\ V_{CC(PS on)} - 0.5 \text{ V}$                                                                         | V <sub>HV(MIN)</sub><br>V <sub>HV(MIN_</sub> PSM)                                                                     | _                     | _                           | 38<br>30                        | V   |

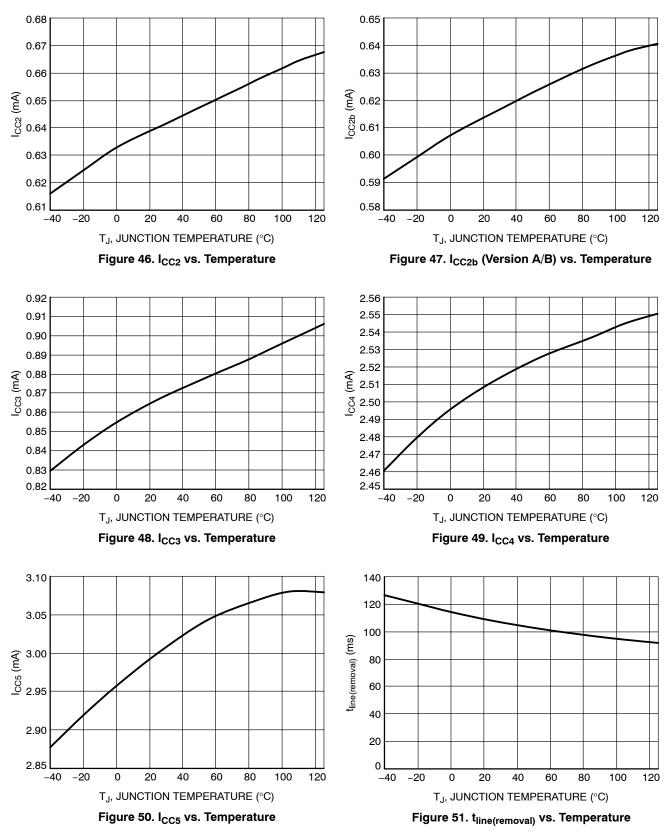

| Supply Current<br>In Power Saving Mode (C/D Version)<br>Latch<br>Before Start-Up (A/B Version)<br>Standby Mode<br>No Switching<br>Operating Current | $V_{CC} = V_{CC}(PS_{on})$ $V_{Fault} = 4 V$ $V_{CC} = V_{CC(on)} - 0.5 V$ $V_{standby} = 0 V, V_{Restart} = 3 V$ $V_{FB} = 2.55 V$ $f = 50 \text{ kHz}, C_{DRV} = \text{open},$ $V_{Control} = 2.5 V, V_{FB} = 2.45 V$ | I <sub>CC1</sub><br>I <sub>CC2</sub><br>I <sub>CC2b</sub><br>I <sub>CC3</sub><br>I <sub>CC4</sub><br>I <sub>CC5</sub> | -<br>-<br>-<br>-<br>- | -<br>0.6<br>0.6<br>-<br>2.0 | 0.1<br>1.0<br>1.0<br>2.8<br>3.5 | mA  |

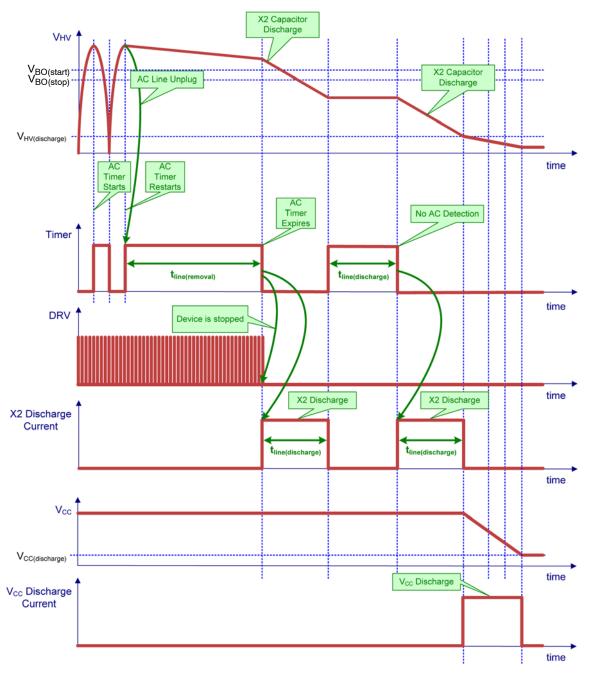

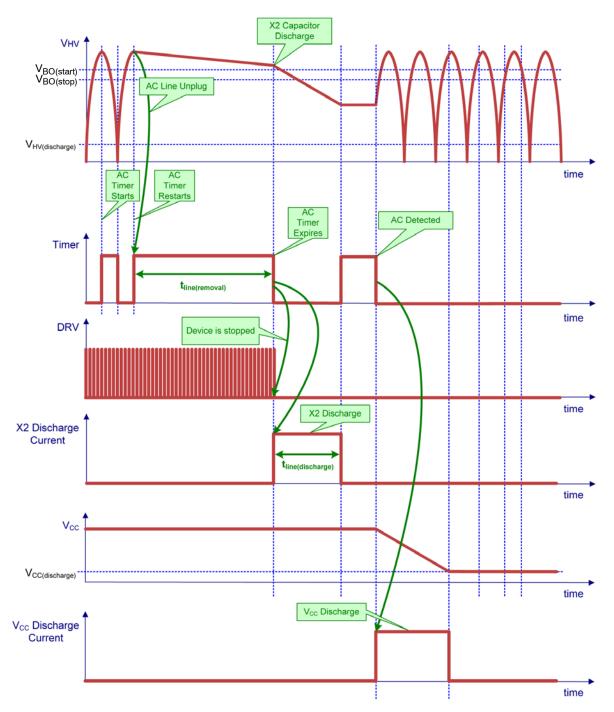

| LINE REMOVAL                                                                                                                                        | •                                                                                                                                                                                                                       | •                                                                                                                     |                       |                             |                                 |     |

| Line Voltage Removal Detection Timer                                                                                                                |                                                                                                                                                                                                                         | t <sub>line(removal)</sub>                                                                                            | 60                    | 100                         | 165                             | m   |

| Discharge Timer Duration                                                                                                                            |                                                                                                                                                                                                                         | t <sub>line(discharge)</sub>                                                                                          | 21                    | 32                          | 60                              | m   |

| Discharge Current (C/D Version)                                                                                                                     | $V_{CC} = V_{CC(off)} + 200 \text{ mV}$ $V_{CC} = V_{CC(discharge)} + 200 \text{ mV}$                                                                                                                                   | I <sub>CC(discharge)</sub>                                                                                            | 20<br>10              | 25<br>16.5                  | 30<br>30                        | m   |

| HV Discharge Level (C/D Version)                                                                                                                    |                                                                                                                                                                                                                         | V <sub>HV(discharge)</sub>                                                                                            | _                     | -                           | 40                              | V   |

| V <sub>CC</sub> Discharge Level (C/D Version)                                                                                                       |                                                                                                                                                                                                                         | V <sub>CC(discharge)</sub>                                                                                            | 3.8                   | 4.5                         | 5.4                             | V   |

| BROWNOUT DETECTION                                                                                                                                  | •                                                                                                                                                                                                                       |                                                                                                                       |                       |                             |                                 |     |

| System Start-Up Threshold<br>A/B/C/D Version                                                                                                        | V <sub>HV</sub> increasing                                                                                                                                                                                              | V <sub>BO(start)</sub>                                                                                                | 102                   | 111                         | 118                             | V   |

| A/B/C/D Version<br>C2/D2 Version                              | V <sub>HV</sub> increasing | VBO(start)            | 102<br>86 | 111<br>95 | 118<br>102 | v |

|---------------------------------------------------------------|----------------------------|-----------------------|-----------|-----------|------------|---|

| System Shutdown Threshold<br>A/B/C/D Version<br>C2/D2 Version | V <sub>HV</sub> decreasing | V <sub>BO(stop)</sub> | 92<br>78  | 100<br>87 | 108<br>94  | V |

| Characteristics                                                       | Conditions                                                                                                         | Symbol                                           | Min         | Тур          | Max          | Unit |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------|--------------|--------------|------|

| BROWNOUT DETECTION                                                    |                                                                                                                    |                                                  |             |              |              |      |

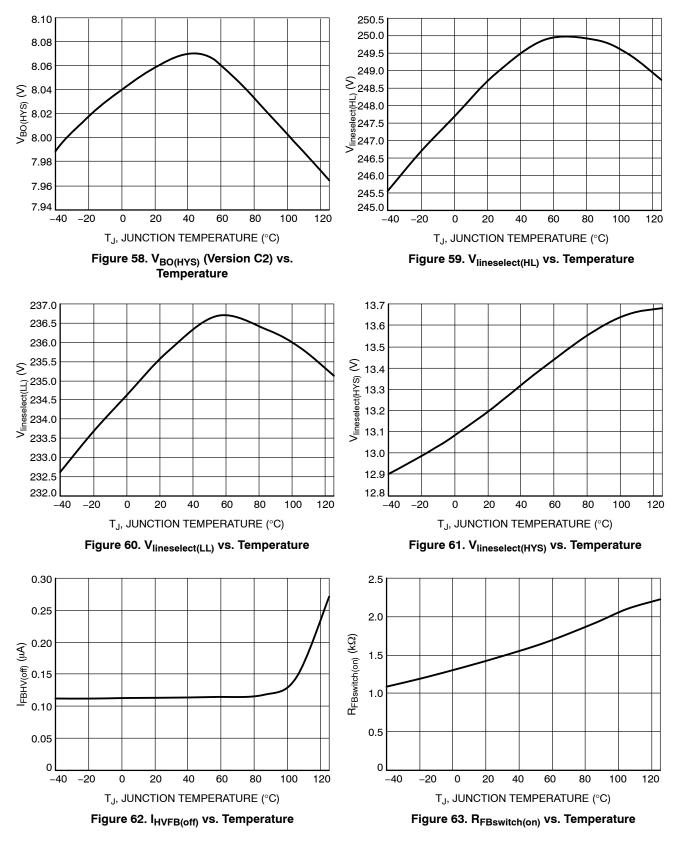

| Hysteresis<br>A/B/C/D Version<br>C2/D2 Version                        | V <sub>HV</sub> increasing                                                                                         | V <sub>BO(HYS)</sub>                             | 7<br>5      | 11<br>8      |              | V    |

| Brownout Detection Blanking Time                                      | V <sub>HV</sub> decreasing, delay from<br>V <sub>BO(stop)</sub> to drive disable                                   | t <sub>BO(stop)</sub>                            | 43          | 54           | 65           | ms   |

| Control Pin Sink Current in Brownout                                  | t <sub>BO(stop)</sub> expires                                                                                      | I <sub>Control(BO)</sub>                         | 40          | 50           | 60           | μA   |

| LINE DETECTION                                                        |                                                                                                                    |                                                  |             |              |              |      |

| High Line Level Detection Threshold                                   | V <sub>HV</sub> increasing                                                                                         | V <sub>lineselect(HL)</sub>                      | 232         | 250          | 267          | V    |

| Low Line Level Detection Threshold                                    | V <sub>HV</sub> decreasing                                                                                         | V <sub>lineselect(LL)</sub>                      | 220         | 236          | 252          | V    |

| Line Select Hysteresis                                                | V <sub>HV</sub> increasing                                                                                         | V <sub>lineselect(HYS)</sub>                     | 10          | -            | -            | V    |

| High to Low Line Mode Selector Timer                                  | V <sub>HV</sub> decreasing                                                                                         | t <sub>line</sub>                                | 43          | 54           | 65           | ms   |

| Low to High Line Mode Selector Timer                                  | V <sub>HV</sub> increasing                                                                                         | t <sub>delay(line)</sub>                         | 200         | 300          | 400          | μs   |

| Line Valley Lockout Counter                                           | After t <sub>high to low line</sub> expires                                                                        | n <sub>LL</sub>                                  | -           | 8            | -            |      |

| POWER SAVING MODE (C/D VERSION)                                       |                                                                                                                    |                                                  |             |              |              |      |

| PSM Enable Threshold                                                  | V <sub>PSTimer</sub> increasing                                                                                    | V <sub>PS_in</sub>                               | 3.325       | 3.500        | 3.675        | V    |

| PSM Disable Threshold                                                 | V <sub>PSTimer</sub> decreasing                                                                                    | V <sub>PS_out</sub>                              | 0.45        | 0.50         | 0.55         | V    |

| PSTimer Pull Up Current Source                                        | V <sub>PSTimer</sub> = 0.9 V                                                                                       | I <sub>PSTimer1</sub>                            | 4.5         | 5.9          | 7.3          | μA   |

| PSTimer Fast Pull Up Current Source                                   | V <sub>PSTimer</sub> = 3.4 V                                                                                       | I <sub>PSTimer2</sub>                            | 800         | 1000         | 1200         | μA   |

| PSTimer Leakage Current                                               | V <sub>PSTimer</sub> = 4 V                                                                                         | I <sub>PSTimer(bias)</sub>                       | -           | -            | 100          | nA   |

| I <sub>PSTimer2</sub> Enable Threshold                                |                                                                                                                    | V <sub>PSTimer2</sub>                            | 0.95        | 1.00         | 1.05         | V    |

| Filter Delay Before Entering PSM                                      | V <sub>PSTimer</sub> > V <sub>PS_in</sub>                                                                          | t <sub>delay(PS_in)</sub>                        | -           | 40           | -            | μs   |

| Detection Delay Before Exiting PSM and<br>Turning On Start-Up Circuit | V <sub>PSTimer</sub> < V <sub>PS_out</sub>                                                                         | t <sub>delay(PS_out)</sub>                       | _           | -            | 100          | μs   |

| PSTimer Discharge Current                                             | V <sub>PSTimer</sub> = V <sub>PSTimer(off)</sub> + 10 mV                                                           | I <sub>PSTimer(DIS)</sub>                        | 160         | -            | -            | μA   |

| PSTimer Discharge Turn Off Threshold                                  | V <sub>PSTimer</sub> decreasing                                                                                    | V <sub>PSTimer(off)</sub>                        | 0.05        | 0.10         | 0.15         | V    |

| PFC FB SWITCH (C/D VERSION)                                           |                                                                                                                    |                                                  |             |              |              |      |

| PFC Off-State Leakage Current                                         | V <sub>PSTimer</sub> = 4 V, V <sub>HVFB</sub> = 500 V                                                              | I <sub>HVFB(off)</sub>                           | -           | 0.1          | 3            | μA   |

| PFC Feedback Switch On Resistance                                     | V <sub>HVFB</sub> = 2.75 V, I <sub>HVFB</sub> = 100 μA                                                             | R <sub>FBswitch(on)</sub>                        | -           | -            | 10           | kΩ   |

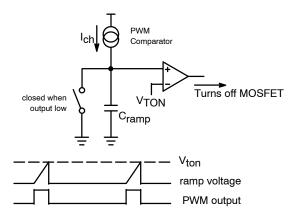

| ON-TIME CONTROL                                                       |                                                                                                                    |                                                  |             |              |              |      |

| PFC Maximum On Time                                                   | $V_{HV} = 162.5 \text{ V}, V_{Control} = V_{Control}(MAX)$ $V_{HV} = 162.5 \text{ V}, V_{Control} = 2.5 \text{ V}$ | t <sub>on(LL)</sub><br>t <sub>on(LL)2</sub>      | 20.5<br>9.5 | 23.7<br>11.0 | 27.5<br>13.0 | μs   |

|                                                                       | V <sub>HV</sub> = 325 V, V <sub>Control</sub> =<br>V <sub>Control(MAX)</sub>                                       | t <sub>on(HL)</sub>                              | 5.2         | 6.0          | 7.0          |      |

| Minimum On-Time                                                       | V <sub>HV</sub> = 162 V<br>V <sub>HV</sub> = 325 V                                                                 | t <sub>onLL(MIN)</sub><br>t <sub>onHL(MIN)</sub> | -           |              | 200<br>100   | ns   |

| CURRENT SENSE                                                         |                                                                                                                    |                                                  |             |              |              |      |

| Current Limit Threshold                                               |                                                                                                                    | V <sub>ILIM</sub>                                | 0.46        | 0.50         | 0.54         | V    |

| Leading Edge Blanking Duration                                        |                                                                                                                    | t <sub>OCP(LEB)</sub>                            | 100         | 200          | 350          | ns   |

| Current Limit Propagation Delay                                       | Step V <sub>CS/ZCD</sub> > V <sub>ILIM</sub> to DRV<br>falling edge                                                | t <sub>OCP(delay)</sub>                          | -           | 40           | 200          | ns   |

| Overstress Leading Edge Blanking Duration                             |                                                                                                                    | t <sub>OVS(LEB)</sub>                            | 50          | 100          | 170          | ns   |

| Characteristics                                                 | Conditions                                                                                                   | Symbol                                                   | Min          | Тур          | Max          | Unit |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|--------------|--------------|------|

| CURRENT SENSE                                                   |                                                                                                              |                                                          |              |              |              |      |

| Over Stress Detection Propagation Delay                         | V <sub>CS/ZCD</sub> > V <sub>ZCD(rising)</sub> to DRV<br>falling edge                                        | t <sub>OVS(delay)</sub>                                  | —            | 40           | 200          | ns   |

| REGULATION BLOCK                                                |                                                                                                              |                                                          |              | -            | -            |      |

| Reference Voltage                                               | $T_J = 25^{\circ}C$<br>$T_J = -40$ to $125^{\circ}C$                                                         | V <sub>REF</sub><br>V <sub>REF</sub>                     | 2.45<br>2.44 | 2.50<br>2.50 | 2.55<br>2.56 | V    |

| Error Amplifier Current Source Sink                             |                                                                                                              | I <sub>EA(SRC)</sub><br>I <sub>EA(SNK)</sub>             | 16<br>16     | 20<br>20     | 24<br>24     | μA   |

| Open Loop Error Amplifier Transconductance                      | $V_{FB} = V_{REF} + /-100 \text{ mV}$                                                                        | 9 <sub>m</sub>                                           | 180          | 210          | 245          | μS   |

| Maximum Control Voltage                                         | V <sub>FB</sub> = 2 V                                                                                        | V <sub>Control(MAX)</sub>                                | -            | 4.5          | -            | V    |

| Minimum Control Voltage                                         | V <sub>FB</sub> = 2.6 V                                                                                      | V <sub>Control(MIN)</sub>                                | -            | 0.5          | -            | V    |

| EA Output Control Voltage Range                                 | V <sub>Control(MAX)</sub> – V <sub>Control(MIN)</sub>                                                        | $\Delta V_{Control}$                                     | 3.9          | 4.0          | 4.1          | V    |

| DRE Detect Threshold                                            | V <sub>FB</sub> decreasing                                                                                   | V <sub>DRE</sub>                                         | -            | 2.388        | -            | V    |

| DRE Threshold Hysteresis                                        | V <sub>FB</sub> increasing                                                                                   | V <sub>DRE(HYS)</sub>                                    | -            | -            | 25           | mV   |

| Ratio between the DRE Detect Threshold and the Regulation Level | $V_{FB}$ decreasing, $V_{DRE}/V_{REF}$                                                                       | K <sub>DRE</sub>                                         | 95.0         | 95.5         | 96.0         | %    |

| Control Pin Source Current During Start–Up<br>(C/D Version)     | PFCOK = Low, V <sub>VControl</sub> = 2 V                                                                     | I <sub>Control(start-up)</sub>                           | 80           | 100          | 113          | μA   |

| EA Boost Current During Start-Up<br>(C/D Version)               |                                                                                                              | I <sub>boost(start-up)</sub>                             | —            | 80           | -            | μA   |

| Control Pin Source Current During DRE                           | V <sub>VControl</sub> = 2 V                                                                                  | I <sub>Control(DRE)</sub>                                | 180          | 220          | 250          | μA   |

| EA Boost Current During DRE                                     |                                                                                                              | I <sub>boost(DRE)</sub>                                  | -            | 200          | -            | μA   |

| PFC GATE DRIVE                                                  |                                                                                                              |                                                          |              |              | -            |      |

| Rise Time (10–90%)                                              | $V_{DRV}$ from 10 to 90% of $V_{DRV}$                                                                        | t <sub>DRV(rise)</sub>                                   | _            | 40           | 80           | ns   |

| Fall Time (90–10%)                                              | 90 to 10% of $V_{\mbox{DRV}}$                                                                                | t <sub>DRV(fall)</sub>                                   | -            | 20           | 60           | ns   |

| Source Current Capability                                       | V <sub>DRV</sub> = 0 V                                                                                       | I <sub>DRV(SRC)</sub>                                    | _            | 500          | -            | mA   |

| Sink Current Capability                                         | V <sub>DRV</sub> = 12 V                                                                                      | I <sub>DRV(SNK)</sub>                                    | -            | 800          | -            | mA   |

| High State Voltage                                              | $\label{eq:V_CC} \begin{split} V_{CC} &= V_{CC(off)} + 0.2 \text{ V}, \\ R_{DRV} &= 10  k\Omega \end{split}$ | V <sub>DRV(high1)</sub>                                  | 8            | -            | -            | V    |

|                                                                 | $V_{CC}$ = 28 V, $R_{DRV}$ = 10 k $\Omega$                                                                   | V <sub>DRV(high2)</sub>                                  | 10           | 12           | 14           |      |

| Low Stage Voltage                                               | V <sub>STDBY</sub> = 0 V                                                                                     | V <sub>DRV(low)</sub>                                    | -            | -            | 0.25         | V    |

| ZERO CURRENT DETECTION                                          |                                                                                                              |                                                          |              |              |              |      |

| Zero Current Detection Threshold                                | $V_{CS/ZCD}$ rising $V_{CS/ZCD}$ falling                                                                     | V <sub>ZCD(rising)</sub><br>V <sub>ZCD(falling)</sub>    | 675<br>200   | 750<br>250   | 825<br>300   | mV   |

| ZCD and Current Sense Ratio                                     | V <sub>ZCD(rising)</sub> /V <sub>ILIM</sub>                                                                  | K <sub>ZCD/ILIM</sub>                                    | 1.4          | 1.5          | 1.6          | -    |

| Positive Clamp Voltage                                          | $I_{CS/ZCD} = 0.75 \text{ mA}$<br>$I_{CS/ZCD} = 5 \text{ mA}$                                                | V <sub>CS/ZCD(MAX1)</sub><br>V <sub>CS/ZCD(MAX2)</sub>   | 7.1<br>15.4  | 7.4<br>15.8  | 7.8<br>16.1  | V    |

| CS/ZCD Input Bias Current                                       | $V_{CS/ZCD} = V_{ZCD(rising)}$<br>$V_{CS/ZCD} = V_{ZCD(falling)}$                                            | I <sub>CS/ZCD(bias1)</sub><br>I <sub>CS/ZCD(bias2)</sub> | 0.5<br>0.5   |              | 2.0<br>2.0   | μΑ   |

| ZCD Propagation Delay                                           | Measured from V <sub>CS/ZCD</sub> =<br>V <sub>ZCD(falling)</sub> to DRV rising                               | tzcD                                                     | _            | 60           | 200          | ns   |

| Minimum detectable ZCD Pulse Width                              | Measured from V <sub>ZCD(rising)</sub> to<br>V <sub>ZCD(falling)</sub>                                       | tsync                                                    | _            | 110          | 200          | ns   |

| Maximum Off-Time (Watchdog Timer)                               | V <sub>CS/ZCD</sub> > V <sub>ZCD(rising)</sub>                                                               | t <sub>off1</sub><br>t <sub>off2</sub>                   | 80<br>700    | 200<br>1000  | 320<br>1300  | μs   |

| Table 4. ELECTRICAL CHARACTERISTICS (V <sub>CC</sub> = 15 V, V <sub>HV</sub> = 120 V, V <sub>FB</sub> = 2.4 V, R <sub>HVFB</sub> = 200 kΩ, V <sub>HVFB</sub> = 20 V, C <sub>VControl</sub> =                                            | =  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 10 nF, V <sub>FFcontrol</sub> = 2.6 V, V <sub>ZCD/CS</sub> = 0 V, R <sub>ZCD/CS</sub> = 3 kΩ, V <sub>FOVPBUV</sub> = 2.4 V, V <sub>STDBY</sub> = 1 V, V <sub>Restart</sub> = 1 V, V <sub>PSTimer</sub> = 0 V, V <sub>Fault</sub> = oper | n, |

| V <sub>PFCOK</sub> = open, C <sub>DRV</sub> = 1 nF, for typical values T <sub>J</sub> = 25°C, for min/max values, T <sub>J</sub> is –40°C to 125°C, unless otherwise noted)                                                             |    |

| Characteristics                                      | Conditions                                                                                                       | Symbol                                                   | Min            | Тур            | Max            | Unit |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------|----------------|----------------|------|

| ZERO CURRENT DETECTION                               | -                                                                                                                | <u> </u>                                                 |                | -              |                | •    |

| Missing Valley Timeout Timer                         | Measured after last ZCD transition                                                                               | t <sub>tout</sub>                                        | 20             | 30             | 50             | μs   |

| Pull–Up Current Source                               | Detects open pin fault.                                                                                          | I <sub>CS/ZCD1</sub>                                     | _              | 1              | -              | μA   |

| Source Current for CS/ZCD Impedance Testing          | Pulls up at the end of t <sub>off1</sub>                                                                         | I <sub>CS/ZCD2</sub>                                     | -              | 250            | -              | μΑ   |

| CURRENT CONTROLLED FREQUENCY FOLD                    | BACK                                                                                                             |                                                          |                |                |                |      |

| Dead Time                                            | $V_{FFCntrol} = 2.6 V$<br>$V_{FFCntrol} = 1.75 V$<br>$V_{FFCntrol} = 1.0 V$                                      | t <sub>DT1</sub><br>t <sub>DT2</sub><br>t <sub>DT3</sub> | _<br>4.5<br>11 | -<br>6.5<br>13 | 0<br>7.5<br>15 | μs   |

| FFcontrol Pin Current                                | $      V_{HV} = 162.5V, V_{Control} = V_{Control(MAX)} \\       V_{HV} = 325 V, V_{Control} = V_{Control(MAX)} $ | I <sub>DT1</sub><br>I <sub>DT2</sub>                     | 180<br>92      | 200<br>103     | 220<br>114     | μA   |

| FFcontrol Skip Level                                 | V <sub>FFCntrol</sub> = increasing<br>V <sub>FFCntrol</sub> = decreasing                                         | V <sub>skip(out)</sub><br>V <sub>skip(in)</sub>          | _<br>0.55      | 0.75<br>0.65   | 0.85<br>_      | V    |

| FFcontrol Skip Hysteresis                            |                                                                                                                  | V <sub>SKIP(HYS)</sub>                                   | 50             | -              | -              | mV   |

| Minimum Operating Frequency                          |                                                                                                                  | f <sub>MIN</sub>                                         | -              | 26             | -              | kHz  |

| FEEDBACK OVER AND UNDERVOLTAGE PR                    | OTECTION                                                                                                         |                                                          |                | -              |                |      |

| Soft-OVP to V <sub>REF</sub> Ratio                   | V <sub>FB</sub> = increasing, V <sub>SOVP</sub> /V <sub>REF</sub>                                                | K <sub>SOVP/VREF</sub>                                   | 104            | 105            | 106            | %    |

| Soft-OVP Threshold                                   | V <sub>FB</sub> = increasing                                                                                     | V <sub>SOVP</sub>                                        | _              | 2.625          | -              | V    |

| Soft-OVP Hysteresis                                  | V <sub>FB</sub> = decreasing                                                                                     | V <sub>SOVP(HYS)</sub>                                   | 35             | 50             | 65             | mV   |

| Static OVP Minimum Duty Ratio                        | V <sub>FB</sub> = 2.55 V, V <sub>Control</sub> = open                                                            | D <sub>MIN</sub>                                         | _              | -              | 0              | %    |

| Undervoltage to V <sub>REF</sub> Ratio               | $V_{FB}$ = increasing, $V_{UVP1}/V_{REF}$                                                                        | K <sub>UVP1/VREF</sub>                                   | 8              | 12             | 16             | %    |

| Undervoltage Threshold                               | V <sub>FB</sub> = decreasing                                                                                     | V <sub>UVP1</sub>                                        | _              | 300            | -              | mV   |

| Undervoltage to V <sub>REF</sub> Hysteresis Ratio    | V <sub>FB</sub> = increasing                                                                                     | V <sub>UVP1(HYS)</sub>                                   | _              | -              | 25             | mV   |

| Feedback Input Sink Current                          | $V_{FB} = V_{SOVP}$ , HVFB = open<br>$V_{FB} = V_{UVP1}$ , HVFB = open                                           | I <sub>FB(SNK1)</sub><br>I <sub>FB(SNK2)</sub>           | 50<br>50       | 200<br>200     | 450<br>450     | nA   |

| FAST OVERVOLTAGE AND BULK UNDERVOL                   | TAGE PROTECTION (FOVP and BL                                                                                     | JV)                                                      |                |                |                |      |

| Fast OVP Threshold                                   | V <sub>FOVP/BUV</sub> increasing                                                                                 | V <sub>FOVP</sub>                                        | _              | 2.675          | -              | V    |

| Fast OVP Hysteresis                                  | V <sub>FOVP/BUV</sub> decreasing                                                                                 | V <sub>FOVP(HYS)</sub>                                   | 15             | 30             | 60             | mV   |

| Ratio Between Fast and Soft OVP Levels               | K <sub>FOVP/SOVP</sub> = V <sub>FOVP</sub> / V <sub>SOVP</sub>                                                   | K <sub>FOVP/SOVP</sub>                                   | 101.5          | 102.0          | 102.5          | %    |

| Ratio Between Fast OVP and $V_{REF}$                 | K <sub>FOVP/VREF</sub> = V <sub>FOVP</sub> / V <sub>REF</sub>                                                    | K <sub>FOVP/VREF</sub>                                   | 106            | 107            | 108            | %    |

| Bulk Undervoltage Threshold                          | V <sub>FOVP/BUV</sub> decreasing                                                                                 | V <sub>BUV</sub>                                         | _              | 1.9            | -              | V    |

| Undervoltage Protection Threshold to $V_{REF}$ Ratio | $V_{FOVP/BUV}$ decreasing, $V_{BUV}/V_{REF}$                                                                     | K <sub>BUV/VREF</sub>                                    | 74             | 76             | 78             | %    |

| Open Pin Detection Threshold                         | V <sub>FOVP/BUV</sub> decreasing                                                                                 | V <sub>UVP2</sub>                                        | 0.2            | 0.3            | 0.4            | V    |

| Open Pin Detection Hysteresis                        | V <sub>FOVP/BUV</sub> increasing                                                                                 | V <sub>UVP2(HYS)</sub>                                   | -              | 10             | -              | mV   |

| Pull-Down Current Source                             | V <sub>FOVP/BUV</sub> = V <sub>BUV</sub><br>V <sub>FOVP/BUV</sub> = V <sub>UVP2</sub>                            | IFOVP/BUV(bias1)<br>IFOVP/BUV(bias2)                     | 50<br>50       | 200<br>200     | 450<br>450     | nA   |

| LINE OVP                                             |                                                                                                                  | • · · · · ·                                              |                | -              |                | •    |

| Ratio Between Line OVP and VREF                      | V <sub>FB</sub> increasing                                                                                       | K <sub>LOVP</sub>                                        | 111            | 112.5          | 114            | %    |

| Line Overvoltage Threshold                           |                                                                                                                  | V <sub>LOVP</sub>                                        | _              | 2.813          | -              | V    |

| Line Overvoltage Filter                              | V <sub>FB</sub> increasing                                                                                       | t <sub>LOVP(blank)</sub>                                 | 45             | 55             | 65             | μs   |

| STANDBY INPUT                                        | 1                                                                                                                | · · /                                                    |                |                | <u>n</u>       | 1    |

| Standby Input Threshold                              | V <sub>STDBY</sub> decreasing                                                                                    | V <sub>standby</sub>                                     | 285            | 300            | 315            | mV   |

| Standby Input Blanking Duration                      |                                                                                                                  | t <sub>blank(STDBY)</sub>                                | 0.8            | 1              | 1.2            | ms   |

| =                                                    |                                                                                                                  | · · · · /                                                |                |                | 1              | 8    |

| <b>Table 4. ELECTRICAL CHARACTERISTICS</b> (V <sub>CC</sub> = 15 V, V <sub>HV</sub> = 120 V, V <sub>FB</sub> = 2.4 V, R <sub>HVFB</sub> = 200 kΩ, V <sub>HVFB</sub> = 20 V, C <sub>VControl</sub> =                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 nF, V <sub>FFcontrol</sub> = 2.6 V, V <sub>ZCD/CS</sub> = 0 V, R <sub>ZCD/CS</sub> = 3 kΩ, V <sub>FOVPBUV</sub> = 2.4 V, V <sub>STDBY</sub> = 1 V, V <sub>Restart</sub> = 1 V, V <sub>PSTimer</sub> = 0 V, V <sub>Fault</sub> = open, |

| $V_{PFCOK}$ = open, $C_{DRV}$ = 1 nF, for typical values $T_J$ = 25°C, for min/max values, $T_J$ is -40°C to 125°C, unless otherwise noted)                                                                                              |

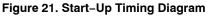

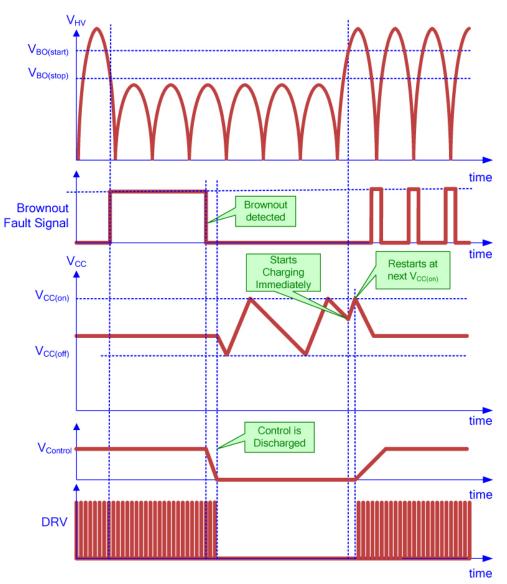

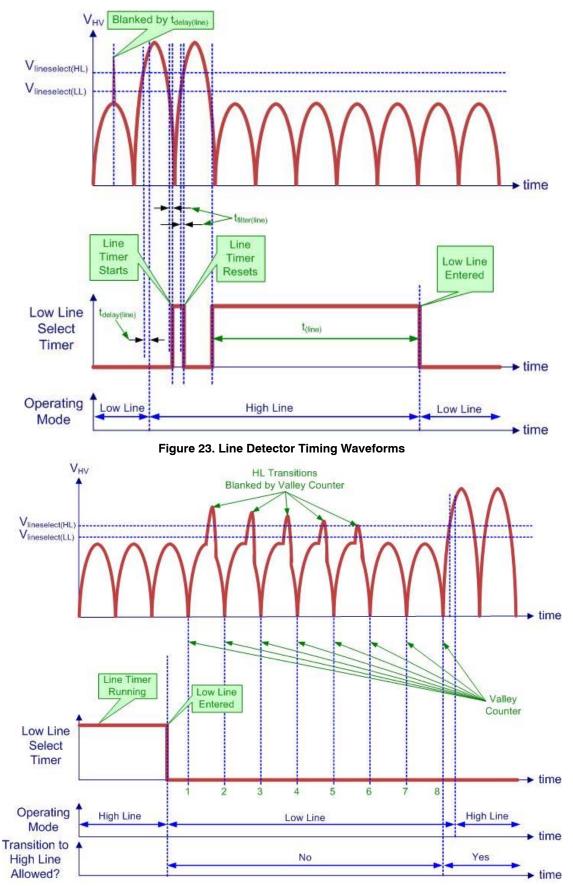

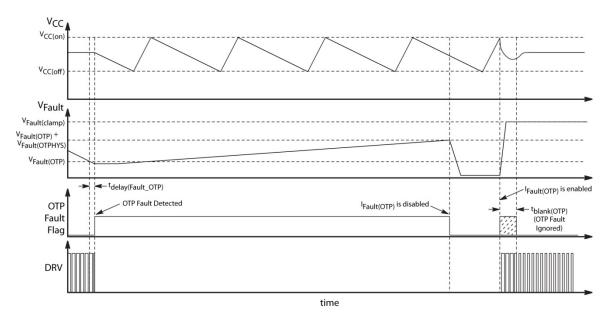

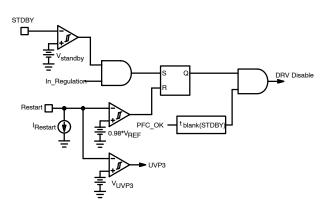

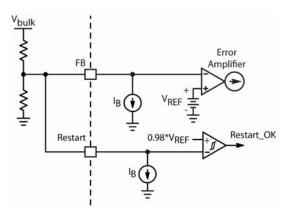

| Characteristics                                                                     | Conditions                                                     | Symbol                                               | Min          | Тур          | Мах          | Unit |