#

# High-Voltage Watchdog Timers with Adjustable Timeout Delay

## **General Description**

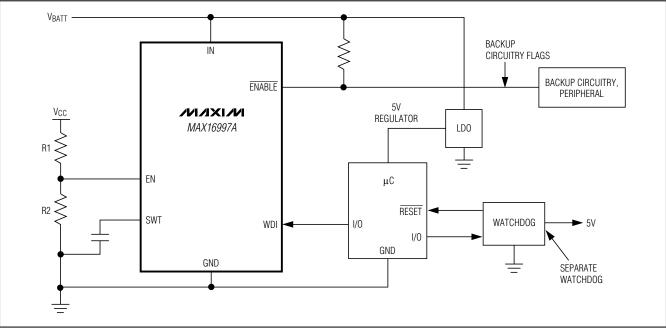

The MAX16997/MAX16998 are microprocessor ( $\mu$ P) supervisory circuits for high-input-voltage and low-quiescent-current applications. These devices detect downstream circuit failures and provide switchover to redundant circuitry. See the *Selector Guide* for the different versions of this product family.

The MAX16997/MAX16998 family has four independent inputs for reset and watchdog functions. SWT and SRT inputs independently set the timeout periods of watchdog and reset timers through external capacitors. RESETIN/EN monitor voltages at respective inputs. A resistive voltage-divider sets the reset threshold.

The MAX16998A/B/D generate two output signals, RESET and ENABLE. RESET asserts whenever RESETIN drops below its threshold voltage or when the watchdog timer detects a timing fault at WDI. Once asserted, and after all reset conditions are removed, RESET remains low for the reset timeout period, tRESET, and then goes high. The MAX16997A generates one output signal (ENABLE) based on the voltage level at EN and the signal at WDI.

The MAX16997A does not have a RESET output. The watchdog is disabled if the voltage at EN is below its threshold. The MAX16997A watchdog timer starts timing when the voltage at EN becomes higher than the preset threshold voltage level. Each time EN rises above the preset threshold voltage, the initial watchdog timeout period is 8 times the normal watchdog timeout period (twp).

The MAX16997/MAX16998 are available in 8-pin lead-free  $\mu$ MAX® packages and are fully specified over the -40°C to +125°C automotive temperature range.

## **Applications**

Automotive Industrial

## **Features**

- Wide 5V to 40V Input Voltage Range

- ♦ 18µA Quiescent Current (Typical at +125°C)

- Capacitor-Adjustable Timeout Period for Watchdog and Reset

- Windowed Watchdog Timer Options (MAX16998B/D)

- External Voltage Monitoring (RESETIN for the MAX16998A/B/D and EN for the MAX16997A)

- Car Battery-Compatible EN Input

- TTL- and CMOS-Compatible Open-Drain Outputs

- ♦ 18V Maximum Open-Drain Reset Output Voltage

- 28V Maximum Open-Drain Enable Output Voltage

- Power-On/Power-Off Reset Functionality (MAX16998A/B/D Only)

- AEC-Q100 Qualified

- ♦ -40°C to +125°C Operating Temperature Range

- Small (3mm x 3mm) µMAX Package

- WDI Narrow Pulse Immunity

### **\_Ordering Information**

| PART            | TEMP RANGE      | PIN-PACKAGE |

|-----------------|-----------------|-------------|

| MAX16997AAUA+   | -40°C to +125°C | 8 µMAX      |

| MAX16997AAUA/V+ | -40°C to +125°C | 8 µMAX      |

| MAX16998AAUA+   | -40°C to +125°C | 8 µMAX      |

| MAX16998AAUA/V+ | -40°C to +125°C | 8 µMAX      |

| MAX16998BAUA+   | -40°C to +125°C | 8 µMAX      |

| MAX16998BAUA/V+ | -40°C to +125°C | 8 µMAX      |

| MAX16998DAUA+   | -40°C to +125°C | 8 µMAX      |

| MAX16998DAUA/V+ | -40°C to +125°C | 8 µMAX      |

|                 |                 |             |

+Denotes a lead(Pb)-free/RoHS-compliant package. /V Denotes Automotive qualified part.

## Selector Guide

| PART      | WATCHDOG<br>WINDOW SIZE (%) |   | EN | RESETIN |   |

|-----------|-----------------------------|---|----|---------|---|

| MAX16997A | 100                         | 1 | —  | 1       | — |

| MAX16998A | 100                         | 1 | ✓  | —       | 1 |

| MAX16998B | 50                          | ✓ | ✓  | —       | 1 |

| MAX16998D | 75                          | 1 | 1  | _       | 1 |

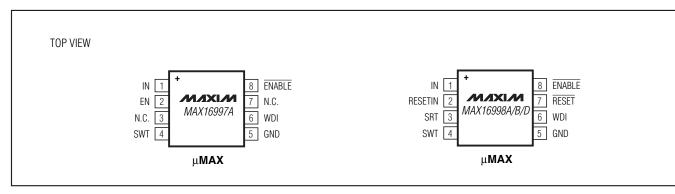

Pin Configurations appear at end of data sheet.

µMAX is a registered trademark of Maxim Integrated Products, Inc.

###

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| (All pins referenced to GND, unless other        | ,            |

|--------------------------------------------------|--------------|

| IN, ENABLE                                       | 0.3V to +45V |

| WDI, RESET, EN                                   | 0.3V to +20V |

| RESETIN                                          | 0.3V to +20V |

| SRT, SWT                                         | 0.3V to +12V |

| Maximum Current (all pins)                       | 30mA         |

| Continuous Power Dissipation ( $T_A = +70^\circ$ | °C)          |

| a man a sa s    |              |

Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) (Note 1).....42°C/W Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) (Note 1).....206.3°C/W Operating Temperature Range ( $T_A$ )......-40°C to +125°C Junction Temperature ( $T_J$ ).....+150°C Storage Temperature Range .....-65°C to +150°C Lead Temperature (soldering, 10s)....+300°C

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

|                                                                      | construction of the second |                                                                            |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| $(V_{IN} = 14V, T_A = T_J = -40^{\circ}C \text{ to } +125^{\circ}C,$ | uniess otherwise noted. Typica                                                                                 | $1 \text{ values are at } 1 \text{ A} = +25^{\circ} \text{ G}$ .) (Note 2) |

| PARAMETER                         | SYMBOL                | CONDITIONS                                                  | MIN   | ТҮР    | МАХ   | UNITS |  |

|-----------------------------------|-----------------------|-------------------------------------------------------------|-------|--------|-------|-------|--|

| Operating Voltage Range           | V <sub>IN</sub>       |                                                             | 5.0   |        | 40.0  | V     |  |

| Current Current                   |                       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$               |       | 18     | 30    |       |  |

| Supply Current                    | IIN                   | $T_A = -40^{\circ}C \text{ to } + 125^{\circ}C$             |       | 18     | 60    | μA    |  |

| SWT Ramp Current                  | IRAMP_SWT             | $V_{SWT} = 1.0V$                                            | 450   | 500    | 550   | nA    |  |

| SRT Ramp Current                  | IRAMP_SRT             | $V_{SRT} = 1.0V$                                            | 410   | 500    | 600   | nA    |  |

| SWT/SRT Ramp Threshold<br>Voltage | VRAMP                 |                                                             | 1.115 | 1.235  | 1.363 | V     |  |

| RESET TIMER                       | •                     |                                                             |       |        |       | •     |  |

| Power-On Reset Input Threshold    | Vaar                  | VRESETIN rising                                             | 1.135 | 1.255  | 1.383 | V     |  |

| Voltage                           | Vpon                  | VRESETIN falling                                            | 1.115 | 1.235  | 1.363 | V     |  |

| RESETIN Input Leakage Current     | <b>I</b> LPON         | VRESETIN = 2V                                               |       | 0.1    |       | μA    |  |

|                                   |                       | RESET asserted, ISINK = 1mA                                 |       |        | 0.9   |       |  |

| RESET Output Low Voltage          | Volrst                | $V_{IN} = 1.1V$ , $I_{SINK} = 160\mu A$ , RESET asserted    |       |        | 0.4   | V     |  |

|                                   |                       | RESET asserted, ISINK = 0.4mA                               |       |        | 0.4   |       |  |

| RESET Leakage Current             | ILKGR                 | $V_{\overline{RESET}} = 20V, \overline{RESET}$ not asserted |       | 0.1    |       | μA    |  |

| ENABLE Output Low Voltage         | VOLEN                 | ENABLE asserted, I <sub>SINK</sub> = 5mA                    |       |        | 0.4   | V     |  |

| ENABLE Leakage Current            | ILKGE                 | VENABLE = 14V, ENABLE not asserted                          |       | 0.1    |       | μA    |  |

| Minimum Reset Timeout Period      | <b>t</b> RESETmin     | C <sub>SRT</sub> = 390pF (Note 3)                           |       | 1      |       | ms    |  |

| Reset Timeout Period              | <b>t</b> RESET        | C <sub>SRT</sub> = 2000pF (Note 3)                          |       | 5      |       | ms    |  |

| Maximum Reset Time Period         | t <sub>RESETmax</sub> | C <sub>SRT</sub> = 47nF                                     |       | 116.09 |       | ms    |  |

| RESET to ENABLE Delay             | t <sub>REDL</sub>     |                                                             |       | 1.5    |       | μs    |  |

| RESETIN to RESET Delay            | tRRDL                 | RESETIN falling below VPON to RESET falling edge            |       | 1      |       | μs    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 14V, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                | SYMBOL              | CONDITIONS                         | MIN  | TYP    | MAX       | UNITS      |

|------------------------------------------|---------------------|------------------------------------|------|--------|-----------|------------|

| WATCHDOG TIMER                           |                     | •                                  |      |        |           | •          |

|                                          | V <sub>IH</sub>     |                                    | 2.25 |        |           | V          |

| WDI Input Threshold                      | VIL                 |                                    |      |        | 0.9       | v          |

| WDI Input Hysteresis                     | WDI <sub>HYST</sub> |                                    |      | 200    |           | mV         |

| WDI Minimum Pulse Width                  | twDImin             | (Note 4)                           | 6.5  |        |           | μs         |

| WDI Input Current                        | I <sub>WDI</sub>    | WDI = 0 or 14V                     |      | 0.1    |           | μA         |

| Minimum Watchdog Timeout                 | twPmin              | C <sub>SWT</sub> = 680pF (Note 3)  |      | 6.8    |           | ms         |

| Watchdog Timeout Period                  | twp                 | C <sub>SWT</sub> = 1200pF (Note 3) |      | 12     |           | ms         |

| Maximum Watchdog Timeout                 | twpmax              | $C_{SWT} = 22nF$                   |      | 217.36 |           | ms         |

| Wetchdog Window                          | Dure                | MAX16998B                          | 45   | 50     | 55        | 9/ to 1/10 |

| Watchdog Window                          | Dwdi                | MAX16998D                          | 67.5 | 75     | 82.5 %twp |            |

| WDI to ENABLE Output Delay               |                     | Start from WDI third wrong trigger |      | 100    |           | μs         |

| RESET Pullup Resistor Supply<br>Voltage  |                     | (Note 5)                           | 2.25 | 2.5    | 18.00     | V          |

| ENABLE Pullup Resistor Supply<br>Voltage |                     | (Note 5)                           | 2.25 | 2.5    | 28.00     | V          |

Note 2: R<sub>RESET</sub> and R<sub>ENABLE</sub> are external pullup resistors for open-drain outputs. Connect R<sub>RESET</sub> and R<sub>ENABLE</sub> to a minimum 2.5V voltage. Connect R<sub>RESET</sub> to a maximum voltage of 18V and connect R<sub>ENABLE</sub> to a maximum voltage of 28V.

Note 3: Calculated based on  $V_{RAMP} = 1.235V$  and  $I_{RAMP} = 500nA$ .

Note 4: WDI pulses narrower than 1µs will be ignored. WDI pulses wider than 6.5µs will be recognized.

Note 5: Not production tested, guaranteed by design.

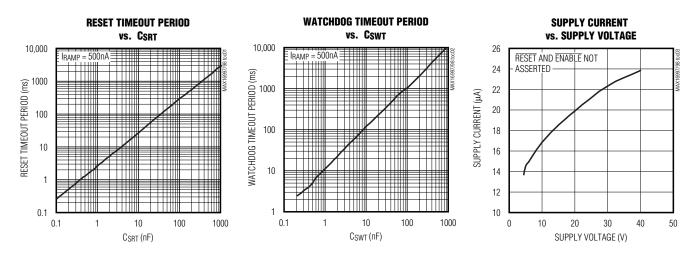

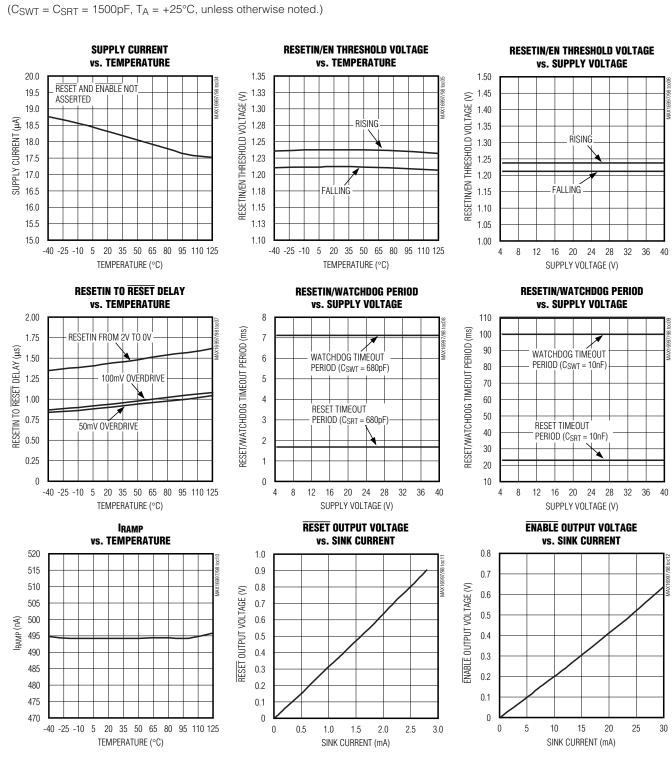

# **Typical Operating Characteristics**

(C<sub>SWT</sub> = C<sub>SRT</sub> = 1500pF,  $T_A$  = +25°C, unless otherwise noted.)

**Typical Operating Characteristics (continued)**

MIXIM

MAX16997/MAX16998

# Pin Description

|           | PIN           |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-----------|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX16997A | MAX16998A/B/D | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1         | 1             | IN      | Power-Supply Input. Bypass IN to GND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 2         |               | EN      | High-Impedance Input to the Enable Comparator. Depending on the voltage leve at EN, the internal watchdog timer is turned on or off (see the <i>EN Input</i> section).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 3, 7      |               | N.C.    | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 4         | 4             | SWT     | Watchdog Timeout Adjustment Input. Connect a capacitor between SWT and GI to set the basic watchdog timeout period. Connect SWT to ground to disable the watchdog timer function. See the <i>Selecting the Watchdog Timeout Capacitor</i> section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 5         | 5             | GND     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 6         | 6             | WDI     | Watchdog Input.<br>MAX16997A/MAX16998A (Timeout Watchdog): Two consecutive WDI falling<br>edges must occur at WDI within the watchdog timeout period or RESET asserts.<br>The watchdog timer clears when a falling edge occurs on WDI or whenever RESET<br>is asserted. ENABLE asserts if three consecutive watchdog timeout periods have<br>expired without a falling edge at WDI. WDI is a high-impedance input. Leaving<br>WDI unconnected will cause improper operation of the watchdog time.<br>MAX16998B/D (Window Watchdog): WDI falling transitions within periods shorter<br>than the closed window width or longer than the basic watchdog timeout period<br>force RESET to assert low for the reset timeout period. The watchdog timer begins<br>to count after RESET is deasserted. The watchdog timer clears when a WDI falling<br>edge occurs or whenever RESET is asserted. ENABLE asserts if three consecutive<br>watchdog timeout periods have expired without a falling edge at WDI. WDI is a<br>high-impedance input. Leaving WDI unconnected will cause improper operation of<br>the watchdog timer. |  |

| 8         | 8             | ENABLE  | Open-Drain Enable Output. ENABLE asserts when three consecutive WDI faults occur. ENABLE remains low until three consecutive good WDI falling edges occur. ENABLE does not assert if the voltage at RESETIN (EN) is below its threshold. These devices are guaranteed to be in correct ENABLE output logic state when V <sub>IN</sub> remains greater than 1.1V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| _         | 2             | RESETIN | Reset Input. High-impedance input to the reset comparator. When V <sub>RESETIN</sub> falls below 1.235V, RESET asserts. RESET remains asserted as long as V <sub>RESETIN</sub> is low and for the reset timeout period after RESETIN goes high. Connect V <sub>RESETIN</sub> to the center point of an external resistive divider to set the threshold for the externally monitored voltage. Connect RESETIN to a defined voltage logic-level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|           | 3             | SRT     | Reset Timeout Adjustment Input. Connect a capacitor between SRT and GND to set the reset timeout period. See the <i>Selecting the Reset Timeout Capacitor</i> section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| _         | 7             | RESET   | Open-Drain Reset Output. RESET asserts whenever RESETIN drops below the selected reset threshold voltage (V <sub>PON</sub> ). RESET remains low for the reset timeout period after all reset conditions are removed, and then goes high. RESET asserts for a period of t <sub>RESET</sub> whenever a WDI fault occurs. Connect RESET to a pullup resistor connected to a voltage higher than 2.5V (typ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

IN //IXI//I MAX16997/MAX16998 PREG RESET  $V_{BG}$ RESETIN (MAX16998) EN (MAX16997) WDI BUFFER ENABLE MAX16997A/ Iramp MAX16998A/B/D LOGIC V<sub>BG</sub> ¥ SRT (MAX16998) IRAMP V<sub>BG</sub> SWT GND

**Functional Diagram**

MAX16997/MAX16998

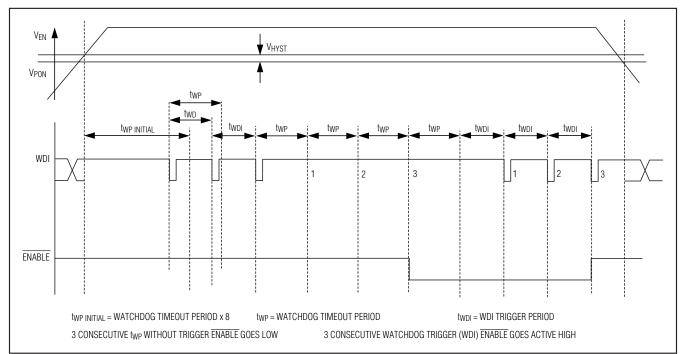

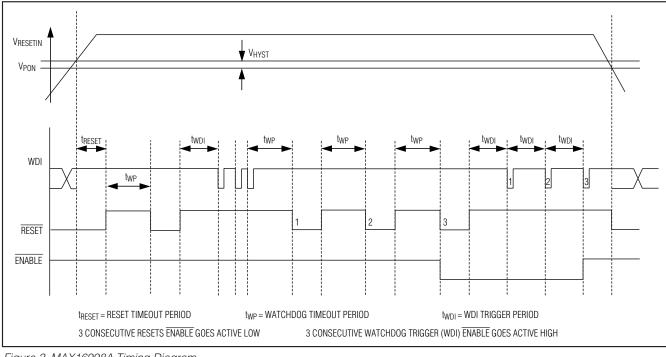

## **Timing Diagrams**

MAX16997/MAX16998

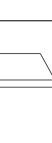

Figure 1. MAX16997A Timing Diagram

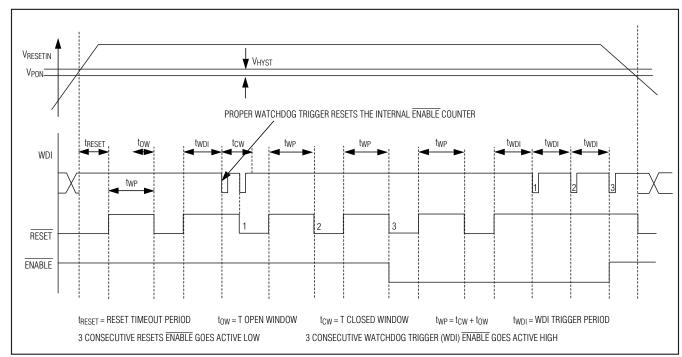

Figure 2. MAX16998A Timing Diagram

7

## Timing Diagrams (continued)

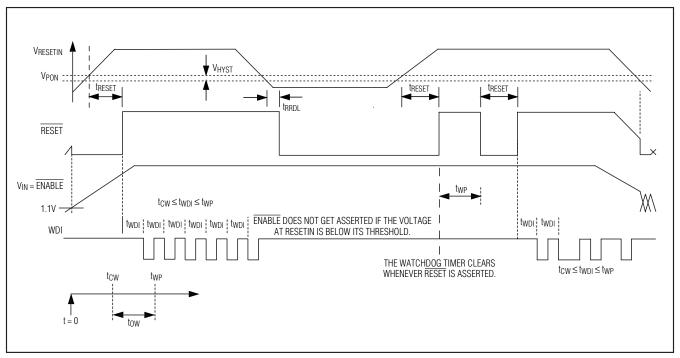

Figure 3. MAX16998B/D Timing Diagram

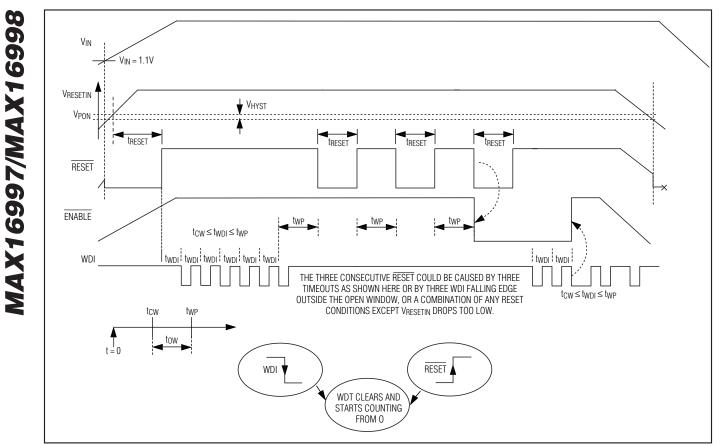

Figure 4. RESETIN, RESET, VIN, ENABLE, and WDI Voltage Monitoring

MAX16997/MAX16998

## **Detailed Description**

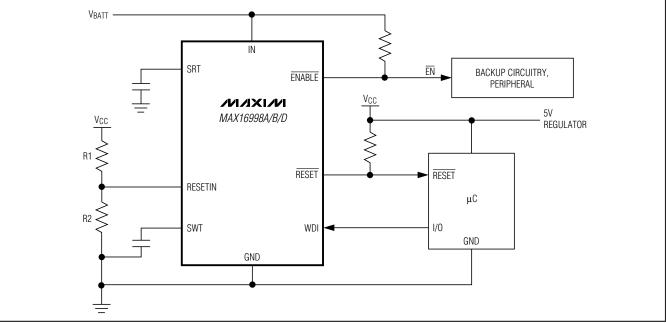

The MAX16997/MAX16998 are  $\mu$ P supervisory circuits for high-input-voltage and low-quiescent-current applications. These devices improve system reliability by monitoring the sub-system for software code execution errors. The MAX16997A/MAX16998A/B/D detect downstream circuit failures, and provide switchover to redundant circuitry. These devices provide complete adjustability for reset and watchdog functions.

The MAX16998A/B/D generate two output signals, RESET and ENABLE, that depend on the voltage level at RESETIN and the signal at WDI. RESET asserts whenever RESETIN drops below the selected reset threshold voltage. RESET remains low for the reset timeout period after all reset conditions are deasserted, and then goes high. RESET also asserts for a period of tRESET whenever a WDI fault occurs. The MAX16997A generates one output signal (ENABLE) based on the voltage level at EN and the signal at WDI.

The MAX16997A/MAX16998A provide watchdog timeout adjustability with an external capacitor. The MAX16998A asserts RESET when two consecutive WDI falling edges do not occur within the watchdog timeout period. This device also asserts ENABLE if three consecutive watchdog timeout periods have elapsed without a falling edge at WDI. ENABLE remains low until three consecutive good WDI falling edges occur. ENABLE does not assert if the voltage at RESETIN (EN) is below its threshold. For the MAX16997A, the watchdog timer starts timing if the voltage at EN is higher than a preset threshold level. Each time the voltage at EN rises from below to above the preset threshold voltage, the initial watchdog timeout period is 8 times the normal watchdog timeout period (twp). Other than described above, the MAX16997A behaves the same as the MAX16998A.

The MAX16998B/MAX16998D contain a window watchdog timer that looks for activity outside an expected window of operation. The window size is factory-set to 50% (MAX16998B) or 75% (MAX16998D) of the adjusted watchdog timeout period.

**Reset Output (RESET) (MAX16998A/B/D)** The reset output is typically connected to the reset input of the  $\mu$ C to start or restart it in a known state. The MAX16998A/B/D provide an active-low open-drain reset logic to prevent code execution errors. For the MAX16998A/B/D, RESET asserts whenever RESETIN drops below the selected reset threshold voltage (VPON). RESET remains low for the reset timeout period after RESETIN exceeds the selected threshold voltage, and then goes high.

The MAX16998A asserts  $\overline{\text{RESET}}$  for a period of tresset when two consecutive WDI falling edges do not occur within the adjusted watchdog timeout period. The MAX16998B/D also assert RESET for a period of tresset when a WDI falling edge does not occur within the open window period.

Anytime reset asserts, the watchdog timer clears. At the end of the reset timeout period, RESET goes high, and the watchdog timer is restarted from zero (see the *Selecting the Watchdog Timeout Capacitor* section).

#### Enable Output (ENABLE)

If the  $\mu$ C fails to operate correctly (e.g., the software execution is stuck in a loop), WDI does not trigger any more and RESET pulls low, resetting the  $\mu$ C. If the  $\mu$ C does not work properly in the next loop either, the device asserts RESET again. After three watchdog timeout periods elapse with no falling edges at WDI, ENABLE asserts and flags a backup circuit that can take over the operation.

**ENABLE** remains low until three consecutive WDI falling edges with periods shorter than the watchdog timeout occur. **ENABLE** does not assert if the voltage at RESETIN (EN) is below its threshold. These devices are guaranteed to be in correct **ENABLE** output logic state when VIN remains greater than 1.1V.

#### **Power-On/Power-Off Sequence**

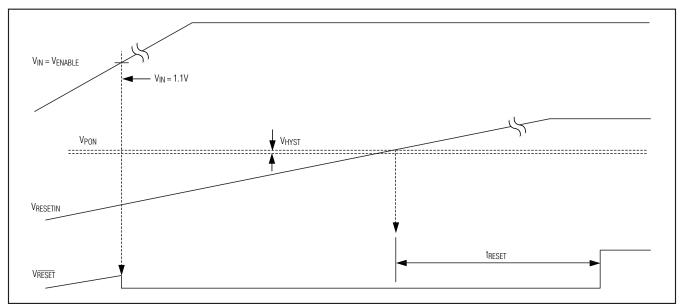

Figure 5 shows the power-up and power-down sequence for RESET and ENABLE for the MAX16998A/B/D.

On power-up, once V<sub>IN</sub> reaches 1.1V, RESET goes logic-low. As RESETIN rises, RESET remains low. When RESETIN rises above V<sub>PON</sub>, the reset timer starts and RESET remains low. When the reset timeout period ends, RESET goes high.

On power-down, once RESETIN goes below VPON, RESET goes low and remains low until VIN drops below 1.1V. Figure 6 shows the detailed power-up sequence for the MAX16998A/B/D.

Figure 5. Power-On Reset and Power-Down Reset for the MAX16998A/B/D

Figure 6. Detailed Power-Up Sequence for the MAX16998A/B/D

#### **RESETIN Input (MAX16998A/B/D)**

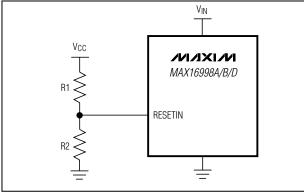

The MAX16998A/B/D monitor the voltage at RESETIN using an adjustable reset threshold, set with an external resistive divider (see Figure 7). RESET asserts when VRESETIN is below 1.235V.

Use the following equations to calculate the externally monitored voltage (V<sub>CC</sub>).

$$V_{TH} = V_{PON} \left[ \frac{R_1}{R_2} + 1 \right]$$

where V<sub>TH</sub> is the desired reset threshold voltage, and V<sub>PON</sub> = 1.235V. To simplify the resistor selection, choose a value for  $R_2$  (< than 1M $\Omega$ ) and calculate  $R_1$ .

$$R_1 = R_2 \left[ \frac{V_{TH}}{V_{PON}} - 1 \right]$$

#### **EN** Input

The MAX16997A provides a high-impedance input (EN) to the enable comparator. Based on the voltage level at EN, the watchdog timer is turned on or off. The watchdog timer starts timing if the voltage level at EN is higher than a preset threshold voltage (V<sub>PON</sub>). Each time the voltage at EN rises from below to above the preset threshold voltage, the initial watchdog timeout period is 8 times the normal watchdog timeout period (twp).

## Watchdog Timer

#### MAX16997A

The watchdog circuit monitors the  $\mu$ C's activity. For the MAX16997A, the watchdog timer starts timing once the voltage at EN is higher than a preset threshold voltage. ENABLE asserts if three consecutive watchdog timeout periods have elapsed without a falling edge at WDI. ENABLE remains low until three consecutive WDI falling edges with periods shorter than the watchdog timeout period occur.

Each time the voltage at EN rises from below to above the preset threshold voltage, the first watchdog timeout period extends by a factor of 8 (8 x twp). If a WDI falling edge occurs during that time, then the watchdog timeout period is immediately switched over to a single twp. If no watchdog falling edge occurs during this prolonged watchdog timeout period, ENABLE goes low at the end of this period and stays low. After this, the first falling edge at WDI switches the watchdog timeout period to a single twp. See Figure 1. The MAX16997A watchdog timeout period (twp) is adjustable by a single capacitor at SWT.

Figure 7. Setting RESETIN Voltage for the MAX16998A/B/D

#### MAX16998A

The MAX16998A asserts RESET when two consecutive WDI falling edges do not occur within the adjusted watchdog timeout period (twp). RESET remains asserted for the reset timeout period (tRESET) and then goes high. This device also asserts ENABLE if three consecutive watchdog timeout periods have elapsed without a falling edge at WDI. ENABLE remains low until three consecutive WDI falling edges with periods shorter than the watchdog timeout period occur (see Figure 2).

The internal watchdog timer is cleared by a RESET rising edge or by a falling edge at WDI. The watchdog timer remains cleared while RESET is asserted; as soon as RESET is released, the timer starts counting. WDI falling edges are ignored when RESET is low. If no WDI falling edge occurs within the watchdog timeout period, RESET immediately goes low and stays low for the adjusted reset timeout period.

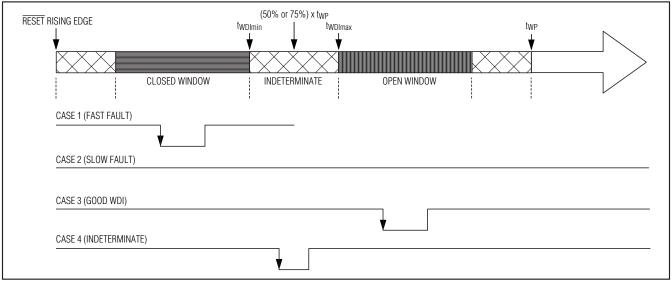

#### MAX16998B/D

The MAX16998B/D have a windowed watchdog timer. The watchdog timeout period (twp) is the sum of a closed window period (t<sub>CW</sub>) and an open window period (t<sub>OW</sub>). If the  $\mu$ C issues a WDI falling edge within the open window period, RESET stays high. Once a WDI falling edge occurs within the closed window period, RESET immediately goes low and stays low for the adjusted reset timeout period (see Figure 3). If no WDI falling edge occurs within the watchdog timeout period, RESET immediately goes low and stays low for the adjusted reset timeout period. The open window size is factory-set to 50% of the watchdog timeout period for the MAX16998B and 75% for the MAX16998D.

Figure 8 shows a WDI falling edge identified as a *good* or a *bad* WDI signal edge. In case 1, the WDI falling edge occurs within the closed window period and is considered a *bad* WDI falling edge (early fault); therefore, it asserts RESET. Case 2 also shows another fault. In this case, no

WDI falling edge occurs within the watchdog timeout period (twp) and is considered a late fault that asserts RESET. In case 3, the WDI falling edge occurs within the open window period and is considered a *good* WDI signal falling edge. In this case, RESET stays high. In case 4, the WDI falling edge occurs within the indeterminate region. In this case, the RESET state is indeterminate.

These devices assert ENABLE after three consecutive bad WDI falling edges. ENABLE returns high after three consecutive good WDI signal falling edges (see Figure 3).

Either a rising edge at  $\overline{\text{RESET}}$  or a falling edge at WDI clears the internal watchdog timer. The watchdog timer remains cleared while  $\overline{\text{RESET}}$  is asserted. The watchdog timer begins counting when  $\overline{\text{RESET}}$  goes high. WDI falling edges are ignored when  $\overline{\text{RESET}}$  is low.

## Applications Information

#### **Selecting the Reset Timeout Capacitor**

The reset timeout period is adjustable to accommodate a variety of  $\mu$ P applications. Adjust the reset timeout period (tRESET) by connecting a capacitor (CSRT) between SRT and ground. See the Reset Timeout Period vs. CSRT graph in the *Typical Operating Characteristics*. Calculate the reset timeout capacitance using the equation below:

$$C_{SRT} = t_{RESET} \times \frac{I_{RAMP}}{V_{RAMP}}$$

where  $V_{RAMP}$  is in volts,  $t_{RESET}$  is in seconds,  $I_{RAMP}$  is in nA, and  $C_{SRT}$  is in nF.

Leakage currents and stray capacitance (e.g., a scope probe, which induces both) at SRT may cause errors in the reset timeout period. If precise time control is required, use capacitors with low leakage current and high stability.

#### Selecting the Watchdog Timeout Capacitor

The watchdog timeout period is adjustable to accommodate a variety of  $\mu$ P applications. With this feature, the watchdog timeout can be optimized for software execution. The programmer determines how often the watchdog timer should be serviced. Adjust the watchdog timeout period (twp) by connecting a capacitor (CSWT) between SWT and GND. For normal mode operation, calculate the watchdog timeout capacitance using the following equation:

$$C_{SWT} = t_{WP} \times \frac{I_{RAMP}}{4 \times V_{RAMP}}$$

where  $V_{RAMP}$  is in volts, twp is in seconds,  $I_{RAMP}$  is in nA, and  $C_{SWT}$  is in nF. See the Watchdog Timeout Period vs.  $C_{SWT}$  graph in the *Typical Operating Characteristics*.

For the MAX16998B/MAX16998D, the open window size is factory-set to 50% (MAX16998B) or 75% (MAX16998D) of the watchdog period. Leakage currents and stray capacitance (e.g., a scope probe, which induces both) at SWT may cause errors in the watchdog timeout period. If precise time control is required, use capacitors with low leakage current and high stability. To disable the watchdog timer function, connect SWT to ground and connect WDI to either the high- or low-logic state.

Figure 8. The MAX16998B/D Window Watchdog Diagram

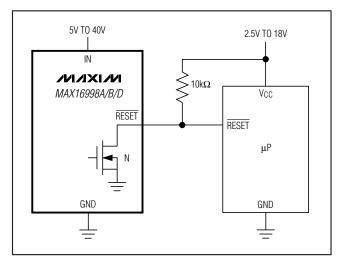

#### Interfacing to Other Voltages for Logic Compatibility

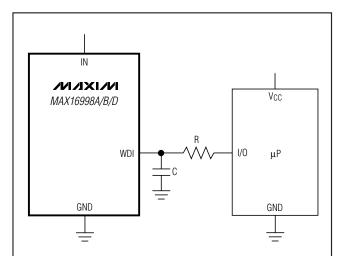

As shown in Figure 9, the open-drain RESET output can operate in the 2.5V to 18V range. This allows the device to interface a  $\mu$ P with other logic levels.

#### **WDI Glitch Immunity**

For additional glitch immunity, connect an RC lowpass filter as close as possible to WDI (see Figure 10).

For example, for glitches with duration of 1 $\mu$ s, a 12k $\Omega$  resistor and a 47pF capacitor will provide immunity.

#### Layout Considerations

SRT and SWT are connected to internal precision current sources. When developing the layout for the application, minimize stray capacitance attached to SRT and SWT as well as leakage currents that can reach those nodes. SRT and SWT traces should be as short as possible. Route traces carrying high-speed digital signals and traces with large voltage potentials as far from SRT and SWT as possible. Leakage currents and stray capacitance (e.g., a scope probe, which induces both) at these pins may cause errors in the reset and/or watchdog timeout period. When evaluating these parts, use clean prototype boards to ensure accurate reset and watchdog timeout periods. RESETIN is a high-impedance input and a high-impedance resistive divider (e.g.,  $100k\Omega$  to  $1M\Omega$ ) sets the threshold level. Minimize coupling to transient signals by keeping the connections to this input short. Any DC leakage current at RESETIN (e.g., a scope probe) causes errors in the programmed reset threshold.

#### **Typical Operating Circuits**

RESET remains asserted as long as RESETIN is below the regulated voltage and for the reset timeout period after RESETIN goes high to assure that the monitored LDO voltage is settled. Then, the  $\mu$ C starts operating and triggers WDI.

If the  $\mu$ C fails to operate correctly (e.g., the software execution is stuck in a loop), the WDI signal does not trigger the watchdog timer any more, and RESET is pulled low, resetting the  $\mu$ C. If the  $\mu$ C does not work properly in the next loop either, the device asserts RESET again. After three watchdog timeout periods with no WDI falling edges, ENABLE asserts and flags backup or safety circuits that take over the operation.

Figure 9. Interfacing to Other Voltage Levels

Figure 10. Additional WDI Glitch Immunity Circuit

Figure 11. MAX16998A/B/D Switch Over to Backup Circuitry

Figure 12. MAX16997A Application Diagram

## Pin Configurations

## **Chip Information**

PROCESS: BICMOS

| Package Information                                              |

|------------------------------------------------------------------|

| For the latest package outline information and land patterns, go |

| to www.maxim-ic.com/packages.                                    |

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 8 µMAX       | U8-1         | <u>21-0036</u> |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                               | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------------------------------------------------------------------|------------------|

| 0                  | 2/08             | Initial release                                                                           | —                |

| 1                  | 4/09             | Added bullet to <i>Features</i> section, revised <i>Electrical Characteristics</i> table. | 1, 2, 3          |

| 2                  | 8/09             | Added automotive qualified parts.                                                         | 1                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.