# **HiperPFS-4** Family

# PFC Controller with Integrated 600 V MOSFET Optimized for High PF and Efficiency Across Load Range

#### **Key Benefits**

- · Integrated 600 V MOSFET

- · High efficiency and power factor across load range

- >95% efficiency from 10% load to 100% load

- <60 mW no-load consumption at 230 VAC</li>

- PF >0.95 achievable at 20% load

- EN61000-3-2 Class C and D compliant

- · Highly integrated for smallest boost PFC form factor

- · Packaging optimized for high volume production

- Eliminates insulating pad/heat-spreader

- · Programmable Power Good (PG) signal

- User selectable power limit: Enables different HiperPFS-4 family members to be tested in the same design for optimum device selection

- Integrated non-linear amplifier for fast output OV and UV protection and transient response

- Digital line peak detection for robust performance even with distorted input voltage from UPS or generators

- Digital power factor enhancer compensates for EMI filter and bridge distortion, providing high-line PF >0.95 @ 20% load

- · Frequency adjusted over line voltage and thru each line cycle

- Spread-spectrum across >60 kHz window simplifies EMI filtering

- Reduces boost inductance

- Provides up to 450 W peak output power for universal applications, 610 W for high-line only applications

- Protection features include: UVLO, UV, OV, OTP, brown-in/out, cycle-by-cycle current limit and power limiting for overload protection

- Withstands 305 VAC steady-state and 410 VAC abnormal input

- · Halogen free and RoHS compliant

## **Applications**

- PC

- Printer

- LCD TV

- Video game consoles

- 80 Plus™ Platinum designs

- · High-power adaptors

- · High-power LED lighting

- Industrial and appliance

- Generic PFC converters

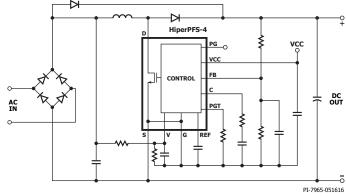

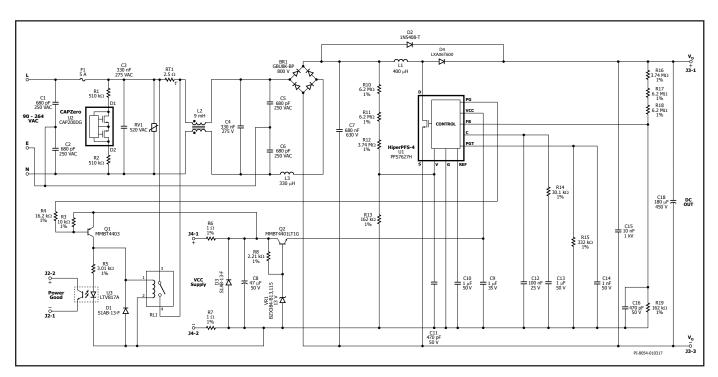

Figure 1. Typical Application Schematic.

| <b>Output Powe</b> | er Table (Full Pov                      | ver Mode)         |  |  |  |  |  |  |  |

|--------------------|-----------------------------------------|-------------------|--|--|--|--|--|--|--|

|                    | Universal Input Devices                 |                   |  |  |  |  |  |  |  |

| Product            | Continuous<br>Output Power at<br>90 VAC | Peak Output Power |  |  |  |  |  |  |  |

| PFS7623H/L         | 110 W                                   | 120 W             |  |  |  |  |  |  |  |

| PFS7624H/L         | 130 W                                   | 150 W             |  |  |  |  |  |  |  |

| PFS7625H/L         | 185 W                                   | 205 W             |  |  |  |  |  |  |  |

| PFS7626H/L         | 230 W                                   | 260 W             |  |  |  |  |  |  |  |

| PFS7627H/L         | 290 W                                   | 320 W             |  |  |  |  |  |  |  |

| PFS7628H/L         | 350 W                                   | 385 W             |  |  |  |  |  |  |  |

| PFS7629H/L         | 405 W                                   | 450 W             |  |  |  |  |  |  |  |

**High-Line Input Only Devices**

| Product  | Continuous<br>Output Power at<br>180 VAC | Peak Output Power |

|----------|------------------------------------------|-------------------|

| PFS7633H | 255 W                                    | 280 W             |

| PFS7634H | 315 W                                    | 350 W             |

| PFS7635H | 435 W                                    | 480 W             |

| PFS7636H | 550 W                                    | 610 W             |

Table 1. Output Power Table (See Table 2 on page 10 for more information.)

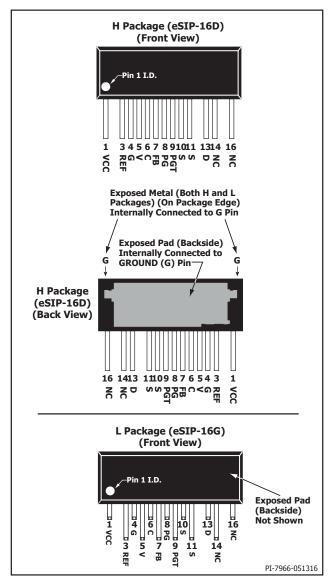

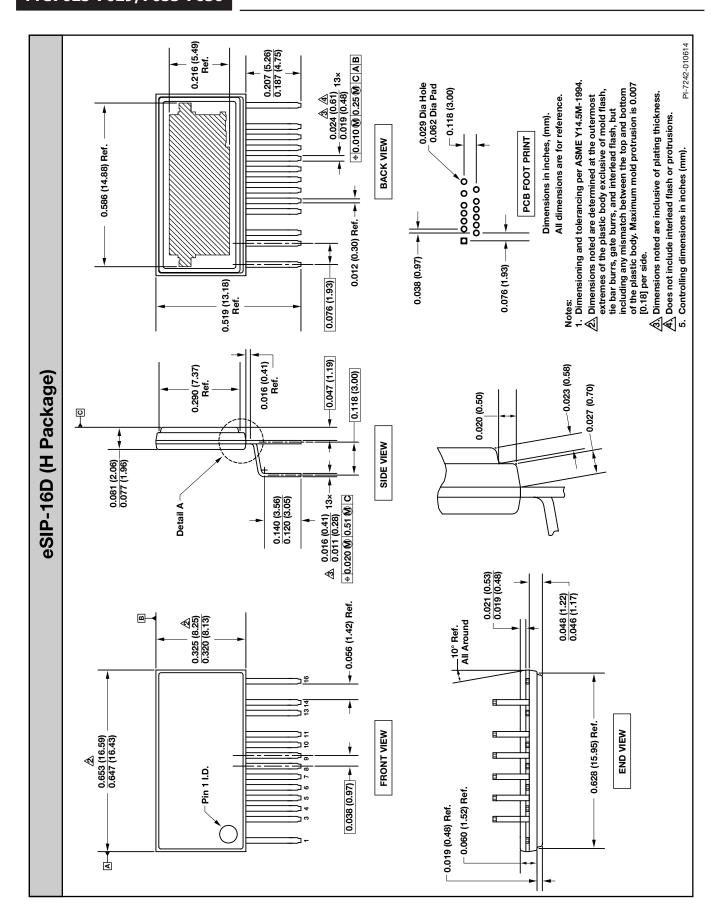

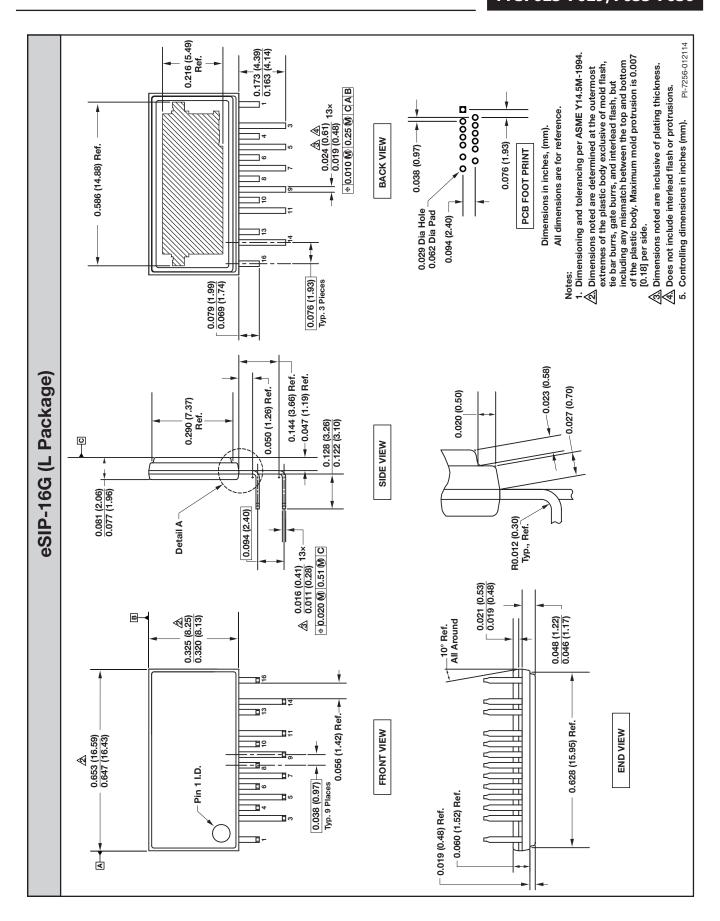

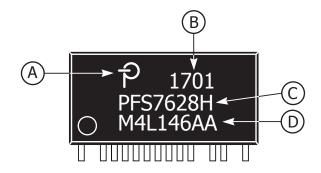

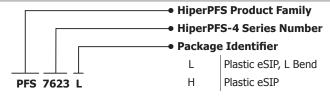

eSIP-16D (H Package)

eSIP-16G (L Package)

Figure 2. Package Options (Body Dimensions: 16.53 mm Width x 8.25 mm Height.)

## **Description**

The HiperPFS™-4 devices incorporate a continuous conduction mode (CCM) boost PFC controller, gate driver and 600 V power MOSFET in a single, low-profile (GROUND pin connected) power package. HiperPFS-4 devices eliminate need for external current sense resistors and their associated power loss, and use an innovative control technique that adjusts the switching frequency over output load, input line voltage, and input line cycle.

This control technique maximizes efficiency over the entire load range, particularly at light loads. Additionally, it minimizes the EMI filtering requirements due to its wide bandwidth spread spectrum effect. The HiperPFS-4 uses advanced digital techniques for line monitoring, line feed-forward scaling, and power factor enhancement; while using analog techniques for the core controller in order to maintain extremely low no-load power consumption. The HiperPFS-4 also features an integrated non-linear error amplifier for enhanced load transient response, a user programmable Power Good (PG) signal as well as user selectable power limit functionality. HiperPFS-4 includes Power Integrations' standard set of comprehensive protection features, such as UV, OV, brown-in/out, and hysteretic thermal shutdown. HiperPFS-4 also provides cycle-by-cycle current limit and Safe Operating Area (SOA) protection of the power MOSFET, output power limiting for overload protection, and pin-to-pin short-circuit protection

HiperPFS-4's innovative variable frequency continuous conduction mode operation (VF-CCM) minimizes switching losses by maintaining a low average switching frequency, while modulating the switching frequency in order to suppress EMI, the traditional challenge with continuous conduction mode solutions. Systems using HiperPFS-4 typically reduce the total X and Y capacitance requirements of the converter, the inductance of both the boost choke and EMI noise suppression chokes, thereby reducing overall system size and cost. Additionally, HiperPFS-4 devices dramatically reduce component count and board footprint while simplifying system design and enhancing reliability, when compared with designs that use discrete MOSFETs and controllers. The innovative variable frequency, continuous conduction mode controller enables the HiperPFS-4 to realize all of the benefits of continuous conduction mode operation while leveraging low-cost, small, simple EMI filters.

Many regions mandate high power factor for many electronic products with high power requirements. These rules are combined with numerous application-specific standards that require high power supply efficiency across the entire load range, from full load to as low as 10% load. High efficiency at light load is a challenge for traditional PFC solutions where fixed MOSFET switching frequencies cause fixed switching losses on each cycle, even at light loads. In addition to featuring flat efficiency across the load range, HiperPFS-4 also enables a high power factor of >0.95 at 20% load. HiperPFS-4 simplifies compliance with new and emerging energy-efficiency standards over a broad market space in applications such as PCs, LCD TVs, notebooks, appliances, pumps, motors, fans, printers and LED lighting.

HiperPFS-4's advanced power packaging technology and high efficiency simplify the complexity of mounting the IC and thermal management, while providing very high power capabilities in a single compact package; these devices are suitable for PFC applications with maximum continuous power from 75 W to 405 W universal (550 W high-line only).

## **Product Highlights**

#### **Protected Power Factor Correction Solution**

- Incorporates 600 V power MOSFET, controller and gate driver.

- EN61000-3-2 Class C and Class D compliance.

- Integrated protection features reduce external component count

- Accurate built-in brown-in/out protection.

- Accurate built-in undervoltage (UV) protection.

- Accurate built-in overvoltage (OV) protection.

- · Hysteretic thermal shutdown (OTP).

- Internal power limiting function for overload protection.

- Cycle-by-cycle power-switch current limit.

- Internal non-linear error amplifier for enhanced load transient response

- · No external current sense resistor required.

- · Provides 'lossless' internal sensing via sense-FET.

- Reduces component count and system losses.

- · Minimizes high current gate drive loop area.

- Minimizes output overshoot and stresses during start-up

- · Integrated power limit.

- · Improved dynamic response.

- Digitally controlled input line feed-forward gain adjustment for flattened loop gain across entire input voltage range.

- Eliminates up to 39 discrete components for higher reliability and lower cost.

#### Solution for High Efficiency, Low EMI and High PF

- Continuous conduction mode PFC uses novel constant amp-second [on-time] volt-second [off-time] control.

- · High efficiency across load.

- High power factor across load.

- Frequency sliding technique for light load efficiency improvements.

- >95% efficiency from 10% load to full load achievable at nominal input voltages.

- Variable switching frequency to simplify EMI filter design.

- Varies over line input voltage to maximize efficiency and minimize EMI filter requirements.

- Varies with input line cycle voltage by >60 kHz to maximize spread spectrum effect.

#### **Advanced Package for High Power Applications**

- Up to 450 W [universal], 610 W [high-line only] peak output power capability in a highly compact package.

- Simple adhesive or clip mounting to heat sink.

- No insulation pad required and can be directly connected to heat sink.

- Staggered pin arrangement allows simple routing of board traces and to meet high-voltage creepage requirements.

- Single package solution for PFC converter reduces assembly costs and layout size.

#### **Pin Functional Description**

#### **BIAS POWER (VCC) Pin:**

This is a 10.2-15 VDC [12 V typical] bias supply used to power the IC. The bias voltage must be externally clamped to prevent the BIAS POWER pin from exceeding 15 VDC to ensure long-term reliability

#### **REFERENCE (REF) Pin:**

This pin is connected to an external bypass capacitor and is used to program the IC for either FULL or EFFICIENCY power mode. The external capacitor is connected between the REFERENCE and SIGNAL GROUND [G] pins. Note: the return trace to the ground pin must not be shared with other return traces that may pass large return currents during surge events. The REFERENCE pin has two valid capacitor values to select 'Full' (1.0  $\mu F$  ±20%) or 'Efficiency' (0.1  $\mu F$  ±20%) power modes.

## **SIGNAL GROUND (G) Pin:**

Discrete components used in the feedback circuit, including loop compensation, decoupling capacitors for the BIAS POWER (VCC), REFERENCE (REF) and VOLTAGE MONITOR (V) must be referenced to the SIGNAL GROUND (G) pin. The SIGNAL GROUND pin is also connected to the tab of the device. The SIGNAL GROUND pin should not be tied directly to the SOURCE pin external to the IC.

#### **VOLTAGE MONITOR (V) Pin:**

The VOLTAGE MONITOR pin is tied to the rectified high-voltage DC rail through a 100:1, 1% high-impedance resistor divider to minimize power dissipation and standby power consumption. The recommended resistance value is between 8 M $\Omega$  and 16 M $\Omega$ . Changing this divider ratio affects peak power limit, brown-in/out thresholds and will degrade input current quality (reduce power factor and increase THD). A small ceramic capacitor forming an 80  $\mu s$  nominal time-constant must be connected between the VOLTAGE MONITOR pin to the SIGNAL GROUND pin to bypass any switching noise present on the rectified DC bus.

This pin also features brown-in/out detection thresholds and incorporates a weak current source that acts as a pull-down in the event of an open circuit condition.

#### **COMPENSATION (C) Pin:**

This pin is used for loop pole/zero compensation of the OTA error amplifier via the connection of a network of capacitors and a resistor between the COMPENSATION pin and SIGNAL GROUND pin. The COMPENSATION pin connects internally to the output of the OTA error amplifier and the input to the on-time and off-time controllers.

#### FEEDBACK (FB) Pin:

This pin is connected to the main voltage regulation feedback resistor divider network and is also used for fast over and undervoltage protection. This pin also detects the presence of the feedback voltage divider network at start-up and during operation. The divider ratio should be the same as the VOLTAGE MONITOR pin for proper and optimized power limit and power factor. A large upper resistor between 8 M $\Omega$  and 16 M $\Omega$  ±1% is recommended. A small ceramic capacitor between FEEDBACK and SIGNAL GROUND, forming a nominal 80  $\mu s$  time-constant with the bottom resistor, is required.

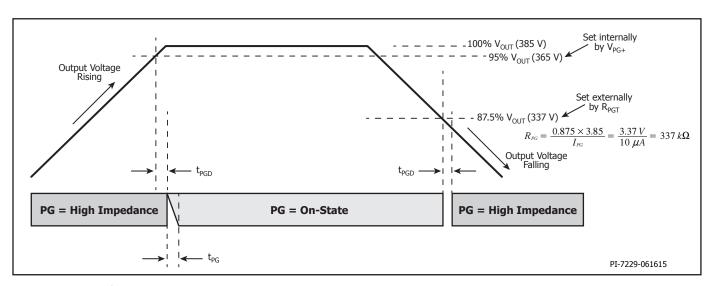

#### **POWER GOOD (PG) Pin:**

Use of the PG function is optional. The POWER GOOD pin is an active low, open-drain connection which sinks current when the output voltage is in regulation. At start-up, once the FEEDBACK pin voltage has risen to  $\sim\!95\%$  of the internal reference voltage, the POWER GOOD pin is asserted low.

After start-up, the output voltage threshold at which the PG signal becomes high-impedance depends on the threshold programmed by the POWER GOOD THRESHOLD pin resistor. When not used, the POWER GOOD pin is left unconnected.

#### **POWER GOOD THRESHOLD (PGT) Pin:**

This pin is used to program the output voltage threshold at which the PG signal becomes high-impedance representing the PFC stage falling out of regulation. The low threshold for the PG signal is programmed with a resistor between the POWER GOOD THRESHOLD and SIGNAL GROUND pins. Tying the POWER GOOD THRESHOLD to the REFERENCE pin disables the power good function (i.e. POWER GOOD pin remains high impedance).

#### **SOURCE (S) Pins:**

These pins are the source connection of the power switch as well as the negative bulk capacitor terminal connection.

#### DRAIN (D) Pin:

This is the drain connection of the internal power switch.

Figure 3. Pin Configuration.

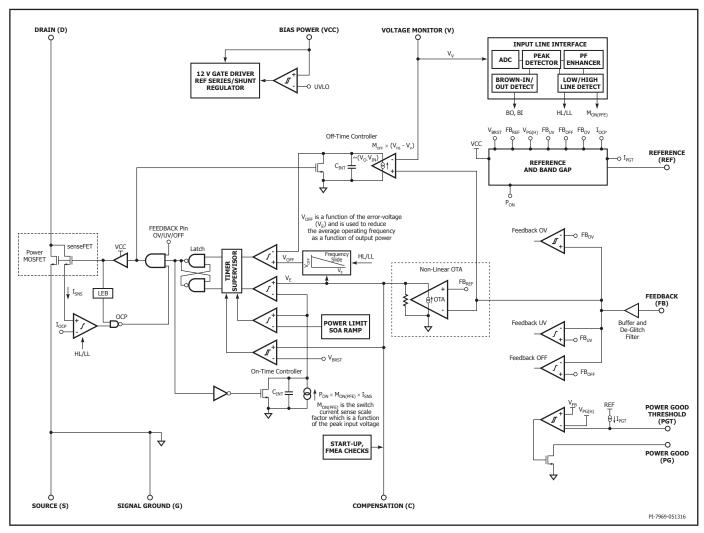

Figure 4. Functional Block Diagram.

## **Functional Description**

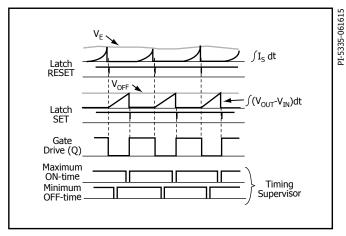

The HiperPFS-4 family are variable switching frequency boost PFC devices. It employs a constant amp-second on-time and constant volt-second off-time control algorithm. This algorithm is used to regulate the output voltage and shape the input current to comply with regulatory harmonic current limits (high power factor). Integrating the switch current and controlling it to have a constant amp-sec product over the on-time of the switch allows the average input current to follow the input voltage. Integrating the difference between the output and input voltage maintains a constant volt-second balance dictated by the electro-magnetic properties of the boost inductor and thus regulates the output voltage and power.

More specifically, the control technique sets constant volt-seconds for the off-time ( $t_{\text{OFF}}$ ). The off-time is controlled such that:

$$(V_O - V_{IN}) \times t_{OFF} = K_1 \tag{1}$$

Since the volt-seconds during the on-time must equal the volt-seconds during the off-time, to maintain flux equilibrium in the PFC choke, the on-time ( $t_{\text{CN}}$ ) is controlled such that

$$V_{IN} \times t_{ON} = K_1 \tag{2}$$

The controller also sets a constant value of charge delivered during each on-cycle of the power MOSFET. The charge per cycle is varied gradually over many switching cycles in response to load changes so it can be considered constant for a half line cycle. With this constant charge (or amp-second) control, the following relationship is therefore also true:

$$I_{IN} \times t_{ON} = K_2 \tag{3}$$

Substituting  $t_{\rm ON}$  from (2) into (3) gives:

$$I_{IN} = V_{IN} \times \frac{K_2}{K_1} \tag{4}$$

The relationship of (4) demonstrates that by controlling a constant amp-second on-time and constant volt-second off-time, the input current  $\mathbf{I}_{\text{IN}}$  is proportional to the input voltage  $\mathbf{V}_{\text{IN}}$ , therefore providing the fundamental requirement of power factor correction.

This control produces a continuous mode power switch current waveform that varies both in frequency and peak current value across a line half-cycle to produce an input current proportional to the input voltage.

#### **Control Engine**

The controller features a low bandwidth, high gain OTA error-amplifier of which its non-inverting terminal is connected to an internal voltage reference of 3.85 V. The inverting terminal of the error-amplifier is available on the external FEEDBACK pin which connects to the output voltage divider network with a divider ratio of 1:100 to regulate the output voltage to 385 V nominally. The FEEDBACK pin connects directly to the divider network for fast transient load response.

The internally sensed FET switch current is scaled by the input voltage peak detector current sense gain  $(M_{\text{ON}})$  then integrated and compared with the error-amplifier signal  $(V_{\text{E}})$  to determine the cycle on-time. Internally the difference between the input and output voltage is derived and the resultant is scaled, integrated, and compared to a voltage reference  $(V_{\text{OFF}})$  to determine the cycle off-time. Careful selection of the internal scaling factors produce input current waveforms with very low distortion and high power factor.

## Line Feed-Forward Scaling Factor ( $\rm M_{\scriptscriptstyle ON})$ and PF Enhancer

The VOLTAGE MONITOR (V) pin voltage is sampled and converted by a  $\Delta\text{-}\Sigma$  ADC to a quantized digital value. A digital line cycle peak detector, with dynamic time constants and multi-cycle filtering, derives and smooths the peak of the input line voltage. This peak is used internally to scale the gain of the current sense signal through the  $M_{\text{ON}}$  variable. This contribution is required to reduce the dynamic range of the control feedback signal as well as flatten the loop gain over the operating input line range. The line-sense feed-forward gain adjustment is proportional to the square of the peak rectified AC line voltage and is adjusted as a function of the VOLTAGE MONITOR pin voltage.

At high-line and light load, the feed-forward  $\rm M_{ON}$  variable is dynamically adjusted across the line cycle in order to compensate for the line current distortion through the EMI filter and full bridge network, and improve power factor.

The line-sense feed-forward gain is also important in providing a switch power limit over the input line range.

Figure 5. Idealized Converter Waveforms.

This characteristic is optimized to maintain a relatively constant internal error-voltage level at full load from an input line of 90 to 230 VAC.

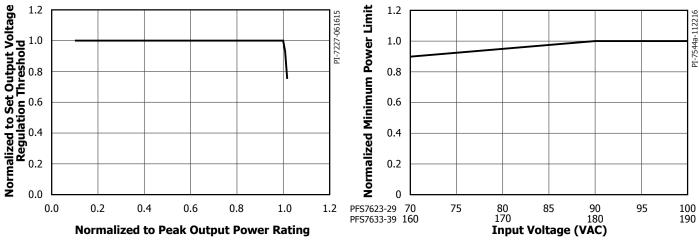

Beyond the specified peak power rating of the device, the internal power limit will regulate the output voltage below the set regulation threshold as a function of output overload to maintain constant output power. Figure 6 illustrates the typical regulation characteristic as a function of load.

Below the brown-in threshold ( $V_{BR+}$ ) the power limit is reduced when the device is operated in the 'Full' power mode as shown in Figure 7. As the input line voltage is reduced toward the brown-out threshold ( $V_{BR}$ ) and if the load exceeds the power limit derating, the boost output voltage will drop out of regulation in accordance with Figure 6.

The rated peak power shown in Table 1 is not derated for voltages below the brown-in threshold when the device is operated in the 'Efficiency' mode.

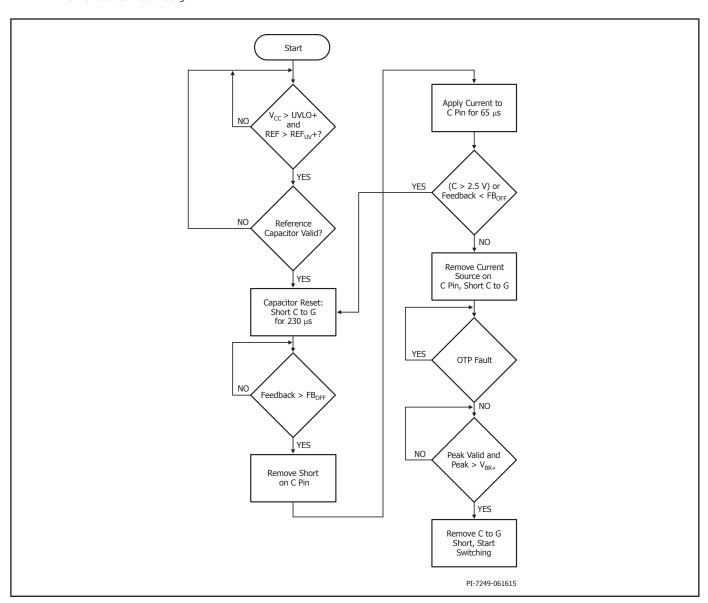

#### Start-Up with Pin-to-Pin Short-Circuit Protection

At start-up, the engine performs a sequence of operational checks and pin short/open evaluations, as shown in Figure 8, prior to the commencement of switching. When the input voltage peak is above brown-in, the engine enables switching.

The OTA error amplifier provides a non-linear amplifier (NLA) mechanism to overcome the inherently slow feedback loop response when the sensed output voltage on the FEEDBACK pin is outside its regulation window. This allows the error amplifier function to limit the maximum overshoot and undershoot during load transient events.

To reduce switch and output diode current stress at start-up, the HiperPFS-4 calculates off-time based upon output voltage ( $V_{\text{OUT}}$ ) during start-up, resulting in a relatively soft controlled start-up.

Once the applied VCC is above the VCC<sub>UVLO+</sub> threshold, and the output of the on-chip  $V_{REF}$  regulator is above REF<sub>UV+</sub>, the value of the REFERENCE pin capacitor is detected and the full or efficiency power mode is latched. The pin open/short tests are performed, and if the FEEDBACK pin voltage is valid the over-temperature OTP is checked to be false. Once the preceding checks are satisfied the input voltage is monitored via the VOLTAGE MONITOR pin until it exceeds the  $V_{\rm BR+}$  threshold [but the peak detector is not saturated]. It is at this point that switching is enabled.

#### **Timing Supervisor and Operating Frequency Range**

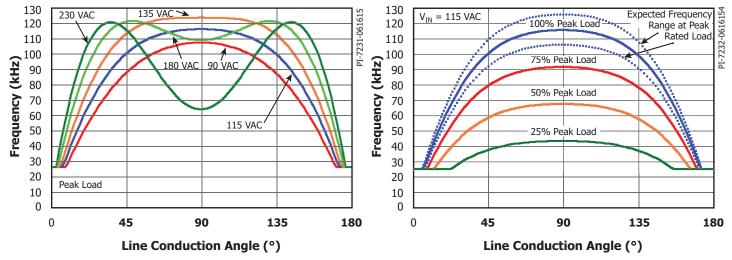

The controller operates with a variable switching frequency over the line frequency half-cycle, typically spanning a range of 22 − 123 kHz when operating in CCM, the controller also features a timing supervisor function which monitors and limits the maximum switch on-time and off-time as well as ensures a minimum cycle on-time. Figure 9(a) shows the typical half-line frequency profile of the device switching frequency as a function of input voltage at peak load conditions. Figure 9(b) shows for a given line condition of 115 VAC, the effect of EcoSmart™ on the switching frequency as a function of load.

Figure 6. Typical Normalized Output Voltage Characteristics as Function of Normalized Peak Load Rating.

Figure 7. Normalized Minimum Power Limit as Function of Input Voltage.

Figure 8. Start-Up Flow Chart.

#### **EcoSmart**

The HiperPFS-4 includes an EcoSmart function wherein the internal error signal (V<sub>E</sub>) is used to detect the converter output power. This sets the average switching frequency as a function of output power.

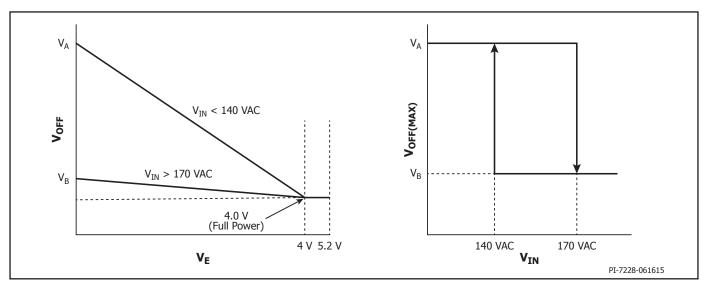

As shown in Figure 10, the off-time integrator control reference (V<sub>OFF</sub>) is controlled with respect to the internal error-voltage level (output power) to allow the converter to maintain output voltage regulation and relatively flat conversion efficiency from 20% to 100% of rated load, which is essential to meet many efficiency directives. The degree of frequency slide is also controlled as a function of input line voltage. The lower  $V_{\mbox{\tiny OFF}}$  slope as a function of input voltage reduces the average frequency extremes for high input line operation.

#### **Burst-Mode for No-Load Power Consumption Reduction**

Under no-load conditions the HiperPFS-4 engine is architected to enter a burst mode which gates the power switch on and off between fixed error voltage levels. This ensures low power consumption by switching in bursts in order to maintain regulation when leakage

currents constitute the majority of the load. Higher output voltage ripple at light load is an artifact of efficient burst mode operation.

### Power Good Signal (PG)

The HiperPFS-4 features a 'power good' (PG) circuit which comprises an internal comparator that turns 'on' an open-drain switch during start-up when the sensed output voltage on the FEEDBACK pin rises to ~95% (V<sub>pG+</sub>) of the output voltage threshold. During start-up, prior to the output voltage reaching V<sub>PG,</sub>, the PG signal is in a high-impedance state (internal switch is in off-state).

The power good signal transitions from 'on' to off-state when the sensed output voltage on the FEEDBACK pin falls to a user selected threshold, programmed via resistor on the POWER GOOD THRESH-OLD (PGT) pin. The POWER GOOD THRESHOLD pin sources a fixed current  $I_{\tiny {\scriptsize PCT}}$ . This current combined with the power good threshold resistor sets the threshold when the power good signal transitions from the on-state to the high-impedance off-state as the PFC output falls out of regulation.

(a) Frequency Variation over Line Half-Cycle as a Function of Input Voltage (b) Frequency Variation over Line Half-Cycle as a Function of Load. Note: Frequency Profiles Shown were Analytically Derived and Reflect CCM Operation Across the Entire Line Cycle.

Figure 10. EcoSmart Frequency Slide  $V_{\rm OFF}$  vs.  $V_{\rm E}$  and  $V_{\rm OFF(MAX)}$  vs. Input Voltage.

The power good comparator has an internal 81  $\mu s$  de-glitch filter (t\_{PGD}) to prevent noise events from falsely triggering the programmed  $V_{PG-}$  threshold.

In the event a load fault prevents the boost from achieving regulation (above  ${\sim}95\%$  of the set output voltage threshold) the PG function will remain in the high-impedance state and will not indicate when an output voltage has fallen below the user programmed  $V_{\text{PG}}$  threshold. The  $V_{\text{PG}}$  user programmed threshold is enabled once the  $V_{\text{PG}}$  threshold has been reached.

If the POWER GOOD THRESHOLD programming pin is tied to REFERENCE pin, the power good function is disabled and PG remains in the high-impedance ('off') state. This is the preferred configuration when PG is not in use. If the POWER GOOD THRESHOLD pin is shorted to the SIGNAL GROUND pin, the PG signal will transition to the on-state at  $V_{\rm PG+}$  and remain low ('on') until the PFC output voltage has fallen below the  $V_{\rm FB\_UV}$  threshold for greater than  $t_{\rm FB\_UV}$  seconds.

Similar to the disable condition described above, if the value of the PGT resistor is such that the  $V_{\text{PG}}$  threshold is greater than the  $V_{\text{PG}}$  threshold, the PG signal will latch off and remain in the high-impedance off-state.

The Power Good function is not valid under the following conditions:

- A. VCC or VREF are not in a valid range of operation. VCC below UVLOor VREF below REF<sub>UV</sub>. the power good function is not valid with the POWER GOOD pin in a high-impedance state.

- B. Power Good will go to high-impedance state when a soft shutdown is initiated by an over-temperature fault to provide early indication to secondary circuits of an OT fault.

- C. PGT is outside the valid programming range of between 225 V and 360 V. PGT voltages above this range, including PGT floating, will prevent PG from transitionning to active pull-down. PGT voltages below this range result in PG deassertion at the output undervoltage ( $V_{\text{FB IV}}$ ) threshold.

- D. Once the start-up sequence check has passed and the converter goes into start-up, if PGT is opened, then the PG signal will remain latched in the high-impedance state until the controller is reset.

#### **Selectable Power Limit**

The capacitor on the REFERENCE pin allows user selection between 'full' and 'efficiency' power limit for each device. The 'efficiency' power mode will permit user selection of a larger device for a given output power requirement for increased conversion efficiency.

In 'full' power mode the REFERENCE pin capacitor is 1.0  $\mu F$  ±20% and the 'efficiency' power limit mode is selected with a 0.1  $\mu F$  ±20% capacitor.

If the REFERENCE pin is accidentally shorted to ground, the IC will disable switching and remain disabled until all conditions for the start-up sequence are satisfied..

If the REFERENCE pin is open-circuit, the absence of a bypass capacitor will prevent start-up. During operation, an open-circuit may result in enough REFERENCE pin noise to result in a VREF REF<sub>INC</sub> shutdown.

#### **Protection Modes**

## Brown-In Protection (V<sub>BR+</sub>)

The VOLTAGE MONITOR pin has an input line undervoltage detection to limit the minimum start-up voltage. This detection threshold will inhibit the device from starting at input voltages below brown-in and above input peak voltages of 400  $V_{\rm pc}$ .

## **Brown-Out Protection (V<sub>BR-</sub>)**

The VOLTAGE MONITOR pin features a brown-out protection mode wherein the HiperPFS-4 will turn-off when the VOLTAGE MONITOR pin voltage is below the line undervoltage threshold (VBR-) for a period exceeding  $t_{\text{BRWN\_OUT}}$  (brown-out debounce period). In the event a single half-line cycle is missing (normal operating line frequency is 47 Hz to 63 Hz) the brown-out detection will not be initiated. Once brown-out has been triggered, the HiperPFS-4 soft-shutdown gradually reduces the internal error-voltage to zero volts over a period of 1 ms to ramp the power MOSFET on-time to zero. The onset of this soft-shutdown is aligned to the next line cycle zero crossing to minimize reactive component di/dt transients and allow time for the energy stored within the boost choke as well as the input EMI filter to dissipate. This helps minimize voltage transients after the bridge rectifier, which helps to prevent false restarts. The device will enter

Figure 11. Power Good Function Description.

an auto-restart, including FMEA pin fault checks and other start-up qualifications prior to checking for the line voltage being above the brown-in voltage by virtue of the VOLTAGE MONITOR pin being above  $V_{\tiny{BDL}}$ .

After a brown-in event, until after the  $t_{STARTUP}$  timer has expired, the line voltage brown-out threshold is reduced to  $V_{BR-NTC}$  and the brown-out timer is extended to  $t_{BRWN\_OUT\_NTC}$  to allow for the drop in line voltage due to an in-rush limiting negative temperature coefficient (NTC) thermistor in series with the input line.

If the  $t_{BRWN\_OUT\_NTC}$  debounce timer is triggered by the sensed line voltage dropping below the  $V_{BR-NTC}$  threshold but the line voltage recovers to above the  $V_{BR-NTC}$  threshold before the  $t_{BRWN\_OUT\_NTC}$  expires, then the  $t_{STARTUP}$  timer will be re-started. If the line does not recover above the  $V_{BR-NTC}$  threshold before the  $t_{BRWN\_OUT\_NTC}$  debounce timer expires a shutdown will occur.

After the  $t_{\text{STARTUP}}$  timer has expired, if the VOLTAGE MONITOR pin voltage rises above  $V_{\text{BR-NTC}}$ , the brown-out debounce timer will switch to normal period  $(t_{\text{BRWN\_OUT}})$  and the brown-out threshold will switch to  $V_{\text{BR}}$ . If the VOLTAGE MONITOR pin voltage is not qualified above  $V_{\text{BR}}$  after the subsequent  $t_{\text{BRWN\_OUT}}$  timer has expired then a brown-out shutdown will occur.

HiperPFS-4 incorporates input waveform discrimination to determine if the line signal peak-to-average ratio is more representative of a sine wave or a high duty cycle square wave. The brown-out threshold is reduced to  $V_{\mbox{\scriptsize BR\_SQ}}$  when a high duty cycle (UPS) square wave is detected.

#### VCC Undervoltage Protection (UVLO)

The BIAS POWER (VCC) pin has an undervoltage lock-out protection which inhibits the IC from starting unless the applied VCC voltage is above the VCC  $_{\mbox{\tiny UVLO+}}$  threshold. The IC initiates a start-up once the BIAS POWER pin voltage exceeds the VCC  $_{\mbox{\tiny UVLO+}}$  threshold. After start-up the IC will continue to operate until the BIAS POWER pin voltage has fallen below the VCC  $_{\mbox{\tiny UVLO-}}$  level. The absolute maximum voltage on the BIAS POWER pin is 17.5 V which must be externally limited to prevent long term damage to the IC.

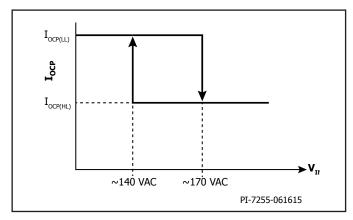

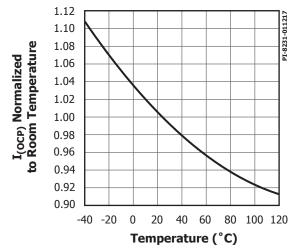

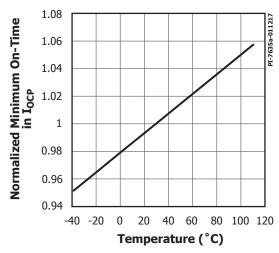

#### Line Dependent Over Current Protection (OCP) limit

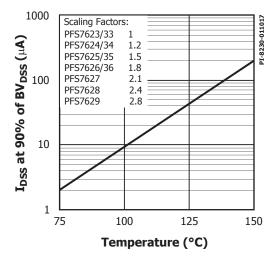

The device includes a cycle-by-cycle over-current protection mechanism which protects the device in the event of a fault. The intent of OCP protection in this device is protection of the internal power MOSFET and is not specifically intended to protect the converter from output short-circuit or overload fault conditions.

For universal line input parts, the OCP limit is set as a function of the input line voltage, one setting for low-line voltages and another setting for high-line voltages. This helps to bound power limit into short-circuits as well as helps to minimize the stress on the switch due to current overloads at higher input line conditions. Figure 12 illustrates the hysteretic adjustment of the OCP levels as a function of VOLTAGE MONITOR pin line-sensing. This equates to selecting the low-line OCP (the greater of the two settings) when the peak of the input line voltage drops below 140 VAC for 3 consecutive half-cycles and selecting the high-line OCP level (the lesser of the two settings) when the input line voltage rises above 170 VAC for 1 half-cycle, (except in follower mode, as described in the subsequent sections).

The HiperPFS-4 utilizes a high input line OCP after detecting the VOLTAGE MONITOR pin above the high-line threshold,  $V_{\rm HIGH+}$ . The controller reverts back to low-line OCP (as well as low-line frequency slide) only after 3 consecutive half-line cycle peak values that are

Figure 12. Line Dependent OCP.

below the low-line threshold  $V_{\rm HIGH}$ . In the event of a line drop-out, the controller may revert from high-line to low-line parameters if the drop-out exceeds 37 ms (nominal). High-line only input parts use a single fixed OCP threshold.

A follower-mode feature updates the controller to high-line status rapidly, as soon as the input voltage exceeds  $V_{\mbox{\tiny HIGH+}}$ . This feature has particular benefit for high-line hard-start conditions after a long AC line drop-out where the peak detector may initially indicate a low input line condition.

A leading edge blanking circuit inhibits the current limit comparator for a short time ( $t_{\text{LEB}}$ ) after the power MOSFET is turned on. This leading edge blanking time is set so that switch current spikes caused by drain capacitance and rectifier reverse recovery time will not cause premature termination of the MOSFET conduction period.

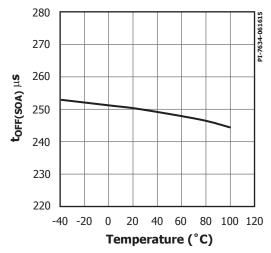

#### Safe Operating Area (SOA) Mode

Since the cycle-by-cycle OCP mechanism described above does not prevent the possibility of inductor current 'stair-casing', an SOA mode is also featured. Rapid build-up of the switch current can occur in the event of inductor saturation or when the input and output voltage differential is small combined with too little inductor reset time.

The SOA mode is triggered whenever the switch current reaches current limit ( $I_{\text{OCP}}$ ) and the on-time is less than  $t_{\text{SOA}}$ . The SOA mode forces an off-time equal to  $t_{\text{OFF}(\text{SOA})}$  and pulls the internal error-voltage ( $V_{\text{E}}$ ) down by 1/2 of its maximum value in order to ensure the switch remains within its SOA.

## Fast Output Voltage Overvoltage Protection (FB<sub>ov</sub>)

The HiperPFS-4 features a voltage feedback threshold comparator on the FEEDBACK pin which detects an output voltage overvoltage condition to allow rapid response, independent of the COMPENSATION pin response, to prevent hazardous voltage conditions from occurring. The overvoltage protection is hysteretic – the voltage on the FEEDBACK pin must drop by 0.1 V (equating to an output voltage drop of 10 V) before switching is re-started.

#### **FEEDBACK to COMPENSATION Pin Short Detection Safeguard**

The PFC controller continuously monitors the FEEDBACK and COMPENSATION pins to ensure that there are no potential short conditions between the adjacent FEEDBACK and COMPENSATION pins, which could result in output overvoltage conditions if not detected. In the event a potential short is detected, a rapid short check is performed and a shutdown is executed in the event that a suspected short is validated.

## PFS7623-7629/7633-7636

#### **Open FEEDBACK Pin Protection**

The FEEDBACK pin continuously sinks a static current of  $I_{\text{FBPD}}$  [VCC >VCC $_{\text{UVLO}+}$ ] to protect against a fault related to an open FEEDBACK pin or incomplete feedback divider network. The internal current sink introduces a small static offset to the output regulation which can be accounted for in selecting the output feedback regulation components (FEEDBACK pin divider).

#### **Hysteretic Thermal Shutdown**

The thermal shutdown circuit senses the controller die temperature which is well coupled to the heat sink through the exposed, grounded pad. The threshold is set at 117 °C typical with a 36 °C hysteresis. When the controller die temperature rises above this threshold (OTP), the controller initiates a soft-shutdown and remains disabled until the controller die temperature falls by  $\sim$ 36 °C, at which point the device will re-initiate the start-up sequence.

The maximum time delay for soft-shutdown to occur after an OTP event is detected is  $t_{\text{orp}}$  beyond the next zero-crossing.

## **HiperPFS-4 Additional Features and Changes**

HiperPFS-4 maintained similar pin-out as HiperPFS-3 except for pin 16, which is not connected.

- The breakdown voltage rating of the PFC MOSFET has been increased to 600 V.

- PFC diode has been removed to reduce the HiperPFS-4 case temperature.

- PFC output voltage can be designed for up to 440 VDC output to allow operation with 277 VAC line voltage.

#### **Output Power Table**

|            | eSIP Package                                                          |                 |                                                    |                      |                                                |                                                    |  |  |  |  |  |  |

|------------|-----------------------------------------------------------------------|-----------------|----------------------------------------------------|----------------------|------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|

|            | Effici                                                                | II Power Mode C | C <sub>REF</sub> = 1.0 μF                          |                      |                                                |                                                    |  |  |  |  |  |  |

| Product    | Product Maximum Continuous Output Power Rating at 90 VAC <sup>2</sup> |                 | Peak Output Power<br>Rating at 90 VAC <sup>4</sup> | Output Pow           | Continuous<br>er Rating at<br>/AC <sup>2</sup> | Peak Output Power<br>Rating at 90 VAC <sup>4</sup> |  |  |  |  |  |  |

|            | Minimum <sup>3</sup>                                                  | Maximum         |                                                    | Minimum <sup>3</sup> | Maximum                                        |                                                    |  |  |  |  |  |  |

| PFS7623H/L | 65 W                                                                  | 90 W            | 100 W                                              | 85 W                 | 110 W                                          | 120 W                                              |  |  |  |  |  |  |

| PFS7624H/L | 80 W                                                                  | 110 W           | 125 W                                              | 100 W                | 130 W                                          | 150 W                                              |  |  |  |  |  |  |

| PFS7625H/L | 110 W                                                                 | 150 W           | 170 W                                              | 140 W                | 185 W                                          | 205 W                                              |  |  |  |  |  |  |

| PFS7626H/L | 140 W                                                                 | 190 W           | 215 W                                              | 180 W                | 230 W                                          | 260 W                                              |  |  |  |  |  |  |

| PFS7627H/L | 175 W                                                                 | 235 W           | 265 W                                              | 220 W                | 290 W                                          | 320 W                                              |  |  |  |  |  |  |

| PFS7628H/L | 210 W                                                                 | 285 W           | 320 W                                              | 270 W                | 350 W                                          | 385 W                                              |  |  |  |  |  |  |

| PFS7629H/L | 245 W                                                                 | 335 W           | 375 W                                              | 300 W                | 405 W                                          | 450 W                                              |  |  |  |  |  |  |

|          | Effici               | ency Power Mod                                  | de C <sub>REF</sub> = 0.1 μF                        | Full Power Mode $C_{REF} = 1.0 \mu F$ |         |                                                     |  |  |  |

|----------|----------------------|-------------------------------------------------|-----------------------------------------------------|---------------------------------------|---------|-----------------------------------------------------|--|--|--|

| Product  | Output Pow           | Continuous<br>ver Rating at<br>VAC <sup>2</sup> | Peak Output Power<br>Rating at 180 VAC <sup>4</sup> |                                       |         | Peak Output Power<br>Rating at 180 VAC <sup>4</sup> |  |  |  |

|          | Minimum <sup>3</sup> | Maximum                                         |                                                     | Minimum <sup>3</sup>                  | Maximum |                                                     |  |  |  |

| PFS7633H | 155 W                | 205 W                                           | 230 W                                               | 195 W                                 | 255 W   | 280 W                                               |  |  |  |

| PFS7634H | 200 W                | 260 W                                           | 290 W                                               | 240 W                                 | 315 W   | 350 W                                               |  |  |  |

| PFS7635H | 275 W                | 360 W                                           | 400 W                                               | 335 W                                 | 435 W   | 480 W                                               |  |  |  |

| PFS7636H | 350 W                | 460 W                                           | 510 W                                               | 415 W                                 | 550 W   | 610 W                                               |  |  |  |

Table 2. Output Power Table.

Notes:

- 1. See Key Application considerations.

- 2. Maximum practical continuous power in an open-frame design with adequate heat sinking, measured at 50 °C ambient.

- 3. Recommended "efficiency power mode" for **best light load efficiency**.

- 4. Internal output power limit.

#### **Application Example**

## A High Efficiency, 275 W, 385 VDC Universal Input PFC

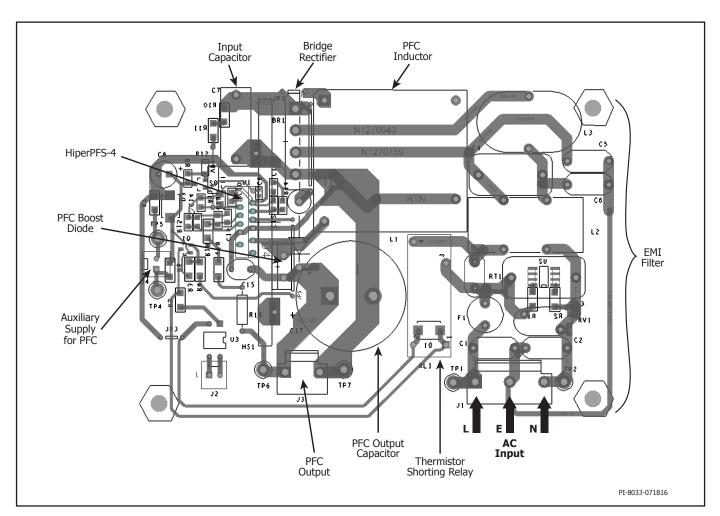

The circuit shown in Figure 13 is designed using a device from the HiperPFS-4 family of integrated PFC controllers. This design is rated for a continuous output power of 275 W and provides a regulated output voltage of 385 VDC nominal, maintaining a high input power factor and overall efficiency from light load to full load.

Fuse F1 provides protection to the circuit and isolates it from the AC supply in the event of a fault. Diode bridge BR1 rectifies the AC input voltage. Capacitors C1-C7 together with inductors L2 and L3 form the EMI filter which reduces the common mode and differential mode noise. Resistors R1, R2 and CAPZero-2, IC U2 are required to discharge the EMI filter capacitors once the circuit is disconnected. CAPZero-2 eliminates static losses in R1 and R2 by only connecting these components across the input when AC is removed.

Metal oxide varistor (MOV) RV1 protects the circuit during line surge events by effectively clamping the input voltage seen by the power supply.

Inductor L1 and boost diode D4 in conjunction with HiperPFS-4 IC U1, form the boost converter stage, controlling the input current of the power supply while simultaneously regulating the output DC voltage. Diode D2 prevents a resonant buildup of output voltage at start-up by bypassing inductor L1 while simultaneously charging output capacitor C18.

Thermistor RT1 limits the inrush input current of the circuit at start-up and prevents saturation of L1. However in the highest efficiency designs, an electro-mechanical relay RL1 will be used to bypass the thermistor once the output voltage is in regulation as indicated by a power good signal (asserted low). Resistors R3 and R4, and transistor Q1, drive relay RL1 and optocoupler U3. Diode D1 clamps the relay

coil reverse voltage during de-assertion transitions. Resistor R5 limits the current to the diode in the optocoupler. IC U3 provides optocoupler isolation through connector J2 for a power-good output signal if required.

Capacitor C15 is used for reducing the loop length and area of the output circuit to reduce EMI and overshoot of voltage across the drain and source of the MOSFET inside U1 at each switching edge.

The PFS7627H IC requires a regulated supply of 12 V for operation (15 V max). Resistors R6, R7, R8, Zener diode VR1, and transistor Q2 form a series pass regulator that prevents the supply voltage to IC U1 from exceeding 15 V. Capacitors C8, and C9 filter the supply voltage and provide bypassing and decoupling to ensure reliable operation of IC U1. Diode D3 provides reverse polarity protection.

Resistor R15 programs the output voltage level [via the POWER GOOD THRESHOLD (PGT) pin] below which the POWER GOOD [PG] pin will go into a high-impedance state. Capacitor C14 provides noise immunity on the POWER GOOD THRESHOLD pin.

IC U1 is configured in full power mode by capacitor C10 which is connected to the REFERENCE pin.

The rectified AC input voltage of the power supply is sensed by IC U1 using resistors R10-R13. These resistors values are large to minimize power consumption. Capacitor C11 connected in parallel with the bottom resistor R13 filters noise coupled into the VOLTAGE MONITOR pin.

Output voltage divider network comprising resistors R16 - R19 are used to scale the output voltage and provide feedback to the IC. Capacitor C16 in parallel with resistor R19 attenuates high frequency noise.

Components R14, C12 and C13 are required for shaping the loop response of the feedback network.

Figure 13. 275 W PFC using PFS7627H.

## **Design, Assembly, and Layout Considerations**

#### **Power Table**

The data sheet power table as shown in Table 2 represents the maximum practical continuous output power based on the following conditions:

For the universal input devices (PFS7623L/H - PFS7629H):

- 1. An input voltage range of 90 VAC to 264 VAC.

- 2. Overall efficiency of at least 93% at the lowest operating voltage.

- 3. 385 V nominal output.

- Sufficient heat sinking to keep device temperature ≤100 °C.

Operation beyond the limits stated above will require de-rating. Operation at elevated temperatures could result in reduced MTBF and performance degradation, e.g. reduced efficiency, reduced power limit, PF, and potential of observing hysteretic brown-out, etc., and is not recommended.

#### **HiperPFS-4 Selection**

Selection of the optimum HiperPFS-4 part depends on required maximum output power, PFC efficiency and overall system efficiency (when used with a second stage DC-DC converter), heat sinking constraints, system requirements and cost goals. The HiperPFS-4 part used in a design can be easily replaced with the next higher or lower part in the power table to optimize performance, improve efficiency or for applications where there are thermal design constraints. Minor adjustments to the inductance value and EMI filter components may be necessary in some designs when the next higher or the next lower HiperPFS-4 part is used in an existing design for performance optimization.

Every HiperPFS-4 family part has an optimal load level where it offers the most value. Operating frequency of a part will change depending on load level. Change of frequency will result in change in peak to peak current ripple in the inductance used. Change in current ripple will affect input PF and total harmonic distortion of input current.

#### **Input Fuse and Protection Circuit**

The input fuse should be rated for a continuous current above the input current at which the PFC turns-off due to input undervoltage. This voltage is referred to as the brown-out voltage.

The fuse should also have sufficient I2t rating in order to avoid nuisance failures during start-up. At start-up a large current is drawn from the input as the output capacitor charges to the peak of the applied voltage. The charging current is only limited by any inrush limiting thermistors, impedance of the EMI filter inductors and the forward resistance of the input rectifier diodes. A MOV will typically be required to protect the PFC from line surges. Selection of the MOV rating will depend on the energy level (EN1000-4-5 Class level) which the PFC is required to withstand.

A suitable NTC thermistor should be used on the input side to provide inrush current limiting. Choice of this thermistor should depend on the inrush current specification for the power supply. NTC thermistors may not be placed in any other location in the circuit as they fail to limit the stress on the part in the event of line transients and also fail to limit the inrush current in a predictable manner. The example in Figure 13 shows the circuit configuration that has the inrush limiting NTC thermistor on the input side which is bypassed with a relay after PFC start-up. This arrangement ensures that a consistent inrush limiting performance is achieved by the circuit.

#### **Input EMI Filter**

The variable switching frequency of the HiperPFS-4 effectively modulates the switching frequency and reduces conducted EMI peaks associated with the harmonics of the fundamental switching frequency.

This is particularly beneficial for the average detection mode used in EMI measurements.

The PFC is a switching converter and will need an EMI filter at the input in order to meet the requirements of most safety agency standards for conducted and radiated EMI. Typically a common mode filter with X capacitors connected across the line will provide the required attenuation of high frequency components of input current to an acceptable level. The leakage reactance of the common mode filter inductor and the X capacitors form a low pass filter. In some designs, additional differential filter inductors may have to be used to supplement the differential mode inductance of the commonmode choke.

A filter capacitor with low ESR and high ripple current capability should be connected at the output of the input bridge rectifier. This capacitor reduces the generation of the switching frequency components of the input current ripple and simplifies EMI filter design. Typically, 0.33  $\mu F$  per 100 W should be used for universal input designs and 0.15  $\mu F$  per 100 W of output power should be used for 230 VAC only designs.

It is often possible to use a higher value of capacitance after the bridge rectifier and reduce the X capacitance in the EMI filter.

For applications where PF at light load is important, be aware that all capacitors prior to the boost stage are not corrected for PF and thus the larger the capacitor value may degrade PF performance at light load

Regulatory requirements require use of a discharge resistor to be connected across the input X capacitance on the AC side of the bridge rectifier. This is to ensure that residual charge is dissipated after the input voltage is removed when the capacitance is higher than 0.1  $\mu\text{F}.$  Use of CAPZero-2 integrated circuits from Power Integrations, helps eliminate the steady-state losses associated with the use of discharge resistors connected permanently across the X capacitors.

#### **Inductor Design**

For ferrite inductors the optimal design has  $K_{\rm p}$  of 0.3 to 0.45. ( $K_{\rm p}$  is defined as the current peak-to-peak value divided by the peak value at minimum AC voltage and 90° phase angle, full load).  $K_{\rm p}$  <0.3 (more continuous) tends towards excessive inductor size, while higher  $K_{\rm p}$  >0.45 tends towards excessive winding AC resistance losses due to large high-frequency AC currents, especially since most ferrite inductor designs will require >3 winding layers. Flux density at maximum current limit should be <3900 gauss to prevent core saturation.

If Sendust core material is used, 90m or 125m material is recommended, because the higher m materials tend to produce greater inductance at lower currents, and thus reduced peak-to-peak inductor currents at lower line phase angles (<45°) which reduces losses and improves PF at lighter loads and higher input voltages. The design target is for H at the peak current (low-line, full-load, 90° line phase angle) to be  $\sim$ 60 A-t/cm. Higher H tends towards excessive core loss, and lower than this increases AC copper losses.

For high performance designs, use of Litz wire is recommended to reduce copper loss due to skin effect and proximity effect. For toroidal inductors the numbers of layers should be less than 3 and for bobbin wound inductors, inter layer insulation should be used to minimize inter layer capacitance.

The HiperPFS-4 design spreadsheet simplifies this process and automatically recommends a core size and design for either ferrite or Sendust.

#### **Output Diode**

For a 385 V nominal PFC output voltage, use of a diode with 600 V or higher PIV rating is recommended. CCM operation with hard switching demands that diodes with low reverse recovery time and reverse recovery charge should be used. The variable frequency CCM operation of HiperPFS-4 reduces diode switching losses as compared to fixed frequency solutions and use of readily available high frequency diodes (such as Qspeed diode family from Power Integrations), with soft recovery characteristics that result in a reduced EMI. For highly demanding applications such as 80 PLUS Gold power supplies, use of Silicon Carbide diodes may be considered. These uses will typically provide further full load improvement in efficiency.

Selected diodes should have a forward continuous current rating of at least 1.2 A to 1.5 A for every 100 W of output power.

#### **Output Capacitor**

For a 385 V nominal PFC output voltage, use of an electrolytic capacitor with 450 V or higher continuous rating is recommended. The capacitance required is dependent on the acceptable level of output ripple and any hold up time requirements. The equations below provide an easy way to determine the required capacitance in order to meet the hold-up time requirement and also to meet the output ripple require- ments. The higher of the two values would be required to be used.

The capacitance required for meeting hold-up time requirements is calculated using the equation:

$$C_o = \frac{2 \times P_{OUT} \times t_{HOLD\_UP}}{V_{OUT}^2 - V_{OUT(MIN)}^2}$$

PFC output capacitance in farads.

PFC output power in watts.

Hold-up time specification for the power supply  $\mathsf{t}_{\scriptscriptstyle{\mathsf{HOLD-UP}}}$

in seconds.

${\rm V}_{\rm out}$ Lowest nominal output voltage of the PFC in volts.  $V_{OUT(MIN)}$ Lowest permissible output voltage of the PFC at

the end of hold-up time in volts.

The capacitance required for meeting the low frequency ripple specification is calculated using the equation:

$$C_{o} = \frac{I_{O(MAX)}}{2 \times \pi \times f_{L} \times \Delta V_{o} \times \eta_{PFC}}$$

$f_L \\ \Delta V_O$ Input frequency in Hz.

Peak-peak output voltage ripple in volts.

PFC operating efficiency.  $\eta_{\text{PFC}}$

Maximum output current in amps.  $I_{O(MAX)}$

The capacitance calculated using the above method should be appropriately increased to account for ageing and tolerances.

#### **Power Supply for the IC**

A 12 V regulated supply should be used for the HiperPFS-4. If the VCC exceeds 15 V, the HiperPFS-4 may be damaged. In most applications a simple series pass linear regulator made using an NPN transistor and Zener diode is adequate since the HiperPFS-4 only requires approximately  $\boldsymbol{I}_{\text{CC(ON)}}$  maximum for its operation.

It is recommended that a 1  $\mu$ F or larger, low ESR ceramic capacitor be used to decouple the VCC supply. This capacitor should be placed directly at the IC pin on the circuit board.

#### **Line-Sense Network**

The line-sense network connected to the VOLTAGE MONITOR pin provides input voltage information to the HiperPFS-4. A value of 16 M $\Omega$ is chosen in this example design to minimize power consumption in these resistors. Only 1% or better tolerance resistors are recommended.

A decoupling capacitor of 470 pF forming an 80 ms time constant is required to be connected in parallel with the bottom resistor from the VOLTAGE MONITOR pin to the GROUND pin of the HiperPFS-4. If the impedance of the resistor divider is different than that shown in the example schematic, Figure 13, the decoupling capacitor value must also be changed to maintain the 80 µs time constant. This capacitor should be placed directly at the IC pin on the circuit board.

#### **Feedback Network**

A resistor divider network that provides 3.85 V at the FEEDBACK pin at the rated output voltage should be used for optimal performance. It should be scaled in direct proportion to the VOLTAGE MONITOR pin resistor divider network in order to ensure proper regulation and power delivery. The HiperPFS-4 controller has been optimized for operation with an output voltage of 385 VDC. Applications requiring voltages that deviate from this nominal parameter, thereby requiring a FEEDBACK pin divider ratio other than the recommended 100:1, need to be evaluated for trade-offs of the key target parameters of the specific design. E.g.: the VOLTAGE MONITOR pin divider ratio should be modified to be equivalent to that of the feedback divider in order to optimize power factor. However, this will have an impact on power limit, as well as brown-in/brown-out thresholds, etc. Modification of FEEDBACK and VOLTAGE MONITOR pin resistor divider ratios within 2.5% of nominal should not result in dramatically compromised performance, but should be thoroughly verified. Changes in excess of this are not recommended. Itemized trade-offs of this type are outside the scope of this data sheet.

Please refer to DER-547 as a design example with 440 V output voltage and 100-300 VAC input voltage. When addressing higher input voltage designs such as 277 VAC, the output voltage of the PFC needs to be increased to optimize the performance. If the FEEDBACK pin resistor divider ratio is changed for higher output voltages, ensure FEEDBACK and VOLTAGE pin resistor divider ratios are matched. Also be aware that the brown-in/out will also increase as a result of VOLTAGE pin resistor divider ratio change. Refer to DER-547 report for more details.

Voltage de-rating requirements for the power MOSFET, boost diode, and all design choices should be validated with bench tests.

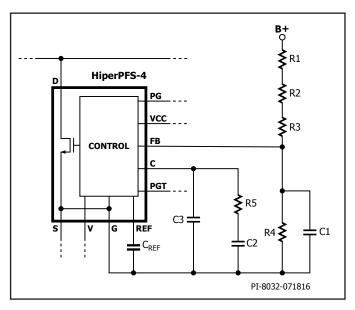

The recommended circuit is shown in Figure 14.

Figure 14. Recommended Feedback Circuit.

## PFS7623-7629/7633-7636

Resistors, R1 to R4 comprise of the main output voltage divider network. The sum of resistors R1, R2 and R3 is the upper divider resistor and the lower feedback resistor is R4. Capacitor C1 is to filter any switching noise from coupling into the FEEDBACK pin. Resistor R5, capacitor C2 and C3 is the loop compensation network required to tailor the loop response to ensure low cross-over frequency and sufficient phase margin. The recommended values for the components used are as follows:

$R1 = 3.74 M\Omega$

$R2 = 6.2 M\Omega$

$R3 = 6.2 M\Omega$

$R5 = 30.1 \text{ k}\Omega$

C1 = 470 pF

C1 = 170 pr $C2 = 1 \mu\text{F}$

C3 = 100 nF

When the above component values are used, the value of resistor R4 can be calculated using the equation below:

$$R_4 = \frac{(R_1 + R_2 + R_3)}{\left(\frac{V_O}{V_{FB(REF)}} - 1\right)}$$

V<sub>o</sub> Output voltage.

V<sub>FB(RFF)</sub> FEEDBACK pin voltage, 3.85 V.

The value of resistor R5 will have to be adjusted in some designs and as a guideline the value from the following calculation can be used:

$$R_5 = R_Z = \frac{P_O}{0.3 \times V_O^2 \times C_O} (k\Omega)$$

P<sub>o</sub> Maximum continuous output power in watts.

V<sub>0</sub> Nominal PFC output voltage in volts.

C<sub>0</sub> PFC output capacitance in farads.

## **Heat Sinking and Thermal Design**

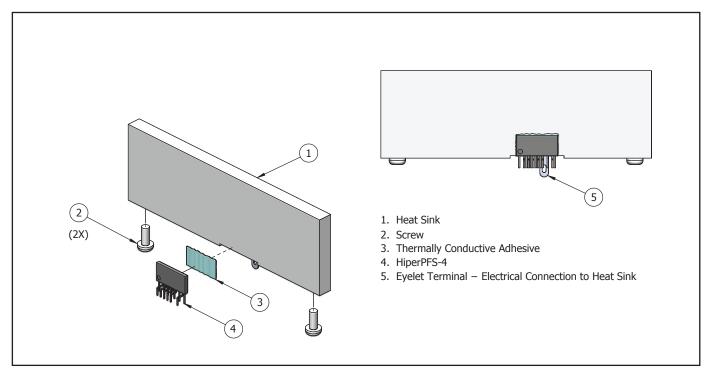

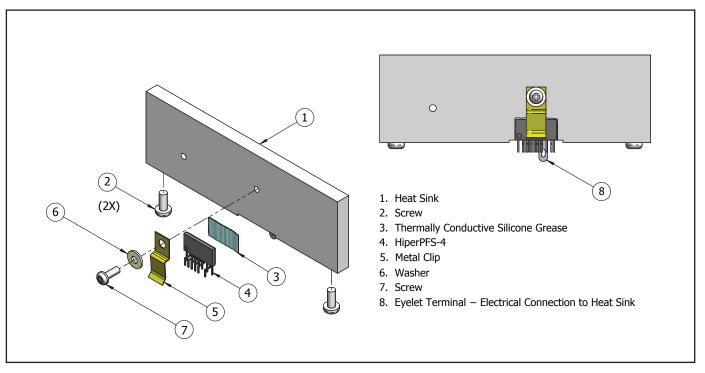

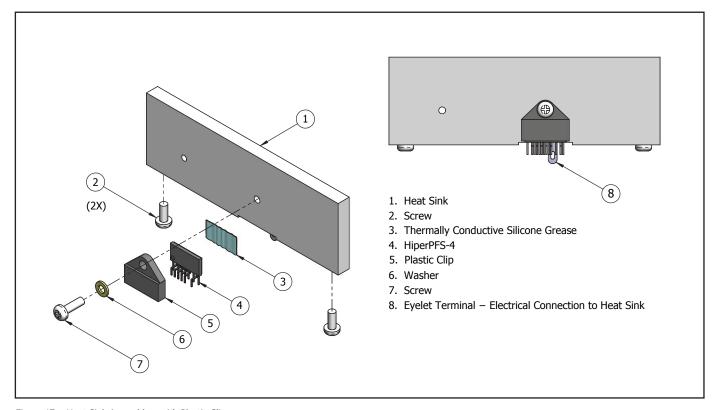

Figures 15, 16, 17 show an example of the recommended assembly for the HiperPFS-4. In this assembly, no insulation pad is required and HiperPFS-4 can be directly connected to the heat sink by mechanical clip or adhesive thermal compound.

It is required, on the PCB, that the heat sink is connected to the HiperPFS-4 source terminal in order to reduce EMI and optimize operation.

Figure 15. Heat Sink Assembly – using Thermally Conductive Adhesive.

Figure 16. Heat Sink Assembly – with Metal Clip.

Figure 17. Heat Sink Assembly – with Plastic Clip.

#### **PCB Design Guidelines and Design Example**

The line-sense network and the feedback circuit use large resistance values in order to minimize power dissipation in the feedback network and the line-sense network. Care should be taken to place the feedback circuit and the line-sense network components away from the high-voltage and high current nodes to minimize any interference. Any noise injected in the feedback network or the line-sense network will typically manifest as degradation of power factor. Excessive noise injection can lead to waveform instability or dissymmetry.

The EMI filter components should be clustered together to improve filter effectiveness. The placement of the EMI filter components on the circuit board should be such that the input circuit is located away from the drain node of the PFC inductor.

A filter or decoupling capacitor should be placed at the output of the bridge rectifier. This capacitor together with the X capacitance in the EMI filter and the differential inductance of the EMI filter section and the source impedance, works as a filter to reduce the switching frequency current ripple in the input current. This capacitor also helps to minimize the loop area of the switching frequency current loop thereby reducing EMI.

The connection between the HiperPFS-4 drain node, output diode drain terminal and the PFC inductor should be kept as short as possible.

A low loss ceramic dielectric capacitor should be connected between the cathode of the PFC output diode and the source terminal of the HiperPFS-4 IC. This ensures that the loop area of the loop carrying high frequency currents at the transition of the MOSFET and helps to reduce radiated EMI due to the high frequency pulsating nature of the diode current traversing through the loop.

During placement of components on the board, it is best to place the voltage monitor, feedback, reference and bias power decoupling capacitors as close as possible to the pins before the other components are placed and routed. REFERENCE pin decoupling capacitor needs to have dedicated return path to GROUND pin. Failing to do so could reduce the noise immunity during surge and ESD test. Power supply return trace from the GROUND pin should be separate from the trace connecting the feedback circuit components to the GROUND pin.

To minimize the effects of trace impedance on regulation, output feedback should be taken directly from the output capacitor positive terminal. The upper end of the line-sense resistors should be connected to the high frequency filter capacitor connected at the output of the bridge rectifier.

Figure 18. PCB Layout Example.

## **Quick Design Checklist**

As with any power supply design, all HiperPFS-4 family designs should be verified on the bench to make sure that component specifications are not exceeded under worst-case conditions. The following minimum set of tests is strongly recommended:

- Maximum drain voltage Verify that peak VDS does not exceed 600 V at lowest input voltage and maximum overload output power. Maximum overload output power occurs when the output is overloaded to a level just above the highest rated load or before the power supply output voltage starts falling out of regulation. Additional external snubbers should be used if this voltage is exceeded. In most designs, addition of a ceramic capacitor in the range of 33 pF and 100 pF connected across the PFC output diode will reduce the maximum drain-source voltage to a level below the  $\mathrm{BV}_{\mathrm{DSS}}$  rating. When measuring drain-source voltage of the MOSFET, a high-voltage probe should be used. When the probe tip is removed, a silver ring in the vicinity of the probe tip can be seen. This ring is at ground potential and the best ground connection point for making noise free measurements. Wrapping stiff wire around the ground ring and then connecting that ground wire into the circuit with the shortest possible wire length, and connecting the probe tip to the point being measured, ensures error free measurement. Probe should be compensated according to probe manufacturer's guidelines to ensure error-free measurement.

- Maximum drain current Drain current can be measured indirectly by monitoring inductor current. A current probe should be inserted between the bridge rectifier and inductor connection. At maximum ambient temperature, minimum input voltage and maximum output load, verify drain current waveforms at start-up for any signs of inductor saturation. When performing this measurement with Sendust inductor, it is typical to see inductor wave-forms that show exponential increase in current due to permeability drop. This should not be confused with hard saturation.

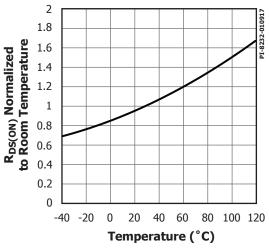

- 3. Thermal check At maximum output power, minimum input voltage and maximum ambient temperature; verify that temperature specifications are not exceeded for the HiperPFS-4, PFC inductor, output diodes and output capacitors. Enough thermal margin should be allowed for the part-to-part variation of the R<sub>DS(ON)</sub> of HiperPFS-4, as specified in the data sheet. A maximum package temperature of 100 °C is recommended to allow for these variations.

- Input PF should improve with load, if performance is found to progressively deteriorate with loading, it is a sign of possible noise pick-up by the VOLTAGE MONITOR pin circuit or the feedback divider network and the compensation circuit.

## PFS7623-7629/7633-7636

#### **Absolute Maximum Ratings**(1,2)

| DRAIN Pin Peak Current:         | PFS7623/PFS7633.  | 7.5 A           |

|---------------------------------|-------------------|-----------------|

|                                 | PFS7624/PFS7634.  | 9.0 A           |

|                                 | PFS7625/PFS7635 . | 11.3 A          |

|                                 | PFS7626/PFS7636.  | 13.5 A          |

|                                 | PFS7627           | 15.8 A          |

|                                 | PFS7628           | 18.0 A          |

|                                 | PFS7629           | 21.0 A          |

| DRAIN Pin Voltage               |                   | 0.3 V to 600 V  |

| VCC <sup>(3)</sup> Pin Voltage  |                   |                 |

| PG                              |                   | 0.3 V to 17.5 V |

| PG Pin Current                  |                   | 10 mA           |

| V, PGT, FB, C, REF Pin Vo       | Itage             | 0.3 V to 5.6 V  |

| Storage Temperature             |                   |                 |

| Junction Temperature(4)         |                   |                 |

| Lead Temperature <sup>(5)</sup> |                   | 260 °C          |

|                                 |                   |                 |

#### Notes:

- 1. All voltages referenced to SOURCE,  $T_A = 25$  °C.

- Maximum ratings specified may be applied one at a time without causing permanent damage to the product. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect product reliability.

- 3. The absolute maximum rating of the VCC is 17.5 V. This is an absolute maximum condition that must not be exceeded. Voltages between the max operating voltage (15 V) and this abs max rating should be very infrequent and short in duration (e.g. at start-up or temporary fault conditions). It is not intended as a guarantee of the reliability of the product up to the absolute maximum rating, but is a guideline as to the level of applied voltage above which there is a risk of immediate damage to the product.

- 4. Normally limited by internal circuitry. Applies to Controller  $T_{_{J(C)}}$  and MOSFET  $T_{_{J(M)}}.$

- 5. 1/16" from case for 5 seconds.

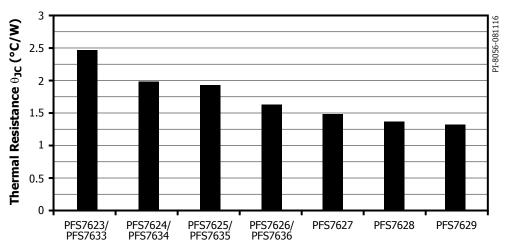

#### **Thermal Resistance**

| Thermal Resistance: H/L Package: |                 |

|----------------------------------|-----------------|

| $(\theta_{_{1\Delta}})^{(1)}$    | 103 °C/W        |

| $(\theta_{1C})$                  | (see Figure 19) |

Notes:

1. Measured without heat sink in still air.

| Parameter                                                                   | Symbol                 | Conditions  SOURCE = 0 V; $V_{CC}$ = 12 V,  -40 °C < $T_{J(C)}$ < 125 °C (Note C)  (Unless Otherwise Specified) | Pin | Min | Тур | Max | Units |

|-----------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-------|

| Currents                                                                    |                        |                                                                                                                 |     |     |     |     |       |

| Undervoltage Current<br>Consumption After<br>Power-Up of Core and<br>Zeners | I <sub>CC(UVLO)</sub>  | $V_{CC} < UVLO+(min)$<br>V = 1  V,  C = 0  V,  FB = 3.85  V<br>$0 \text{ °C} < T_{J(C)} < 100 \text{ °C}$       | VCC |     | 140 |     | μА    |

| Standby Current<br>Consumption – No<br>Switching Prior to<br>Brown-In       | $I_{\text{CC(STBY)}}$  | V = 1 V, C = 0 V, FB = 3.85 V<br>0 °C < T <sub>J(C)</sub> < 100 °C                                              | VCC |     | 320 |     | μА    |

| Current Consumption – in Burst Mode, No Switching                           | I <sub>CC(BURST)</sub> | FB = 3.85 V, C < $V_{ERR\_MIN}$<br>V = 1.414 V<br>0 °C < $T_{J(C)}$ < 100 °C                                    | VCC |     | 395 | 470 | μА    |

| Parameter                                               | Symbol                     | Condition SOURCE = 0 V; V $-40 \text{ °C} < T_{J(C)} <$ (Note C) (Unless Other                                                   |                                   | Min  | Тур  | Max  | Units |

|---------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|------|------|-------|

|                                                         |                            | (Note C) (Unless Otherwise Specified)                                                                                            |                                   |      |      |      |       |

| Currents (cont.)                                        | I                          |                                                                                                                                  |                                   |      | I    | ı    |       |

|                                                         |                            |                                                                                                                                  | PFS7623 / PFS7633                 | 0.64 | 0.75 | 0.90 | _     |

|                                                         |                            |                                                                                                                                  | PFS7624 / PFS7634                 | 0.69 | 0.82 | 0.97 |       |

|                                                         |                            | No-load on REF                                                                                                                   | PFS7625 / PFS7635                 | 0.74 | 0.88 | 1.05 |       |

| Operating Current                                       | I <sub>CC(ON)</sub>        | Switching at $F_{MIN}$<br>$(T_{OFF} = T_{OFF(MIN)}, T_{ON} = T_{ON(MAX)})$                                                       | PFS7626 / PFS7636                 | 0.79 | 0.93 | 1.12 | mA    |

|                                                         |                            | $(T_{OFF} = T_{OFF(MIN)} T_{ON} = T_{ON(MAX)}$<br>$0 \text{ °C} < T_{J(C)} < 100 \text{ °C}$                                     | PFS7627                           | 0.85 | 1.00 | 1.20 |       |

|                                                         |                            |                                                                                                                                  | PFS7628                           | 0.91 | 1.07 | 1.28 |       |

|                                                         |                            |                                                                                                                                  | PFS7629                           | 0.98 | 1.15 | 1.38 |       |

| Leakage Current in<br>UVLO State                        | I <sub>oz</sub>            | 0 < Pin Voltage < REF<br>$0 °C < T_{J(C)} < 100 °C$                                                                              | V, FB, C, PGT                     |      | ±10  |      | nA    |

|                                                         |                            | V <sub>PG</sub> = 12 V                                                                                                           | PG                                |      | ±0.1 |      | μА    |

| Pull-Down Current<br>on Feedback                        | I <sub>FB(PD)</sub>        | Not Active When VCC < UVLO+ $0  ^{\circ}\text{C} < T_{\text{J(C)}} < 100  ^{\circ}\text{C}$                                      | FB                                |      | 100  |      | nA    |

| Pull-Down Current<br>on Voltage                         | I <sub>V(PD)</sub>         | Not Active When VCC < UVLO+ 0 °C < T <sub>J(C)</sub> < 100 °C                                                                    | V                                 |      | 100  |      | nA    |

| On-Time Controller                                      |                            |                                                                                                                                  |                                   |      |      |      |       |

| Maximum Operating<br>"On"-Time                          | t <sub>on(MAX)</sub>       | 0 °C < T <sub>J(C)</sub> < 1                                                                                                     | .00 °C                            | 29   | 34   | 40   | μS    |

| Off-Time Controller                                     | l                          |                                                                                                                                  |                                   |      | ı    |      |       |

| Maximum Operating<br>"Off"-Time                         | t <sub>OFF(MAX)</sub>      | 0 °C < T <sub>J(C)</sub> < 1                                                                                                     | .00 °C                            | 36   | 43   | 48   | μS    |

| Off-Time Accuracy                                       | t <sub>OFF(ACCURACY)</sub> | $0 \text{ °C} < T_{\text{J(C)}} < 1$<br>V = 1.414<br>FB = 3.85<br>C > = 4  V                                                     | V<br>V                            |      | ±4.0 |      | %     |

| Feedback                                                | I                          |                                                                                                                                  |                                   |      |      |      |       |

| Feedback Voltage                                        | V <sub>FB(REF)</sub>       | T <sub>J(C)</sub> = 25 °                                                                                                         | C                                 | 3.82 | 3.85 | 3.88 | V     |

| Reference                                               | * FB(REF)                  | 0 °C < T <sub>J(C)</sub> < 1                                                                                                     | .00 °C                            | 3.75 | 3.85 | 3.95 |       |

| Feedback Error-<br>Amplifier Transconduc-<br>tance Gain | G <sub>M</sub>             | $3.75 \text{ V} < \text{V}_{FB} < 3.95 \text{ V}$ $\text{V}_{C} = 4 \text{ V}$ $0 \text{ °C} < \text{T}_{J(C)} < 100 \text{ °C}$ |                                   | 75   | 90   | 105  | μA/V  |

| Soft Shutdown Time                                      | t <sub>shutdwn</sub>       | See Note                                                                                                                         | A                                 | 0.86 | 1.00 | 1.16 | ms    |