# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

#### **General Description**

The MAX9939 is a general-purpose, differential-input programmable-gain amplifier (PGA) that is ideal for conditioning a variety of wide dynamic range signals such as those found in motor current-sense, medical instrumentation, and sonar data acquisition applications. It features programmable differential gains from 0.2V/V to 157V/V, input offset-voltage compensation, and an output amplifier that can be configured either as a high-order active filter or to provide a differential output.

The PGA is optimized for high-signal bandwidth and its gain can be programmed to be 0.2V/V, 1V/V, 10V/V, 20V/V, 30V/V, 40V/V, 60V/V, 80V/V, 119V/V, and 157V/V. Precision resistor matching provides extremely low gain tempco and high CMRR. Although the MAX9939 operates from a single supply  $V_{CC}$  between 2.9V to 5.5V, it can process signals both above and below ground due to the use of an input level-shifting amplifier stage. Furthermore, its inputs are protected to ±16V, allowing it to withstand fault conditions and signal overranges.

The output amplifier is designed for high bandwidth and low-bias currents, making it ideal for use in multiplefeedback active filter topologies that offer much higher Qs and stopband attenuation than Sallen-Key architectures.

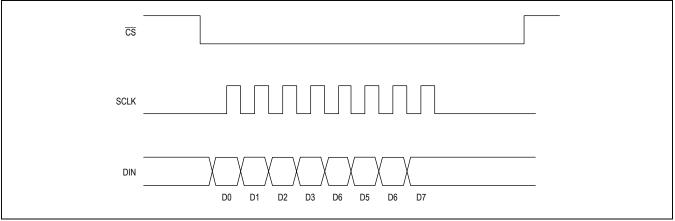

The MAX9939 draws 3.4mA of quiescent supply current at 5V, and includes a software-programmable shutdown mode that reduces its supply current to only 13 $\mu$ A. The MAX9939 is available in a 10-pin  $\mu$ MAX<sup>®</sup> package and operates over the -40°C to +125°C automotive temperature range.

#### **Applications**

- Sensorless Motor Control

- Medical Signal Conditioning

- Sonar and General Purpose Data Acquisition

- Differential to Single-Ended Conversion

- Differential-Input, Differential-Output Signal Amplification

- Sensor Interface and Signal Processing

$\mu$ MAX is a registered trademark of Maxim Integrated Products, Inc.

Functional Diagram appears at end of data sheet.

#### **Features**

- SPI-Programmable Gains: 0.2V/V to 157V/V

- Extremely Low Gain Tempco

- Integrated Amplifier for R/C Programmable Active Filter

- Input Offset-Voltage Compensation

- Input Protection to ±16V

- 13µA Software Shutdown Mode

- -40°C to +125°C Operating Temperature Range

- 10-Pin µMAX Package

### **Ordering Information**

| PART           | TEMP RANGE      | PIN-PACKAGE |

|----------------|-----------------|-------------|

| MAX9939AUB+    | -40°C to +125°C | 10 µMAX     |

| MAX9939AUB/V+T | -40°C to +125°C | 10 µMAX     |

/V denotes an automotive-qualified part.

+Denotes a lead(Pb)-free/RoHS-compliant package.

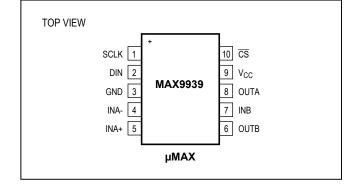

### **Pin Configuration**

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

### **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND                                | 0.3V to +6V                |

|-------------------------------------------------------|----------------------------|

| INB, OUTA, OUTB, SCLK, DIN, CS0.3V to                 | o (V <sub>CC</sub> + 0.3V) |

| INA+, INA- to GND                                     | 16V to +16V                |

| Output Short-Circuit Current Duration                 | Continuous                 |

| Continuous Input Current into Any Terminal            | ±20mA                      |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                            |

| 10-Pin µMAX (derate 5.6mW/°C above +70°C)             | )707mW                     |

| Operating Temperature Range       | -40°C to +125°C |

|-----------------------------------|-----------------|

| Junction Temperature              | +150°C          |

| Storage Temperature Range         | -65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C          |

| Soldering Temperature (reflow)    | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{CC} = 5V, V_{GND} = 0V, V_{INA+} = V_{INA-}, Gain = 10V/V, R_{OUTA} = R_{OUTB} = 1k\Omega$  to  $V_{CC}/2, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                       | SYMBOL                            | CONDITIONS                                                                               | MIN                 | TYP  | MAX                      | UNITS  |

|---------------------------------|-----------------------------------|------------------------------------------------------------------------------------------|---------------------|------|--------------------------|--------|

| PGA CHARACTERISTICS             |                                   |                                                                                          |                     |      |                          |        |

| Gain Error                      | GE                                | T <sub>A</sub> = +25°C, 0.2V ≤ V <sub>OUTA</sub> ≤ VCC - 0.2V                            |                     | 0.05 | 0.38                     | %      |

| Gain Temperature-Coefficient    | Tc-GE                             |                                                                                          |                     | 2.2  | 17                       | ppm/°C |

| Innut Offeet Veltere (Nete 2)   |                                   | With no V <sub>OS</sub> trim, T <sub>A</sub> = +25°C                                     |                     | 1.5  | 9                        | - mV   |

| Input Offset Voltage (Note 2)   | V <sub>OS-A</sub>                 | With no V <sub>OS</sub> trim, $T_A = T_{MIN}$ to $T_{MAX}$                               |                     |      | 15                       |        |

| Input Offset-Voltage Drift      |                                   |                                                                                          |                     | 10   |                          | μV/C   |

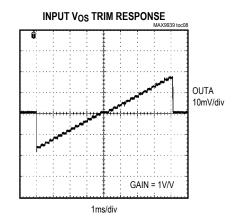

| Input Offset-Voltage Trim Range |                                   |                                                                                          |                     | ±17  |                          | mV     |

| Input Common-Mode Range         | V <sub>CM</sub>                   | Guaranteed by CMRR test (Note 3)                                                         | -V <sub>CC</sub> /2 |      | V <sub>CC</sub><br>- 2.2 | V      |

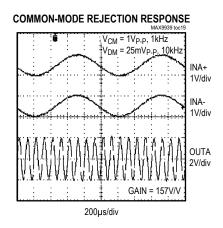

|                                 |                                   | $-1V \le V_{CM} \le V_{CC} - 2.2V$                                                       | 50                  | 60   |                          |        |

| Common-Mode Rejection Ratio     | CMRR                              | $-V_{CC}/2 \le V_{CM} \le V_{CC} - 2.2V, T_A = +25^{\circ}C$                             | °C 50 60<br>39      |      |                          | dB     |

|                                 |                                   | $-V_{CC}/2 \le V_{CM} \le V_{CC} - 2.2V$                                                 |                     |      |                          | 1      |

| Output Short-Circuit current    | I <sub>SC</sub>                   |                                                                                          |                     | 70   |                          | mA     |

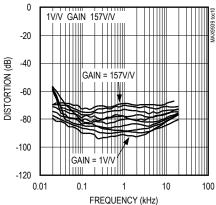

| Input-Voltage Noise Density     | V <sub>N</sub>                    | f = 10kHz, gain = 157V/V                                                                 |                     | 54   |                          | nV/√Hz |

|                                 |                                   | Gain = 0.2V/V                                                                            |                     | 2.15 |                          |        |

| Gain-Bandwidth Product          | GBW                               | Gain = 1V/V                                                                              | 2.15                |      |                          | MHz    |

|                                 |                                   | Gain = 157V/V                                                                            |                     |      |                          |        |

| Slew Rate                       | SR                                |                                                                                          |                     | 9    |                          | V/µs   |

| Settling Time                   | t <sub>S</sub>                    | To 1%, 2V output step                                                                    |                     | 0.45 |                          | μs     |

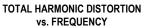

| Distortion                      | THD                               | $f = 1 kHz, V_{OUTA} = 2.5 V_{P-P}$                                                      |                     | 89   |                          | dB     |

| Max Capacitive Load             | C <sub>L(MAX)</sub>               |                                                                                          |                     | 1    |                          | nF     |

| Output Swing                    | V <sub>OH</sub> , V <sub>OL</sub> | Voltage output high = $V_{CC} - V_{OUTA}$ ,<br>voltage output low = $V_{OUTA} - V_{GND}$ |                     | 25   | 60                       | mV     |

| OUTPUT AMPLIFIER CHARACT        | ERISTICS                          |                                                                                          |                     |      |                          |        |

| Input Bias Current              | lb                                | (Note 4)                                                                                 | 1                   |      |                          | pА     |

| Input Offeet Veltage (Note 2)   |                                   | T <sub>A</sub> = +25°C                                                                   |                     | 1.5  | 9                        | m)/    |

| Input Offset Voltage (Note 2)   | V <sub>OS-B</sub>                 | $T_A = T_{MIN}$ to $T_{MAX}$                                                             | 15                  |      | 15                       | - mV   |

| Output Short-Circuit Current    | I <sub>SC</sub>                   |                                                                                          |                     | 70   |                          | mA     |

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

### **Electrical Characteristics (continued)**

$(V_{CC} = 5V, V_{GND} = 0V, V_{INA+} = V_{INA-}, Gain = 10V/V, R_{OUTA} = R_{OUTB} = 1k\Omega$  to  $V_{CC}/2, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                    | SYMBOL                            | CONDITIONS                                                                                                               | MIN                              | ΤΥΡ  | MAX | UNITS  |

|------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|-----|--------|

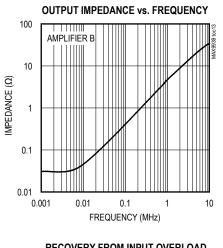

| Unity-Gain Bandwidth         | UGBW                              |                                                                                                                          |                                  | 2.2  |     | MHz    |

| Slew Rate                    | SR                                |                                                                                                                          |                                  | 6.4  |     | V/µs   |

| Settling Time                | t <sub>S</sub>                    | To 1%, 2V output step                                                                                                    |                                  | 0.86 |     | μs     |

| Input-Voltage Noise Density  | V <sub>N</sub>                    |                                                                                                                          |                                  | 36   |     | nV/√Hz |

| Distortion                   | THD                               | f = 1kHz, V <sub>OUTA</sub> = 2.5V <sub>P-P</sub> , gain = -1V/V                                                         |                                  | 90   |     | dB     |

| Max Capacitive Load          | C <sub>L(MAX)</sub>               |                                                                                                                          |                                  | 1    |     | nF     |

| Output Swing                 | V <sub>OH</sub> , V <sub>OL</sub> | Voltage output high = V <sub>CC</sub> - V <sub>OUTB</sub> ,<br>voltage output low = V <sub>OUTB</sub> - V <sub>GND</sub> |                                  | 25   | 60  | mV     |

| POWER SUPPLY                 |                                   |                                                                                                                          | -                                |      |     |        |

| Supply Voltage Range         | V <sub>CC</sub>                   | Guaranteed by PSRR                                                                                                       | 2.9                              |      | 5.5 | V      |

| Power-Supply Rejection Ratio | PSRR                              | 1kΩ between OUTA and INB, 1kΩ between                                                                                    |                                  |      | dB  |        |

| Supply Current               | ICC                               | OUTA and OUTB unloaded                                                                                                   |                                  | 3.4  | 6.7 | mA     |

| Shutdown Supply Current      | ISHDN                             | Soft shutdown through SPI                                                                                                |                                  | 13   | 24  | μA     |

| SPI CHARACTERISTICS          |                                   |                                                                                                                          | ·                                |      |     | •      |

| Input-Voltage Low            | VIL                               |                                                                                                                          |                                  |      | 0.8 | V      |

| Innut Valtaga Lligh          |                                   | V <sub>CC</sub> = 5V                                                                                                     | 2.0                              |      |     | v      |

| Input-Voltage High           | V <sub>IH</sub>                   | V <sub>CC</sub> = 3.3V                                                                                                   | 1.65                             |      |     |        |

| Input Leakage Current        | I <sub>IN</sub>                   |                                                                                                                          |                                  |      | ±1  | μA     |

| Input Capacitance            | C <sub>IN</sub>                   |                                                                                                                          |                                  | 5    |     | pF     |

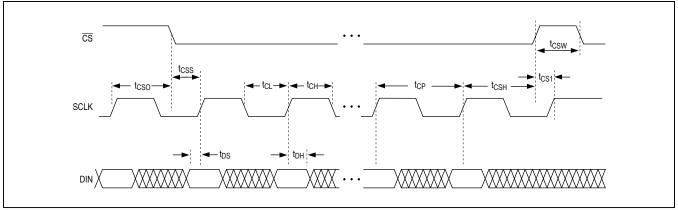

| SPI TIMING CHARACTERISTIC    | S                                 |                                                                                                                          |                                  |      |     |        |

| SCLK Frequency               | fSCLK                             | (Note 5)                                                                                                                 |                                  |      | 5   | MHz    |

| SCLK Period                  | t <sub>CP</sub>                   |                                                                                                                          | 200                              |      |     | ns     |

| SCLK Pulse-Width High        | t <sub>CH</sub>                   |                                                                                                                          | 80                               |      |     | ns     |

| SCLK Pulse-Width Low         | t <sub>CL</sub>                   |                                                                                                                          | 80                               |      |     | ns     |

| CS Fall to SCLK Rise Setup   | t <sub>CSS</sub>                  |                                                                                                                          | 80                               |      |     | ns     |

| CS Fall to SCLK Rise Hold    | t <sub>CSH</sub>                  |                                                                                                                          | 20 + (0.5<br>x t <sub>CP</sub> ) |      |     | ns     |

| DIN to SCLK Setup            | t <sub>DS</sub>                   |                                                                                                                          | 55                               |      |     | ns     |

| DIN Hold after SCLK          | t <sub>DH</sub>                   |                                                                                                                          | 0                                |      |     | ns     |

| SCLK Rise to CS Fall Delay   | t <sub>CS0</sub>                  |                                                                                                                          | 20                               |      |     | ns     |

| CS Rise to SCLK Rise Hold    | t <sub>CS1</sub>                  |                                                                                                                          | 80                               |      |     | ns     |

| CS Pulse-Width High          | t <sub>CSW</sub>                  |                                                                                                                          | 200                              |      |     | ns     |

Note 1: All devices are 100% production tested at  $T_A = +25$ °C. Temperature limits are guaranteed by design.

Note 2: The input offset voltage includes the effects of mismatches in the internal  $V_{CC}/2$  resistor dividers.

Note 3: For gain of 0.25V/V, the input common-mode range is -1V to  $V_{CC}$  - 2V.

Note 4: The input current of a CMOS device is too low to be accurately measured on an ATE and is typically on the order of 1pA.

**Note 5:** Parts are functional with  $f_{SCLK} = 10MHz$ .

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

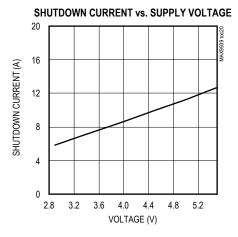

Figure 1. SPI Interface Timing Diagram

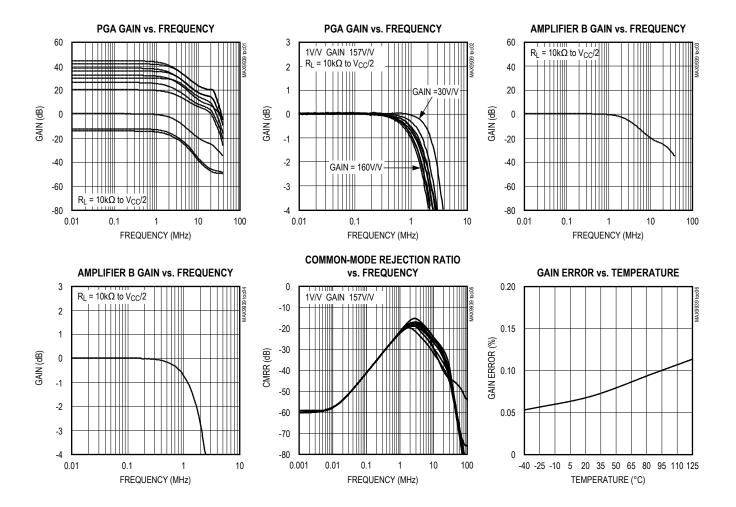

### **Typical Operating Characteristics**

$(V_{CC} = 5V, V_{GND} = 0V, V_{IN+} = V_{IN-} = 0V, Gain = 10V/V, R_{OUTA} = R_{OUTB} = 1k\Omega \text{ to } V_{CC}/2, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

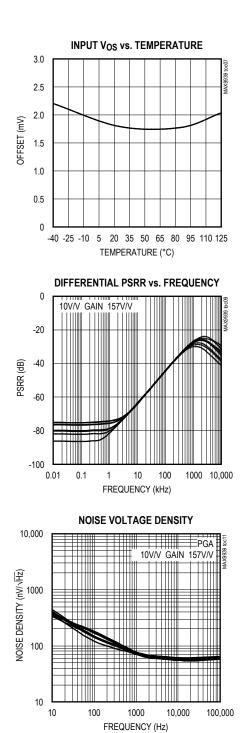

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 5V, V_{GND} = 0V, V_{IN+} = V_{IN-} = 0V, Gain = 10V/V, R_{OUTA} = R_{OUTB} = 1k\Omega$  to  $V_{CC}/2, T_A = +25^{\circ}C$ , unless otherwise noted.)

NOISE VOLTAGE DENSITY

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 5V, V_{GND} = 0V, V_{IN+} = V_{IN-} = 0V, Gain = 10V/V, R_{OUTA} = R_{OUTB} = 1k\Omega \text{ to } V_{CC}/2, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

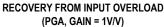

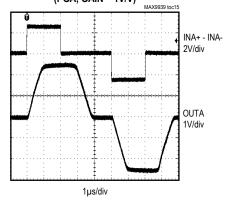

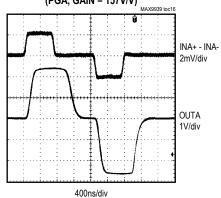

RECOVERY FROM INPUT OVERLOAD (OUTPUT AMPLIFIER)

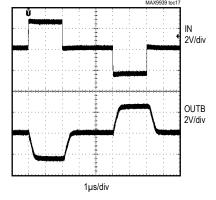

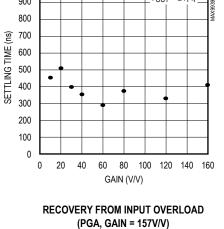

1% SETTLING TIME vs. GAIN (PGA) 1000 900 800

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 5V, V_{GND} = 0V, V_{IN+} = V_{IN-} = 0V, Gain = 10V/V, R_{OUTA} = R_{OUTB} = 1k\Omega \text{ to } V_{CC}/2, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

#### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                            |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SCLK            | Serial-Clock Input                                                                                                                                  |

| 2   | DIN             | Serial-Data Input. Data is clocked into the serial interface on the rising edge of SCLK.                                                            |

| 3   | GND             | Ground                                                                                                                                              |

| 4   | INA-            | PGA Inverting Input                                                                                                                                 |

| 5   | INA+            | PGA Noninverting Input                                                                                                                              |

| 6   | OUTB            | Buffer Output                                                                                                                                       |

| 7   | INB             | Buffer Input                                                                                                                                        |

| 8   | OUTA            | PGA Output                                                                                                                                          |

| 9   | V <sub>CC</sub> | Power Supply. Bypass to GND with 0.1µF and 1µF capacitors.                                                                                          |

| 10  | CS              | Active-Low Chip-Select Input. Drive $\overline{CS}$ low to enable the serial interface. Drive $\overline{CS}$ high to disable the serial interface. |

#### **Detailed Description**

The MAX9939 is a general-purpose PGA with input offset trim capability. Its gain and input offset voltage ( $V_{OS}$ ) are SPI programmable. The device also includes an uncommitted output operational amplifier that can be used as either a high-order active filter or to provide a differential output. The device can be put into shutdown through SPI.

The gain of the amplifier is programmable between 0.2V/V and 157V/V (default gain is set to 1 V/V). The input offset

is programmable between ±17mV and can be used to regain output dynamic range in high gain settings. An input offset-voltage measurement mode enables input offset voltage to be calibrated out in firmware to obtain excellent DC accuracy.

The main amplifier accepts a differential input and provides a single-ended output. The relationship between the differential input and singled-ended output is given by the representative equation:

$V_{OUTA} = V_{CC}/2$  - Gain x ( $V_{INA+} - V_{INA-}$ ) + Gain x  $V_{OS}$

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

Figure 2. SPI Interface Timing Diagram (CPOL = CPHA = 0)

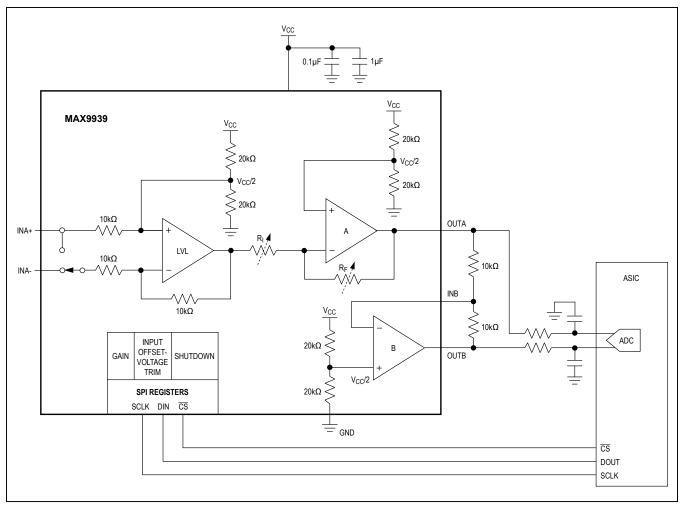

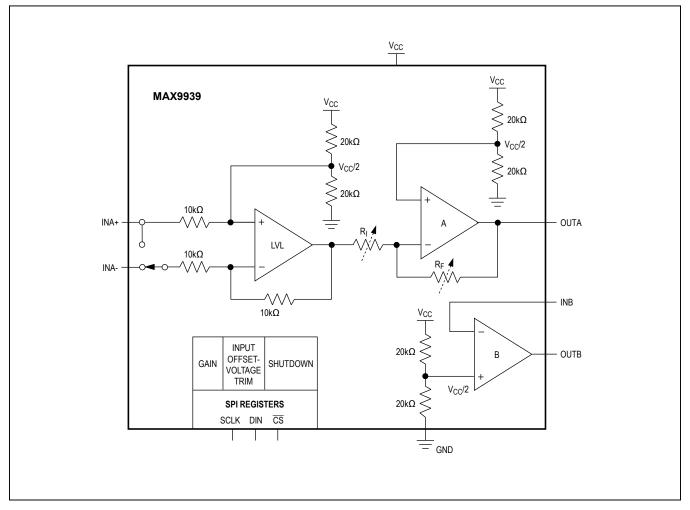

#### Architecture

The MAX9939 features three internal amplifiers as shown in the *Functional Diagram*. The first amplifier (amplifier LVL) is configured as a differential amplifier for differential to single-ended conversion with an input offset-voltage trim network. It has extremely high CMRR, gain accuracy, and very low temperature drift due to precise resistor matching. The output of this amplifier is level shifted to V<sub>CC</sub>/2.

This amplifier is followed by a programmable-gain inverting amplifier (amplifier A) with programmable R<sub>F</sub> and R<sub>I</sub> resistors whose gain varies between 0.2V/V and 157V/V. The output of this amplifier is biased at V<sub>CC</sub>/2 and has extremely high gain accuracy and low temperature drift. The MAX9939 has an uncommitted op amp (amplifier B) whose noninverting input is referenced to V<sub>CC</sub>/2. Its inverting input and output are externally accessible, allowing it to be configured either as an active filter or as a differential output.

A robust input ESD protection scheme allows input voltages at INA+ and INA- to reach  $\pm 16V$  without damaging the MAX9939, thus making the part extremely attractive for use in front-ends that can be exposed to high voltages during fault conditions. In addition, its input-voltage range extends down to  $-V_{CC}/2$  (e.g., -2.5V when powered from a 5V single supply) allowing the MAX9939 to translate below ground signals to a 0V to 5V output signal. This feature simplifies interfacing ground-referenced signals with unipolar-input ADCs.

#### **SPI-Compatible Serial Interface**

The MAX9939 has a write-only interface, consisting of three inputs: the clock signal (SCLK), data input (DIN), and chip-select input ( $\overline{CS}$ ). The serial interface works with

the clock polarity (CPOL) and clock phase (CPHA) both set to 0 (see Figure 1). Initiating a write to the MAX9939 is accomplished by pulling  $\overline{CS}$  low. Data is clocked in on the rising edge of each clock pulse, and is written LSB first. Each write to the MAX9939 consists of 8 bits (1 byte). Pull  $\overline{CS}$  high after the 8th bit has been clocked in to latch the data and before sending the next byte of instruction. Note that the internal register is not updated if  $\overline{CS}$  is pulled high before the falling edge of the 8th clock pulse.

#### **Register Description**

The MAX9939 consists of three registers: a shift register and two internal registers. The shift register accepts data and transfers it to either of the two internal registers. The two internal registers store data that is used to determine the gain, input offset voltage, and operating modes of the amplifier. The two internal registers are the Input V<sub>OS</sub> Trim register and Gain register. The format of the 8-bit write to these registers is shown in Tables 1 and 2. Data is sent to the shift register LSB first.

#### Table 1. Input VOS Trim Register

| D7<br>MSB | D6   | D5 | D4 | D3 | D2 | D1 | D0<br>LSB |

|-----------|------|----|----|----|----|----|-----------|

| SHDN      | MEAS | V4 | V3 | V2 | V1 | V0 | SEL = 0   |

#### Table 2. Gain Register

| D7<br>MSB | D6   | D5 | D4 | D3 | D2 | D1 | D0<br>LSB |

|-----------|------|----|----|----|----|----|-----------|

| SHDN      | MEAS | Х  | G3 | G2 | G1 | G0 | SEL = 1   |

X = Don't care.

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

**SEL:** The SEL bit selects which internal register is written to. Set SEL to 0 to write bits D5:D1 to the input  $V_{OS}$  trim register. Set SEL to 1 to write D4:D1 to the Gain register (D5 is don't care when SEL = 1).

**SHDN:** Set SHDN to 0 for normal operation. Set SHDN to 1 to place the device in a low-power  $13\mu$ A shutdown mode. In shutdown mode, the outputs OUTA and OUTB are high impedance, however, the SPI decode circuitry is still active. Each instruction requires a write to the SHDN bit.

**MEAS:** The MAX9939 provides a means for measuring its own input offset voltage. When MEAS is set to 1, the INA- input is disconnected from the input signal path and internally shorted to INA+. This architecture thus allows the input common-mode voltage to be compensated at the application-specific input common-mode voltage of interest. The input offset voltage of the PGA is the output offset voltage divided by the programmed gain without any V<sub>OS</sub> trim (i.e., V3:V0 set to 0):

#### $V_{OS-INHERENT} = (V_{OUTA} - V_{CC}/2)/Gain$

Program  $V_{OS}$  to offset  $V_{OS-INHERENT}$ . The input  $V_{OS}$  also includes the effect of mismatches in the resistordividers. Setting MEAS to 0 switches the inputs back to the signals on INA+ and INA-. Each instruction requires a write to the MEAS bit.

#### **Programming Gain**

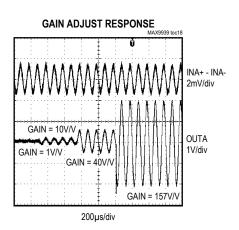

The PGA's gain is set by the bits G3:G0 in the Gain register. Table 3 shows the relationship between the bits G3:G0 and the amplifier's gain. The slew rate and small-signal bandwidth (SSBW) of the PGA depend on its gain setting as shown in Table 3.

#### Programming Input Offset Voltage (VOS)

The input offset voltage is set by the bits V4:V0 in the Input Offset Voltage Trim register. Bit V4 determines the polarity of the offset. Setting V4 to 0 makes the offset positive, while setting V4 to 1 makes the offset negative. Table 4 shows the relationship between V3:V0 and  $V_{OS}$ .

To determine the effect of  $V_{OS}$  at the output of the amplifier for gains other than 1, use the following formula:

$V_{OUTA} = V_{CC}/2 + Gain x (V_{OS-INHERENT} + V_{OS})$

where  $V_{OS\text{-}INHERENT}$  is the inherent input offset voltage of the amplifier, which can be measured by setting MEAS to 1.

#### **Applications Information**

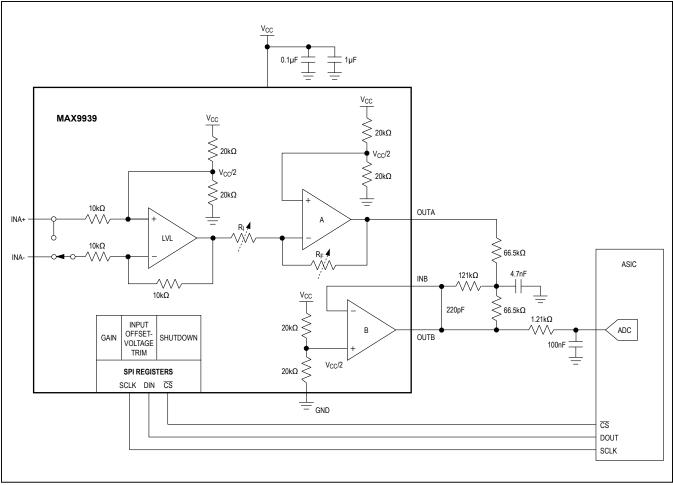

#### Use of Output Amplifier as Active Filter

The output amplifier can be configured as a multiplefeedback active filter as shown in Figure 3, which traditionally has better stopband attenuation characteristics than Sallen-Key filters. These filters also possess inherently better distortion performance since there are no common-mode induced effects (i.e., the common-mode voltage of the operational amplifier is always fixed at  $V_{CC}/2$  instead of it being signal dependent such as in Sallen-Key filters). Choose external resistors and capacitors to create lowpass, bandpass, or highpass filters.

| Table 3. Gain | Tab | le 3. | Gain |

|---------------|-----|-------|------|

|---------------|-----|-------|------|

| G3:G0 | GAIN<br>(V/V)                 | SLEW RATE<br>(V/µs) | SMALL-SIGNAL BANDWIDTH (MHz) |

|-------|-------------------------------|---------------------|------------------------------|

| 0000  | 1                             | 2.90                | 2.15                         |

| 0001  | 10                            | 8.99                | 2.40                         |

| 0010  | 20                            | 8.70                | 1.95                         |

| 0011  | 30                            | 12.80               | 3.40                         |

| 0100  | 40                            | 12.50               | 2.15                         |

| 0101  | 60                            | 13.31               | 2.60                         |

| 0110  | 80                            | 12.15               | 1.91                         |

| 0111  | 120                           | 18.53               | 2.30                         |

| 1000  | 157                           | 16.49               | 1.78                         |

| 1001  | 0.2 (V <sub>CC</sub> = 5V)    | 2.96                | 1.05                         |

| 1001  | 0.25 (V <sub>CC</sub> = 3.3V) | 2.86                | 1.95                         |

| 1010  | 1                             | 2.90                | 2.15                         |

| INPUT OFFSET VOLTAGE<br>(V4 = 0 TRIMS POSITIVE, V4 = 1 TRIMS NEGATIVE) |                      |  |  |  |

|------------------------------------------------------------------------|----------------------|--|--|--|

| V3:V0                                                                  | V <sub>OS</sub> (mV) |  |  |  |

| 0000                                                                   | 0                    |  |  |  |

| 0001                                                                   | 1.3                  |  |  |  |

| 0010                                                                   | 2.5                  |  |  |  |

| 0011                                                                   | 3.8                  |  |  |  |

| 0100                                                                   | 4.9                  |  |  |  |

| 0101                                                                   | 6.1                  |  |  |  |

| 0110                                                                   | 7.3                  |  |  |  |

| 0111                                                                   | 8.4                  |  |  |  |

| 1000                                                                   | 10.6                 |  |  |  |

| 1001                                                                   | 11.7                 |  |  |  |

| 1010                                                                   | 12.7                 |  |  |  |

| 1011                                                                   | 13.7                 |  |  |  |

| 1100                                                                   | 14.7                 |  |  |  |

| 1101                                                                   | 15.7                 |  |  |  |

| 1110                                                                   | 16.7                 |  |  |  |

| 1111                                                                   | 17.6                 |  |  |  |

#### Table 4. Input Offset-Voltage Trim

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

#### Differential-Input, Differential-Output PGA

The output amplifier can be configured so that the MAX9939 operates as a differential-input, differentialoutput programmable gain amplifier. As shown in Figure 4, use a 10k $\Omega$  resistor between OUTA and INB, and between INB and OUTB. Such a differential-output configuration is ideal for use in low-voltage applications that can benefit from the 2X output voltage dynamic range when compared to single-ended output format.

#### Use of Output Operational Amplifier as TIA

CMOS inputs on the output op amp makes it ideal for use as an input transimpedance amplifier (TIA) in certain current-output sensor applications. In such a situation, keep in mind that the inverting input operates at fixed voltage of  $V_{CC}/2$ . Use a high-value resistor as a feedback gain element, and use a feedback capacitor in parallel with this resistor if necessary to aid amplifier stability in the presence of high photodiode or cable capacitance. The output of this TIA can be routed to INA+ or INA- for further processing and signal amplification.

#### **Power-Supply Bypassing**

Bypass V<sub>CC</sub> to GND with a  $0.1\mu$ F capacitor in parallel with a  $1\mu$ F low-ESR capacitor placed as close as possible to the MAX9939.

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

Figure 3. Using the MAX9939 Output Amplifier as an Anti-Aliasing Filter (Corner Frequency = 1.3kHz) to Maximize Nyquist Bandwidth

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

Figure 4. Using the MAX9939 as a Differential-Input, Differential-Output PGA

# **Chip Information**

PROCESS: BiCMOS

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

## **Functional Diagram**

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

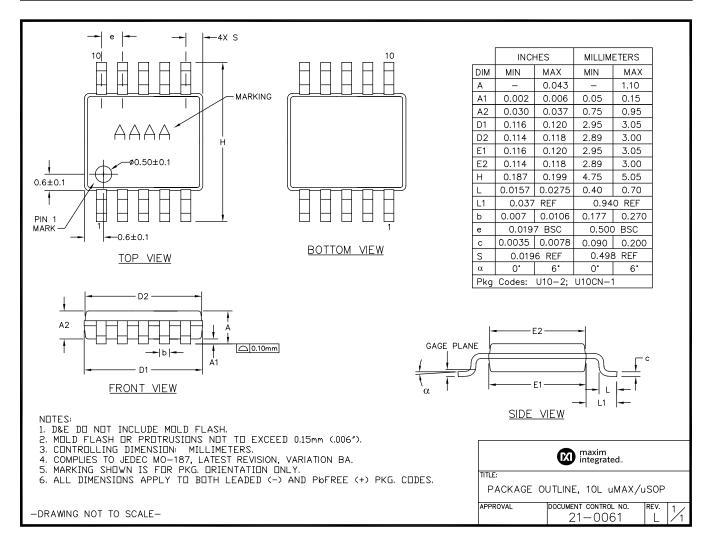

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 10 µMAX      | U10+2        | <u>21-0061</u> | <u>90-0330</u>   |

# SPI Programmable-Gain Amplifier with Input VOS Trim and Output Op Amp

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                     | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------|------------------|

| 0                  | 11/08            | Initial release                 | —                |

| 1                  | 2/09             | Corrected gain value in Table 3 | 9                |

| 2                  | 12/10            | Modified Figure 2               | 8                |

| 3                  | 12/12            | Added the MAX9939AUB/V+T        | 1                |

| 4                  | 8/19             | Updated Detailed Description    | 7                |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.