# CorePCIF v3.6

Handbook

#### Actel Corporation, Mountain View, CA 94043

© 2008 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200087-5

Release: April 2009

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### **Trademarks**

Actel and the Actel logo are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

# **Table of Contents**

|   | Introduction5Core Versions6CorePCIF Device Requirements6                                                                                                                                                                                                                                                                           |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Functional Block Descriptions13Functional Description13CorePCIF Master Function16CardBus Support18CompactPCI Hot-Swap Support18CorePCIF Backend Dataflow18FIFO Recovery Logic19                                                                                                                                                    |

| 2 | Core Structure                                                                                                                                                                                                                                                                                                                     |

| 3 | Tool Flows27SmartDesign27Synthesis in Libero IDE27Place-and-Route in Libero IDE30                                                                                                                                                                                                                                                  |

| 4 | CorePCIF Parameters33General Configuration Parameters33PCI Configuration Space Parameters35Master/DMA Parameters37                                                                                                                                                                                                                 |

| 5 | Core Interfaces41PCI Bus Signals41Backend System-Level Signals42Backend Target and Master Dataflow Signals43                                                                                                                                                                                                                       |

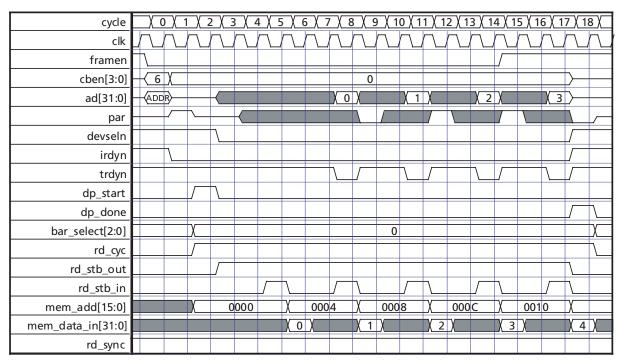

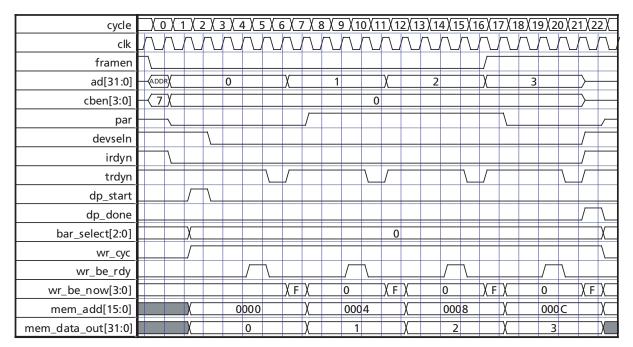

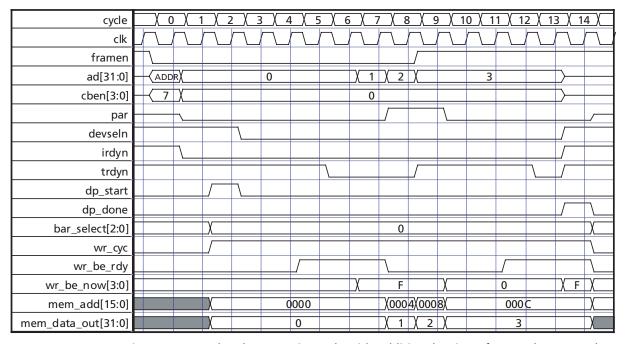

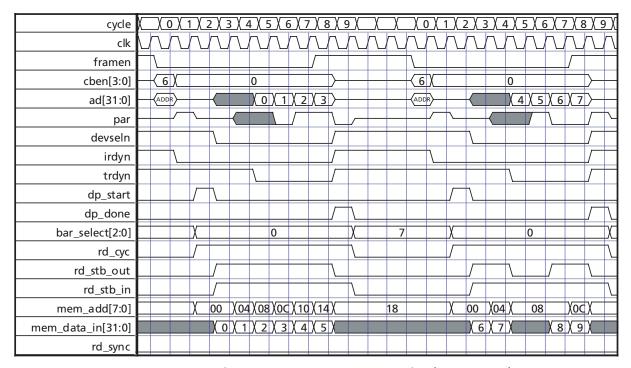

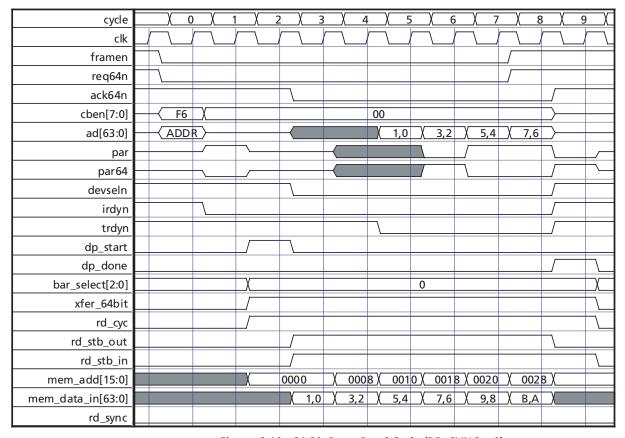

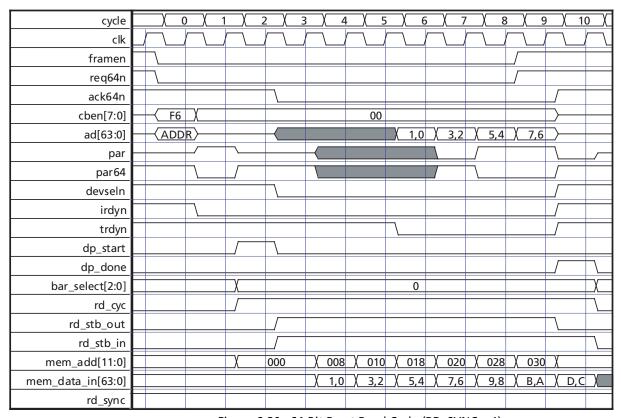

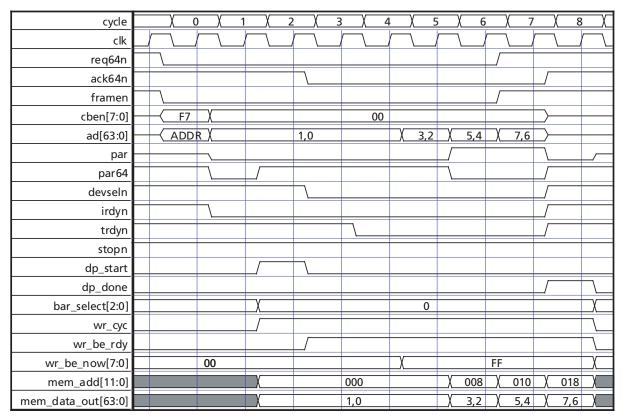

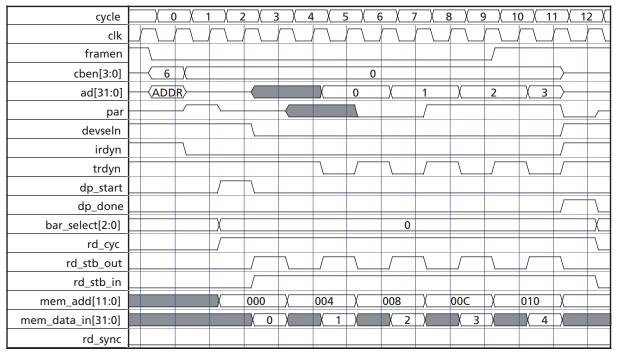

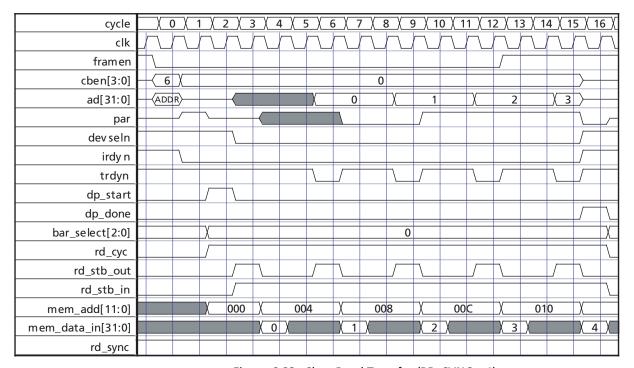

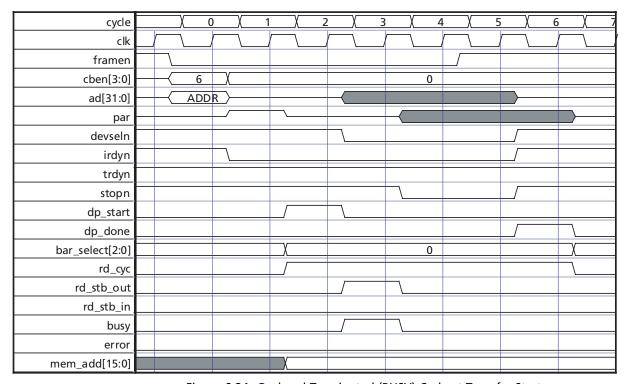

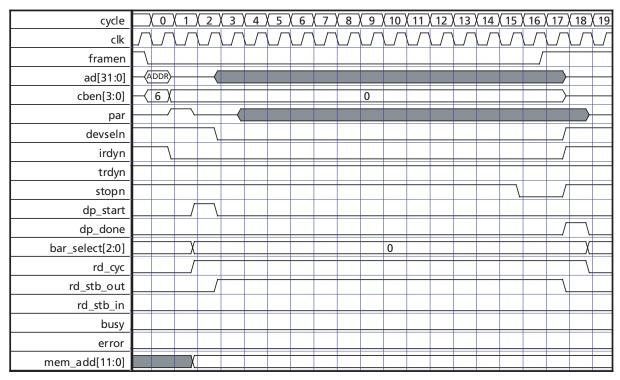

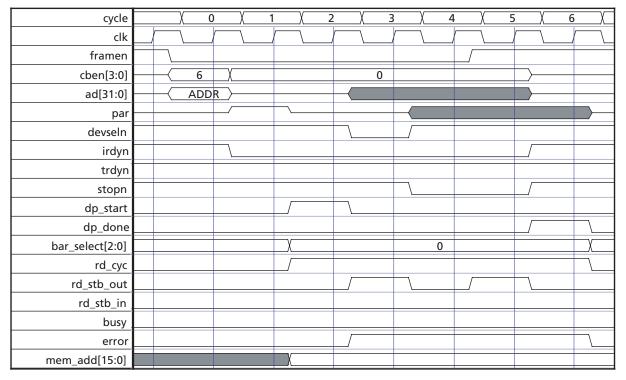

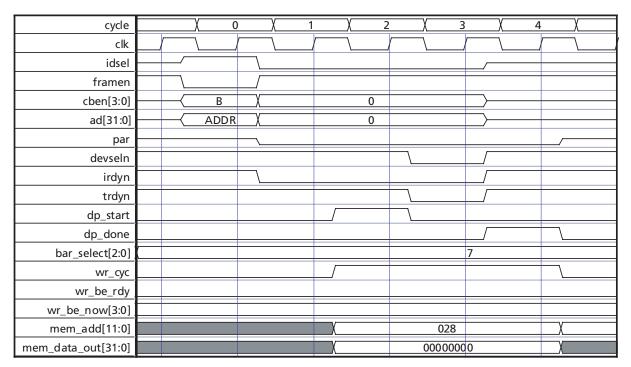

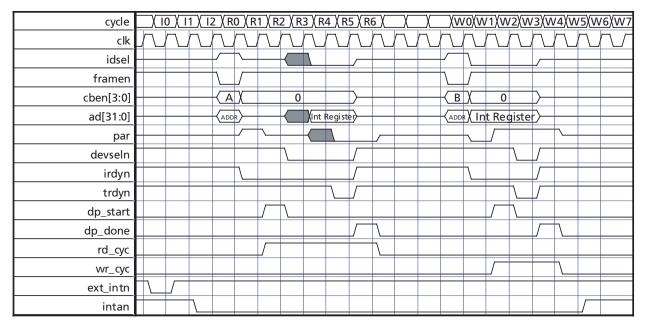

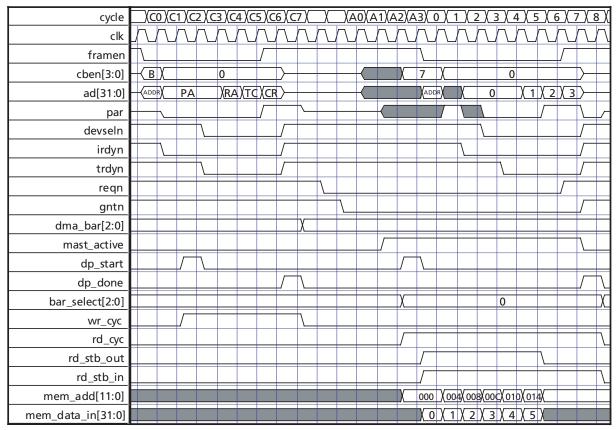

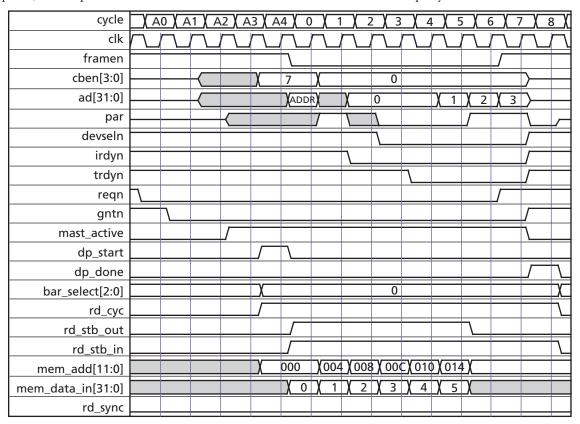

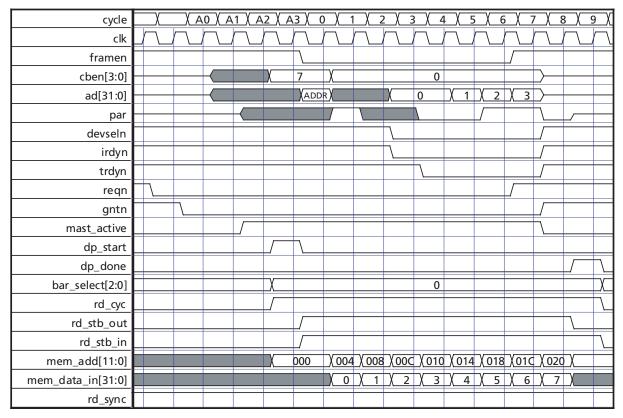

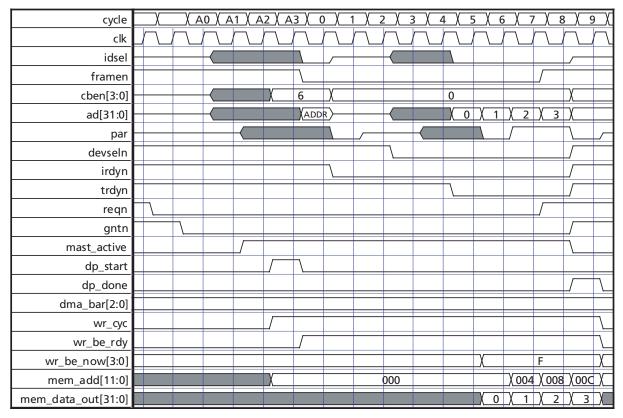

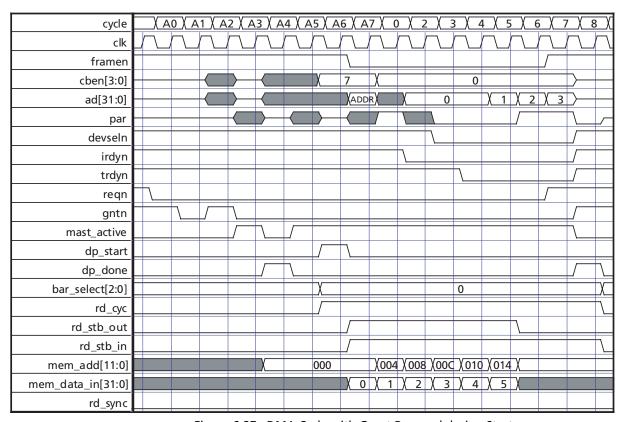

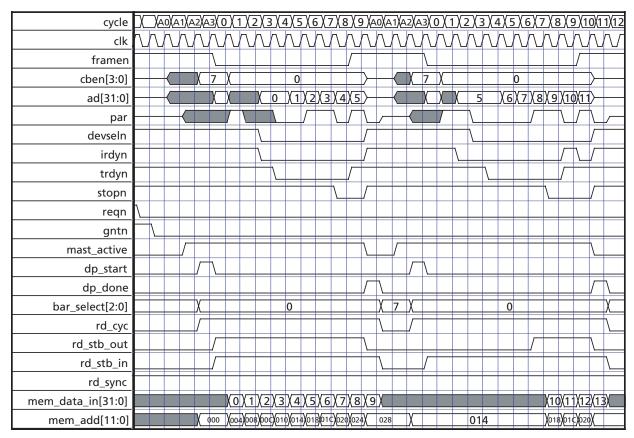

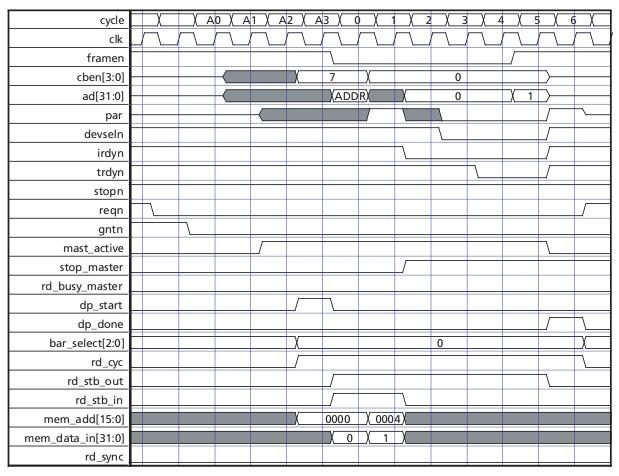

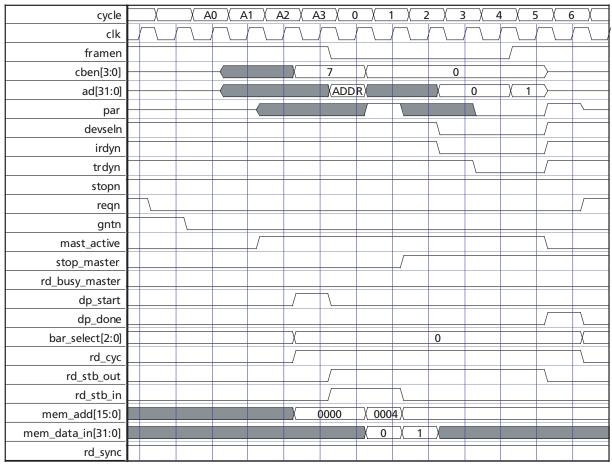

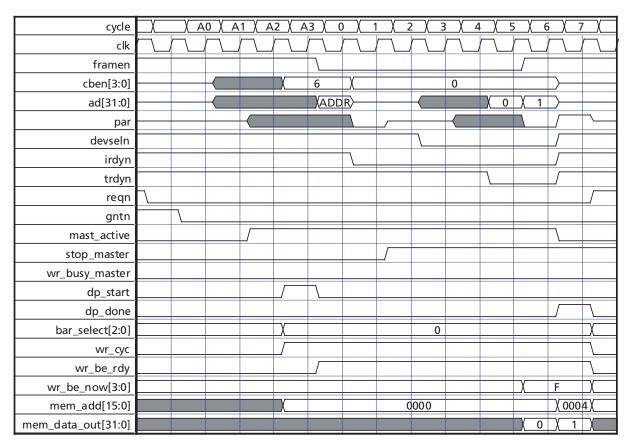

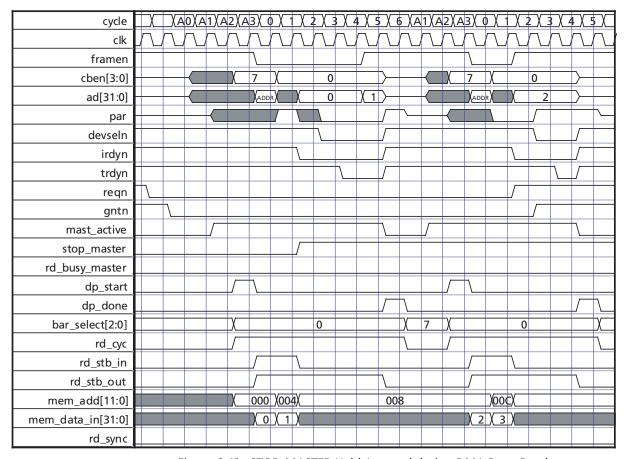

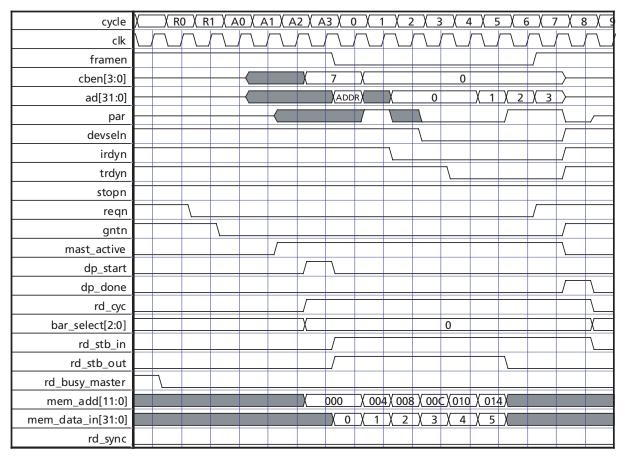

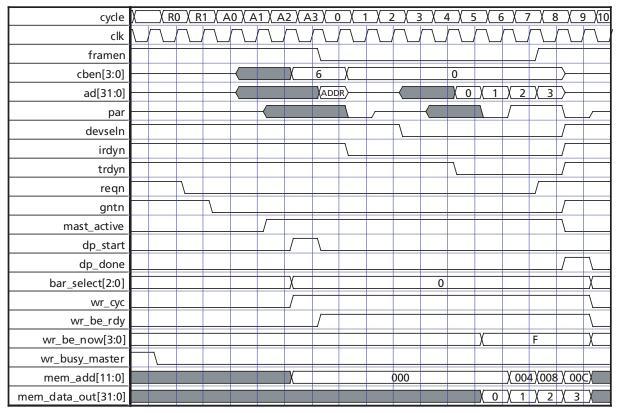

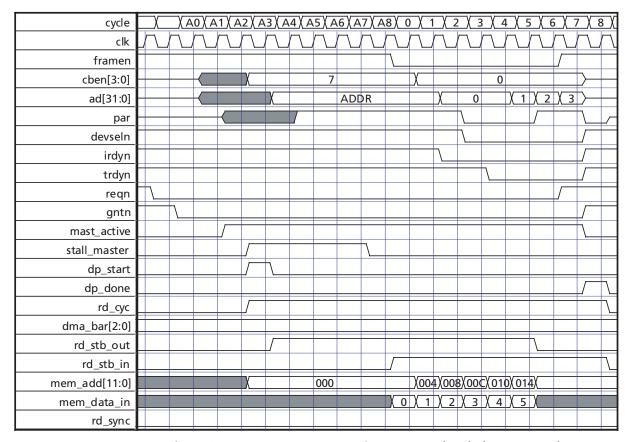

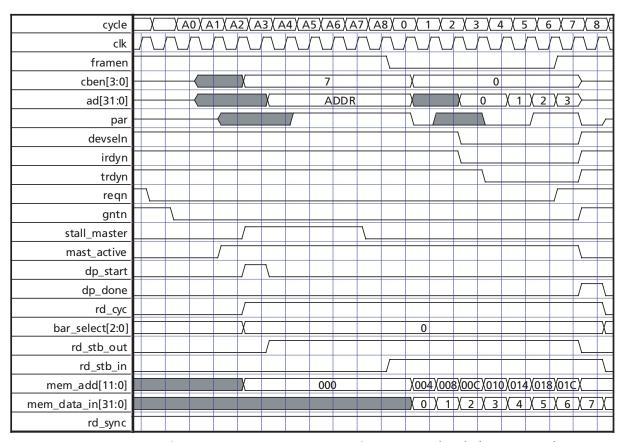

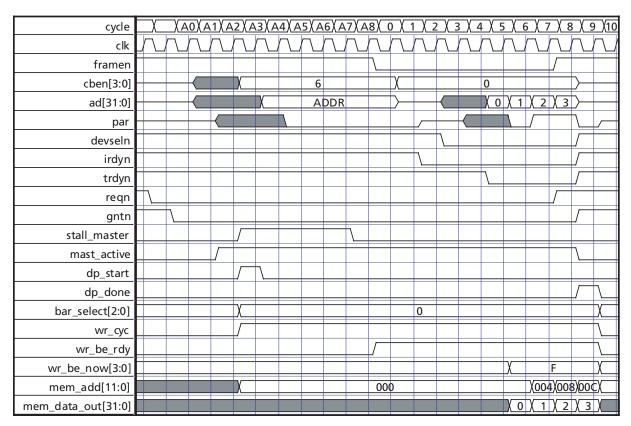

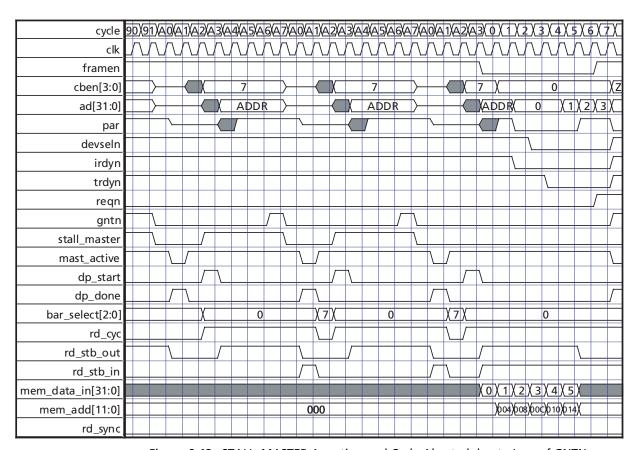

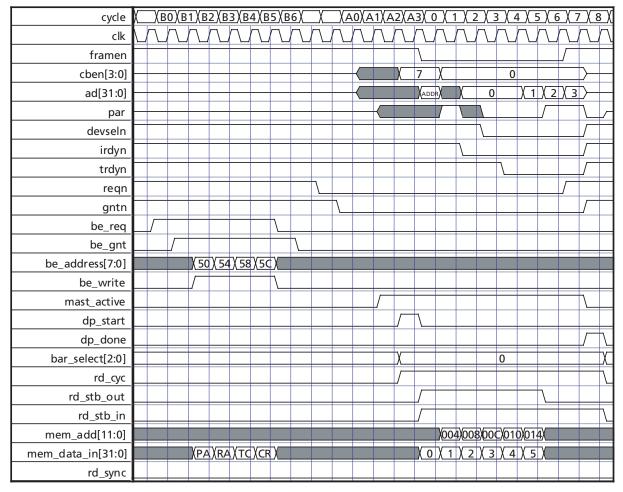

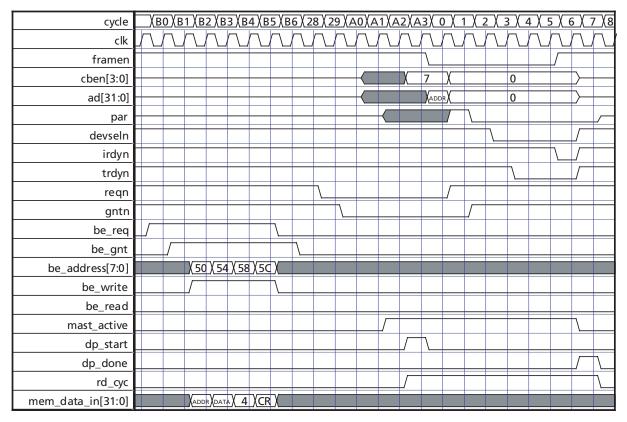

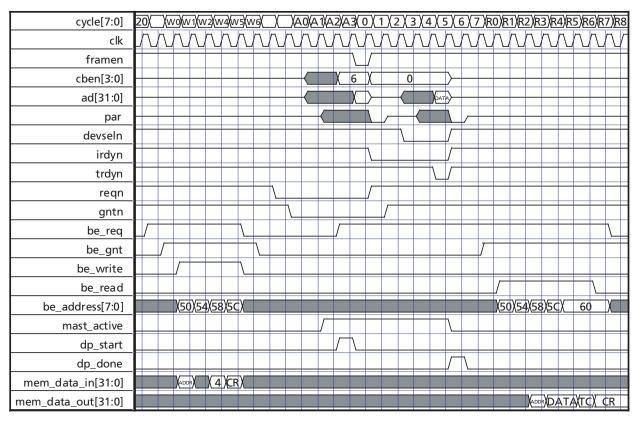

| 6 | Timing Diagrams49Burst Transfer at Maximum Transfer Rate53Burst Transfer with a Slow PCI Master55Burst Transfer with a Slow Backend57Backend-Terminated (BUSY) Cycle at Transfer Start (Target)71Backend-Terminated (ERROR) Cycle at Transfer Start (Target)73PCI Interrupt Generation79Direct DMA Transfers99Hot-Swap Sequence101 |

| 7 | PCI Configuration Space                                                                                                                                                                                                                                                                                                            |

v3.3 3

Table of Contents CorePCIF v3.6

| 8 | Testbench Operation                                                                                                                     |                          |

|---|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 9 | Implementation Hints       Clocking         Clock and Reset Networks          Assigning Pin Layout Constraints          Pin Assignments | 125<br>125<br>125        |

| A | PCI Pinout                                                                                                                              | 129                      |

| В | Synthesis Timing Constraints                                                                                                            | 131                      |

| C | Place-and-Route Timing Constraints                                                                                                      | 133                      |

| D | Verification Testbench Tests                                                                                                            | 135                      |

| E | VHDL User Testbench Procedures                                                                                                          | 137                      |

| F | Verilog User Testbench Procedures                                                                                                       | 139                      |

| G | Ordering Information                                                                                                                    |                          |

| Η | List of Document Changes                                                                                                                | 143                      |

| I | Product Support . Customer Service                                                                                                      | 145<br>145<br>145<br>145 |

|   | Index                                                                                                                                   | 147                      |

# Introduction

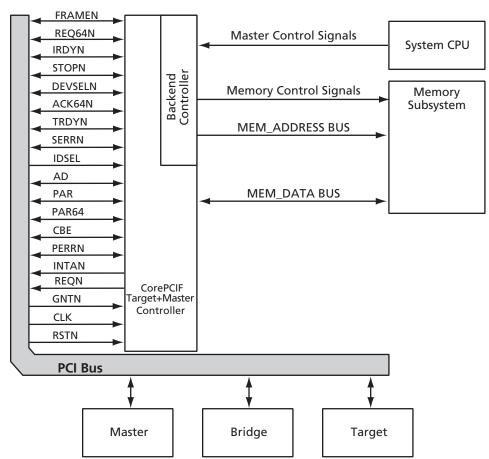

CorePCIF connects memory, FIFO, and processor subsystem resources to the main system via the PCI bus. CorePCIF is intended for use with a wide variety of peripherals where high-performance data transactions are required. Figure 1 depicts typical system applications using the core. Though CorePCIF can handle any transfer rate, most applications will operate with zero wait states. When required, wait states can be inserted automatically by a slower peripheral.

CorePCIF can implement Target and/or Master functions. The Target function allows the PCI bus to access memory devices attached to the CorePCIF backend. The Master function allows CorePCIF to move data between the backend or internal registers and the PCI bus using the internal DMA engine. The DMA engine can be programmed either from the PCI bus or directly from the backend.

CorePCIF can be customized. A variety of parameters are provided to easily change features such as memory and I/O sizes along with the PCI vendor and device IDs. A single top-level core has parameters that enable and disable functions, allowing a minimal-size core to be implemented for the required functionality. The core consists of four basic units: the Target controller, the Master controller, the DMA controller, and the backend controller. The backend controller provides the necessary control for the I/O or memory subsystem, allowing external (to the core) memory and FIFOs to be directly connected to the core.

Figure 1 · CorePCIF System Block Diagram

v3.3 5

Introduction CorePCIF v3.6

## **Core Versions**

This handbook applies to CorePCIF v3.6. The release notes provided with the core list known discrepancies between this handbook and the core release associated with the release notes.

# **CorePCIF Device Requirements**

CorePCIF includes Target and/or Master functions. The core also has an option for a built-in DMA controller.

There are eight implementations available for the core. The SMALL32 implementation is the smallest Target core possible but does not support zero-wait-state transfers; TARG32 does support zero-wait-state transfers. MAST32 is the smallest Master-only core possible. TARGDMA32 implements a typical Target and Master function. TARGMAST32 implements a fully configured core. The remaining four implementations are 64-bit versions of the 32-bit implementations. Table 1 describes example implementations.

Table 1 · Example Implementations

| Implementation | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMALL32        | 32-bit Target-only core with a single base address register (BAR). The slow read function is enabled. Interrupts, BAR overflow, and hot-swap features are disabled.                                                                                                                                                                                                                                                |

| TARG32         | 32-bit Target-only core with a single 64 kB BAR. The FIFO recovery logic is not implemented. BAR overflow logic and hot-swap features are disabled.                                                                                                                                                                                                                                                                |

| MAST32         | 32-bit Master-only core with a single 64 kB BAR. The FIFO recovery logic is not implemented. Direct DMA is enabled.                                                                                                                                                                                                                                                                                                |

| TARGDMA32      | 32-bit Target and Master function with a single 64 kB BAR. DMA registers are accessible from the PCI side and are memory-mapped in the second BAR. The FIFO recovery logic is not implemented. BAR overflow logic and hot-swap features are disabled. Backend access to the DMA registers is not implemented. Direct DMA is disabled.                                                                              |

| TARGMAST32     | 32-bit Target and Master function with five memory BARs that have variable sizes from 64 kB to 1 GB. The DMA registers are memory-mapped to the sixth BAR. All of the memory BARs include the FIFO recovery logic. The Expansion ROM address registers are also implemented. BAR overflow logic and hot-swap features are enabled. Backend access to the DMA registers is also implemented. Direct DMA is enabled. |

| TARG64         | 64-bit Target-only core with a single 64 kB BAR. The FIFO recovery logic is not implemented. BAR overflow logic and hot-swap features are disabled. Direct DMA is disabled.                                                                                                                                                                                                                                        |

| MAST64         | 64-bit Master-only core with a single 64 kB BAR. The FIFO recovery logic is not implemented. Direct DMA is disabled.                                                                                                                                                                                                                                                                                               |

| TARGDMA64      | 64-bit Target and Master function with a single 64 kB memory. DMA registers are accessible from the PCI side and are memory-mapped in the second BAR. The FIFO recovery logic is not implemented. BAR overflow logic and hot-swap features are disabled. Backend access to the DMA registers is not implemented. Direct DMA is disabled.                                                                           |

| TARGMAST64     | 64-bit Target and Master function with five memory BARs that have variable sizes from 64 kB to 1 GB. The DMA registers are memory-mapped to the sixth BAR. All of the memory BARs include the FIFO recovery logic. The Expansion ROM address registers are also implemented. BAR overflow logic and hot-swap features are enabled. Backend access to the DMA registers is also implemented. Direct DMA is enabled. |

## **Utilization Statistics**

Table 2 and Table 3 on page 8 give the CorePCIF device utilization for both 32-bit and 64-bit implementations. The numbers in these tables are typical and will vary based on the actual core configuration and the synthesis tools used. CorePCIF device utilization and performance varies, depending on which features are implemented. The core has approximately 50 configuration parameters. Table 2 (32-bit) and Table 3 on page 8 (64-bit) give example utilizations for typical implementations. The exact parameter settings are detailed in Table 4-4 on page 37.

Table 2 · 32-Bit CorePCIF Device Utilization

| I              | Family                   | Cells or Tiles |            |       | Memory Blocks | Device    | Utilization |  |

|----------------|--------------------------|----------------|------------|-------|---------------|-----------|-------------|--|

| Implementation | ranniy                   | Combinatorial  | Sequential | Total | Memory Blocks | Device    | Ctilization |  |

| SMALL32        |                          | 544            | 177        | 721   | 0             | AFS600    | 5%          |  |

| TARG32         | Fusion®                  | 661            | 203        | 864   | 2             | AGLE600   | 6%          |  |

| MAST32         | IGLOO®/e<br>ProASIC®3/E  | 1,434          | 383        | 1,817 | 2             | AGL600    | 13%         |  |

| TARGDMA32      | ProASIC3L                | 1,594          | 369        | 1,963 | 2             | A3PE600   | 14%         |  |

| TARGMAST32     |                          | 2,698          | 658        | 3,356 | 2             | A3P600    | 24%         |  |

| SMALL32        |                          | 658            | 215        | 873   | 0             | APA150    | 14%         |  |

| TARG32         |                          | 716            | 208        | 924   | 4             | APA150    | 15%         |  |

| MAST32         | ProASIC <sup>PLUS®</sup> | 1,479          | 422        | 1,901 | 4             | APA150    | 31%         |  |

| TARGDMA32      |                          | 1,644          | 377        | 2,021 | 4             | APA300    | 25%         |  |

| TARGMAST32     |                          | 3,020          | 697        | 3,717 | 4             | APA300    | 45%         |  |

| SMALL32        |                          | 350            | 178        | 528   | 0             | RTAX250S  | 12%         |  |

| TARG32         |                          | 465            | 244        | 709   | 0             | RTAX250S  | 17%         |  |

| MAST32         | RTAX-S                   | 799            | 422        | 1,221 | 0             | RTAX250S  | 29%         |  |

| TARGDMA32      |                          | 867            | 414        | 1,281 | 0             | RTAX250S  | 30%         |  |

| TARGMAST32     |                          | 2,562          | 2,206      | 4,768 | 0             | RTAX1000S | 26%         |  |

| SMALL32        |                          | 381            | 180        | 561   | 0             | AX500     | 7%          |  |

| TARG32         |                          | 453            | 210        | 663   | 1             | AX500     | 8%          |  |

| MAST32         | Axcelerator®             | 830            | 393        | 1,223 | 1             | AX500     | 15%         |  |

| TARGDMA32      |                          | 874            | 380        | 1,254 | 1             | AX500     | 16%         |  |

| TARGMAST32     |                          | 1,677          | 653        | 2,330 | 1             | AX500     | 29%         |  |

| SMALL32        |                          | 387            | 221        | 608   | 0             | RT54SX32S | 21%         |  |

| TARG32         |                          | 491            | 282        | 773   | 0             | RT54SX32S | 27%         |  |

| MAST32         | RTSX-S                   | 1,134          | 507        | 1,641 | 0             | RT54SX32S | 57%         |  |

| TARGDMA32      |                          | 966            | 465        | 1,431 | 0             | RT54SX72S | 24%         |  |

| TARGMAST32     |                          | 1,359          | 834        | 2,193 | 0             | RT54SX72S | 36%         |  |

| SMALL32        |                          | 385            | 222        | 607   | 0             | A54SX32A  | 21%         |  |

| TARG32         |                          | 494            | 285        | 779   | 0             | A54SX32A  | 27%         |  |

| MAST32         | SX-A                     | 1,111          | 507        | 1,618 | 0             | A54SX32A  | 56%         |  |

| TARGDMA32      |                          | 959            | 460        | 1,419 | 0             | A54SX72A  | 24%         |  |

| TARGMAST32     |                          | 1,352          | 834        | 2,186 | 0             | A54SX72A  | 36%         |  |

Introduction CorePCIF v3.6

Table 3 · 64-Bit CorePCIF Device Utilization

| Implementation | Family                  | Cells or Tiles |            |       | Memory Blocks  | Device            | Utilization |  |

|----------------|-------------------------|----------------|------------|-------|----------------|-------------------|-------------|--|

| Implementation | ranniy                  | Combinatorial  | Sequential | Total | Wiemory Blocks | Device            | Cimzation   |  |

| TARG64         | Fusion                  | 930            | 315        | 1,245 | 4              | AFS600            | 9%          |  |

| MAST64         | IGLOO/e                 | 1,686          | 498        | 2,184 | 4              | AGLE600<br>AGL600 | 16%         |  |

| TARGDMA64      | ProASIC3/E<br>ProASIC3L | 1,852          | 484        | 2,336 | 4              | A3PE600           | 17%         |  |

| TARGMAST64     | TIOASICSL               | 2,989          | 772        | 3,761 | 4              | A3P600            | 27%         |  |

| TARG64         |                         | 961            | 319        | 1,280 | 8              | APA150            | 21%         |  |

| MAST64         | ProASIC <sup>PLUS</sup> | 1,770          | 542        | 2,312 | 8              | APA150            | 38%         |  |

| TARGDMA64      | ProASIC                 | 1,962          | 500        | 2,462 | 8              | APA150            | 40%         |  |

| TARGMAST64     |                         | 3,173          | 814        | 3,987 | 8              | APA300            | 49%         |  |

| TARG64         |                         | 634            | 387        | 1,021 | 0              | RTAX250S          | 24%         |  |

| MAST64         | DELAY C                 | 1,002          | 565        | 1,567 | 0              | RTAX250S          | 37%         |  |

| TARGDMA64      | RTAX-S                  | 1,087          | 553        | 1,640 | 0              | RTAX1000S         | 9%          |  |

| TARGMAST64     |                         | 3,524          | 3,858      | 7,382 | 0              | RTAX1000S         | 41%         |  |

| TARG64         |                         | 642            | 317        | 959   | 2              | AX500             | 12%         |  |

| MAST64         | Axcelerator             | 1,021          | 502        | 1,523 | 2              | AX500             | 19%         |  |

| TARGDMA64      | Axcelerator             | 1,087          | 493        | 1,580 | 2              | AX500             | 20%         |  |

| TARGMAST64     |                         | 1,874          | 765        | 2,639 | 2              | AX500             | 33%         |  |

| TARG64         |                         | 693            | 456        | 1,149 | 0              | A54SX32A          | 40%         |  |

| MAST64         | SX-A                    | 1,095          | 682        | 1,777 | 0              | A54SX72A          | 29%         |  |

| TARGDMA64      | δΛ-A                    | 1,201          | 645        | 1,846 | 0              | A54SX72A          | 31%         |  |

| TARGMAST64     |                         | 1,711          | 1,200      | 2,911 | 0              | A54SX72A          | 48%         |  |

# **Performance Statistics**

Table 4 and Table 7 on page 12 give the device speed grades required to meet either 33 MHz or 66 MHz PCI operation for the 32-bit and 64-bit cores for the three operating environments supported by Actel. Not all families support 64-bit or 66 MHz operation.

Table 4 · Device Speed Grade Requirements

|                 | Family                          | Commercial | Industrial | Military |

|-----------------|---------------------------------|------------|------------|----------|

|                 | Fusion                          | STD        | STD        |          |

|                 | IGLOO/e                         | STD        | STD        |          |

|                 | ProASIC3/E/L                    | STD        | STD        |          |

| 22 MH_ 22 L:4   | ProASIC <sup>PLUS</sup>         | STD        | STD        | STD      |

| 33 MHz 32-bit   | RTAX-S                          | N/A        | N/A        | STD      |

|                 | Axcelerator                     | STD        | STD        | STD      |

|                 | RTSX-S                          | N/A        | N/A        | -1       |

|                 | SX-A                            | STD        | STD        | STD      |

|                 | Fusion                          | STD        | STD        |          |

|                 | IGLOO/e                         | STD        | STD        |          |

|                 | ProASIC3/E/L                    | STD        | STD        |          |

| 33 MHz 64-bit   | ProASIC <sup>PLUS</sup>         | STD        | STD        | STD      |

| 33 WIFIZ 64-DIT | RTAX-S                          | N/A        | N/A        | STD      |

|                 | Axcelerator                     | STD        | STD        | STD      |

|                 | RTSX-S                          | N/A        | N/A        | N/A      |

|                 | SX-A                            | STD        | STD        | STD      |

|                 | Fusion                          | -2         | -2         |          |

|                 | IGLOO/e                         | N/A        | N/A        |          |

|                 | ProASIC3/E                      | -2         | -2         | N/A      |

|                 | ProASIC <sup>PLUS</sup>         | N/A        | N/A        | N/A      |

| // MII 22 1:    | RTAX-S (RTAX250S)               | N/A        | N/A        | -1       |

| 66 MHz 32-bit   | RTAX-S (RTAX1000S to RTAX4000S) | N/A        | N/A        | N/A      |

|                 | Axcelerator (AX125 to AX500)    | -1         | -1         | -1       |

|                 | Axcelerator (AX1000 to AX2000)  | -2         | -2         | -2       |

|                 | RTSX-S                          | N/A        | N/A        | N/A      |

|                 | SX-A                            | N/A        | N/A        | N/A      |

Introduction CorePCIF v3.6

Table 4 · Device Speed Grade Requirements (Continued)

|                  | Family                          | Commercial | Industrial | Military |

|------------------|---------------------------------|------------|------------|----------|

|                  | Fusion                          | -2         | -2         |          |

|                  | IGLOO/e                         | N/A        | N/A        |          |

|                  | ProASIC3/E                      | -2         | -2         | N/A      |

|                  | ProASIC <sup>PLUS</sup>         | N/A        | N/A        | N/A      |

| 66 MHz 64-bit    | RTAX-S (RTAX250S)               | N/A        | N/A        | -1       |

| 00 WII 12 04-DIL | RTAX-S (RTAX1000S to RTAX4000S) | N/A        | N/A        | N/A      |

|                  | Axcelerator (AX125 to AX500)    | -1         | -1         | -1       |

|                  | Axcelerator (AX1000 to AX2000)  | -2         | -2         | -2       |

|                  | RTSX-S                          | N/A        | N/A        | N/A      |

|                  | SX-A                            | N/A        | N/A        | N/A      |

The PCI specification timing requirements are given in Table 5.

Table 5 · PCI Bus Timing

| Signals                         | Set    | tup    | Н      |        | Clock to Out |        |

|---------------------------------|--------|--------|--------|--------|--------------|--------|

| oighais .                       | 33 MHz | 66 MHz | 33 MHz | 66 MHz | 33 MHz       | 66 MHz |

| Bussed Signals                  | 7 ns   | 3 ns   | 0 ns   | 0 ns   | 11 ns        | 6 ns   |

| Non-Bussed Signals (e.g., GNTN) | 10 ns  | 5 ns   | 0 ns   | 0 ns   | 11 ns        | 6 ns   |

# I/O Requirements

Table 6 gives the I/O requirements for CorePCIF. The number of device I/O pins required for the PCI interface varies, depending on the bus width as well as whether the core supports Target and/or Master functions. The number of backend device I/O pins that the core requires depends on the core interface. For instance, a device that implements a PCI-to-serial communication channel may only require a single device I/O pin, whereas a PCI-to-memory interface may require many I/O pins. Table 6 shows the maximum number of I/O pins, assuming all the core backend pins are connected to device I/O pins.

Table 6 · CorePCIF I/O Requirements

|                                                 | I/O Count |         |      |       |      |  |

|-------------------------------------------------|-----------|---------|------|-------|------|--|

| Core                                            | PCI       | Backend |      | Total |      |  |

|                                                 | 1 (1      | Min.    | Max. | Min.  | Max. |  |

| 32-bit Target                                   | 48        | 1       | 146  | 49    | 194  |  |

| 64-bit Target                                   | 88        | 1       | 219  | 89    | 307  |  |

| 32-bit Master with backend interface            | 49        | 1       | 162  | 50    | 211  |  |

| 64-bit Master with backend interface            | 88        | 1       | 235  | 89    | 323  |  |

| 32-bit Target and Master                        | 50        | 1       | 146  | 51    | 196  |  |

| 64-bit Target and Master                        | 89        | 1       | 219  | 90    | 308  |  |

| 32-bit Target and Master with backend interface | 50        | 1       | 162  | 51    | 212  |  |

| 64-bit Target and Master with backend interface | 89        | 1       | 235  | 90    | 324  |  |

Introduction CorePCIF v3.6

# **Electrical Requirements**

CorePCIF supports both the 3.3 V and 5.0 V PCI specifications when operating at 33 MHz; at 66 MHz, the PCI bus must operate at 3.3 V. The SX-A and RTSX-S families have I/O buffers that directly support 5.0 V operation. Other families in 5.0 V PCI environments may require external voltage level translator devices, or may not be supported. See Table 7 for details.

CorePCIF also supports CardBus functionality. Contact Actel Technical Support for advice on silicon that supports the CardBus electrical specifications.

Table 7 · Supported Electrical Environments

| Clock Speed | Family                  | PCI Voltage with Direct FPGA Connection | PCI Voltage with<br>Level Translators |

|-------------|-------------------------|-----------------------------------------|---------------------------------------|

|             | Fusion                  | 3.3                                     | 3.3 and 5.0                           |

|             | IGLOO/e                 | 3.3                                     | 3.3 and 5.0                           |

|             | ProASIC3/E/L            | 3.3                                     | 3.3 and 5.0                           |

| 33 MHz      | ProASIC <sup>PLUS</sup> | 3.3                                     | 3.3 and 5.0                           |

| 33 MHZ      | RTAX-S                  | 3.3                                     | 3.3 and 5.0                           |

|             | Axcelerator             | 3.3                                     | 3.3 and 5.0                           |

|             | RTSX-S                  | 3.3 and 5.0                             | 3.3 and 5.0                           |

|             | SX-A                    | 3.3 and 5.0                             | 3.3 and 5.0                           |

|             | Fusion                  | 3.3                                     | 3.3                                   |

|             | IGLOO/e                 | 3.3                                     | 3.3                                   |

|             | ProASIC3/E              | 3.3                                     | 3.3                                   |

| 66 MHz      | ProASIC <sup>PLUS</sup> | Not supported                           | Not supported                         |

| 00 MHZ      | RTAX-S                  | 3.3                                     | 3.3                                   |

|             | Axcelerator             | 3.3                                     | 3.3                                   |

|             | RTSX-S                  | Not supported                           | Not supported                         |

|             | SX-A                    | Not supported                           | Not supported                         |

# **Functional Block Descriptions**

# **Functional Description**

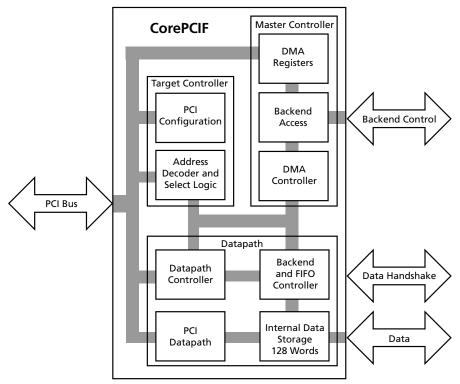

CorePCIF consists of three major functional blocks, shown in Figure 1-1. These blocks are the Target Controller, Master Controller, and Datapath. With both a Target and Master, all three blocks are required. Otherwise, only the Datapath and either the Target or Master function are required.

Figure 1-1 · CorePCIF Block Diagram

#### **Target Controller**

The Target controller implements the PCI Target function. It contains two sub-blocks: the PCI configuration space and the address decoder logic. The configuration block implements a "type 0" PCI configuration space, supporting up to six base address registers and the Expansion ROM register.

The actual registers implemented are described in Table 7-1 on page 103.

The address decoder block monitors the PCI bus for address cycles and compares the address with the base address registers configured in the configuration space. A match signals the datapath controller to start a PCI cycle.

#### **Master Controller**

The Master controller implements the PCI Master function. It contains three sub-blocks: the DMA registers, DMA controller, and backend access logic. The DMA register block implements the four 32-bit registers that control the DMA controller. These registers can be programmed either from the PCI bus or from the backend.

The DMA controller implements a PCI-compliant Master function that can burst up to  $2^{32}$  bytes of data without intervention. The controller will stop a DMA burst automatically if the backend runs out of data, and restart when data is available.

v3.3 13

CorePCIF v3.6

The backend access block allows a processor connected to the core backend to access the DMA registers and initiate a DMA transfer.

### **Datapath**

The datapath block provides the data control and storage path between the backend and the PCI bus. It contains four sub-blocks: the PCI datapath, the PCI datapath controller, the backend and FIFO controller, and the internal data storage memory.

The PCI datapath controller is responsible for controlling the PCI control signals and coordinating the data transfers with the backend controller for both Target and Master operations.

The PCI datapath block selects which data should be routed to the PCI bus. Data may come from the PCI configuration block, the DMA register block, or the internal data storage. The datapath block also generates and verifies the PCI parity signals.

The backend controller implements the FIFO control logic. This interfaces to the user's backend logic and moves data from the backend interface into the internal storage. It also includes logic that monitors how much data is actually transferred on the PCI bus. The backend controller can recover data that has not actually been transferred, such as when a Master transfer is terminated with a disconnect without data.

### **Internal Data Storage**

CorePCIF includes a 64-word internal memory block that is used to store data being moved from the backend to the PCI bus. Data being transferred from the PCI bus to the backend is not stored internally in the core.

This data storage performs two functions. First, it implements a four-word FIFO that decouples the PCI data transfers from the backend data transfers, thereby increasing throughput. Second, it provides storage for the FIFO recovery logic used to prevent data loss when the backend is connected to a standard FIFO.

Each of the seven supported BARs (six BARs and the Expansion ROM) is allocated eight words of memory. BAR 0 is allocated locations 0–7, BAR 1 is allocated 8–15, etc. The Expansion ROM is allocated locations 48–55, and the remaining eight locations are not used. Each word is 32 bits wide for 32-bit implementations and 64 bits wide for 64-bit implementations.

For the Axcelerator, ProASIC PLUS, ProASIC3, and ProASIC3E families, the data storage is implemented using FPGA memory resources. For SX-A and RTSX-S families, the storage is implemented using FPGA logic resources. For the RTAX-S family, the storage can be implemented using FPGA logic resources or memory resources. Each BAR will require at least 256 logic modules to implement the storage. Storage is only required for the enabled BARs.

When the SLOW\_READ parameter is set, the internal data storage is not implemented, eliminating the need for FPGA memory resources. Instead, the data throughput rate is reduced to prevent data loss.

## **CorePCIF Target Function**

The CorePCIF Target function acts as a slave on the PCI bus. The Target controller monitors the bus and checks for hits to the configuration space or the address space defined in its BARs. When a hit is detected, the Target controller notifies the backend and then acts to control the flow of data between the PCI bus and the backend.

### **Supported Target Commands**

Table 1-1 lists the PCI commands supported in the CorePCIF Target implementation.

Table 1-1 · Supported PCI Target Commands

| CBEN[3:0] | Command Type                | Supported |

|-----------|-----------------------------|-----------|

| 0000      | Interrupt Acknowledge       | No        |

| 0001      | Special Cycle               | No        |

| 0010      | I/O Read                    | Yes       |

| 0011      | I/O Write                   | Yes       |

| 0100      | Reserved                    | -         |

| 0101      | Reserved                    | -         |

| 0110      | Memory Read                 | Yes       |

| 0111      | Memory Write                | Yes       |

| 1000      | Reserved                    | -         |

| 1001      | Reserved                    | _         |

| 1010      | Configuration Read          | Yes       |

| 1011      | Configuration Write         | Yes       |

| 1100      | Memory Read Multiple        | Yes       |

| 1101      | Dual Address Cycle          | No        |

| 1110      | Memory Read Line            | Yes       |

| 1111      | Memory Write and Invalidate | Yes       |

#### I/O Read (0010) and Write (0011)

The I/O Read command is used to read data mapped into I/O address space. The I/O Write command is used to write data mapped into I/O address space. In this case, the write is qualified by the byte enables.

#### Memory Read (0110) and Write (0111)

The Memory Read command is used to read data in memory-mapped address space. The Memory Write command is used to write data mapped into memory address space. In this case, the write is qualified by the byte enables.

#### Memory Read Multiple (1100) and Memory Read Line (1110)

The Memory Read Multiple and Memory Read Line commands are treated in the same manner as a Memory Read command. Typically, the bus master will use these commands when data is prefetchable.

#### **Memory Write and Invalidate (1111)**

The Memory Write and Invalidate command is treated in the same manner as a Memory Write command.

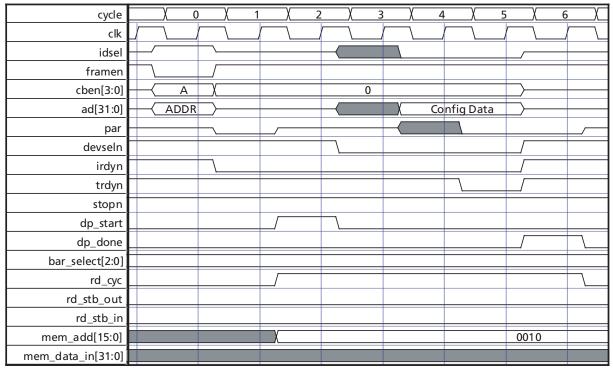

#### **Configuration Read (1010) and Write (1011)**

The Configuration Read command is used to read the configuration space of each device. The Configuration Write command is used to write information into the configuration space. The device is selected if its IDSEL signal is asserted and AD[1:0] are set to '00'. Additional address bits are defined as follows:

- AD[7:2] contain one of 64 DWORD addresses for the configuration registers.

- AD[10:8] indicate which device of a multi-function agent is addressed. The core does not support multi-function devices, and these bits should be '000'.

- · AD[31:11] are ignored.

The core supports burst configuration read and write cycles.

#### **Disconnects and Retries**

The CorePCIF Target will perform either single-DWORD or burst transactions, depending on the request from the system Master. If the backend is unable to deliver data quickly enough, the Target will respond with either a PCI retry or disconnect, with or without data. If the system Master requests a transfer that the backend is not able to perform, a Target abort can be initiated by the backend.

## **CorePCIF Master Function**

The Master function in CorePCIF is designed to do the following:

- · Arbitrate for the PCI bus

- · Initiate a PCI cycle

- · Pass dataflow control to the Target controller

- End the transfer when the DMA count has been exhausted

- · Allow the backend hardware to stop and start DMA cycles

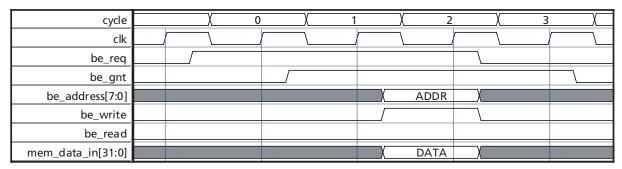

Master transfers can be initiated directly from the backend interface, or another PCI device may program the DMA engine to initiate a PCI transfer.

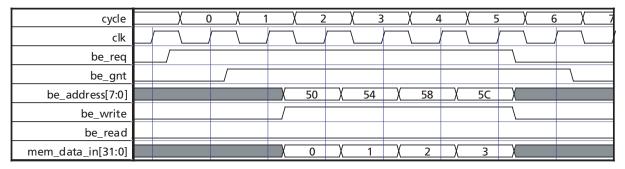

#### **Backend Interface**

Through the backend interface (BE\_REQ, BE\_GNT, BE\_ADDRESS, etc.), an external processor can access the DMA Master control registers and initiate a Master transfer. This interface also allows the complete PCI configuration space to be accessed so the core can be self-configured by a backend processor. This is required when the core is used to implement the PCI device responsible for configuring the PCI bus. A hardware lock (BE\_CFGLOCK) is provided for safety reasons to prevent the backend from changing the values in the PCI configuration space.

### **Supported Master Commands**

The CorePCIF Master controller is capable of performing configuration, I/O, memory, and interrupt acknowledge cycles. Data transfers can be up to 2<sup>32</sup> bytes.

The Master controller will attempt to complete the transfer using a maximum-length PCI burst unless the maximum burst length bits are set in the control register. If the addressed Target is unable to complete the transfer and performs a retry or disconnect, the Master control will restart the transfer and continue from the last known good transfer. If a Target does not respond (no DEVSELn asserted) or responds with a Target abort cycle, the Master controller will abort the current transaction and report it as an error in the control register.

### **DMA Master Registers**

There are four 32-bit registers used to control the function of the CorePCIF Master. The first register is the PCI address register. The second register is the RAM or backend address register. These two registers provide the source/destination addressing for all data transfers. The third register contains the number of words to be transferred, and the final control register defines the type and status of a Master transfer. These registers are cleared on reset. They are defined in detail in Table 7-15 on page 110 through Table 7-21 on page 112.

The DMA registers can be accessed from either the PCI or the backend interface. The address locations for the DMA registers are listed in Table 1-2. When these registers are accessible from the PCI bus, they can be memory-, I/O-, or configuration-mapped. The DMA\_REG\_LOC, DMA\_REG\_BAR, and BACKEND parameters control access to these registers.

The complete configuration space can be read when BAR access to these registers is enabled, but writing can be done only to the four DMA control registers.

When the BACKEND parameter is set, the four registers and the complete PCI configuration space can be accessed via the backend (Table 1-2).

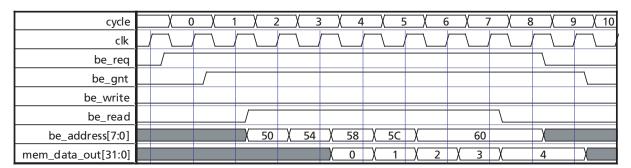

| Register Name                | Address |

|------------------------------|---------|

| PCI address                  | 50h     |

| RAM address or data register | 54h     |

| DMA transfer length          | 58h     |

| DMA control register         | 5Ch     |

Table 1-2 · DMA Register Addresses

#### **Master Transfers**

The CorePCIF Master function supports full DMA transfers to and from the backend interface and initiates direct PCI transfers

When normal DMA transfers are used, CorePCIF writes each data word to or fetches it from memory through its backend interface. This allows data to be transferred directly from the PCI bus to or from backend memory blocks. In some circumstances, this is inefficient, especially if a processor connected to the backend simply wants to carry out a single-word PCI read or write. In this case, the processor writes the data word to a known location in its memory map. It then programs the DMA controller to perform a single-word DMA transfer. The DMA controller accesses the memory location to obtain the data value; this may require the processor to stop operating while the PCI core accesses the memory to complete the PCI transfer.

When direct DMA transfers are enabled, the processor simply writes the PCI address and data into the core and starts the transfer by writing to the control register, setting the DMA\_BAR value to '111'. The core then fetches the data value or writes it to the internal register during the PCI transfer. Access to the backend memory is not required to complete the DMA transfer.

Direct DMA transfer supports only 32-bit transfers. When using 64-bit versions of the core, the 64-bit transfer mode select bit in the DMA control register should not be set if Direct DMA mode is enabled.

### **Master Byte Commands**

CorePCIF can either transfer multiple whole DWORDs (QWORDs for 64-bit transfers) or perform a single DWORD or QWORD transfer with one or more byte enables active.

When multiple words are to be transferred—the DMA transfer length register is greater than four bytes (eight bytes for 64-bit)—the byte enable bits in the DMA control register should be programmed to all ones. All four or eight (64-bit) bytes will be transferred in each data cycle.

If a partial-word read or write is required, the DMA transfer length register should be programmed to four bytes (or eight for 64-bit) and the correct bits set in the byte enable bits in the DMA control register. The DMA engine will transfer a single word, setting the appropriate byte enable bits on both the backend and the PCI interface.

If a non-aligned DMA transfer is required, three separate DMA operations should be performed. The first DMA transfer should be configured to transfer a single DWORD with just the initial bytes enabled. The second DMA should transfer the remaining complete DWORDs with all bytes enabled. A third DMA transfer should transfer the final DWORD with just the remaining bytes enabled. For example, a transfer starting at address 3 and ending at address 12 would require three operations. The first DMA transfer would enable byte 3 only, the second transfer would transfer two DWORD addresses to bytes 4 through 11, and the third DMA transfer would enable byte 0 and transfer address 12.

# **CardBus Support**

CorePCIF directly supports CardBus functional requirements. Two top-level parameters, CIS\_UPPER and CIS\_LOWER, specify the 32-bit configuration space setting for the CIS pointer. CIS\_UPPER sets the upper 16 bits, and CIS\_LOWER sets the lower 16 bits.

The CIS address space must be mapped to one of the BARs or the Expansion ROM. It may not be mapped to configuration space, which means the lower three bits of the CIS pointer (i.e., the lower three bits of CIS\_LOWER) must not be set to '000'. This allows the user to implement the CIS address space as one of the external backend BAR memory spaces.

When CardBus support is enabled, the IDSEL core input is disabled. CardBus does not require IDSEL to be active for configuration cycles.

# **CompactPCI Hot-Swap Support**

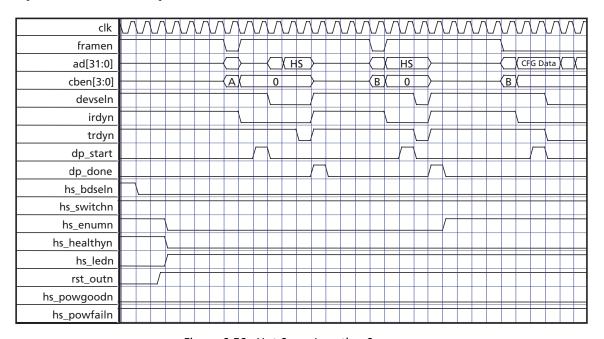

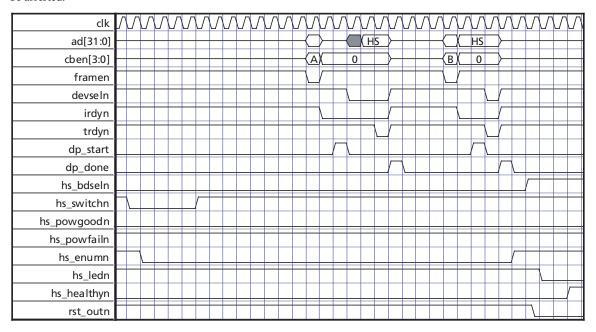

CorePCIF supports the CompactPCI Hot-Swap PICMG 2.1 R2.0 standard; additional inputs and outputs are provided to support this standard. When enabled, the core includes the hot-swap capabilities register in the configuration space and a state machine that implements the hardware connection process defined in the PICMG Hot-Swap specification. The insertion and extraction sequences are shown in Figure 6-56 on page 101 and Figure 6-57 on page 102.

## **CorePCIF Backend Dataflow**

CorePCIF has a very flexible backend interface that supports various transfer rates as well as FIFOs. To decouple the backend data transfers from the PCI transfers, CorePCIF implements an eight-stage FIFO for each BAR. During normal operation, the FIFO stores up to four data words, the remaining four locations being used for the FIFO recovery mechanism. This is implemented using FPGA memory resources in all families except SX-A, RTSX-S, and RTAX-S.

#### **Burst Transfers**

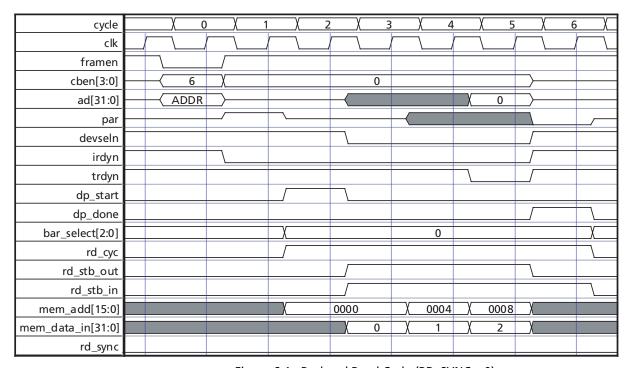

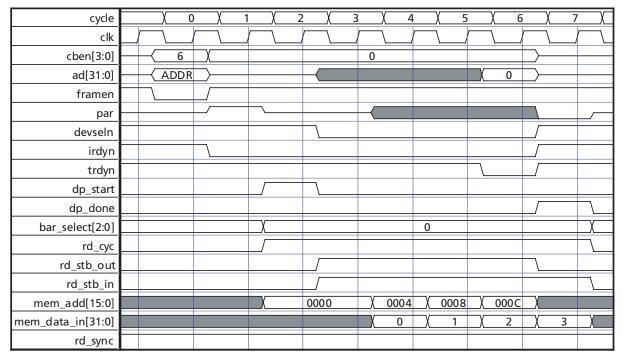

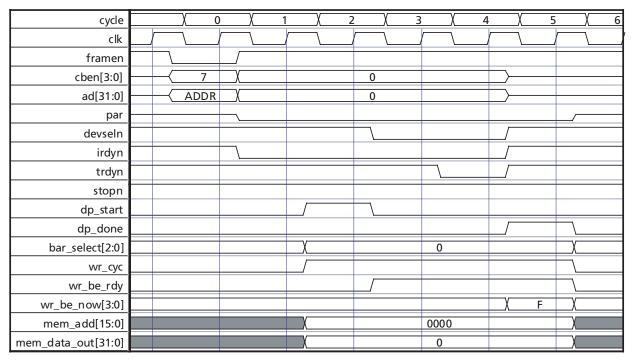

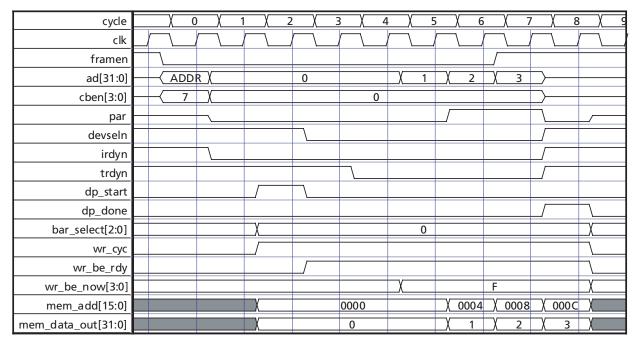

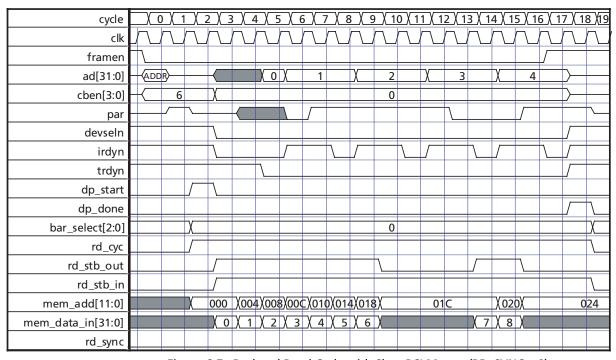

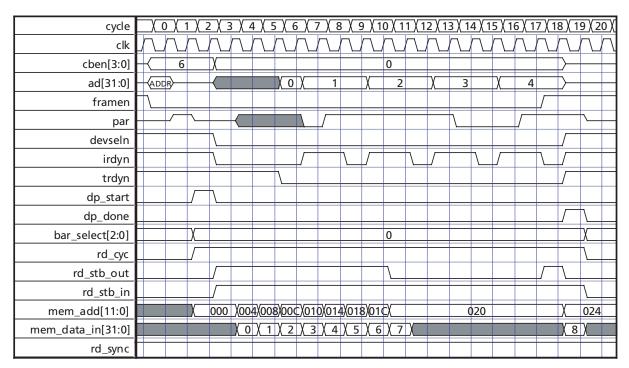

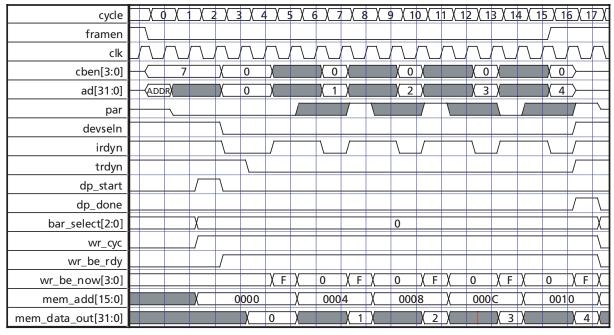

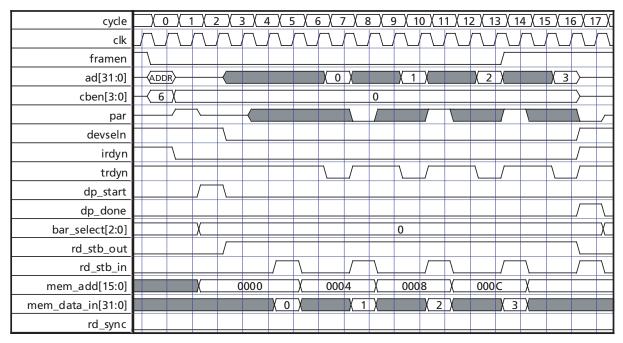

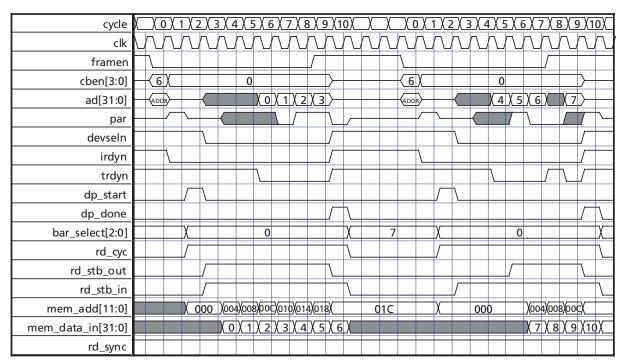

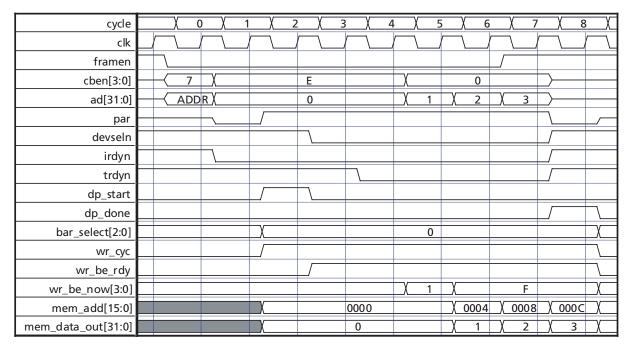

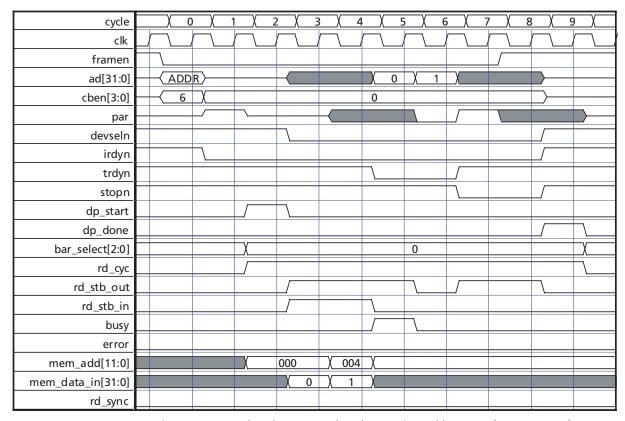

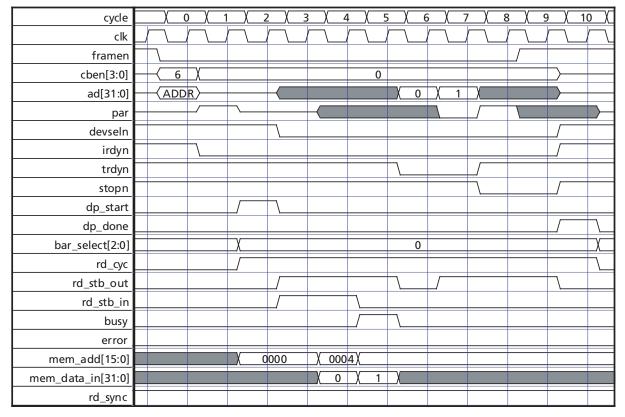

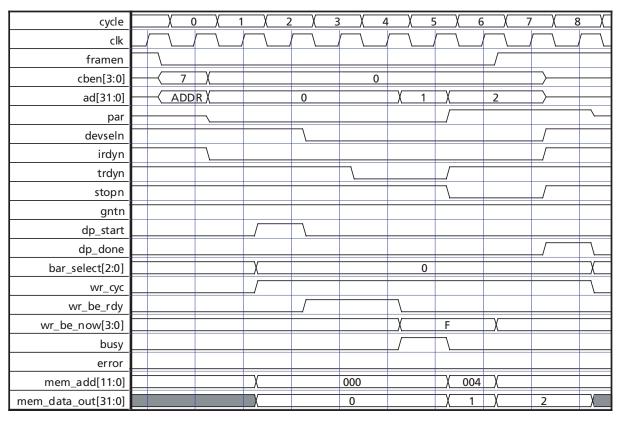

CorePCIF is capable of bursting data from the PCI bus to the backend or vice versa. During transfers to the backend, the WR\_BE\_RDY and WR\_BE\_NOW signals are used to control the dataflow. When the backend asserts WR\_BE\_RDY, the core is allowed to write data to the backend by asserting WR\_BE\_NOW. A separate WR\_BE\_NOW signal is provided for each byte.

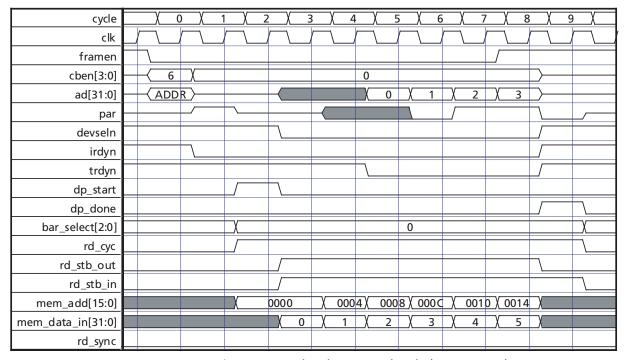

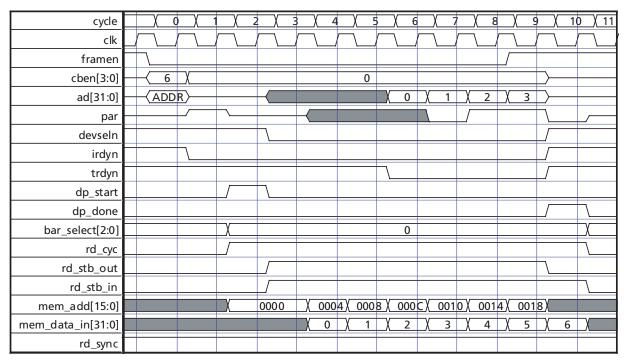

For transfers from the backend, RD\_STB\_IN and RD\_STB\_OUT control the dataflow. When both of these signals are active, data is transferred from the backend into the core.

CorePCIF v3.6

### **Byte-Controlled Transfers**

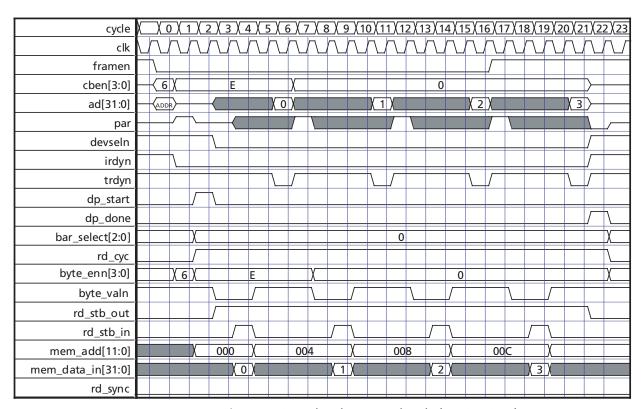

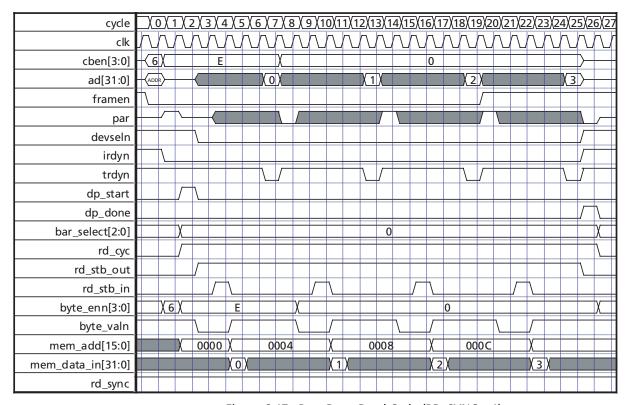

CorePCIF supports both write- and read-controlled byte transfers to the backend. When data is written to the backend, four (eight for 64-bit operations) write strobes (WR\_BE\_NOW) are provided, indicating which bytes should be written.

When data is read from the backend interface, the BYTE\_ENN and BYTE\_VALN signals can be used to control the byte reads. The backend should wait until BYTE\_VALN is active (LOW) and then use the four (eight for 64-bit) BYTE\_ENN signals (active low) to control the data read. Using the BYTE\_VALN signal prevents the core from bursting data every clock cycle; in that case, data will be transferred once every four clock cycles at best.

#### **Dataflow Control**

CorePCIF allows the backend to stop data transfers in Master and Target mode, and to initiate transfers in Master mode. In Target mode, the BUSY signal can be used to terminate a data transfer so it will be retried. The ERROR signal can be used to simply terminate a transfer.

Likewise, in Master mode, the STOP\_MASTER signal can be used to terminate a data transfer. The WR\_BUSY\_MASTER and RD\_BUSY\_MASTER signals can be used to delay a DMA transfer from starting. If STOP\_MASTER and RD\_BUSY\_MASTER are connected to a FIFO empty signal, the DMA engine will automatically stop a DMA cycle when the FIFO becomes empty and restart it when the FIFO becomes non-empty. This allows the core to move data from a FIFO to PCI memory without any host intervention.

## **FIFO Recovery Logic**

The CorePCIF backend interface directly supports the connection of external FIFOs using internal FPGA FIFO memories or external FIFO devices. To prevent data loss, CorePCIF includes optional FIFO recovery logic for each BAR. In normal burst operations, the core reads data from the backend at the same time as previous data is being transferred on the PCI bus. When the Master terminates the Target transfer, it is likely that data has been read from the FIFO and not transferred on the PCI bus (Figure 6-5 on page 54). Without recovery logic, this data would be lost; however, if the FIFO recovery logic is enabled (Figure 6-14 on page 61), the core stores this data until the next Target access to the same BAR. Data loss also potentially occurs when the core is operating in Master mode. In this case, the core also needs to recover data lost due to PCI cycles that are terminated with a disconnect without data cycle.

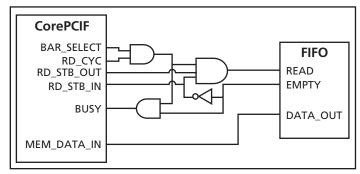

Figure 1-2 on page 20 and Figure 1-3 on page 20 show how to connect a FIFO to the backend interface, supporting Target and Master transfers. In Target mode, the FIFO empty signal is used to assert the BUSY input while the FIFO is empty and to assert RD\_STB\_IN when data is available.

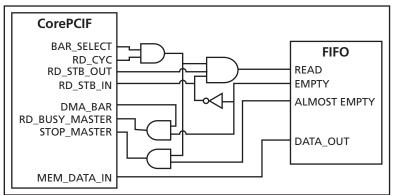

In Master mode, the FIFO empty signal is used to assert the RD\_BUSY\_MASTER input while the FIFO is empty, preventing a DMA cycle from starting, and to assert RD\_STB\_IN when data is available. The FIFO almost empty signal is used to assert STOP\_MASTER, which will cause the current DMA cycle to be terminated as soon as possible. Additional data words may be read from the backend after STOP\_MASTER has been asserted.

If both Master and Target transfers will be used, the connections in both Figure 1-2 and Figure 1-3 should be implemented.

Figure 1-2 · External FIFO Connection (Target mode)

Figure 1-3 · External FIFO Connection (Master mode)

## **Example System Implementation**

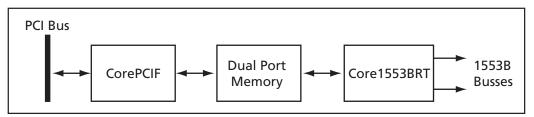

CorePCIF provides an extremely flexible PCI interface that can be configured in many ways. Figure 1-4 shows a PCI-to-1553 interface. In this example, CorePCIF is configured as a Target with a single memory BAR used to access the Core1553BRT memory.

Figure 1-4 · Simple Target Implementation

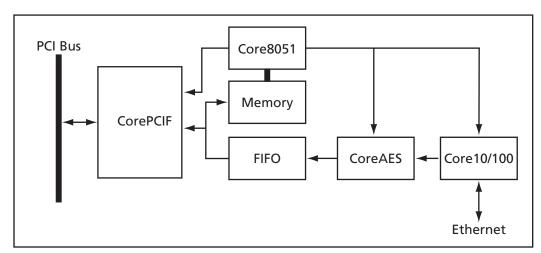

A more complex system is shown in Figure 1-5. In this case, the core supports both Target and Master operation. Core8051 is connected to the backend interface, allowing it to initiate PCI cycles. Core8051 is used to control the AES encryption core and the Core10/100 Ethernet interface. CorePCIF has two memory BARs configured. The first allows the PCI interface to access the 8051 memory space, and the second reads data from the FIFO.

Figure 1-5 · Master and Target Implementation

# **Core Structure**

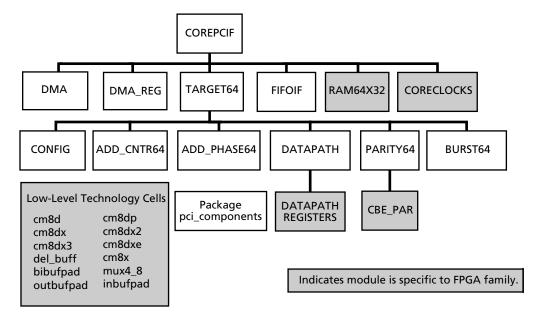

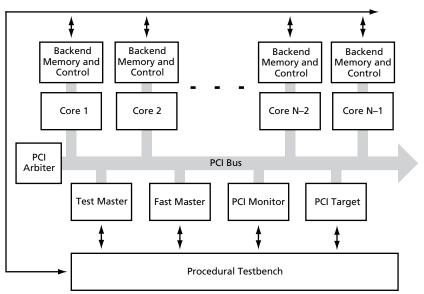

This chapter describes the internal core structure and associated source files.

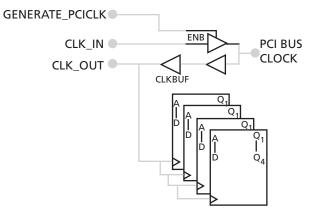

As shown in Figure 2-1, the unshaded modules are common to all FPGA families; the shaded modules are specific to each family. This is required to consistently meet the PCI timing constraints. The shaded modules are optimized specifically for each of the supported logic families. The low-level technology cells are used in the higher-level modules.

Figure 2-1 · CorePCIF Structure

Table 2-1 on page 24 provides details for each of the common source modules and the functions they implement. Table 2-2 on page 25 provides the details of the FPGA technology files. Table 2-2 on page 25 provides details of a few high-level source files not directly used by the core but provided to create test databases.

v3.3 23

Core Structure CorePCIF v3.6

Table 2-1 · CorePCIF Common Source Files

| Common Files   | Description                                                                                                                                                                                                                                            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| corepcif       | This is the top level of the core. It includes all the top-level ports. Parameters will enable and disable the Target, Master, and backend functions as well as switching between 32- and 64-bit operation.                                            |

| pci_components | This is the VHDL package that contains the component declarations used within the core along with some common type conversion functions.                                                                                                               |

| fifoif         | This is the control logic that manages internal data storage and performs FIFO recovery cycles.                                                                                                                                                        |

| target64       | This is the top level of the main PCI Target function.                                                                                                                                                                                                 |

| burst64        | This is the main control logic used to handle the PCI protocol and manage data transfers to and from the PCI bus.                                                                                                                                      |

| add_cntr64     | This is the main address counter that tracks both the current PCI and backend addresses.                                                                                                                                                               |

| add_phase64    | This block compares the PCI address during an address phase to detect whether the configuration space or one of the BARs on the Target is being addressed. It also contains the logic to detect BAR overflows so a Target disconnect can be triggered. |

| config         | This block contains the registers required to implement PCI configuration space.                                                                                                                                                                       |

| datapath       | This block routes the data between the backend interface or memory buffer and the PCI bus. It provides a data storage register used to recover when transferred data are stalled.                                                                      |

| parity64       | This block creates the top-level structure for parity generation and checking. The parity generation and checking is done using the cbe_par module.                                                                                                    |

| dma            | This is the main Master control logic. It contains state machines and counters that control the DMA engine and initiate PCI cycles.                                                                                                                    |

| dma_reg        | This module contains the four DMA control registers and the main DMA transfer counters.                                                                                                                                                                |

Table 2-2 · Technology-Specific Source Files

| FPGA Specific Files | Description                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bibufpad            | This module contains a bidirectional I/O pad.                                                                                                                                         |

| cbe_par             | This block implements a PCI parity generator and checker. The 36-input parity tree is hand-optimized to obtain the most efficient implementation for each FPGA family.                |

| cm8d                | This is a low-level FPGA technology cell implementing a four-input multiplexer and register with clear.                                                                               |

| cm8dp               | This is a low-level FPGA technology cell implementing a four-input multiplexer and register with preset.                                                                              |

| cm8dx               | This is a low-level FPGA technology cell implementing a four-input multiplexer and register with clear.                                                                               |

| cm8dx2              | This is a low-level FPGA technology cell implementing a four-input multiplexer and register with clear, with some inputs tied or shared.                                              |

| cm8dx3              | This is a low-level FPGA technology cell implementing a four-input multiplexer and register with clear, with some inputs tied or shared.                                              |

| cm8dxe              | This is a low-level FPGA technology cell implementing a four-input multiplexer and register with enable and clear.                                                                    |

| cm8x                | This is a low-level FPGA technology cell implementing a four-input multiplexer.                                                                                                       |

| coreclocks          | This module contains the global and clock buffers.                                                                                                                                    |

| datapath_registers  | This module implements the datapath registers used to interface to the PCI bus.                                                                                                       |

| del_buff            | This module contains a delay element used to insert delays to control the PCI hold times. The amount of inserted delay for all critical PCI input paths can be adjusted in this file. |

| family              | This is a VHDL package or Verilog include file that sets the FPGA family to enable some family-specific optimizations.                                                                |

| inbufpad            | This module contains an input I/O pad.                                                                                                                                                |

| mux4_8              | This is a low-level FPGA technology cell implementing eight four-input multiplexers.                                                                                                  |

| outputpad           | This module contains an output I/O pad.                                                                                                                                               |

| ram64x32            | This module contains a 64×32 RAM using the appropriate FPGA memory blocks.                                                                                                            |

Table 2-3 · CorePCIF Miscellaneous Source Files

| Miscellaneous Files | Description                                                                                                                                                                                                                                                                                          |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pcicoretest         | This is a top-level wrapper module that creates a simple top-level design with just the PCI I/O pins used for creating the example layout databases in the release. It connects all PCI interface signals to top-level ports, and then all interface signals to the loopback module.                 |

| loopback            | This module is used in the example database designs. It connects core backend output signals to input signals. This removes the need for the backend signals to be connected to FPGA I/O pins when creating the example designs, allowing the core to be placed and routed in small pinout packages. |

| pcicore_components  | This is a VHDL components package that contains the PCI core component declaration.                                                                                                                                                                                                                  |

## **Tool Flows**

## **SmartDesign**

CorePCIF is available for download to the SmartDesign IP Catalog, via the Actel Libero® Integrated Design Environment (IDE) web repository. For information on using SmartDesign to instantiate, configure, connect, and generate cores, refer to the Libero IDE online help.

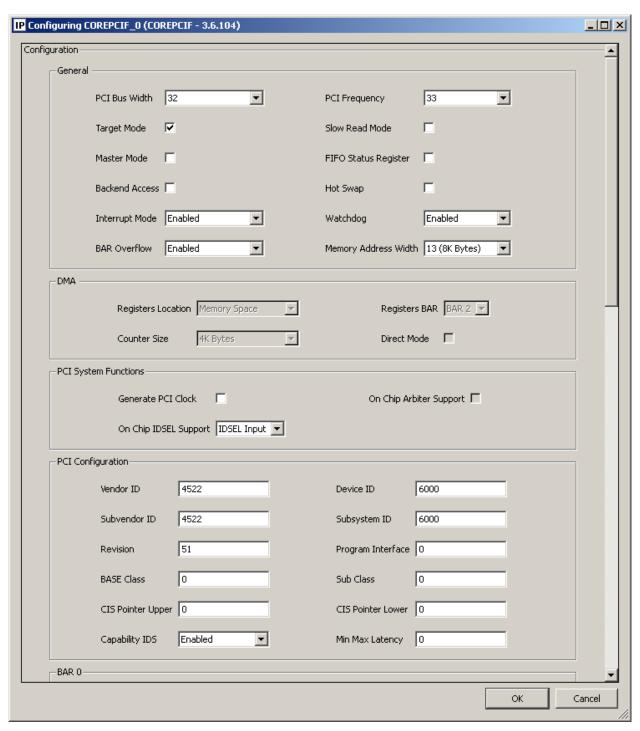

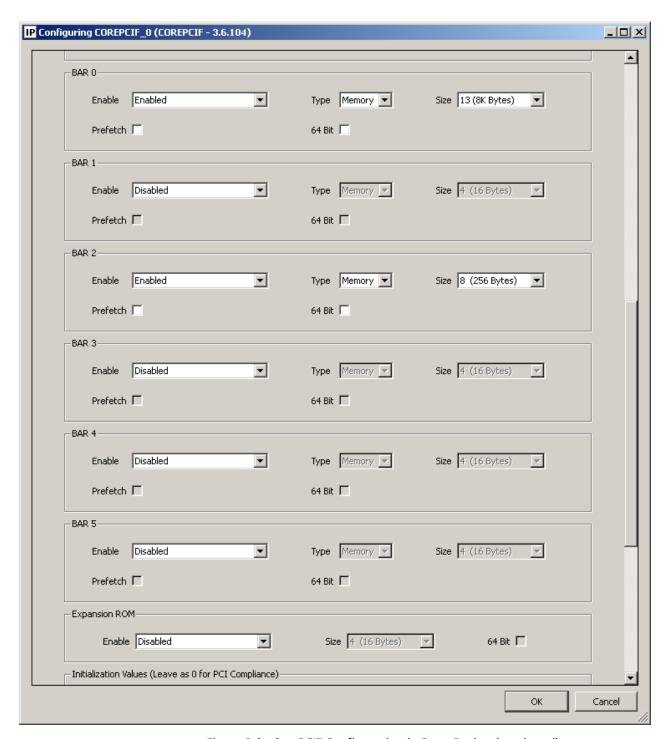

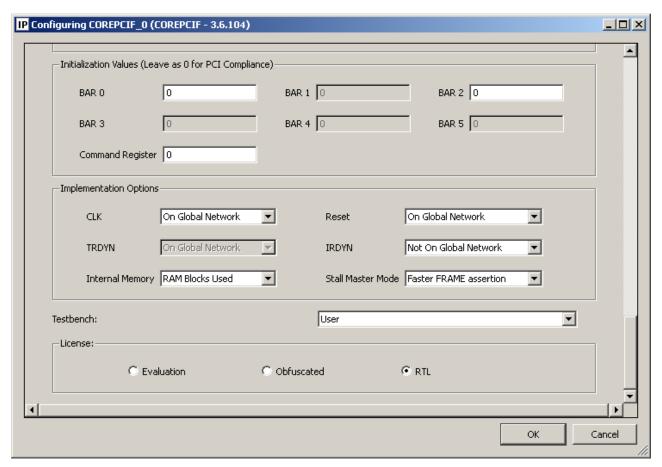

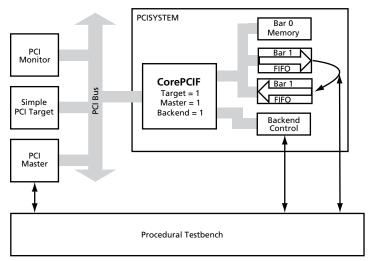

The core can be configured using the configuration GUI within SmartDesign, as shown in Figure 3-1 on page 28 through Figure 3-3 on page 30. "General Configuration Parameters" on page 33 explains the configuration parameters and their recommended values.

## Synthesis in Libero IDE

To run Synthesis on the core, set the design root to the top of the project. This is a wrapper around the core that sets all the generics appropriately.

Make sure the required timing constraints files are associated with the synthesis tool. There should be four timing constraints files available, covering 33/66 MHz and 32-/64-bit operation:

```

pcitiming32_33_synplicity.sdc

pcitiming32_66_synplicity.sdc

pcitiming64_33_synplicity.sdc

pcitiming64_66_synplicity.sdc

```

Appendix B on page 131 details the timing constraints that are required.

Click the **Synthesis** icon in Libero IDE. The synthesis window appears, displaying the Synplicity® project. To run Synthesis, click the **Run** icon.

To allow the core to be synthesized standalone within Libero IDE, an additional top-level module, PCICORETEST, is also imported into Libero IDE. The top level only includes the PCI bus signals; all the core backend signals are connected to a loopback module. This allows the core to synthesized and place-and-route performed in small-pin-count packages so that utilization and performance can be verified without user logic being connected to the backend interface. To use this top level, the design root must be set to PCICORETEST in Libero IDE.

Additionally, the *PCISYSTEM* or *PCISYSTEM2* stimulus file can be moved to the HDL directory; these files add fully functioning memory and FIFO to the backend of the core (Axcelerator, IGLOO/e, ProASIC3/E/L, and Fusion FPGA families only), creating a single-chip PCI system (see "User Testbench" on page 120). To synthesize the PCISYSTEM design, move the *pcisystem*, *fifo*, *memory*, *ram2k8*, and *fifo512x32* files from the CorePCI stimulus directory to the HDL source files directory in Libero IDE, and then set the design root to PCISYSTEM. For the PCISYSTEM2 design, move the *pcisystem2*, *memory*, and *ram2k8* files.

v3.3 27

Tool Flows CorePCIF v3.6

Figure 3-1 · CorePCIF Configuration in SmartDesign

**Actel**®

Figure 3-2 · CorePCIF Configuration in SmartDesign (continued)

v3.3 29

Tool Flows CorePCIF v3.6

Figure 3-3 · CorePCIF Configuration in SmartDesign (continued)

## Place-and-Route in Libero IDE

Make sure required timing and physical constraints files are associated with the place-and-route tool. There should be multiple timing and physical constraints files available, covering the PCI functions: 33/66 MHz and 32-/64-bit operation as well as device package combinations.

$T_pcitiming 32_33_designer.sdc$

$T_pcitiming 32\_66\_designer.sdc$

T\_pcitiming64\_33\_designer.sdc

$T_pcitiming 64_66_designer.sdc$

TM\_pcitiming32\_33\_designer.sdc

TM\_pcitiming32\_66\_designer.sdc

TM\_pcitiming64\_33\_designer.sdc

TM\_pcitiming64\_66\_designer.sdc

M\_pcitiming32\_33\_designer.sdc

M\_pcitiming32\_66\_designer.sdc

M\_pcitiming64\_33\_designer.sdc  $M_pcitiming 64_66_designer.sdc$ M\_pci32\_pa3e\_FG484.pdc M\_pci64\_pa3e\_FG484.pdc TM\_pci32\_pa3e\_FG484.pdc TM\_pci64\_pa3e\_FG484.pdc T\_pci32\_pa3e\_FG484.pdc T\_pci64\_pa3e\_FG484.pdc

For Target-only cores, the  $T_{-}$  files should be used; for Master-only cores, the  $M_{-}$  files should be used; and for Target and Master operation, the TM\_ files should be used.

32/64 selects 32- or 64-bit PCI operation.

33/66 selects 33 or 66 MHz PCI operation.

The supplied timing constraints files assume a typical configuration of the core. Some configurations may cause the timing constraints files to cause an error when loaded by Designer. For example, if the ONCHIP\_IDSEL function is enabled, the IDSEL input is not used and Synthesis will remove the IDSEL input. When this occurs, Designer will detect an error when it tries to set a timing constraint on the nonexistent IDSEL input. In this case, the timing constraints on the IDSEL input should be removed from the SDC files.

If there is not a good match for your selected device and package, you should create your own physical constraints files, following the rules in the "Implementation Hints" section on page 125.

Having set the design root appropriately and run Synthesis, click the Layout icon in Libero IDE to invoke Designer. CorePCIF requires no special place-and-route settings. Actel recommends you set the compile options given in Table 3-1.

Compile Option(s) **Device Family** ProASICPLUS No special requirements Set pdc\_abort\_on\_error "off" Fusion Set pdc\_eco\_display\_unmatched\_objects "off" IGLOO/e Set demote\_globals "off" -promote\_globals "off" ProASIC3/E/L Set combine\_register "on" -delete\_buffer\_tree "off" Set report\_high\_fanout\_nets\_limit 10 Axcelerator Set combine\_register = 1 RTAX-S Set combine\_register = 1 SX-A No special requirements RTSX-S No special requirements

Table 3-1 · Designer Compile Options

# **CorePCIF Parameters**

CorePCIF is a highly configurable core. The configuration is controlled by approximately 50 top-level parameters. These are listed in Table 4-1 to Table 4-4 on page 37.

# **General Configuration Parameters**

Table 4-1 shows general configuration parameters for CorePCIF.

Table 4-1 · General Parameters

| Name          | Values   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAMILY        | 8 to 21  | Must be set to the required FPGA family:  8: SX-A  9: RTSX-S  11: Axcelerator  12: RTAX-S  14: ProASIC PLUS  15: ProASIC3  16: ProASIC3E  17: Fusion  20: IGLOO  21: IGLOOe  22: ProASIC3L                                                                                                                                                                                                                                                                                                                                                                                                               |

| MASTER        | 0 or 1   | When 1, the PCI Master function with DMA controller is implemented.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TARGET        | 0 or 1   | When 1, the PCI Target function is implemented.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PCI_FREQ_     | 33 or 66 | When 66, the 66 MHz bit in the PCI configuration space is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SLOW_READ     | 0 or 1   | When 1, the core inserts either one or two wait states in all read transfers, eliminating the requirement for internal data storage within the core. This parameter must not be set if the FIFO recovery option is enabled.                                                                                                                                                                                                                                                                                                                                                                              |

| PCI_WIDTH     | 32 or 64 | Sets 32- or 64-bit PCI implementation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DISABLE_WDOG  | 0 or 1   | When 1, the data transfer watchdog inside the core is disabled. The core normally includes a transfer watchdog that will terminate a PCI cycle if the backend logic fails to provide or accept data within the time limits defined by the PCI specification. This function can be disabled in embedded systems if longer access times are permitted.                                                                                                                                                                                                                                                     |

| DISABLE_BAROV | 0 or 1   | When 1, the core will not disconnect when a memory or I/O transfer overflows the BAR as required by the PCI specification. Instead, the core will wrap the address and jump to the beginning of the BAR space. Setting the parameter to 1 will reduce the number of logic elements in the core. When the BAR overflow logic is enabled, the core may disconnect burst transfers before they reach the upper limit of the BAR, depending on the transfer rate controlled by IRDY and TRDY. This may require the PCI Master to perform several separate PCI transfers before the top of memory is reached. |

| REMOVE_CAP_ID | 0 or 1   | When 1, the capability pointer and capability values in the PCI configuration space are all held at 0. The interrupt and DMA control registers are still accessible at locations 48 and 50–5C hex. When 0, the capability IDs are as described in Table 7-1 on page 103 and Table 7-2 on page 104.                                                                                                                                                                                                                                                                                                       |

CorePCIF Parameters CorePCIF v3.6

Table 4-1 · General Parameters (Continued)

| Name             | Values     | Description                                                                                                                                                                                                                                                                                                                                                    |

|------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTERRUPT_MODE   | 0 to 2     | Configures the PCI interrupt:  0: The interrupt register is implemented as per Table 7-15 on page 110 and Table 7-21 on page 112.  1: The interrupt system is disabled.  2: The interrupt register (48h) is not implemented, and the EXT_INTn input directly drives INTAn.                                                                                     |

|                  |            | When Master functions are enabled (MASTER = 1), this parameter should be set to 0.  When INTERRUPT_MODE is set to 0 or 2, the interrupt disable and status bits in the configuration space control and status registers are implemented and may be used to disable the interrupt.                                                                              |

| ENABLE_FIFOSTAT  | 0 to 1     | When 1, the FIFO status register as per Table 7-16 on page 110 is implemented.                                                                                                                                                                                                                                                                                 |

| USE_REGISTERS    | 0 or 1     | When 1, the internal RAM blocks are replaced with a register-based implementation.  For SX-A and RTSX-S, the internal RAM blocks are always replaced with registers.                                                                                                                                                                                           |

| MADDR_WIDTH      | 8 to 32    | Specifies the width of the backend address bus. This should match the largest BAR address width (Table 4-3 on page 36). For example, if 64 kB of address space are configured, MADDR_WIDTH should be set to 16. If all BARs are less than 256 bytes, MADDR_WIDTH should be set to 8. Values below 8 are not permitted.  Memory Size = 2 <sup>MADDR_WIDTH</sup> |