# 256-Kbit (32K x 8) Serial (SPI) F-RAM

#### **Features**

- 256-Kbit ferroelectric random access memory (F-RAM) logically organized as 32K × 8

- ☐ High-endurance 100 trillion (10<sup>14</sup>) read/writes

- □ 151-year data retention (See the Data Retention and Endurance table)

- □ NoDelay™ writes

- Advanced high-reliability ferroelectric process

- Very fast serial peripheral interface (SPI)

- □ Up to 40-MHz frequency

- □ Direct hardware replacement for serial flash and EEPROM

- □ Supports SPI mode 0 (0, 0) and mode 3 (1, 1)

- Sophisticated write-protection scheme

- ☐ Hardware protection using the Write Protect (WP) pin

- □ Software protection using Write Disable instruction

- □ Software block protection for 1/4, 1/2, or entire array

- Device ID

- Manufacturer ID and Product ID

- Low power consumption

- □ 2.5-mA active current at 40 MHz

- □ 150-μA standby current

- □ 8-μA sleep mode current

- Low-voltage operation: V<sub>DD</sub> = 2.0 V to 3.6 V

- Industrial temperature: -40 °C to +85 °C

- Packages

- □ 8-pin small outline integrated circuit (SOIC) package

- □ 8-pin dual flat no-leads (DFN) package

- Restriction of hazardous substances (RoHS) compliant

# **Functional Description**

The FM25V02A is a 256-Kbit nonvolatile memory employing an advanced ferroelectric process. An F-RAM is nonvolatile and performs reads and writes similar to a RAM. It provides reliable data retention for 151 years while eliminating the complexities, overhead, and system-level reliability problems caused by serial flash, EEPROM, and other nonvolatile memories.

Unlike serial flash and EEPROM, the FM25V02A performs write operations at bus speed. No write delays are incurred. Data is written to the memory array immediately after each byte is successfully transferred to the device. The next bus cycle can commence without the need for data polling. In addition, the product offers substantial write endurance compared with other nonvolatile memories. The FM25V02A is capable of supporting 10<sup>14</sup> read/write cycles, or 100 million times more write cycles than EEPROM.

These capabilities make the FM25V02A ideal for nonvolatile memory applications requiring frequent or rapid writes. Examples range from data logging, where the number of write cycles may be critical, to demanding industrial controls where the long write time of serial flash or EEPROM can cause data loss.

The FM25V02A provides substantial benefits to users of serial EEPROM or flash as a hardware drop-in replacement. The FM25V02A uses the high-speed SPI bus, which enhances the high-speed write capability of F-RAM technology. The device incorporates a read-only Device ID that allows the host to determine the manufacturer, product density, and product revision. The device specifications are guaranteed over an industrial range of -40~°C to +85~°C.

For a complete list of related resources, click here.

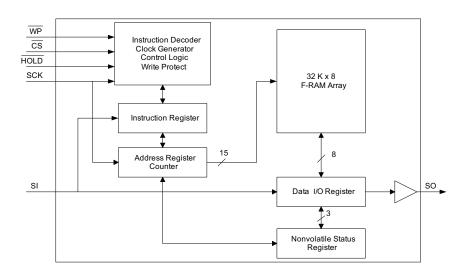

# **Logic Block Diagram**

# Contents

| Pinouts                               | 3  |

|---------------------------------------|----|

| Pin Definitions                       | 3  |

| Overview                              | 4  |

| Memory Architecture                   | 4  |

| Serial Peripheral Interface - SPI Bus | 4  |

| SPI Overview                          | 4  |

| SPI Modes                             | 5  |

| Power-Up to First Access              |    |

| Command Structure                     | 6  |

| WREN - Set Write Enable Latch         | 6  |

| WRDI - Reset Write Enable Latch       | 6  |

| Status Register and Write Protection  | 7  |

| RDSR - Read Status Register           | 7  |

| WRSR - Write Status Register          | 7  |

| Memory Operation                      | 8  |

| Write Operation                       | 8  |

| Read Operation                        | 8  |

| Fast Read Operation                   |    |

| HOLD Pin Operation                    | 10 |

| Sleep Mode                            | 10 |

| Device ID                             | 11 |

| Endurance                             | 10 |

| Maximum Ratings13                         |   |

|-------------------------------------------|---|

| Operating Range13                         | 3 |

| DC Electrical Characteristics13           |   |

| Data Retention and Endurance14            | 4 |

| Capacitance14                             | 4 |

| Thermal Resistance14                      | 4 |

| AC Test Conditions14                      | 4 |

| AC Switching Characteristics15            | 5 |

| Power Cycle Timing17                      | 7 |

| Ordering Information18                    | 8 |

| Ordering Code Definitions18               |   |

| Package Diagrams19                        | 9 |

| Acronyms21                                |   |

| Document Conventions21                    | 1 |

| Units of Measure2                         | 1 |

| Document History Page22                   | 2 |

| Sales, Solutions, and Legal Information23 | 3 |

| Worldwide Sales and Design Support23      | 3 |

| Products23                                | 3 |

| PSoC® Solutions                           | 3 |

| Cypress Developer Community23             | 3 |

| Technical Support23                       | 3 |

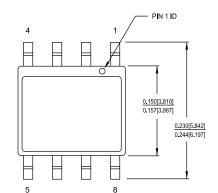

# **Pinouts**

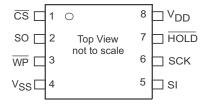

Figure 1. 8-pin SOIC Pinout

Figure 2. 8-pin DFN Pinout

# **Pin Definitions**

| Pin Name          | I/O Type     | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK               | Input        | <b>Serial Clock</b> . All I/O activity is synchronized to the serial clock. Inputs are latched on the rising edge and outputs occur on the falling edge. Because the device is synchronous, the clock frequency may be any value between 0 and 40 MHz and may be interrupted at any time.                                                                                         |

| CS                | Input        | <b>Chip Select</b> . This active LOW input activates the device. When HIGH, the device enters the low-power standby mode, ignores other inputs, and the output is tristated. When LOW, the device internally activates the SCK signal. A falling edge on $\overline{\text{CS}}$ must occur before every opcode.                                                                   |

| SI <sup>[1]</sup> | Input        | <b>Serial Input</b> . All data is input to the device on this pin. The pin is sampled on the rising edge of SCK and is ignored at other times. It should always be driven to a valid logic level to meet I <sub>DD</sub> specifications.                                                                                                                                          |

| SO <sup>[1]</sup> | Output       | <b>Serial Output</b> . This is the data output pin. It is driven during a read and remains tristated at all other times including when HOLD is LOW. Data transitions are driven on the falling edge of the serial clock.                                                                                                                                                          |

| WP                | Input        | <b>Write Protect</b> . This active LOW pin prevents write operation to the Status Register when WPEN is set to '1'. This is critical because other write protection features are controlled through the Status Register. A complete explanation of write protection is provided on Status Register and Write Protection on page 7. This pin must be tied to $V_{DD}$ if not used. |

| HOLD              | Input        | HOLD Pin. The HOLD pin is used when the host CPU must interrupt a memory operation for another task. When HOLD is LOW, the current operation is suspended. The device ignores any transition on SCK or CS. All transitions on HOLD must occur while SCK is LOW. This pin has a weak internal pull-up (refer to the R <sub>IN</sub> spec in DC Electrical Characteristics).        |

| V <sub>SS</sub>   | Power supply | Ground for the device. Must be connected to the ground of the system.                                                                                                                                                                                                                                                                                                             |

| V <sub>DD</sub>   | Power supply | Power supply input to the device.                                                                                                                                                                                                                                                                                                                                                 |

| EXPOSED PAD       | No connect   | The EXPOSED PAD on the bottom of 8-pin DFN package is not connected to the die. The EXPOSED PAD should not be soldered on the PCB.                                                                                                                                                                                                                                                |

### Note

<sup>1.</sup> SI may be connected to SO for a single pin data interface.

### Overview

The FM25V02A is a serial F-RAM memory. The memory array is logically organized as  $32,768 \times 8$  bits and is accessed using an industry-standard serial peripheral interface (SPI) bus. The functional operation of the F-RAM is similar to serial flash and serial EEPROMs. The major difference between the FM25V02A and a serial flash or EEPROM with the same pinout is the F-RAM's superior write performance, high endurance, and low power consumption.

# **Memory Architecture**

When accessing the FM25V02A, the user addresses 32K locations of eight data bits each. These eight data bits are shifted in or out serially. The addresses are accessed using the SPI protocol, which includes a chip select (to permit multiple devices on the bus), an opcode, and a two-byte address. The upper bit of the address range is 'don't care' value. The complete address of 15 bits specifies each byte address uniquely.

Most functions of the FM25V02A are either controlled by the SPI interface or are handled by on-board circuitry. The access time for the memory operation is essentially zero, beyond the time needed for the serial protocol. That is, the memory is read or written at the speed of the SPI bus. Unlike a serial flash or EEPROM, it is not necessary to poll the device for a ready condition because writes occur at bus speed. By the time a new bus transaction can be shifted into the device, a write operation is complete. This is explained in more detail in Memory Operation on page 8.

## Serial Peripheral Interface - SPI Bus

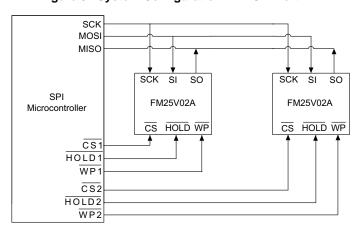

The FM25V02A is a SPI slave device and operates at speeds up to 40 MHz. This high-speed serial bus provides high-performance serial communication to a SPI master. Many common microcontrollers have hardware SPI ports allowing a direct interface. It is quite simple to emulate the port using ordinary port pins for microcontrollers that do not. The FM25V02A operates in SPI Mode 0 and 3.

#### **SPI Overview**

The SPI is a four-pin interface with Chip Select ( $\overline{CS}$ ), Serial Input (SI), Serial Output (SO), and Serial Clock (SCK) pins.

The SPI is a synchronous serial interface, which uses clock and data pins for memory access and supports multiple devices on the data bus. A device on the SPI bus is activated using the CS pin.

The relationship between chip select, clock, and data is dictated by the SPI mode. This device supports SPI modes 0 and 3. In both of these modes, data is clocked into the F-RAM on  $\underline{\text{the}}$  rising edge of SCK starting from the first rising edge after  $\overline{\text{CS}}$  goes active.

The SPI protocol is controlled by opcodes. These opcodes specify the commands from the bus master to the slave device. After CS is activated, the first byte transferred from the bus

master is the opcode. Following the opcode, any addresses and data are then transferred. The  $\overline{\text{CS}}$  must go inactive after an operation is complete and before a new opcode can be issued. The commonly used terms in the SPI protocol are as follows:

#### SPI Master

The SPI master device controls the operations on a SPI bus. An SPI bus may have only one master with one or more slave devices. All the slaves share the same SPI bus lines and the master may select any of the slave devices using the  $\overline{\text{CS}}$  pin. All of the operations must be initiated by the master activating a slave device by pulling the  $\overline{\text{CS}}$  pin of the slave LOW. The master also generates the SCK and all the data transmission on SI and SO lines are synchronized with this clock.

### SPI Slave

The SPI slave device is activated by the master through the Chip Select line. A slave device gets the SCK as an input from the SPI master and all the communication is synchronized with this clock. An SPI slave never initiates a communication on the SPI bus and acts only on the instruction from the master.

The FM25V02A operates as an SPI slave and may share the SPI bus with other SPI slave devices.

# Chip Select (CS)

To select any <u>slave</u> device, the master needs to pull down the corresponding  $\overline{CS}$  pin. Any instruction can be issued to a slave device only while the  $\overline{CS}$  pin is LOW. When the device is not selected, data through the SI pin is ignored and the serial output pin (SO) remains in a high-impedance state.

**Note** A new instruction must begin with the falling edge of  $\overline{\text{CS}}$ . Therefore, only one opcode can be issued for each active Chip Select cycle.

### Serial Clock (SCK)

The serial clock is generated by the SPI master  $\underline{\text{and}}$  the communication is synchronized with this clock after  $\overline{\text{CS}}$  goes LOW.

The FM25V02A enables SPI modes 0 and 3 for data communication. In both of these modes, the inputs are latched by the slave device on the rising edge of SCK and outputs are issued on the falling edge. Therefore, the first rising edge of SCK signifies the arrival of the first bit (MSB) of a SPI instruction on the SI pin. Further, all data inputs and outputs are synchronized with SCK.

#### Data Transmission (SI/SO)

The SPI data bus consists of two lines, SI and SO, for serial data communication. SI is also referred to as Master Out Slave In (MOSI) and SO is referred to as Master In Slave Out (MISO). The master issues instructions to the slave through the SI pin, while the slave responds through the SO pin. Multiple slave devices may share the SI and SO lines as described earlier.

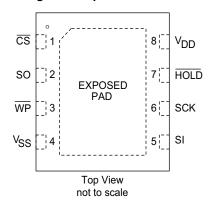

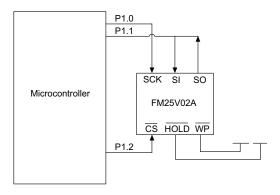

The FM25V02A has two separate pins for SI and SO, which can be connected with the master as shown in Figure 3.

For a microcontroller that has no dedicated SPI bus, a general-purpose port may be used. To reduce hardware resources on the controller, it is possible to connect the two data pins (SI, SO) together and tie off (HIGH) the HOLD and WP pins. Figure 4 shows such a configuration, which uses only three pins.

#### Most Significant Bit (MSB)

The SPI protocol requires that the first bit to be transmitted is the Most Significant Bit (MSB). This is valid for both address and data transmission.

The 256-Kbit serial F-RAM requires a 2-byte address for any read or write operation. Because the address is only 15 bits, the upper bit which is fed in is ignored by the device. Although the upper bit is 'don't care', Cypress recommends that these bits be set to 0s to enable seamless transition to higher memory densities.

### Serial Opcode

After the slave device is selected with  $\overline{\text{CS}}$  going LOW, the first byte received is treated as the opcode for the intended operation. FM25V02A uses the standard opcodes for memory accesses.

### Invalid Opcode

If an invalid opcode is received, the opcode is ignored and the device ignores any <u>additional</u> serial data on the SI pin until the next falling edge of  $\overline{CS}$ , and the SO pin remains tristated.

### Status Register

FM25V02A has an 8-bit Status Register. The bits in the Status Register are used to configure the device. These bits are described in Table 3 on page 7.

Figure 3. System Configuration with SPI Port

Figure 4. System Configuration Without SPI Port

### **SPI Modes**

FM25V02A may be driven by a microcontroller with its SPI peripheral running in either of the following two modes:

- SPI Mode 0 (CPOL = 0, CPHA = 0)

- SPI Mode 3 (CPOL = 1, CPHA = 1)

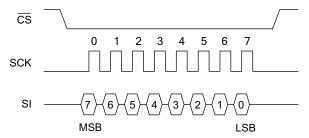

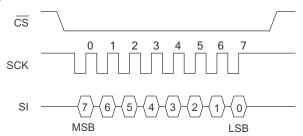

For both these modes, the input data is latched in on the rising edge of SCK starting from the first rising edge after  $\overline{CS}$  goes

active. If the clock starts from a HIGH state (in mode 3), the first rising edge after the clock toggles is considered. The output data is available on the falling edge of SCK. The two SPI modes are shown in Figure 5 on page 6 and Figure 6 on page 6. The status of the clock when the bus master is not transferring data is:

- SCK remains at 0 for Mode 0

- SCK remains at 1 for Mode 3

The device detects the SPI mode from the status of the SCK pin when the device is selected by bringing the  $\overline{\text{CS}}$  pin LOW. If the SCK pin is LOW when the device is selected, SPI Mode 0 is assumed and if the SCK pin is HIGH, it works in SPI Mode 3.

Figure 5. SPI Mode 0

Figure 6. SPI Mode 3

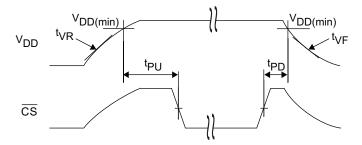

#### **Power-Up to First Access**

The FM25V02A is not accessible for a  $t_{PU}$  time after power-up. Users must comply with the timing parameter  $t_{PU}$ , which is the minimum time from  $V_{DD}$  (min) to the first  $\overline{CS}$  LOW.

### **Command Structure**

There are nine commands, called opcodes, that can be issued by the bus master to the FM25V02A. They are listed in Table 1. These opcodes control the functions performed by the memory.

**Table 1. Opcode Commands**

| Name     | Description              | Opcode     |

|----------|--------------------------|------------|

| WREN     | Set write enable latch   | 0000 0110b |

| WRDI     | Reset write enable latch | 0000 0100b |

| RDSR     | Read Status Register     | 0000 0101b |

| WRSR     | Write Status Register    | 0000 0001b |

| READ     | Read memory data         | 0000 0011b |

| FSTRD    | Fast read memory data    | 0000 1011b |

| WRITE    | Write memory data        | 0000 0010b |

| SLEEP    | Enter sleep mode         | 1011 1001b |

| RDID     | Read device ID           | 1001 1111b |

| Reserved | Reserved                 | 1100 0011b |

|          |                          | 1100 0010b |

|          |                          | 0101 1010b |

|          |                          | 0101 1011b |

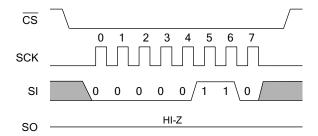

### **WREN - Set Write Enable Latch**

The FM25V02A will power up with writes disabled. The WREN command must be issued before any write operation. Sending the WREN opcode allows the user to issue subsequent opcodes for write operations. These include writing the Status Register (WRSR) and writing the memory (WRITE).

Sending the WREN opcode causes the internal Write Enable Latch to be set. A flag bit in the Status Register, called WEL, indicates the state of the latch. WEL = '1' indicates that writes are permitted. Attempting to write the WEL bit in the Status Register has no effect on the state of this bit - only the WREN opcode can set this bit. The WEL bit will be automatically cleared on the rising edge of  $\overline{\text{CS}}$  following a WRDI, a WRSR, or a WRITE operation. This prevents further writes to the Status Register or the F-RAM array without another WREN command. Figure 7 illustrates the WREN command bus configuration.

Figure 7. WREN Bus Configuration

### WRDI - Reset Write Enable Latch

The WRDI command disables all write activity by clearing the Write Enable Latch. The user can verify that writes are disabled by reading the WEL bit in the Status Register and verifying that WEL is equal to '0'. Figure 8 illustrates the WRDI command bus configuration.

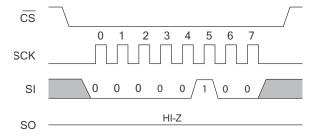

Figure 8. WRDI Bus Configuration

# **Status Register and Write Protection**

The write protection features of the FM25V02A are multi-tiered and are enabled through the status register. The status register is organized as follows (the default value shipped from the factory for bits in the status register is '0'):

Table 2. Status Register

| Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1   | Bit 0 |

|----------|-------|-------|-------|---------|---------|---------|-------|

| WPEN (0) | X (0) | X (0) | X (0) | BP1 (0) | BP0 (0) | WEL (0) | X (0) |

Table 3. Status Register Bit Definition

| Bit          | Definition               | Description                                                                                                                                       |

|--------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0        | Don't care               | This bit is non-writable and always returns '0' upon read.                                                                                        |

| Bit 1 (WEL)  |                          | WEL indicates if the device is write enabled. This bit defaults to '0' (disabled) on power-up. WEL = '1'> Write enabled WEL = '0'> Write disabled |

| Bit 2 (BP0)  | Block Protect bit '0'    | Used for block protection. For details, see Table 4 on page 7.                                                                                    |

| Bit 3 (BP1)  | Block Protect bit '1'    | Used for block protection. For details, see Table 4 on page 7.                                                                                    |

| Bit 4-6      | Don't care               | These bits are non-writable and always return '0' upon read.                                                                                      |

| Bit 7 (WPEN) | Write Protect Enable bit | Used to enable the function of Write Protect Pin ( $\overline{\text{WP}}$ ). For details, see Table 5 on page 7.                                  |

Bits 0 and 4-6 are fixed at '0'; none of these bits can be modified. Note that bit 0 ("Ready or Write in progress" bit in serial flash and EEPROM) is unnecessary, as the F-RAM writes in real-time and is never busy, so it reads out as a '0'. An exception to this is when the device is waking up from sleep mode, which is described in Sleep Mode on page 10. The BP1 and BP0 control the software write-protection features and are nonvolatile bits. The WEL flag indicates the state of the Write Enable Latch. Attempting to directly write the WEL bit in the Status Register has no effect on its state. This bit is internally set and cleared via the WREN and WRDI commands, respectively.

BP1 and BP0 are memory block write protection bits. They specify portions of memory that are write-protected as shown in Table 4.

**Table 4. Block Memory Write Protection**

| BP1 | BP0 | Protected Address Range    |

|-----|-----|----------------------------|

| 0   | 0   | None                       |

| 0   | 1   | 6000h to 7FFFh (upper 1/4) |

| 1   | 0   | 4000h to 7FFFh (upper 1/2) |

| 1   | 1   | 0000h to 7FFFh (all)       |

The BP1 and BP0 bits and the Write Enable Latch are the only mechanisms that protect the memory from writes. The remaining write protection features protect inadvertent changes to the block protect bits.

The write protect enable bit (WPEN) in the Status Register controls the effect of the hardware write protect ( $\overline{WP}$ ) pin. When the WPEN bit is set to '0', the status of the  $\overline{WP}$  pin is ignored. When the WPEN bit is set to '1', a LOW on the WP pin inhibits a

write to the Status Register. Thus the Status Register is write-protected only when WPEN = '1' and  $\overline{WP}$  = '0'.

Table 5 summarizes the write protection conditions.

**Table 5. Write Protection**

| WEL | WPEN | WP | Protected<br>Blocks | Unprotected Blocks | Status<br>Register |

|-----|------|----|---------------------|--------------------|--------------------|

| 0   | Х    | Χ  | Protected           | Protected          | Protected          |

| 1   | 0    | Χ  | Protected           | Unprotected        | Unprotected        |

| 1   | 1    | 0  | Protected           | Unprotected        | Protected          |

| 1   | 1    | 1  | Protected           | Unprotected        | Unprotected        |

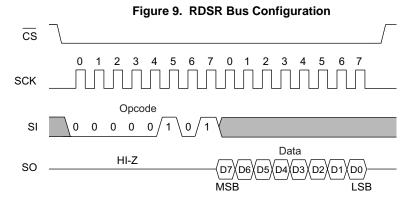

#### RDSR - Read Status Register

The RDSR command allows the bus master to verify the contents of the Status Register. Reading the status register provides information about the current state of the write-protection features. Following the RDSR opcode, the FM25V02A will return one byte with the contents of the Status Register.

### WRSR - Write Status Register

The WRSR command allows the SPI bus master to write into the Status Register and change the write protect configuration by setting the WPEN, BP0, and BP1 bits as required. Prior to issuing a WRSR command, the  $\overline{WP}$  pin must be HIGH or inactive. Note that on the FM25V02A,  $\overline{WP}$  only prevents writing to the Status Register, not the memory array. Before sending the WRSR command, the user must send a WREN command to enable writes. Executing a WRSR command is a write operation and therefore, clears the Write Enable Latch.

# **Memory Operation**

The SPI interface, which is capable of a high clock frequency, highlights the fast write capability of the F-RAM technology. Unlike serial flash and EEPROMs, the FM25V02A can perform sequential writes at bus speed. No page register is needed and any number of sequential writes may be performed.

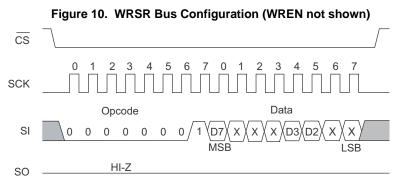

### Write Operation

All writes to the memory begin with a WREN opcode with  $\overline{\text{CS}}$  being asserted and deasserted. The next opcode is WRITE. The WRITE opcode is followed by a two-byte address containing the 15-bit address (A14-A0) of the first data byte to be written into the memory. The upper bit of the two-byte address is ignored. Subsequent bytes are data bytes, which are written sequentially. Addresses are incremented internally as long as the bus master continues to issue clocks and keeps  $\overline{\text{CS}}$  LOW. If the last address of 7FFFh is reached, the counter will roll over to 0000h. Data is written MSB first. The rising edge of  $\overline{\text{CS}}$  terminates a write operation. A write operation is shown in Figure 11.

**Note** When a burst write reaches a protected block address, the automatic address increment stops and all the subsequent data bytes received for write will be ignored by the device.

EEPROMs use page buffers to increase their write throughput. This compensates for the technology's inherently slow write operations. F-RAM memories do not have page buffers because each byte is written to the F-RAM array immediately after it is

clocked in (after the eighth clock). This allows any number of bytes to be written without page buffer delays.

**Note** If the power is lost in the middle of the write operation, only the last completed byte will be written.

### **Read Operation**

After the falling edge of  $\overline{\text{CS}}$ , the bus master can issue a READ opcode. Following the READ command is a two-byte address containing the 15-bit address (A14-A0) of the first byte of the read operation. The upper bit of the address is ignored. After the opcode and address are issued, the device drives out the read data on the next eight clocks. The SI input is ignored during read data bytes. Subsequent bytes are data bytes, which are read out sequentially. Addresses are incremented internally as long as the bus master continues to issue clocks and  $\overline{\text{CS}}$  is LOW. If the last address of 7FFFh is reached, the counter will roll over to 0000h. Data is read MSB first. The rising edge of  $\overline{\text{CS}}$  terminates a read operation and tristates the SO pin. A read operation is shown in Figure 12.

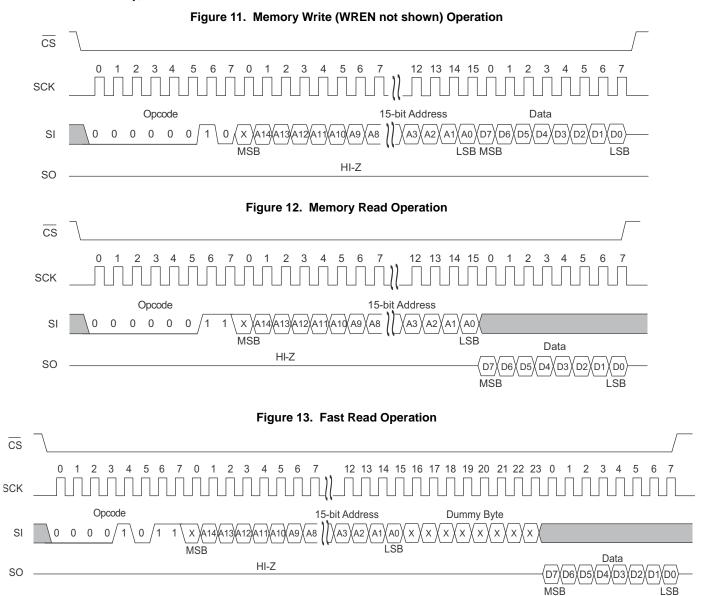

#### **Fast Read Operation**

The FM25V02A supports a FAST READ opcode (0Bh) that is provided for code compatibility with serial flash devices. The FAST READ opcode is followed by a two-byte address containing the 15-bit address (A14-A0) of the first byte of the read operation and then a dummy byte. The dummy byte inserts a read latency of an 8-clock cycle. The fast read operation is otherwise the same as an ordinary read operation except that it

requires an additional dummy byte. After receiving the opcode, address, and a dummy byte, the FM25V02A starts driving its SO line with data bytes, with the MSB first, and continues transmitting as long as the device is selected and the clock is available. In case of bulk read, the internal address counter is incremented automatically, and after the last address 7FFFh is

reached, the counter rolls over to 0000h. When the device is driving data on its SO line, any transition on its SI line is ignored. The rising edge of  $\overline{CS}$  terminates a fast read operation and tristates the SO pin. A Fast Read operation is shown in Figure 13.

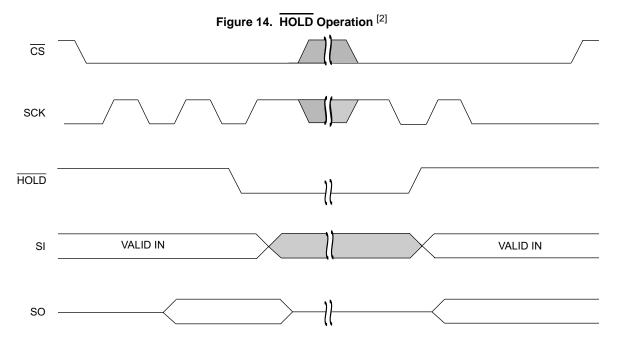

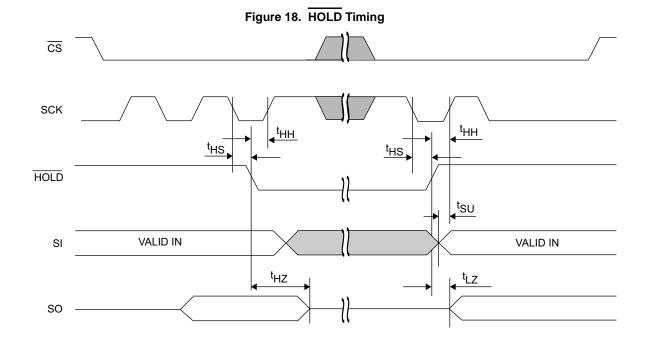

# **HOLD Pin Operation**

The HOLD pin can be used to interrupt a serial operation without aborting it. If the bus master pulls the HOLD pin LOW while SCK is LOW, the current operation will pause. Taking the HOLD pin

HIGH while <u>SCK</u> is LOW will resume an operation. The transitions of HOLD must occur while SCK is LOW, but the SCK and CS pin can toggle during a hold state.

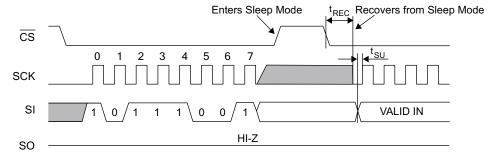

### Sleep Mode

A low-power sleep mode is implemented on the FM25V02A device. The device will enter the low-power state when the SLEEP opcode B9h is clocked-in and a rising edge of  $\overline{CS}$  is applied. When in sleep mode, the SCK and SI pins are ignored and SO will be HI-Z, but the device continues to monitor the  $\overline{CS}$

pin. On the next falling edge of  $\overline{\text{CS}}$ , the device will return to normal operation within  $t_{\text{REC}}$  time. The SO pin remains in a HI-Z state during the wakeup period. The device does not necessarily respond to an opcode within the wakeup period. To start the wakeup procedure, the controller may send a "dummy" read, for example, and wait the remaining  $t_{\text{REC}}$  time.

Figure 15. Sleep Mode Operation

#### Note

<sup>2.</sup> Figure 14 shows the  $\overline{\text{HOLD}}$  operation for input mode and output mode.

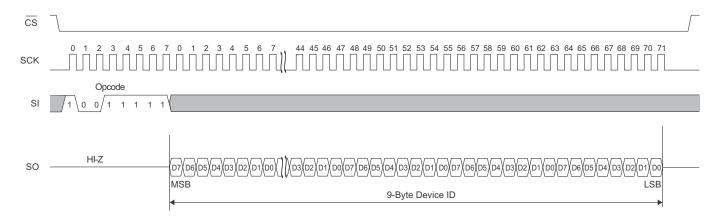

### **Device ID**

The FM25V02A device can be interrogated for its manufacturer, product identification, and die revision. The RDID opcode 9Fh allows the user to read the manufacturer ID and product ID, both of which are read-only bytes. The JEDEC-assigned

manufacturer ID places the Cypress (Ramtron) identifier in bank 7; therefore, there are six bytes of the continuation code 7Fh followed by the single byte C2h. There are two bytes of product ID, which includes a family code, a density code, a sub code, and the product revision code.

Table 6. Device ID

|                        | Device ID Description         |                   |                  |                 |                 |                 |  |

|------------------------|-------------------------------|-------------------|------------------|-----------------|-----------------|-----------------|--|

| Device ID<br>(9 bytes) | 71–16<br>(56 bits)            | 15–13<br>(3 bits) | 12–8<br>(5 bits) | 7–6<br>(2 bits) | 5–3<br>(3 bits) | 2–0<br>(3 bits) |  |

| (3 bytes)              | Manufacturer ID               | Product ID        |                  |                 |                 |                 |  |

|                        | Wallufacturer 1D              | Family            | Density          | Sub             | Rev             | Rsvd            |  |

| 7F7F7F7F7F7FC22208h    | 01111111011111110111111110111 | 001               | 00010            | 00              | 001             | 000             |  |

Figure 16. Read Device ID

### **Endurance**

The FM25V02A devices are capable of being accessed at least 10<sup>14</sup> times, reads or writes. An F-RAM memory operates with a read and restore mechanism. Therefore, an endurance cycle is applied on a row basis for each access (read or write) to the memory array. The F-RAM architecture is based on an array of rows and columns of 4K rows of 64-bits each. The entire row is internally accessed once whether a single byte or all eight bytes are read or written. Each byte in the row is counted only once in an endurance calculation. Table 7 shows endurance calculations for a 64-byte repeating loop, which includes an opcode, a starting address, and a sequential 64-byte data stream. This causes each byte to experience one endurance cycle through the loop.

Table 7. Time to Reach Endurance Limit for Repeating 64-byte Loop

| SCK Freq<br>(MHz) | Endurance<br>Cycles/sec | Endurance<br>Cycles/year | Years to Reach<br>Limit |

|-------------------|-------------------------|--------------------------|-------------------------|

| 40                | 74,620                  | $2.35 \times 10^{12}$    | 42.6                    |

| 20                | 37,310                  | 1.18 × 10 <sup>12</sup>  | 85.1                    |

| 10                | 18,660                  | $5.88 \times 10^{11}$    | 170.2                   |

| 5                 | 9,330                   | $2.94 \times 10^{11}$    | 340.3                   |

# **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. These user quidelines are not tested.

| device. These user guidelines are not tested.                                              |

|--------------------------------------------------------------------------------------------|

| Storage temperature55 °C to + 125 °C                                                       |

| Maximum junction temperature                                                               |

| Supply voltage on $\rm V_{DD}$ relative to $\rm V_{SS}$ 1.0 V to + 4.5 V                   |

| Input voltage –1.0 V to +4.5 V and $V_{IN}$ < $V_{DD}$ + 1.0 V                             |

| DC voltage applied to outputs in HI-Z state0.5 V to $V_{DD}$ + 0.5 V                       |

| Transient voltage (< 20 ns) on any pin to ground potential2.0 V to V <sub>DD</sub> + 2.0 V |

| Package power dissipation capability (T <sub>A</sub> = 25 °C)                   |

|---------------------------------------------------------------------------------|

| Surface mount lead soldering temperature (3 seconds)+260 °C                     |

| DC output current (1 output at a time, 1s duration) 15 mA                       |

| Electrostatic discharge voltage Human Body Model (JEDEC Std JESD22-A114-B) 2 kV |

| Charged Device Model (JEDEC Std JESD22-C101-A) 500 V                            |

| Latch-up current > 140 mA                                                       |

# **Operating Range**

| Range      | Ambient Temperature (T <sub>A</sub> ) | V <sub>DD</sub> |

|------------|---------------------------------------|-----------------|

| Industrial | −40 °C to +85 °C                      | 2.0 V to 3.6 V  |

# **DC Electrical Characteristics**

Over the Operating Range

| Parameter                      | Description                         | Test Conditions                                                                                  | Min                   | <b>Typ</b> <sup>[3]</sup> | Max                   | Unit |

|--------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------|---------------------------|-----------------------|------|

| $V_{DD}$                       | Power supply                        |                                                                                                  | 2.0                   | 3.3                       | 3.6                   | V    |

| I <sub>DD</sub>                | V <sub>DD</sub> supply current      | SCK toggling between $V_{DD} - f_{SCK} = 40 \text{ MHz}$                                         | _                     | _                         | 2.5                   | mA   |

|                                |                                     | 0.2 V and $V_{SS}$ , other inputs $V_{SS}$ or $V_{DD} = 0.2$ V. SO = Open.                       | -                     | _                         | 0.22                  | mA   |

| $I_{SB}$                       | V <sub>DD</sub> standby current     | $\overline{\text{CS}}$ = V <sub>DD</sub> . All other inputs V <sub>SS</sub> or V <sub>DD</sub> . | -                     | 90                        | 150                   | μΑ   |

| I <sub>ZZ</sub>                | Sleep mode current                  | $\overline{\text{CS}}$ = V <sub>DD</sub> . All other inputs V <sub>SS</sub> or V <sub>DD</sub> . | -                     | 5                         | 8                     | μΑ   |

| ILI                            | Input leakage current (Except HOLD) | $V_{SS} \le V_{IN} \le V_{DD}$                                                                   | <b>–1</b>             | _                         | +1                    | μА   |

|                                | Input leakage current (for HOLD)    |                                                                                                  | -100                  | _                         | +1                    | μА   |

| I <sub>LO</sub>                | Output leakage current              | $V_{SS} \leq V_{OUT} \leq V_{DD}$                                                                | -1                    | -                         | +1                    | μΑ   |

| V <sub>IH</sub>                | Input HIGH voltage                  |                                                                                                  | $0.7 \times V_{DD}$   | _                         | V <sub>DD</sub> + 0.3 | V    |

| $V_{IL}$                       | Input LOW voltage                   |                                                                                                  | - 0.3                 | _                         | 0.3 × V <sub>DD</sub> | V    |

| V <sub>OH1</sub>               | Output HIGH voltage                 | $I_{OH} = -1 \text{ mA}, V_{DD} = 2.7 \text{ V}.$                                                | 2.4                   | _                         | _                     | V    |

| V <sub>OH2</sub>               | Output HIGH voltage                 | $I_{OH} = -100 \mu A$                                                                            | V <sub>DD</sub> - 0.2 | _                         | -                     | V    |

| V <sub>OL1</sub>               | Output LOW voltage                  | I <sub>OL</sub> = 2 mA, V <sub>DD</sub> = 2.7 V                                                  | _                     | _                         | 0.4                   | V    |

| $V_{OL2}$                      | Output LOW voltage                  | I <sub>OL</sub> = 150 μA                                                                         | _                     | _                         | 0.2                   | V    |

| R <sub>in</sub> <sup>[4]</sup> | Input resistance (HOLD)             | For V <sub>IN</sub> = V <sub>IL</sub> (max)                                                      | 800                   | _                         | _                     | kΩ   |

|                                |                                     | For V <sub>IN</sub> = V <sub>IH</sub> (min)                                                      | 30                    | _                         | _                     | kΩ   |

Typical values are at 25 °C, V<sub>DD</sub> = V<sub>DD</sub> (typ). Not 100% tested.

The input pull-up circuit is strong (30 kΩ) when the input voltage is above V<sub>IH</sub> and weak (800 kΩ) when the input voltage is below V<sub>IL</sub>.

# **Data Retention and Endurance**

| Parameter       | Description    | Test condition             | Min              | Max | Unit   |

|-----------------|----------------|----------------------------|------------------|-----|--------|

| T <sub>DR</sub> | Data retention | T <sub>A</sub> = 85 °C     | 10               | _   | Years  |

|                 |                | T <sub>A</sub> = 75 °C     | 38               | _   |        |

|                 |                | T <sub>A</sub> = 65 °C     | 151              | _   |        |

| $NV_C$          | Endurance      | Over operating temperature | 10 <sup>14</sup> | _   | Cycles |

# Capacitance

| Parameter [5]  | Description                 | Test Conditions                                                               | Max | Unit |

|----------------|-----------------------------|-------------------------------------------------------------------------------|-----|------|

| Co             | Output pin capacitance (SO) | $T_A = 25 {}^{\circ}\text{C}, f = 1 \text{MHz}, V_{DD} = V_{DD} \text{(typ)}$ | 8   | pF   |

| C <sub>I</sub> | Input pin capacitance       |                                                                               | 6   | pF   |

# **Thermal Resistance**

| Parameter         | Description                              | Test Conditions                                                                   | 8-pin SOIC | 8-pin DFN | Unit |

|-------------------|------------------------------------------|-----------------------------------------------------------------------------------|------------|-----------|------|

| $\Theta_{JA}$     | Thermal resistance (junction to ambient) | Test conditions follow standard test methods and procedures for measuring thermal | _          | 31        | °C/W |

| $\Theta_{\sf JC}$ | Thermal resistance (junction to case)    | impedance, per EIA/ JESD51.                                                       | 48         | 35        | °C/W |

# **AC Test Conditions**

| Input pulse levels              | 10% and 90% of $V_{DD}$         |

|---------------------------------|---------------------------------|

| Input rise and fall times       | 3 ns                            |

| Input and output timing referen | ice levels0.5 × V <sub>DD</sub> |

| Output load capacitance         | 30 pF                           |

Document Number: 001-90865 Rev. \*D

Note

5. This parameter is periodically sampled and not 100% tested.

# **AC Switching Characteristics**

Over the Operating Range

| Param                             | eters [6]         |                          | V <sub>DD</sub> = 2.0 | V to 3.6 V | V <sub>DD</sub> = 2.7 | V to 3.6 V |      |

|-----------------------------------|-------------------|--------------------------|-----------------------|------------|-----------------------|------------|------|

| Cypress<br>Parameter              | Alt.<br>Parameter | Description              | Min                   | Max        | Min                   | Max        | Unit |

| f <sub>SCK</sub>                  | _                 | SCK clock frequency      | 0                     | 25         | 0                     | 40         | MHz  |

| t <sub>CH</sub>                   | _                 | Clock HIGH time          | 18                    | _          | 11                    | _          | ns   |

| t <sub>CL</sub>                   | _                 | Clock LOW time           | 18                    | _          | 11                    | _          | ns   |

| t <sub>CSU</sub>                  | t <sub>CSS</sub>  | Chip select setup        | 12                    | _          | 10                    | _          | ns   |

| t <sub>CSH</sub>                  | t <sub>CSH</sub>  | Chip select hold         | 12                    | _          | 10                    | _          | ns   |

| t <sub>OD</sub> <sup>[7, 8]</sup> | t <sub>HZCS</sub> | Output disable time      | _                     | 20         | _                     | 12         | ns   |

| t <sub>ODV</sub>                  | t <sub>CO</sub>   | Output data valid time   | _                     | 16         | _                     | 9          | ns   |

| t <sub>OH</sub>                   | _                 | Output hold time         | 0                     | _          | 0                     | _          | ns   |

| t <sub>D</sub>                    | _                 | Deselect time            | 60                    | _          | 40                    | _          | ns   |

| t <sub>R</sub> <sup>[9, 10]</sup> | _                 | Data in rise time        | _                     | 50         | _                     | 50         | ns   |

| t <sub>F</sub> <sup>[9, 10]</sup> | _                 | Data in fall time        | _                     | 50         | _                     | 50         | ns   |

| t <sub>SU</sub>                   | t <sub>SD</sub>   | Data setup time          | 8                     | _          | 5                     | _          | ns   |

| t <sub>H</sub>                    | t <sub>HD</sub>   | Data hold time           | 8                     | _          | 5                     | _          | ns   |

| t <sub>HS</sub>                   | t <sub>SH</sub>   | HOLD setup time          | 12                    | _          | 10                    | _          | ns   |

| t <sub>HH</sub>                   | t <sub>HH</sub>   | HOLD hold time           | 12                    | -          | 10                    | _          | ns   |

| t <sub>HZ</sub> [7, 8]            | t <sub>HHZ</sub>  | HOLD LOW to HI-Z         | _                     | 25         | _                     | 20         | ns   |

| t <sub>LZ</sub> [8]               | t <sub>HLZ</sub>  | HOLD HIGH to data active | -                     | 25         | _                     | 20         | ns   |

#### Notes

<sup>6.</sup> Test conditions assume a signal transition time of 3 ns or less, timing reference levels of 0.5 x V<sub>DD</sub>, input pulse levels of 10% to 90% of V<sub>DD</sub>, output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> and 30 pF load capacitance shown in AC Test Conditions.

<sup>7.</sup>  $t_{OD}$  and  $t_{HZ}$  are specified with a load capacitance of 5 pF. Transition is measured when the outputs enter a high impedance state.

<sup>8.</sup> Characterized but not 100% tested in production.

<sup>9.</sup> Rise and fall times measured between 10% and 90% of waveform.

<sup>10.</sup> These parameters are guaranteed by design and are not tested.

SCK

SI

VALID IN

VALID IN

VALID IN

TOD

HI-Z

SO

HI-Z

Figure 17. Synchronous Data Timing (Mode 0)

# **Power Cycle Timing**

Over the Operating Range

| Parameter                           | Description                                                         | Min | Max | Unit |

|-------------------------------------|---------------------------------------------------------------------|-----|-----|------|

| t <sub>PU</sub>                     | Power-up V <sub>DD</sub> (min) to first access ( <del>CS</del> LOW) | 1   | -   | ms   |

| t <sub>PD</sub>                     | Last access (CS HIGH) to power-down (V <sub>DD</sub> (min))         | 0   | _   | μs   |

| t <sub>VR</sub> <sup>[11, 12]</sup> | V <sub>DD</sub> power-up ramp rate                                  | 50  | _   | μs/V |

| t <sub>VF</sub> [11, 12]            | V <sub>DD</sub> power-down ramp rate                                | 100 | _   | µs/V |

| t <sub>REC</sub> [13]               | Recovery time from sleep mode                                       | _   | 400 | μs   |

Figure 19. Power Cycle Timing

- Notes

11. Slope measured at any point on V<sub>DD</sub> waveform.

- 12. These parameters are guaranteed by design and are not tested.

- 13. Refer to Figure 15 on page 10 for sleep mode recovery timing.

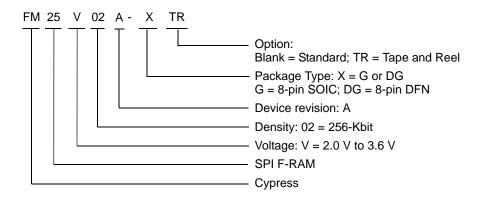

# **Ordering Information**

| Ordering Code | Package<br>Diagram | Package Type | Operating Range |

|---------------|--------------------|--------------|-----------------|

| FM25V02A-G    | 51-85066           | 8-pin SOIC   | Industrial      |

| FM25V02A-DG   | 001-85260          | 8-pin DFN    |                 |

All these parts are Pb-free. Contact your local Cypress sales representative for availability of these parts.

# **Ordering Code Definitions**

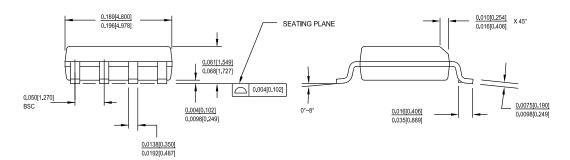

# **Package Diagrams**

Figure 20. 8-pin SOIC (150 Mils) Package Outline, 51-85066

- 1. DIMENSIONS IN INCHES[MM]  $\frac{\text{MIN.}}{\text{MAX.}}$

- PIN 1 ID IS OPTIONAL,

ROUND ON SINGLE LEADFRAME

RECTANGULAR ON MATRIX LEADFRAME

- 3. REFERENCE JEDEC MS-012

- 4. PACKAGE WEIGHT 0.07gms

| PART#   |               |  |

|---------|---------------|--|

| S08.15  | STANDARD PKG  |  |

| SZ08.15 | LEAD FREE PKG |  |

| SW8.15  | LEAD FREE PKG |  |

51-85066 \*G

# Package Diagrams (continued)

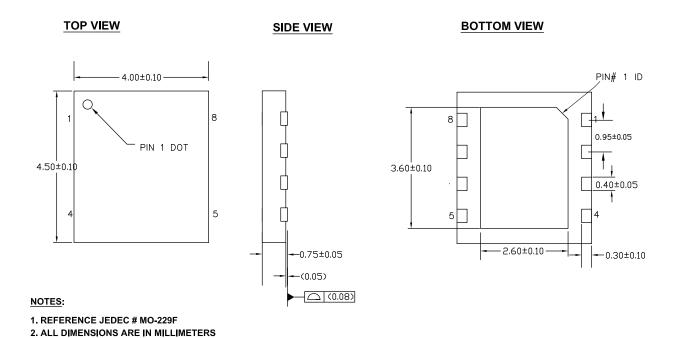

Figure 21. 8-pin DFN (4.0 mm  $\times$  4.5 mm  $\times$  0.8 mm) Package Outline, 001-85260

001-85260 \*B

# Acronyms

| Acronym | Description                                         |

|---------|-----------------------------------------------------|

| СРНА    | Clock Phase                                         |

| CPOL    | Clock Polarity                                      |

| DFN     | Dual Flat No-lead                                   |

| EEPROM  | Electrically Erasable Programmable Read-Only Memory |

| EIA     | Electronic Industries Alliance                      |

| F-RAM   | Ferroelectric Random Access Memory                  |

| I/O     | Input/Output                                        |

| JEDEC   | Joint Electron Devices Engineering Council          |

| JESD    | JEDEC Standards                                     |

| LSB     | Least Significant Bit                               |

| MSB     | Most Significant Bit                                |

| RoHS    | Restriction of Hazardous Substances                 |

| SPI     | Serial Peripheral Interface                         |

| SOIC    | Small Outline Integrated Circuit                    |

# **Document Conventions**

# **Units of Measure**

| Symbol | Unit of Measure |

|--------|-----------------|

| °C     | degree Celsius  |

| Hz     | hertz           |

| kHz    | kilohertz       |

| kΩ     | kilohm          |

| Kbit   | Kilobit         |

| MHz    | megahertz       |

| μΑ     | microampere     |

| μF     | microfarad      |

| μS     | microsecond     |

| mA     | milliampere     |

| ms     | millisecond     |

| ns     | nanosecond      |

| Ω      | ohm             |

| %      | percent         |

| pF     | picofarad       |

| V      | volt            |

| W      | watt            |

# **Document History Page**

| Document Title: FM25V02A, 256-Kbit (32K × 8) Serial (SPI) F-RAM Document Number: 001-90865 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev.                                                                                       | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| **                                                                                         | 4265427 | GVCH               | 01/29/2014         | New data sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *A                                                                                         | 4390913 | GVCH               | 06/20/2014         | Changed status from Advance to Preliminary.  Pin Definitions: Updated $\overline{HOLD}$ pin description Added the sentence, "This pin has a weak internal pull-up (refer to the R <sub>IN</sub> spec in DC Electrical Characteristics)."  Maximum Ratings:Electrostatic Discharge Voltage Removed machine model  DC Electrical Characteristics: Added I <sub>SB</sub> and I <sub>ZZ</sub> typical value Changed R <sub>in</sub> value from 40 k $\Omega$ to 30 k $\Omega$ for V <sub>IN</sub> = V <sub>IH</sub> (min) and 1 M $\Omega$ to 800 k $\Omega$ for V <sub>IN</sub> = V <sub>IL</sub> (max)  Updated footnote 4  Thermal Resistance: Added thermal resistance values |

| *B                                                                                         | 4571858 | GVCH               | 11/18/2014         | Table 1: Added reserved opcodes - 0xC3, 0xC2, 0x5A, 0x5B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *C                                                                                         | 4197512 | ZSK                | 02/10/2015         | Changed status from Preliminary to Final. Replaced "TDFN" with "DFN" in all instances across the document. Updated Functional Description: Added "For a complete list of related resources, click here." at the end. Updated Pin Definitions: Updated description of "EXPOSED PAD". Updated Package Diagrams: spec 51-85066 – Changed revision from *F to *G.                                                                                                                                                                                                                                                                                                                 |

| *D                                                                                         | 4784430 | GVCH               | 06/02/2015         | Updated Package Diagrams:<br>spec 001-85260 – Changed revision from *A to *B.<br>Updated to new template.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Automotive Clocks & Buffers

Interface

Lighting & Power Control

Memory PSoC

Touch Sensing USB Controllers

USB Controlle Wireless/RF cypress.com/go/automotive cypress.com/go/clocks cypress.com/go/interface cypress.com/go/powerpsoc cypress.com/go/memory cypress.com/go/psoc cypress.com/go/touch cypress.com/go/USB cypress.com/go/wireless

# PSoC® Solutions

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

## **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

# **Technical Support**

cypress.com/go/support

© Cypress Semiconductor Corporation, 2014-2015. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.