# PIC16F627A/628A/648A Data Sheet

Flash-Based, 8-Bit CMOS Microcontrollers with nanoWatt Technology

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, Keeloq, Keeloq logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# 18-pin Flash-Based, 8-Bit CMOS Microcontrollers with nanoWatt Technology

### **High-Performance RISC CPU:**

- Operating speeds from DC 20 MHz

- · Interrupt capability

- · 8-level deep hardware stack

- · Direct, Indirect and Relative Addressing modes

- 35 single-word instructions:

- All instructions single cycle except branches

### **Special Microcontroller Features:**

- · Internal and external oscillator options:

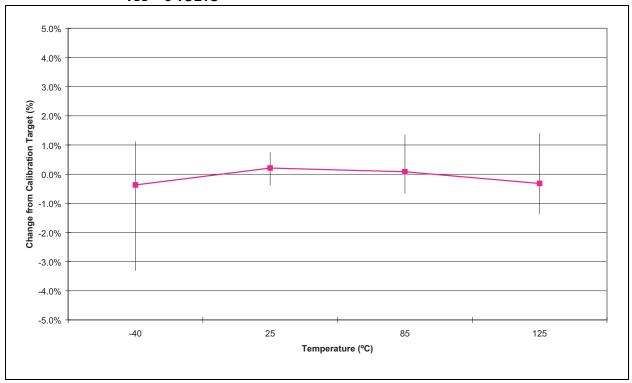

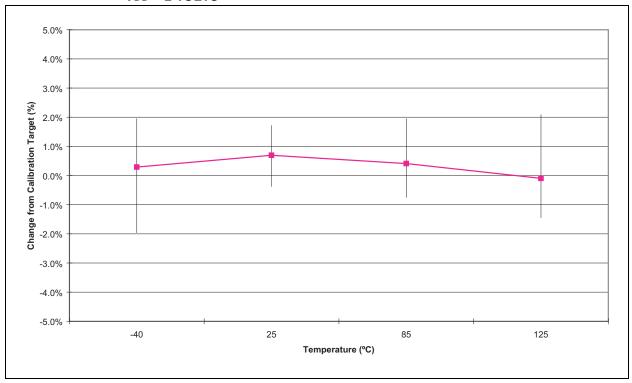

- Precision internal 4 MHz oscillator factory calibrated to ±1%

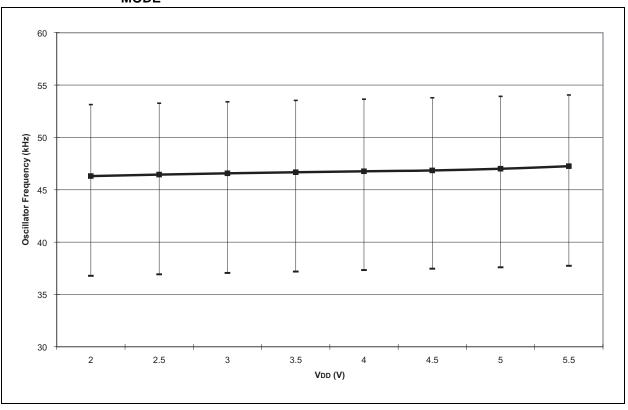

- Low-power internal 48 kHz oscillator

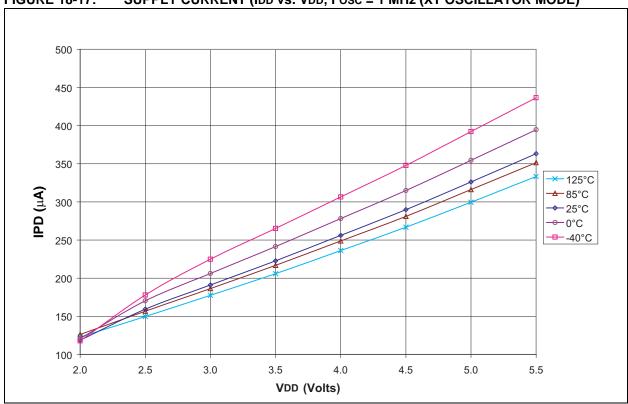

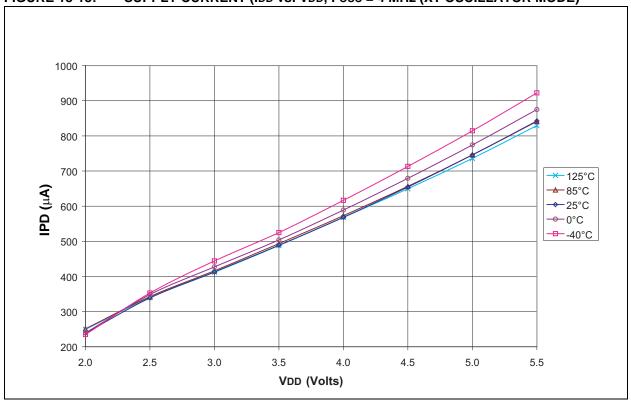

- External Oscillator support for crystals and resonators

- · Power-saving Sleep mode

- Programmable weak pull-ups on PORTB

- · Multiplexed Master Clear/Input-pin

- Watchdog Timer with independent oscillator for reliable operation

- · Low-voltage programming

- In-Circuit Serial Programming<sup>™</sup> (via two pins)

- · Programmable code protection

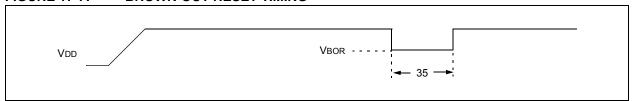

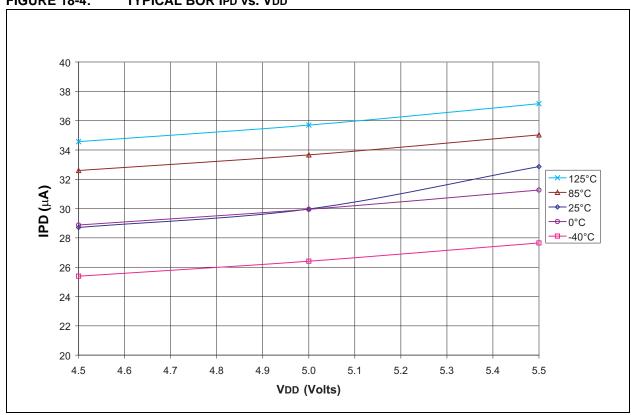

- Brown-out Reset

- · Power-on Reset

- · Power-up Timer and Oscillator Start-up Timer

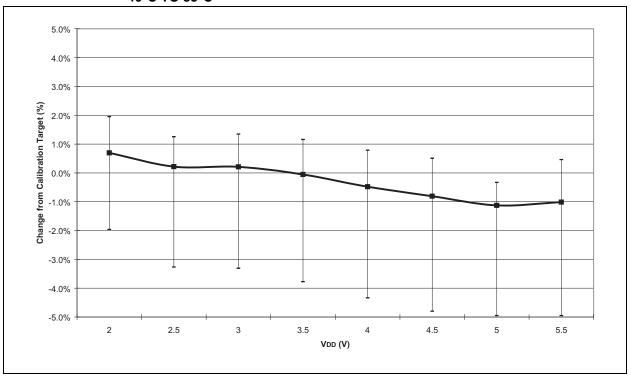

- Wide operating voltage range (2.0-5.5V)

- · Industrial and extended temperature range

- High-Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- 40 year data retention

### Low-Power Features:

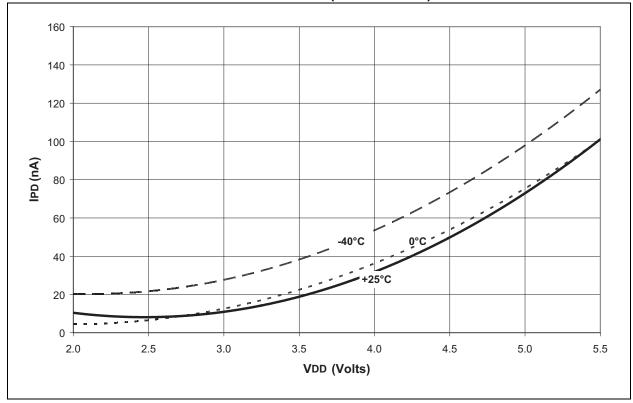

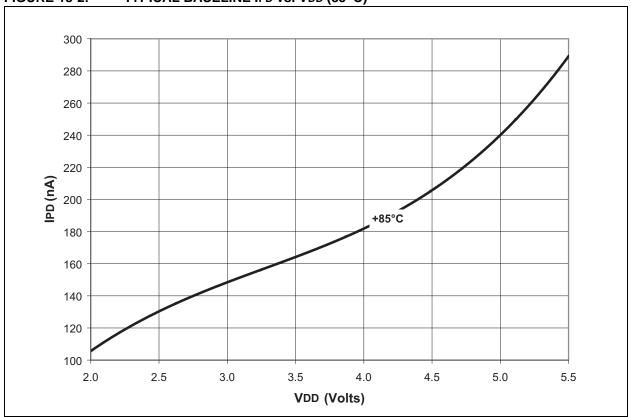

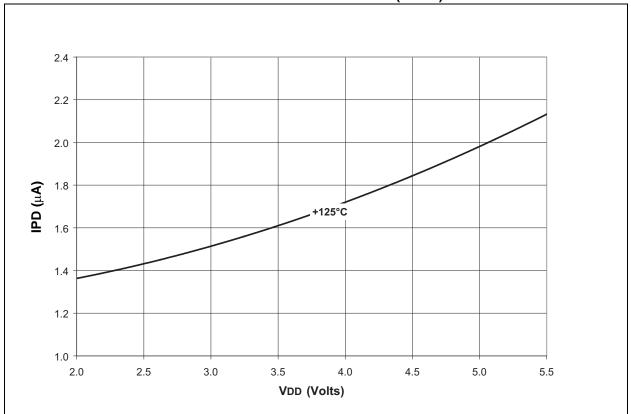

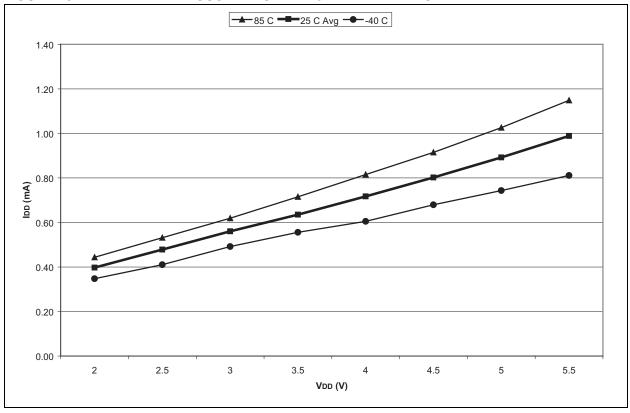

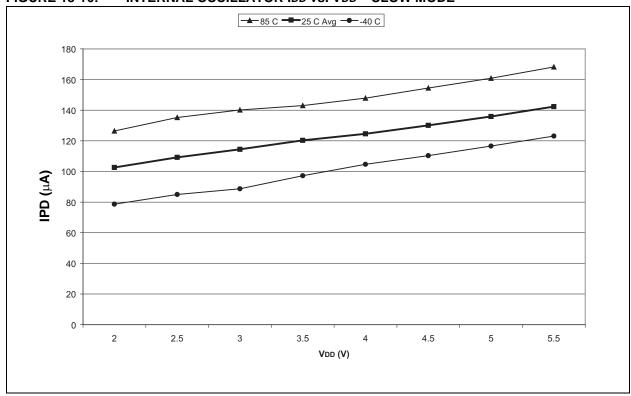

- · Standby Current:

- 100 nA @ 2.0V, typical

- · Operating Current:

- 12 μA @ 32 kHz, 2.0V, typical

- 120 μA @ 1 MHz, 2.0V, typical

- · Watchdog Timer Current:

- 1 μA @ 2.0V, typical

- · Timer1 Oscillator Current:

- 1.2 μA @ 32 kHz, 2.0V, typical

- · Dual-speed Internal Oscillator:

- Run-time selectable between 4 MHz and 48 kHz

- 4 μs wake-up from Sleep, 3.0V, typical

### **Peripheral Features:**

- · 16 I/O pins with individual direction control

- · High current sink/source for direct LED drive

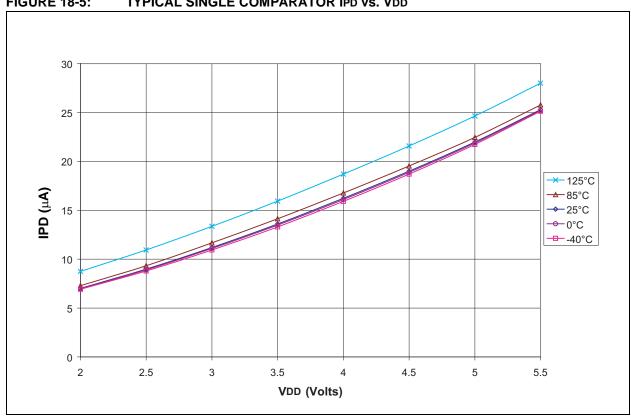

- · Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Selectable internal or external reference

- Comparator outputs are externally accessible

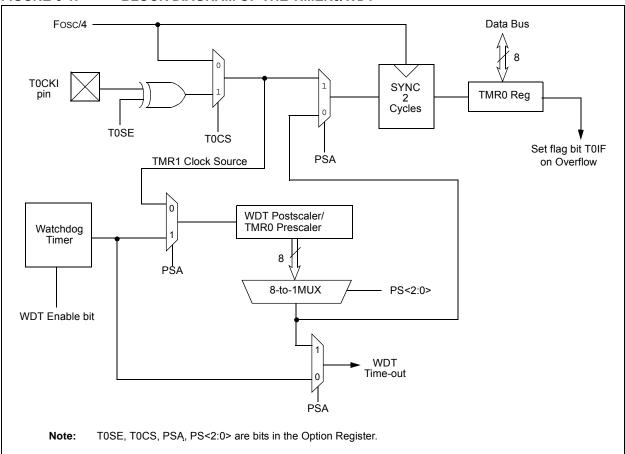

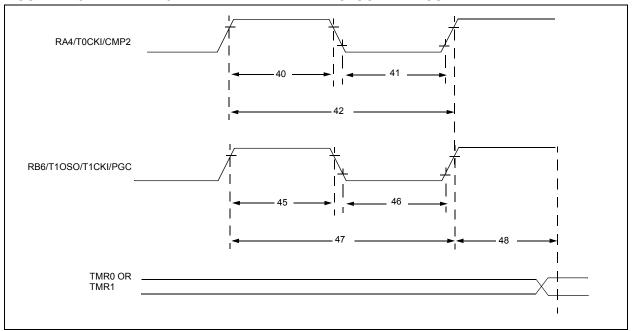

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

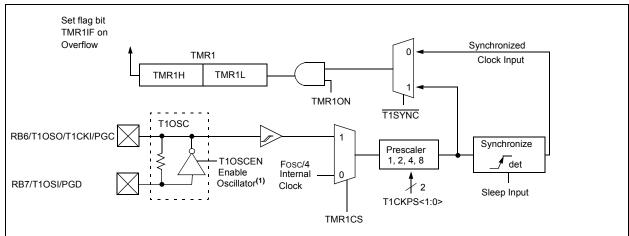

- Timer1: 16-bit timer/counter with external crystal/ clock capability

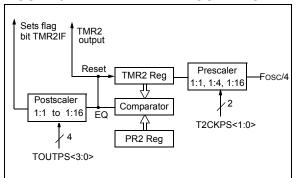

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

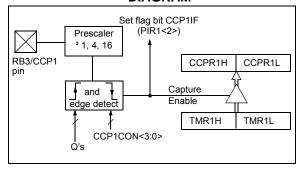

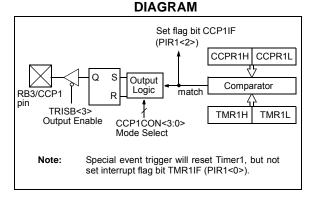

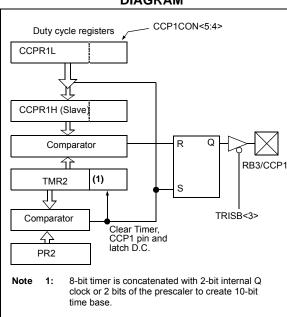

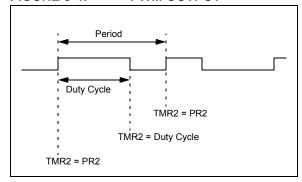

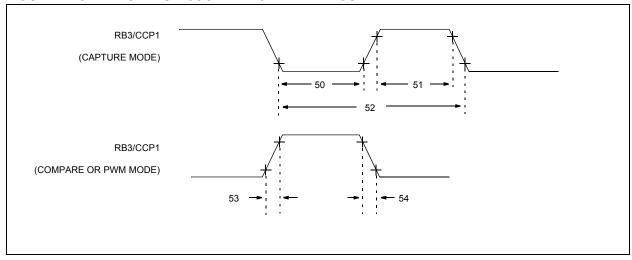

- · Capture, Compare, PWM module:

- 16-bit Capture/Compare

- 10-bit PWM

- Addressable Universal Synchronous/Asynchronous Receiver/Transmitter USART/SCI

| Device     | Program<br>Memory | Data N          | lemory            | 1/0 | ССР   | USART | Compositors | Timers   |  |

|------------|-------------------|-----------------|-------------------|-----|-------|-------|-------------|----------|--|

| Device     | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | (PWM) | USART | Comparators | 8/16-bit |  |

| PIC16F627A | 1024              | 224             | 128               | 16  | 1     | Y     | 2           | 2/1      |  |

| PIC16F628A | 2048              | 224             | 128               | 16  | 1     | Y     | 2           | 2/1      |  |

| PIC16F648A | 4096              | 256             | 256               | 16  | 1     | Υ     | 2           | 2/1      |  |

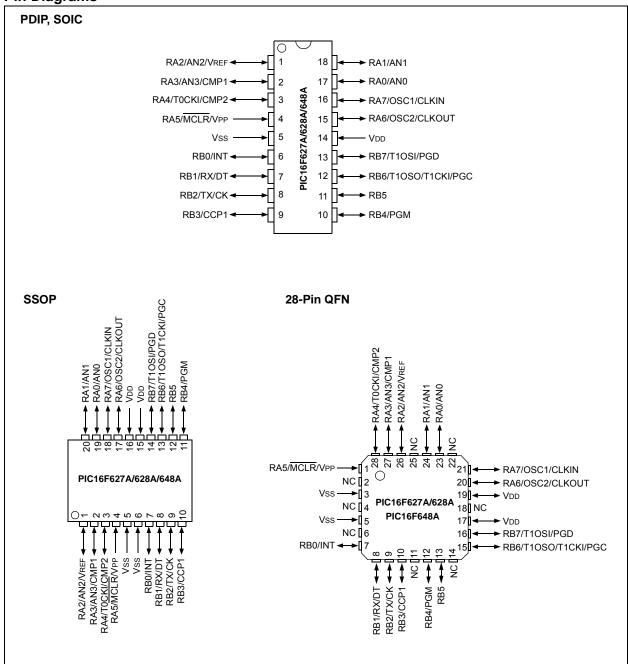

### **Pin Diagrams**

#### **Table of Contents**

| 1.0 General Description                                                     | 7    |

|-----------------------------------------------------------------------------|------|

| 2.0 PIC16F627A/628A/648A Device Varieties                                   | 9    |

| 3.0 Architectural Overview                                                  | . 11 |

| 4.0 Memory Organization                                                     | 17   |

| 5.0 I/O Ports                                                               | . 33 |

| 6.0 Timer0 Module                                                           | 47   |

| 7.0 Timer1 Module                                                           | 50   |

| 8.0 Timer2 Module                                                           | . 54 |

| 9.0 Capture/Compare/PWM (CCP) Module                                        | . 57 |

| 10.0 Comparator Module                                                      |      |

| 11.0 Voltage Reference Module                                               | . 69 |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) Module | . 73 |

| 13.0 Data EEPROM Memory                                                     |      |

| 14.0 Special Features of the CPU                                            |      |

| 15.0 Instruction Set Summary                                                | 117  |

| 16.0 Development Support                                                    | 131  |

| 17.0 Electrical Specifications                                              | 135  |

| 18.0 DC and AC Characteristics Graphs and Tables                            | 151  |

| 19.0 Packaging Information                                                  | 163  |

| Appendix A: Data Sheet Revision History                                     |      |

| Appendix B: Device Differences                                              | 171  |

| Appendix C: Device Migrations                                               |      |

| Appendix D: Migrating from other PIC <sup>®</sup> Devices                   | 172  |

| The Microchip Web Site                                                      | 173  |

| Customer Change Notification Service                                        |      |

| Customer Support                                                            | 173  |

| Reader Response                                                             | 174  |

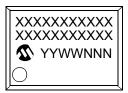

| Product Identification System                                               | 179  |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

### 1.0 GENERAL DESCRIPTION

The PIC16F627A/628A/648A are 18-pin Flash-based members of the versatile PIC16F627A/628A/648A family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC® microcontrollers employ an advanced RISC architecture. The PIC16F627A/628A/648A have enhanced core features, an eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available, complemented by a large register set

PIC16F627A/628A/648A microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC16F627A/628A/648A devices have integrated features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption.

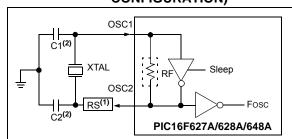

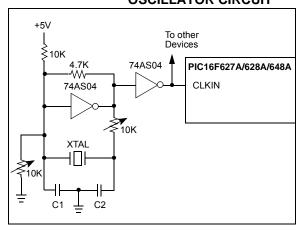

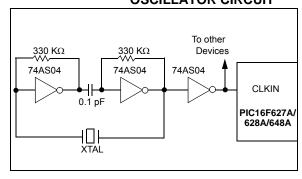

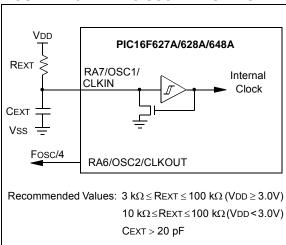

The PIC16F627A/628A/648A has 8 oscillator configurations. The single-pin RC oscillator provides a low-cost solution. The LP oscillator minimizes power consumption, XT is a standard crystal, and INTOSC is a self-contained precision two-speed internal oscillator.

The HS mode is for High-Speed crystals. The EC mode is for an external clock source.

The Sleep (Power-down) mode offers power savings. Users can wake-up the chip from Sleep through several external interrupts, internal interrupts and Resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

Table 1-1 shows the features of the PIC16F627A/628A/648A mid-range microcontroller family.

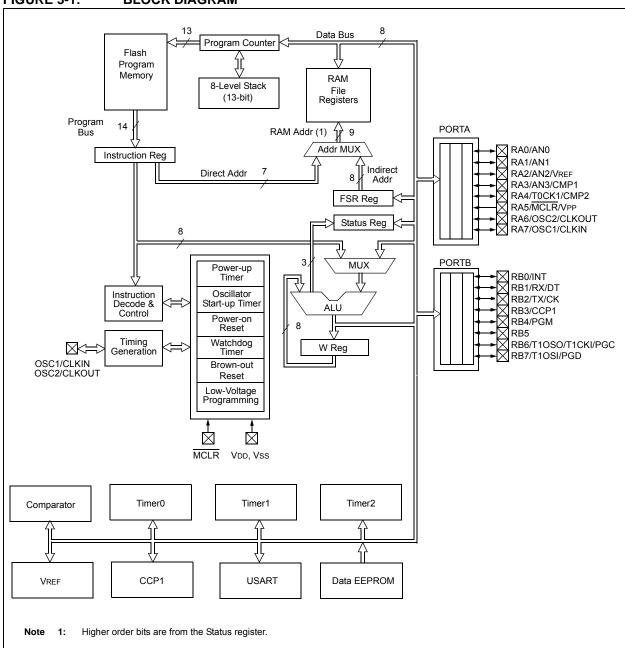

A simplified block diagram of the PIC16F627A/628A/648A is shown in Figure 3-1.

The PIC16F627A/628A/648A series fits in applications ranging from battery chargers to low power remote sensors. The Flash technology makes customizing application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages makes this microcontroller series ideal for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16F627A/628A/648A very versatile.

### 1.1 Development Support

The PIC16F627A/628A/648A family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost in-circuit debugger, a low cost development programmer and a full-featured programmer. A Third Party "C" compiler support tool is also available.

TABLE 1-1: PIC16F627A/628A/648A FAMILY OF DEVICES

|             |                                      | PIC16F627A                                         | PIC16F628A                                         | PIC16F648A                                         | PIC16LF627A                                        | PIC16LF628A                                        | PIC16LF648A                                        |

|-------------|--------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                                                 | 20                                                 | 20                                                 | 20                                                 | 20                                                 | 20                                                 |

|             | Flash Program<br>Memory (words)      | 1024                                               | 2048                                               | 4096                                               | 1024                                               | 2048                                               | 4096                                               |

| Memory      | RAM Data Memory (bytes)              | 224                                                | 224                                                | 256                                                | 224                                                | 224                                                | 256                                                |

|             | EEPROM Data<br>Memory (bytes)        | 128                                                | 128                                                | 256                                                | 128                                                | 128                                                | 256                                                |

|             | Timer module(s)                      | TMR0, TMR1,<br>TMR2                                |

|             | Comparator(s)                        | 2                                                  | 2                                                  | 2                                                  | 2                                                  | 2                                                  | 2                                                  |

| Peripherals | Capture/Compare/<br>PWM modules      | 1                                                  | 1                                                  | 1                                                  | 1                                                  | 1                                                  | 1                                                  |

|             | Serial Communications                | USART                                              | USART                                              | USART                                              | USART                                              | USART                                              | USART                                              |

|             | Internal Voltage<br>Reference        | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                |

|             | Interrupt Sources                    | 10                                                 | 10                                                 | 10                                                 | 10                                                 | 10                                                 | 10                                                 |

|             | I/O Pins                             | 16                                                 | 16                                                 | 16                                                 | 16                                                 | 16                                                 | 16                                                 |

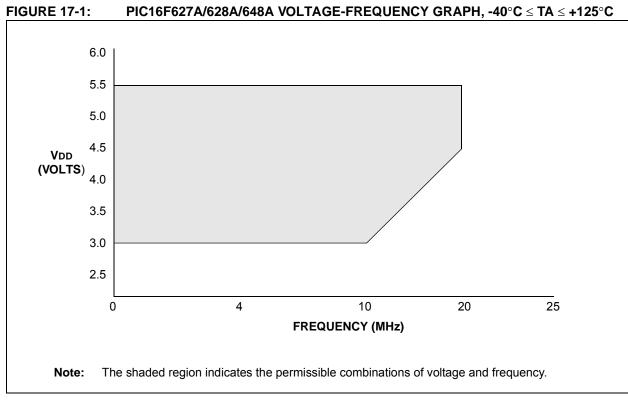

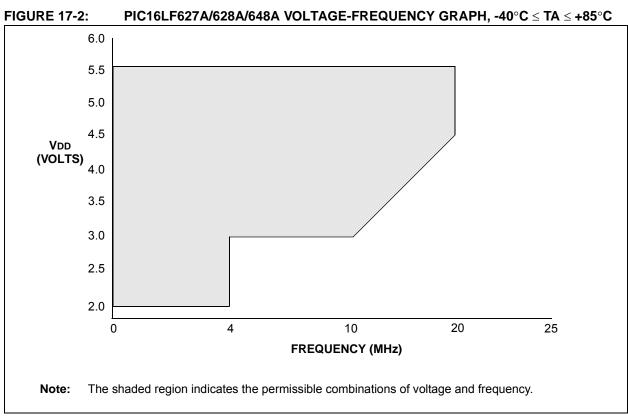

| Features    | Voltage Range (Volts)                | 3.0-5.5                                            | 3.0-5.5                                            | 3.0-5.5                                            | 2.0-5.5                                            | 2.0-5.5                                            | 2.0-5.5                                            |

|             | Brown-out Reset                      | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                | Yes                                                |

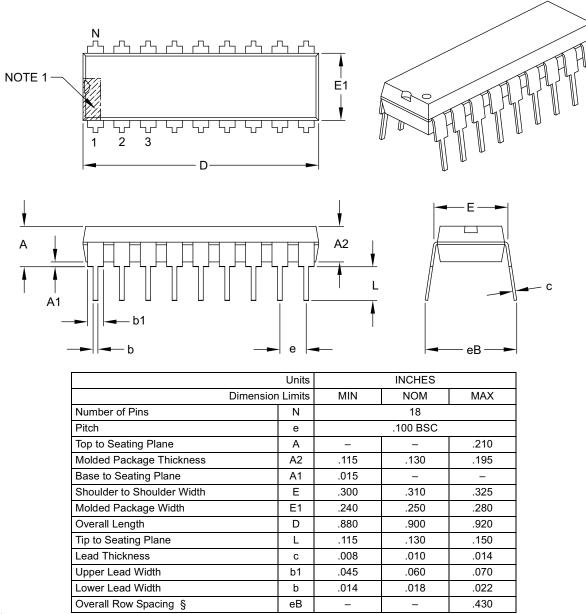

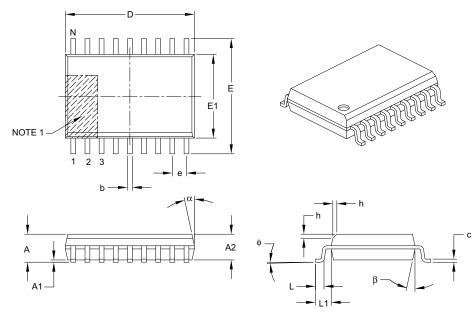

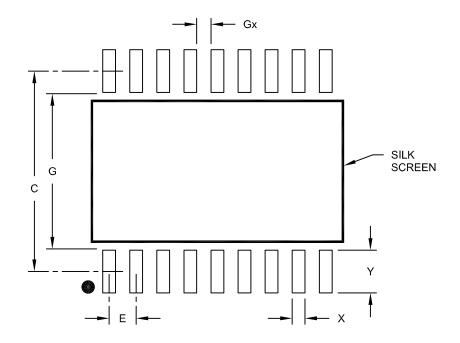

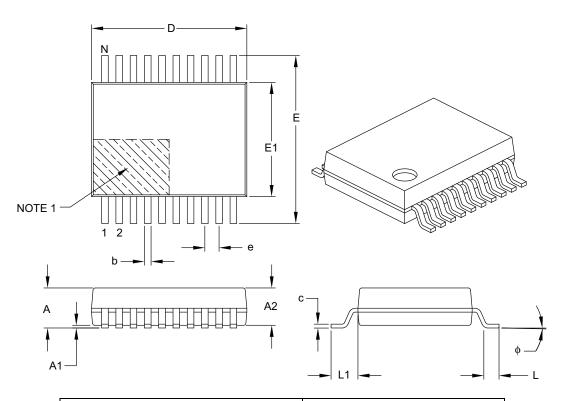

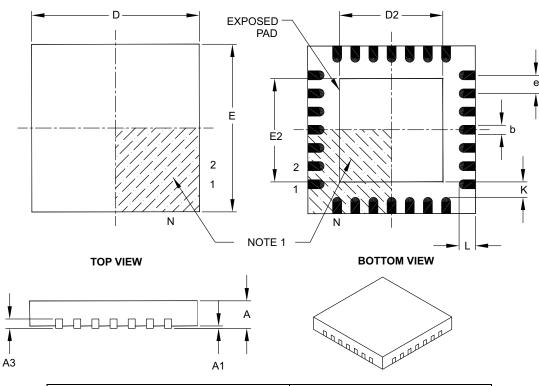

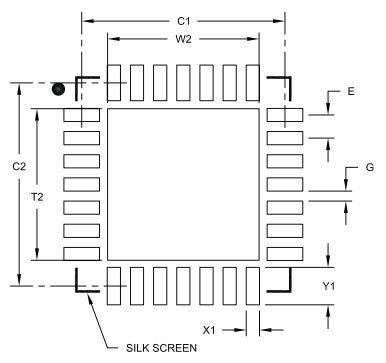

|             | Packages                             | 18-pin DIP,<br>SOIC, 20-pin<br>SSOP,<br>28-pin QFN |

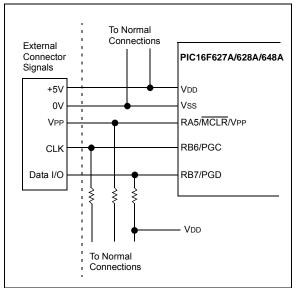

All PIC® family devices have Power-on Reset, selectable Watchdog Timer, selectable code-protect and high I/O current capability. All PIC16F627A/628A/648A family devices use serial programming with clock pin RB6 and data pin RB7.

NOTES:

# 2.0 PIC16F627A/628A/648A DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16F627A/628A/648A Product Identification System, at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

#### 2.1 Flash Devices

Flash devices can be erased and re-programmed electrically. This allows the same device to be used for prototype development, pilot programs and production.

A further advantage of the electrically erasable Flash is that it can be erased and reprogrammed in-circuit, or by device programmers, such as Microchip's PICSTART® Plus or PRO MATE® II programmers.

# 2.2 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are standard Flash devices, but with all program locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

### 2.3 Serialized Quick-Turnaround-Production (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

NOTES:

### 3.0 ARCHITECTURAL OVERVIEW

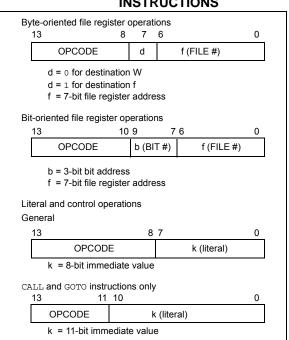

The high performance of the PIC16F627A/628A/648A family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16F627A/628A/648A uses a Harvard architecture in which program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional Von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single-word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single-cycle (200 ns @ 20 MHz) except for program branches.

Table 3-1 lists device memory sizes (Flash, Data and EEPROM).

TABLE 3-1: DEVICE MEMORY LIST

|             | Memory           |             |                |  |  |  |  |  |  |

|-------------|------------------|-------------|----------------|--|--|--|--|--|--|

| Device      | Flash<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |  |  |  |

| PIC16F627A  | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |  |  |

| PIC16F628A  | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |  |  |

| PIC16F648A  | 4096 x 14        | 256 x 8     | 256 x 8        |  |  |  |  |  |  |

| PIC16LF627A | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |  |  |

| PIC16LF628A | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |  |  |

| PIC16LF648A | 4096 x 14        | 256 x 8     | 256 x 8        |  |  |  |  |  |  |

The PIC16F627A/628A/648A can directly or indirectly address its register files or data memory. All Special Function Registers (SFR), including the program counter, are mapped in the data memory. The PIC16F627A/628A/648A have an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any addressing mode. This symmetrical nature and lack of 'special optimal situations' makes programming with the PIC16F627A/628A/648A simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16F627A/628A/648A devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the Status Register. The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, and a description of the device pins in Table 3-2.

Two types of data memory are provided on the PIC16F627A/628A/648A devices. Nonvolatile EEPROM data memory is provided for long term storage of data, such as calibration values, look-up table data, and any other data which may require periodic updating in the field. These data types are not lost when power is removed. The other data memory provided is regular RAM data memory. Regular RAM data memory is provided for temporary storage of data during normal operation. Data is lost when power is removed.

FIGURE 3-1: BLOCK DIAGRAM

TABLE 3-2: PIC16F627A/628A/648A PINOUT DESCRIPTION

| Name               | Function | Input Type | Output Type | Description                                                                                                                                                    |

|--------------------|----------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0            | RA0      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | AN0      | AN         | _           | Analog comparator input                                                                                                                                        |

| RA1/AN1            | RA1      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | AN1      | AN         | _           | Analog comparator input                                                                                                                                        |

| RA2/AN2/VREF       | RA2      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | AN2      | AN         | _           | Analog comparator input                                                                                                                                        |

|                    | VREF     | _          | AN          | VREF output                                                                                                                                                    |

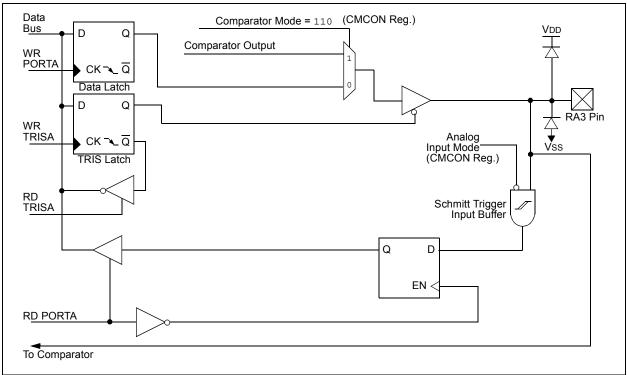

| RA3/AN3/CMP1       | RA3      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | AN3      | AN         | _           | Analog comparator input                                                                                                                                        |

|                    | CMP1     | _          | CMOS        | Comparator 1 output                                                                                                                                            |

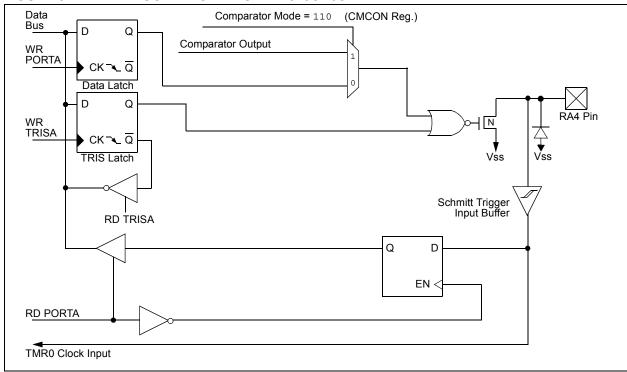

| RA4/T0CKI/CMP2     | RA4      | ST         | OD          | Bidirectional I/O port                                                                                                                                         |

|                    | T0CKI    | ST         | _           | Timer0 clock input                                                                                                                                             |

|                    | CMP2     | _          | OD          | Comparator 2 output                                                                                                                                            |

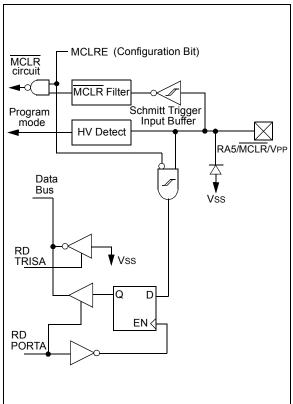

| RA5/MCLR/VPP       | RA5      | ST         | _           | Input port                                                                                                                                                     |

|                    | MCLR     | ST         | _           | Master clear. When configured as MCLR, this pin is an active low Reset to the device.  Voltage on MCLR/VPP must not exceed VDD during normal device operation. |

|                    | VPP      | _          | _           | Programming voltage input                                                                                                                                      |

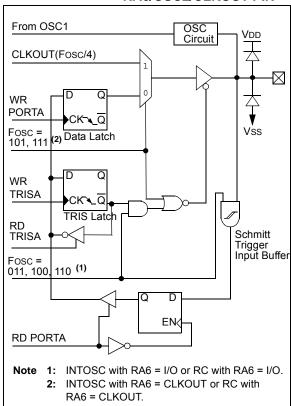

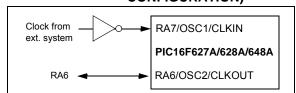

| RA6/OSC2/CLKOUT    | RA6      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | OSC2     | _          | XTAL        | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                                                                        |

|                    | CLKOUT   | _          | CMOS        | In RC/INTOSC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1.                                                                            |

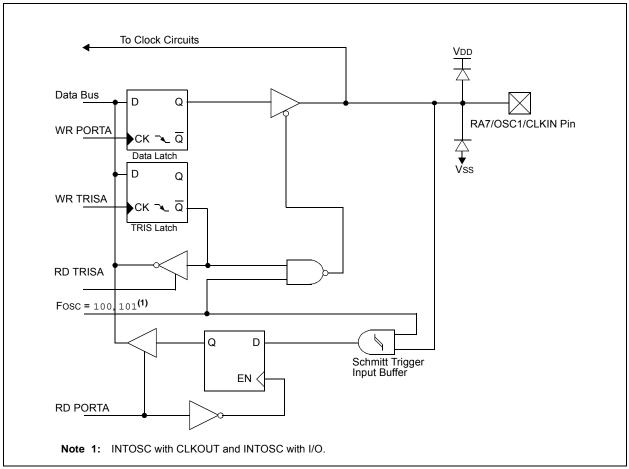

| RA7/OSC1/CLKIN     | RA7      | ST         | CMOS        | Bidirectional I/O port                                                                                                                                         |

|                    | OSC1     | XTAL       | _           | Oscillator crystal input                                                                                                                                       |

|                    | CLKIN    | ST         | _           | External clock source input. RC biasing pin.                                                                                                                   |

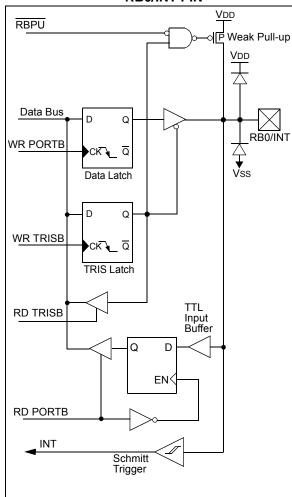

| RB0/INT            | RB0      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                  |

|                    | INT      | ST         | _           | External interrupt                                                                                                                                             |

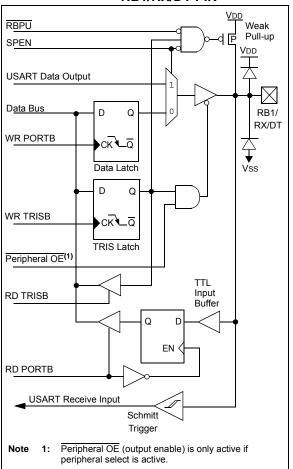

| RB1/RX/DT          | RB1      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                  |

|                    | RX       | ST         | _           | USART receive pin                                                                                                                                              |

|                    | DT       | ST         | CMOS        | Synchronous data I/O                                                                                                                                           |

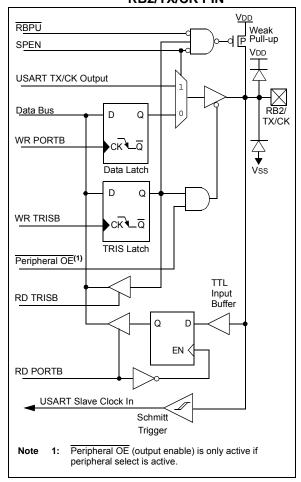

| RB2/TX/CK          | RB2      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                  |

|                    | TX       | _          | CMOS        | USART transmit pin                                                                                                                                             |

|                    | CK       | ST         | CMOS        | Synchronous clock I/O                                                                                                                                          |

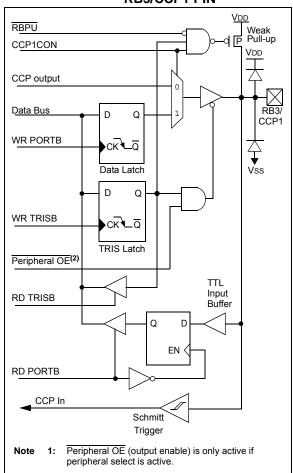

| RB3/CCP1           | RB3      | TTL        | CMOS        | Bidirectional I/O port. Can be software programmed for internal weak pull-up.                                                                                  |

|                    | CCP1     | ST         | CMOS        | Capture/Compare/PWM I/O                                                                                                                                        |

| Legend: O = Output |          | 01100      | MOS Output  | D = Dower                                                                                                                                                      |

**Legend:** O = Output CMOS = CMOS Output P = Power

— = Not used I = Input ST = Schmitt Trigger Input

TTL = TTL Input OD = Open Drain Output AN = Analog

TABLE 3-2: PIC16F627A/628A/648A PINOUT DESCRIPTION (CONTINUED)

| Name                | Function | Input Type | Output Type | Description                                                                                                                                     |

|---------------------|----------|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

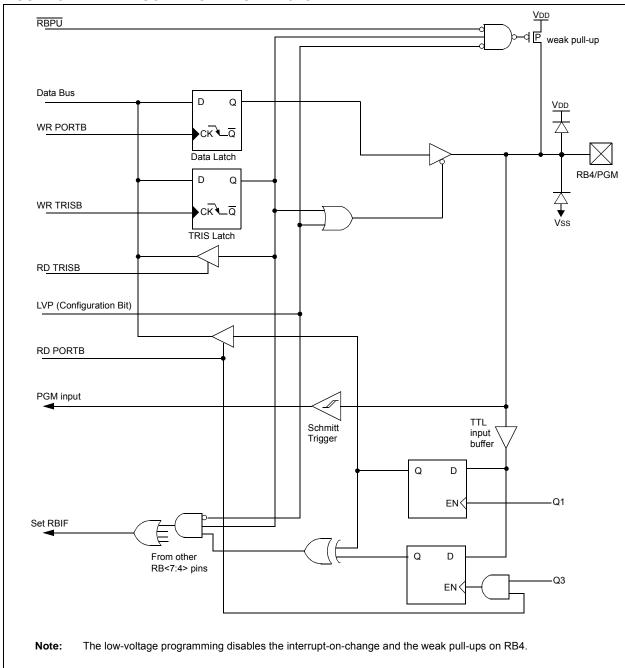

| RB4/PGM             | RB4      | TTL        | CMOS        | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                    |

|                     | PGM      | ST         | _           | Low-voltage programming input pin. When low-voltage programming is enabled, the interrupt-on-pin change and weak pull-up resistor are disabled. |

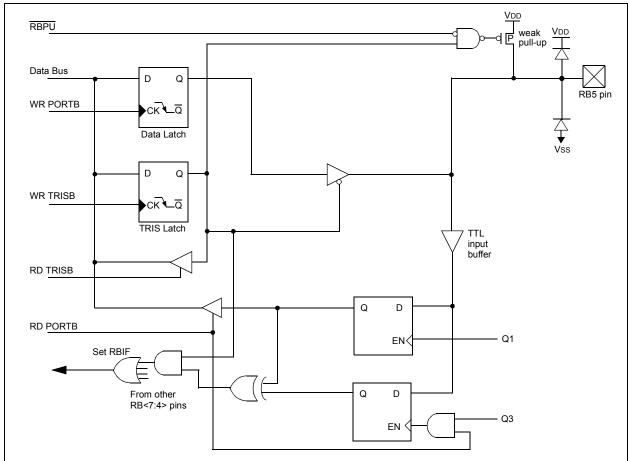

| RB5                 | RB5      | TTL        | CMOS        | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                    |

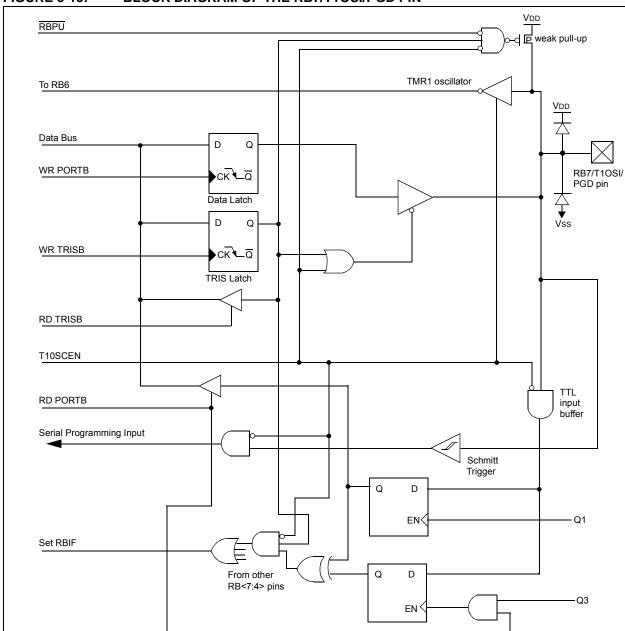

| RB6/T1OSO/T1CKI/PGC | RB6      | TTL        | CMOS        | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                    |

|                     | T10S0    | _          | XTAL        | Timer1 oscillator output                                                                                                                        |

|                     | T1CKI    | ST         | _           | Timer1 clock input                                                                                                                              |

|                     | PGC      | ST         | _           | ICSP™ programming clock                                                                                                                         |

| RB7/T1OSI/PGD       | RB7      | TTL        | CMOS        | Bidirectional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                    |

|                     | T10SI    | XTAL       | _           | Timer1 oscillator input                                                                                                                         |

|                     | PGD      | ST         | CMOS        | ICSP data I/O                                                                                                                                   |

| Vss                 | Vss      | Power      | _           | Ground reference for logic and I/O pins                                                                                                         |

| VDD                 | VDD      | Power      | _           | Positive supply for logic and I/O pins                                                                                                          |

**Legend:** O = Output CMOS = CMOS Output P = Power

— = Not used I = Input ST = Schmitt Trigger Input

TTL = TTL Input OD = Open Drain Output AN = Analog

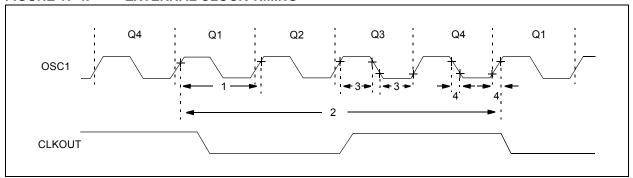

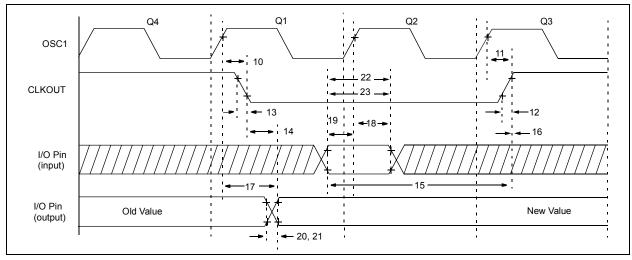

# 3.1 Clocking Scheme/Instruction Cycle

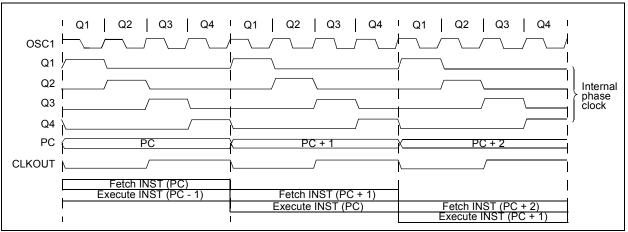

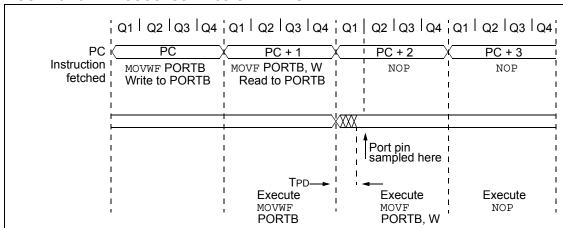

The clock input (RA7/OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the Program Counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

### 3.2 Instruction Flow/Pipelining

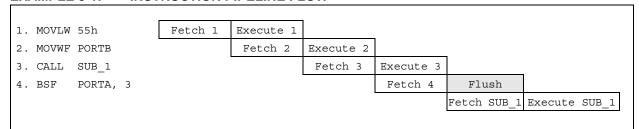

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

**Note:** All instructions are single cycle except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

NOTES:

### 4.0 MEMORY ORGANIZATION

### 4.1 Program Memory Organization

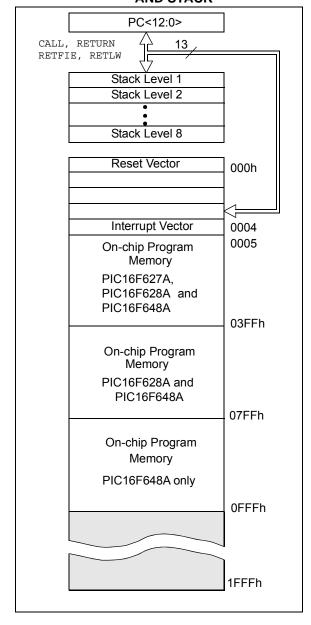

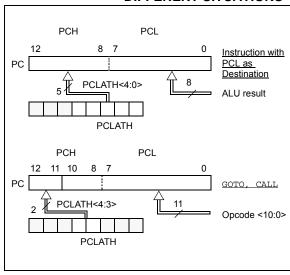

The PIC16F627A/628A/648A has a 13-bit program counter capable of addressing an  $8K \times 14$  program memory space. Only the first  $1K \times 14$  (0000h-03FFh) for the PIC16F627A,  $2K \times 14$  (0000h-07FFh) for the PIC16F628A and  $4K \times 14$  (0000h-0FFFh) for the PIC16F648A are physically implemented. Accessing a location above these boundaries will cause a wraparound within the first  $1K \times 14$  space (PIC16F627A),  $2K \times 14$  space (PIC16F628A) or  $4K \times 14$  space (PIC16F648A). The Reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1).

FIGURE 4-1: PROGRAM MEMORY MAP AND STACK

### 4.2 Data Memory Organization

The data memory (Figure 4-2 and Figure 4-3) is partitioned into four banks, which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). The SFRs are located in the first 32 locations of each bank. There are General Purpose Registers implemented as static RAM in each bank. Table 4-1 lists the General Purpose Register available in each of the four banks.

TABLE 4-1: GENERAL PURPOSE STATIC RAM REGISTERS

|       | PIC16F627A/628A      | PIC16F648A |

|-------|----------------------|------------|

| Bank0 | 20-7Fh               | 20-7Fh     |

| Bank1 | A0h-FF               | A0h-FF     |

| Bank2 | 120h-14Fh, 170h-17Fh | 120h-17Fh  |

| Bank3 | 1F0h-1FFh            | 1F0h-1FFh  |

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are implemented as common RAM and mapped back to addresses 70h-7Fh.

Table 4-2 lists how to access the four banks of registers via the Status register bits RP1 and RP0.

TABLE 4-2: ACCESS TO BANKS OF REGISTERS

| Bank | RP1 | RP0 |

|------|-----|-----|

| 0    | 0   | 0   |

| 1    | 0   | 1   |

| 2    | 1   | 0   |

| 3    | 1   | 1   |

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 224 x 8 in the PIC16F627A/628A and 256 x 8 in the PIC16F648A. Each is accessed either directly or indirectly through the File Select Register (FSR), See **Section 4.4** "Indirect Addressing, INDF and FSR Registers".

FIGURE 4-2: DATA MEMORY MAP OF THE PIC16F627A AND PIC16F628A

| Indirect addr.(1) | 00h        | Indirect addr.(1)     | 00: | Indirect addr.(1)   | 100h          | Indirect addr.(1) | ] 40       |

|-------------------|------------|-----------------------|-----|---------------------|---------------|-------------------|------------|

| TMR0              | -          |                       | 80h |                     |               | OPTION            | 18         |

|                   | 01h        | OPTION                | 81h | TMR0<br>PCL         | 101h<br>102h  |                   | 18         |

| PCL               | 02h<br>03h | PCL                   | 82h | STATUS              | 102h          | PCL               | 18         |

| STATUS            | 4          | STATUS                | 83h | FSR                 | 103h          | STATUS            | 18         |

| FSR               | 04h        | FSR                   | 84h | FOR                 | 10411<br>105h | FSR               | 18         |

| PORTA             | 05h        | TRISA                 | 85h | PORTB               | 106h          | TRISB             | 18         |

| PORTB             | 06h        | TRISB                 | 86h | PORTB               | 100h          | TRISB             | 18         |

|                   | 07h        |                       | 87h |                     |               |                   | 18         |

|                   | 08h        |                       | 88h |                     | 108h          |                   | 18         |

| 501.4711          | 09h        |                       | 89h | DOLATII.            | 109h          | DOL ATU           | 18         |

| PCLATH            | 0Ah        | PCLATH                | 8Ah | PCLATH              | 10Ah          | PCLATH            | 18         |

| INTCON            | 0Bh        | INTCON                | 8Bh | INTCON              | 10Bh          | INTCON            | 18         |

| PIR1              | 0Ch        | PIE1                  | 8Ch |                     | 10Ch          |                   | 18         |

|                   | 0Dh        |                       | 8Dh |                     | 10Dh          |                   | 18         |

| TMR1L             | 0Eh        | PCON                  | 8Eh |                     | 10Eh          |                   | 18         |

| TMR1H             | 0Fh        |                       | 8Fh |                     | 10Fh          |                   | 18         |

| T1CON             | 10h        |                       | 90h |                     |               |                   |            |

| TMR2              | 11h        |                       | 91h |                     |               |                   |            |

| T2CON             | 12h        | PR2                   | 92h |                     |               |                   |            |

|                   | 13h        |                       | 93h |                     |               |                   |            |

|                   | 14h        |                       | 94h |                     |               |                   |            |

| CCPR1L            | 15h        |                       | 95h |                     |               |                   |            |

| CCPR1H            | 16h        |                       | 96h |                     |               |                   |            |

| CCP1CON           | 17h        |                       | 97h |                     |               |                   |            |

| RCSTA             | 18h        | TXSTA                 | 98h |                     |               |                   |            |

| TXREG             | 19h        | SPBRG                 | 99h |                     |               |                   |            |

| RCREG             | 1Ah        | EEDATA                | 9Ah |                     |               |                   |            |

|                   | 1Bh        | EEADR                 | 9Bh |                     |               |                   |            |

|                   | 1Ch        | EECON1                | 9Ch |                     |               |                   |            |

|                   | 1Dh        | EECON2 <sup>(1)</sup> | 9Dh |                     |               |                   |            |

|                   | 1Eh        |                       | 9Eh |                     |               |                   |            |

| CMCON             | 1Fh        | VRCON                 | 9Fh |                     | 11Fh          |                   |            |

|                   | 20h        |                       | A0h | General             | 120h          |                   |            |

| General           |            | General               | Aon | Purpose<br>Register |               |                   |            |

| Purpose           |            | Purpose               |     | 48 Bytes            | 14Fh          |                   |            |

| Register          |            | Register<br>80 Bytes  |     | -                   | 150h          |                   |            |

| 80 Bytes          |            | oo byles              |     |                     |               |                   |            |

|                   | 6Fh        |                       | EFh |                     | 16Fh          |                   | 1E         |

|                   | 70h        |                       | F0h |                     | 170h          |                   | 1F         |

| 16 Bytes          |            | accesses              |     | accesses            |               | accesses          |            |

|                   | 75         | 70h-7Fh               |     | 70h-7Fh             | 1755          | 70h-7Fh           | 4-         |

| Bank 0            | 7Fh        | Bank 1                | FFh | Bank 2              | 17Fh          | Bank 3            | <b>ا</b> ا |

| Dank 0            |            | Daint 1               |     | Dailly E            |               | 23.11.0           |            |

FIGURE 4-3: **DATA MEMORY MAP OF THE PIC16F648A** File Address Indirect addr. (1) Indirect addr.(1) Indirect addr. (1) Indirect addr. (1) 100h 00h 80h 180h 101h OPTION TMR0 01h **OPTION** TMR0 81h 181h PCL 102h PCL 02h PCL 82h **PCL** 182h **STATUS** 103h **STATUS** 03h **STATUS STATUS** 83h 183h **FSR** 04h **FSR** 104h FSR 184h **FSR** 84h 105h **PORTA** 05h 185h **TRISA** 85h TRISB **PORTB PORTB** 06h 106h **TRISB** 86h 186h 07h 107h 87h 187h 08h 108h 88h 188h 09h 109h 189h 89h **PCLATH** 10Ah **PCLATH** 0Ah **PCLATH** 8Ah **PCLATH** 18Ah INTCON 0Bh INTCON 10Bh INTCON INTCON 8Bh 18Bh PIR1 0Ch 10Ch 18Ch PIE1 8Ch 10Dh 0Dh 18Dh 8Dh 10Eh TMR1L 0Eh **PCON** 8Eh 18Eh TMR1H 0Fh 10Fh 18Fh 8Fh T1CON 10h 90h TMR2 11h 91h T2CON 12h PR2 92h 13h 93h 14h 94h CCPR1L 15h 95h CCPR1H 16h 96h CCP1CON 17h 97h 18h **RCSTA TXSTA** 98h 19h 99h **TXREG** SPBRG EEDATA 1Ah **RCREG** 9Ah 1Bh **EEADR** 9Bh EECON1 1Ch 9Ch EECON2(1) 1Dh 9Dh 1Eh 9Eh 1Fh **CMCON VRCON** 9Fh 11Fh 20h 120h A0h General General General Purpose Purpose Purpose Register 80 Bytes Register Register 80 Bytes 80 Bytes 1EFh 6Fh **EFh** 16Fh 1F0h 70h F0h 170h accesses accesses accesses 16 Bytes 70h-7Fh 70h-7Fh 70h-7Fh 1FFh 7Fh FFh 17Fh Bank 1 Bank 2 Bank 3 Bank 0 Unimplemented data memory locations, read as '0'. Note 1: Not a physical register.

### 4.2.2 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 4-3). These registers are static RAM.

The special registers can be classified into two sets (core and peripheral). The SFRs associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

TABLE 4-3: SPECIAL REGISTERS SUMMARY BANKO

| Address | Name    | Bit 7      | Bit 6                            | Bit 5         | Bit 4           | Bit 3           | Bit 2         | Bit 1        | Bit 0        | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|---------|------------|----------------------------------|---------------|-----------------|-----------------|---------------|--------------|--------------|-----------------------------------------|--------------------|

| Bank 0  |         |            |                                  |               |                 |                 |               |              |              |                                         |                    |

| 00h     | INDF    | Addressir  | ng this location                 | on uses conte | ents of FSR t   | o address da    | ta memory (   | not a physic | al register) | xxxx xxxx                               | 30                 |

| 01h     | TMR0    | Timer0 M   | odule's Regi                     | ster          |                 |                 |               |              |              | xxxx xxxx                               | 47                 |

| 02h     | PCL     | Program    | Counter's (P                     | C) Least Sig  | nificant Byte   |                 |               |              |              | 0000 0000                               | 30                 |

| 03h     | STATUS  | IRP        | RP1                              | RP0           | TO              | PD              | Z             | DC           | С            | 0001 1xxx                               | 24                 |

| 04h     | FSR     | Indirect D | ata Memory                       | Address Poi   | nter            | •               |               |              | •            | xxxx xxxx                               | 30                 |

| 05h     | PORTA   | RA7        | A7 RA6 RA5 RA4 RA3 RA2 RA1 RA0 3 |               |                 |                 |               |              | xxxx 0000    | 33                                      |                    |

| 06h     | PORTB   | RB7        | RB6                              | RB5           | RB4             | RB3             | RB2           | RB1          | RB0          | xxxx xxxx                               | 38                 |

| 07h     | _       | Unimplen   | nented                           |               |                 |                 |               |              |              | _                                       | _                  |

| 08h     | _       | Unimplen   | nented                           |               |                 |                 |               |              |              | _                                       | _                  |

| 09h     | _       | Unimplen   | nented                           |               |                 |                 |               |              |              | _                                       | _                  |

| 0Ah     | PCLATH  | _          | ı                                | _             | Write Buffer    | for upper 5 l   | bits of Progr | am Counter   |              | 0 0000                                  | 30                 |

| 0Bh     | INTCON  | GIE        | PEIE                             | T0IE          | INTE            | RBIE            | TOIF          | INTF         | RBIF         | 0000 000x                               | 26                 |

| 0Ch     | PIR1    | EEIF       | CMIF                             | RCIF          | TXIF            | _               | CCP1IF        | TMR2IF       | TMR1IF       | 0000 -000                               | 28                 |

| 0Dh     | _       | Unimplen   | nented                           |               |                 |                 |               |              |              | _                                       | _                  |

| 0Eh     | TMR1L   | Holding F  | Register for th                  | ne Least Sigr | nificant Byte o | of the 16-bit T | MR1 Regist    | er           |              | xxxx xxxx                               | 50                 |

| 0Fh     | TMR1H   | Holding F  | Register for th                  | ne Most Sign  | ificant Byte o  | f the 16-bit T  | MR1 Registe   | er           |              | xxxx xxxx                               | 50                 |

| 10h     | T1CON   | _          | _                                | T1CKPS1       | T1CKPS0         | T10SCEN         | T1SYNC        | TMR1CS       | TMR10N       | 00 0000                                 | 50                 |

| 11h     | TMR2    | TMR2 Mo    | odule's Regis                    | ter           |                 |                 |               |              |              | 0000 0000                               | 54                 |

| 12h     | T2CON   | _          | TOUTPS3                          | TOUTPS2       | TOUTPS1         | TOUTPS0         | TMR2ON        | T2CKPS1      | T2CKPS0      | -000 0000                               | 54                 |

| 13h     | _       | Unimplen   | nented                           |               |                 |                 |               |              |              | _                                       | _                  |

| 14h     | _       | Unimplen   | nented                           |               |                 |                 |               |              |              | _                                       | _                  |

| 15h     | CCPR1L  | Capture/0  | Compare/PW                       | 'M Register ( | LSB)            |                 |               |              |              | xxxx xxxx                               | 57                 |

| 16h     | CCPR1H  | Capture/0  | Compare/PW                       | 'M Register ( | MSB)            |                 |               |              |              | xxxx xxxx                               | 57                 |

| 17h     | CCP1CON | _          | -                                | CCP1X         | CCP1Y           | CCP1M3          | CCP1M2        | CCP1M1       | CCP1M0       | 00 0000                                 | 57                 |

| 18h     | RCSTA   | SPEN       | RX9                              | SREN          | CREN            | ADEN            | FERR          | OERR         | RX9D         | 0000 000x                               | 74                 |

| 19h     | TXREG   | USART T    | ransmit Data                     | Register      |                 |                 |               |              |              | 0000 0000                               | 79                 |

| 1Ah     | RCREG   | USART F    | Receive Data                     | Register      |                 |                 |               |              |              | 0000 0000                               | 82                 |

| 1Bh     | _       | Unimplen   | nented                           |               |                 |                 |               |              |              | _                                       | _                  |

| 1Ch     | _       | Unimplen   | nented                           |               |                 |                 |               |              |              | _                                       | _                  |

| 1Dh     | _       | Unimplen   | nented                           |               |                 |                 |               |              |              | _                                       | _                  |

| 1Eh     | _       | Unimplen   | nented                           |               |                 |                 |               |              |              | _                                       | _                  |

| 1Fh     | CMCON   | C2OUT      | C1OUT                            | C2INV         | C1INV           | CIS             | CM2           | CM1          | CM0          | 0000 0000                               | 63                 |

**Legend:** - = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented **Note** 1: For the initialization condition for registers tables, refer to Table 14-6 and Table 14-7.

TABLE 4-4: SPECIAL FUNCTION REGISTERS SUMMARY BANK1

| Address | Name   | Bit 7                | Bit 6                                         | Bit 5         | Bit 4         | Bit 3        | Bit 2         | Bit 1         | Bit 0  | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|--------|----------------------|-----------------------------------------------|---------------|---------------|--------------|---------------|---------------|--------|-----------------------------------------|--------------------|

| Bank 1  |        |                      |                                               |               |               |              |               |               |        |                                         |                    |

| 80h     | INDF   | Addressing register) | this location                                 | uses conter   | nts of FSR to | address da   | ata memory    | (not a physic | al     | xxxx xxxx                               | 30                 |

| 81h     | OPTION | RBPU                 | INTEDG                                        | T0CS          | T0SE          | PSA          | PS2           | PS1           | PS0    | 1111 1111                               | 25                 |

| 82h     | PCL    | Program C            | Program Counter's (PC) Least Significant Byte |               |               |              |               |               |        |                                         |                    |

| 83h     | STATUS | IRP                  | IRP RP1 RP0 TO PD Z DC C                      |               |               |              |               |               |        |                                         | 24                 |

| 84h     | FSR    | Indirect Da          | Indirect Data Memory Address Pointer          |               |               |              |               |               |        |                                         | 30                 |

| 85h     | TRISA  | TRISA7               | TRISA6                                        | TRISA5        | TRISA4        | TRISA3       | TRISA2        | TRISA1        | TRISA0 | 1111 1111                               | 33                 |

| 86h     | TRISB  | TRISB7               | TRISB6                                        | TRISB5        | TRISB4        | TRISB3       | TRISB2        | TRISB1        | TRISB0 | 1111 1111                               | 38                 |

| 87h     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 88h     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 89h     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 8Ah     | PCLATH | _                    | ı                                             | 1             | Write Buffe   | er for upper | 5 bits of Pro | gram Counte   | er     | 0 0000                                  | 30                 |

| 8Bh     | INTCON | GIE                  | PEIE                                          | T0IE          | INTE          | RBIE         | T0IF          | INTF          | RBIF   | 0000 000x                               | 26                 |

| 8Ch     | PIE1   | EEIE                 | CMIE                                          | RCIE          | TXIE          | _            | CCP1IE        | TMR2IE        | TMR1IE | 0000 -000                               | 27                 |

| 8Dh     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 8Eh     | PCON   | _                    | -                                             | -             | _             | OSCF         | _             | POR           | BOR    | 1-0x                                    | 29                 |

| 8Fh     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 90h     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 91h     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 92h     | PR2    | Timer2 Per           | riod Register                                 |               |               |              |               |               |        | 1111 1111                               | 54                 |

| 93h     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 94h     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 95h     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 96h     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 97h     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 98h     | TXSTA  | CSRC                 | TX9                                           | TXEN          | SYNC          | _            | BRGH          | TRMT          | TX9D   | 0000 -010                               | 73                 |

| 99h     | SPBRG  | Baud Rate            | Generator Re                                  | egister       |               |              |               |               |        | 0000 0000                               | 75                 |

| 9Ah     | EEDATA | EEPROM               | Data Register                                 |               |               |              |               |               |        | xxxx xxxx                               | 91                 |

| 9Bh     | EEADR  | EEPROM A             | Address Regis                                 | ster          |               |              |               |               |        | xxxx xxxx                               | 92                 |

| 9Ch     | EECON1 | _                    | _                                             | _             | _             | WRERR        | WREN          | WR            | RD     | x000                                    | 92                 |

| 9Dh     | EECON2 | EEPROM (             | Control Regist                                | er 2 (not a p | ohysical reg  | ister)       |               |               |        |                                         | 92                 |

| 9Eh     | _      | Unimpleme            | ented                                         |               |               |              |               |               |        | _                                       | _                  |

| 9Fh     | VRCON  | VREN                 | VROE                                          | VRR           | _             | VR3          | VR2           | VR1           | VR0    | 000- 0000                               | 69                 |

Legend: - = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: For the initialization condition for registers tables, refer to Table 14-6 and Table 14-7.

TABLE 4-5: SPECIAL FUNCTION REGISTERS SUMMARY BANK2

| Address | Name   | Bit 7                    | Bit 6          | Bit 5       | Bit 4        | Bit 3        | Bit 2         | Bit 1        | Bit 0         | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|--------|--------------------------|----------------|-------------|--------------|--------------|---------------|--------------|---------------|-----------------------------------------|--------------------|

| Bank 2  |        |                          |                |             |              |              |               |              |               |                                         |                    |

| 100h    | INDF   | Addressing               | this location  | uses conter | nts of FSR t | o address d  | ata memory    | (not a physi | cal register) | xxxx xxxx                               | 30                 |

| 101h    | TMR0   | Timer0 Mo                | dule's Registe | er          |              |              |               |              |               | xxxx xxxx                               | 47                 |

| 102h    | PCL    | Program C                | counter's (PC) | Least Signi | ificant Byte |              |               |              |               | 0000 0000                               | 30                 |

| 103h    | STATUS | IRP RP1 RP0 TO PD Z DC C |                |             |              |              |               |              |               | 0001 1xxx                               | 24                 |

| 104h    | FSR    | Indirect Da              | ita Memory A   | dress Point | ter          | I            | l             | ı            | I             | xxxx xxxx                               | 30                 |

| 105h    | _      | Unimpleme                | Unimplemented  |             |              |              |               |              |               | _                                       | _                  |

| 106h    | PORTB  | RB7                      | RB6            | RB5         | RB4          | RB3          | RB2           | RB1          | RB0           | xxxx xxxx                               | 38                 |

| 107h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 108h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 109h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       |                    |

| 10Ah    | PCLATH | _                        | _              | _           | Write        | Buffer for u | pper 5 bits o | f Program C  | ounter        | 0 0000                                  | 30                 |

| 10Bh    | INTCON | GIE                      | PEIE           | T0IE        | INTE         | RBIE         | TOIF          | INTF         | RBIF          | 0000 000x                               | 26                 |

| 10Ch    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 10Dh    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 10Eh    | _      | Unimpleme                | Unimplemented  |             |              |              |               |              |               |                                         | _                  |

| 10Fh    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 110h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 111h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 112h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 113h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 114h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 115h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 116h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 117h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | -                  |

| 118h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 119h    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 11Ah    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 11Bh    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 11Ch    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 11Dh    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 11Eh    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

| 11Fh    | _      | Unimpleme                | ented          |             |              |              |               |              |               | _                                       | _                  |

**Legend:** -= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented.

Note 1: For the initialization condition for registers tables, refer to Table 14-6 and Table 14-7.

TABLE 4-6: SPECIAL FUNCTION REGISTERS SUMMARY BANK3

| Address | Name   | Bit 7       | Bit 6           | Bit 5      | Bit 4         | Bit 3        | Bit 2         | Bit 1         | Bit 0         | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|--------|-------------|-----------------|------------|---------------|--------------|---------------|---------------|---------------|-----------------------------------------|--------------------|

| Bank 3  |        |             |                 |            |               |              |               |               |               |                                         |                    |

| 180h    | INDF   | Addressing  | g this location | uses conte | nts of FSR to | o address d  | ata memory    | (not a physic | cal register) | xxxx xxxx                               | 30                 |

| 181h    | OPTION | RBPU        | INTEDG          | T0CS       | T0SE          | PSA          | PS2           | PS1           | PS0           | 1111 1111                               | 25                 |

| 182h    | PCL    | Program C   | counter's (PC)  | Least Sign | ificant Byte  |              |               |               |               | 0000 0000                               | 30                 |

| 183h    | STATUS | IRP         | RP1             | RP0        | TO            | PD           | Z             | DC            | С             | 0001 1xxx                               | 24                 |

| 184h    | FSR    | Indirect Da | ita Memory Ad   | dress Poin | ter           |              |               |               |               | xxxx xxxx                               | 30                 |

| 185h    | _      | Unimpleme   | ented           |            |               |              |               |               |               | _                                       | _                  |

| 186h    | TRISB  | TRISB7      | TRISB6          | TRISB5     | TRISB4        | TRISB3       | TRISB2        | TRISB1        | TRISB0        | 1111 1111                               | 38                 |

| 187h    | _      | Unimpleme   | ented           |            |               |              |               |               |               | _                                       | _                  |

| 188h    | _      | Unimpleme   | ented           |            |               |              |               |               |               | _                                       | _                  |

| 189h    | _      | Unimpleme   | ented           |            |               |              |               |               |               | _                                       | _                  |

| 18Ah    | PCLATH | _           | _               | _          | Write Buffe   | er for upper | 5 bits of Pro | gram Counte   | er            | 0 0000                                  | 30                 |

| 18Bh    | INTCON | GIE         | PEIE            | T0IE       | INTE          | RBIE         | T0IF          | INTF          | RBIF          | 0000 000x                               | 26                 |

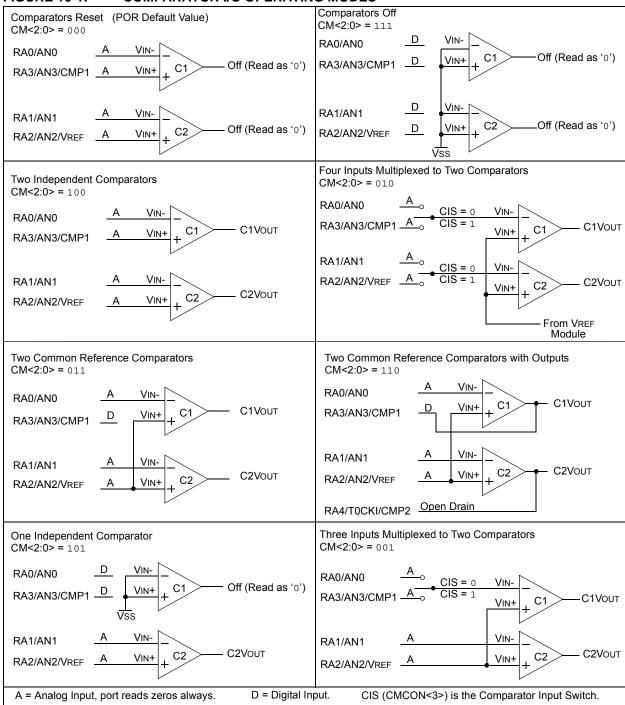

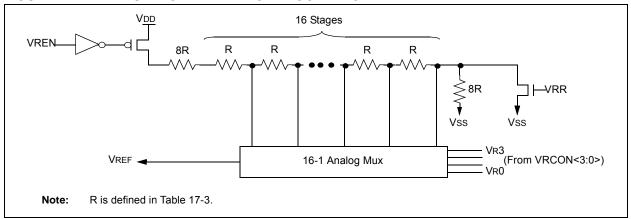

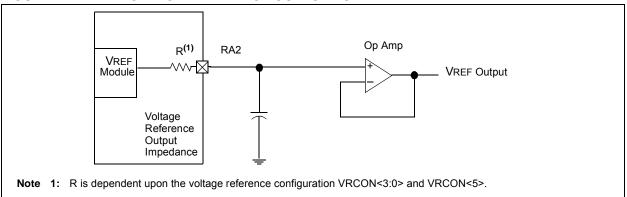

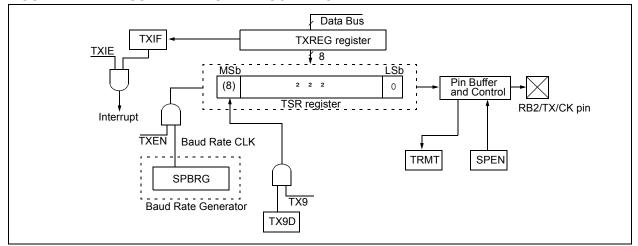

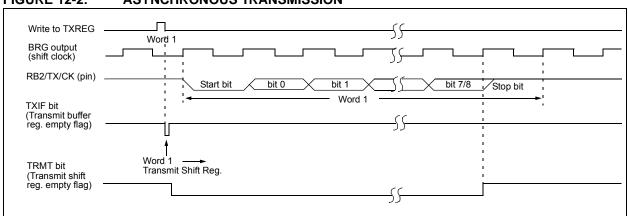

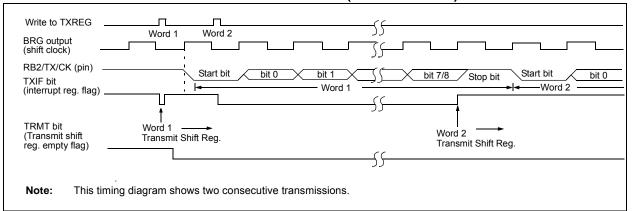

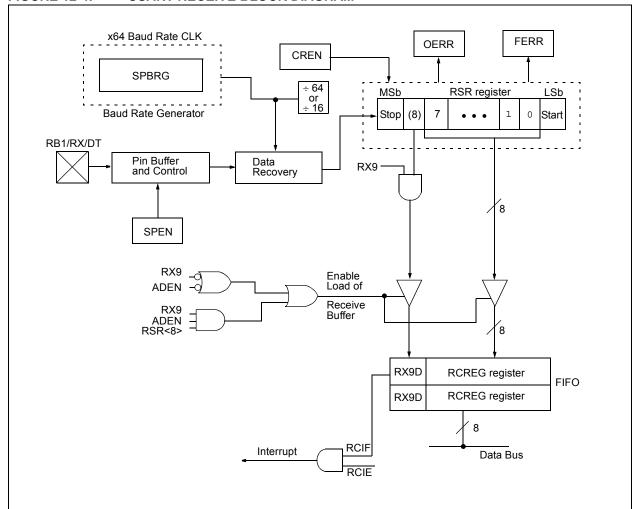

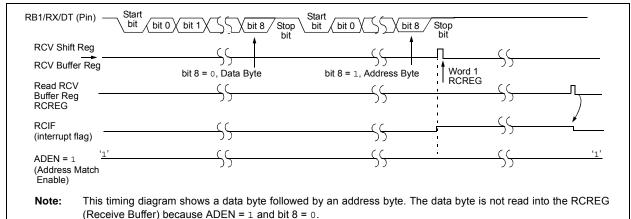

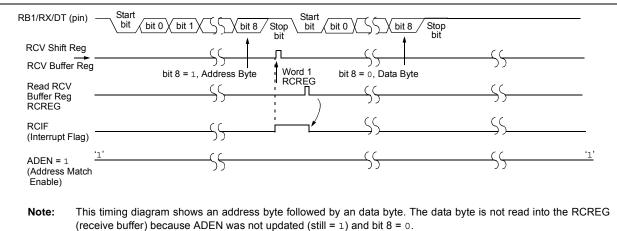

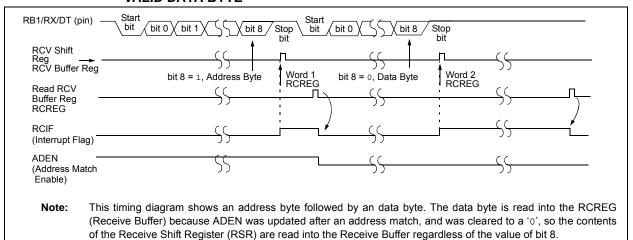

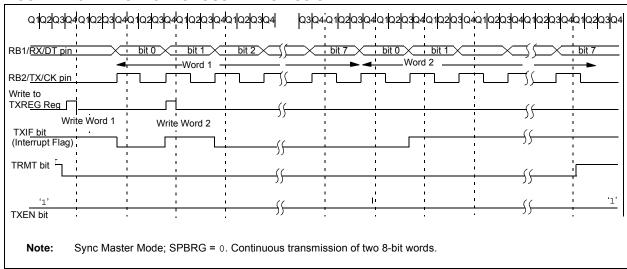

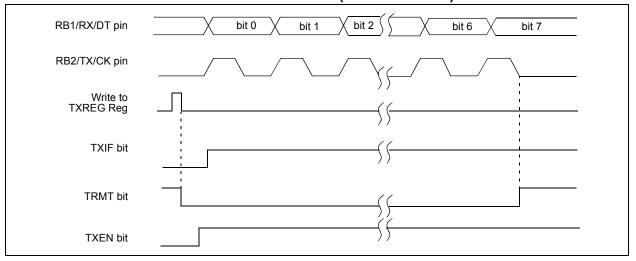

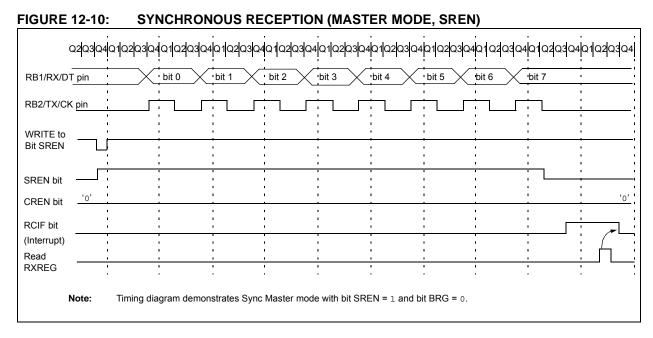

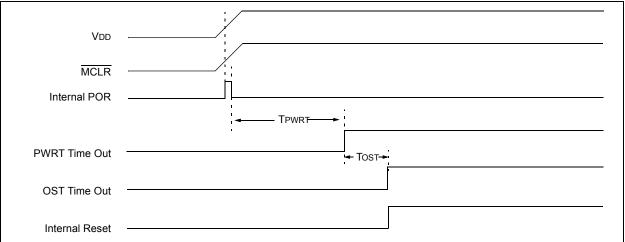

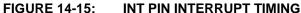

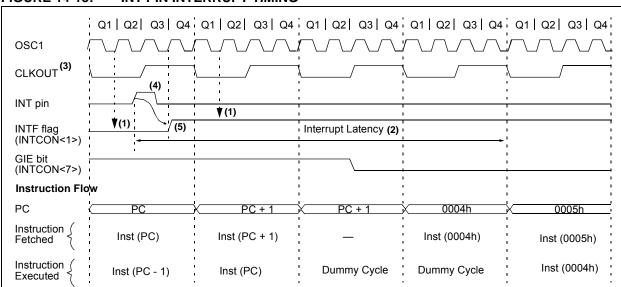

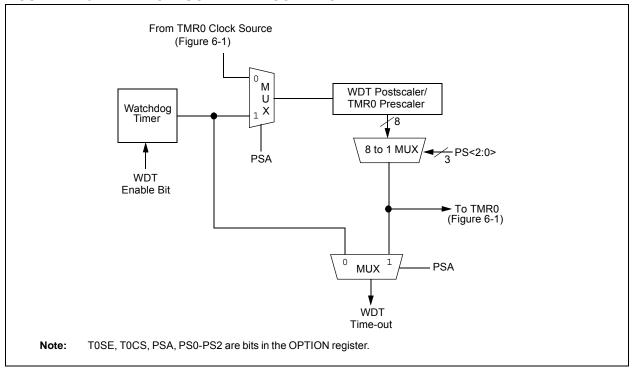

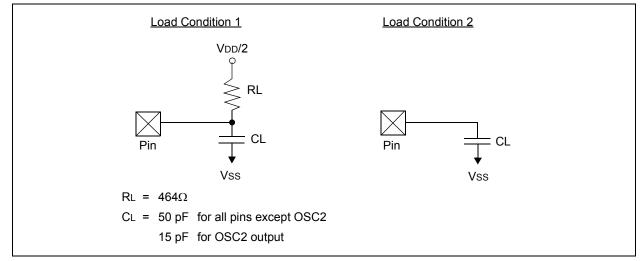

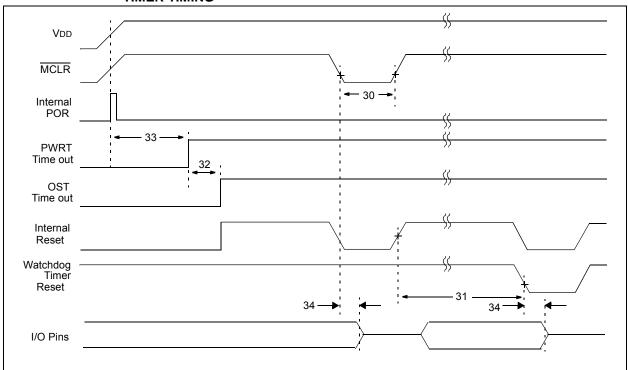

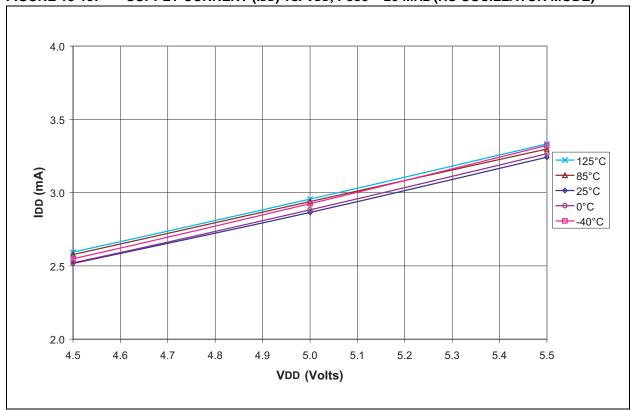

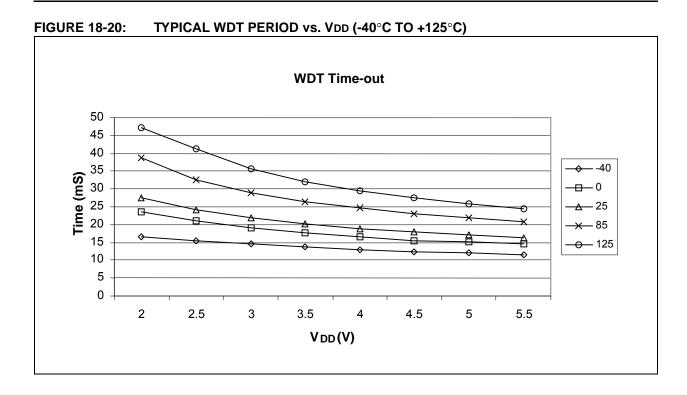

| 18Ch    | _      | Unimpleme   | ented           |            |               |              |               |               |               | _                                       | _                  |