# Dual 18A or Single 36A µModule Regulator with Digital Power System Management

## DESCRIPTION

The LTM®4677 is a dual 18A or single 36A step-down µModule® (power module) DC/DC regulator with 40ms turn-on time. It features remote configurability and telemetry-monitoring of power management parameters over PMBus— an open standard I<sup>2</sup>C-based digital interface protocol. The LTM4677 is comprised of fast analog control loops, precision mixed-signal circuitry, EEPROM, power MOSFETs, inductors and supporting components.

The LTM4677's 2-wire serial interface allows outputs to be margined, tuned and ramped up and down at programmable slew rates with sequencing delay times. Input and output currents and voltages, output power, temperatures, uptime and peak values are readable. Custom configuration of the EEPROM contents is not required. At start-up, output voltages, switching frequency, and channel phase angle assignments can be set by pin-strapping resistors. The LTpowerPlay™ GUI and DC1613 USB-to-PMBus converter and demo kits are available.

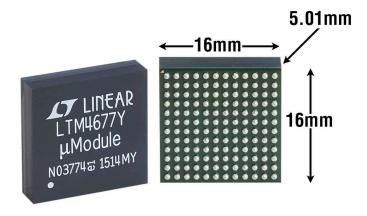

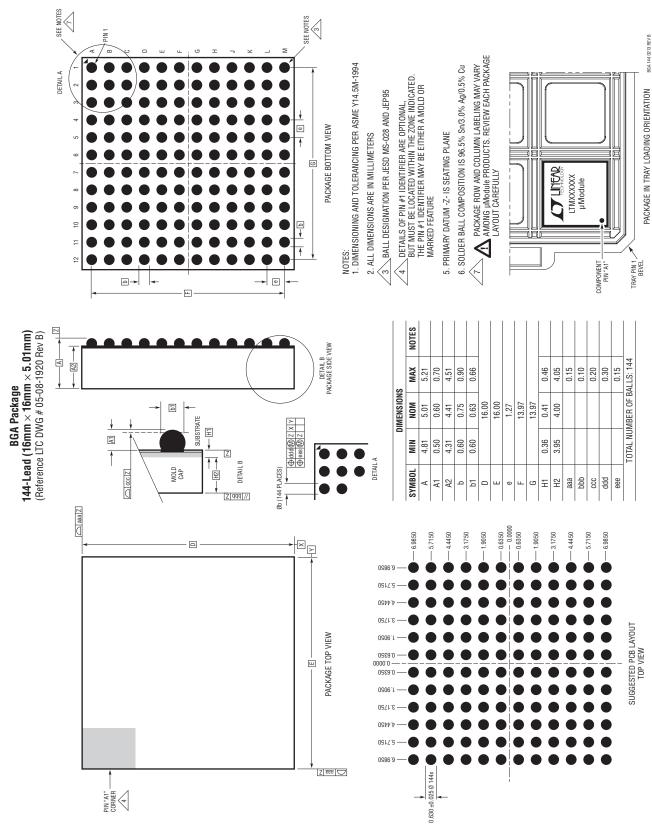

The LTM4677 is pin compatible with the LTM4676A (dual 13A) and is offered in a  $16 \text{mm} \times 16 \text{mm} \times 5.01 \text{mm}$  BGA package available with SnPb or RoHS compliant terminal finish.

**Δ7**, LT, LTC, LTM, Linear Technology, the Linear logo, μModule, Burst Mode and PolyPhase are registered trademarks and LTpowerPlay is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5408150, 5481178, 5705919, 5929620, 6144194, 6177787, 6580258, 7420359, 8163643. Licensed under U.S. Patent 7000125 and other related patents worldwide.

#### **FEATURES**

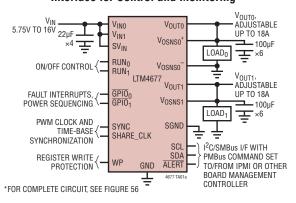

- Dual, Fast, Analog Loops with Digital Interface for Control and Monitoring

- Wide Input Voltage Range: 4.5V to 16V

- Output Voltage Range: 0.5V to 1.8V

- ±0.5% Maximum DC Output Error Over Temperature

- ±2.5% Current Readback Accuracy

- Pin Compatible with LTM4676A (Dual 13A, Single 26A)

- 400kHz PMBus-Compliant I<sup>2</sup>C Serial Interface

- Supports Telemetry Polling Rates up to 125Hz

- Integrated 16-Bit  $\Delta\Sigma$  ADC

- Constant Frequency Current Mode Control

- Parallel and Current Share Multiple Modules

- 16mm × 16mm × 5.01mm BGA Package

#### Readable Data:

- Input and Output Voltages, Currents, and Temperatures

- Running Peak Values, Uptime, Faults and Warnings

- Onboard EEPROM Fault Log Record with ECC

#### Writable Data and Configurable Parameters:

- Output Voltage, Voltage Sequencing and Margining

- Digital Soft-Start/Stop Ramp

- OV/UV/OT, UVLO, Frequency and Phasing

## **APPLICATIONS**

- System Optimization, Characterization and Data Mining in Prototype, Production and Field Environments

- Telecom, Datacom, and Storage Systems

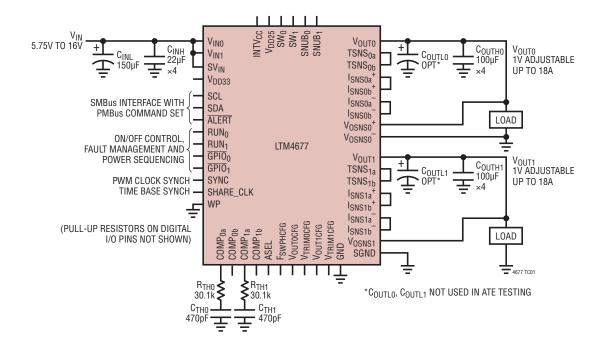

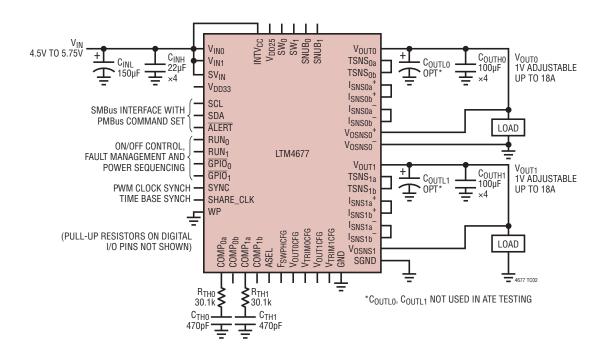

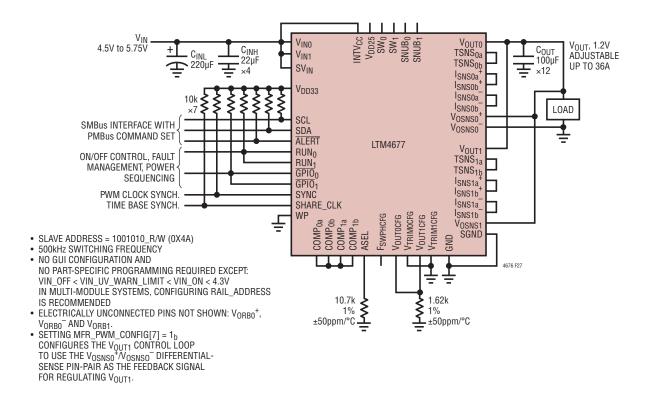

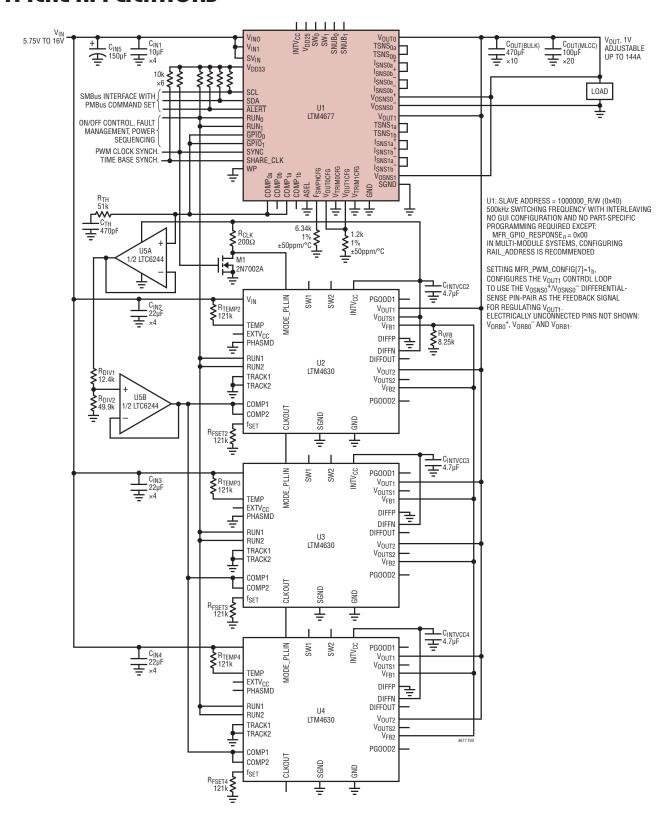

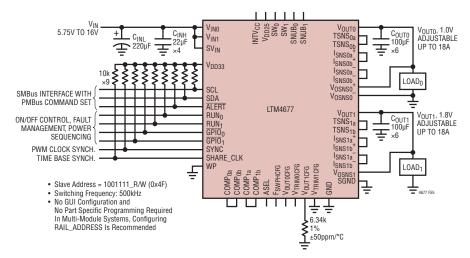

## TYPICAL APPLICATION

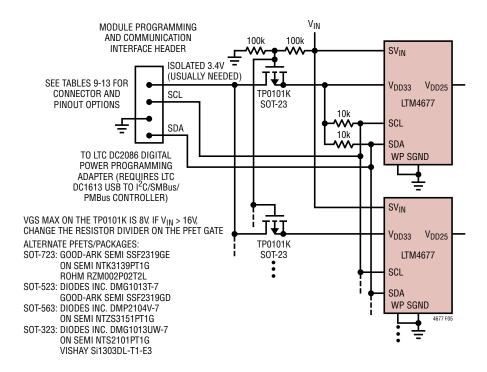

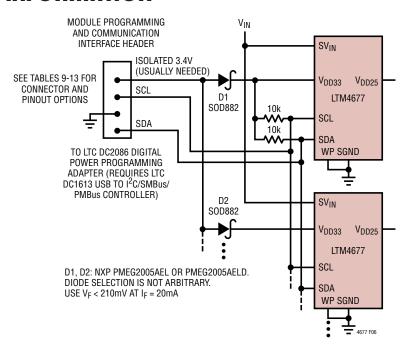

Dual 18A µModule Regulator with Digital Interface for Control and Monitoring\*

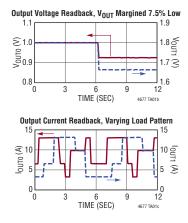

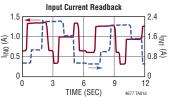

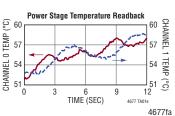

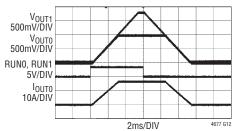

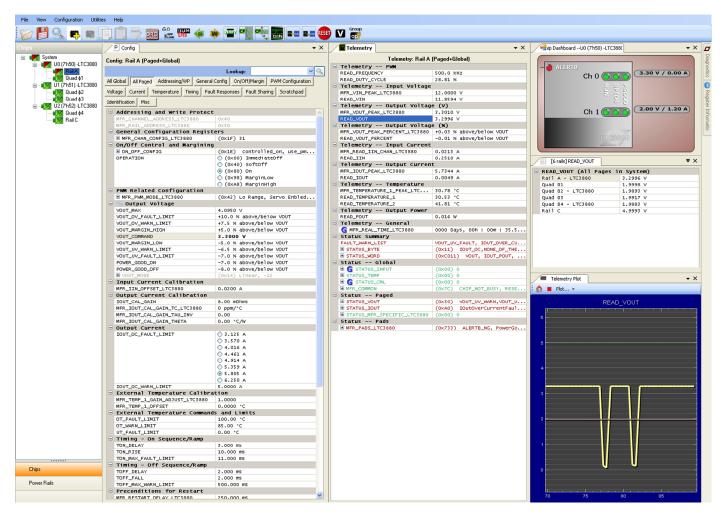

Using PMBus and LTpowerPlay to Monitor Telemetry and Margin  $V_{OUTO}/V_{OUT1}$  During Load Pattern Tests. 10Hz Polling Rate. 12 $V_{IN}$

1

# LTM4677

# TABLE OF CONTENTS

| Features                                                  | 1  |

|-----------------------------------------------------------|----|

| Applications                                              | 1  |

| Typical Application                                       | 1  |

| Description                                               |    |

| Absolute Maximum Ratings                                  | 4  |

| Order Information                                         |    |

| Pin Configuration                                         |    |

| Electrical Characteristics                                |    |

| Typical Performance Characteristics                       |    |

| Pin Functions                                             |    |

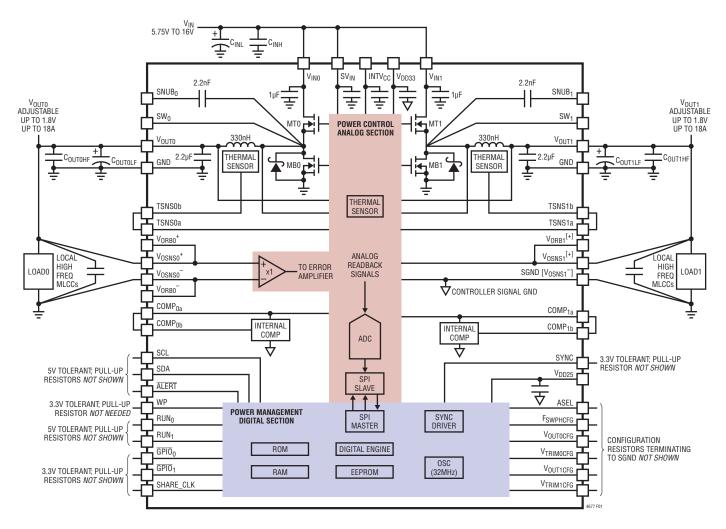

| Simplified Block Diagram                                  |    |

| Decoupling Requirements                                   |    |

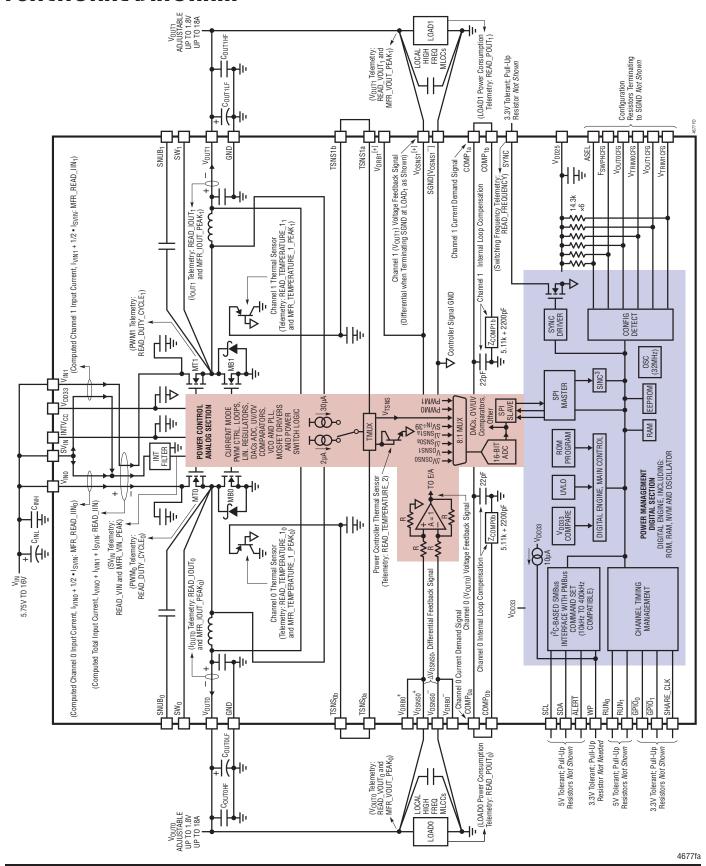

| Functional Diagram                                        |    |

| Test Circuits                                             |    |

| Operation                                                 |    |

| Power Module Introduction                                 |    |

| Power Module Configurability and                          |    |

| Readback Data                                             | 25 |

| Time-Averaged and Peak Readback Data                      | 28 |

| Power Module Overview                                     |    |

| EEPROM                                                    |    |

| Serial Interface                                          |    |

| Device Addressing                                         | 36 |

| Fault Detection and Handling                              |    |

| Responses to V <sub>OUT</sub> and I <sub>OUT</sub> Faults |    |

| Responses to Timing Faults                                | 39 |

| Responses to SV <sub>IN</sub> OV Faults                   |    |

| Responses to OT/UT Faults                                 |    |

| Responses to External Faults                              |    |

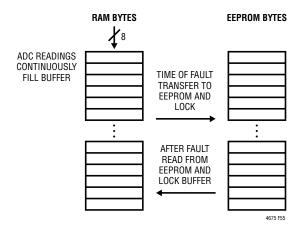

| Fault Logging                                             |    |

| Bus Timeout Protection                                    |    |

| PMBus Command Summary                                  |    |

|--------------------------------------------------------|----|

| PMBus Commands                                         | 41 |

| Applications Information                               | 48 |

| V <sub>IN</sub> to V <sub>OUT</sub> Step-Down Ratios   | 50 |

| Input Capacitors                                       | 51 |

| Output Capacitors                                      | 51 |

| Light Load Current Operation                           | 51 |

| Switching Frequency and Phase                          | 52 |

| Minimum On-Time Considerations                         | 53 |

| Variable Delay Time, Soft-Start and Output Voltage     |    |

| Ramping                                                |    |

| Digital Servo Mode                                     | 55 |

| Soft Off (Sequenced Off)                               |    |

| Undervoltage Lockout                                   | 56 |

| Fault DETECTION AND HANDLING                           |    |

| Open-Drain Pins                                        |    |

| Phase-Locked Loop and Frequency Synchronization        | n  |

| 58                                                     |    |

| RCONFIG Pin-Straps (External Resistor                  |    |

| Configuration Pins)                                    |    |

| Voltage Selection                                      | 59 |

| Connecting the USB to the I <sup>2</sup> C/SMBus/PMBus |    |

| Controller to the LTM4677 In System                    |    |

| PMBus Communication and Command Processing             | 63 |

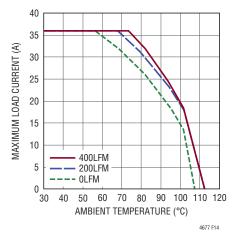

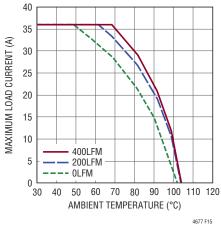

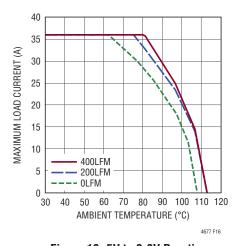

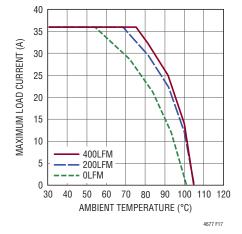

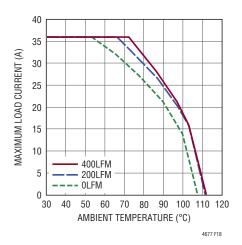

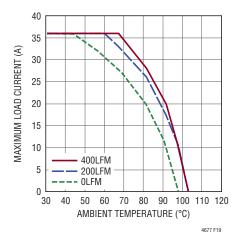

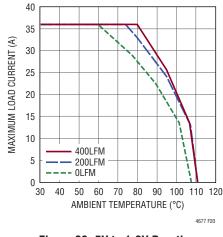

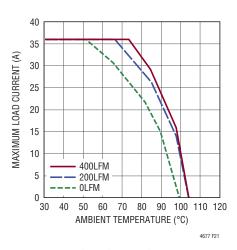

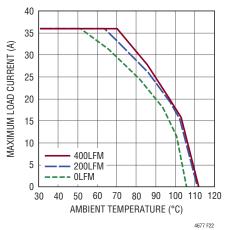

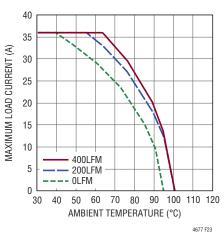

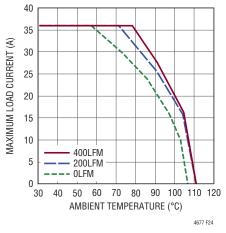

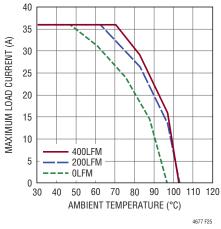

| Thermal Considerations and                             |    |

| Output Current Derating                                |    |

| Applications Information-Derating Curves               |    |

| EMI Performance                                        |    |

| Safety Considerations                                  |    |

| Layout Checklist/Example                               |    |

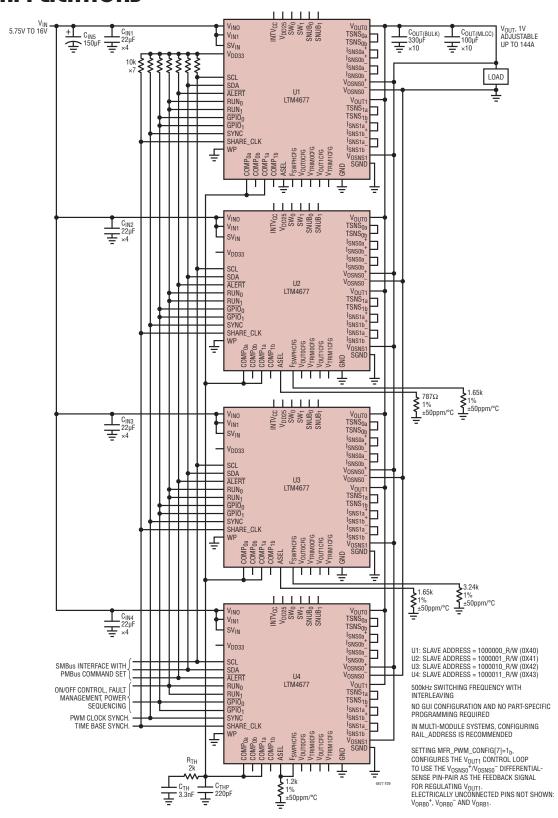

| Typical Applications                                   | 73 |

# TABLE OF CONTENTS

| Appendix A                                           | 77 |

|------------------------------------------------------|----|

| Similarity Between PMBus, SMBus and I <sup>2</sup> C |    |

| 2-Wire Interface                                     | 77 |

| Appendix B                                           | 78 |

| PMBus Serial Digital Interface                       | 78 |

| Appendix C: PMBus Command Details                    | 82 |

| Addressing and Write Protect                         |    |

| General Configuration Registers                      | 84 |

| On/Off/Margin                                        | 85 |

| PWM Config                                           | 87 |

| Voltage                                              | 89 |

| Current                                              | 92 |

| Temperature                                          |    |

| Timing                                               | 97 |

| Fault Response               | 99  |

|------------------------------|-----|

| Fault Sharing                |     |

| Scratchpad                   | 108 |

| Identification               | 108 |

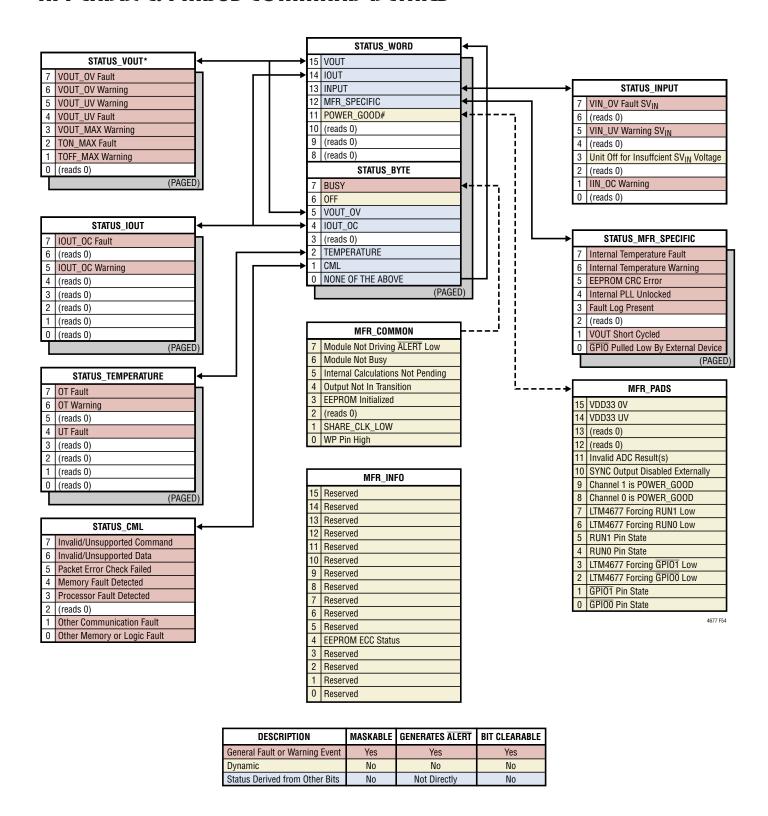

| Fault Warning and Status     | 110 |

| Telemetry                    | 116 |

| NVM (EEPROM) Memory Commands | 121 |

| Package Description          | 128 |

| Package Photograph           | 129 |

| Revision History             | 131 |

| Typical Application          | 132 |

| Design Resources             |     |

| Related Parts                | 132 |

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

#### **Terminal Voltages:**

| V <sub>INn</sub> (Note 4), SV <sub>IN</sub>                              | 0.3V to 18V      |

|--------------------------------------------------------------------------|------------------|

| V <sub>OUT</sub> <i>n</i>                                                |                  |

| V <sub>OSNS0</sub> <sup>+</sup> , V <sub>ORB0</sub> <sup>+</sup>         | 0.3V to 6V       |

| V <sub>OSNS1</sub> , V <sub>ORB1</sub> , INTV <sub>CC</sub>              | 0.3V to 6V       |

| RUN <sub>n</sub> , SDA, SCL, ALERT                                       | 0.3V to 5.5V     |

| F <sub>SWPHCFG</sub> , V <sub>OUTnCFG</sub> , V <sub>TRIMnCFG</sub> , AS | EL0.3V to 2.75V  |

| $V_{DD33}$ , $\overline{GPIO}_n$ , SYNC, SHARE_CLK, V                    | $NP, TSNS_{na},$ |

| $COMP_{na}$ , $COMP_{nb}$ , $V_{OSNS0}^-$ , $V_{ORB0}^-$                 | –0.3V to 3.6V    |

| SGND                                                                     | –0.3V to 0.3V    |

#### **Temperatures**

| internal Operating Temperature Ra | uige              |

|-----------------------------------|-------------------|

| (Note 2, 3)                       | 40°C to 125°C     |

| Storage Temperature Range         | 55°C to 125°C     |

| Peak Solder Reflow Package Body   | Temperature 245°C |

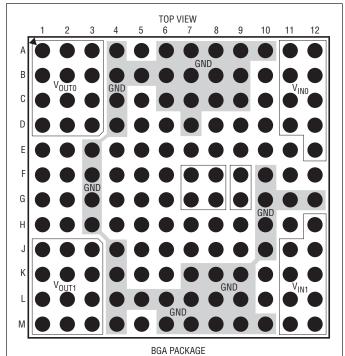

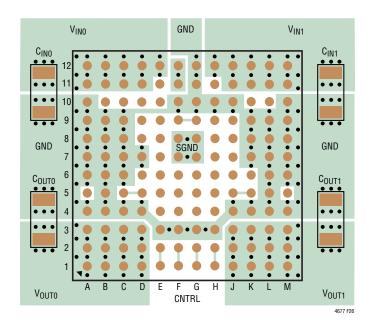

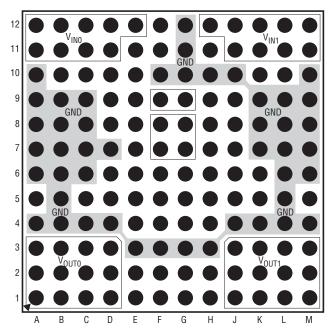

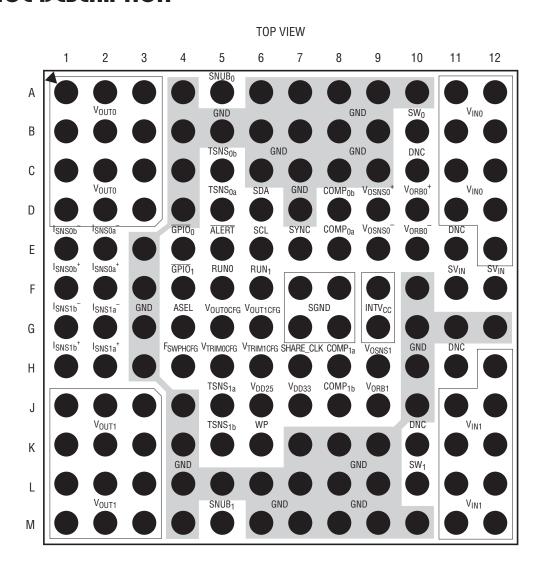

## PIN CONFIGURATION

144-LEAD (16mm × 16mm × 5.01mm)

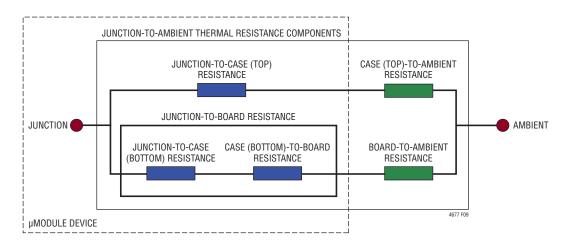

$$\begin{split} T_{JMAX} = 125\text{°C}, \ \theta_{JCtop} = 8.8\text{°C/W}, \ \theta_{JCbottom} = 0.8\text{°C/W}, \ \theta_{JB} = 1.3\text{°C/W}, \ \theta_{JA} = 8.3\text{°C/W} \\ \theta \ VALUES \ DETERMINED \ PER \ JESD51-12 \\ WEIGHT = 3.5 \ GRAMS \end{split}$$

# ORDER INFORMATION http://www.linear.com/product/LTM4677#orderinfo

| PART NUMBER   | PAD OR BALL FINISH | PART MAR | KING*       | PACKAGE | MSL    | TEMPERATURE RANGE |

|---------------|--------------------|----------|-------------|---------|--------|-------------------|

|               |                    | DEVICE   | FINISH CODE | TYPE    | RATING | (See Note 2)      |

| LTM4677EY#PBF | SAC305 (RoHS)      | LTM4677Y | e1          | BGA     | 4      | -40°C to 125°C    |

| LTM4677IY#PBF | SAC305 (RoHS)      | LTM4677Y | e1          | BGA     | 4      | -40°C to 125°C    |

| LTM4677IY     | SnPb (63/37)       | LTM4677Y | e0          | BGA     | 4      | -40°C to 125°C    |

Consult Marketing for parts specified with wider operating temperature ranges. \*Device temperature grade is indicated by a label on the shipping container. Pad or ball finish code is per IPC/JEDEC J-STD-609.

• Terminal Finish Part Marking: www.linear.com/leadfree

- Recommended LGA and BGA PCB Assembly and Manufacturing Procedures:

- www.linear.com/umodule/pcbassembly

- LGA and BGA Package and Tray Drawings: www.linear.com/packaging

| SYMBOL                                   | PARAMETER                                                   | CONDITIONS                                                                                                                                                                                                                                                                                                                                               |   | MIN            | TYP            | MAX            | UNITS             |

|------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|----------------|----------------|-------------------|

| V <sub>IN</sub>                          | Input DC Voltage                                            | Test Circuit 1<br>Test Circuit 2; VIN_OFF < VIN_ON = 4.25V                                                                                                                                                                                                                                                                                               | • | 5.75<br>4.5    |                | 16<br>5.75     | V<br>V            |

| $V_{OUT}$                                | Range of Output Voltage<br>Regulation                       | V <sub>OUTO</sub> Differentially Sensed on V <sub>OSNSO</sub> <sup>+</sup> /V <sub>OSNSO</sub> <sup>-</sup> Pin-Pair;<br>V <sub>OUT1</sub> Differentially Sensed on V <sub>OSNS1</sub> /SGND Pin-Pair;<br>Commanded by Serial Bus or with Resistors Present at Start-Up on<br>V <sub>OUT,DCFG</sub> and/or V <sub>TRIM,DCFG</sub>                        | • | 0.5<br>0.5     |                | 1.8<br>1.8     | V                 |

| V <sub>OUT</sub> n(DC)                   | Output Voltage, Total<br>Variation with Line and<br>Load    | Digital Servo Engaged (MFR_PWM_MODE $_n$ [6] = 1 $_b$ ) Digital Servo Disengaged (MFR_PWM_MODE $_n$ [6] = 0 $_b$ ) VOUT $_n$ Commanded to 1.000V, VOUT $_n$ Low Range (MFR_PWM_MODE $_n$ [1] = 1 $_b$ ) (Note 5)                                                                                                                                         | • | 0.995<br>0.985 | 1.000<br>1.000 | 1.005<br>1.015 | V                 |

| Input Specification                      | 1\$                                                         |                                                                                                                                                                                                                                                                                                                                                          |   |                |                |                |                   |

| I <sub>INRUSH(VIN)</sub>                 | Input Inrush Current at<br>Start-Up                         | Test Circuit 1, $V_{OUTn}$ = 1V, $V_{IN}$ = 12V; No Load Besides Capacitors; TON_RISE <sub>n</sub> = 3ms                                                                                                                                                                                                                                                 |   |                | 400            |                | mA                |

| I <sub>Q(SVIN)</sub>                     | Input Supply Bias Current                                   | Forced Continuous Mode, MFR_PWM_MODE <sub>n</sub> [0] = $1_b$<br>RUN <sub>n</sub> = 5V, RUN <sub>1-n</sub> = 0V<br>Shutdown, RUN <sub>0</sub> = RUN <sub>1</sub> = 0V                                                                                                                                                                                    |   |                | 40<br>20       |                | mA<br>mA          |

| I <sub>S(VIN<i>n</i>,PSM)</sub>          | Input Supply Current in<br>Pulse-Skipping Mode<br>Operation | Pulse-Skipping Mode, MFR_PWM_MODE <sub><math>n</math></sub> [0] = 0 <sub>b</sub> , $I_{OUTn}$ = 100mA                                                                                                                                                                                                                                                    |   |                | 20             |                | mA                |

| I <sub>S(VIN<i>n</i>,FCM)</sub>          | Input Supply Current in Forced-Continuous Mode Operation    | Forced Continuous Mode, MFR_PWM_MODE <sub>n</sub> [0] = $1_b$<br>$I_{OUTn}$ = 100mA<br>$I_{OUTn}$ = 18A                                                                                                                                                                                                                                                  |   |                | 35<br>1.9      |                | mA<br>A           |

| I <sub>S(VIN<i>n</i>,SHUTDOWN)</sub>     | Input Supply Current in Shutdown                            | Shutdown, $RUN_n = 0V$                                                                                                                                                                                                                                                                                                                                   |   |                | 50             |                | μА                |

| Output Specification                     | ons                                                         |                                                                                                                                                                                                                                                                                                                                                          |   |                |                |                |                   |

| I <sub>OUT</sub> n                       | Output Continuous<br>Current Range                          | (Note 6)                                                                                                                                                                                                                                                                                                                                                 |   | 0              |                | 18             | A                 |

| $\frac{\Delta V_{OUTn(LINE)}}{V_{OUTn}}$ | Line Regulation Accuracy                                    | Digital Servo Engaged (MFR_PWM_MODE $_n$ [6] = 1 $_b$ ) Digital Servo Disengaged (MFR_PWM_MODE $_n$ [6] = 0 $_b$ ) SV $_{IN}$ and V $_{INn}$ Electrically Shorted Together and INTV $_{CC}$ Open Circuit; $I_{OUTn}$ = 0A, 5.75V $\leq$ V $_{IN}$ $\leq$ 16V, V $_{OUT}$ Low Range (MFR_PWM_MODE $_n$ [1] = 1 $_b$ ), FREQUENCY_SWITCH = 350kHz (Note 5) | • |                | 0.03<br>0.03   | ±0.2           | %/V<br>%/V        |

| $\frac{\Delta V_{OUTn(LOAD)}}{V_{OUTn}}$ | Load Regulation<br>Accuracy                                 | Digital Servo Engaged (MFR_PWM_MODE $_n$ [6] = 1 $_b$ )<br>Digital Servo Disengaged (MFR_PWM_MODE $_n$ [6] = 0 $_b$ )<br>0A $\leq$ 1 $_{OUT}$ $_n$ $\leq$ 18A, V $_{OUT}$ Low Range, (MFR_PWM_MODE $_n$ [1] = 1 $_b$ )<br>(Note 5)                                                                                                                       | • |                | 0.03<br>0.2    | 0.5            | %<br>%            |

| V <sub>OUT</sub> n(AC)                   | Output Voltage Ripple                                       |                                                                                                                                                                                                                                                                                                                                                          |   |                | 10             |                | mV <sub>P-P</sub> |

| f <sub>S</sub> (Each Channel)            | V <sub>OUT</sub> Ripple Frequency                           | FREQUENCY_SWITCH Set to 500kHz (0xFBE8)                                                                                                                                                                                                                                                                                                                  | • | 462.5          | 500            | 537.5          | kHz               |

| $\Delta V_{OUTn(START)}$                 | Turn-On Overshoot                                           | $TON_RISE_n = 3ms$ (Note 12)                                                                                                                                                                                                                                                                                                                             |   |                | 8              |                | mV                |

| <sup>†</sup> START                       | Turn-On Start-Up Time                                       | Time from $V_{IN}$ Toggling from 0V to 12V to Rising Edge of $\overline{\text{GPIO}}_n$ .<br>TON_DELAY <sub>n</sub> = 0ms, TON_RISE <sub>n</sub> = 3ms,<br>MFR_GPIO_PROPAGATE <sub>n</sub> = 0x0100,<br>MFR_GPIO_RESPONSE <sub>n</sub> = 0x0000                                                                                                          | • |                | 35             | 40             | ms                |

| SYMBOL                            | PARAMETER                                                                | CONDITIONS                                                                                                                                                                                                                                                                             |             | MIN T      | ΥP        | MAX                                           | UNITS           |

|-----------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-----------|-----------------------------------------------|-----------------|

| t <sub>DELAY(0ms)</sub>           | Turn-On Delay Time                                                       | Time from First Rising Edge of $RUN_n$ to Rising Edge of $\overline{GPIO}_n$ . TON_DELAY <sub>n</sub> = 0ms, TON_RISE <sub>n</sub> = 3ms, MFR_GPIO_PROPAGATE <sub>n</sub> = 0x0100, MFR_GPIO_RESPONSE <sub>n</sub> = 0x0000. V <sub>IN</sub> Having Been Established for at Least 40ms | •           | 2.75 3     | 3.1       | 3.5                                           | ms              |

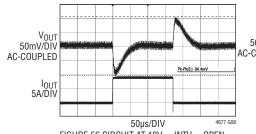

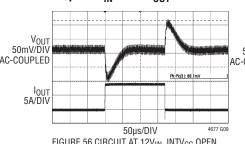

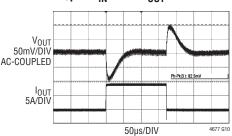

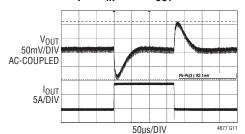

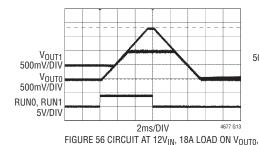

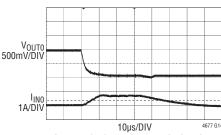

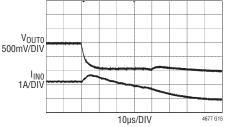

| $\Delta V_{OUTn(LS)}$             | Peak Output Voltage<br>Deviation for Dynamic<br>Load Step                | Load: 0A to 9A and 9A to 0A at 9A/ $\mu$ s, Figure 56 Circuit, $V_{OUTn} = 1V$ , $V_{IN} = 12V$ (Note 12)                                                                                                                                                                              |             | Ę          | 50        |                                               | mV              |

| tsettle                           | Settling Time for<br>Dynamic Load Step                                   | Load: 0A to 9A and 9A to 0A at 9A/µs, Figure 56 Circuit, $V_{OUTn} = 1V$ , $V_{IN} = 12V$ (Note 12)                                                                                                                                                                                    |             | 3          | 35        |                                               | μs              |

| I <sub>OUT</sub> n(OCL_PK)        | Output Current Limit,<br>Peak                                            | Cycle-by-Cycle Inductor Peak Current Limit Inception                                                                                                                                                                                                                                   |             | 2          | 25        |                                               | А               |

| I <sub>OUT</sub> n(OCL_AVG)       | Output Current Limit,<br>Time Averaged                                   | Time-Averaged Output Inductor Current Limit Inception Threshold, Commanded by IOUT_OC_FAULT_LIMIT_n (Note 12)                                                                                                                                                                          |             | Specificat | ion ((    | I <sub>O-RB-AC</sub> o<br>Output C<br>Accurac | urrent          |

| Control Section                   |                                                                          |                                                                                                                                                                                                                                                                                        |             |            |           |                                               |                 |

| V <sub>FBCM0</sub>                | Channel 0 Feedback Input<br>Common Mode Range                            | V <sub>OSNSO</sub> <sup>-</sup> Valid Input Range (Referred to SGND)<br>V <sub>OSNSO</sub> <sup>+</sup> Valid Input Range (Referred to SGND)                                                                                                                                           | •           | -0.1       |           | 0.3<br>2.1                                    | V               |

| V <sub>FBCM1</sub>                | Channel 1 Feedback Input<br>Common Mode Range                            | SGND Valid Input Range (Referred to GND)<br>V <sub>OSNS1</sub> Valid Input Range (Referred to SGND)                                                                                                                                                                                    | •           | -0.3       |           | 0.3<br>2.1                                    | V               |

| V <sub>OUT-RNG1</sub>             | Full-Scale Command<br>Voltage, Range 1                                   | (Notes 7, 15) $V_{OUTn}$ Commanded to 2.750V, MFR_PWM_MODE <sub>n</sub> [1] = 1 <sub>b</sub> Resolution LSB Step Size                                                                                                                                                                  |             |            | 12<br>875 | 2.788                                         | V<br>Bits<br>mV |

| R <sub>VSENSE0</sub> <sup>+</sup> | V <sub>OSNS0</sub> <sup>+</sup> Impedance to SGND                        | $0.05V \le V_{VOSNS0}^+ - V_{SGND} \le 1.8V$                                                                                                                                                                                                                                           |             | 2          | 11        |                                               | kΩ              |

| R <sub>VSENSE1</sub>              | V <sub>OSNS1</sub> Impedance to SGND                                     | $0.05V \le V_{VOSNS1} - V_{SGND} \le 1.8V$                                                                                                                                                                                                                                             |             | 3          | 37        |                                               | kΩ              |

| t <sub>ON(MIN)</sub>              | Minimum On-Time                                                          | (Note 8)                                                                                                                                                                                                                                                                               |             | 4          | 15        |                                               | ns              |

| Analog OV/UV (O                   | vervoltage/Undervoltage) Outp                                            | out Voltage Supervisor Comparators (VOUT_OV/UV_FAULT_LIMIT and V                                                                                                                                                                                                                       | <b>/</b> 0U | r_ov/uv_wa | RN_       | LIMIT M                                       | onitors)        |

| N <sub>OV/UV_COMP</sub>           | Resolution, Output<br>Voltage Supervisors                                | (Note 15)                                                                                                                                                                                                                                                                              |             |            | 8         |                                               | Bits            |

| V <sub>OV-RNG</sub>               | Output OV Comparator<br>Threshold Detection<br>Range                     | (Note 15)<br>High Range Scale, MFR_PWM_MODE <sub>n</sub> [1] = $0_b$<br>Low Range Scale, MFR_PWM_MODE <sub>n</sub> [1] = $1_b$                                                                                                                                                         |             | 1<br>0.5   |           | 5.6<br>2.7                                    | V               |

| V <sub>OU-STP</sub>               | Output OV and UV<br>Comparator Threshold<br>Programming LSB Step<br>Size | (Note 15)<br>High Range Scale, MFR_PWM_MODE <sub>n</sub> [1] = $0_b$<br>Low Range Scale, MFR_PWM_MODE <sub>n</sub> [1] = $1_b$                                                                                                                                                         |             |            | 22<br>I 1 |                                               | mV<br>mV        |

| SYMBOL                          | PARAMETER                                                                                           | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | MIN TYP                                                  | MAX                    | UNITS              |

|---------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------|------------------------|--------------------|

| V <sub>OV-ACC</sub>             | Output OV Comparator<br>Threshold Accuracy                                                          | $ \begin{array}{l} (\text{See Note 14}) \\ 1 \text{V} \leq \text{V}_{\text{VOSNS0}}^+ - \text{V}_{\text{VOSNS0}}^- \leq 1.8 \text{V}, \text{MFR}\_\text{PWM}\_\text{MODE}_0[1] = 1_b \\ 0.5 \text{V} \leq \text{V}_{\text{VOSNS0}}^+ - \text{V}_{\text{VOSNS0}}^- < 1 \text{V}, \text{MFR}\_\text{PWM}\_\text{MODE}_0[1] = 1_b \\ 1.5 \text{V} \leq \text{V}_{\text{VSENSE}1} - \text{V}_{\text{SGND}} \leq 1.8 \text{V}, \text{MFR}\_\text{PWM}\_\text{MODE}_1[1] = 1_b \\ 0.5 \text{V} \leq \text{V}_{\text{VSENSE}1} - \text{V}_{\text{SGND}} < 1.5 \text{V}, \text{MFR}\_\text{PWM}\_\text{MODE}_1[1] = 1_b \\ \end{array} $   | • • • |                                                          | ±2<br>±20<br>±2<br>±30 | %<br>mV<br>%<br>mV |

| V <sub>UV-RNG</sub>             | Output UV Comparator<br>Threshold Detection<br>Range                                                | (Note 15) High Range Scale, MFR_PWM_MODE <sub>n</sub> [1] = 0 <sub>b</sub> Low Range Scale, MFR_PWM_MODE <sub>n</sub> [1] = 1 <sub>b</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | 1<br>0.5                                                 | 5.4<br>2.7             | V                  |

| V <sub>UV-ACC</sub>             | Output UV Comparator<br>Threshold Accuracy                                                          | $ \begin{array}{l} (\text{See Note 14}) \\ 1 \text{V} \leq \text{V}_{\text{VSENSE0}}^+ - \text{V}_{\text{VSENSE0}}^- \leq 1.8 \text{V}, \text{MFR}\_\text{PWM}\_\text{MODE}_0[1] = 1_b \\ 0.5 \text{V} \leq \text{V}_{\text{VSENSE0}}^+ - \text{V}_{\text{VSENSE0}}^- < 1 \text{V}, \text{MFR}\_\text{PWM}\_\text{MODE}_0[1] = 1_b \\ 1.5 \text{V} \leq \text{V}_{\text{VOSNS1}} - \text{V}_{\text{SGND}} \leq 1.8 \text{V}, \text{MFR}\_\text{PWM}\_\text{MODE}_1[1] = 1_b \\ 0.5 \text{V} \leq \text{V}_{\text{VOSNS1}} - \text{V}_{\text{SGND}} < 1.5 \text{V}, \text{MFR}\_\text{PWM}\_\text{MODE}_1[1] = 1_b \\ \end{array} $ | • • • |                                                          | ±2<br>±20<br>±2<br>±30 | %<br>mV<br>%<br>mV |

| t <sub>PROP-OV</sub>            | Output OV Comparator<br>Response Times                                                              | Overdrive to 10% Above Programmed Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                                                          | 35                     | μs                 |

| t <sub>PROP-UV</sub>            | Output UV Comparator<br>Response Times                                                              | Underdrive to 10% Below Programmed Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |                                                          | 50                     | μs                 |

| Analog OV/UV SV <sub>IN</sub>   | Input Voltage Supervisor                                                                            | Comparators (Threshold Detectors for VIN_ON and VIN_OFF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                          |                        |                    |

| N <sub>SVIN-OV/UV-COMP</sub>    | SV <sub>IN</sub> OV/UV Comparator<br>Threshold-Programming<br>Resolution                            | (Note 15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 8                                                        |                        | Bits               |

| SV <sub>IN-OU-RANGE</sub>       | SV <sub>IN</sub> OV/UV Comparator<br>Threshold-Programming<br>Range                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •     | 4.5                                                      | 18                     | V                  |

| SV <sub>IN-OU-STP</sub>         | SV <sub>IN</sub> OV/UV Comparator<br>Threshold-Programming<br>LSB Step Size                         | (Note 15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 82                                                       |                        | mV                 |

| SV <sub>IN-OU-ACC</sub>         | SV <sub>IN</sub> OV/UV Comparator<br>Threshold Accuracy                                             | 9V < SV <sub>IN</sub> ≤ 16V<br>4.5V ≤ SV <sub>IN</sub> ≤ 9V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •     |                                                          | ±2.5<br>±225           | %<br>mV            |

| t <sub>PROP-SVIN-HIGH-VIN</sub> | SV <sub>IN</sub> OV/UV Comparator<br>Response Time, High V <sub>IN</sub><br>Operating Configuration | Test Circuit 1, and: VIN_ON = 9V; SV <sub>IN</sub> Driven from 8.775V to 9.225V VIN_OFF = 9V; SV <sub>IN</sub> Driven from 9.225V to 8.775V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •     |                                                          | 35<br>35               | μs<br>μs           |

| t <sub>PROP-SVIN-LOW-VIN</sub>  | SV <sub>IN</sub> OV/UV Comparator<br>Response Time, Low V <sub>IN</sub><br>Operating Configuration  | Test Circuit 2, and: VIN_ON = 4.5V; SV <sub>IN</sub> Driven from 4.225V to 4.725V VIN_OFF = 4.5V; SV <sub>IN</sub> Driven from 4.725V to 4.225V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • •   |                                                          | 35<br>35               | μs<br>μs           |

| Channels 0 and 1 (              | Output Voltage Readback (I                                                                          | READ_VOUT <sub>n</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                          |                        |                    |

| N <sub>VO-RB</sub>              | Output Voltage Readback<br>Resolution and LSB Step<br>Size                                          | (Note 15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 16<br>244                                                |                        | Bits<br>μV         |

| V <sub>0-F/S</sub>              | Output Voltage Full-Scale<br>Digitizable Range                                                      | $V_{RUNn} = 0V \text{ (Notes 7, 15)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 8                                                        |                        | V                  |

| V <sub>O-RB-ACC</sub>           | Output Voltage Readback<br>Accuracy                                                                 | Channel 0: $1V \le V_{VOSNS0}^+ - V_{VOSNS0}^- \le 1.8V$<br>Channel 0: $0.6V \le V_{VOSNS0}^+ - V_{VOSNS0}^- < 1V$<br>Channel 1: $1V \le V_{VOSNS1} - V_{SGND} \le 1.8V$<br>Channel 1: $0.6V \le V_{VOSNS1} - V_{SGND} < 1V$                                                                                                                                                                                                                                                                                                                                                                                                       | • • • | Within ±0.5'<br>Within ±5m<br>Within ±0.5'<br>Within ±5m | V of Read<br>% of Read | ling<br>ding       |

| t <sub>CONVERT-VO-RB</sub>      | Output Voltage Readback<br>Update Rate                                                              | MFR_ADC_CONTROL = 0×00 (Notes 9, 15) MFR_ADC_CONTROL = 0×00 (Notes 9, 15) MFR_ADC_CONTROL = 0×05 or 0×09 (Notes 9, 15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | 90<br>27<br>8                                            |                        | ms<br>ms<br>ms     |

| SYMBOL                                  | PARAMETER                                                                                   | CONDITIONS                                                                                                                                                                    |       | MIN TYP MAX                    | UNITS          |

|-----------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------|----------------|

| Input Voltage (SV                       | <sub>IN</sub> ) Readback (READ_VIN)                                                         |                                                                                                                                                                               |       |                                |                |

| N <sub>SVIN-RB</sub>                    | Input Voltage Readback<br>Resolution and LSB Step<br>Size                                   | (Notes 10, 15)                                                                                                                                                                |       | 10<br>15.625                   | Bits<br>mV     |

| SV <sub>IN-F/S</sub>                    | Input Voltage Full-Scale<br>Digitizable Range                                               | (Notes 11, 15)                                                                                                                                                                |       | 38.91                          | V              |

| SV <sub>IN-RB-ACC</sub>                 | Input Voltage Readback<br>Accuracy                                                          | READ_VIN, $4.5V \le SV_{IN} \le 16V$                                                                                                                                          | •     | Within ±2% of Rea              | ading          |

| t <sub>CONVERT-SVIN-RB</sub>            | Input Voltage Readback<br>Update Rate                                                       | MFR_ADC_CONTROL = 0×00 (Notes 9, 15)<br>MFR_ADC_CONTROL = 0×01 (Notes 9, 15)                                                                                                  |       | 90<br>8                        | ms<br>ms       |

| Channels 0 and 1 0                      | Output Current (READ_IOUT <sub>n</sub> )                                                    | , Duty Cycle (READ_DUTY_CYCLE $_{\it n}$ ), and Computed Input Current (M                                                                                                     | FR_RE | AD_IIN <sub>n</sub> ) Readback |                |

| N <sub>IO-RB</sub>                      | Output Current Readback<br>Resolution and LSB Step<br>Size                                  | (Notes 10, 12)                                                                                                                                                                |       | 10<br>15.6                     | Bits<br>mA     |

| I <sub>0-F/S</sub> , I <sub>I-F/S</sub> | Output Current Full-Scale<br>Digitizable Range and<br>Input Current Range of<br>Calculation | (Note 12)                                                                                                                                                                     |       | ±40                            | A              |

| I <sub>O-RB-ACC</sub>                   | Output Current, Readback<br>Accuracy                                                        | READ_IOUT <sub>n</sub> , Channels 0 and 1, $0 \le I_{OUTn} \le 10A$ ,<br>Forced-Continuous Mode, MFR_PWM_MODE <sub>n</sub> [1:0] = $10_b$                                     | •     | Within 250mA of R              | eading         |

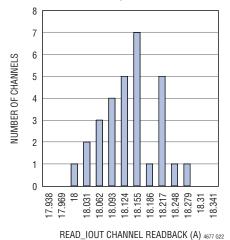

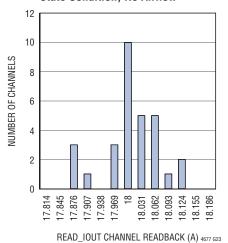

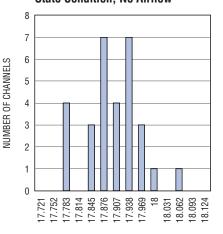

| I <sub>O-RB(18A)</sub>                  | Full Load Output Current<br>Readback                                                        | $I_{OUTn}$ = 18A (Note 12). See Histograms in Typical Performance Characteristics                                                                                             |       | 18                             | A              |

| N <sub>II-RB</sub>                      | Computed Input Current,<br>Readback Resolution and<br>LSB Step Size                         | (Notes 10, 12)                                                                                                                                                                |       | 10<br>1.95                     | Bits<br>mA     |

| I <sub>I-RB-ACC</sub>                   | Computed Input Current,<br>Readback Accuracy,<br>Neglecting I <sub>SVIN</sub>               | MFR_READ_IIN <sub>n</sub> , Channels 0 and 1, $0 \le I_{OUTn} \le 10A$ , Forced-Continuous Mode, MFR_PWM_MODE <sub>n</sub> [1:0] = $10_b$ , MFR_IIN_OFFSET <sub>n</sub> = 0mA | •     | Within 150mA of Re             | ading          |

| t <sub>CONVERT-IO-RB</sub>              | Output Current Readback<br>Update Rate                                                      | MFR_ADC_CONTROL = 0×00 (Notes 9, 15)<br>MFR_ADC_CONTROL = 0×00 (Notes 9, 15)<br>MFR_ADC_CONTROL = 0×05 or 0×09 (Notes 9, 15)                                                  |       | 90<br>27<br>8                  | ms<br>ms<br>ms |

| t <sub>CONVERT-II-RB</sub>              | Computed Input Current,<br>Readback Update Rate                                             | (Notes 9, 15)<br>MFR_ADC_CONTROL = 0×00                                                                                                                                       |       | 90                             | ms             |

| N <sub>DUTY-RB</sub>                    | Resolution, Duty Cycle<br>Readback                                                          | (Notes 10, 15)                                                                                                                                                                |       | 10                             | Bits           |

| D <sub>RB-ACC</sub>                     | Duty Cycle TUE                                                                              | READ_DUTY-CYCLE <sub>n</sub> , 16.3% Duty Cycle (Note 15)                                                                                                                     |       | ±3                             | %              |

| t <sub>CONVERT-DUTY-RB</sub>            | Duty Cycle Readback<br>Update Rate                                                          | (Notes 9, 15)<br>MFR_ADC_CONTROL = 0×00                                                                                                                                       |       | 90                             | ms             |

| Temperature Read                        |                                                                                             | el 1, and Controller (Respectively: READ_TEMPERATURE_1 <sub>0</sub> , REA                                                                                                     | D_TEM | PERATURE_1 <sub>1</sub> ,      |                |

| T <sub>RES-RB</sub>                     | Temperature Readback<br>Resolution                                                          | Channel 0, Channel 1, and Controller (Note 15)                                                                                                                                |       | 0.0625                         | °C             |

| T <sub>RB-CH-ACC(72mV)</sub>            | Channel Temperature<br>TUE, Switching Action Off                                            | Channels 0 and 1, PWM Inactive, RUN <sub><math>\eta</math></sub> = 0V, $\Delta V_{TSNSna}$ = 72mV                                                                             | •     | Within ±3°C of Rea             | ading          |

| T <sub>RB-CH-ACC(ON)</sub>              | Channel Temperature<br>TUE, Switching Action On                                             | READ_TEMPERATURE_1 <sub>n</sub> , Channels 0 and 1,<br>PWM Active, RUN <sub>n</sub> = 5V (Note 12)                                                                            |       | Within ±3°C of Rea             | ading          |

| SYMBOL                                                            | PARAMETER                                                                                                               | CONDITIONS                                                                                                                                                                                                                                             |   | MIN | TYP                             | MAX          | UNITS                           |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---------------------------------|--------------|---------------------------------|

| T <sub>RB-CTRL-ACC(ON)</sub>                                      | Control IC Die<br>Temperature TUE,<br>Switching Action On                                                               | READ_TEMPERATURE_2, PWM Active, RUN <sub>0</sub> = RUN <sub>1</sub> = 5V (Note 12)                                                                                                                                                                     |   | Wit | hin ±1°C                        | of Read      | ing                             |

| t <sub>CONVERT-TEMP-RB</sub>                                      | Temperature Readback<br>Update Rate                                                                                     | MFR_ADC_CONTROL = 0×00 (Notes 9, 15)<br>MFR_ADC_CONTROL = 0×06 or 0×0A (Notes 9, 15)                                                                                                                                                                   |   |     | 90<br>8                         |              | ms<br>ms                        |

| INTV <sub>CC</sub> Regulator                                      |                                                                                                                         |                                                                                                                                                                                                                                                        |   |     |                                 |              |                                 |

| V <sub>INTVCC</sub>                                               | Internal V <sub>CC</sub> Voltage No<br>Load                                                                             | 6V ≤ V <sub>IN</sub> ≤ 16V                                                                                                                                                                                                                             |   | 4.8 | 5                               | 5.2          | V                               |

| $\frac{\Delta V_{\text{INTVCC}(\text{LOAD})}}{V_{\text{INTVCC}}}$ | INTV <sub>CC</sub> Load Regulation                                                                                      | 0mA ≤ I <sub>INTVCC</sub> ≤ 50mA                                                                                                                                                                                                                       |   |     | 0.5                             | ±2           | %                               |

| V <sub>DD33</sub> Regulator                                       |                                                                                                                         |                                                                                                                                                                                                                                                        |   |     |                                 |              |                                 |

| V <sub>VDD33</sub>                                                | Internal V <sub>DD33</sub> Voltage                                                                                      |                                                                                                                                                                                                                                                        |   | 3.2 | 3.3                             | 3.4          | V                               |

| I <sub>LIM(VDD33)</sub>                                           | V <sub>DD33</sub> Current Limit                                                                                         | V <sub>DD33</sub> Electrically Short-Circuited to GND                                                                                                                                                                                                  |   |     | 70                              |              | mA                              |

| V <sub>VDD33_0V</sub>                                             | V <sub>DD33</sub> Overvoltage<br>Threshold                                                                              | (Note 15)                                                                                                                                                                                                                                              |   |     | 3.5                             |              | V                               |

| V <sub>VDD33_UV</sub>                                             | V <sub>DD33</sub> Undervoltage<br>Threshold                                                                             | (Note 15)                                                                                                                                                                                                                                              |   |     | 3.1                             |              | V                               |

| V <sub>DD25</sub> Regulator                                       |                                                                                                                         |                                                                                                                                                                                                                                                        |   |     |                                 |              |                                 |

| $\overline{V_{VDD25}}$                                            | Internal V <sub>DD25</sub> Voltage                                                                                      |                                                                                                                                                                                                                                                        |   |     | 2.5                             |              | V                               |

| I <sub>LIM(VDD25)</sub>                                           | V <sub>DD25</sub> Current Limit                                                                                         | V <sub>DD25</sub> Electrically Short-Circuited to GND                                                                                                                                                                                                  |   |     | 50                              |              | mA                              |

| Oscillator and Pha                                                | ase-Locked Loop (PLL)                                                                                                   |                                                                                                                                                                                                                                                        |   |     |                                 |              |                                 |

| f <sub>OSC</sub>                                                  | Oscillator Frequency<br>Accuracy                                                                                        | FREQUENCY_SWITCH = 500kHz (0xFBE8)<br>250kHz \le FREQUENCY_SWITCH \le 750kHz (Note 15)                                                                                                                                                                 | • |     |                                 | ±7.5<br>±7.5 | %<br>%                          |

| f <sub>SYNC</sub>                                                 | PLL SYNC Capture Range                                                                                                  | FREQUENCY_SWITCH Set to Frequency Slave Mode (0x0000);<br>SYNC Driven by External Clock; 1.8V <sub>OUT</sub>                                                                                                                                           | • | 225 |                                 | 800          | kHz                             |

| V <sub>TH,SYNC</sub>                                              | SYNC Input Threshold                                                                                                    | V <sub>SYNC</sub> Rising (Note 15)<br>V <sub>SYNC</sub> Falling (Note 15)                                                                                                                                                                              |   |     | 1.5<br>1                        |              | V                               |

| V <sub>OL,SYNC</sub>                                              | SYNC Low Output<br>Voltage                                                                                              | I <sub>SYNC</sub> = 3mA                                                                                                                                                                                                                                | • |     | 0.3                             | 0.4          | V                               |

| I <sub>SYNC</sub>                                                 | SYNC Leakage Current in Frequency Slave Mode                                                                            | 0V ≤ V <sub>SYNC</sub> ≤ 3.6V<br>MFR_CONFIG_ALL[4]=1 <sub>b</sub>                                                                                                                                                                                      | • |     |                                 | ±5           | μА                              |

| θ <sub>SYNC</sub> -θ0                                             | SYNC-to-Channel 0<br>Phase Relationship, Lag<br>from Falling Edge of Sync<br>to Rising Edge of Top<br>MOSFET (MT0) Gate | $ \begin{array}{l} \text{(Note 15)} \\ \text{MFR\_PWM\_CONFIG[2:0]} = 000_b,  01X_b \\ \text{MFR\_PWM\_CONFIG[2:0]} = 101_b \\ \text{MFR\_PWM\_CONFIG[2:0]} = 001_b \\ \text{MFR\_PWM\_CONFIG[2:0]} = 1X0_b \\ \end{array} $                           |   |     | 0<br>60<br>90<br>120            |              | Deg<br>Deg<br>Deg<br>Deg        |

| θ <sub>SYNC</sub> -θ1                                             | SYNC-to-Channel 1<br>Phase Relationship, Lag<br>from Falling Edge of Sync<br>to Rising Edge of Top<br>MOSFET (MT1) Gate | (Note 15) $ \begin{array}{l} \text{MFR\_PWM\_CONFIG[2:0] = 011}_b \\ \text{MFR\_PWM\_CONFIG[2:0] = 000}_b \\ \text{MFR\_PWM\_CONFIG[2:0] = 010}_b, 10X_b \\ \text{MFR\_PWM\_CONFIG[2:0] = 001}_b \\ \text{MFR\_PWM\_CONFIG[2:0] = 110}_b \end{array} $ |   |     | 120<br>180<br>240<br>270<br>300 |              | Deg<br>Deg<br>Deg<br>Deg<br>Deg |

| SYMBOL                   | PARAMETER                                | CONDITIONS                                                                                                                                                                                                      |   | MIN         | TYP              | MAX        | UNITS          |

|--------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|------------------|------------|----------------|

| EEPROM Charac            | teristics                                |                                                                                                                                                                                                                 |   |             |                  |            |                |

| Endurance                | (Note 13)                                | $0^{\circ}C \le T_{J} \le 85^{\circ}C$ During EEPROM Write Operations (Note 3)                                                                                                                                  | • | 10,000      |                  |            | Cycles         |

| Retention                | (Note 13)                                | $T_J < T_{J(MAX)}$ , with Most Recent EEPROM Write Operation Having Occurred at 0°C $\leq T_J \leq$ 85°C (Note 3)                                                                                               | • | 10          |                  |            | Years          |

| Mass_Write               | Mass Write Operation<br>Time             | Execution of STORE_USER_ALL Command, $0^{\circ}C \le T_{J} \le 85^{\circ}C$ (ATE-Tested at $T_{J} = 25^{\circ}C$ ) (Notes 3, 13)                                                                                |   |             | 440              | 4100       | ms             |

| Digital I/Os             |                                          |                                                                                                                                                                                                                 |   |             |                  |            |                |

| $\overline{V_{IH}}$      | Input High Threshold<br>Voltage          | SCL, SDA, RUN <i>n</i> , GPIO <sub>n</sub> (Note 15)<br>SHARE_CLK, WP (Note 15)                                                                                                                                 |   | 1.35<br>1.8 |                  |            | V              |

| $V_{IL}$                 | Input Low Threshold<br>Voltage           | SCL, SDA, RUN <i>n</i> , GPIO <sub>n</sub> (Note 15)<br>SHARE_CLK, WP (Note 15)                                                                                                                                 |   |             |                  | 0.8<br>0.6 | V              |

| V <sub>HYST</sub>        | Input Hysteresis                         | SCL, SDA (Note 15)                                                                                                                                                                                              |   |             | 80               |            | mV             |

| V <sub>OL</sub>          | Output Low Voltage                       | SCL, SDA, $\overline{\text{ALERT}}$ , RUN <sub>n</sub> , $\overline{\text{GPIO}}_n$ , SHARE_CLK: $I_{\text{SINK}} = 3\text{mA}$                                                                                 | • |             | 0.3              | 0.4        | V              |

| I <sub>OL</sub>          | Input Leakage Current                    | SDA, SCL, $\overline{\text{ALERT}}$ , RUN <sub>n</sub> : $0V \le V_{\text{PIN}} \le 5.5V$<br>$\overline{\text{GPIO}}_n$ and SHARE_CLK: $0V \le V_{\text{PIN}} \le 3.6V$                                         | • |             |                  | ±5<br>±2   | μA<br>μA       |

| t <sub>FILTER</sub>      | Input Digital Filtering                  | $\frac{RUN_n}{GPIO_n} \text{ (Note 15)}$                                                                                                                                                                        |   |             | 10<br>3          |            | μs<br>μs       |

| C <sub>PIN</sub>         | Input Capacitance                        | SCL, SDA, RUN <sub>n</sub> , GPIO <sub>n</sub> , SHARE_CLK, WP (Note 15)                                                                                                                                        |   |             |                  | 10         | pF             |

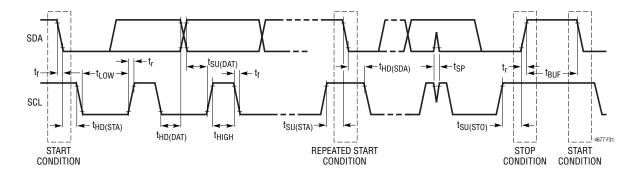

| PMBus Interface          | Timing Characteristics                   |                                                                                                                                                                                                                 |   |             |                  |            |                |

| f <sub>SMB</sub>         | Serial Bus Operating Frequency           | (Note 15)                                                                                                                                                                                                       |   | 10          |                  | 400        | kHz            |

| t <sub>BUF</sub>         | Bus Free Time Between<br>Stop and Start  | (Note 15)                                                                                                                                                                                                       |   | 1.3         |                  |            | μѕ             |

| t <sub>HD,STA</sub>      | Hold Time After Repeated Start Condition | Time Period After Which First Clock Is Generated (Note 15)                                                                                                                                                      |   | 0.6         |                  |            | μs             |

| t <sub>SU,STA</sub>      | Repeated Start Condition<br>Setup Time   | (Note 15)                                                                                                                                                                                                       |   | 0.6         |                  |            | μs             |

| t <sub>SU,STO</sub>      | Stop Condition Setup<br>Time             | (Note 15)                                                                                                                                                                                                       |   | 0.6         |                  |            | μs             |

| t <sub>HD,DAT</sub>      | Data Hold Time                           | Receiving Data (Note 15) Transmitting Data (Note 15)                                                                                                                                                            |   | 0<br>0.3    |                  | 0.9        | μs<br>μs       |

| t <sub>SU,DAT</sub>      | Data Setup Time                          | Receiving Data (Note 15)                                                                                                                                                                                        |   | 0.1         |                  |            | μs             |

| t <sub>TIMEOUT_SMB</sub> | Stuck PMBus Timer<br>Timeout             | Measured from the Last PMBus Start Event:  Block Reads MFR_CONFIG_ALL[3] = 0 <sub>b</sub> (Note 15)  Non-Block Reads MFR_CONFIG_ALL[3] = 0 <sub>b</sub> (Note 15)  MFR_CONFIG_ALL[3] = 1 <sub>b</sub> (Note 15) |   |             | 150<br>32<br>250 |            | ms<br>ms<br>ms |

| $t_{LOW}$                | Serial Clock Low Period                  | (Note 15)                                                                                                                                                                                                       |   | 1.3         |                  | 10000      | μs             |

| t <sub>HIGH</sub>        | Serial Clock High Period                 | (Note 15)                                                                                                                                                                                                       |   | 0.6         |                  |            | μs             |

**Note 1:** Stresses beyond those listing under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating conditions for extended periods may affect device reliability and lifetime.

**Note 2:** The LTM4677 is tested under pulsed-load conditions such that  $T_J \approx T_A$ . The LTM4677E is guaranteed to meet performance specifications over the 0°C to 125°C internal operating temperature range. Specifications

over the -40°C to 125°C internal operating temperature range are assured by design, characterization and correlation with statistical process controls. The LTM4677I is guaranteed to meet specifications over the full -40°C to 125°C internal operating temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal resistance and other environmental factors.

4677fa

### **ELECTRICAL CHARACTERISTICS**

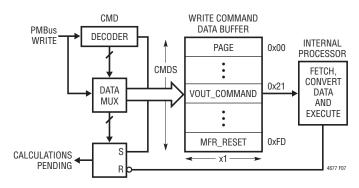

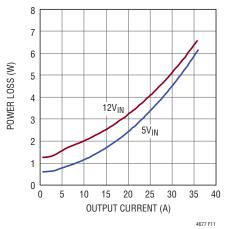

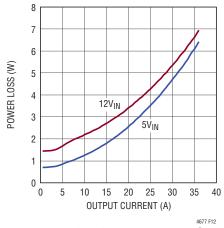

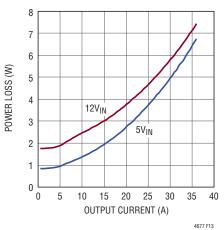

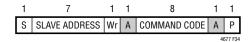

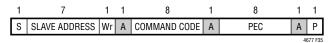

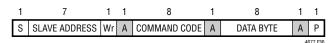

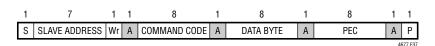

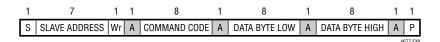

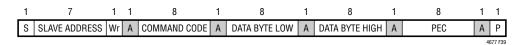

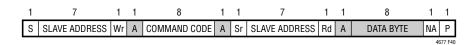

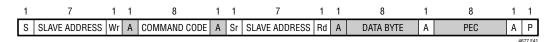

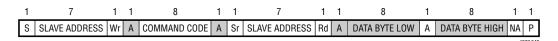

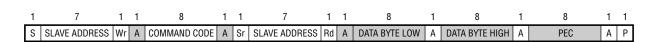

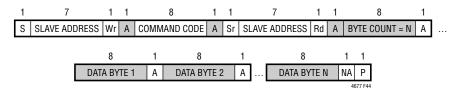

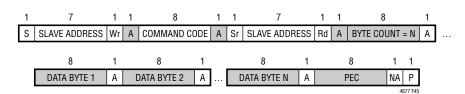

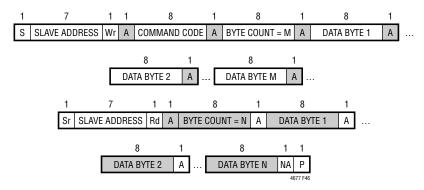

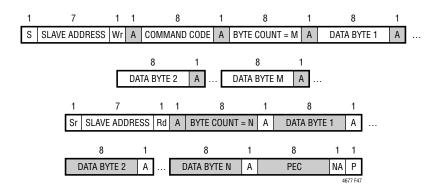

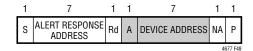

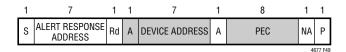

Note 3: The LTM4677's EEPROM temperature range for valid write commands is 0°C to 85°C. To achieve guaranteed EEPROM data retention, execution of the "STORE\_USER\_ALL" command—i.e., uploading RAM contents to NVM—outside this temperature range is not recommended. However, as long as the LTM4677's EEPROM temperature is less than 130°C, the LTM4677 will obey the STORE\_USER\_ALL command. Only when EEPROM temperature exceeds 130°C, the LTM4677 will not act on any STORE\_USER\_ALL transactions: instead, the LTM4677 NACKs the serial command and asserts its relevant CML (communications, memory, logic) fault bits. EEPROM temperature can be queried prior to commanding STORE\_USER\_ALL; see the Applications Information section.