## IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

### **General Description**

### Features

The MAX5988A/MAX5988B provide a complete powersupply solution as IEEE<sup>®</sup> 802.3af-compliant Class 1/ Class 2 Powered Devices (PDs) in a Power-over-Ethernet (PoE) system. The devices integrate the PD interface with an efficient DC-DC converter, offering a low external part count PD solution. The devices also include a low-dropout regulator, MPS, sleep, and ultra-low-power modes.

The PD interface provides a detection signature and a Class 1/Class 2 classification signature with a single external resistor. The PD interface also provides an isolation power MOSFET, a 60mA (max) inrush current limit, and a 321mA (typ) operating current limit.

The integrated step-down DC-DC converter uses a peak current-mode control scheme and provides an easy-to-implement architecture with a fast transient response. The step-down converter operates in a wide input voltage range from 8.8V to 60V and supports up to 6.49W of input power at 1.3A load. The DC-DC converter operates at a fixed 215kHz switching frequency, with an efficiency-boosting frequency foldback that reduces the switching frequency by half at light loads.

The devices feature an input undervoltage-lockout (UVLO) with wide hysteresis and long deglitch time to compensate for twisted-pair cable resistive drop and to assure glitch-free transition during power-on/-off conditions. The devices also feature overtemperature shutdown, short-circuit protection, output overvoltage protection, and hiccup current limit for enhanced performance and reliability.

All devices are available in a 20-pin, 4mm x 4mm, TQFN power package and operate over the -40°C to +85°C temperature range.

### **Applications**

IEEE 802.3af-Powered Devices

IP Phones

Wireless Access Nodes

**IP Security Cameras**

WiMAX<sup>®</sup> Base Stations

IEEE is a registered service mark of the Institute of Electrical and Electronics Engineers, Inc.

*WiMAX is a registered certification mark and registered service mark of WiMAX Forum.*

- ◆ IEEE 802.3af Compliant

- PoE Class 1/Class 2 Classification

- Sleep and Ultra-Low-Power Mode

- Intelligent Maintain Power Signature (MPS)

- Simplified Wall Adapter Interface

- Efficient, Integrated DC-DC Converter (with Integrated Switches)

- ♦ 8.8V to 60V Wide Input Voltage Range

- ♦ 3.0V to 14V Programmable Output Voltage Range

- Internal Compensation

- Fixed 215kHz Switching Frequency

- Frequency Foldback for High-Efficiency Light-Load Operation

- Built-In Output-Voltage Monitoring

- ♦ Open-Drain RESET Output

- Protects Against Overload, Output Short Circuit, Output Overvoltage, and Overtemperature

- Hiccup-Mode Runaway Current Limit

- Back-Bias Capability to Optimize the Efficiency

- Integrated TVS Diode Withstands Cable Discharge Event (CDE)

- Internal LDO Regulator with Up to 100mA Load

- Fixed 3.3V or Adjustable Output Voltage Through an External Resistive Divider (LDO)

- 49mA (typ) Inrush Current Limit

- Pass 2kV, 200m CAT-6 Cable Discharge Event

<u>Ordering Information/Selector Guide</u> appears at end of data sheet.

For related parts and recommended products to use with this part, refer to <u>www.maximintegrated.com/MAX5988A.related</u>.

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND, unless otherwise noted.) | VDRV to $V_{DD}$                                       |

|-----------------------------------------------------------|--------------------------------------------------------|

| V <sub>DD</sub> to GND0.3V to +70V (internally clamped)   | PGND to GND0.3V to +0.3V                               |

| (100V, 100ms, $R_{TEST} = 3.3 k\Omega$ ) (Note 1)         | LX Total RMS Current1.6A                               |

| $V_{CC}$ , WAD, RREF to GND0.3V to ( $V_{DD}$ + 0.3V)     | Continuous Power Dissipation ( $T_A = + 70^{\circ}C$ ) |

| AUX, LDO_IN, LED to GND0.3V to 16V                        | TQFN (derate 28.6mW/°C above +70°C)2285.7mW            |

| LDO_OUT to GND0.3V to (LDO_IN + 0.3V)                     | Operating Temperature Range40°C to +85°C               |

| LDO_FB to GND0.3V to +6V                                  | Junction Temperature+150°C                             |

| LX to GND0.3V to (V <sub>CC</sub> + 0.3V)                 | Storage Temperature Range65°C to +150°C                |

| LDO_OUT, VDRV, FB, RESET, WK, SL, ULP, MPS, CLASS2        | Lead Temperature (soldering, 10s)+300°C                |

| to GND0.3V to +6V                                         | Soldering Temperature (reflow)+260°C                   |

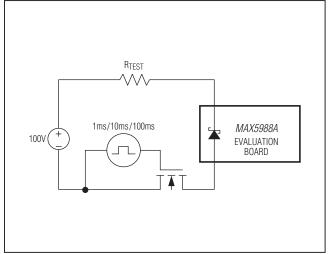

#### Note 1: See Figure 1, Test Circuit.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 2)

| Junction-to-Ambient Thermal Resistance $(\theta_{JA})$ | .35°C/W |

|--------------------------------------------------------|---------|

| Junction-to-Case Thermal Resistance $(\theta_{JC})$    | 2.7°C/W |

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 48V, R_{SIG} = 24.9k\Omega, LED, V_{CC}, \overline{SL}, \overline{ULP}, \overline{WK}, \overline{RESET}, LDO_OUT unconnected, WAD = LDO_EN = LDO_IN = PGND = GND, C1 = 68nF, C2 = 10\muF, C3 = 1\muF (see Figure 3), V_{FB} = V_{AUX} = 0V, LX unconnected, CLASS2 = 0V, MPS = 0V. All voltages are referenced to GND, unless otherwise noted. T_A = T_J = -40^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.) (Note 3)$

| PARAMETER                                  | SYMBOL          | CONDITIONS                                                 |                | MIN   | ТҮР   | MAX   | UNITS |  |

|--------------------------------------------|-----------------|------------------------------------------------------------|----------------|-------|-------|-------|-------|--|

| POWER DEVICE (PD) INTERFACE                |                 |                                                            |                |       |       |       |       |  |

| DETECTION MODE                             |                 |                                                            |                |       |       |       |       |  |

| Input Offset Current                       | IOFFSET         | $V_{VDD} = 1.4V$ to                                        | 10.1V (Note 4) |       |       | 8     | μA    |  |

| Effective Differential Input<br>Resistance | dR              | V <sub>VDD</sub> = 1.4V to 10.1V with 1V step,<br>(Note 5) |                | 23.95 |       | 25.5  | kΩ    |  |

| CLASSIFICATION MODE                        |                 |                                                            |                |       |       |       |       |  |

| Classification Enable Threshold            | VTH,CLS,EN      | V <sub>DD</sub> rising                                     |                | 10.2  | 11.42 | 12.5  | V     |  |

| Classification Disable Threshold           | VTH,CLS,DIS     | V <sub>DD</sub> rising                                     |                | 22    | 23    | 23.8  | V     |  |

| Classification Stability Time              |                 |                                                            |                |       | 2     |       | ms    |  |

| Classification Current                     |                 | V <sub>DD</sub> = 12.6V<br>to 20V                          | CLASS2 = GND   | 9.12  | 10.5  | 11.88 |       |  |

| Classification Current                     | ICLASS          |                                                            | CLASS2 = VDRV  | 16.1  | 18    | 20.9  | - mA  |  |

| POWER MODE                                 |                 |                                                            |                |       |       |       |       |  |

| V <sub>DD</sub> Supply Voltage Range       | V <sub>DD</sub> |                                                            |                |       |       | 60    | V     |  |

| V <sub>DD</sub> Supply Current             | IDD             | $V_{DD} = 60V$                                             |                |       | 3.3   | 4.5   | mA    |  |

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 48V, R_{SIG} = 24.9k\Omega, LED, V_{CC}, \overline{SL}, \overline{ULP}, \overline{WK}, \overline{RESET}, LDO_OUT unconnected, WAD = LDO_EN = LDO_IN = PGND = GND, C1 = 68nF, C2 = 10\muF, C3 = 1\muF (see Figure 3), V_{FB} = V_{AUX} = 0V, LX unconnected, CLASS2 = 0V, MPS = 0V. All voltages are referenced to GND, unless otherwise noted. T_{A} = T_{I} = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at T\_{A} = +25°C.) (Note 3)

| PARAMETER                                | SYMBOL               | CONDIT                                                                    | IONS                                         | MIN  | TYP        | MAX | UNITS |

|------------------------------------------|----------------------|---------------------------------------------------------------------------|----------------------------------------------|------|------------|-----|-------|

| V <sub>DD</sub> Turn-On Voltage          | VON                  | V <sub>DD</sub> rising                                                    |                                              | 37.2 | 38.8       | 40  | V     |

| V <sub>DD</sub> Turn-Off Voltage         | VOFF                 | V <sub>DD</sub> falling                                                   |                                              | 30   | 31.5       |     | V     |

| V <sub>DD</sub> Turn-On/Off Hysteresis   | VHYST_UVLO           | (Note 6)                                                                  |                                              |      | 7.3        |     | V     |

| V <sub>DD</sub> Deglitch Time            | <sup>t</sup> OFF_DLY | V <sub>DD</sub> falling from 40'<br>(Note 5)                              | V to 20V                                     |      | 150        |     | μs    |

| Inrush to Operating Mode Delay           | <sup>t</sup> DELAY   | t <sub>DELAY</sub> = time after<br>from 1.5V to 0V                        | (V <sub>DD</sub> - V <sub>CC</sub> )         |      | 123        |     | ms    |

| Isolation Power MOSFET On-<br>Resistance | R <sub>ON_ISO</sub>  | IVCC = 100mA                                                              | $T_J = +25^{\circ}C$<br>$T_J = +85^{\circ}C$ |      | 1.2<br>1.5 |     | Ω     |

| MAINTAIN POWER SIGNATURE                 | (MPS = VDRV)         | I                                                                         | 0                                            |      |            |     |       |

| PoE MPS Current Rising<br>Threshold      | IMPS_RISE            |                                                                           |                                              | 18   | 28.7       | 40  | mA    |

| PoE MPS Current Falling<br>Threshold     | IMPS_FALL            |                                                                           |                                              | 14   | 24         | 35  | mA    |

| PoE MPS Current Threshold<br>Hysteresis  | IMPS_HYS             |                                                                           |                                              |      | 4.3        |     | mA    |

| PoE MPS Output Average<br>Current        | IMPS_AVE             |                                                                           |                                              |      | 4.8        |     | mA    |

| PoE MPS Peak Output Current              | IMPS_PEAK            |                                                                           |                                              | 10   | 12.6       |     | mA    |

| PoE MPS Time High                        | IMPS_HIGH            |                                                                           |                                              |      | 95         |     | ms    |

| PoE MPS Time Low                         | IMPS_LOW             |                                                                           |                                              |      | 190        |     | ms    |

| CURRENT LIMIT                            |                      |                                                                           |                                              |      |            |     |       |

| Inrush Current Limit                     | INRUSH               | During initial turn-or<br>V <sub>DD</sub> - V <sub>CC</sub> = 4V, m       |                                              | 39   | 49         | 60  | mA    |

| Current Limit During Normal<br>Operation | ILIM                 | After inrush completed, $V_{CC} = V_{DD}$<br>- 1.5V, measured at $V_{CC}$ |                                              | 290  | 321        | 360 | mA    |

| LOGIC                                    |                      | •                                                                         |                                              |      |            |     |       |

| WAD Detection Rising Threshold           | VWAD_RISE            |                                                                           |                                              |      |            | 8.8 | V     |

| WAD Detection Falling Threshold          | VWAD_FALL            |                                                                           |                                              | 5.8  |            |     | V     |

| WAD Detection Hysteresis                 |                      |                                                                           |                                              |      | 0.6        |     | V     |

| WAD Input Current                        | IWAD                 | $V_{WAD} = 24V$                                                           |                                              |      | 125        |     | μA    |

| CLASS2, MPS Voltage Rising<br>Threshold  | VCLASS2, RISE        |                                                                           |                                              |      |            | 2.9 | V     |

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 48V, R_{SIG} = 24.9k\Omega, LED, V_{CC}, \overline{SL}, \overline{ULP}, \overline{WK}, \overline{RESET}, LDO_OUT unconnected, WAD = LDO_EN = LDO_IN = PGND = GND, C1 = 68nF, C2 = 10\muF, C3 = 1\muF (see Figure 3), V_{FB} = V_{AUX} = 0V, LX unconnected, CLASS2 = 0V, MPS = 0V. All voltages are referenced to GND, unless otherwise noted. T_A = T_1 = -40^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.) (Note 3)$

| PARAMETER                                 | SYMBOL              | CONDITIONS                                                              | MIN  | TYP   | MAX  | UNITS |

|-------------------------------------------|---------------------|-------------------------------------------------------------------------|------|-------|------|-------|

| CLASS2, MPS Voltage Falling<br>Threshold  | VCLASS2, FALL       |                                                                         | 0.4  |       |      | V     |

| RESET Output Voltage Low                  | VOL_RESET           | I <sub>SINK</sub> = 1mA                                                 |      |       | 0.2  | V     |

| RESET, CLASS2, MPS Leakage                | ILOG_LEAK           |                                                                         | -10  |       | +10  | μA    |

| INTERNAL REGULATOR WITH E                 | BACK BIAS           |                                                                         |      |       |      |       |

| V <sub>AUX</sub> Input Voltage Range      | V <sub>AUX</sub>    | Inferred from V <sub>AUX</sub> input current                            | 4.75 |       | 14   | V     |

| VAUX Input Current                        | IAUX                | V <sub>AUX</sub> from 4.75V to 14V                                      | 0.65 |       | 3.1  | mA    |

| V <sub>DRV</sub> Output Voltage           |                     |                                                                         | 4.2  |       | 5.5  | V     |

| SLEEP MODE                                | 1                   |                                                                         |      |       |      |       |

| WK and ULP Logic Threshold                | V <sub>TH</sub>     | $V_{\overline{WK}}$ falling and $V_{\overline{ULP}}$ rising and falling | 1.6  |       | 2.9  | V     |

| SL Logic Threshold                        |                     | Falling                                                                 | 0.55 |       | 0.8  | V     |

| SL Current                                |                     | $V_{\overline{SL}} = 0V$                                                |      | 62.4  |      | μA    |

|                                           |                     | $R_{\overline{SL}} = 60.4 k\Omega$ , $V_{LED} = 6.5 V$                  | 9.2  | 10.6  | 12   |       |

| LED Current Amplitude                     | LED                 | $R_{SL} = 30.2 k\Omega, V_{LED} = 6.5 V$                                | 19.2 | 21.2  | 23.5 | 5 mA  |

|                                           |                     | $R_{SL} = 30.2 k\Omega, V_{LED} = 3.5 V$                                |      | 21.2  |      |       |

| LED Current Programmable<br>Range         | IRANGE              |                                                                         | 10   |       | 20   | mA    |

| LED Current with Grounded $\overline{SL}$ | ILED_MAX            | $V_{\overline{SL}} = 0V$                                                | 20.6 | 26    | 31.4 | mA    |

| LED Current Frequency                     | fILED               | Sleep and ultra-low-power modes                                         |      | 250   |      | Hz    |

| LED Current Duty Cycle                    | DILED               | Sleep and ultra-low-power modes                                         |      | 25    |      | %     |

| V <sub>DD</sub> Current Amplitude         | IVDD                | Sleep mode, $V_{LED} = 6.5V$                                            | 10   | 12    | 14.5 | mA    |

| Internal Current Duty Cycle               | DIVDD               | Sleep and ultra-low-power modes                                         |      | 75    |      | %     |

| Internal Current Enable Time              | tmp_enable          | Ultra-low-power mode                                                    | 76   | 88    | 98   | ms    |

| Internal Current Disable Time             | tmp_disable         | Ultra-low-power mode                                                    | 205  | 237   | 265  | ms    |

| THERMAL SHUTDOWN                          |                     |                                                                         |      |       |      |       |

| Thermal Shutdown Threshold                | T <sub>SD</sub>     | T <sub>J</sub> rising                                                   |      | 151   |      | °C    |

| Thermal Shutdown Hysteresis               | T <sub>SD,HYS</sub> |                                                                         |      | 16    |      | °C    |

| LDO                                       |                     |                                                                         |      |       |      |       |

| Input Voltage Range                       |                     | Inferred from line regulation                                           | 4.5  |       | 14   | V     |

| Output Voltage                            |                     | $LDO_FB = V_{DRV}$                                                      |      | 3.3   |      | V     |

| Max Output Voltage Setting                |                     | With external divider to LDO_FB                                         |      |       | 5.5  | V     |

| LDO FB Regulation Voltage                 |                     |                                                                         | 1.2  | 1.227 | 1.25 | V     |

## IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 48V, R_{SIG} = 24.9k\Omega, LED, V_{CC}, \overline{SL}, \overline{ULP}, \overline{WK}, \overline{RESET}, LDO_OUT unconnected, WAD = LDO_EN = LDO_IN = PGND = GND, C1 = 68nF, C2 = 10\muF, C3 = 1\muF (see <u>Figure 3</u>), V_{FB} = V_{AUX} = 0V, LX unconnected, CLASS2 = 0V, MPS = 0V. All voltages are referenced to GND, unless otherwise noted. T_A = T_1 = -40°C to +85°C, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 3)$

| PARAMETER                           | SYMBOL              | CONDITIONS                                                         | MIN   | TYP   | MAX   | UNITS |

|-------------------------------------|---------------------|--------------------------------------------------------------------|-------|-------|-------|-------|

| LDO FB Leakage Current              |                     |                                                                    | -1    |       | +1    | μA    |

| Dropout                             | VDROPOUT            | $V_{LDO_IN} = 5V, V_{LDO_FB} = V_{DRV},$<br>$I_{LOAD} = 80mA$      |       | 300   |       | mV    |

| Load Regulation                     |                     | ILOAD from 1mA to 80mA                                             |       | 0.5   |       | mV/mA |

| Line Regulation                     |                     | VLDO_IN from 4.5V to 14V                                           |       | 1.4   |       | mV/V  |

| Overcurrent Protection<br>Threshold | IOVC                |                                                                    | 85    |       |       | mA    |

| LDO_FB Rising Threshold             |                     |                                                                    |       | 3.3   | 3.7   | V     |

| LDO_FB Hysteresis                   |                     |                                                                    | 2.3   | 2.4   |       | V     |

| DC-DC CONVERTER INPUT SUP           | PLY                 |                                                                    | •     |       |       |       |

| V Voltago Dango                     | VDD,RISING          | $V_{CC} = V_{DD} = V_{WAD} - 0.3V$ , rising                        | 8     |       | 60    | V     |

| V <sub>DD</sub> Voltage Range       | VDD,FALLING         | $V_{CC} = V_{DD} = V_{WAD} - 0.3V$ , falling                       | 7.7   |       | 60    |       |

| WAD Detection Rising Threshold      | VWAD,RISE           | (Note 7)                                                           |       |       | 8.8   | V     |

| WAD Detection Falling Threshold     | Vwad,fall           | (Note 7)                                                           | 5.8   |       |       | V     |

| WAD Detection Hysteresis            |                     |                                                                    |       | 0.6   |       | V     |

| POWER MOSFETs                       |                     |                                                                    | •     |       |       |       |

| High-Side pMOS On-Resistance        | R <sub>DSON-H</sub> | $I_{LX} = 0.5A$ (sourcing)                                         |       | 0.54  |       | Ω     |

| Low-Side nMOS On-Resistance         | R <sub>DSON-L</sub> | $I_{LX} = 0.5A$ (sinking)                                          |       | 0.14  |       | Ω     |

| LX Leakage Current                  | ILX-LKG             | $V_{DD} = V_{CC} = 28V, V_{LX} = (V_{PGND} + 1V) to (V_{CC} - 1V)$ | -5    |       | +5    | μA    |

| SOFT-START (SS)                     |                     |                                                                    | •     |       |       |       |

| Soft-Start Time                     | <sup>t</sup> SS-TH  |                                                                    |       | 10    |       | ms    |

| FEEDBACK (FB)                       |                     |                                                                    |       |       |       |       |

| FB Regulation Voltage               | VFB-RG              |                                                                    | 1.203 | 1.226 | 1.252 | V     |

| FB Input Bias Current               | I <sub>FB</sub>     | V <sub>FB</sub> = 1.224V                                           |       | 10    | 200   | nA    |

| OUTPUT VOLTAGE                      |                     |                                                                    |       |       |       |       |

| Output Voltage Range                | Vour                | MAX5988A                                                           | 3.0   |       | 5.6   | V     |

|                                     | VOUT                | MAX5988B                                                           | 5.4   |       | 14    | v     |

| Cycle-by-Cycle Overvoltage          |                     | Rising (Note 8)                                                    | 100.5 | 103   | 108   | %     |

| Protection                          | Vout-ov             | Falling (Note 8)                                                   | 98.5  | 101.1 | 104   | /0    |

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 48V, R_{SIG} = 24.9k\Omega, LED, V_{CC}, \overline{SL}, \overline{ULP}, \overline{WK}, \overline{RESET}, LDO_OUT unconnected, WAD = LDO_EN = LDO_IN = PGND = GND, C1 = 68nF, C2 = 10\muF, C3 = 1\muF (see <u>Figure 3</u>), V_{FB} = V_{AUX} = 0V, LX unconnected, CLASS2 = 0V, MPS = 0V. All voltages are referenced to GND, unless otherwise noted. T_A = T_1 = -40°C to +85°C, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 3)$

| PARAMETER                                                | SYMBOL               | CON                              | DITIONS            | MIN  | TYP   | MAX | UNITS  |

|----------------------------------------------------------|----------------------|----------------------------------|--------------------|------|-------|-----|--------|

| INTERNAL COMPENSATION NE                                 | TWORK                |                                  |                    |      |       |     |        |

| Compensation Network Zero-<br>Resistance                 | RZERO                |                                  |                    |      | 200   |     | kΩ     |

| Compensation Network Zero-<br>Capacitance                | CZERO                |                                  |                    |      | 150   |     | pF     |

| CURRENT LIMIT                                            |                      |                                  |                    |      |       |     |        |

|                                                          |                      |                                  | CLASS2 = GND       | 1.45 | 1.64  |     |        |

| Peak Current-Limit Threshold                             |                      | MAX5988A                         | CLASS2 = VDRV      | 1.66 | 1.79  |     |        |

|                                                          | IPEAK-LIMIT          |                                  | CLASS2 = GND       | 0.75 | 0.81  |     | A      |

|                                                          |                      | MAX5988B                         | CLASS2 = VDRV      | 0.85 | 0.94  |     |        |

|                                                          |                      |                                  | CLASS2 = GND       |      | 1.9   |     |        |

| Runaway Current-Limit<br>Threshold                       | RUNAWAY-LIMIT        | MAX5988A                         | CLASS2 = VDRV      |      | 2.2   |     | A      |

|                                                          |                      |                                  | CLASS2 = GND       |      | 0.93  |     |        |

|                                                          |                      | MAX5988B                         | CLASS2 = VDRV      |      | 1.07  |     |        |

|                                                          | h                    | MAX5988A                         |                    |      | 1.5   |     | A      |

| Valley Current-Limit Threshold                           | IVALLEY-LIMIT        | MAX5988B                         |                    | 0.75 |       |     |        |

| ZX Threshold                                             | I <sub>ZX</sub>      |                                  |                    |      | 25    |     | mA     |

| TIMINGS                                                  |                      |                                  |                    |      |       |     |        |

| Switching Frequency                                      | fsw                  |                                  |                    | 190  | 215   | 238 | kHz    |

| Frequency Foldback                                       | <sup>f</sup> SW-FOLD |                                  |                    | 95   | 107.5 | 119 | kHz    |

| Consecutive ZX Events for<br>Entering Foldback           |                      |                                  |                    |      | 8     |     | Events |

| Consecutive ZX Events for<br>Exiting Foldback            |                      |                                  |                    |      | 8     |     | Events |

| V <sub>OUT</sub> Undervoltage Trip Level to Cause HICCUP | VOUT-HICF            | After soft-start of              | completed (Note 8) | 55   | 60    | 65  | %      |

| HICCUP Timeout                                           |                      |                                  |                    |      | 154   |     | ms     |

| Minimum On-Time                                          | ton-min              |                                  |                    |      | 113   | 140 | ns     |

| LX Dead Time                                             |                      |                                  |                    |      | 14    |     | ns     |

| RESET                                                    |                      |                                  |                    |      |       |     |        |

| VFB Threshold for RESET<br>Assertion                     | VFB-OKF              | V <sub>FB</sub> falling (Note 8) |                    | 87   | 90    | 93  | %      |

| V <sub>FB</sub> Threshold for RESET<br>Deassertion       | V <sub>FB-OKR</sub>  | V <sub>FB</sub> rising (Note     | e 8)               | 91.5 | 95    | 98  | %      |

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 48V, R_{SIG} = 24.9k\Omega, LED, V_{CC}, \overline{SL}, \overline{ULP}, \overline{WK}, \overline{RESET}, LDO_OUT unconnected, WAD = LDO_EN = LDO_IN = PGND = GND, C1 = 68nF, C2 = 10\muF, C3 = 1\muF (see Figure 3), V_{FB} = V_{AUX} = 0V, LX unconnected, CLASS2 = 0V, MPS = 0V. All voltages are referenced to GND, unless otherwise noted. T_A = T_J = -40^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.) (Note 3)$

| PARAMETER                                  | SYMBOL      | CONDITIONS                                                         | MIN | ТҮР | MAX | UNITS |

|--------------------------------------------|-------------|--------------------------------------------------------------------|-----|-----|-----|-------|

| VLDO_FB Threshold for RESET<br>Assertion   | VLDO_FB-OKF | V <sub>LDO_FB</sub> falling, LDO_FB = V <sub>DRV</sub><br>(Note 9) |     | 90  |     | %     |

| VLDO_FB Threshold for RESET<br>Deassertion |             | V <sub>FB</sub> rising                                             |     | 95  |     | %     |

| RESET Deassertion Delay                    |             |                                                                    |     | 4.8 |     | ms    |

Note 3: All devices are 100% production tested at  $T_A = +25$  °C. Limits over temperature are guaranteed by design.

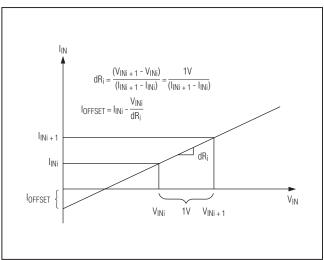

Note 4: The input offset current is illustrated in Figure 2.

Note 5: Effective differential input resistance is defined as the differential resistance between V<sub>DD</sub> and GND, see Figure 2.

**Note 6:** A 20V glitch on input voltage, which takes V<sub>DD</sub> below V<sub>ON</sub> shorter than or equal to t<sub>OFF\_DLY</sub> does not cause the device to exit power-on mode.

**Note 7:** The WAD detection rising and falling thresholds control the isolation power MOS transistor. To turn the DC-DC on in WAD mode, the WAD must be detected and the V<sub>DD</sub> must be within the V<sub>DD</sub> voltage range.

Note 8 Referred to feedback regulation voltage.

Note 9: Referred to LDO feedback regulation voltage.

Figure 1. MAX5988A–MAX5988D Internal TVS Test Setup

Figure 2. Effective Differential Resistance and Offset Current

# MAX5988A/MAX5988B IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

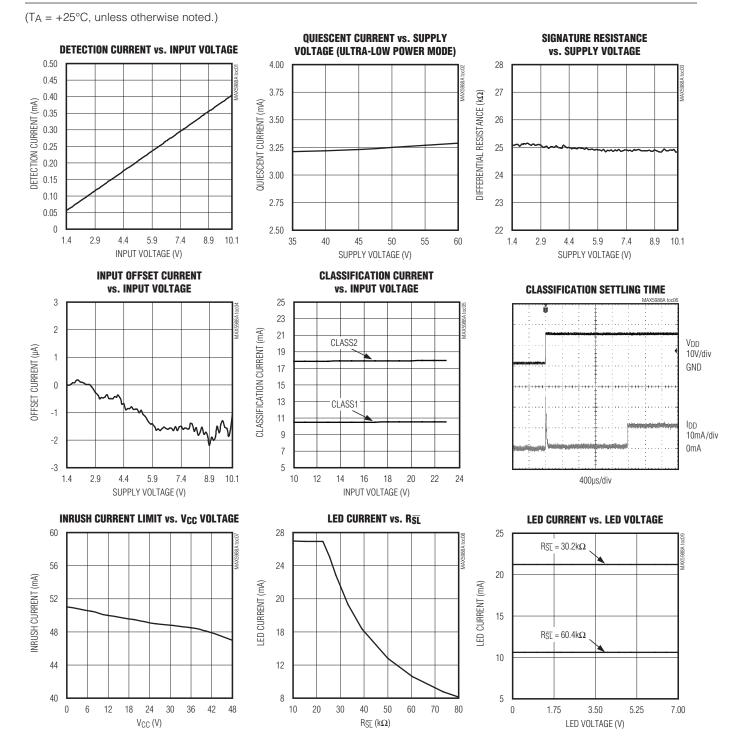

#### **Typical Operating Characteristics**

Maxim Integrated

# **MAX5988A/MAX5988B** IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, **Powered Devices with Integrated DC-DC Converter**

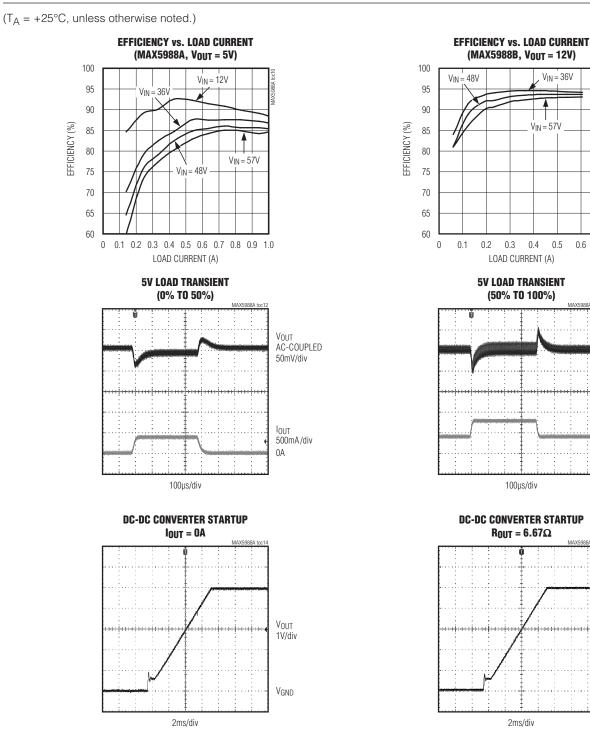

**Typical Operating Characteristics (continued)**

V<sub>IN</sub> = 36V

0.6 0.7

V<sub>OUT</sub> AC-COUPLED

50mV/div

lout

0A

Vout

1V/div

VGND

ISA toc15

500mA/div

V<sub>IN</sub> = 57V

## IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

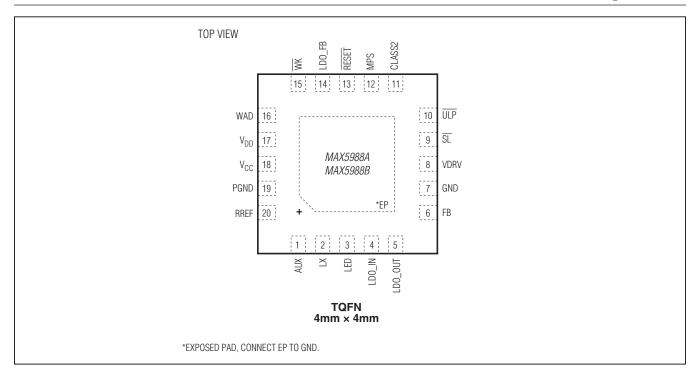

**Pin Configuration**

### **Pin Description**

| PIN                                                                                                                                                                                                                                                                    | NAME FUNCTION                                                                 |                                                                                                                                                  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1Auxiliary Voltage Input. Auxiliary input to the internal regulator, VDRV. Connect AUX to the or<br>the buck converter, if the output voltage is greater than 4.75V, to back bias the internal circle<br>increase efficiency. Connect to a clean ground when not used. |                                                                               |                                                                                                                                                  |  |  |  |  |

| 2                                                                                                                                                                                                                                                                      | LX Inductor Connection. Inductor connection for the internal DC-DC converter. |                                                                                                                                                  |  |  |  |  |

| 3                                                                                                                                                                                                                                                                      | LED                                                                           | LED Driver Output. In sleep mode, LED sources a periodic current ( $I_{LED}$ ) at 250Hz with 25% duty cycle.                                     |  |  |  |  |

| 4 LDO_IN LDO Input Voltage. Connect LDO_IN to output when used; otherwise, connect to GND. Co<br>minimum 1µF bypass capacitor between LDO_IN and GND.                                                                                                                  |                                                                               | LDO Input Voltage. Connect LDO_IN to output when used; otherwise, connect to GND. Connect a minimum 1µF bypass capacitor between LDO_IN and GND. |  |  |  |  |

| 5                                                                                                                                                                                                                                                                      | LDO_OUT                                                                       | LDO Output Voltage. Connect a minimum 1µF output capacitor between LDO_OUT and GND.                                                              |  |  |  |  |

| 6                                                                                                                                                                                                                                                                      | FB                                                                            | Feedback. Feedback input for the DC-DC buck converter. Connect FB to a resistive divider from the output to GND to adjust the output voltage.    |  |  |  |  |

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

**Pin Description (continued)**

| 7 8 | GND<br>VDRV     | <ul> <li>Ground. Reference rail for the device. It is also the "quiet" ground for all voltage references (e.g., FB is referenced to this GND).</li> <li>Internal 5V Regulator Voltage Output. The internal voltage regulator provides 5V to the MOSFET driver and other internal circuits. VDRV is referenced to GND. Do not use VDRV to drive external circuits.</li> </ul>                                                                                   |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | VDRV            | and other internal circuits. VDRV is referenced to GND. Do not use VDRV to drive external circuits.                                                                                                                                                                                                                                                                                                                                                            |

|     |                 | Connect a 1µF bypass capacitor between VDRV and GND.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9   | SL              | Sleep Mode Enable Input. A falling edge on $\overline{SL}$ brings the device into sleep mode. An external resistor ( $R_{\overline{SL}}$ ) connected between $\overline{SL}$ and GND sets the LED current ( $I_{LED}$ ).                                                                                                                                                                                                                                       |

| 10  | ULP             | Ultra-Low Power-Mode Enable Input. $\overline{\text{ULP}}$ has an internal 50k $\Omega$ pullup resistor to the internal 5V bias rail. A falling edge on $\overline{\text{SL}}$ while $\overline{\text{ULP}}$ is asserted low enables ultra-low power mode. When ultra-low power mode is enabled, the power consumption of the device is reduced even lower than sleep mode to comply with ultra-low power sleep power requirements while still supporting MPS. |

| 11  | CLASS2          | Class 2 Selection Pin. Connect to VDRV for Class 2 operation. Connect to GND for Class 1 operation.                                                                                                                                                                                                                                                                                                                                                            |

| 12  | MPS             | MPS Enable Pin. Connect to VDRV to turn the MPS function on. Connect to GND to turn the MPS function off.                                                                                                                                                                                                                                                                                                                                                      |

| 13  | RESET           | Open-Drain RESET Output. The RESET output is driven low if either LDO_OUT or FB drops below 90% of its set value. RESET goes high 4.8ms after both LDO_OUT and FB rise above 95% of their set values. Leave unconnected when not used.                                                                                                                                                                                                                         |

| 14  | LDO_FB          | LDO Regulator Feedback Input. Connect to VDRV to get the preset LDO output voltage of 3.3V, or connect to a resistive divider from LDO_OUT to GND for an adjustable LDO output voltage.                                                                                                                                                                                                                                                                        |

| 15  | WK              | Wake Mode Enable Input. $\overline{\text{WK}}$ has an internal 50k $\Omega$ pullup resistor to the internal 5V bias rail. A falling edge on $\overline{\text{WK}}$ brings the device out of sleep mode and into the normal operating mode (wake mode).                                                                                                                                                                                                         |

| 16  | WAD             | Wall Power Adapter Detector Input. Wall adapter detection is enabled when the voltage from WAD to GND is greater than 8.8V. When a wall power adapter is present, the isolation p-channel power MOSFET turns off. Connect WAD directly to GND when the wall power adapter or other auxiliary power source is not used.                                                                                                                                         |

| 17  | V <sub>DD</sub> | Positive Supply Input. Connect a 68nF (min) bypass capacitor between V <sub>DD</sub> and PGND.                                                                                                                                                                                                                                                                                                                                                                 |

| 18  | V <sub>CC</sub> | DC-DC Converter Power Input. V <sub>DD</sub> is connected to V <sub>CC</sub> by an isolation p-channel MOSFET. Connect a 10 $\mu$ F capacitor in parallel with a 1 $\mu$ F ceramic capacitor between V <sub>CC</sub> and PGND.                                                                                                                                                                                                                                 |

| 19  | PGND            | Power Ground. Power ground of the DC-DC converter power stage. Connect PGND to GND with a star connection. Do not use PGND as reference for sensitive feedback circuit.                                                                                                                                                                                                                                                                                        |

| 20  | RREF            | Signature Resistor Connection. Connect a 24.9k $\Omega$ resistor (R <sub>SIG</sub> ) to GND.                                                                                                                                                                                                                                                                                                                                                                   |

|     | EP              | Exposed Pad. Connect the exposed pad to GND.                                                                                                                                                                                                                                                                                                                                                                                                                   |

## IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

#### **Detailed Description**

#### **PD** Interface

The MAX5988A/MAX5988B include complete interface functions for a PD to comply with the IEEE 802.3af standard as a Class 1/Class 2 PD. The devices provide the detection and classification signatures using a single external signature resistor. An integrated MOSFET provides isolation from the buck converter when the PSE has not applied power. The devices guarantee a leakage current offset of less than 10µA during the detection phase. The devices feature power-mode undervoltage-lockout (UVLO) with wide hysteresis and long deglitch time to compensate for twisted-pair-cable resistive drop and to ensure glitch-free transitions between detection, classification, and power-on/-off modes.

#### **Operating Modes**

The devices operate in three different modes depending on  $V_{DD}$ . The three modes are detection mode, classification mode, and power mode. The device is in detection mode when  $V_{DD}$  is between 1.4V and 10.1V, classification mode when  $V_{DD}$  is between 12.6V and 20V, and power mode when the input voltage exceeds  $V_{ON}$ .

#### Detection Mode $(1.4V \le V_{DD} \le 10.1V)$

In detection mode, the devices provide a signature differential resistance to V<sub>DD</sub>. During detection, the power-sourcing equipment (PSE) applies two voltages to V<sub>DD</sub>, both between 1.4V and 10.1V with a minimum 1V increment. The PSE computes the differential resistance to ensure the presence of the 24.9k $\Omega$  signature resistor. Connect the 24.9k $\Omega$  signature resistor (R<sub>SIG</sub>) from RREF to GND for proper signature detection. The device applies V<sub>DD</sub> to RREF when in detection mode, and the V<sub>DD</sub> offset current due to the device is less than 10µA. The DC offset due to protection diodes does not significantly affect the signature resistance measurement.

#### Classification Mode (12.6V $\leq$ V<sub>DD</sub> $\leq$ 20V)

In classification mode, the devices sink Class 1/Class 2 classification currents. The PSE applies a classification voltage between 12.6V and 20V, and measures the classification currents. The devices use the external 24.9k $\Omega$  resistor (RSIG) and the CLASS2 pin to set the classifi

cation current at 10.5mA (Class 1, CLASS1 = GND) or 18mA (Class 2, CLASS2 = VDRV). The PSE uses this to determine the maximum power to deliver. The classification current includes current drawn by the supply current of the device so the total current drawn by the PD is within the IEEE 802.3af standard. The classification current is turned off when the device leaves classification mode.

#### Power Mode ( $V_{DD} \ge V_{ON}$ )

In power mode, the devices have the isolation MOSFET between  $V_{DD}$  and  $V_{CC}$  fully on. The devices have the buck regulator enabled and the LDO enabled. The devices can be in either wake mode, sleep mode, or ultra-low-power mode. The buck regulator and LDO are only enabled in wake mode.

The devices enter power mode when V<sub>DD</sub> rises above the undervoltage lockout threshold (V<sub>ON</sub>). When V<sub>DD</sub> rises above V<sub>ON</sub>, the device turns on the internal p-channel isolation MOSFET to connect V<sub>CC</sub> to V<sub>DD</sub> with inrush current limit internally set to 49mA (typ). The isolation MOSFET is fully turned on when V<sub>CC</sub> is near V<sub>DD</sub> and the inrush current is below the inrush limit. Once the isolation MOSFET is fully turned on, the device changes the current limit to 321mA (typ). The buck converter turns on 123ms after the isolation MOSFET turns on fully.

#### **Undervoltage Lockout**

The devices operate with up to a 60V supply voltage with a turn-on UVLO threshold (V<sub>ON</sub>) at 38.8V (typ), and a turn-off UVLO threshold (V<sub>OFF</sub>) at 31.5V (typ). When the input voltage is above V<sub>ON</sub>, the device enters power mode and the internal isolation MOSFET is turned on. When the input voltage is below V<sub>OFF</sub> for more than t<sub>OFF DLY</sub>, the MOSFET and the buck converter are off.

#### **LED Driver**

The devices drive an LED, or multiple LEDs in series, with a maximum LED voltage of 6.5V. In sleep mode and ultralow-power mode, the LED current is pulse width modulated with a duty cycle of 25% and the amplitude is set by  $R_{\overline{SL}}$ . The LED driver current amplitude is programmable from 10mA to 20mA using  $R_{\overline{SL}}$  according to the formula:

$$I_{LED} = 646/R_{\overline{SL}} (mA)$$

where  $R_{\overline{SL}}$  is in k $\Omega$ .

## IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

#### Sleep and Ultra-Low-Power Modes

The devices feature a sleep mode and an ultra-lowpower mode in which the internal p-channel isolation MOSFET is kept on and the buck regulator is off. In sleep mode, the LED driver output (LED) pulse width modulates the LED current with a 25% duty cycle. The peak LED current ( $I_{LED}$ ) is set by an external resistor  $R_{\overline{SL}}$ . To enable sleep mode, apply a falling edge to  $\overline{SL}$  with ULP disconnected or high impedance. Sleep mode can only be entered from wake mode.

Ultra-low-power mode allows the devices to reduce power consumption lower than sleep mode, while maintaining the power signature of the IEEE standard. The ultra-low-power-mode enable input  $\overline{\text{ULP}}$  is internally held high with a 50k $\Omega$  pullup resistor to the internal 5V bias of the device. To enable ultra-low-power mode, apply a falling edge to  $\overline{\text{SL}}$  with  $\overline{\text{ULP}}$  = LOW. Ultra-low-power mode can only be entered from wake mode.

To exit from sleep mode or ultra-low-power mode and resume normal operation, apply a falling edge on the wake-mode enable input ( $\overline{WK}$ ).

#### **Thermal-Shutdown Protection**

If the devices' die temperature reaches  $151^{\circ}$ C, an overtemperature fault is generated and the device shuts down. The die temperature must cool down below + $135^{\circ}$ C to remove the overtemperature fault condition. After a thermal shutdown condition clears, the device is reset.

#### WAD Description

For applications where an auxiliary power source such as a wall power adapter is used to power the PD, the devices feature wall power adapter detection.

The wall power adapter is connected from WAD to PGND. The devices detect the wall power adapter when the voltage from WAD to PGND is greater than 8.8V. When a wall power adapter is detected, the internal isolation MOSFET is turned off, classification current is disabled.

Connect the auxiliar power source to WAD, connect a diode from WAD to V<sub>DD</sub>, and connect a diode from WAD to V<sub>CC</sub>. See the typical application circuit in Figures 3 and 4.

The application circuit must ensure that the auxiliary power source can provide power to  $V_{\mbox{DD}}$  and  $V_{\mbox{CC}}$  by

means of external diodes. The voltage on V<sub>DD</sub> must be within the V<sub>DD</sub> voltage range to allow the DC-DC to operate. To allow operation of the DC-DC converter, the V<sub>DD</sub> and V<sub>CC</sub> voltage must be greater than 8V, on the rising edge, while on the falling edge the V<sub>DD</sub> and V<sub>CC</sub> may fall down to 7.7V keeping the DC-DC converter on.

**Note:** When operating solely with a wall power adapter, the WAD voltage must be able to meet the condition  $V_{DD}$  > 8.8V, that likely results in WAD > 8.8V.

**Internal Linear Regulator and Back Bias** An internal voltage regulator provides VDRV to internal circuitry. The VDRV output is filtered by a 1µF capacitor connected from VDRV to GND. The regulator is for internal use only and cannot be used to provide power to external circuits. VDRV can be powered by either V<sub>DD</sub> or V<sub>AUX</sub>, depending on V<sub>AUX</sub>. The internal regulator is used for both PD and buck converter operations.

$V_{OUT}$  can be used to back bias the VDRV voltage regulator if  $V_{OUT}$  is greater than 4.75V. Back biasing VDRV increases device efficiency by drawing current from  $V_{OUT}$  instead of  $V_{DD}$ . If  $V_{OUT}$  is used as back bias, connect AUX directly to  $V_{OUT}$ . In this configuration, the VDRV source switches from  $V_{DD}$  to  $V_{AUX}$  after the buck converter's output has reached its regulation voltage.

#### **Cable Discharge Event Protection (CDE)**

A 70V voltage clamp is integrated to protect the internal circuits from a cable discharge event.

#### **DC-DC Buck Converter**

The DC-DC buck converter uses a PWM, peak currentmode, fixed-frequency control scheme providing an easy-to-implement architecture without sacrificing a fast transient response. The buck converter operates in a wide input voltage range from 8.8V to 60V and supports up to 6.49W of output power at 1.3A load. The devices provide a wide array of protection features including UVLO, overtemperature shutdown, short-circuit protection with hiccup runaway current limit, cycle-by-cycle peak current protection, and cycle-by-cycle output overvoltage protection, for enhanced performance and reliability. A frequency foldback scheme is implemented to reduce the switching frequency to half at light loads to increase the efficiency.

gives priority to the WAD supply over V<sub>D</sub> supply, and

smoothly switches the power supply to WAD when it is

detected. The wall power adapter is connected from

WAD to PGND. The devices detect the wall power adapt-

er when the voltage from WAD to PGND is greater than

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, **Powered Devices with Integrated DC-DC Converter**

#### Frequency Foldback Protection for High-Efficiency Light-Load Operation

The devices enter frequency foldback mode when eight consecutive inductor current zero-crossings occur. The switching frequency is 215kHz under loads large enough that the inductor current does not cross zero. In frequency foldback mode, the switching frequency is reduced to 107.5kHz to increase power conversion efficiency. The device returns to normal mode when the inductor current does not cross zero for eight consecutive switching periods. Frequency foldback mode is forced during startup until 50% of the soft-start is completed.

#### Hiccup Mode

The devices include a hiccup protection feature. When hiccup protection is triggered, the devices turn off the high-side and turn on the low-side MOSFET until the inductor current reaches the valley current limit. The control logic waits 154ms until attempting a new softstart sequence. Hiccup mode is triggered if the current in the high-side MOSFET exceeds the runaway currentlimit threshold, both during soft-start and during normal operating mode. Hiccup mode can also be triggered in normal operating mode in the case of an output undervoltage event. This happens if the regulated feedback voltage drops below 60% (typ).

**RESET** Output The devices feature an open-drain RESET output that indicates if either the LDO or the switching regulator drop out of regulation. The RESET output goes low if either regulator drops below 90% of its regulated feedback value. RESET goes high impedance 4.8ms after both regulators are above 95% of their value.

#### Maintain Power Signature (MPS)

The devices feature the MPS to comply with the IEEE 802.3af standard. It is able to maintain a minimum current (10mA) of the port to avoid the power disconnection from the PSE. The devices enter MPS mode when the port current is lower than 14mA and also exit the MPS mode when the port current is greater than 40mA. The feature is enabled by connecting the MPS pin to VDRV, or disabled by connecting the MPS pin to GND.

### **Applications Information**

#### **Operation with Wall Adapter**

For applications where an auxiliary power source such as a wall power adapter is used to power the PD, the devices feature wall power adapter detection. The device

### Adjusting Buck Converter Output Voltage

The buck converter output voltage is set by changing the feedback resistor-divider ratio. The output voltage can be set from 3.0V to 5.6V (MAX5988A) or 5.4V to 14V (MAX5988B). The FB voltage is regulated to 1.227V. Keep the trace from the FB pin to the center of the resistive divider short, and keep the total feedback resistance around  $10k\Omega$ .

#### Inductor Selection

Choose an inductor with the following equation:

$$L = \frac{V_{OUT} \times (V_{CC} - V_{OUT})}{f_{S} \times V_{CC} \times L_{IR} \times I_{OUT(MAX)}}$$

where  $L_{IR}$  is the ratio of the inductor ripple current to full load current at the minimum duty cycle. Choose LIR between 20% to 40% for best performance and stability. Use an inductor with the lowest possible DC resistance that fits in the allotted dimensions. Powdered iron ferrite core types are often the best choice for performance. With any core material, the core must be large enough not to saturate at the current limit of the devices.

8.8V. When a wall power adapter is detected, the internal isolation MOSFET is turned off, classification current is disabled and the device draws power from the auxiliary power source through V<sub>CC</sub>. Connect the auxiliary power source to WAD, connect a diode from WAD to  $V_{CC}$ . See the typical application circuit in Figures 3 and 4.

#### Adjusting LDO Output Voltage

An uncommitted LDO regulator is available to provide a supply voltage to external circuits. A preset voltage of 3.3V is set by connecting LDO\_FB directly to VDRV. For different output voltages connect a resistor divider from LDO\_OUT and LDO\_FB to GND. The total feedback resistance should be in the range of  $100k\Omega$ . The minimum output current capability is 85mA and thermal considerations must be taken to prevent triggering thermal shutdown. The LDO regulator can be powered by VOUT, a different power supply, or grounded when not used. The LDO is enabled once the buck converter has reached the regulation voltage. The LDO is disabled when the buck converter is turned off or not regulating.

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

#### V<sub>CC</sub> Input Capacitor Selection

The input capacitor reduces the current peaks drawn from the input power supply and reduces switching noise in the IC. The total input capacitance must be equal or greater than the value given by the following equation to keep the input-ripple voltage within specification and minimize the high-frequency ripple current being fed back to the input source:

$$C_{IN\_MIN} = \frac{D \times T_S \times I_{OUT}}{V_{IN-RIPPLE}}$$

where  $V_{IN-RIPPLE}$  is the maximum allowed input ripple voltage across the input capacitors and is recommended to be less than 2% of the minimum input voltage. D is the duty cycle ( $V_{OUT}/V_{IN}$ ) and T<sub>S</sub> is the switching period (1/f<sub>S</sub>).

The impedance of the input capacitor at the switching frequency should be less than that of the input source so high-frequency switching currents do not pass through the input source, but are instead shunted through the input capacitor. The input capacitor must meet the ripple current requirement imposed by the switching currents. The RMS input ripple current is given by:

$$I_{\text{RIPPLE}} = I_{\text{LOAD}} \times \frac{\sqrt{V_{\text{OUT}} \times (V_{\text{CC}} - V_{\text{OUT}})}}{V_{\text{IN}}}$$

where IRIPPLE is the input RMS ripple current.

#### **Output Capacitor Selection**

The key selection parameters for the output capacitor are capacitance, ESR, ESL, and voltage-rating requirements. These affect the overall stability, output ripple voltage, and transient response of the DC-DC converter. The output ripple occurs due to variations in the charge stored in the output capacitor, the voltage drop due to the capacitor's ESR, and the voltage drop due to the capacitor's ESL. Estimate the output-voltage ripple due to the output capacitance, ESR, and ESL:

$V_{RIPPLE} = V_{RIPPLE(C)} + V_{RIPPLE(ESR)} + V_{RIPPLE(ESL)}$

where the output ripple due to output capacitance, ESR, and ESL is:

$$V_{RIPPLE(C)} = \frac{I_{P_-P}}{8 \times C_{OUT} \times f_S}$$

$$V_{RIPPLE(ESR)} = I_{P_-P} \times ESR$$

$$V_{RIPPLE(ESL)} = \frac{I_{P_-P}}{t_{ON}} \times ESL$$

or

$$V_{RIPPLE(ESL)} = \frac{I_{P_-P}}{t_{OFF}} \times ESL$$

or whichever is larger. The peak-to-peak inductor current  $(\mathsf{I}_{\mathsf{P}\text{-}\mathsf{P}})$

$$I_{P-P} = \frac{V_{CC} - V_{OUT}}{f_S \times L} \times \frac{V_{OUT}}{V_{CC}}$$

Use these equations for initial output capacitor selection. Determine final values by testing a prototype or an evaluation circuit. A smaller ripple current results in less output-voltage ripple. Since the inductor ripple current is a factor of the inductor value, the output-voltage ripple decreases with larger inductance. Use ceramic capacitors for low ESR and low ESL at the switching frequency of the converter. The ripple voltage due to ESL is negligible when using ceramic capacitors.

Load-transient response depends on the selected output capacitance. During a load transient, the output instantly changes by ESR x  $I_{LOAD}$ . Before the controller can respond, the output deviates further, depending on the inductor and output capacitor values. After a short time, the controller responds by regulating the output voltage back to its predetermined value. The controller response time depends on the closed-loop bandwidth. A higher bandwidth yields a faster response time, preventing the output from deviating further from its regulating value.

| OUTPUT | C          | C <sub>IN</sub> |                |            | 01.400 |

|--------|------------|-----------------|----------------|------------|--------|

| (V)    | CERAMIC    | ELECTROLYTIC    | CERAMIC        | L          | CLASS  |

| 3.3    | 2.2µF/100V | 10µF/63V        | 1 x 100µF/6.3V | 33µH/1.4A  | 1      |

| 5      | 2.2µF/100V | 10µF/63V        | 1 x 100µF/6.3V | 47µH/1.6A  | 1 or 2 |

| 12     | 2.2µF/100V | 10µF/63V        | 2 x 10µF/16V   | 220µH/0.8A | 1 or 2 |

Table 1. Design Selection Table

Maxim Integrated

## IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

#### **PCB** Layout

Careful PCB layout is critical to achieve clean and stable operation. It is highly recommended to duplicate the MAX5988A EV kit layout for optimum performance. If deviation is necessary, follow these guidelines for good PCB layout:

- 1) Connect input and output capacitors to the power ground plane; connect all other capacitors to the signal ground plane.

- 2) Place capacitors on  $V_{DD}$ ,  $V_{CC}$ , AUX, VDRV as close as possible to the IC and its corresponding pin using direct traces. Keep power ground plane (connected to PGND) and signal ground plane (connected to GND) separate.

- 3) Keep the high-current paths as short and wide as possible. Keep the path of switching current short

and minimize the loop area formed by LX, the output capacitors, and the input capacitors.

- Connect V<sub>DD</sub>, V<sub>CC</sub>, and PGND separately to a large copper area to help cool the IC to further improve efficiency and long-term reliability.

- 5) Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close as possible to the IC.

- 6) Route high-speed switching nodes, such as LX, away from sensitive analog areas (FB).

- 7) Place enough vias in the pad for the EP of the devices so that heat generated inside can be effectively dissipated by the PCB copper. The recommended spacing for the vias is 1mm to 1.2mm pitch. The thermal vias should be plated (1oz copper) and have a small barrel diameter (0.3mm to 0.33mm).

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

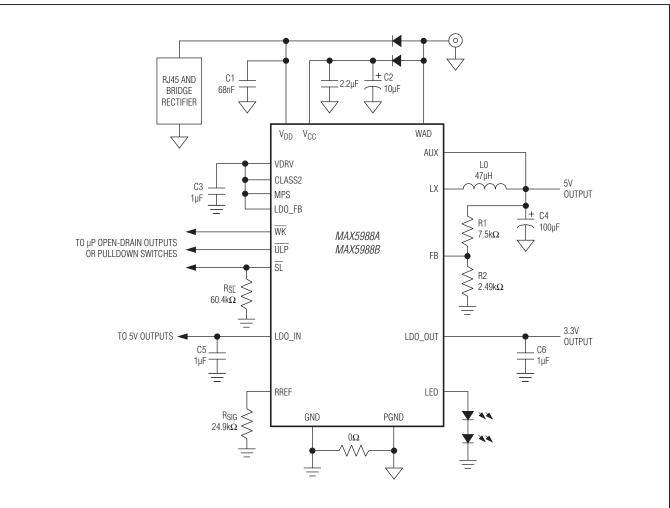

**Typical Application Circuits**

Figure 3. MAX5988A/MAX5988B Buck Regulator and Fixed LDO Output

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

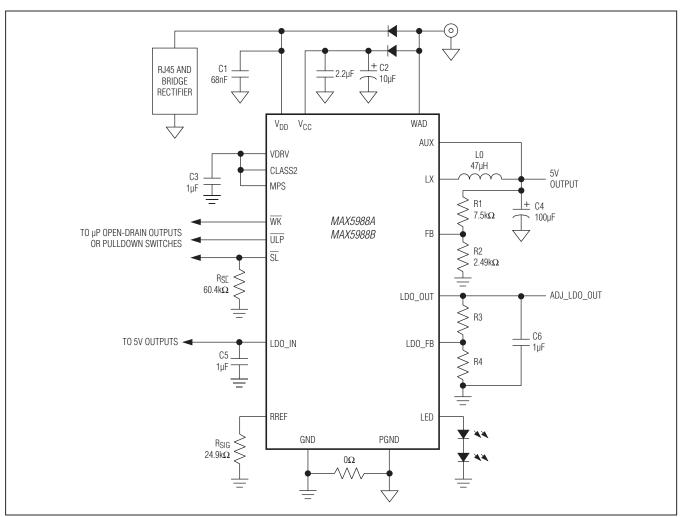

**Typical Application Circuits (continued)**

Figure 4. MAX5988A/MAX5988B Buck Regulator and Adjustable LDO Output

# IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

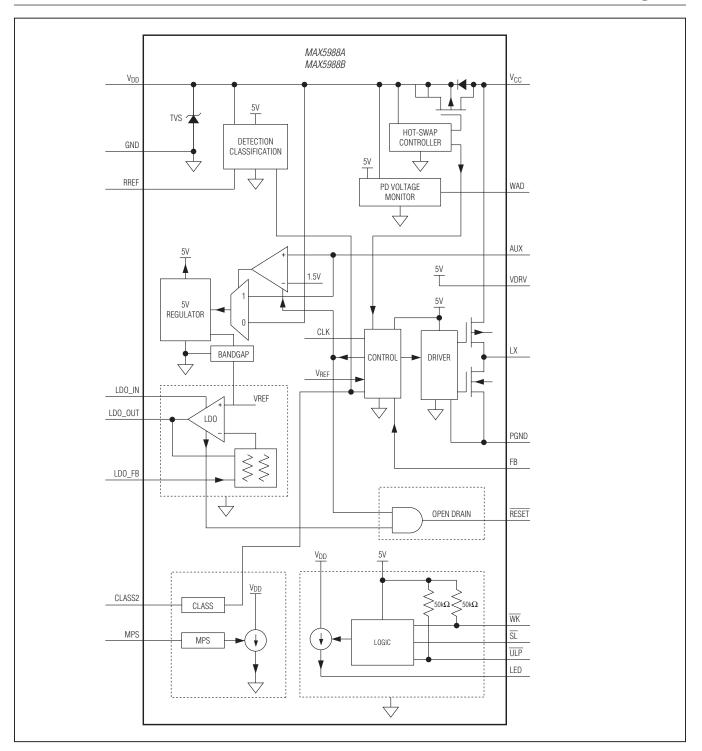

**Functional Diagram**

## IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

### **Chip Information**

PROCESS: BiCMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | OUTLINE        | LAND           |

|------------|---------|----------------|----------------|

| TYPE       | CODE    | NO.            | PATTERN NO.    |

| 20 TQFN-EP | T2044+4 | <u>21-0139</u> | <u>90-0409</u> |

### **Ordering Information/Selector Guide**

| PART         | PIN-PACKAGE | SLEEP/ULP<br>MODE | LDO | UVLO (V) | RESET | MPS/CLASS2 | OUTPUT <sub>ADJ</sub><br>(V) |

|--------------|-------------|-------------------|-----|----------|-------|------------|------------------------------|

| MAX5988AETP+ | 20 TQFN-EP* | Yes               | Yes | 38.8     | Yes   | Yes        | 3 to 5.6                     |

| MAX5988BETP+ | 20 TQFN-EP* | Yes               | Yes | 38.8     | Yes   | Yes        | 5.4 to 14                    |

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

## IEEE 802.3af-Compliant, High-Efficiency, Class 1/Class 2, Powered Devices with Integrated DC-DC Converter

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                   | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------|------------------|

| 0                  | 11/12            | Initial release               | _                |

| 1                  | 1/13             | Corrected land pattern number | 20               |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

#### Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000

© 2013 Maxim Integrated Products, Inc.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.