# **LXT905**

# Universal 10BASE-T Transceiver with 3.3V Support

## **Datasheet**

The LXT905 Universal 10BASE-T Transceiver is designed for IEEE 802.3 physical layer applications. It provides, in a single CMOS device, all the active circuitry for interfacing most standard IEEE 802.3 controllers to 10BASE-T media.

The LXT905 functions include Manchester encoding/decoding, receiver squelch and transmit pulse shaping, jabber, link integrity testing, and reversed polarity detection/correction. The LXT905 drives the 10BASE-T twisted-pair cable, with only a simple isolation transformer, using a single 3.3V or 5V power supply. Integrated filters simplify the design work required for FCC-compliant EMI performance.

The LXT905 is part of the Intel Carrier Class Ethernet family of products. The LXT905 Universal Transceiver offers 10BASE-T connectivity solutions that support operations over an extended temperature range, while providing features that increase reliability. The device has an operational lifetime of at least ten years, with less than 100 failures per billion hours, and will be available a minimum of five years from the introduction of the product.

Intel Carrier Class Ethernet products are ideal for applications where equipment must function reliably under environmentally controlled conditions, such as base stations, telecom/network switches, factory floor equipment, and industrial computers.

# **Applications**

- Access devises (DSL, Cable Modems, and Set-top Boxes)

- Routers/Bridges/Switches/Hubs

- Telecom Backplane

- USB to Ethernet Converters

## **Product Features**

- Transparent 3.3V or 5V operation

- Integrated filters Simplifies FCC compliance

- Integrated Manchester encoder/decoder

- 10BASE-T compliant transceiver

- Automatic polarity correction

- SQE enable/disable

- Four LED drivers

- Full-duplex capability

- Power-down mode with tri-state

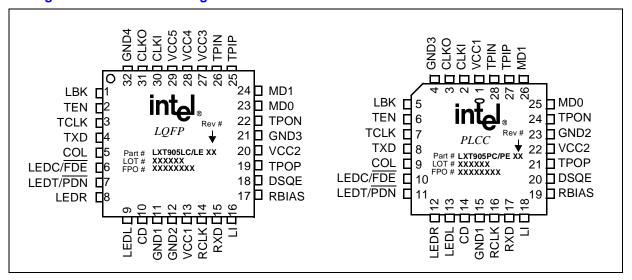

- Available in 28-pin PLCC and 32-pin LQFP packages

- Commercial Temperature Range (0 to +70°C)

- Extended Temperature Range (-40 to +85°C)

Order Number: 249271-002

June 2001

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT905 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0    | Pin A                                  | Assignments and Signal Descriptions                                                                                                                                                                                                                                            | 8                                |

|--------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.0    | Fund                                   | ctional Description                                                                                                                                                                                                                                                            | 10                               |

|        | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Introduction Controller Compatibility Modes Transmit Function Jabber Control Function SQE Function Receive Function                                                                                                                                                            | 10<br>11<br>11<br>12             |

|        | 2.7<br>2.8<br>2.9                      | Polarity Reverse Function  Collision Detection Function  Loopback Functions  2.9.1 Internal Loopback  2.9.2 External Loopback/Full Duplex  Link Integrity Test Function                                                                                                        | 14<br>15<br>15<br>15             |

| 3.0    |                                        | ication Information                                                                                                                                                                                                                                                            |                                  |

| 3.0    | 3.1<br>3.2<br>3.3<br>3.4               | Introduction                                                                                                                                                                                                                                                                   | 17<br>17<br>17<br>17<br>18<br>18 |

| 4.0    | Test                                   | Specifications                                                                                                                                                                                                                                                                 | 22                               |

|        | 4.1<br>4.2<br>4.3<br>4.4               | Timing Diagrams for Mode 1 (MD1 = Low, MD0 = Low) Figures 11 - 14  Timing Diagrams for Mode 2 (MD1 = Low, MD0 = High) Figures 15 - 18  Timing Diagrams for Mode 3 (MD1 = High, MD0 = Low) Figures 19 - 22  Timing Diagrams for Mode 4 (MD1 = High, MD0 = High) Figures 23 - 26 | 28<br>30                         |

| 5.0    | Mech                                   | nanical Specifications                                                                                                                                                                                                                                                         | 34                               |

| Α      | Orde                                   | ering Information                                                                                                                                                                                                                                                              | 37                               |

| Figure | S                                      |                                                                                                                                                                                                                                                                                |                                  |

|        | 1<br>2<br>3<br>4<br>5<br>6             | LXT905 Block Diagram  LXT905 Pin Assignments  LXT905 TPO Output Waveform  Jabber Control Function  SQE Function  Collision Detection Function  Link Integrity Test Function                                                                                                    | 8<br>10<br>12<br>13              |

## **Contents**

**Tables**

| 8  | Intel Controller Application (Mode 2)                            | 19 |

|----|------------------------------------------------------------------|----|

| 9  | LXT905/380C26 Interface for Dual 10BASE-T and Token Ring Support |    |

|    | (Mode 4)                                                         |    |

| 10 | LXT905/MC68EN360 Interface for Full-Duplex 10BASE-T (Mode 1)     | 21 |

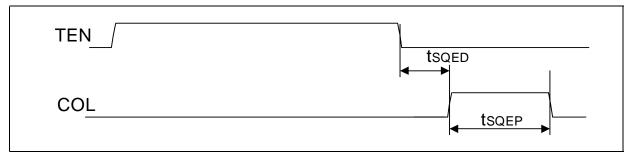

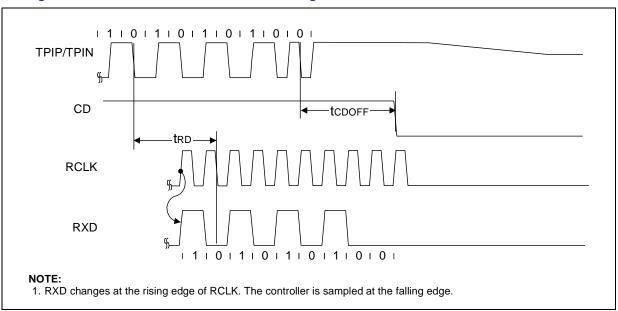

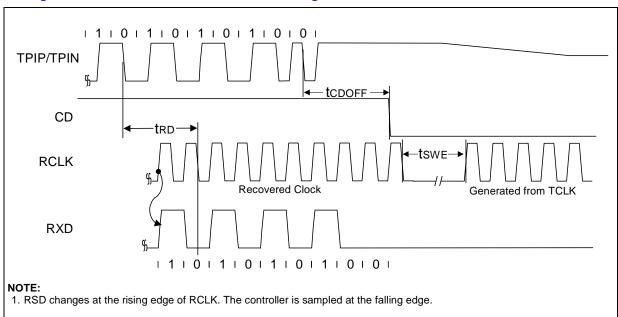

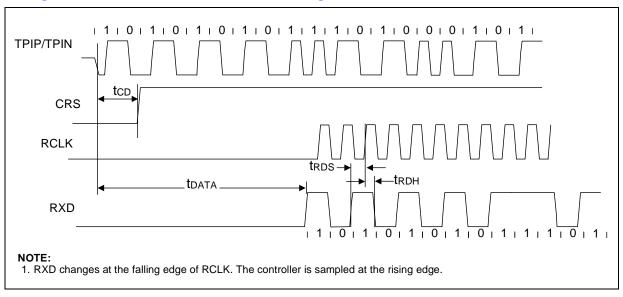

| 11 | Mode 1 RCLK/Start-of-Frame Timing                                | 26 |

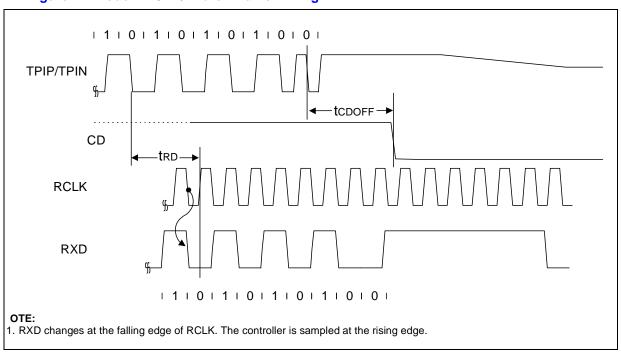

| 12 | Mode 1 RCLK/End-of-Frame Timing                                  | 26 |

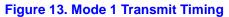

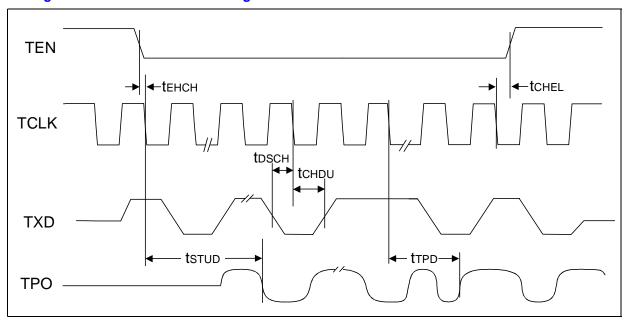

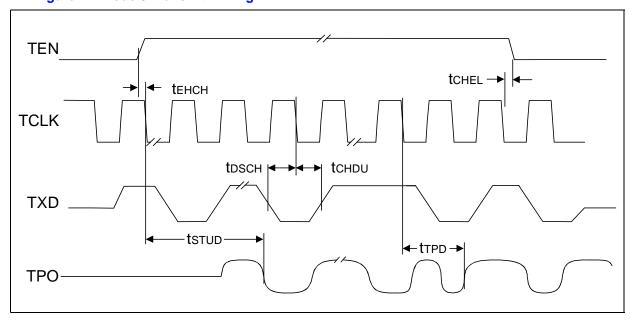

| 13 | Mode 1 Transmit Timing                                           | 27 |

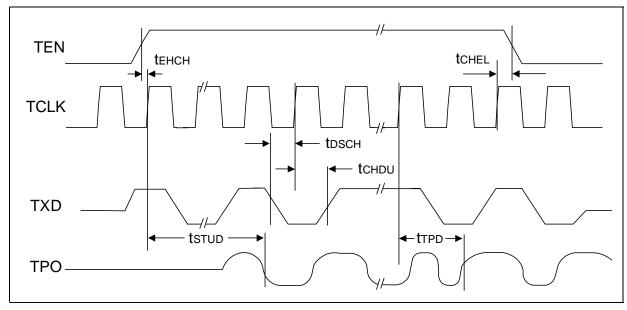

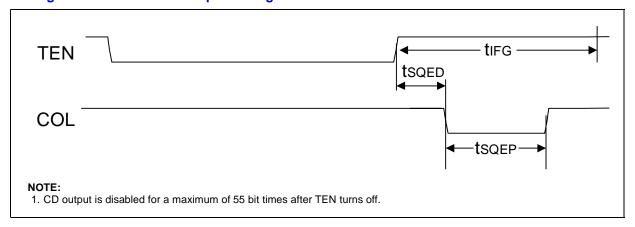

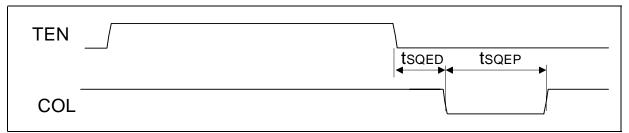

| 14 | Mode 1 COL Output Timing                                         | 27 |

| 15 | Mode 2 RCLK/Start-of-Frame                                       | 28 |

| 16 | Mode 2 RCLK/End-of-Frame Timing                                  | 28 |

| 17 | Mode 2 Transmit Timing                                           | 29 |

| 18 | Mode 2 COL Output Timing                                         | 29 |

| 19 | Mode 3 RCLK/Start-of-Frame Timing                                |    |

| 20 | Mode 3 RCLK/End-of-Frame Timing                                  |    |

| 21 | Mode 3 Transmit Timing                                           |    |

| 22 | Mode 3 COL Output Timing                                         | 31 |

| 23 | Mode 4 RCLK/Start-of-Frame Timing                                |    |

| 24 | Mode 4 RCLK/End-of-Frame Timing                                  | 32 |

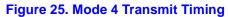

| 25 | Mode 4 Transmit Timing                                           | 33 |

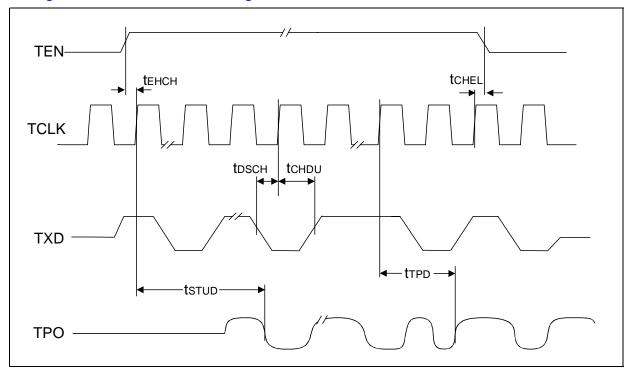

| 26 | Mode 4 COL Output Timing                                         |    |

| 27 | LXT905PC Package Specifications                                  | 34 |

| 28 | LXT905LC Package Specifications                                  | 35 |

| 29 | Ordering Information - Sample                                    | 37 |

|    | ·                                                                |    |

|    |                                                                  |    |

|    |                                                                  |    |

| 1  | LXT905 Signal Descriptions                                       | 9  |

| 2  | Controller Compatibility Mode Options                            |    |

| 3  | Loopback Modes                                                   |    |

| 4  | Suitable Crystals                                                |    |

| 5  | Absolute Maximum Values                                          |    |

| 6  | Recommended Operating Conditions                                 | 22 |

| 7  | I/O Electrical Characteristics                                   | 22 |

| 8  | TP Electrical Characteristics                                    | 23 |

| 9  | Switching Characteristics                                        | 23 |

| 10 | RCLK/Start-of-Frame Timing                                       | 24 |

| 11 | RCLK/End-of-Frame Timing                                         |    |

| 12 | Transmit Timing                                                  |    |

| 13 | Miscellaneous Timing                                             |    |

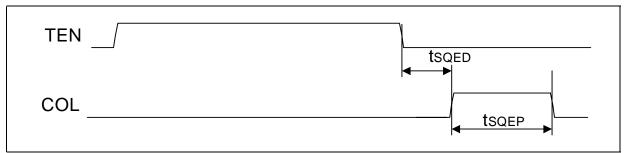

| 14 | PLASTIC LEADED CHIP CARRIER                                      |    |

| 15 | QUAD FLAT PACKAGE                                                |    |

| 16 | Product Information                                              |    |

# **Revision History**

| Date      | Revision | Page #                                        | Description                                                                                       |  |  |  |

|-----------|----------|-----------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

|           |          | 1                                             | New information under "Applications".                                                             |  |  |  |

|           |          | 1                                             | Added new carrier class information (paragraphs 3 and 4).                                         |  |  |  |

|           |          | 19                                            | Added +5V to Line Status, Figure 8.                                                               |  |  |  |

|           |          | 20                                            | Added +5V to Line Status, Figure 9.                                                               |  |  |  |

| June 2001 | 002      | 22                                            | Added second paragraph under Test Specifications "Note" regarding Quality and Reliability issues. |  |  |  |

|           |          | 22 Deleted Ambient operating temperatures fro |                                                                                                   |  |  |  |

|           |          | 34                                            | Added new diagram and table for LXT905PC/PE mechanical specifications.                            |  |  |  |

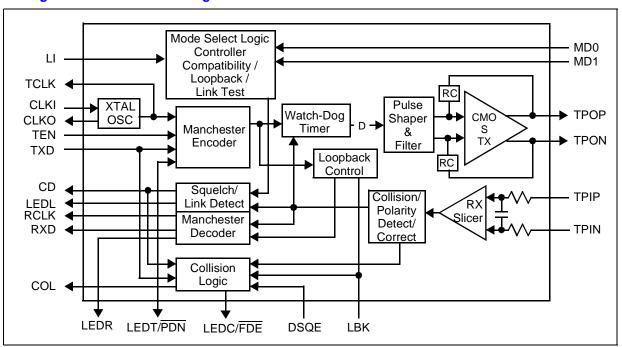

Figure 1. LXT905 Block Diagram

# 1.0 Pin Assignments and Signal Descriptions

Figure 2. LXT905 Pin Assignments

8

Table 1. LXT905 Signal Descriptions

| LQFP<br>Pin# | PLCC<br>Pin # | Symbol       | I/O | Description                                                                                                                                                                                                                                                                    |  |  |

|--------------|---------------|--------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 13           | 1             | VCC1         | _   |                                                                                                                                                                                                                                                                                |  |  |

| 20           | 22            | VCC2         | _   |                                                                                                                                                                                                                                                                                |  |  |

| 27           | _             | VCC3         | _   | <b>Power Inputs 1 thru 5.</b> Power supply inputs of 3.3V or 5V.                                                                                                                                                                                                               |  |  |

| 28           | _             | VCC4         | _   | 1171                                                                                                                                                                                                                                                                           |  |  |

| 29           | _             | VCC5         | _   |                                                                                                                                                                                                                                                                                |  |  |

| -            | 2             |              |     | 0 10 11 10 11 1                                                                                                                                                                                                                                                                |  |  |

| 30           | 2             | CLKI         | 1   | <b>Crystal Oscillator.</b> A 20 MHz crystal must be connected across these pins, or a 20 MHz clock applied at CLKI, with CLKO left open.                                                                                                                                       |  |  |

| 31           | 3             | CLKO         | 0   | 20 Will 2 Glock applied at OEKT, with OEKO lon open.                                                                                                                                                                                                                           |  |  |

| 11           | 15            | GND1         | _   |                                                                                                                                                                                                                                                                                |  |  |

| 12           | 23            | GND2         | -   | Ground.                                                                                                                                                                                                                                                                        |  |  |

| 21           | 4             | GND3         | _   | Glound.                                                                                                                                                                                                                                                                        |  |  |

| 32           | _             | GND4         | _   |                                                                                                                                                                                                                                                                                |  |  |

| 1            | 5             | LBK          | I   | <b>Loopback.</b> When High, forces internal loopback. Disables collision and the transmission of both data and link pulses. Pulled Low internally <sup>1</sup> .                                                                                                               |  |  |

| 2            | 6             | TEN          | I   | <b>Transmit Enable.</b> Enables data transmission and starts the Watch-Dog Timer (WDT). Synchronous to TCLK. Pulled Low internally <sup>1</sup> .                                                                                                                              |  |  |

| 3            | 7             | TCLK         | 0   | <b>Transmit Clock.</b> A 10 MHz clock output. This clock signal should be directly connected to the transmit clock input of the controller.                                                                                                                                    |  |  |

| 4            | 8             | TXD          | I   | <b>Transmit Data.</b> Input signal containing NRZ data to be transmitted on the network. TXD should be connected directly to the transmit data output of the controller. Pulled Low internally <sup>1</sup> .                                                                  |  |  |

| 5            | 9             | COL          | 0   | Collision Signal. Output that drives the collision detect input of the controller.                                                                                                                                                                                             |  |  |

|              |               |              |     | LED Collision or Full-Duplex Enable.                                                                                                                                                                                                                                           |  |  |

| 6            | 10            | LEDC/<br>FDE | 0   | LEDC is an open drain driver for the collision indicator pulls Low during collision.  LED "on" (which is Low output) time is extended by approximately 100 ms.  FDE enables full-duplex mode (external loopback) if tied Low externally. Pulled High internally <sup>1</sup> . |  |  |

|              |               |              |     | LED Transmit or Power Down.                                                                                                                                                                                                                                                    |  |  |

| 7            | 11            | LEDT/<br>PDN | 0   | LEDT is an open drain driver for the transmit indicator. LED "on" (which is Low output) time is extended by approximately 100 ms. Output is pulled Low during transmit. <sup>2</sup> If externally tied Low, the LXT905 goes to power down state (PDN). In power-              |  |  |

|              |               |              |     | down mode, all logic inputs and outputs are tristated.                                                                                                                                                                                                                         |  |  |

| 8            | 12            | LEDR         | 0   | <b>LED Receive.</b> Open drain driver for the receive indicator LED. LED "on" ( <i>i.e.</i> , Low output) time is extended by approximately 100 ms. Output is pulled Low during receive. Pulled High internally <sup>1</sup> .                                                 |  |  |

| 9            | 13            | LEDL         | 0   | <b>LED Link.</b> Open drain driver for link integrity indicator. Output is pulled Low during link test pass. Pulled High internally <sup>1</sup> .                                                                                                                             |  |  |

| 10           | 14            | CD           | 0   | <b>Carrier Detect.</b> An output for notifying the controller that activity exists on the network.                                                                                                                                                                             |  |  |

| 14           | 16            | RCLK         | 0   | Receive Clock. A recovered 10 MHz clock that is synchronous to the received data and connected to the controller receive clock input.                                                                                                                                          |  |  |

| 15           | 17            | RXD          | 0   | <b>Receive Data.</b> Output signal connected directly to the receive data input of the controller.                                                                                                                                                                             |  |  |

<sup>1.</sup> Externally pull-up or pull-down each pin separately using a 10k  $\Omega$ , 1% termination resistor or tie directly to Vcc or ground. 2. Do not allow this pin to float. If unused, tie High.

**Datasheet**

9

Table 1. LXT905 Signal Descriptions (Continued)

| LQFP<br>Pin # | PLCC<br>Pin # | Symbol | I/O | Description                                                                                                                                                                                                                               |  |  |  |

|---------------|---------------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 16            | 18            | LI     | I   | Link Enable. Controls link integrity test; enabled when LI is High, disabled when LI is Low.                                                                                                                                              |  |  |  |

| 17            | 19            | RBIAS  | I   | <b>Bias Circuitry.</b> A 7.5 kW 1% resistor to ground at this pin controls operating circuit bias.                                                                                                                                        |  |  |  |

| 18            | 20            | DSQE   | I   | <b>SQE Disable.</b> When DSQE is High, the SQE function is disabled. When DSQE is Low, the SQE function is enabled. SQE should be disabled for normal operation in Hub/Switch/Repeater applications. Pulled Low internally <sup>1</sup> . |  |  |  |

| 19            | 21            | TPOP   | 0   | Twisted-Pair Outputs. Differential outputs to the twisted-pair cable. The                                                                                                                                                                 |  |  |  |

| 22            | 24            | TPON   | 0   | outputs are pre-equalized.                                                                                                                                                                                                                |  |  |  |

| 23            | 25            | MDO    | I   | Mode Select 0 and 1. Mode select pins determine controller compatibility mode                                                                                                                                                             |  |  |  |

| 24            | 26            | MDI    | I   | in accordance with Table 2. Pulled Low internally 1.                                                                                                                                                                                      |  |  |  |

| 25            | 27            | TPIP   | I   | Twisted-Pair Inputs. A differential input pair from the twisted-pair cable.                                                                                                                                                               |  |  |  |

| 26            | 28            | TPIN   | I   | Receive filter is integrated on-chip. No external filters are required.                                                                                                                                                                   |  |  |  |

<sup>1.</sup> Externally pull-up or pull-down each pin separately using a 10k  $\Omega$ , 1% termination resistor or tie directly to Vcc or ground.

# 2.0 Functional Description

# 2.1 Introduction

The LXT905 Universal 10BASE-T Transceiver performs the physical layer signaling (PLS) and Media Attachment Unit (MAU) functions, as defined by the IEEE 802.3 specification. It functions as an integrated PLS/MAU for use with 10BASE-T twisted-pair networks.

The LXT905 interfaces a back-end controller to a twisted-pair (TP) cable. The controller interface includes a transmit and receive clock and NRZ data channels, as well as mode control logic and signaling. The twisted-pair interface comprises two circuits: Twisted-Pair Input (TPI) and Twisted-Pair Output (TPO). In addition to the two basic interfaces, the LXT905 contains an internal crystal oscillator and four LED drivers for visual status reporting.

Functions are defined from the back-end controller side of the interface. The LXT905 Transmit function refers to data transmitted by the back-end to the twisted-pair network The LXT905 Receive function refers to data received by the back-end from the twisted-pair network. The LXT905 performs all required functions defined by the IEEE 802.3 10BASE-T MAU specification, such as collision detection, link integrity testing, signal quality error messaging, jabber control, and loopback.

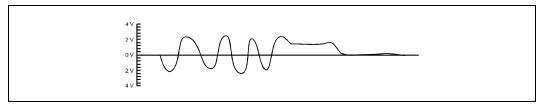

Figure 3. LXT905 TPO Output Waveform

10 Datasheet

<sup>2.</sup> Do not allow this pin to float. If unused, tie High.

# 2.2 Controller Compatibility Modes

The LXT905 is compatible with most industry standard controllers, including devices produced by Advanced Micro Devices (AMD), Intel, Fujitsu, National Semiconductor, Seeq, Motorola, and Texas Instruments. Four different control signal timing and polarity schemes (Modes 1 through 4) are required to achieve this compatibility. Mode select pins MD0 and MD1 determine controller compatibility modes as listed in Table 2. Refer to the Test Specifications section for timing diagrams and parameters.

## 2.3 Transmit Function

The LXT905 receives NRZ data from the controller at the TXD input, as shown in the block diagram, and passes it through a Manchester encoder. The encoded data is then transferred to the twisted-pair network (TPO circuit). The advanced integrated pulse shaping and filtering network produces the output signal on TPON and TPOP, as shown in Figure 3 on page 10. The TPO output is pre-distorted and pre-filtered to meet the 10BASE-T jitter template. An internal, continuous resistor-capacitor filter is used to remove any high-frequency clocking noise from the pulse shaping circuitry. Integrated filters simplify the design work required for FCC compliant EMI performance. During idle periods, the LXT905 transmits link integrity test pulses on the TPO circuit (if LI is enabled and LBK is disabled).

# **Table 2. Controller Compatibility Mode Options**

| Controller Mode                                                                          | MD1  | MD0  |

|------------------------------------------------------------------------------------------|------|------|

| Mode 1 - For Motorola MC68EN360 or compatible controllers (AMD AM7990)                   | Low  | Low  |

| Mode 2 - For Intel 82596 or compatible controllers <sup>1</sup>                          | Low  | High |

| Mode 3 - For Fujitsu MB86950, MB86960 or compatible controllers (Seeq 8005) <sup>2</sup> | High | Low  |

| Mode 4 - For TI TMS380C26 or compatible controllers                                      | High | High |

Refer to Intel Application Note 51 (MAC Interface Design Guide for Intel Controllers) when designing with Intel controllers.

<sup>2.</sup> SEEQ controllers require inverters on CLKI, LBK, RCLK and COL.

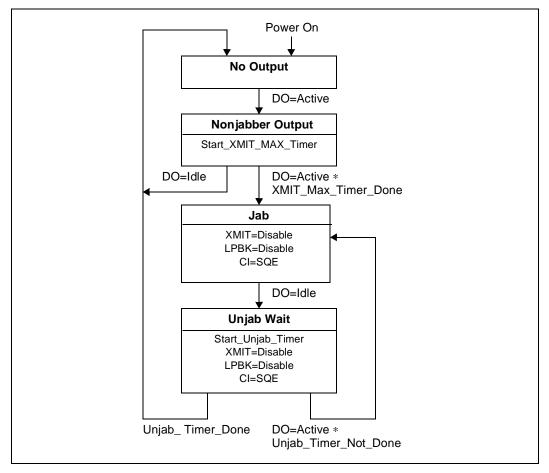

# 2.4 Jabber Control Function

Figure 4 is a state diagram of the LXT905 jabber control function. The LXT905 on-chip Watch-Dog Timer (WDT) prevents the DTE from locking into a continuous transmit mode. When a transmission exceeds the time limit, the WDT disables the transmit and loopback functions and activates the COL pin. Once the LXT905 is in the jabber state, the TXD circuit must remain idle for a period of 0.25 to 0.75 seconds before it exits the jabber state.

Figure 4. Jabber Control Function

12 Datasheet

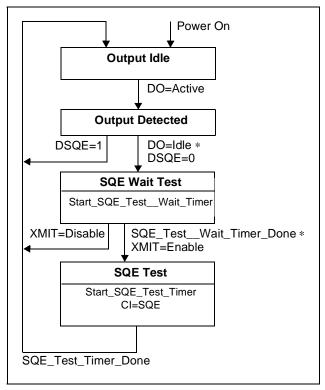

# 2.5 SQE Function

The LXT905 supports the Signal Quality Error (SQE) function as shown in Figure 5. After every successful transmission on the 10BASE-T network, the LXT905 transmits the SQE signal for 10 bit times (BT)  $\pm$  5BT on the COL pin of the device.

The SQE can be disabled for repeater/switch applications. When DSQE is set High, the SQE function is disabled. When DSQE is Low, the SQE function is enabled.

Figure 5. SQE Function

## 2.6 Receive Function

The LXT905 receive function acquires timing and data from the twisted-pair network (TPI circuit). Valid received signals are passed through the on-chip filters and Manchester decoder, then output as decoded NRZ data and receive timing on the RXD and RCLK pins, respectively.

An internal RC filter and an intelligent squelch function discriminate noise from link test pulses and valid data streams. The receive function is activated only by valid data streams above the squelch level with proper timing.

If the differential signal at the TPI circuit inputs falls below 85 percent of the threshold level (unsquelched) for 8 bit times (typical), the LXT905 receive function enters the idle state. The LXT905 automatically corrects reversed polarity on the TPI circuit.

# 2.7 Polarity Reverse Function

The LXT905 polarity reverse function uses both link pulses and end-of-frame data to determine polarity of the received signal. If Link Integrity testing is disabled, polarity detection is based only on received data. A reversed polarity condition is detected when eight consecutive opposite receive link pulses are detected without receipt of a link pulse of the expected polarity. Reversed polarity is also detected if four consecutive frames are received with a reversed start-of-idle. Whenever a correct polarity frame or a correct link pulse is received, these two counters are reset to zero. If the LXT905 enters the link fail state and no valid data or link pulses are received within 96 to 128 ms, the polarity is reset to the default non-flipped condition. Polarity correction is always enabled.

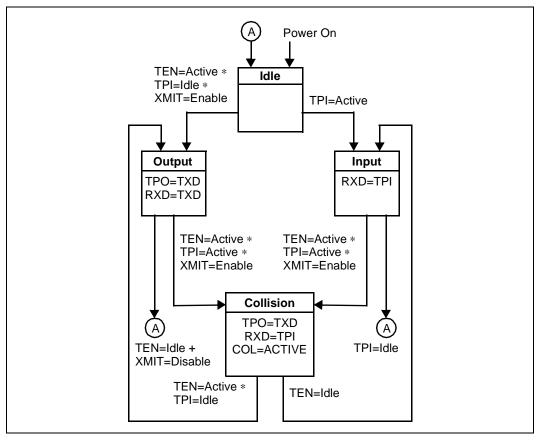

# 2.8 Collision Detection Function

A collision is defined as the simultaneous presence of valid signals on both the TPI circuit and the TPO circuit. The LXT905 reports collisions to the back-end via the COL pin. If the TPI circuit becomes active while there is activity on the TPO circuit, the TPI data is passed to the back-end over the RXD circuit, disabling normal loopback. Figure 6 is a state diagram of the LXT905 collision detection function.

**Figure 6. Collision Detection Function**

14 Datasheet

# 2.9 Loopback Functions

# 2.9.1 Internal Loopback

The LXT905 provides standard loopback mode as specified in the IEEE specification for the twisted-pair port, as well as a forced internal loopback mode. Loopback mode operates in conjunction with the transmit function. Data transmitted by the MAC is internally looped back within the LXT905 from the TXD pin through the Manchester encoder/decoder to the RXD pin and returned to the MAC.

Standard loopback mode is disabled when a data collision occurs, clearing the RXD circuit for the TPI data. Standard loopback is also disabled during link fail, jabber, and full-duplex states. Loopback is always enabled during forced internal loopback mode.

## 2.9.2 External Loopback/Full Duplex

The LXT905 also provides an external loopback test mode for system-level testing. When both LEDC/FDE and LBK are Low, the LXT905 enables external loopback and full-duplex mode. Internal loopback circuits, SQE, and collision detection are disabled. Refer to Table 3 for a summary of loopback and duplex modes.

## Table 3. Loopback Modes

| Pin S | ettings      |                                                                                                                       |  |  |  |  |  |

|-------|--------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| LBK   | LEDC/<br>FDE | Mode Description                                                                                                      |  |  |  |  |  |

| Low   | Low          | Disable internal loopback.                                                                                            |  |  |  |  |  |

| LOW   | LOW          | Enable external loopback test mode and full-duplex mode.                                                              |  |  |  |  |  |

|       |              | Standard loopback mode (default).                                                                                     |  |  |  |  |  |

| Low   | High         | Data transmitted by the MAC is internally looped back and returned to the MAC except during collision.                |  |  |  |  |  |

|       |              | Standard loopback is disabled when a data collision occurs, clearing RXD for data on the twisted-pair port.           |  |  |  |  |  |

| High  | Low          | Not Used.                                                                                                             |  |  |  |  |  |

| High  | High         | Forced internal loopback.  Transmit data is looped back on the receive data bus and the twisted-pair port is ignored. |  |  |  |  |  |

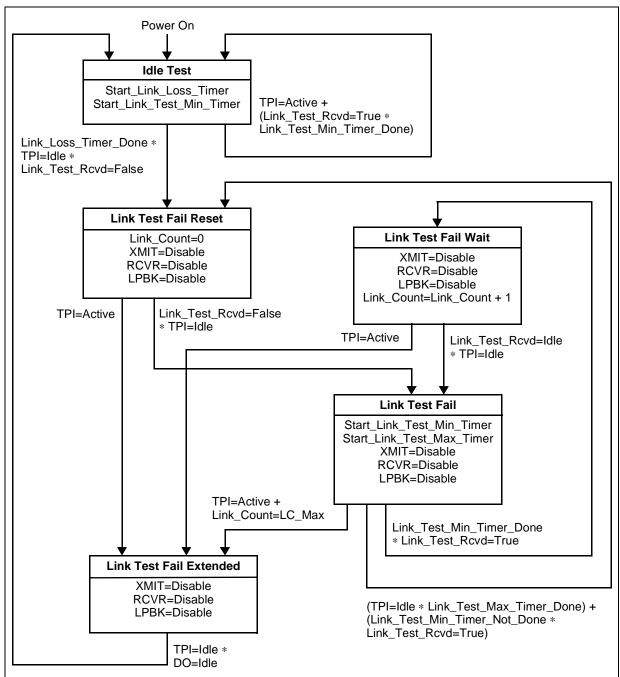

# 2.10 Link Integrity Test Function

Figure 7 on page 16 is a state diagram of the LXT905 Link Integrity test function. The link integrity test is used to determine the status of the receive side twisted-pair cable. Link integrity testing is enabled when LI is tied High. When enabled, the receiver recognizes link integrity pulses which are transmitted in the absence of receive traffic. If no serial data stream or link integrity pulses are detected within 50~150 ms, the chip enters a link fail state and disables the transmit and normal loopback functions. The LXT905 ignores any link integrity pulse with interval less than 2~7 ms. The LXT905 remains in the link fail state until it detects either a serial data packet or two or more link integrity pulses.

Figure 7. Link Integrity Test Function

#### **Application Information** 3.0

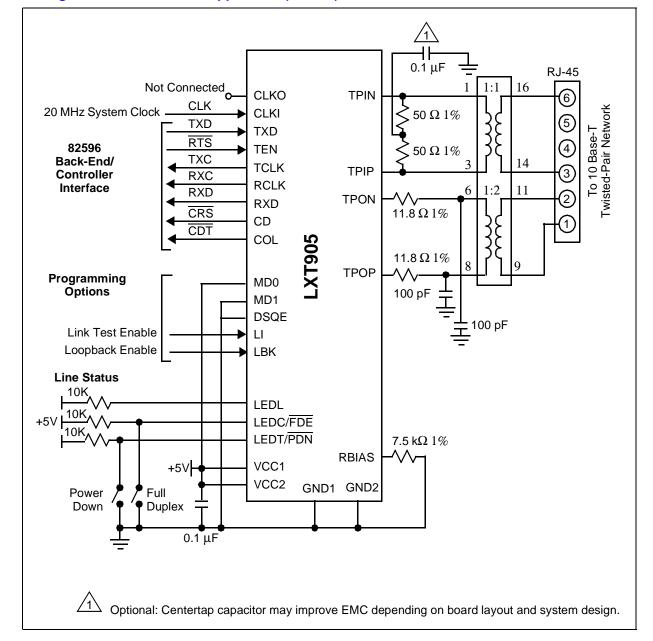

#### 3.1 Introduction

Figure 8 on page 19 through Figure 10 on page 21 show typical LXT905 applications. These diagrams group similar pins; they do not portray the actual chip pinout. The controller interface pins; Transmit Data (TXD), Transmit Clock (TCLK) Transmit Enable (TEN), Receive Data (RXD), Receive Clock (RCLK), Collision Signal (COL), and Carrier Detect (CD) pins are at the upper left of the diagram.

Power and ground pins are at the bottom of each diagram. VCC1 and VCC2 use a single power supply with decoupling capacitors installed between the power and ground busses. VCC may be powered by a 5V or 3.3V supply.

#### 3.1.1 **Termination Circuitry**

Several I/O pins are pulled-up or pulled-down internally to keep the signals from floating. It is recommended to hard-wire these pins either High or Low. Externally pull-up pins (LEDT/PDN, LEDC/FDE, LEDR, LEDL) and pull-down pins (LBK, TEN, TXD, DSQE, MDO, MDI) separately using a 10k  $\Omega$ , 1% resistor, or tie directly to VCC or ground.

#### 3.1.2 **Twisted-Pair Interface**

The Twisted-Pair interface (TPOP/N and TPIP/N) is at the upper right of the diagram. The I/O pairs have impedance-matching resistors for  $100\Omega$  UTP, but no external filters are required.

#### 3.1.3 **RBIAS Pin**

The RBIAS pin sets the levels for the LXT905 output drivers. The LXT905 requires a 7.5k  $\Omega$ , 1% resistor directly connected between the RBIAS pin and ground. This resistor should be located as close to the device as possible. Keep the traces as short as possible and isolated from all other high speed signals.

#### 3.1.4 **Crystal Information**

Based on limited evaluation, Table 4 lists some suitable crystals. Designers should test and validate all crystals before committing to a specific component.

## Table 4. Suitable Crystals

| Manufacturer | Part Number |

|--------------|-------------|

| MTRON        | MP-1        |

| WITKON       | MP-2        |

17

# 3.1.5 Magnetic Information

The LXT905 requires a 1:1 turns ratio for the receive transformer and a 1:2 turns ratio for the transmit transformer. Application Note 073, Magnetic Manufacturers (248991-001) lists transformers suitable for the applications described in this data sheet. Designers are advised to test and validate all magnetics before committing to a specific component.

# 3.2 Typical 10BASE-T Application

Figure 8 on page 19 is a typical LXT905 application. The DTE is connected to a 10BASE-T network through the twisted-pair RJ-45 connector. With MD0 tied high and MD1 grounded, the LXT905 logic and framing are set to Mode 2 (compatible with Intel 82596 controllers\*). Connect a 20 MHz system clock input at CLKI (leave CLKO open). The LI pin externally controls the link test function.

\* Refer to Intel Application Note 51, MAC Interface Design Guide for Intel Controllers (249007-001) when designing with Intel controllers.

18 Datasheet

Figure 8. Intel Controller Application (Mode 2)

# 3.3 Dual Network Support - 10BASE-T and Token Ring

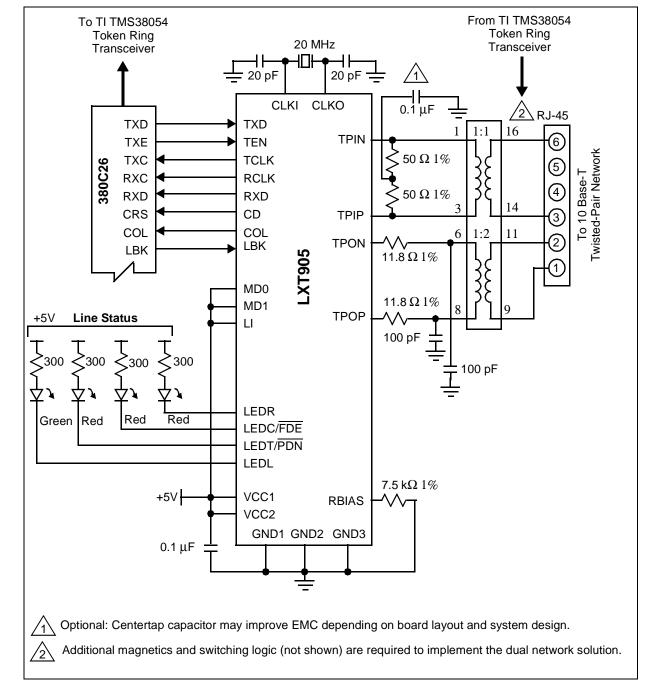

Figure 9 on page 20 shows the LXT905 with a Texas Instruments 380C26 CommProcessor. The 380C26 is compatible with Mode 4 (MD0 and MD1 both high). When used with the 380C26, both the LXT905 and a TMS38054 Token Ring transceiver can be tied to a single RJ-45 allowing dual network support from a single connector.

Figure 9. LXT905/380C26 Interface for Dual 10BASE-T and Token Ring Support (Mode 4)

# 3.4 Simple 10BASE-T Connection

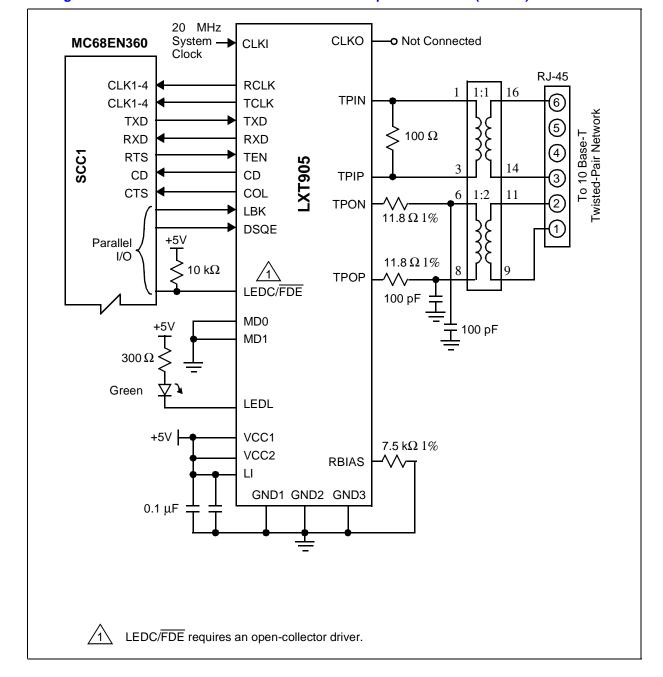

Figure 10 shows a simple 10BASE-T application using an LXT905 transceiver and a Motorola MC68EN360. The MC68EN360 is compatible with Mode 1 (MD0 and MD1 both Low).

Figure 10. LXT905/MC68EN360 Interface for Full-Duplex 10BASE-T (Mode 1)

# 4.0 Test Specifications

Note: The minimum and maximum values in Table 5 through Table 13 on page 25 and Figure 11 on page 26 through Figure 26 on page 33 represent the performance specifications of the LXT905 and are guaranteed by test, except where noted by design. Minimum and maximum values in Table 7 through Table 13 on page 25 apply over the recommended operating conditions specified in Table 6.

For all Quality and Reliability issues (for example, parts packaging and thermal specifications), please send your questions to Intel at the following e-mail address: qr.requests@intel.com.

### Table 5. Absolute Maximum Values

| Parameter           | Symbol | Min  | Max  | Units |

|---------------------|--------|------|------|-------|

| Supply voltage      | Vcc    | -0.3 | +6   | V     |

| Storage temperature | Тѕт    | -65  | +150 | °C    |

tion: Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### **Table 6. Recommended Operating Conditions**

| Parameter                                                    | Symbol | Min   | Тур                                                           | Max  | Units |  |  |  |  |  |

|--------------------------------------------------------------|--------|-------|---------------------------------------------------------------|------|-------|--|--|--|--|--|

| Recommended supply voltage <sup>1</sup>                      | Vcc    | 3.135 | 5.0                                                           | 5.25 | V     |  |  |  |  |  |

| Recommended operating temperature (Commercial)               | Тор    | 0     | -                                                             | +70  | °C    |  |  |  |  |  |

| Recommended operating temperature (Extended)                 | Тор    | -40   | -                                                             | +85  | °C    |  |  |  |  |  |

| 1. Voltage is with respect to ground unless specified otherw | vise.  |       | Voltage is with respect to ground unless specified otherwise. |      |       |  |  |  |  |  |

### Table 7. I/O Electrical Characteristics

| Parameter                                     |                 | Sym  | Min | Typ <sup>1</sup> | Max | Units | Test Conditions |

|-----------------------------------------------|-----------------|------|-----|------------------|-----|-------|-----------------|

| Input low voltag                              | e <sup>2</sup>  | VIL  | _   | -                | 0.8 | V     |                 |

| Input high voltage                            | ge <sup>2</sup> | ViH  | 2.0 | -                | _   | V     |                 |

| Output low voltage                            |                 | Vol  | _   | _                | 0.4 | V     | IOL = 1.6 mA    |

|                                               |                 | Vol  | _   | -                | 10  | %Vcc  | IOL < 10 μA     |

| Output low voltage<br>(Open drain LED driver) |                 | Voll | -   | -                | 0.7 | %Vcc  | IOLL = 10 mA    |

| Output high volt                              | 2000            | Voн  | 2.4 | _                | _   | V     | Іон = 40 μΑ     |

| Output high voltage                           |                 | Voн  | 90  | _                | _   | %Vcc  | IOH < 10 μA     |

| Output rise                                   | CMOS            | -    | _   | 3                | 15  | ns    | CLOAD = 20 pF   |

| time<br>TCLK & RCLK                           | TTL             | _    | ı   | 2                | 15  | ns    |                 |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only, are not guaranteed, and are not subject to production testing.

22 Datasheet

<sup>2.</sup> Limited functional tests are performed at these input levels. The majority of functional tests are performed at levels of 0V and 3V. This applies to all inputs except TPIP and TPIN.

Table 7.

I/O Electrical Characteristics (Continued)

| Para                               | meter              | Sym | Min | Typ <sup>1</sup> | Max   | Units | Test Conditions    |

|------------------------------------|--------------------|-----|-----|------------------|-------|-------|--------------------|

| Output fall                        | CMOS               | _   | _   | 3                | 15    | ns    | CLOAD= 20 pF       |

| time<br>TCLK & RCLK                | TTL                | _   | _   | 2                | 15    | ns    |                    |

| CLKI rise time (externally driven) |                    | -   | -   | -                | 10    | ns    |                    |

| CLKI duty cycle driven)            | (externally        | -   | -   | 50/50            | 40/60 | %     |                    |

|                                    | Normal Mode        | Icc | _   | 40               | 80    | mA    | Idle Mode          |

| Supply current                     |                    | Icc | _   | 70               | 100   | mA    | Transmitting on TP |

| ,                                  | Power Down<br>Mode | Icc | -   | 0.01             | 1     | μА    |                    |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only, are not guaranteed, and are not subject to production testing.

## **Table 8. TP Electrical Characteristics**

| Parameter                                                                | Symbol | Min | Typ <sup>1</sup> | Max  | Units | Test Conditions                                                             |

|--------------------------------------------------------------------------|--------|-----|------------------|------|-------|-----------------------------------------------------------------------------|

| Transmit output impedance                                                | Zout   | _   | 5                | -    | Ω     | _                                                                           |

| Transmit timing jitter addition <sup>2</sup>                             | -      | _   | ±6.4             | ±10  | ns    | 0 line length for internal MAU                                              |

| Transmit timing jitter added by the MAU and PLS sections <sup>2, 3</sup> | -      | -   | ±3.5             | ±5.5 | ns    | After line model<br>specified by IEEE 802.3<br>for 10BASE-T internal<br>MAU |

| Receive input impedance                                                  | ZIN    | _   | 24               | -    | kΩ    | Between TPIP/TPIN                                                           |

| Differential squelch threshold                                           | VDS    | 300 | 420              | 585  | mV    | 5 MHz square wave input                                                     |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only, are not guaranteed, and are not subject to production testing.

## Table 9. Switching Characteristics

| F              | Parameter              | Symbol | Minimum | Typical <sup>1</sup> | Maximum | Units |

|----------------|------------------------|--------|---------|----------------------|---------|-------|

| Jabber Timing  | Maximum transmit time  | _      | 20      | _                    | 150     | ms    |

| Jabber Tilling | Unjab time             | _      | 250     | _                    | 750     | ms    |

|                | Time link loss receive | _      | 50      | _                    | 150     | ms    |

| Link Integrity | Link min receive       | _      | 2       | _                    | 7       | ms    |

| Timing         | Link max receive       | _      | 50      | _                    | 150     | ms    |

|                | Link transmit period   | _      | 8       | 10                   | 24      | ms    |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only, are not guaranteed, and are not subject to production testing.

Datasheet 23

<sup>2.</sup> Limited functional tests are performed at these input levels. The majority of functional tests are performed at levels of 0V and 3V. This applies to all inputs except TPIP and TPIN.

<sup>2.</sup> Parameter is guaranteed by design; not subject to production testing.

<sup>3.</sup> IEEE 802.3 specifies maximum jitter additions at 0.5 ns from the encoder, and 3.5 ns from the MAU.

Table 10. RCLK/Start-of-Frame Timing

| Paramete                                    | Symbol            | Min   | <b>Typ</b> <sup>1</sup> | Max  | Units |    |

|---------------------------------------------|-------------------|-------|-------------------------|------|-------|----|

| Decoder acquisition time                    |                   | tdata | _                       | 1300 | 1500  | ns |

| CD turn-on delay                            |                   | tCD   | -                       | 400  | 550   | ns |

| Receive data setup from                     | Mode 1            | trds  | 60                      | 70   | -     | ns |

| RCLK                                        | Modes 2, 3, and 4 | trds  | 30                      | 45   | _     | ns |

| Receive data hold from RCLK                 | Mode 1            | trdh  | 10                      | 20   | -     | ns |

| Modes 2, 3, and 4                           |                   | trdh  | 30                      | 45   | _     | ns |

| RCLK shut off delay from CD assert (Mode 3) |                   | tsws  | -                       | ±100 | _     | ns |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only, are not guaranteed, and are not subject to production testing.

# Table 11. RCLK/End-of-Frame Timing

| Parameter                                    | Туре                 | Sym    | Mode 1 | Mode 2 | Mode 3    | Mode 4 | Units |

|----------------------------------------------|----------------------|--------|--------|--------|-----------|--------|-------|

| RCLK after CD off                            | Min                  | trc    | 5      | 1      | _         | 5      | ВТ    |

| Rcv data through-put delay                   | Max                  | trd    | 400    | 375    | 375       | 375    | ns    |

| CD turn-off delay <sup>2</sup>               | Max                  | tCDOFF | 500    | 475    | 475       | 475    | ns    |

| Receive block out after TEN off <sup>3</sup> | Typical <sup>1</sup> | tıFG   | 5      | 50     | -         | -      | ВТ    |

| RCLK switching delay after CD off            | Typical <sup>1</sup> | tswe   | -      | -      | 120 (±80) | -      | ns    |

<sup>1.</sup> Typical figures are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

## **Table 12. Transmit Timing**

| Parameter                  | Symbol | Minimum | Typical <sup>1</sup> | Maximum | Units |

|----------------------------|--------|---------|----------------------|---------|-------|

| TEN setup from TCLK        | tEHCH  | 22      | -                    | -       | ns    |

| TXD setup from TCLK        | tDSCH  | 22      | -                    | _       | ns    |

| TEN hold after TCLK        | tCHEL  | 5       | -                    | _       | ns    |

| TXD hold after TCLK        | tCHDU  | 5       | -                    | _       | ns    |

| Transmit start-up delay    | tstud  | -       | 350                  | 450     | ns    |

| Transmit through-put delay | tTPD   | -       | 338                  | 350     | ns    |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only, are not guaranteed, and are not subject to production testing.

24 Datasheet

<sup>2.</sup> CD Turnoff delay measured from middle of last bit: timing specification is unaffected by the value of the last

<sup>3.</sup> Blocking of Carrier Detect is disabled during full-duplex operation.

# **Table 13. Miscellaneous Timing**

| Parameter                                  | Symbol | Minimum | Typical <sup>1</sup> | Maximum | Units |

|--------------------------------------------|--------|---------|----------------------|---------|-------|

| COL (SQE) Delay after TEN off <sup>2</sup> | tsqed  | 0.65    | -                    | 1.6     | μς    |

| COL (SQE) Pulse Duration <sup>2</sup>      | tSQEP  | 500     | -                    | 1500    | ns    |

| Power Down recovery time                   | tpdr   | _       | 25                   | _       | ms    |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only, are not guaranteed, and are not subject to production testing.

2. When SQE is enabled (DSQE is Low).

# 4.1 Timing Diagrams for Mode 1 (MD1 = Low, MD0 = Low) Figures 11 - 14

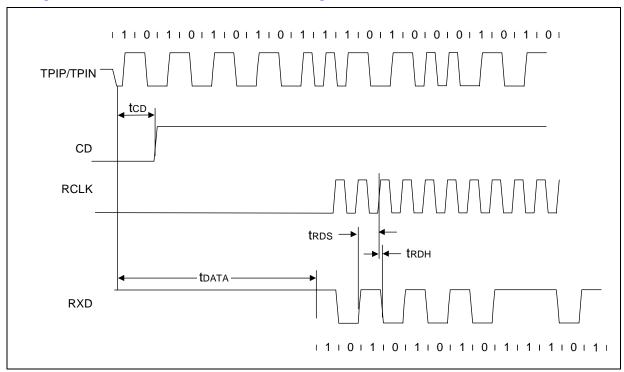

Figure 11. Mode 1 RCLK/Start-of-Frame Timing

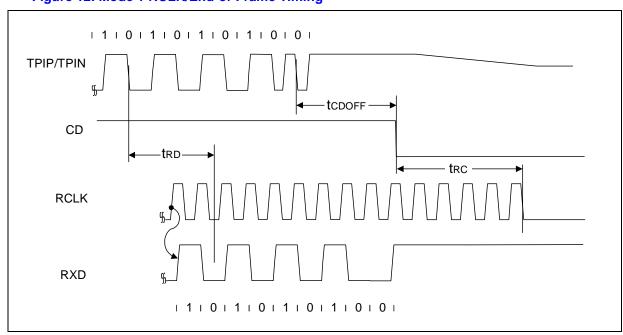

Figure 12. Mode 1 RCLK/End-of-Frame Timing

Figure 14. Mode 1 COL Output Timing

# 4.2 Timing Diagrams for Mode 2 (MD1 = Low, MD0 = High) Figures 15 - 18

Figure 15. Mode 2 RCLK/Start-of-Frame

Figure 16. Mode 2 RCLK/End-of-Frame Timing

Figure 17. Mode 2 Transmit Timing

Figure 18. Mode 2 COL Output Timing

# 4.3 Timing Diagrams for Mode 3 (MD1 = High, MD0 = Low) Figures 19 - 22

Figure 19. Mode 3 RCLK/Start-of-Frame Timing

Figure 20. Mode 3 RCLK/End-of-Frame Timing

Figure 21. Mode 3 Transmit Timing

Figure 22. Mode 3 COL Output Timing

# 4.4 Timing Diagrams for Mode 4 (MD1 = High, MD0 = High) Figures 23 - 26

Figure 23. Mode 4 RCLK/Start-of-Frame Timing

Figure 24. Mode 4 RCLK/End-of-Frame Timing

Figure 26. Mode 4 COL Output Timing

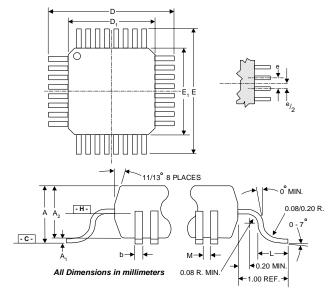

# 5.0 Mechanical Specifications

Figure 27. LXT905PC Package Specifications

| Dim            | Inches<br>Dim |       | Millin | neters |

|----------------|---------------|-------|--------|--------|

|                | Min           | Max   | Min    | Max    |

| Α              | 0.165         | 0.180 | 4.191  | 4.572  |

| A <sub>1</sub> | 0.090         | 0.120 | 2.286  | 3.048  |

| A <sub>2</sub> | 0.062         | 0.083 | 1.575  | 2.108  |

| В              | 0.050         | -     | 1.270  | -      |

| С              | 0.026         | 0.032 | 0.660  | 0.813  |

| D              | 0.485         | 0.495 | 12.319 | 12.573 |

| D <sub>1</sub> | 0.450         | 0.456 | 11.430 | 11.582 |

| F              | 0.013         | 0.021 | 0.330  | 0.533  |

Figure 28. LXT905LC Package Specifications

## 32-Pin LQFP

- Part Number LXT905LC (Commercial Temperature Range)

- Part Number LXT905LE (Extended Temperature Range)

**Table 15. QUAD FLAT PACKAGE**

| Dim.           | AII E          | meters    |      |         |  |

|----------------|----------------|-----------|------|---------|--|

| Diiii.         | Min.           | Тур.      | Max. | Notes   |  |

| Α              |                |           | 1.60 |         |  |

| A <sub>1</sub> | 0.05           | 0.10      | 0.15 |         |  |

| A <sub>2</sub> | 1.35           |           |      |         |  |

| D              |                | 5         |      |         |  |

| D <sub>1</sub> |                | 7.00 BSC. |      |         |  |

| Е              |                | 9.00 BSC  | ;    | 5       |  |

| E <sub>1</sub> |                | 7.00 BSC  | ;    | 6, 7, 8 |  |

| L              | 0.45           | 0.60      | 0.75 |         |  |

| М              | 0.15           |           |      |         |  |

| b              | 0.30 0.37 0.45 |           |      | 9       |  |

| е              |                |           |      |         |  |

### NOTES:

- 1. All dimensions are in millimeters.

- 2. This package conforms to JEDEC publication 95 registration MO-136, variation BC.

- Datum plane -H- located at mold parting line and is coincident with leads where leads exit plastic body at bottom of parting line.

- 4. Measured at seating plane -C-.

- 5. Measured at datum plane -H-.

- 6. Dimensions D1 and E1 do not include mold protrusion. Allowable mold protrusion is 0.254 mm.

- Package top dimensions are smaller than bottom dimensions. Top of package will not overhang bottom of package.

- Dimension b does not include dambar protrusion.

Allowable dambar protrusion is no more than 0.08 mm.

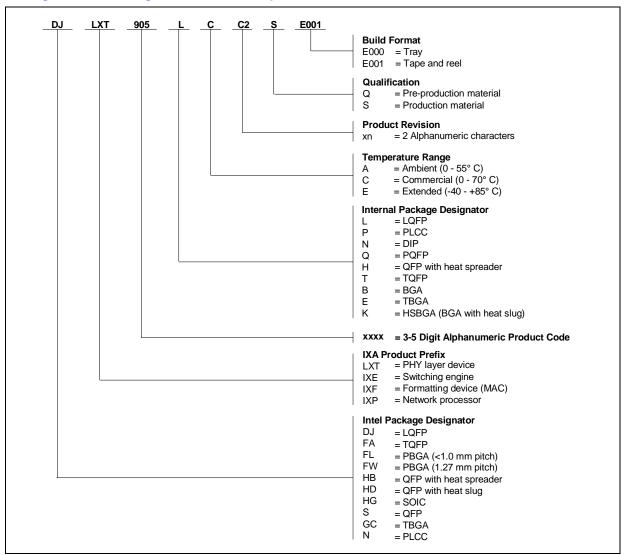

# **Appendix A Ordering Information**

**Table 16. Product Information**

| Number        | Revision | Qualification | Tray MM | Tape & Reel MM |

|---------------|----------|---------------|---------|----------------|

| DJLXT905LC.C2 | C2       | S             | 831645  | 831804         |

| NLXT905PC.C2  | C2       | S             | 831661  | 831817         |

| DJLXT905LE.C2 | C2       | S             | 831646  | 831805         |

| NLXT905PE.C2  | C2       | S             | 831662  | 831818         |

Figure 29. Ordering Information - Sample

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

## Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.