## Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

November 2010

# FAN5234 Dual Mobile-Friendly PWM / PFM Controller

## **Features**

- Wide Input Voltage Range for Mobile Systems: 2V to 24V

- Excellent Dynamic Response with Voltage Feed-Forward and Average-Current-Mode Control

- Lossless Current Sensing on Low-Side MOSFET or Precision Over-Current via Sense Resistor

- V<sub>CC</sub> Under-Voltage Lockout

- Power-Good Signal

- Light-Load Hysteretic Mode Maximizes Efficiency

- 300KHz or 600KHz Operation

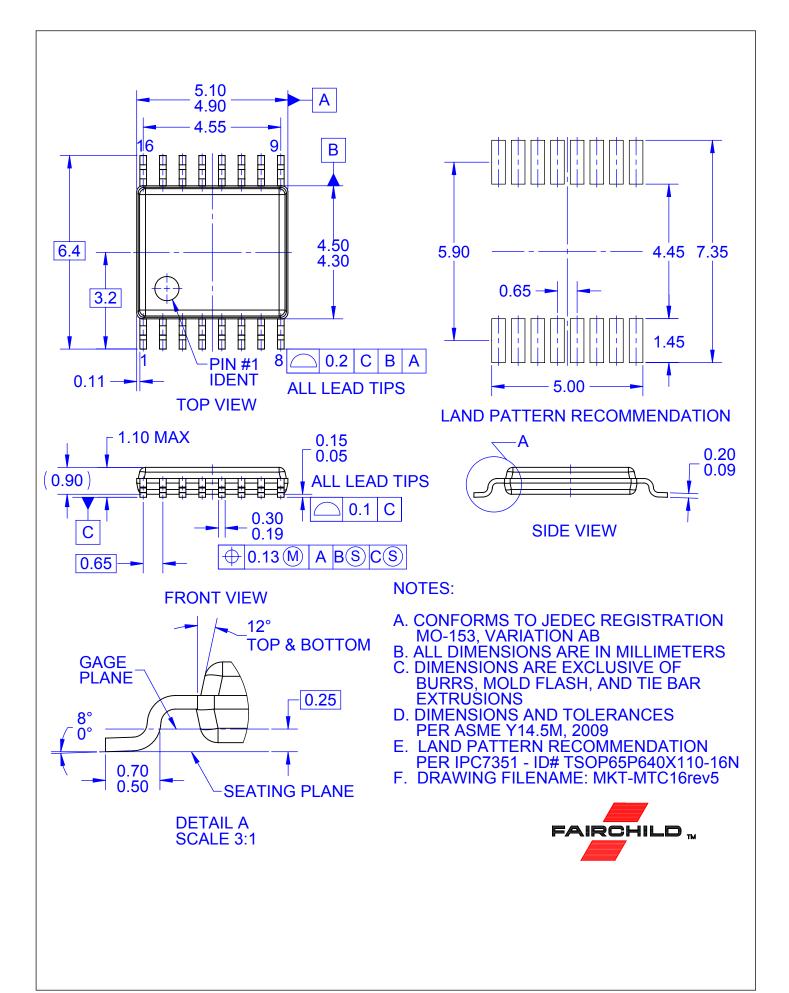

- TSSOP16 Package

# **Applications**

- Mobile PC Regulator

- Handheld PC Power

#### **Related Resources**

- Application Note AN-6002 Component Calculations and Simulation Tools for FAN5234 or FAN5236

- Application Note AN-1029 Maximum Power Enhancement Techniques for SO-8 Power MOSFET

# Description

The FAN5234 PWM controller provides high efficiency and regulation with an adjustable output from 0.9V to 5.5V required to power I/O, chip-sets, memory banks, or peripherals in high-performance notebook computers, PDAs, and internet appliances. Synchronous rectification and hysteretic operation at light loads contribute to a high efficiency over a wide range of loads. The Hysteretic Mode of operation can be disabled if PWM Mode is desired for all load levels. Efficiency is further enhanced by using the MOSFET's  $R_{\text{DS(ON)}}$  as a current-sense component.

Feed-forward ramp modulation, average current mode control, and internal feedback compensation provide fast response to load transients. The FAN5234 monitors these outputs and generates a PGOOD (power-good) signal when the soft-start is completed and the output is within ±10% of its set point. A built-in over-voltage protection prevents the output voltage from going above 120% of the set point. Normal operation is automatically restored when the over-voltage conditions cease. Under-voltage protection latches the chip off when the output drops below 75% of its set value after the soft-start sequence is completed. An adjustable over-current function monitors the output current by sensing the voltage drop across the lower MOSFET.

# **Ordering Information**

| Part Number | Operating<br>Temperature<br>Range | Package                                            | Packing Method |

|-------------|-----------------------------------|----------------------------------------------------|----------------|

| FAN5234MTCX | -10 to +85°C                      | 16-Lead, Thin-Shrink Small-Outline Package (TSSOP) | Tape and Reel  |

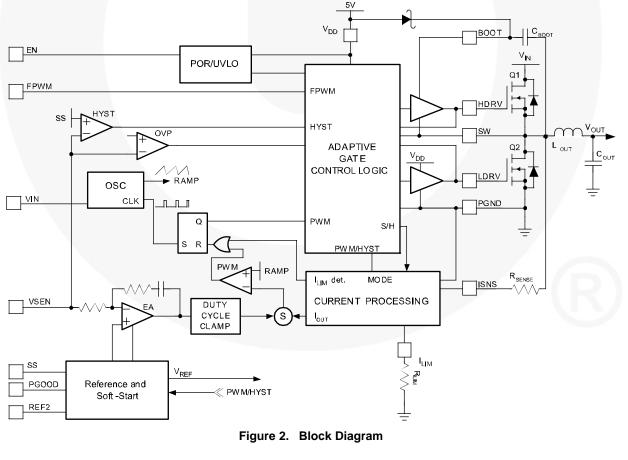

#### **Typical Application** VIN (BATTERY) = 2 to 24V VIN C2 : C1 BOOT 15 Q1A C5 FAN5234 **HDRV** 14 R5 L1 13 1.8V at 3.5A SW C6 ΕN Q1B R1 R3 **LDRV** SS1 10 C3 **PGND FPWM** R2 ISNS 12 **AGND VSEN** 6 **PGOOD VOUT** Figure 1. 1.18V Output Regulator **Block Diagram** POR/UVLO Q1

# **Pin Configuration**

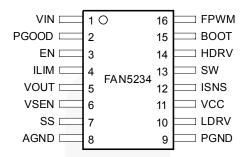

Figure 3. Pin Configuration

# **Pin Definitions**

| Pin# | Name  | Description                                                                                                                                                                                                        |  |  |  |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | VIN   | <b>Input Voltage</b> . Connect to main input power source (battery), also used to program operating frequency for low input voltage operation (see Table 1).                                                       |  |  |  |

| 2    | PGOOD | <b>Power-Good Flag</b> . An open-drain output that pulls LOW when $V_{\text{SEN}}$ is outside of a $\pm 10\%$ range of the 0.9V reference.                                                                         |  |  |  |

| 3    | EN    | <b>Enable</b> . Enables operation when pulled to logic HIGH. Toggling EN resets the regulator after a latched fault condition. This is a CMOS input whose state is indeterminate if left open.                     |  |  |  |

| 4    | ILIM  | Current Limit. A resistor from this pin to GND sets the current limit.                                                                                                                                             |  |  |  |

| 5    | VOUT  | Output Voltage. Connect to output voltage. Used for regulation to ensure a smooth transition during mode changes. When $V_{\text{OUT}}$ is expected to exceed $V_{\text{CC}}$ , tie this pin to $V_{\text{CC}}$ .  |  |  |  |

| 6    | VSEN  | Output Voltage Sense. The feedback from the output. Used for regulation as well as power-good, under-voltage, and over-voltage protection monitoring.                                                              |  |  |  |

| 7    | SS    | <b>Soft-Start</b> . A capacitor from this pin to GND programs the slew rate of the converter during initialization, when this pin is charged with a 5µA current source.                                            |  |  |  |

| 8    | AGND  | Analog Ground. This is the signal ground reference for the IC. All voltage levels are measured with respect to this pin.                                                                                           |  |  |  |

| 9    | PGND  | <b>Power Ground</b> . The return for the low-side MOSFET driver output. Connect to the gate of the low-side MOSFET.                                                                                                |  |  |  |

| 10   | LDRV  | <b>Low-Side Drive</b> . The low-side (lower) MOSFET driver output. Connect to the gate of the low-side MOSFET.                                                                                                     |  |  |  |

| 11   | VCC   | <b>Supply Voltage</b> . This pin powers the chip as well as the LDRV buffers. The IC starts to operate when voltage on this pin exceeds 4.6V (UVLO rising) and shuts down when it drops below 4.3V (UVLO falling). |  |  |  |

| 12   | ISNS  | Current-Sense Input. Monitors the voltage drop across the lower MOSFET or external sense resistor for current feedback.                                                                                            |  |  |  |

| 13   | SW    | Switching Node. Return for the high-side MOSFET driver and a current-sense input. Connect to source of high-side MOSFET and low-side MOSFET drain.                                                                 |  |  |  |

| 14   | HDRV  | <b>High-Side Drive</b> . High-side (upper) MOSFET driver output. Connect to the gate of the high-side MOSFET.                                                                                                      |  |  |  |

| 15   | воот  | BOOT. Positive supply for the upper MOSFET driver. Connect as shown in Figure 2.                                                                                                                                   |  |  |  |

| 16   | FPWM  | Forced PWM Mode. When logic HIGH, inhibits the regulation from entering Hysteretic Mode.                                                                                                                           |  |  |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                              | Min. | Max.                 | Unit |

|------------------|----------------------------------------|------|----------------------|------|

| V <sub>CC</sub>  | V <sub>CC</sub> Supply Voltage         |      | 6.5                  | V    |

| V <sub>IN</sub>  | V <sub>IN</sub> Supply Voltage         |      | 27                   | V    |

|                  | BOOT, SW, ISNS, HDRV Pins              |      | 33                   | V    |

|                  | BOOT to SW Pins                        |      | 6.5                  | V    |

|                  | All Other Pins                         | -0.3 | V <sub>CC</sub> +0.3 | V    |

| $T_J$            | Junction Temperature                   | -10  | +150                 | °C   |

| T <sub>STG</sub> | Storage Temperature                    | -65  | +150                 | °C   |

| TL               | Lead Soldering Temperature, 10 Seconds |      | +300                 | °C   |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol         | Parameter                               | Min. | Тур. | Max. | Unit |

|----------------|-----------------------------------------|------|------|------|------|

| Vcc            | V <sub>CC</sub> Supply Voltage          | 4.75 | 5.00 | 5.25 | V    |

| $V_{IN}$       | V <sub>IN</sub> Supply Voltage          |      |      | 24   | V    |

| T <sub>A</sub> | Ambient Temperature                     | -10  |      | +85  | °C   |

| $\Theta_{JA}$  | Thermal Resistance, Junction to Ambient |      |      | 112  | °C/W |

# **Electrical Characteristics**

Recommended operating conditions, unless otherwise noted.

| Symbol              | Parameter                         | Conditions                                                            | Min.  | Тур.  | Max.  | Units    |  |

|---------------------|-----------------------------------|-----------------------------------------------------------------------|-------|-------|-------|----------|--|

| Power Su            | pplies                            |                                                                       |       |       |       |          |  |

| I <sub>vcc</sub>    | V <sub>CC</sub> Current           | LDRV, HDRV Open;<br>V <sub>SEN</sub> Forced Above<br>Regulation Point |       | 850   | 1300  | μA       |  |

|                     |                                   | Shutdown (EN-0)                                                       |       | 5     | 15    | μA       |  |

| I <sub>SINK</sub>   | V <sub>IN</sub> Current, Sinking  | VIN Pin = Input Voltage<br>Source                                     | 10    | 20    | 30    | μA       |  |

| I <sub>SOURCE</sub> | V <sub>IN</sub> Current, Sourcing | VIN Pin = GND                                                         | 7     | 15    | 20    | μA       |  |

| I <sub>SD</sub>     | V <sub>IN</sub> Current, Shutdown |                                                                       |       |       | 1     | μA       |  |

|                     | LIV/I O Threehold                 | Rising V <sub>CC</sub>                                                | 4.30  | 4.55  | 4.75  | .,       |  |

| $V_{\text{UVLO}}$   | UVLO Threshold                    | Falling                                                               | 4.10  | 4.27  | 4.50  | <b> </b> |  |

| V <sub>UVLOH</sub>  | UVLO Hysteresis                   |                                                                       | 0.1   |       | 0.5   | V        |  |

| Oscillator          |                                   |                                                                       |       |       |       |          |  |

|                     | F                                 | V <sub>IN</sub> > 5V                                                  | 255   | 300   | 345   | IZI I=   |  |

| f <sub>osc</sub>    | Frequency                         | V <sub>IN</sub> = 0V                                                  | 510   | 600   | 690   | KHz      |  |

|                     | Dames Američanda                  | V <sub>IN</sub> = 16V                                                 |       | 2     |       | V        |  |

| $V_{PP}$            | Ramp Amplitude                    | V <sub>IN</sub> > 5V                                                  |       | 1.25  |       |          |  |

| $V_{RAMP}$          | Ramp Offset                       |                                                                       |       | 0.5   |       | V        |  |

| 0                   | D 11/1 0 :                        | $V_{IN} \ge 3V$                                                       |       | 125   |       |          |  |

| G                   | Ramp / V <sub>IN</sub> Gain       | 1V < V <sub>IN</sub> < 3V                                             |       | 250   |       | mV/V     |  |

| Reference           | and Soft-Start                    |                                                                       |       |       |       |          |  |

| V <sub>REF</sub>    | Internal Reference Voltage        |                                                                       | 0.891 | 0.900 | 0.909 | V        |  |

| I <sub>SS</sub>     | Soft-Start Current                | At Startup                                                            |       | 5     |       | μA       |  |

| V <sub>SS</sub>     | Soft-Start Complete Threshold     |                                                                       |       | 1.5   |       | V        |  |

| PWM Con             | verter                            |                                                                       |       |       |       |          |  |

|                     | Load Regulation                   | I <sub>OUT</sub> from 0 to 3A,<br>V <sub>IN</sub> from 2 to 24V       | -1    |       | +1    | %        |  |

| I <sub>SEN</sub>    | V <sub>SEN</sub> Bias Current     |                                                                       | 50    | 80    | 150   | nA       |  |

|                     | VOUT Pin Input Impedance          |                                                                       | 40    | 55    | 65    | ΚΩ       |  |

| UVLO <sub>TSD</sub> | Under-Voltage Shutdown            | % of Set Point,<br>2µs Noise Filter                                   | 70    | 75    | 80    | %        |  |

| I <sub>SNS</sub>    | Over-Current Threshold            | $R_{ILIM}$ = 68.5KΩ, Figure 6                                         | 115   | 144   | 172   | %        |  |

| UVLO                | Over-Voltage Threshold            | % of Set Point,<br>2µs Noise Filter                                   | 113   |       | 120   | μА       |  |

| Output Dr           | ivers                             |                                                                       |       |       |       |          |  |

|                     | HDD// O / / / C · · ·             | Sourcing                                                              |       | 8.0   | 15.0  | _        |  |

|                     | HDRV Output Resistance            | Sinking                                                               |       | 3.2   | 4.0   | Ω        |  |

|                     | 1000/01/10                        | Sourcing                                                              |       | 8.0   | 15.0  | _        |  |

|                     | LDRV Output Resistance            | Sinking                                                               |       | 1.5   | 2.4   | Ω        |  |

Continued on following page...

# **Electrical Characteristics** (Continued)

| Symbol           | Parameter                         | Conditions                          | Min. | Тур. | Max. | Units                  |

|------------------|-----------------------------------|-------------------------------------|------|------|------|------------------------|

| Power-G          | ood Output and Control Pins       |                                     |      |      |      |                        |

|                  | Lower Threshold                   | % of Set Point, 2µs<br>Noise Filter | 86   |      | 92   | %                      |

|                  | Upper Threshold                   | % of Set Point, 2µs<br>Noise Filter | 110  |      | 115  | %                      |

|                  | PGOOD Output Low                  | I <sub>PGOOD</sub> = 4mA            |      |      | 0.5  | V                      |

|                  | Leakage Current                   | V <sub>PULLUP</sub> = 5V            |      |      | 1    | μA                     |

|                  | Soft-Start Voltage, PGOOD Enabled |                                     |      | 1.5  |      | %<br>V <sub>REF2</sub> |

| EN, FPW          | M Inputs                          |                                     |      |      |      |                        |

| $V_{INH}$        | Input High                        |                                     | 2    |      |      | V                      |

| V <sub>INL</sub> | Input Low                         |                                     |      |      | 0.8  | V                      |

# **Functional Description**

#### Overview

The FAN5234 is a PWM controller intended for low-voltage power applications in notebook, desktop, and sub-notebook PCs. The output voltage of the controller can be set in the range of 0.9V to 5.5V by an external resistor divider.

The synchronous buck converter can operate from an unregulated DC source (such as a notebook battery), with voltage ranging from 2V to 24V, or from a regulated system rail. In either case, the IC is biased from a +5V source. The PWM modulator uses an average-current-mode control with input voltage feed-forward for simplified feedback loop compensation and improved line regulation. The controller includes integrated feedback loop compensation that dramatically reduces the number of external components.

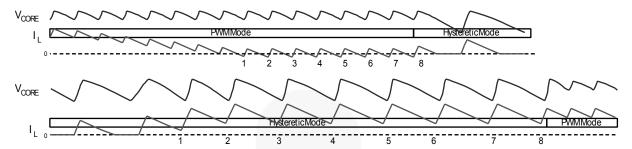

Depending on the load level, the converter can operate in fixed-frequency PWM Mode or in Hysteretic Mode. Switch-over from PWM to Hysteretic Mode improves the converters' efficiency at light loads and prolongs battery run time. In Hysteretic Mode, a comparator is synchronized to the main clock to allow seamless transition between the operational modes and reduced channel-to-channel interaction.

The Hysteretic Mode of operation can be inhibited independently using the FPWM pin if variable frequency operation is not desired.

#### Oscillator

Table 1. Converter Operating Modes

| rable in contents. Specialing incuse |                 |                 |                      |  |  |  |

|--------------------------------------|-----------------|-----------------|----------------------|--|--|--|

| Mode                                 | f <sub>sw</sub> | Converter Power | VIN Pin              |  |  |  |

| Battery                              | 300             | 2 to 24V        | Battery (>5V)        |  |  |  |

| Fixed 300                            | 300             | <5.5V Fixed     | 100K $\Omega$ to GND |  |  |  |

| Fixed 600                            | 600             | <5.5V Fixed     | GND                  |  |  |  |

When  $V_{\text{IN}}$  is from the battery, the oscillator ramp amplitude is proportional to  $V_{\text{IN}}$ , providing voltage feed-forward control for improved loop response. When in either of the fixed modes, oscillator ramp amplitude is fixed. The operating frequency is determined according to the connection on the VIN pin (see Table 1).

#### **Initialization and Soft Start**

Assuming EN is HIGH, FAN5234 is initialized when  $V_{\rm CC}$  exceeds the rising UVLO threshold. Should  $V_{\rm CC}$  drop below the UVLO threshold, an internal power-on reset function disables the chip.

The voltage at the positive input of the error amplifier is limited by the voltage at the SS pin, which is charged with 5mA current source. Once  $C_{SS}$  has charged to  $V_{REF}$  (0.9V), the output voltage is in regulation. The time it takes SS to reach 0.9V is:

$$t_{0.9} = \frac{0.9 \times C_{SS}}{5} \tag{1}$$

where  $t_{0.9}$  is in seconds if  $C_{SS}$  is in  $\mu F$ .

When SS reaches 1.5V, the power-good outputs are enabled and Hysteretic Mode is allowed. The converter is forced into PWM Mode during soft-start.

#### **Operation Mode Control**

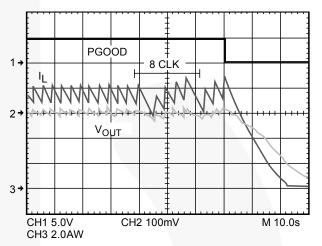

The mode-control circuit changes the converter's mode from PWM to Hysteretic and vice versa based on the voltage polarity of the SW node when the lower MOSFET is conducting and just before the upper MOSFET turns on. For continuous inductor current, the SW node is negative when the lower MOSFET is conducting and the converters operate in fixed-frequency PWM Mode, as shown in Figure 4. This mode achieves high efficiency at nominal load. When the load current decreases to the point where the inductor current flows through the lower MOSFET in the "reverse" direction, the SW node becomes positive and the mode is changed to Hysteretic, which achieves higher efficiency at low currents by decreasing the effective switching frequency.

To prevent accidental mode change or "mode chatter," the transition from PWM to Hysteretic Mode occurs when the SW node is positive for eight consecutive clock cycles (see Figure 4). The polarity of the SW node is sampled at the end of the lower MOSFET conduction time. At the transition between PWM and Hysteretic Mode, both the upper and lower MOSFETs are turned off. The SW node "rings" based on the output inductor and the parasitic capacitance on the SW node and settles out at the value of the output voltage.

The boundary value of inductor current, where current becomes discontinuous, is estimated by the following:

$$I_{LOAD(DIS)} = \left(\frac{(V_{IN} - V_{OUT})V_{OUT}}{2f_{SW}L_{OUT}V_{IN}}\right)$$

(2)

## **Hysteretic Mode**

Conversely, the transition from Hysteretic Mode to PWM Mode occurs when the SW node is negative for eight consecutive cycles.

A sudden increase in the output current causes a change from Hysteretic to PWM Mode. This load increase causes an instantaneous decrease in the output voltage due to the voltage drop on the output capacitor ESR. If the load causes the output voltage (as presented at  $V_{\rm SEN}$ ) to drop below the hysteretic regulation level (20mV below  $V_{\rm REF}$ ), the mode is changed to PWM on the next clock cycle.

In Hysteretic Mode, the PWM comparator and the error amplifier that provide control in PWM Mode are inhibited and the hysteretic comparator is activated. In Hysteretic Mode the low-side MOSFET is operated as a synchronous rectifier, where the voltage across  $(V_{\rm DS(ON)})$  is monitored and it is switched off when  $V_{\rm DS(ON)}$  goes positive (current flowing back from the load), allowing the diode to block reverse conduction.

Figure 4. Transitioning between PWM and Hysteretic Mode

The hysteretic comparator causes HDRV turn-on when the output voltage (at  $V_{\text{SEN}}$ ) falls below the lower threshold (10mV below  $V_{\text{REF}}$ ) and terminates the PFM signal when  $V_{\text{SEN}}$  rises over the higher threshold (5mV above  $V_{\text{REF}}$ ).

The switching frequency is primarily a function of:

- Spread between the two hysteretic thresholds

- ILOAD

- Output inductor and capacitor ESR

A transition back to PWM Continuous Conduction Mode or (CCM) occurs when the inductor current rises sufficiently to stay positive for eight consecutive cycles. This occurs when:

$$I_{LOAD(CCM)} = \left(\frac{\Delta VHYSTERESIS}{2 ESR}\right)$$

(3)

where  $\Delta V_{\text{HYSTERESIS}}$  = 15mV and ESR is the equivalent series resistance of  $C_{\text{OUT}}$ .

Due to different control mechanisms, the value of the load current where transition into PWM operation takes place is typically higher compared to the load level at which transition into Hysteretic Mode occurs. Hysteretic Mode can be disabled by setting the FPWM pin HIGH.

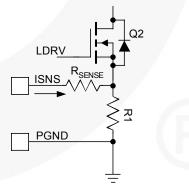

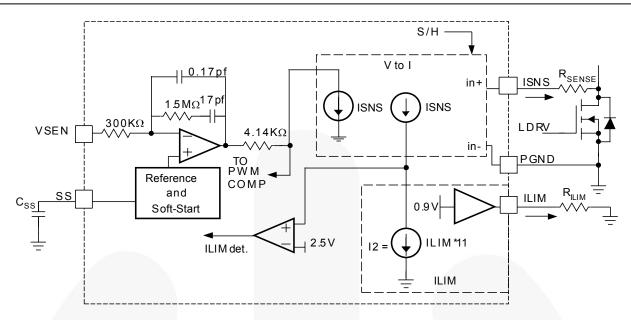

#### **Current Processing**

The following discussion refers to Figure 6.

The current through  $R_{\text{SENSE}}$  resistor ( $I_{\text{SNS}}$ ) is sampled shortly after Q2 is turned on. That current is held and summed with the output of the error amplifier. This effectively creates a current-mode control loop. The resistor connected to the ISNS pin ( $R_{\text{SENSE}}$ ) sets the gain in the current feedback loop. Equation 4 estimates the recommended value of  $R_{\text{SENSE}}$  as a function of the maximum load current ( $I_{\text{LOAD}(\text{MAX})}$ ) and the value of the MOSFET  $R_{\text{DS}(\text{ON})}$ .  $R_{\text{SENSE}}$  must be kept higher than  $700\Omega$  even if the number calculated comes out less than  $700\Omega$ :

$$R_{SENSE} = \left(\frac{I_{LOAD(MAX)} \times R_{DS(ON)}}{150 \mu A} - 100\right)$$

(4)

### **Setting the Current Limit**

A ratio of  $I_{\text{SNS}}$  is also compared to the current established when a 0.9V internal reference drives the ILIM pin:

$$R_{LIM} = \frac{11}{I_{LOAD}} x \left( \frac{(100 + R_{SENSE})}{R_{DS(ON)}} \right)$$

(5)

Since the tolerance on the current limit is largely dependent on the ratio of the external resistors, it is fairly accurate if the voltage drop on the switching node side of R<sub>SENSE</sub> is an accurate representation of the load current. When using the MOSFET as the sensing element, the variation of R<sub>DS(ON)</sub> causes proportional variation in I<sub>SNS</sub>. This value varies from device to device and has a typical junction temperature coefficient of about 0.4%/°C (consult the MOSFET datasheet for actual values), the actual current limit set point decreases proportional to increasing MOSFET die temperature. A factor of 1.6 in the current limit set point should compensate for all MOSFET R<sub>DS(ON)</sub> variations, assuming the MOSFET's heat sinking keep its operating die temperature below 125°C.

Figure 5. Improving Current-Sensing Accuracy

Figure 6. Current Limit / Summing Circuits

More accurate sensing can be achieved by using a resistor (R1) instead of the  $R_{DS(ON)}$  of the FET, as shown in Figure 5. This approach causes higher losses, but yields greater accuracy in both  $V_{DROOP}$  and  $I_{LIMIT}$ . R1 is a low value (e.g.  $10m\Omega$ ) resistor.

Current limit ( $I_{LIMIT}$ ) should be set high enough to allow inductor current to rise in response to an output load transient. Typically, a factor of 1.2 is sufficient. Since  $I_{LIMIT}$  is a peak current cut-off value, multiply  $I_{LOAD(MAX)}$  by the inductor ripple current (use 25%). For example, in Figure 1 the target for  $I_{LIMIT}$  would be:

$$I_{LIMIT} > 1.2 \times 1.25 \times 1.6 \times 3.5A \approx 8.5A$$

(6)

#### **Duty Cycle Clamp**

During severe load increase, the error amplifier output can go to its upper limit, pushing a duty cycle to almost 100% for a significant amount of time. This could cause a large increase of the inductor current and lead to a long recovery from a transient over-current condition or even to a failure at high input voltages. To prevent this, the output of the error amplifier is clamped to a fixed value after two clock cycles if severe output voltage excursion is detected, limiting maximum duty cycle to:

$$DC_{MAX} = \frac{V_{OUT}}{V_{IN}} + \left(\frac{2.4}{V_{IN}}\right) \tag{7}$$

This is designed to not interfere with normal PWM operation. When FPWM is grounded, the duty cycle clamp is disabled and the maximum duty cycle is 87%.

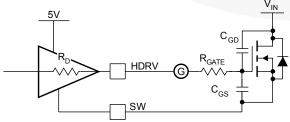

#### **Gate Driver**

The adaptive gate control logic translates the internal PWM control signal into the MOSFET gate drive signals, providing necessary amplification, level shifting, and shoot-through protection. It also has functions that help optimize the IC performance over a wide range of

operating conditions. Since MOSFET switching time can vary dramatically from type to type and with the input voltage, the gate control logic provides adaptive dead time by monitoring the gate-to-source voltages of both upper and lower MOSFETs. The lower MOSFET drive is not turned on until the gate-to-source voltage of the upper MOSFET has decreased to less than approximately 1V. Similarly, the upper MOSFET is not turned on until the gate-to-source voltage of the lower MOSFET has decreased to less than approximately 1V. This allows a wide variety of upper and lower MOSFETs to be used without concern for simultaneous conduction or shoot-through.

There must be a low-resistance, low-inductance path between the driver pin and the MOSFET gate for the adaptive dead-time circuit to work properly. Any delay along that path subtracts from the delay generated by the adaptive dead-time circuit and shoot-through may occur.

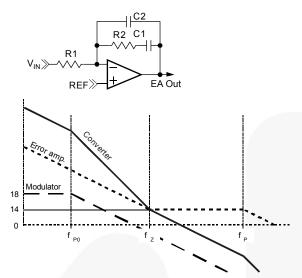

#### **Frequency Loop Compensation**

Due to the implemented current-mode control, the modulator has a single-pole response with -1 slope at frequency determined by load. Therefore:

$$f_{PO} = \frac{1}{2\pi R_{O} C_{O}} \tag{8}$$

where Ro is load resistance and Co is load capacitance.

For this type of modulator, type-2 compensation circuit is usually sufficient. To reduce the number of external components and simplify the design task, the PWM controller has an internally compensated error amplifier. Figure 7 shows a type two amplifier, its response, and the responses of a current mode modulator and the converter. The type-2 amplifier, in addition to the pole at the origin, has a zero-pole pair that causes a flat gain region at frequencies between the zero and the pole.

Figure 7. Compensation

$$f_z = \frac{1}{2\pi R_2 C_1} = 6kHz$$

(9)

$$f_{_{P}} = \frac{1}{2\pi R_{2}C2} = 600kHz \tag{10}$$

This region is also associated with phase "bump" or reduced phase shift. The amount of phase shift reduction depends the width of the region of flat gain and has a maximum value of  $90^{\circ}$ . To further simplify the converter compensation, the modulator gain is kept independent of the input voltage variation by providing feed-forward of  $V_{\text{IN}}$  to the oscillator ramp.

The zero frequency, the amplifier high-frequency gain, and the modulator gain are chosen to satisfy most typical applications. The crossover frequency appears at the point where the modulator attenuation equals the amplifier high-frequency gain. The system designer must specify the output filter capacitors to position the load main pole somewhere within one decade lower than the amplifier zero frequency. With this type of compensation, plenty of phase margin is achieved due to zero-pole pair phase "boost."

Conditional stability may occur only when the main load pole is positioned too much to the left side on the frequency axis due to excessive output filter capacitance. In this case, the ESR zero placed within the 10kHz to 50kHz range gives some additional phase boost. There is an opposite trend in mobile applications to keep the output capacitor as small as possible.

#### **Protections**

The converter output is monitored and protected against extreme overload, short circuit, over-voltage, and under-voltage conditions.

A sustained overload on an output sets the PGOOD pin LOW and latches off the chip. Operation is restored by cycling the  $V_{\rm CC}$  voltage or by toggling the EN pin.

If  $V_{\text{OUT}}$  drops below the under-voltage threshold, the chip shuts down immediately.

#### **Over-Current Sensing**

If the circuit's current-limit signal (" $I_{LIM}$  det" in Figure 6) is HIGH at the beginning of a clock cycle, a pulse-skipping circuit is activated and HDRV is inhibited. The circuit continues to pulse skip in this manner for the next eight clock cycles. If at any time from the ninth to the sixteenth clock cycle, the  $I_{LIM}$  det is again reached, the over-current protection latch is set, disabling the chip. If  $I_{LIM}$  det does not occur between cycles 9 and 16, normal operation is restored and the over-current circuit resets itself.

Figure 8. Over-Current Protection Waveforms

#### Over-Voltage / Under-Voltage Protection

Should the  $V_{\text{SEN}}$  voltage exceed 120% of  $V_{\text{REF}}$  (0.9V) due to an upper MOSFET failure or for other reasons, the over-voltage protection comparator forces LDRV HIGH. This action actively pulls down the output voltage and, in the event of the upper MOSFET failure, eventually blows the battery fuse. As soon as the output voltage drops below the threshold, the OVP comparator is disengaged.

This OVP scheme provides a 'soft' crowbar function to tackle severe load transients and does not invert the output voltage when activated — a common problem for latched OVP schemes.

Similarly, if an output short-circuit or severe load transient causes the output to droop to less than 75% of its regulation set point, the regulator shuts down.

#### **Over-Temperature Protection**

The chip incorporates an over-temperature protection circuit that shuts the chip down when a die temperature reaches 150°C. Normal operation is restored at die temperature below 125°C with internal power on reset asserted, resulting in a full soft-start cycle.

# **Design and Component Selection**

#### Guidelines

As an initial step, define operating input voltage range, output voltage, and minimum and maximum load currents for the controller.

For the examples in the following discussion, select components for:

V<sub>IN</sub> from 5V to 20V

$V_{OUT} = 1.8V$  at  $I_{LOAD(MAX)} = 3.5A$

## **Setting the Output Voltage**

The internal reference is 0.9V. The output is divided down by a voltage divider to the VSEN pin (for example, R1 and R2 in Figure 1). The output voltage therefore is:

$$\frac{0.9V}{R2} = \frac{V_{OUT} - 0.9V}{R1}$$

(11)

To minimize noise pickup on this node, keep the resistor to GND (R2) below 2K; for example R2 at 1.82K, then choose R5:

$$R5 = \frac{(1.82K\Omega) \times (1.8V - 0.9)}{0.9} = 1.82K$$

(12)

# **Output Inductor Selection**

The minimum practical output inductor value keeps inductor current just on the boundary of continuous conduction at some minimum load. The industry standard practice is to choose the ripple current to be somewhere from 15% to 35% of the nominal current. At light-load, the ripple current determines the point where the converter automatically switches to Hysteretic Mode to sustain high efficiency. The following equations help to choose the proper value of the output filter inductor:

$$\Delta I = 2 - 1_{MIN} = \frac{\Delta V_{OUT}}{ESR}$$

(13)

where  $\Delta I$  is the inductor ripple current, which is chosen for 20% of the full load current and  $\Delta V_{OUT}$  is the maximum output ripple voltage allowed:

$$L = \frac{V_{IN} - V_{OUT}}{f_{SW} \times \Delta I} \times \frac{V_{OUT}}{V_{IN}}$$

(14)

For this example, use:

$$V_{IN} = 20V, V_{OUT} = 1.8V$$

$\Delta I = 20\% \times 3.5A = 0.7A$  (15)

$f_{SW} = 300KHz$ .

Therefore;

#### **Output Capacitor Selection**

The output capacitor serves two major functions in a switching power supply. Along with the inductor, it filters the sequence of pulses produced by the switcher and it supplies the load transient currents. The output capacitor requirements are usually dictated by ESR, inductor ripple current ( $\Delta I$ ), and the allowable ripple voltage ( $\Delta V$ ):

$$ESR < \frac{\Delta V}{\Lambda I}$$

(17)

For this example,

$$ESR_{(MAX)} = \frac{\Delta V}{\Delta I} = \frac{0.1V}{0.7A} = 142m\Omega$$

In addition, the capacitor's ESR must be low enough to allow the converter to stay in regulation during a load step. The ripple voltage due to ESR for the converter in Figure 1 is  $100 \text{mV}_{PP}$ . Some additional ripple will appear due to the capacitance value itself:

$$\Delta V = \frac{\Delta I}{C_{OUT} \times 8 \times f_{SW}}$$

(18)

which is only about 1.5mV for the converter in Figure 1 and can be ignored.

The capacitor must also be rated to withstand the RMS current, which is approximately 0.3 X ( $\Delta I$ ) or about 210mA for the converter in Figure 1. High-frequency decoupling capacitors should be placed as close to the loads as physically possible.

#### **Input Capacitor Selection**

The input capacitor should be selected by its ripple current rating. The input RMS current at maximum load current ( $I_L$ ) is:

$$I_{RMS} = I_L \sqrt{D - D^2}$$

(19)

where the converter duty cycle;  $D = \frac{V_{OUT}}{V_{IN}}$  , which for

the circuit in Figure 1, with  $V_{\text{IN}}\text{=}6,$  calculates to  $I_{RMS}=1.6A$  .

#### **Power MOSFET Selection**

Losses in a MOSFET are the sum of its switching ( $P_{SW}$ ) and conduction ( $P_{COND}$ ) losses.

In typical applications, the FAN5234 converter's output voltage is low with respect to its input voltage. Therefore, the lower MOSFET (Q2) is conducting the full-load current for most of the cycle. Q2 should therefore be selected to minimize conduction losses, thereby selecting a MOSFET with low  $R_{\text{DS(ON)}}. \label{eq:respect}$

In contrast, the high-side MOSFET (Q1) has a shorter duty cycle, and its conduction loss has less impact. Q1, however, sees most of the switching losses, so Q1's primary selection criteria should be gate charge.

#### **High-Side Losses**

Figure 9 shows a MOSFET's switching interval, with the upper graph being the voltage and current on the drainto-source and the lower graph detailing  $V_{\rm GS}$  vs. time with a constant current charging the gate. The x-axis therefore is also representative of gate charge (Q<sub>G</sub>).  $C_{\rm ISS} = C_{\rm GD} + C_{\rm GS}$ , and it controls t1, t2, and t4 timing.  $C_{\rm GD}$  receives the current from the gate driver during t3 (as  $V_{\rm DS}$  is falling). The gate charge (Q<sub>G</sub>) parameters on the lower graph are either specified or can be derived from MOSFET datasheets.

Assuming switching losses are about the same for both the rising edge and falling edge, Q1's switching losses, occur during the shaded time when the MOSFET has voltage across it and current through it.

These losses are given by:

$$P_{UPPER} = P_{SW} + P_{COND}$$

(20)

where:

$$P_{SW} = \left(\frac{V_{DS} \times I_{L}}{2} \times 2 \times t_{s}\right) f_{SW}$$

(21)

$$P_{COND} = \left(\frac{V_{OUT}}{V_{IN}}\right) \times I_{OUT}^{2} \times R_{DS(ON)}$$

(22)

$P_{\text{UPPER}}$  is the upper MOSFET's total losses and  $P_{\text{SW}}$  and  $P_{\text{COND}}$  are the switching and conduction losses for a given MOSFET.  $R_{\text{DS(ON)}}$  is at the maximum junction temperature (T<sub>J</sub>).  $t_{\text{S}}$  is the switching period (rise or fall time) and is t2+t3 in Figure 9.

Figure 9. Switching Losses and  $Q_G$ ( $C_{ISS} = C_{GS} || C_{GD}$ )

Figure 10. Drive Equivalent Circuit

The driver's impedance and  $C_{\rm ISS}$  determine t2 while t3's period is controlled by the driver's impedance and  $Q_{\rm GD}$ . Since most of  $t_{\rm S}$  occurs when  $V_{\rm GS} = V_{\rm SP}$ , use a constant current assumption for the driver to simplify the calculation of  $t_{\rm S}$ :

$$t_{s} = \frac{Q_{G(SW)}}{I_{DRIVER}} = \frac{Q_{G(SW)}}{\left(\frac{V_{CC} - V_{SP}}{R_{DRIVER} + R_{GATE}}\right)}$$

(23)

Most MOSFET vendors specify  $Q_{GD}$  and  $Q_{GS}$ .  $Q_{G(SW)}$  can be determined as:

$$Q_{G(SW)} = Q_{GD} + Q_{GS} - Q_{TH}$$

(24)

where  $Q_{TH}$  is the gate charge required to get the MOSFET to its threshold ( $V_{TH}$ ).

For the high-side MOSFET,  $V_{DS} = V_{IN}$ , which can be as high as 20V in a typical portable application. Care should be taken to include the delivery of the MOSFET's gate power ( $P_{GATE}$ ) in calculating the power dissipation required for the FAN5234:

$$P_{GATE} = Q_{G} \times V_{CC} \times f_{SW}$$

(25)

where  $Q_G$  is the total gate charge to reach  $V_{CC}$ .

#### **Low-Side Losses**

Q2 switches on or off with its parallel Schottky diode conducting; therefore,  $V_{DS}{\approx}0.5V$ . Since  $P_{SW}$  is proportional to  $V_{DS}$ , Q2's switching losses are negligible and Q2 is selected based on  $R_{DS(ON)}$  only.

Conduction losses for Q2 are given by:

$$P_{COND} = (1-D) \times I_{OUT}^{2} \times R_{DS(ON)}$$

(26)

where  $R_{DS(ON)}$  is the  $R_{DS(ON)}$  of the MOSFET at the highest operating junction temperature and

$$D = \frac{V_{OUT}}{V_{IN}} \ \, \text{is the minimum duty cycle for the converter}.$$

Since  $D_{MIN}$  <20% for portable computers, (1-D)≈1 produces a conservative result, simplifying the calculation.

The maximum power dissipation ( $P_{D(MAX)}$ ) is a function of the maximum allowable die temperature of the low-side MOSFET, the  $\Theta_{JA}$ , and the maximum allowable ambient temperature rise:

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_{A(MAX)}}{\Theta_{JA}}$$

(27)

Θ<sub>JA</sub> depends primarily on the amount of PCB area that can be devoted to heat sinking (see AN-1029 — Maximum Power Enhancement Techniques for SO-8 Power MOSFET for MOSFET thermal information).

Table 2. Build Of Materials for 1.8V, 3.5A Regulator

| Description                                            | Qty. | Ref.   | Vendor                  | Part Number              |

|--------------------------------------------------------|------|--------|-------------------------|--------------------------|

| Capacitor 68 $\mu$ F, Tantalum, 25V, ESR 95m $\Omega$  | 1    | C1     | AVX.                    | TPSV686*025#095          |

| Capacitor 10nF, Ceramic                                | 2    | C2, C3 | Any                     |                          |

| Capacitor 68μF, Tantalum, 6V, ESR 1.8Ω                 | 1    | C4     | AVX.                    | TAJV686*006              |

| Capacitor 0.1µF, Ceramic                               | 2    | C5     | Any                     |                          |

| Capacitor 330 $\mu$ F, Tantalum, 6V, ESR 100m $\Omega$ | 2    | C6     | AVX.                    | TPSE337*006#0100         |

| 1.82KΩ, 1% Resistor                                    | 2    | R1, R2 | Any                     |                          |

| 1.3KΩ, 1% Resistor                                     | 1    | R3     | Any                     |                          |

| 100KΩ, 5% Resistor                                     | 1    | R4     | Any                     |                          |

| 56.2KΩ, 1% Resistor                                    | 1    | R5     | Any                     |                          |

| Schottky Diode; 0.5A, 20V                              | 2    | D1     | Fairchild Semiconductor | MBR05S0L                 |

| Inductor 8.4µH, 6A                                     | 1    | L1     | Any                     |                          |

| Dual MOSFET with Schottky                              | 1    | Q      | Fairchild Semiconductor | FDS6986AS <sup>(1)</sup> |

| PWM Controller                                         | 1    | U1     | Fairchild Semiconductor | FAN5234                  |

#### Note:

# **Layout Considerations**

Switching converters, even during normal operation, produce short pulses of current that could cause substantial ringing and be a source of EMI if layout constrains are not observed.

There are two sets of critical components in a DC-DC converter. The switching power components process large amounts of energy at high rate and are noise generators. The low-power components responsible for bias and feedback functions are sensitive to noise.

A multi-layer printed circuit board is recommended. Dedicate one solid layer for a ground plane. Dedicate another solid layer as a power plane and break this plane into smaller islands of common voltage levels.

Notice all the nodes that are subjected to high dV/dt voltage swing; such as SW, HDRV, and LDRV. All surrounding circuitry tends to couple the signals from these nodes through stray capacitance. Do not oversize copper traces connected to these nodes. Do not place traces connected to the feedback components adjacent to these traces. It is not recommended to use high density interconnect systems, or micro-vias, on these signals. The use of blind or buried vias should be limited to the low-current signals only. The use of normal thermal vias is at the discretion of the designer.

Keep the wiring traces from the IC to the MOSFET gate and source as short as possible and capable of handling peak currents of 2A. Minimize the area within the gate-source path to reduce stray inductance and eliminate parasitic ringing at the gate.

Locate small critical components, like the soft-start capacitor and current sense resistors, as close as possible to the respective pins of the IC.

The FAN5234 utilizes advanced packaging technologies with lead pitches of 0.6mm. Highperformance analog semiconductors utilizing narrow lead spacing may require special considerations in PWB design and manufacturing. It is critical to maintain proper cleanliness of the area surrounding these devices. It is not recommended to use any type of rosin or acid core solder, or the use of flux, in either the manufacturing or touch up process as these may contribute to corrosion or enable electro-migration and / or eddy currents near the sensitive low-current signals. When chemicals are used on or near the PWB, it is suggested that the entire PWB be cleaned and dried completely before applying power.

<sup>1.</sup> If currents above 4A continuous are required, use single SO-8 packages. For more information, refer to the Power MOSFET Selection Section and AN-6002 for design calculations.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ON Semiconductor: FAN5234MTCX

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.