# high performance needs great design.

Datasheet: AS8650B High-efficient Power Management Device with High-speed CAN Interface

Please be patient while we update our brand image as austriamicrosystems and TAOS are now ams.

# AS8650B

# High-efficient Power Management Device with High-speed CAN Interface

# 1 General Description

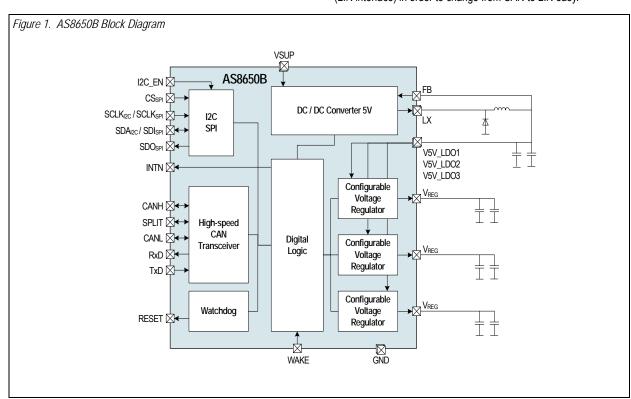

The AS8650B is a companion IC which combines power management functions and a fully conforming high-speed CAN Transceiver in one high performance analog device for automotive applications. The AS8650B is powered by the battery, provides 4 output voltage levels of which 3 outputs in the range of 1.8V to 3.3V with a maximum current consumption up to 120mA at the LDO voltage regulator outputs. An integrated DCDC converter with a very high efficiency for the 5V output supplies the 3 voltage regulators and ensures a voltage stability of  $\pm 2.5\%$ . The combination of DCDC converter with low-drop-out voltage regulators makes the AS8650B suitable for all Automotive Control Units where power efficiency is a must.

The AS8650B provides a high-speed CAN interface up to 1Mbps communication rate conforming to ISO 11898-5. The AS8650B provides wake-up via remote wake-up at CAN bus lines and a local wake pin. The watchdog unit provides three different timing functions: start-up, window- and timeout watchdog; configurable via the SPI and I<sup>2</sup>C interface.

Voltage monitoring is implemented for the battery supply, DCDC output and the 3 LDO regulator outputs. Undervoltage will be signalled on the INTN pin to the microcontroller. All diagnostics and status flags can be accessed with the SPI interface.

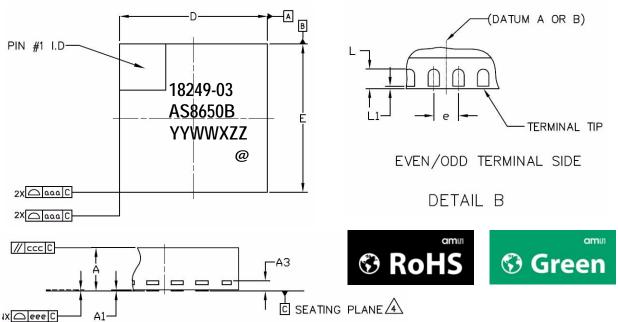

The product is available in a 36-pin QFN (6x6x0.9) package.

# 2 Key Features

- DCDC converter for 5V output with very high efficiency

- Three voltage regulators providing 3.3V, 2.8V and 1.8V with accuracy better than 2.5% (Two are adjustable through factory settings).

- High-speed CAN interface (ISO 11898-5) with remote wake-up

- Comprehensive voltage monitoring

- Configurable watchdog functions for start-up, operation, and standby

- Automatic thermal shutdown protection

- Excellent EMC performance with outstanding switching technology for the DCDC converter

- Ambient temperature range from -40°C to +105°C in maximum load conditions

- Lead-free 36-pin QFN (6x6x0.9) package

# 3 Applications

The AS8650B provides high efficient and flexible power supply together with state-of-the-art high-speed CAN Interface for automotive control units. The device is pin compatible with AS8550 (LIN interface) in order to change from CAN to LIN easy.

# Contents

| 1 | General Description                    | •        |

|---|----------------------------------------|----------|

| 2 | Key Features                           | '        |

| 3 | Applications                           | <i>'</i> |

| 4 | Pin Assignments                        | 4        |

|   | 4.1 Pin Descriptions                   | 4        |

| 5 | Absolute Maximum Ratings               |          |

|   | Electrical Characteristics             |          |

| • | 6.1 Electrical System Specification    |          |

|   | 6.2 DCDC Converter                     |          |

|   | 6.3 Low Drop Out Regulators            |          |

|   | 6.4 CAN Transceiver                    |          |

|   | 6.4.1 Timing Diagrams.                 |          |

|   | 6.5 Undervoltage Detection             |          |

|   | 6.6 Digital Timing Specification       |          |

|   | 6.6.1 System Specification and Timings |          |

| 7 | Detailed Description                   |          |

| • | 7.1 Operating Modes and States         |          |

|   | 7.1.1 Normal Mode                      |          |

|   | 7.1.2 Receive-Only Mode                |          |

|   | 7.1.3 Standby Mode                     |          |

|   | 7.1.4 Sleep Mode                       |          |

|   | 7.2 Power Management Strategy          |          |

|   | 7.3 State Diagram                      |          |

|   | 7.4 Initialization Sequence            | . 20     |

|   | 7.5 DCDC Converter                     |          |

|   | 7.6 Voltage Regulator LDO1             |          |

|   | 7.7 Voltage Regulator LDO2             | . 2      |

|   | 7.8 Voltage Regulator LDO3             | . 2      |

|   | 7.9 Over-Temperature Monitor           | . 2      |

|   | 7.10 Undervoltage Reset                | . 2      |

|   | 7.11 Reset Block                       | . 2      |

|   | 7.12 CAN Transceiver                   | . 2      |

|   | 7.12.1 BUS Driver                      | 24       |

|   | 7.12.2 Normal Receiver                 | 24       |

|   | 7.12.3 Low Power Receiver              | 24       |

|   | 7.12.4 Operating Modes                 |          |

|   | 7.12.5 Local Wake-up Event             |          |

|   | 7.12.6 Remote Wake-up                  |          |

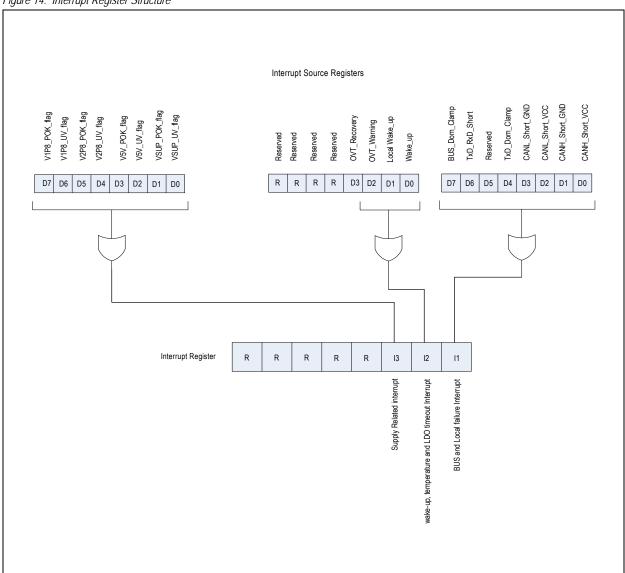

|   | 7.13 Internal Flags                    |          |

|   | 7.13.1 VSUP_UV_flag                    |          |

|   | 7.13.2 VSUP_POK_flag                   |          |

|   | 7.13.3 V5V_UV_flag                     |          |

|   | 7.13.4 V5V_POK_flag                    |          |

|   | 7.13.5 VLDO2_UV_flag                   |          |

|   | 1.10.0 VEDOZ_1 OI\_IIay                | 21       |

| 7.13.7 VLDO3_UV_flag                                      | 26   |

|-----------------------------------------------------------|------|

| 7.13.8 VLDO3_POK_flag                                     | 26   |

| 7.13.9 BUS Wake_up Flag                                   | 27   |

| 7.13.10 Local Wake_up Flag                                | 27   |

| 7.13.11 OVT_Warning Flag                                  | 27   |

| 7.13.12 OVT_Recover Flag                                  | 27   |

| 7.13.13 Bus Failure Flags                                 | 27   |

| 7.13.14 Local Failure Flags                               | 27   |

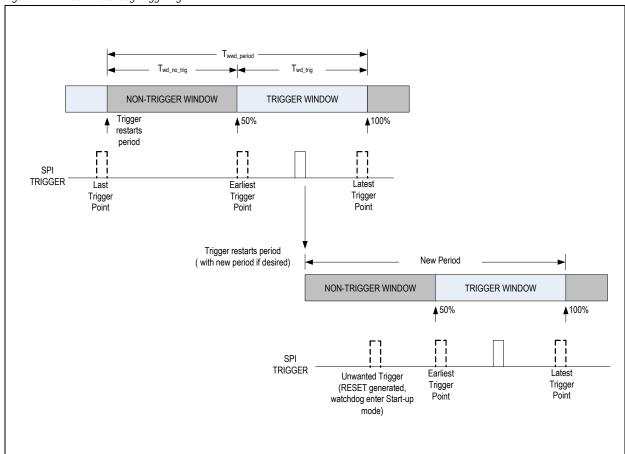

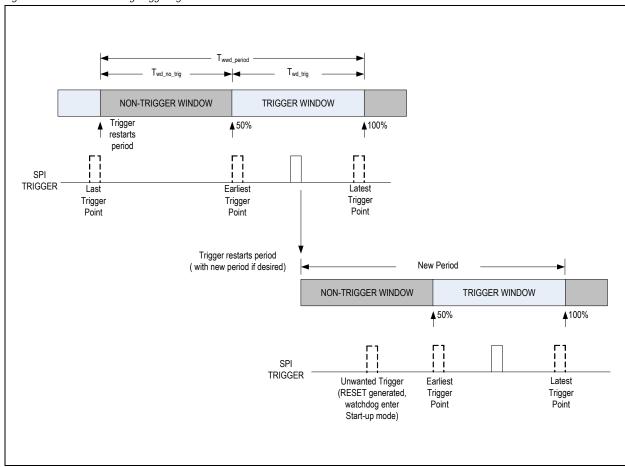

| 7.14 Watchdog (WD)                                        | . 28 |

| 7.14.1 Start-up Watchdog Behavior                         | 28   |

| 7.14.2 Window Watchdog Behavior                           | 28   |

| 7.14.3 Timeout Watchdog Behavior                          | 29   |

| 7.15 Interrupt Generation                                 | . 29 |

| 7.16 Status Registers                                     | . 30 |

| 8 Application Information                                 | 31   |

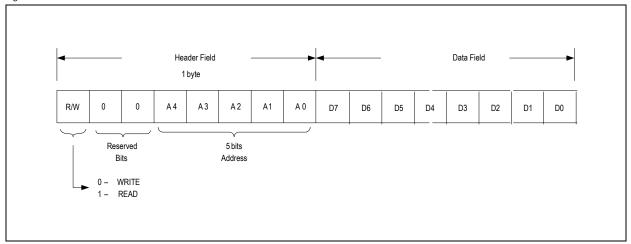

| 8.1 Serial Peripheral Interface                           | . 31 |

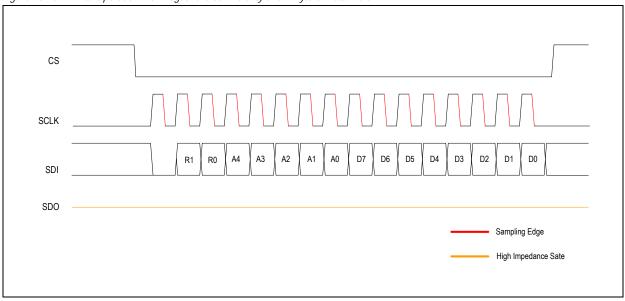

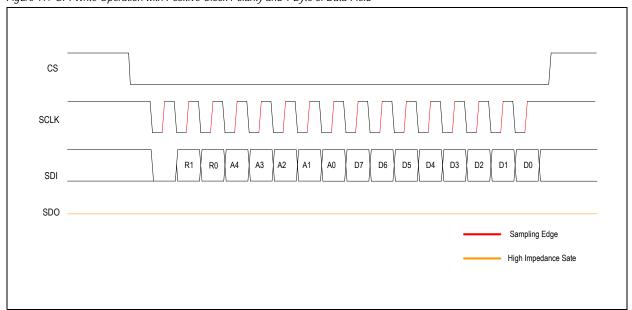

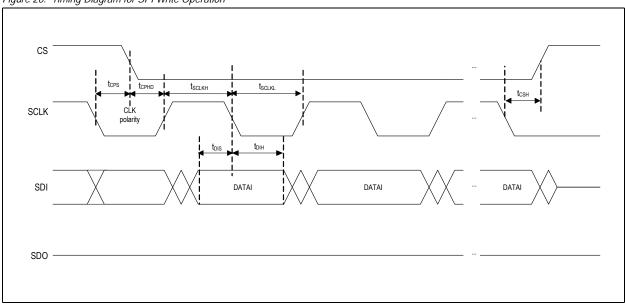

| 8.1.1 SPI Write Operation                                 | 32   |

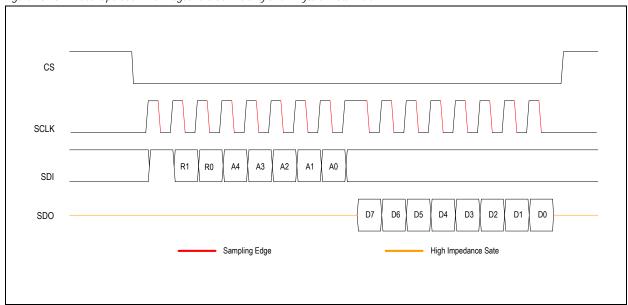

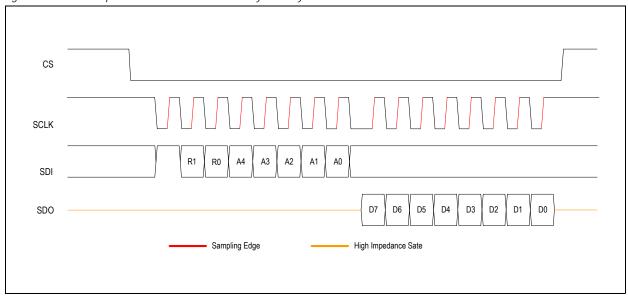

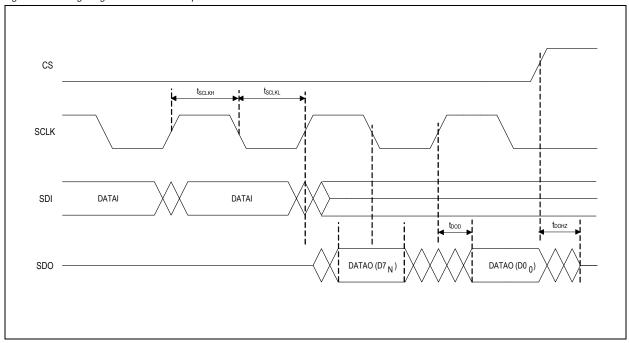

| 8.1.2 SPI Read Operation                                  | 33   |

| 8.1.3 SPI Timing Diagram                                  | 34   |

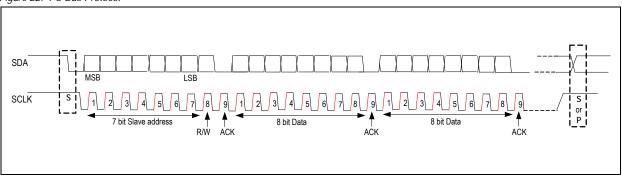

| 8.2 Inter-Integrated Circuit (I <sup>2</sup> C) Interface | . 35 |

| 8.2.1 I <sup>2</sup> C Slave Address                      | 35   |

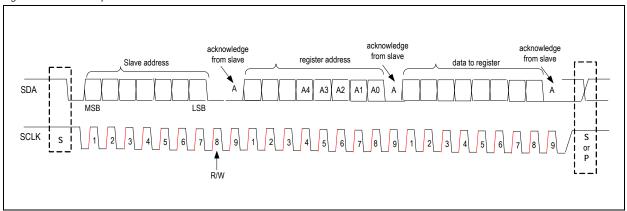

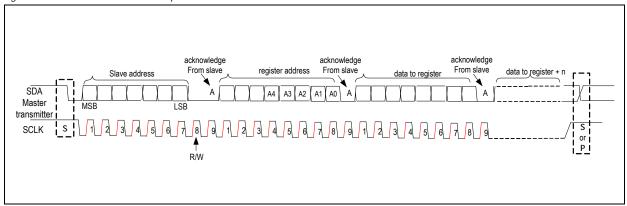

| 8.2.2 I <sup>2</sup> C Write Operation                    | 35   |

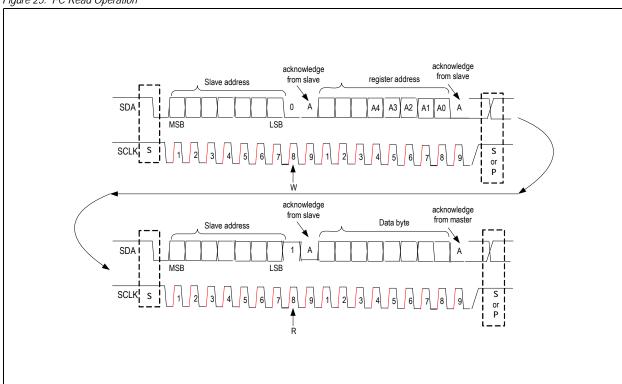

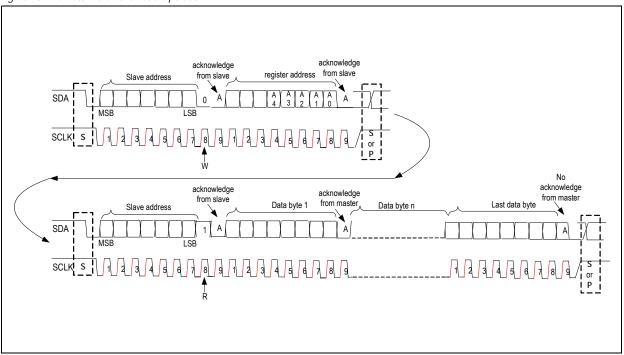

| 8.2.3 I <sup>2</sup> C Read Operation                     | 36   |

| 8.3 Register Space                                        | . 38 |

| 9 Package Drawings and Markings                           | 43   |

| 10 Ordering Information                                   | 45   |

|                                                           |      |

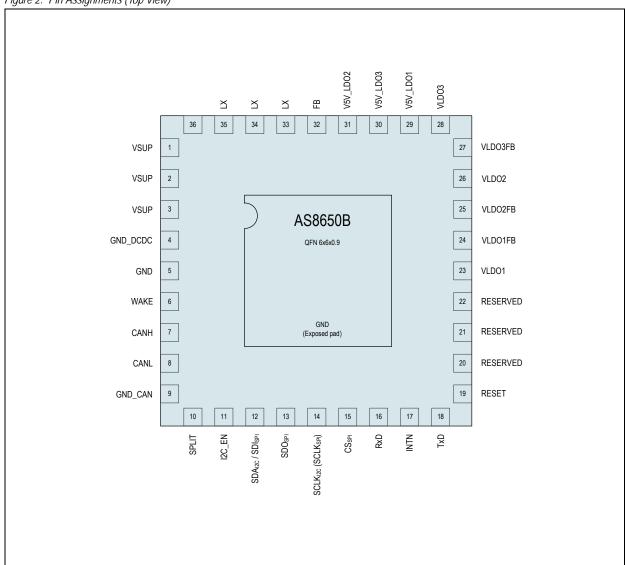

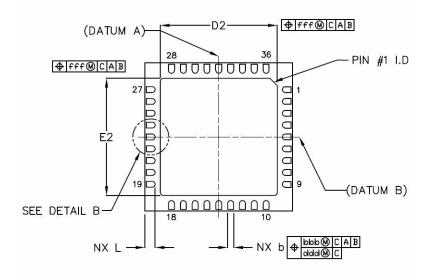

# 4 Pin Assignments

Figure 2. Pin Assignments (Top View)

# 4.1 Pin Descriptions

Table 1. Pin Descriptions

| Pin     | Pin Name | Pin Type                           | Description                             |  |  |

|---------|----------|------------------------------------|-----------------------------------------|--|--|

| 1, 2, 3 | VSUP     |                                    |                                         |  |  |

| 4       | GND_DCDC | Power Supply Input                 | Power Supply                            |  |  |

| 5       | GND      |                                    |                                         |  |  |

| 6       | WAKE     |                                    | Local wake request (high-voltage input) |  |  |

| 7       | CANH     | Analog Input / Output high-voltage | High level CAN bus line                 |  |  |

| 8       | CANL     |                                    | Low level CAN bus line                  |  |  |

| 9       | GND_CAN  | Power Supply Input                 | Power supply                            |  |  |

| 10      | SPLIT    | Analog Input / Output high-voltage | Common-mode stabilization output        |  |  |

Table 1. Pin Descriptions

| Pin        | Pin Name                                  | Pin Type                                               | Description                                                                    |  |  |  |

|------------|-------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|

| 11         | I2C_EN                                    | Digital Input                                          | I <sup>2</sup> C/SPI select signal (High = I <sup>2</sup> C, Low = SPI)        |  |  |  |

| 12         | SDA <sub>I2C</sub> / SDI <sub>SPI</sub>   | Digital Input/Output<br>/ Digital Input                | Unidirectional for SPI, Bidirectional for I <sup>2</sup> C                     |  |  |  |

| 13         | SDO <sub>SPI</sub>                        | Digital Output                                         | SPI data out                                                                   |  |  |  |

| 14         | SCLK <sub>I2C</sub> / SCLK <sub>SPI</sub> | Digital Input                                          | Serial clock (Multiplexed for I <sup>2</sup> C and SPI) unidirectional         |  |  |  |

| 15         | CS <sub>SPI</sub>                         | Digital input with pull-up                             | SPI chip select                                                                |  |  |  |

| 16         | RxD                                       | Digital output with pull-up                            | CAN Transceiver receive signal                                                 |  |  |  |

| 17         | INTN                                      | Digital Output                                         | Active low interrupt to $\mu C$ . Generated if status / diagnostic is updated. |  |  |  |

| 18         | TxD                                       | Digital input with pull-up                             | CAN Transceiver transmit signal                                                |  |  |  |

| 19         | RESET                                     | Digital Output                                         | Digital Output referenced to VLDO1, active low                                 |  |  |  |

| 20         |                                           | Pin with Digital / Analog Input /<br>Open-Drain-Output |                                                                                |  |  |  |

| 21         | Reserved                                  | Analog Input / Output                                  | Reserved                                                                       |  |  |  |

| 22         |                                           | Analog Input / Output                                  |                                                                                |  |  |  |

| 23         | VLDO1                                     | Power Supply Input                                     | Regulated voltage output                                                       |  |  |  |

| 24         | VLDO1FB                                   | Pin with Digital / Analog Input /<br>Open-Drain-Output | Regulated voltage feedback                                                     |  |  |  |

| 25         | VLDO2FB                                   | Pin with Digital / Analog Input /<br>Open-Drain-Output | Regulated voltage feedback                                                     |  |  |  |

| 26         | VLDO2                                     | Power Supply Input                                     | Regulated voltage output                                                       |  |  |  |

| 27         | VLDO3FB                                   | Pin with Digital / Analog Input /<br>Open-Drain-Output | Regulated voltage feedback                                                     |  |  |  |

| 28         | VLDO3                                     |                                                        | Regulated voltage output                                                       |  |  |  |

| 29         | V5V_LDO1                                  | Power Supply Input                                     | Step-down converter 5V output, supply for LDO1                                 |  |  |  |

| 30         | V5V_LDO3                                  | rower Supply Input                                     | Step-down converter 5V output, supply for LDO3                                 |  |  |  |

| 31         | V5V_LDO2                                  |                                                        | Step-down converter 5V output, supply for LDO2                                 |  |  |  |

| 32         | FB (DCDC)                                 | Analog Input                                           | DCDC output voltage feedback                                                   |  |  |  |

| 33, 34, 35 | LX (DCDC)                                 | Power Supply Input                                     | DCDC output                                                                    |  |  |  |

| 0 GND      |                                           | Power Supply input                                     | Exposed pad (GND)                                                              |  |  |  |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 7 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings<sup>1</sup>

| Parameter                                                                                             | Min  | Max                     | Units | Notes                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------|------|-------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Parameters                                                                                 |      |                         |       |                                                                                                                                                                                                                                                                                    |

| Voltage at positive supply pin (V <sub>VSUP</sub> )                                                   | -0.3 | 40                      | V     |                                                                                                                                                                                                                                                                                    |

| Voltage at pin V5V_LDO1, V5V_LDO2,<br>V5V_LDO3, VLDO1, VLDO2, VLDO3, FB,<br>VLDO1FB, VLDO2FB, VLDO3FB | -0.3 | 7                       | V     |                                                                                                                                                                                                                                                                                    |

| Voltage at pin CANH, CANL, SPLIT                                                                      | -40  | +40                     | V     |                                                                                                                                                                                                                                                                                    |

| Voltage at pin LX, WAKE                                                                               | -0.3 | V <sub>VSUP</sub> + 0.3 | V     |                                                                                                                                                                                                                                                                                    |

| Voltage at pin RESET, INTN, RxD, TxD, CS, SCLK, SDO, SDA/SDI, I2C_EN                                  | -0.3 | 4.5                     | V     |                                                                                                                                                                                                                                                                                    |

| Input Supply slew-rate (V <sub>sup_slew</sub> )                                                       |      | 1                       | V/µs  | Input power supply ramp rate                                                                                                                                                                                                                                                       |

| Electrostatic Discharge                                                                               |      |                         |       |                                                                                                                                                                                                                                                                                    |

| Electrostatic discharge voltage                                                                       | ±2   |                         |       | All pins except VSUP, GND, CANH, CANL,<br>WAKE, SPLIT                                                                                                                                                                                                                              |

| AEC-Q100-002 human body model standard (ESD)                                                          | ±4   |                         | kV    | VSUP, GND, WAKE, SPLIT                                                                                                                                                                                                                                                             |

| (202)                                                                                                 | ±8   |                         |       | CANH, CANL                                                                                                                                                                                                                                                                         |

| Latch-Up Immunity                                                                                     | -100 | +100                    | mA    | AEC-Q100-004                                                                                                                                                                                                                                                                       |

| Continuous Power Dissipation                                                                          |      |                         |       |                                                                                                                                                                                                                                                                                    |

| Maximum power dissipation (Ptot)                                                                      |      | 1.2                     | W     |                                                                                                                                                                                                                                                                                    |

| Temperature Ranges and Storage Conditions                                                             |      |                         |       |                                                                                                                                                                                                                                                                                    |

| Junction temperature (TJ)                                                                             |      | 170                     | °C    |                                                                                                                                                                                                                                                                                    |

| Storage temperature (T <sub>stg</sub> )                                                               | -55  | +150                    | °C    |                                                                                                                                                                                                                                                                                    |

| Thermal resistance MLF package (R <sub>thj_36</sub> )                                                 |      | 30                      | °C/W  | SEMI G42-88                                                                                                                                                                                                                                                                        |

| Package body temperature (TBODY)                                                                      |      | 260                     | °C    | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".  The lead finish for Pb-free leaded packages is matte tin (100% Sn). |

| Moisture Sensitivity Level                                                                            |      | 3                       |       | Represents a maximum floor life time of 168h                                                                                                                                                                                                                                       |

<sup>1.</sup> All voltages mentioned above are referred with respect to ground reference voltage V<sub>GND</sub>.

# 6 Electrical Characteristics

Table 3. Electrical Characteristics

| Symbol              | Parameter                   | Conditions                                                                                   | Min           | Тур | Max           | Units |

|---------------------|-----------------------------|----------------------------------------------------------------------------------------------|---------------|-----|---------------|-------|

| Operating Con       | ditions                     |                                                                                              |               |     |               |       |

| Vsup                | Positive supply voltage     | Normal operating condition                                                                   | 6             |     | 18            | V     |

| GND                 | Ground                      | In reference to all the voltages                                                             | 0             |     |               | V     |

| Тамв                | Ambient temperature         | Junction temperature (T <sub>J</sub> ) ≤ 150°C (at full-load)                                | -40           |     | 105           | °C    |

|                     |                             | VSUP = 6V, LDOs at full load,<br>DCDC load = 390mA,<br>CAN dominant                          |               | 425 |               |       |

| Isupp               | Supply current, Normal mode | VSUP = 18V, LDOs at full load,<br>DCDC load = 390mA,<br>CAN dominant, not production tested. |               | 150 |               | mA    |

|                     |                             | VSUP = 16V, LDOs at full load,<br>CAN dominant                                               |               | 170 |               |       |

| CS                  |                             |                                                                                              |               |     |               |       |

| Vt-                 | Negative-Going Threshold    | V/LDO4 = 2.2V/                                                                               | 1.12          |     | 1.52          | V     |

| Vt+                 | Positive-Going Threshold    | - VLDO1 = 3.3V                                                                               | 1.77          |     | 2.23          | V     |

| I <sub>lil_cs</sub> | Pull up current             | In CS pad, Pulled up to VLDO1                                                                | -60           |     | -15           | μA    |

| SDO                 |                             |                                                                                              |               |     |               |       |

| V <sub>OH</sub>     | High level output voltage   |                                                                                              | 2.5           |     |               | V     |

| V <sub>OL</sub>     | Low level output voltage    | VSUP ≥ 6V                                                                                    |               |     | 0.4           | V     |

| I <sub>O</sub>      | Output drive current        |                                                                                              |               |     | 4             | mA    |

| SDA / SDI           |                             |                                                                                              |               |     |               |       |

| V <sub>IH</sub>     | High level input voltage    |                                                                                              | 0.7*<br>VLDO1 |     |               | V     |

| V <sub>IL</sub>     | Low level input voltage     |                                                                                              |               |     | 0.3*<br>VLDO1 | V     |

| $V_{OL}$            | Low level output voltage    |                                                                                              |               |     | 0.4           | V     |

| SCLK                |                             |                                                                                              |               |     |               |       |

| V <sub>IH</sub>     | High level input voltage    | Open-drain, external $500\Omega$ pull-up                                                     | 0.7*<br>VLDO1 |     |               | V     |

| V <sub>IL</sub>     | Low level input voltage     |                                                                                              |               |     | 0.3*<br>VLDO1 | V     |

| RESET, INTN         |                             |                                                                                              |               |     |               |       |

| $V_{OH}$            | High level output voltage   |                                                                                              | 2.5           |     |               | V     |

| $V_{OL}$            | Low level output voltage    | VSUP ≥ 6V                                                                                    |               |     | 0.4           | V     |

| l <sub>0</sub>      | Output drive current        |                                                                                              |               |     | 4             | mA    |

| TxD                 |                             |                                                                                              | <u> </u>      |     |               |       |

| V <sub>IH</sub>     | High level input voltage    |                                                                                              | 2.0           |     |               | V     |

| $V_{IL}$            | Low level input voltage     |                                                                                              |               |     | 0.8           | V     |

| l <sub>0</sub>      | Output drive current        | VSUP ≥ 6V                                                                                    |               |     | 1             | mA    |

| liii                | Pull-up current             | TxD pulled up to VLDO1 with control RxD pulled up to VLDO1                                   | -60           |     | -15           | μΑ    |

Table 3. Electrical Characteristics

| Symbol           | Parameter                 | Conditions                                                 | Min | Тур | Max | Units |  |  |  |

|------------------|---------------------------|------------------------------------------------------------|-----|-----|-----|-------|--|--|--|

| RxD              | RxD                       |                                                            |     |     |     |       |  |  |  |

| V <sub>OH</sub>  | High level output voltage |                                                            | 2.5 |     |     | V     |  |  |  |

| V <sub>OL</sub>  | Low level output voltage  |                                                            |     |     | 0.4 | ٧     |  |  |  |

| l <sub>0</sub>   | Output drive current      | VSUP ≥ 6V                                                  |     |     | 1   | mA    |  |  |  |

| I <sub>lil</sub> | Pull-up current           | TxD pulled up to VLDO1 with control RxD pulled up to VLDO1 | -60 |     | -15 | μA    |  |  |  |

# 6.1 Electrical System Specification

-40°C < TJ < 150°C

Table 4. Electrical System Specification

| Symbol   | Parameter                             | Conditions                         | Min | Тур | Max | Units |

|----------|---------------------------------------|------------------------------------|-----|-----|-----|-------|

| IDDnom   | Current consumption Normal mode       | No load, VSUP = 12V, CAN recessive |     | 3.5 | 6   | mA    |

| IDDrecv  | Current consumption Receive-only mode | No load, VSUP = 12V, CAN recessive |     | 1   | 2   | mA    |

| IDDstby  | Current consumption Standby mode      | No load, VSUP = 12V                |     | 135 | 270 | μA    |

| IDDsleep | Current consumption Sleep mode        | No load, VSUP = 12V                |     | 75  | 150 | μA    |

# 6.2 DCDC Converter

$-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}$ ; all voltages are with respect to ground, normal operating mode, unless otherwise mentioned.

Table 5. DCDC Converter

| Symbol           | Parameter                   | Conditions                                                                                               | Min  | Тур | Max  | Units |

|------------------|-----------------------------|----------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| VSUP             | Battery Voltage Range       |                                                                                                          | 6    | 12  | 18   | V     |

| V5V              | Output Voltage              |                                                                                                          | 4.75 | 5   | 5.25 | V     |

| I <sub>LXS</sub> | LX current limit            | For inductor 22µH and capacitor 100µF                                                                    | 0.8  | 1   | 1.25 | Α     |

| I <sub>V5V</sub> | DCDC output current         |                                                                                                          |      |     | 500  | mA    |

| R <sub>ON</sub>  | LX switch on-resistance     | (bondwire resistance included)                                                                           |      | 0.8 | 1    | Ω     |

| $V_{FB}$         | Reference Voltage for FB    |                                                                                                          | 4.75 | 5   | 5.25 | V     |

| Lireg_dc         | Line regulation             | Step from VIN = 6V to VIN2 = 18V,<br>ILOAD = 100mA<br>Lireg = 100*(VOUT1-VOUT2) /<br>[VOUT2*(VIN1-VIN2)] | -0.1 |     | +0.1 | % / V |

| Loreg_dc         | Load regulation             | ILOAD step from 90mA to 10mA<br>VSUP = 12V<br>Loreg = 100*(V_90mA-V_10mA) / V_90mA                       | -0.9 |     | +0.9 | %     |

| LX_ind           | Output inductor             |                                                                                                          | 10   |     | 22   | μH    |

| V5V_cer1         | Output ceramic capacitor 1  |                                                                                                          | 10   |     | 100  | μF    |

| V5V_esr1         | ESR of ceramic capacitor 1  |                                                                                                          | 0    |     | 0.05 | Ω     |

| V5V_cer2         | Output ceramic capacitor 2  | X7R type                                                                                                 | 100  |     | 220  | nF    |

| V5V_esr2         | ESR of ceramic capacitor 2  |                                                                                                          |      |     | 0.01 | Ω     |

| Csup             | Input capacitor (ceramic)   | For EMC suppression                                                                                      | 22   |     | 100  | μF    |

| Csup_esr         | iliput capacitor (ceraffic) |                                                                                                          |      |     | 1    | Ω     |

# 6.3 Low Drop Out Regulators

-40°C < Tj < 150°C; all voltages are with respect to ground, normal operating mode, unless otherwise mentioned. The LDO block is a linear voltage regulator, which provides a regulated (band-gap stabilized) output voltage from the DCDC converter output voltage (V5V).

Table 6. VLDO1 Block Specifications

| Symbol               | Parameter                    | Conditions                                                | Min   | Тур | Max   | Units |

|----------------------|------------------------------|-----------------------------------------------------------|-------|-----|-------|-------|

| V5V                  | Input Voltage Range          |                                                           | 4.75  | 5   | 5.25  | V     |

| I <sub>OUTLDO1</sub> | Output current               | Guaranteed by design.<br>Not production tested.           | 0     |     | 100   | mA    |

| VLDO1                | Output Voltage Range         |                                                           | 3.217 | 3.3 | 3.383 | V     |

| ICC_SH               | Output Short Circuit Current | Normal mode                                               |       |     | 300   | mA    |

| dVLDO1               | Line Regulation              | ΔVLDO1 / ΔV5V (static) for the input range, ILOAD = 100mA | -8    |     | 8     | mV/V  |

| LOREG_NM             | Load Regulation              | ΔVLDO1 (for 100mA > ILOAD > 1mA),<br>V5V = 5V             | -0.15 |     | +0.15 | mV/mA |

| CL2                  |                              | X7R type                                                  | 2     |     | 5     | μF    |

| ESR2                 | Output Capacitor (Ceramic)   |                                                           | 0.02  |     | 0.1   | Ω     |

| CL1                  |                              | X7R type                                                  | 100   |     | 220   | nF    |

| ESR1                 |                              |                                                           |       |     | 0.01  | Ω     |

Table 7. VLDO2<sup>1</sup> Block Specifications

| Symbol   | Parameter                    | Conditions                                                                              | Min            | Тур  | Max            | Units |

|----------|------------------------------|-----------------------------------------------------------------------------------------|----------------|------|----------------|-------|

| V5V      | Input Voltage Range          |                                                                                         | 4.75           | 5    | 5.25           | V     |

| IOUTLDO2 | Output current               | Guaranteed by design.<br>Not production tested.                                         | 0              |      | 120            | mA    |

| VLDO2    | Output Voltage Range         | VOUT (typ) depends on the trim code as in OTP register mapping. Default code gives 2.8V | 0.975*<br>Vout | Vout | 1.025*<br>Vout | V     |

| ICC_SH   | Output Short Circuit Current | Normal mode                                                                             |                |      | 300            | mA    |

| dVLDO2   | Line Regulation              | $\Delta$ VLDO2 / $\Delta$ V5V (static) for the input range, ILOAD = 100mA               | -8             |      | 8              | mV/V  |

| LOREG_NM | Load Regulation              | ΔVLDO2 (for 120mA > ILOAD > 1mA)                                                        | -0.15          |      | +0.15          | mV/mA |

| CL2      |                              | X7R type                                                                                | 2              |      | 5              | μF    |

| ESR2     | Output Capacitor (Ceramic)   |                                                                                         | 0.02           |      | 0.1            | Ω     |

| CL1      |                              | X7R type                                                                                | 100            |      | 220            | nF    |

| ESR1     |                              |                                                                                         |                |      | 0.01           | Ω     |

<sup>1.</sup> Factory setting: VouT = 2.8V.

Table 8. VLDO3<sup>1</sup> Block Specifications

| Symbol               | Parameter                    | Conditions                                                                              | Min            | Тур  | Max            | Units |

|----------------------|------------------------------|-----------------------------------------------------------------------------------------|----------------|------|----------------|-------|

| V5V                  | Input Voltage Range          |                                                                                         | 4.75           | 5    | 5.25           | V     |

| I <sub>OUTLDO3</sub> | Output current               | Guaranteed by design.<br>Not production tested.                                         | 0              |      | 100            | mA    |

| VLDO3                | Output Voltage Range         | VOUT (typ) depends on the trim code as in OTP register mapping. Default code gives 1.8V | 0.975*<br>Vout | Vout | 1.025*<br>Vout | V     |

| ICC_SH               | Output Short Circuit Current | Normal mode                                                                             |                |      | 300            | mA    |

| dVLDO3               | Line Regulation              | $\Delta$ VLDO3 / $\Delta$ V5V (static) for the input range, ILOAD = 100mA               | -8             |      | 8              | mV/V  |

| LOREG_NM             | Load Regulation              | ΔVLDO3 (for 100mA > ILOAD > 1mA)                                                        | -0.15          |      | +0.15          | mV/mA |

| CL2                  |                              | X7R type                                                                                | 2              |      | 5              | μF    |

| ESR2                 | Output Capacitor (Ceramic)   |                                                                                         | 0.02           |      | 0.1            | Ω     |

| CL1                  |                              | X7R type                                                                                | 100            |      | 220            | nF    |

| ESR1                 |                              |                                                                                         |                |      | 0.01           | Ω     |

<sup>1.</sup> Factory setting: VouT = 1.8V.

# 6.4 CAN Transceiver

$6 \text{V} < \text{VSUP} < 18 \text{V}; -40 ^{\circ}\text{C} < \text{Tj} < 150 ^{\circ}\text{C}; \text{ all voltages are with respect to ground}; 4.75 \text{V} < \text{V5V\_LDO1} < 5.25 \text{V}; \text{RL=}60 \Omega.$

Table 9. DC Electrical Characteristics

| Symbol    | Parameter                                               | Conditions                                                                      | Min  | Тур | Max  | Units |

|-----------|---------------------------------------------------------|---------------------------------------------------------------------------------|------|-----|------|-------|

| Driver    |                                                         |                                                                                 |      |     |      | •     |

| CANH_dom  | Developed autout vallege                                | V TvD = 0V                                                                      | 3    |     | 4.25 | V     |

| CANL_dom  | - Dominant output voltage                               | $V_TxD = 0V$                                                                    | 0.5  |     | 1.75 | V     |

| VO_dom_m  | Matching dominant output voltage V5V_LDO1-V_CANH-V_CANL |                                                                                 | -0.1 |     | 0.15 | V     |

| VO_diff   | Differential output voltage                             | $45\Omega$ < RL < $60\Omega$ ,<br>V_TxD = 0V (dominant)                         | 1.5  |     | 3    | V     |

|           | V_CANH-V_CANL                                           | No load; V_TxD = VLDO1 (recessive)                                              | -50  |     | 50   | mV    |

| VO_rec    | Recessive output voltage                                | V_TxD = VLDO1; No bus load,<br>Normal mode                                      | 2    |     | 3    | V     |

|           | V_CANH, V_CANL                                          | No bus load, Standby mode                                                       | -0.1 |     | 0.1  | V     |

| IO abort  | Chart aircuit autaut aurrant                            | V_TxD = 0V, V_CANH = 0V                                                         | -160 |     | -50  | mA    |

| IO_short  | Short circuit output current                            | V_TxD = 0V, V_CANL = 40V                                                        | +50  |     | +160 | mA    |

| IO_rec    | Recessive output current                                | -27V < V_CAN < 40V                                                              | -2.5 |     | +2.5 | mA    |

| Receiver  |                                                         |                                                                                 |      |     |      | •     |

| V/ DvD +h | Differential receiver threshold                         | -12V < V_CANH < 12V<br>-12V < V_CANL < 12V<br>Receive-only mode (CAN receiver)  | 0.5  |     | 0.9  | V     |

| V_RxD_th  | voltage                                                 | -12V < V_CANH < 12V<br>-12V < V_CANL < 12V<br>Standby mode (low-power receiver) | 0.4  |     | 1.15 | V     |

Table 9. DC Electrical Characteristics

| Symbol     | Parameter                                | Conditions                                                                     | Min              | Тур | Max              | Units |

|------------|------------------------------------------|--------------------------------------------------------------------------------|------------------|-----|------------------|-------|

| V_RxD_hys  | Differential receiver hysteresis voltage | -12V < V_CANH < 12V<br>-12V < V_CANL < 12V<br>Receive-only mode (CAN receiver) | 20               |     | 130              | mV    |

| I_RxD_LEAK | Input leakage current                    | V5V_LDO1 = 0V;<br>V_CANH = V_CANL = 5V                                         | 100              |     | 250              | μΑ    |

| R_IN_cm    | Common mode input resistance             | Tested in Receive-only mode                                                    | 15               |     | 35               | kΩ    |

| R_IN_cm_m  | Common mode input resistance matching    | V_CANH = V_CANL<br>(Tested in Receive-only mode)                               | -3               |     | +3               | %     |

| R_IN_diff  | Differential input resistance            | Tested in Receive-only mode                                                    | 25               |     | 75               | kΩ    |

| VO_SPLIT   | Output voltage on <b>SPLIT</b> pin       | Normal mode<br>-500μA < I_SPLIT < 500μA                                        | 0.3*<br>V5V_LDO1 |     | 0.7*<br>V5V_LDO1 | V     |

| IL SPLIT   | Lookago gurrant an SDLIT nin             | Standby mode<br>0V < V_SPLIT < 35V<br>(Not production tested)                  | -5               |     | +5               | μΑ    |

| IL_OPLII   | Leakage current on <b>SPLIT</b> pin      | Standby mode -22V < V_SPLIT < 0 (Not production tested)                        | -1               |     | +1               | mA    |

#### Table 10. AC Electrical Characteristics

| Symbol         | Parameter                                   | Conditions                                          | Min  | Тур | Max | Units |

|----------------|---------------------------------------------|-----------------------------------------------------|------|-----|-----|-------|

| t_TxD_BUS_on   | Delay TxD to bus dominant                   |                                                     | 10   |     | 110 | ns    |

| t_TxD_BUS_off  | Delay TxD to bus recessive                  |                                                     | 10   |     | 140 | ns    |

| t_BUS_on_RxD   | Delay bus dominant to RxD                   |                                                     | 15   |     | 115 | ns    |

| t_BUS_off_RxD  | Delay bus recessive to RxD                  |                                                     | 20   |     | 160 | ns    |

| t_TxD_RxD      | Propagation Delay TxD to RxD                |                                                     | 40   |     | 255 | ns    |

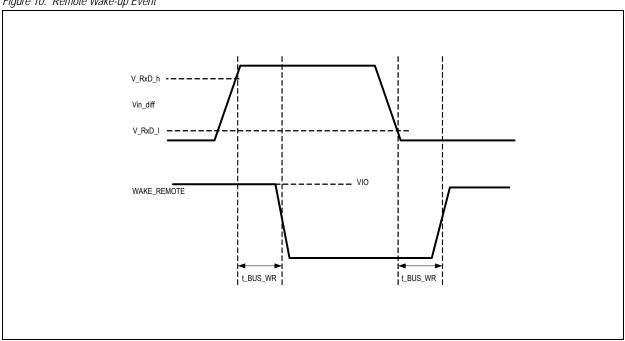

| WAKE UP via BU | S                                           |                                                     |      |     |     |       |

| t_BUS_WR       | Dominant time for wake-up detection via bus |                                                     | 0.75 |     | 5   | μs    |

| BUS Diagnostic |                                             |                                                     |      |     |     |       |

| t_OC_CANH      | Time to detect over current CANH            | V_TxD = 0V, V_CANH = 0V<br>(Not production tested)  | 60   |     |     | μs    |

| t_LC_CANH      | Time to detect low current CANH             | V_TxD = 0V, V_CANH = 40V<br>(Not production tested) | 60   |     |     | μs    |

| t_OC_CANL      | Time to detect over current CANL            | V_TxD = 0V, V_CANL = 40V<br>(Not production tested) | 60   |     |     | μs    |

| t_LC_CANL      | Time to detect low current CANL             | V_TxD = 0V, V_CANL = 0V<br>(Not production tested)  | 60   |     |     | μs    |

Table 11. Temperature Limiter

| Symbol             | Parameter                         | Conditions                                                                     | Min | Тур | Max | Units |

|--------------------|-----------------------------------|--------------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>jshut</sub> | Shut down temperature             | Junction temperature when IC shuts down                                        | 150 | 170 | 185 | °C    |

| T <sub>jrecv</sub> | Recovery temperature              | Junction temperature below which state machine returns from shutdown / warning | 125 | 140 | 155 | °C    |

| T <sub>jwarn</sub> | Over-temperature warning flag set | Junction temperature beyond which the warning flag is set                      | 140 | 157 | 175 | °C    |

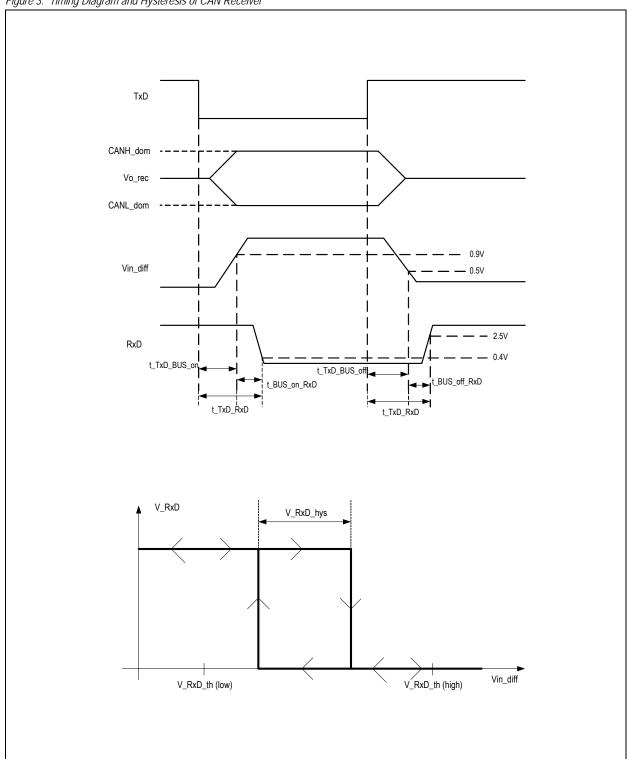

# 6.4.1 Timing Diagrams

Figure 3. Timing Diagram and Hysteresis of CAN Receiver

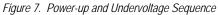

# 6.5 Undervoltage Detection

Table 12. Undervoltage Detection

| Symbol           | Parameter                                                   | Conditions                                                       | Min   | Тур  | Max   | Units    |

|------------------|-------------------------------------------------------------|------------------------------------------------------------------|-------|------|-------|----------|

| VSUP_POR         | VSUP Power on Reset threshold on                            | Rising edge of VSUP                                              | 5.09  | 5.5  | 5.91  | V        |

| VSUP_RESET       | VSUP Power on Reset threshold off                           | (Master Reset for Device)                                        | 4.49  | 4.85 | 5.21  | V        |

| VSUP_POKTH       | VSUP undervoltage threshold off                             | VSUP rising edge<br>(Brown out reset threshold)                  | 4.95  | 5.35 | 5.75  | V        |

| VSUP_UVTH        | VSUP undervoltage threshold on (CAN bus in recessive state) | VSUP falling edge<br>(Brown out reset threshold)                 | 4.625 | 5.0  | 5.375 | <b>V</b> |

| V5V_POKTH        | V5V undervoltage threshold off                              | Rising edge of V5V                                               | 4.16  | 4.5  | 4.84  | V        |

| V5V_UVTH         | V5V undervoltage threshold on                               | Falling edge of V5V                                              | 3.8   | 4.1  | 4.4   | V        |

| VLDO_POKTH       | LDO undervoltage threshold off (VLDO1, VLDO2 and VLDO3)     | Percent value is with respect to LDO output. Rising edge of LDO  | 87    | 89   | 91    | %        |

| VLDO_UVTH        | LDO undervoltage threshold on (VLDO1, VLDO2 and VLDO3)      | Percent value is with respect to LDO output. Falling edge of LDO | 78    | 80   | 82    | %        |

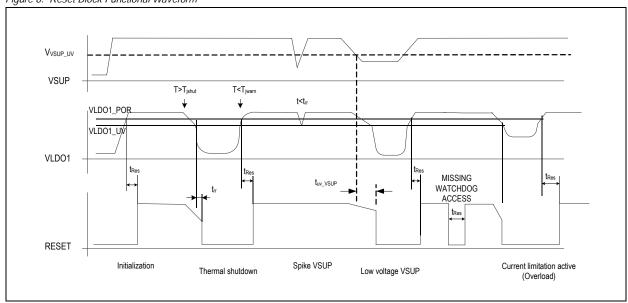

| t <sub>rr</sub>  | Spike filter on VLDO1                                       | To remove disturbance                                            | 2     | 4    | 8     | μs       |

| t <sub>Res</sub> | Reset delay time                                            |                                                                  | 4     | 8    | 12    | ms       |

# 6.6 Digital Timing Specification

# SPI Protocol.

Table 13. SPI Timing Parameters

| Symbol             | Parameter                             | Conditions                                         | Min | Тур | Max | Units |

|--------------------|---------------------------------------|----------------------------------------------------|-----|-----|-----|-------|

| General            |                                       |                                                    |     |     |     |       |

| BR <sub>SPI</sub>  | Bit rate                              |                                                    |     |     | 1   | Mbps  |

| T <sub>SCLKH</sub> | Clock high time                       |                                                    | 500 |     |     | ns    |

| T <sub>SCLKL</sub> | Clock low time                        |                                                    | 500 |     |     | ns    |

| Write Operation    | Parameters                            |                                                    |     |     |     |       |

| t <sub>DIS</sub>   | Data in setup time                    |                                                    | 20  |     |     | ns    |

| tDIH               | Data in hold time                     |                                                    | 10  |     |     | ns    |

| T <sub>CSH</sub>   | CS hold time                          |                                                    | 40  |     |     | ns    |

| Read Operation     | Parameters                            |                                                    |     |     |     |       |

| t <sub>DOD</sub>   | Data out delay                        |                                                    |     |     | 80  | ns    |

| tDOHZ              | Data out to high impedance delay      | Time for the SPI to release the SDO bus            |     |     | 80  | ns    |

| Timing Parame      | ters for SCLK Polarity Identification | 1                                                  |     |     |     |       |

| t <sub>CPS</sub>   | Clock setup time<br>(CLK polarity)    | Setup time of SCLK with respect to CS falling edge | 20  |     |     | ns    |

| t <sub>CPHD</sub>  | Clock hold time<br>(CLK polarity)     | Hold time of SCLK with respect to CS falling edge  | 20  |     |     | ns    |

# *I<sup>2</sup>C Protocol.* Electrical characteristics of SDA & SCLK bus lines for F/S mode

Table 14. I<sup>2</sup>C Electrical Parameters

| Cumahal         | Doromotor                                                                                 | Star      | ndard                   | Fa                             | st                      | Units                           |

|-----------------|-------------------------------------------------------------------------------------------|-----------|-------------------------|--------------------------------|-------------------------|---------------------------------|

| Symbol          | Parameter                                                                                 | Min       | Max                     | Min                            | Min Max                 |                                 |

| VIL             | Low level input voltage:<br>VLDO1related input levels                                     |           | 0.3V*LDO1               |                                | 0.3V*LDO1               | V                               |

| ViH             | High level input voltage:<br>VLDO1-related input levels                                   | 0.7V*LDO1 |                         | 0.7V*LDO1                      |                         | V                               |

| Vhys            | Hysteresis of Schmitt trigger input                                                       | n/a       | n/a                     | 0.05V*LDO1                     |                         | V                               |

| Vol1            | Low level output voltage (open drain or open collector) at 3mA sink current               |           | 0.4                     |                                | 0.4                     | V                               |

| t <sub>of</sub> | Output fall time from VIHmin to VILmax with a bus capacitance from 10pF to 400pF          |           | 250<br>(see Footnote 2) | 20 + 0.1Cb<br>(see Footnote 1) | 250<br>(see Footnote 2) | ns<br>(lab tested<br>only)      |

| t <sub>SP</sub> | Pulse width of spikes which must be suppressed by the input filter                        | n/a       | n/a                     |                                | 50                      | ns                              |

| li              | Input current of each I/O pin with an input voltage between 0.1VLDO1 and 0.9VLDO1 maximum | -10       | 10                      | -10<br>(see Footnote 3)        | 10 (see Footnote 3)     | μΑ                              |

| Ci              | Capacitance for each I/O pin                                                              |           | 10                      |                                | 10                      | pF<br>(guaranteed<br>by design) |

- 1. Cb = capacitance of one bus line in pF.

- 2. The maximum t<sub>f</sub> for the SDA and SCLK bus lines quoted in Table 15 (300ns) is longer than the specified maximum t<sub>of</sub> for the output stages (250ns). This allows for any series protection resistors to be connected between the SDA/SCLK pins and the SDA/SCLK bus lines without exceeding the maximum specified t<sub>f</sub>.

- 3. I/O pins of Fast-mode devices must not obstruct the SDA and SCLK lines if VLDO1 is switched off.

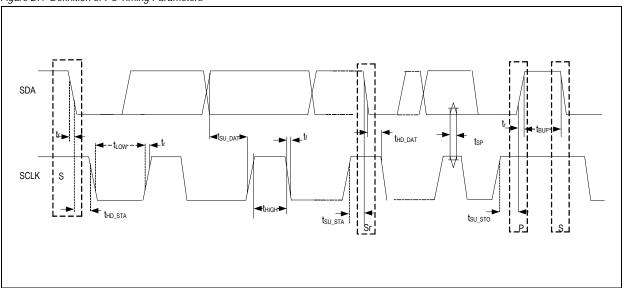

#### Characteristics of the SDA and SCLK Bus Lines for F/S Mode I<sup>2</sup>C Bus.

Table 15. I<sup>2</sup>C Timing Parameters

|                     |                                                                                                   | Stan               | dard                     | Fa                                           | ast                     |       |

|---------------------|---------------------------------------------------------------------------------------------------|--------------------|--------------------------|----------------------------------------------|-------------------------|-------|

| Symbol              | Parameter                                                                                         | Min                | Max                      | Min                                          | Max (see Footnote 1)    | Units |

| f <sub>SCLK</sub>   | SCLK clock frequency                                                                              | 0                  | 100                      | 0                                            | 400                     | kHz   |

| thd_sta             | Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated | 4                  | -                        | 0.6                                          | -                       | μs    |

| tLOW                | Low period of the SCLK clock                                                                      | 4.7                | -                        | 1.3                                          | -                       | μs    |

| tнісн               | High period of the SCLK clock                                                                     | 4.0                | -                        | 0.6                                          | -                       | μs    |

| tsu_sta             | Set-up time for a repeated START condition                                                        | 4.7                | -                        | 0.6                                          | -                       | μs    |

| t <sub>SU_DAT</sub> | Data set-up time                                                                                  | 250                | -                        | 100<br>(see Footnote 2)                      | -                       | ns    |

| t <sub>HD_DAT</sub> | Data hold-time                                                                                    | 0 (see Footnote 5) | 3450<br>(see Footnote 3) | 0 (see Footnote 5)                           | 900<br>(see Footnote 3) | ns    |

| t <sub>r</sub>      | Rise time of SDA and SCLK signals                                                                 | -                  | 1000                     | 20+<br>0.1C <sub>b</sub><br>(see Footnote 4) | 300                     | ns    |

| t <sub>f</sub>      | Fall time of SDA and SCLK signals                                                                 | -                  | 300                      | 20+<br>0.1C <sub>b</sub><br>(see Footnote 4) | 300                     | ns    |

| t <sub>SU_STO</sub> | Set-up time for STOP condition                                                                    | 4.0                | -                        | 0.6                                          | -                       | μs    |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                                  | 4.7                | -                        | 1.3                                          | -                       | μs    |

| C <sub>b</sub>      | Capacitive load for each bus line                                                                 | -                  | 400                      | -                                            | 400                     | pF    |

| V <sub>nL</sub>     | Noise margin at the Low level for each connected device (including hysteresis)                    | 0.1V*LDO1          | -                        | 0.1V*LDO1                                    | -                       |       |

| $V_{nH}$            | Noise margin at the High level for each connected device (including hysteresis)                   | 0.2V*LDO1          | -                        | 0.2V*LDO1                                    | -                       |       |

- 1. All values referred to  $V_{IHmin}$  and  $V_{Ilmax}$  levels (see Table 14).

- 2. A fast mode I²C bus device can be used in Standard mode I²C bus system, but the requirement t<sub>SU\_DAT</sub> ≥ 250ns must then be met. This will automatically be the case if the device do not stretch the low period of the SCLK signal. If such a device does stretch the low period of the SCLK signal, it must output the next data bit to the SDA line t<sub>rmax</sub>. T<sub>SU\_DAT</sub> = 1000 + 250 = 1250ns (according to standard mode I²C bus specification) before the SCLK line released.

- 3. The maximum t<sub>HD:DAT</sub> has only to be met if the device does not stretch the low period (t<sub>LOW</sub>) of the SCLK signal.

- 4. C<sub>b</sub> = total capacitance of one bus line in pF. If mixed with Hs-mode devices, faster fall-times according to Table 14 allowed.

- 5. This device internally provides a hold time of at least 300ns for the SDA signal to bridge the undefined region of the falling edge of the SCLK.

# 6.6.1 System Specification and Timings

Table 16. System Timing Parameters

| Symbol            | Parameter                                                                     | Conditions                                             | Min   | Тур  | Max   | Units       |

|-------------------|-------------------------------------------------------------------------------|--------------------------------------------------------|-------|------|-------|-------------|

| Mode Transition   | n Related Timing                                                              |                                                        |       |      |       | •           |

| T <sub>POST</sub> | Power-up to Standby mode                                                      | Reset time included,<br>Start-up watchdog not included |       |      | 70    | ms          |

| T <sub>STNO</sub> | Standby to Normal mode                                                        |                                                        |       |      | 10    | ms          |

| T <sub>SLST</sub> | Sleep to Standby mode                                                         | Reset time included                                    |       |      | 50    | ms          |

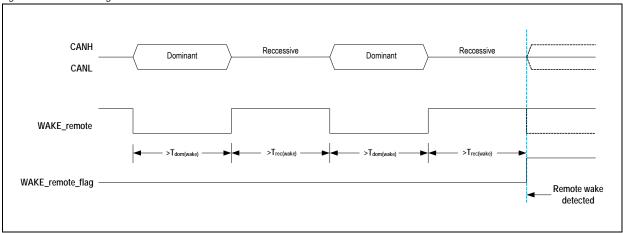

| Wake-up Timino    | ]                                                                             |                                                        |       |      |       |             |

| Tdom(wake)        | Minimum dominant pulse for CAN wake-up detection (remote wake)                |                                                        | 5     |      |       | μs          |

| Trec(wake)        | Minimum recessive pulse for CAN wake-up detection (remote wake)               |                                                        | 5     |      |       | μs          |

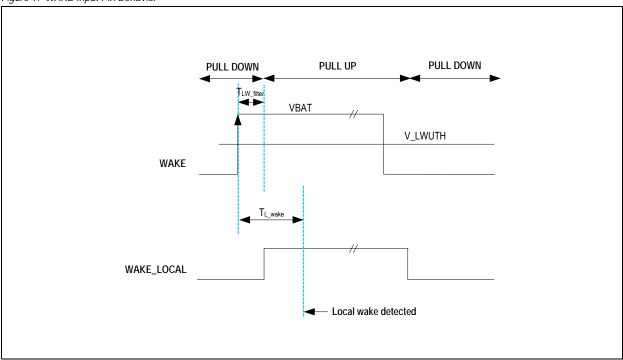

| TL_wake           | Time between edge on WAKE pin to local wake detection                         |                                                        |       | 32   |       | μs          |

| TLW_filter        | Time between edge on WAKE pin to<br>WAKE_LOCAL signal<br>(Filter on WAKE pin) |                                                        | 0.75  |      | 5     | μs          |

| TR_wake           | Remote wake detection time from the valid pattern detection                   |                                                        |       | 24   |       | μs          |

| TINTN             | INTN pin high time                                                            |                                                        | 7     |      |       | μs          |

| V_LWUTH           | Local WAKE threshold input                                                    |                                                        | 2     |      | 4     | V           |

| Local Failure Re  | elated Timing                                                                 |                                                        |       |      |       |             |

| TTxDC(dom)        | TxD dominant timeout period                                                   |                                                        | 600   | 1000 | 1400  | μs          |

| TBUSC(dom)        | BUS dominant clamping timeout period                                          |                                                        | 600   | 1000 | 1400  | μs          |

| Watchdog Timir    | ng & Timeouts                                                                 |                                                        |       |      |       |             |

| TWD(init)         | Start-up Watchdog timeout (initialization time)                               |                                                        |       | 300  |       | ms          |

| Twd_trig          | Window watchdog Trigger window                                                | Twwd_period is defined in WWD register                 | 0.375 | 0.5  | 0.625 | Twwd_period |

# 7 Detailed Description

The AS8650B consists of the following components on chip:

- DCDC converter with 5V outputs that supplies the three LDO voltage regulators and the CAN Transceiver

- Three voltage regulators with output voltages 3.3V, 2.8V and 1.8V and output accuracy up to 2.5%

- High-speed CAN bus Transceiver according to ISO 11898-5

- Integrated RESET unit with a power-on-reset delay and a programmable watchdog time

# 7.1 Operating Modes and States

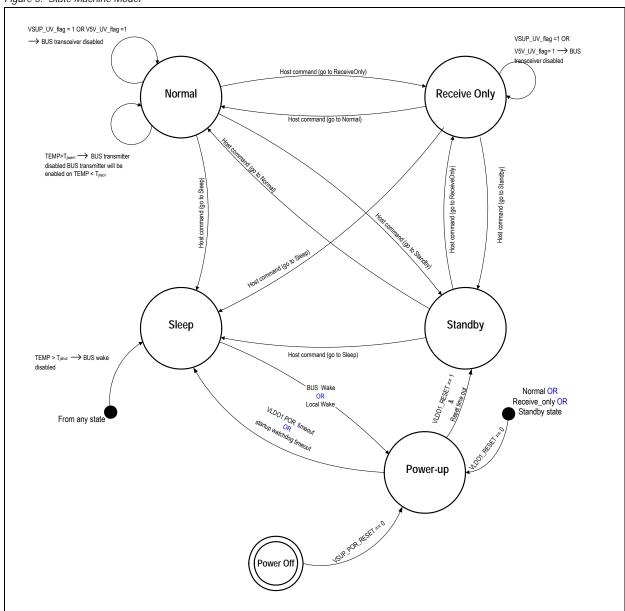

The AS8650B provides four main operating modes Normal, Receive-only, Standby, and Sleep. In Normal mode, the CAN Transceiver can be disabled in case of over-temperature condition. The detailed transition table for each mode is shown in the subsequent pages.

#### 7.1.1 Normal Mode

In Normal mode DCDC converter, the three voltage regulators, BUS Transceiver, and Window Watchdog are turned on with full functionality. All the LDO regulators are capable of delivering maximum load current possible as per their respective ratings. The BUS Transceiver is capable of sending the TxD data from the microcontroller to the CANH at the maximum rate.

#### 7.1.2 Receive-Only Mode

In this mode, the CAN transmitter is disabled. The CAN receiver, the three voltage regulators, and over-temperature monitor circuit are enabled.

#### 7.1.3 Standby Mode

This is the mode after power up. The Standby mode is a functional low-power mode where the CAN Transceiver is disabled. The bus wake-up (low power receiver) circuit, LDO1, and over-temperature monitor circuit are enabled. Both LDO2 and LDO3 can be enabled or disabled (default state) using the host command. The AS8650B can enter Normal mode, Sleep mode or Receive-only mode through host command.

#### 7.1.4 Sleep Mode

Sleep mode is the current saving mode that is entered by host command or by over-temperature condition. The DCDC converter, the three voltage regulators, CAN Transceiver, the reset, and window watchdog unit are all switched off. The bus wake-up (low power receiver) circuit, oscillator, and over-temperature monitor circuit are active. The bus is in recessive state (high). The only wake-up possible is through remote wake-up (through the bus lines) or local wake up (through the WAKE pin) as described in the WAKE specification. In the case of entering Sleep mode due to over-temperature condition ( $T > T_{jshut}$ ), the device can come out of Sleep only after the temperature falls back below the return temperature  $T_{irccv}$  and any one of the wake up events mentioned above.

#### 7.2 Power Management Strategy

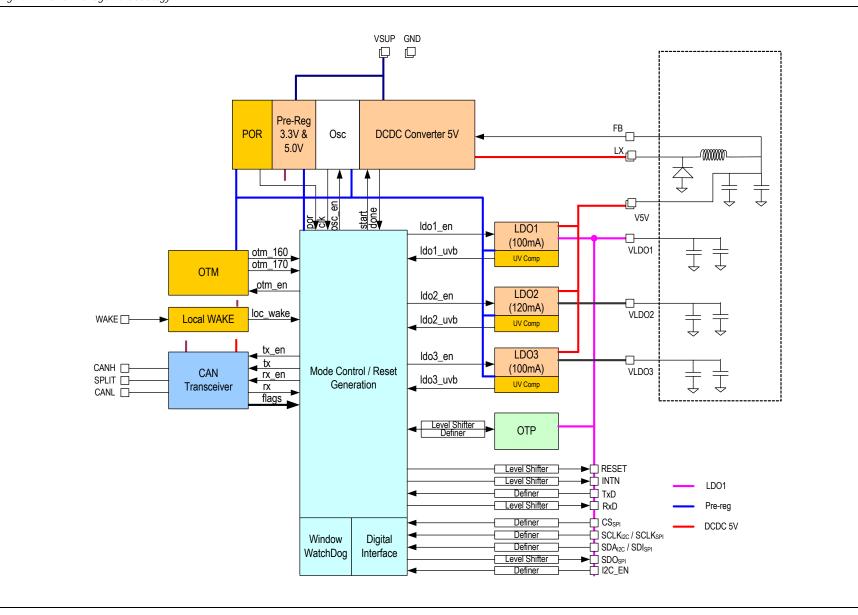

The detailed block diagram and the power management strategy are shown in Figure 4.

*Internal Regulator.* This module is powered externally by the VSUP. All the critical modules that needs to be kept always on, work on this supply. Some of the important modules among them are Over-temperature monitor, Local Wake block, Internal Power-on Reset module, Internal Oscillator, complete mode-control unit, Undervoltage comparators of three external LDOs.

*DCDC Converter.* This is the main supply regulator for all the internal blocks. A step-down hysteretic buck converter is used to generate 5V output from VSUP. This 5V output is then used to generate all the three LDOs. This high-efficiency step-down DCDC converter contains the following features:

- Current limited operation

- Thermal shutdown

*LDO1.* This is the main I/O supply. This is generated internally from the 5V DCDC converter output and gives a regulated 3.3V output to power-up the external micro-controller. All the I/Os that interface with the microcontroller work on this supply.

*LDO2*. This regulator is generated internally from the 5V DCDC converter output and gives a regulated 2.8V output. The voltage level can be changed through factory settings.

*LDO3.* This regulator is generated internally from the 5V DCDC converter output and gives a regulated 1.8V output. The voltage level can be changed through factory settings.

Revision 1.1

Table 17. Power Management Strategy for AS8650B

| Control States     | Power-up | Normal          | Rx Only         | Standby          | Sleep            |

|--------------------|----------|-----------------|-----------------|------------------|------------------|

| Analog Blocks      |          |                 |                 |                  |                  |

| DCDC Converter     | ON       | ON              | ON              | ON               | OFF <sup>1</sup> |

| Oscillator         | ON       | ON              | ON              | ON               | ON               |

| Internal Regulator | ON       | ON              | ON              | ON               | ON               |

| OTM                | ON       | ON              | ON              | ON               | ON               |

| LDO1               | ON       | ON              | ON              | ON               | OFF              |

| LDO2               | OFF      | ON <sup>2</sup> | ON <sup>2</sup> | OFF <sup>1</sup> | OFF              |

| LDO3               | OFF      | ON <sup>2</sup> | ON <sup>2</sup> | OFF <sup>1</sup> | OFF              |

| CAN Tx             | OFF      | ON              | OFF             | OFF              | OFF              |

| CAN Rx             | OFF      | ON              | ON              | OFF              | OFF              |

| Low Power Rx       | OFF      | OFF             | OFF             | ON               | ON               |

| LOCAL WAKE         | OFF      | OFF             | OFF             | ON               | ON               |

| SPLIT Generation   | OFF      | ON              | ON              | ON               | ON               |

| Digital Blocks     | •        |                 | •               | •                | •                |

| WWD                | OFF      | ON              | ON              | ON               | OFF              |

| Digital Interface  | OFF      | ON              | ON              | ON               | OFF              |

<sup>1.</sup> Can be turned ON using Device Configuration Register

<sup>2.</sup> Can be turned OFF using Device Configuration Register

## 7.3 State Diagram

Figure 5. State Machine Model

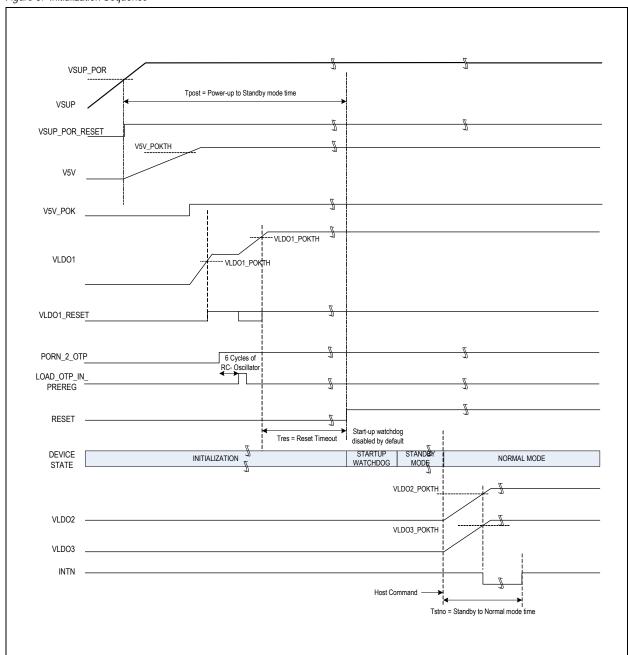

#### 7.4 Initialization Sequence

The DCDC converter is switched 'ON'. Subsequently, on receiving power-good (PG) signal from the DCDC converter, the LDO1 regulator is switched 'ON'. During the initialization sequence, the VLDO1 is set to 2.5V if VLDO1 > VLDO1\_POKTH threshold. VLDO1\_RESET is released to 'high'. Then, active-low PORN\_2\_OTP is generated.

Initially the rising edge of PORN\_2\_OTP loads contents into the OTP latch. Next the LOAD\_OTP\_IN\_PREREG signal loads the content of OTP latch into the pre-regulator domain register. Once the VLDO1\_POKTH threshold is reached, the reset timeout timer also starts.

The RESET signal expires after Reset timeout period T<sub>Res</sub>. After the RESET signal is 'high', the startup watchdog is launched. If the microcontroller generates a trigger within the startup window, then the device enters into Standby mode.

If the microcontroller fails to generate the trigger, then the RESET signal is generated and the Reset timeout will start.

If the microcontroller fails to generate the startup watchdog trigger for 3 consecutive times, then the device enters into Sleep mode. On receiving Normal mode command from the microcontroller, the LDO2 and LDO3 regulators are activated. By the time VLDO2 and VLDO3 reach their respective power-ok (POK) threshold values, an interrupt signal is generated. The AS8650B supports very slow VSUP ramp up of 0.5V/min.

The power initialization sequence diagram is shown in Figure 6.

- After activating the power supply on VSUP pin, the VSUP\_POR\_RESET flag becomes inactive (high) while the voltage exceeds the VSUP\_POR threshold.

- The DCDC output voltage V5V exceeds the V5V\_POKTH thresholds after the DCDC settling time and the first voltage regulator (LDO1) will be activated with the V5V\_POK set.

- If the voltage output at LDO1 (set to 2.5V on power-up) reaches the VLDO1\_POKTH threshold, the PORN\_2\_OTP flag is set and OTP register setting for the LDO1 is read. Consequently the output voltage will be regulated to the actual OTP settings.

- The initialization phase of the device is terminated after the preset output voltage level threshold is exceeded and the reset timeout is expired.

- After entering Standby mode the host controller can switch the device in any operation mode through the I²C or SPI interface.

Figure 6. Initialization Sequence

#### 7.5 DCDC Converter

The high-efficiency, high-voltage, hysteretic step-down DCDC converter, operates in asynchronous mode and delivers 500mA of output load to drive the three internal LDOs and the CAN Transceiver. The low-power architecture extends hold-up time in battery-backed and critical applications where maximum up-time over a wide input supply voltage range is needed, while still providing for high efficiencies of up to 90% during peak current demands.

## 7.6 Voltage Regulator LDO1

The stability of the voltage output is below ±2.5% over the full input range and temperature for load current up to 100mA at 3.3V. Power Input to this LDO is the V5V LDO1 pin. This LDO is activated in Normal, Receive-only or Standby mode. It is switched OFF in Sleep mode.

#### 7.7 Voltage Regulator LDO2