# WM8912

# Ultra Low Power DAC with Headphone Driver for Portable Audio Applications

# DESCRIPTION

The WM8912 is a high performance ultra-low power stereo DAC optimised for portable audio applications.

The device features stereo ground-referenced headphone amplifiers using the Wolfson 'Class-W' amplifier techniques incorporating an innovative dual-mode charge pump architecture - to optimise efficiency and power consumption during playback. The ground-referenced outputs eliminate headphone coupling capacitors. The outputs include common mode feedback paths to reject ground noise.

Control sequences for audio path setup can be pre-loaded and executed by an integrated control write sequencer to reduce software driver development and minimise pops and clicks via Wolfson's SilentSwitch™ technology.

A dynamic range controller provides compression and level control to support a wide range of portable recording applications. Anti-clip and quick release features offer good performance in the presence of loud impulsive noises. ReTune<sup>™</sup> Mobile 5-band parametric equaliser with fully programmable coefficients is integrated for optimization of speaker characteristics.

Common audio sampling frequencies are supported from a wide range of external clocks, either directly or generated using the integrated FLL.

The WM8912 can operate directly from a single 1.8V switched supply. For optimal power consumption, the digital core can be operated from a 1.0V supply.

# FEATURES

- 3.8mW quiescent power consumption for DAC to headphone playback

- DAC SNR 96dB typical, THD -86dB typical

- Class W ground-referenced headphone driver

- 28mW per channel into  $30\Omega$  at <1% THD

- 32mW per channel into 15Ω at <1% THD

- Dynamic range controller

- ReTune<sup>™</sup> Mobile parametric equalizer

- Integrated control write sequencer for pop minimised startup and shutdown

- Single register write for default start-up and shutdown sequences

- On-chip FLL provides all necessary clocks

- DAC supports standard sample rates from 8kHz to 96kHz

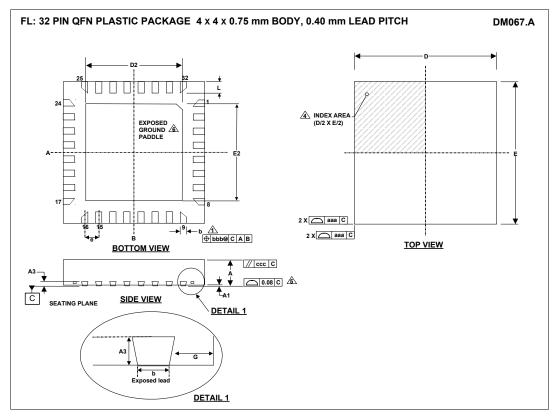

- 32-pin QFN package (4x4mm, 0.4mm pitch)

### APPLICATIONS

- Portable multimedia players

- Multimedia handsets

- Handheld gaming

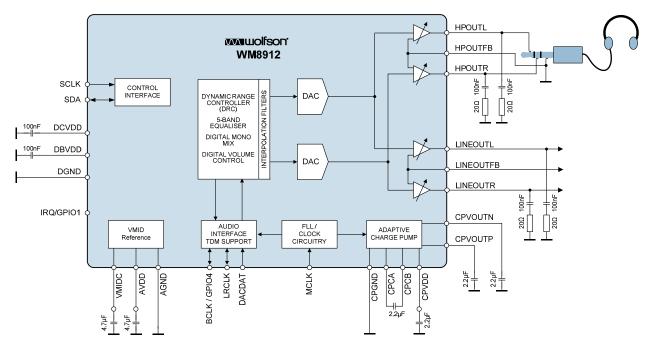

# **BLOCK DIAGRAM**

# TABLE OF CONTENTS

| DESCRIPTION                                                            | 1        |

|------------------------------------------------------------------------|----------|

| FEATURES                                                               | 1        |

| APPLICATIONS                                                           | 1        |

| BLOCK DIAGRAM                                                          | 2        |

| TABLE OF CONTENTS                                                      |          |

| PIN CONFIGURATION                                                      |          |

| ORDERING INFORMATION                                                   | -        |

| PIN DESCRIPTION                                                        |          |

| ABSOLUTE MAXIMUM RATINGS                                               |          |

| RECOMMENDED OPERATING CONDITIONS                                       | 00<br>0  |

|                                                                        |          |

| ELECTRICAL CHARACTERISTICS                                             |          |

|                                                                        |          |

| COMMON TEST CONDITIONS                                                 |          |

|                                                                        |          |

|                                                                        |          |

| FLL<br>OTHER PARAMETERS                                                |          |

| POWER CONSUMPTION                                                      |          |

| COMMON TEST CONDITIONS                                                 |          |

| POWER CONSUMPTION MEASUREMENTS                                         | LT       |

| SIGNAL TIMING REQUIREMENTS                                             |          |

| COMMON TEST CONDITIONS                                                 |          |

| MASTER CLOCK                                                           |          |

| AUDIO INTERFACE TIMING                                                 |          |

| MASTER MODE                                                            |          |

| SLAVE MODE                                                             |          |

|                                                                        |          |

| DIGITAL FILTER CHARACTERISTICS                                         |          |

| DAC FILTER RESPONSES                                                   | -        |

| DE-EMPHASIS FILTER RESPONSES                                           |          |

| DEVICE DESCRIPTION                                                     |          |

| INTRODUCTION                                                           |          |

| DYNAMIC RANGE CONTROL (DRC)                                            |          |

| COMPRESSION/LIMITING CAPABILITIES                                      | 22       |

| GAIN LIMITS                                                            | 24       |

| DYNAMIC CHARACTERISTICS                                                | 24       |

| ANTI-CLIP CONTROL                                                      |          |

| QUICK RELEASE CONTROL                                                  |          |

| GAIN SMOOTHING                                                         |          |

| INITIALISATION<br>RETUNE <sup>™</sup> MOBILE PARAMETRIC EQUALIZER (EQ) | 27<br>28 |

| DEFAULT MODE (5-BAND PARAMETRIC EQ)                                    |          |

| RETUNE™ MOBILE MODE                                                    |          |

| EQ FILTER CHARACTERISTICS                                              |          |

| DIGITAL MIXING                                                         |          |

| DAC INTERFACE ROUTING AND CONTROL                                      |          |

| DAC INTERFACE VOLUME BOOST                                             | 31       |

PD, Rev 4.1, February 2013

| DIGITAL-TO-ANALOGUE CONVERTER (DAC)               |   |

|---------------------------------------------------|---|

| DAC DIGITAL VOLUME CONTROL                        |   |

| DAC SOFT MUTE AND SOFT UN-MUTE                    |   |

| DAC MONO MIX                                      |   |

| DAC DE-EMPHASIS                                   |   |

| DAC SLOPING STOPBAND FILTER                       |   |

| DAC OVERSAMPLING RATIO (OSR)                      |   |

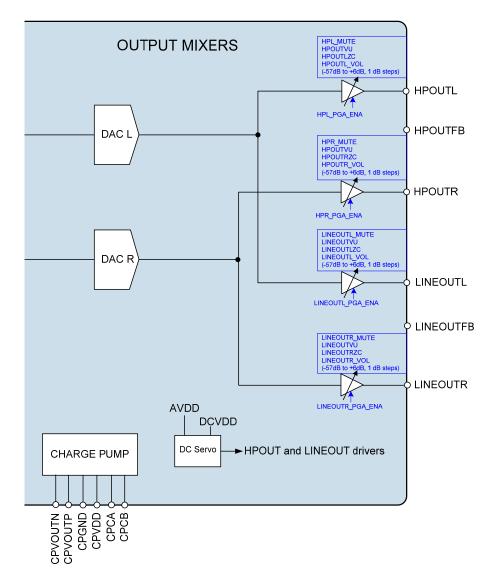

| OUTPUT SIGNAL PATH                                |   |

| OUTPUT SIGNAL PATHS ENABLE                        |   |

| HEADPHONE / LINE OUTPUT SIGNAL PATHS ENABLE       |   |

| OUTPUT VOLUME CONTROL                             |   |

| ANALOGUE OUTPUTS                                  |   |

| HEADPHONE OUTPUTS – HPOUTL AND HPOUTR             |   |

| LINE OUTPUTS – LINEOUTL AND LINEOUTR              |   |

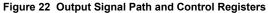

| EXTERNAL COMPONENTS FOR GROUND REFERENCED OUTPUTS |   |

| REFERENCE VOLTAGES AND MASTER BIAS                |   |

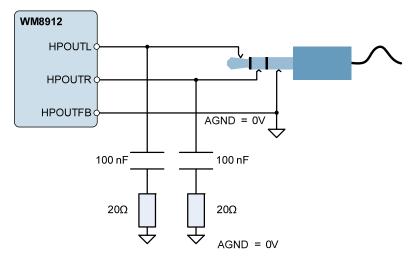

| CHARGE PUMP                                       |   |

| DC SERVO                                          | - |

| DC SERVO ENABLE AND START-UP                      |   |

| DC SERVO ACTIVE MODES                             |   |

| DC SERVO READBACK                                 |   |

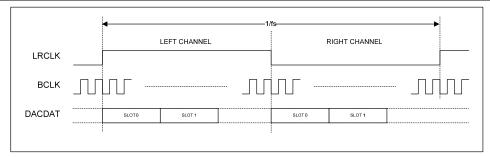

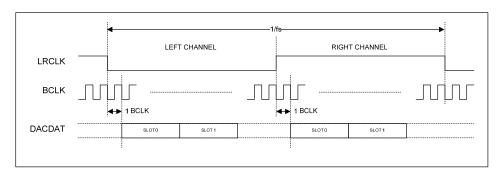

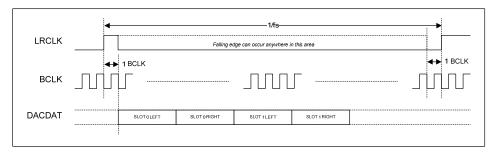

| DIGITAL AUDIO INTERFACE                           |   |

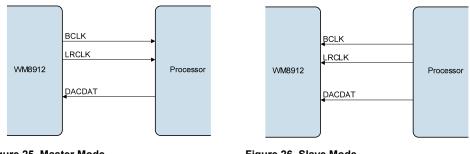

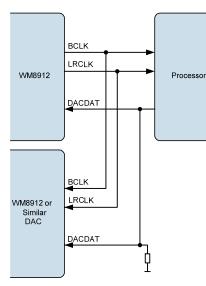

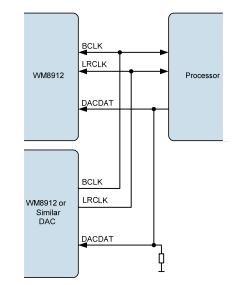

| MASTER AND SLAVE MODE OPERATION                   |   |

| OPERATION WITH TDM                                |   |

| BCLK FREQUENCY                                    |   |

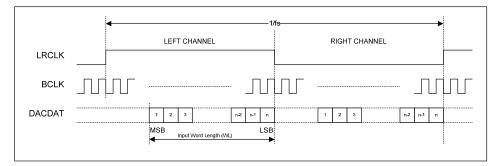

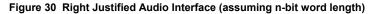

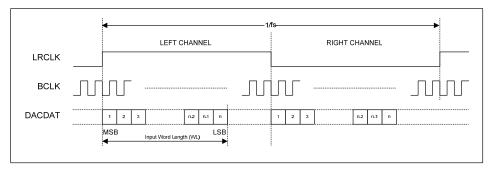

| AUDIO DATA FORMATS (NORMAL MODE)                  |   |

| AUDIO DATA FORMATS (TDM MODE)                     |   |

| DIGITAL AUDIO INTERFACE CONTROL                   |   |

| AUDIO INTERFACE OUTPUT TRI-STATE                  |   |

| BCLK AND LRCLK CONTROL                            |   |

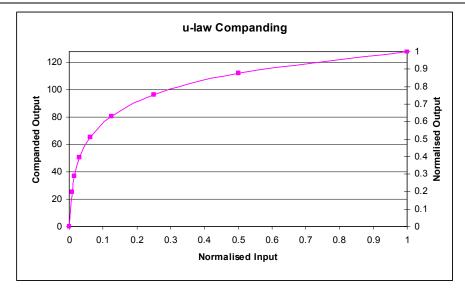

| COMPANDING                                        |   |

| DIGITAL PULL-UP AND PULL-DOWN                     |   |

|                                                   |   |

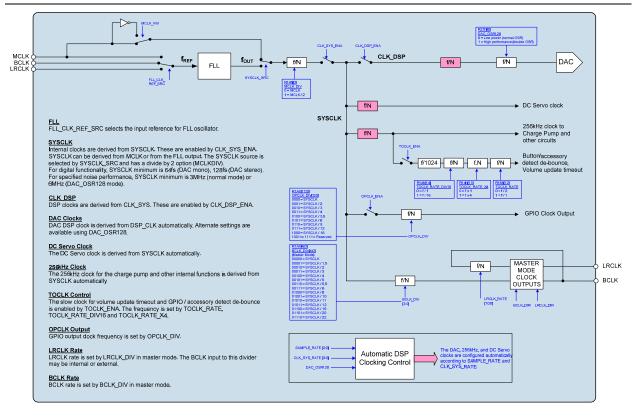

| SYSCLK CONTROL                                    |   |

|                                                   |   |

|                                                   |   |

|                                                   |   |

|                                                   |   |

| TOCLK CONTROL<br>DAC OPERATION AT 88.2K / 96K     |   |

| FREQUENCY LOCKED LOOP (FLL)                       |   |

| FREE-RUNNING FLL CLOCK                            |   |

| EXAMPLE FLL CALCULATION                           |   |

| GPIO OUTPUTS FROM FLL                             |   |

| EXAMPLE FLL SETTINGS                              |   |

| GENERAL PURPOSE INPUT/OUTPUT (GPIO)               |   |

| IRQ/GPI01                                         |   |

| BCLK/GPI01                                        |   |

| INTERRUPTS                                        |   |

| CONTROL INTERFACE                                 | _ |

| CONTROL WRITE SEQUENCER                           |   |

|                                                   |   |

| PROGRAMMING A SEQUENCE                            |   |

| DEFAULT SEQUENCES                                 |   |

|                                                   |   |

PD, Rev 4.1, February 2013

| START-UP SEQUENCE                 |     |

|-----------------------------------|-----|

| SHUTDOWN SEQUENCE                 | 88  |

| POWER-ON RESET                    | 90  |

| QUICK START-UP AND SHUTDOWN       | 91  |

| QUICK START-UP (DEFAULT SEQUENCE) |     |

| FAST START-UP FROM STANDBY        |     |

| QUICK SHUTDOWN (DEFAULT SEQUENCE) |     |

| SOFTWARE RESET AND CHIP ID        | 93  |

| REGISTER MAP                      |     |

| REGISTER BITS BY ADDRESS          |     |

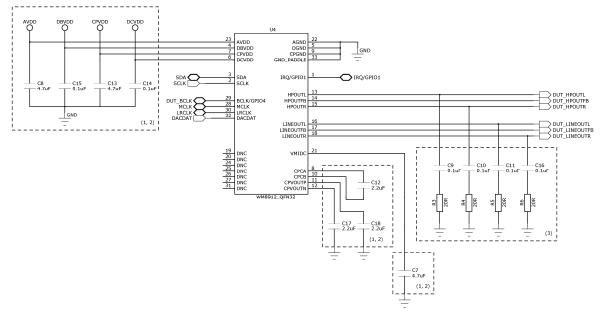

| APPLICATIONS INFORMATION          | 126 |

| RECOMMENDED EXTERNAL COMPONENTS   | 126 |

| PACKAGE DIMENSIONS                | 127 |

| IMPORTANT NOTICE                  | 128 |

| ADDRESS                           |     |

| REVISION HISTORY                  | 129 |

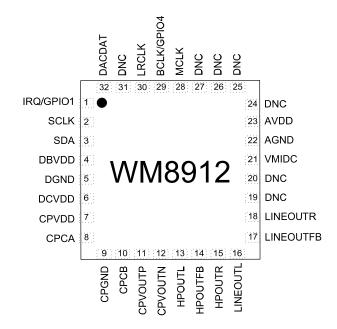

# **PIN CONFIGURATION**

The WM8912 is supplied in a 32-pin QFN package.

# **ORDERING INFORMATION**

| DEVICE         | TEMPERATURE<br>RANGE | PACKAGE                               | MOISTURE<br>SENSITIVITY<br>LEVEL | PEAK<br>SOLDERING<br>TEMPERATURE |

|----------------|----------------------|---------------------------------------|----------------------------------|----------------------------------|

| WM8912CGEFL/V  | -40°C to +85°C       | 32-lead QFN                           | MSL3                             | 260°C                            |

|                |                      | (4x4x0.4mm, lead-free)                |                                  |                                  |

| WM8912CGEFL/RV | -40°C to +85°C       | 32-lead QFN                           | MSL3                             | 260°C                            |

|                |                      | (4x4x0.4mm, lead-free, tape and reel) |                                  |                                  |

Note:

Reel quantity = 3,500

# **PIN DESCRIPTION**

| NAME       | QFN-32 | TYPE                   | DESCRIPTION                                                             |

|------------|--------|------------------------|-------------------------------------------------------------------------|

| IRQ/GPI01  | 1      | Digital Input / Output | GPIO1 / Interrupt                                                       |

| SCLK       | 2      | Digital Input          | Control interface clock input                                           |

| SDA        | 3      | Digital Input / Output | Control interface data input / output                                   |

| DBVDD      | 4      | Supply                 | Digital buffer supply (powers audio interface and control interface)    |

| DGND       | 5      | Supply                 | Digital ground (return path for DCVDD and DBVDD)                        |

| DCVDD      | 6      | Supply                 | Digital core supply                                                     |

| CPVDD      | 7      | Supply                 | Charge pump power supply                                                |

| CPCA       | 8      | Analogue Input         | Charge pump flyback capacitor pin                                       |

| CPGND      | 9      | Supply                 | Charge pump ground                                                      |

| CPCB       | 10     | Analogue Input         | Charge pump flyback capacitor pin                                       |

| CPVOUTP    | 11     | Analogue Output        | Charge pump positive supply decoupling (powers HPOUTL/R, LINEOUTL/R)    |

| CPVOUTN    | 12     | Analogue Output        | Charge pump negative supply decoupling (powers<br>HPOUTL/R, LINEOUTL/R) |

| HPOUTL     | 13     | Analogue Output        | Left headphone output (line or headphone output)                        |

| HPOUTFB    | 14     | Analogue Output        | Headphone output ground loop noise rejection feedback                   |

| HPOUTR     | 15     | Analogue Output        | Right headphone output (line or headphone output)                       |

| LINEOUTL   | 16     | Analogue Output        | Left line output 1 (line output)                                        |

| LINEOUTFB  | 17     | Analogue Output        | Line output ground loop noise rejection feedback                        |

| LINEOUTR   | 18     | Analogue Output        | Right line output 1 (line output)                                       |

| DNC        | 19     | n/a                    | Do Not Connect                                                          |

| DNC        | 20     | n/a                    | Do Not Connect                                                          |

| VMIDC      | 21     | Analogue Output        | Midrail voltage decoupling capacitor                                    |

| AGND       | 22     | Supply                 | Analogue power return                                                   |

| AVDD       | 23     | Supply                 | Analogue power supply                                                   |

| DNC        | 24     | n/a                    | Do Not Connect                                                          |

| DNC        | 25     | n/a                    | Do Not Connect                                                          |

| DNC        | 26     | n/a                    | Do Not Connect                                                          |

| DNC        | 27     | n/a                    | Do Not Connect                                                          |

| MCLK       | 28     | Digital Input          | Master clock for DAC                                                    |

| BCLK/GPIO4 | 29     | Digital Input / Output | Audio interface bit clock / GPIO4                                       |

| LRCLK      | 30     | Digital Input / Output | Audio interface left / right clock                                      |

| DNC        | 31     | n/a                    | Do Not Connect                                                          |

| DACDAT     | 32     | Digital Input          | DAC digital audio data                                                  |

| GND_PADDLE | 33     |                        | Die Paddle                                                              |

### Note:

It is recommended that the QFN ground paddle is connected to analogue ground on the application PCB.

# **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020 for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                           | MIN                 | MAX          |

|-------------------------------------|---------------------|--------------|

| AVDD, DCVDD                         | -0.3V               | +2.5V        |

| DBVDD,                              | -0.3V               | +4.5V        |

| CPVDD                               | -0.3V               | +2.2V        |

| HPOUTL, HPOUTR, LINEOUTL, LINEOUTR  | (CPVDD + 0.3V) * -1 | CPVDD + 0.3V |

| Voltage range digital inputs        | DGND -0.3V          | DBVDD +0.3V  |

| Voltage range analogue inputs       | AGND -0.3V          | AVDD +0.3V   |

| Temperature range, T <sub>A</sub>   | -40°C               | +85°C        |

| Storage temperature after soldering | -65°C               | +150°C       |

Notes:

- 1. Analogue and digital grounds must always be within 0.3V of each other.

- 2. All digital and analogue supplies are completely independent from each other; there is no restriction on power supply sequencing.

- 3. HPOUTL, HPOUTR, LINEOUTL, LINEOUTR are outputs, and should not normally become connected to DC levels. However, if the limits above are exceeded, then damage to the WM8912 may occur.

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                       | SYMBOL            | MIN  | ТҮР | MAX  | UNIT |

|---------------------------------|-------------------|------|-----|------|------|

| Digital supply range (Core)     | DCVDD             | 0.95 | 1.0 | 1.98 | V    |

| Digital supply range (Buffer)   | DBVDD             | 1.42 | 1.8 | 3.6  | V    |

| Analogue supplies range         | AVDD              | 1.71 | 1.8 | 2.0  | V    |

| Charge pump supply range        | CPVDD             | 1.71 | 1.8 | 2.0  | V    |

| Ground                          | DGND, AGND, CPGND |      | 0   |      | V    |

| Operating Temperature (ambient) | T <sub>A</sub>    | -40  | +25 | +85  | °C   |

# **ELECTRICAL CHARACTERISTICS**

### TERMINOLOGY

- Signal-to-Noise Ratio (dB) SNR is the difference in level between a full scale output signal and the device output noise with no signal applied, measured over a bandwidth of 20Hz to 20kHz. This ratio is also called idle channel noise. (No Auto-zero or Automute function is employed).

- Total Harmonic Distortion (dB) THD is the difference in level between a 1kHz full scale sinewave output signal and the first seven harmonics of the output signal. The amplitude of the fundamental frequency of the output signal is compared to the RMS value of the next seven harmonics and expressed as a ratio.

- 3. Total Harmonic Distortion + Noise (dB) THD+N is the difference in level between a 1kHz full scale sine wave output signal and all noise and distortion products in the audio band. The amplitude of the fundamental reference frequency of the output signal is compared to the RMS value of all other noise and distortion products and expressed as a ratio.

- 4. Channel Separation (dB) is a measure of the coupling between left and right channels. A full scale signal is applied to the left channel only, the right channel amplitude is measured. Then a full scale signal is applied to the right channel only and the left channel amplitude is measured. The worst case channel separation is quoted as a ratio.

- 5. Channel Level Matching (dB) measures the difference in gain between the left and the right channels.

- 6. Power Supply Rejection Ratio (dB) PSRR is a measure of ripple attenuation between the power supply pin and an output path. With the signal path idle, a small signal sine wave is summed onto the power supply rail, The amplitude of the sine wave is measured at the output port and expressed as a ratio.

- 7. All performance measurements carried out with 20kHz AES17 low pass filter for distortion measurements, and an A-weighted filter for noise measurement. Failure to use such a filter will result in higher THD and lower SNR and Dynamic Range readings than are found in the Electrical Characteristics. The low pass filter removes out of band noise; although it is not audible it may affect dynamic specification values.

# **COMMON TEST CONDITIONS**

Unless otherwise stated, the following test conditions apply throughout the following sections:

- DCVDD = 1.0V

- DBVDD = 1.8V

- AVDD = CPVDD =1.8V

- Ambient temperature = +25°C

- Audio signal: 1kHz sine wave, sampled at 48kHz with 24-bit data resolution

- SYSCLK\_SRC = 0 (system clock comes direct from MCLK, not from FLL).

Additional, specific test conditions are given within the relevant sections below.

# **OUTPUT SIGNAL PATH**

| Test conditions: HPOUTL_VOL = HPOU | $JIR_VOL = 111001$ | D (UOB)                                 |      | -     | -    |      |

|------------------------------------|--------------------|-----------------------------------------|------|-------|------|------|

| PARAMETER                          | SYMBOL             | TEST CONDITIONS                         | MIN  | TYP   | MAX  | UNIT |

| Output Power (per Channel)         | Po                 | 1% THD                                  |      | 28    |      | mW   |

|                                    |                    | $R_{Load}$ = 30 $\Omega$                |      | 0.92  |      | Vrms |

|                                    |                    |                                         |      | -0.76 |      | dBV  |

|                                    |                    | 1% THD                                  |      | 32    |      | mW   |

|                                    |                    | $R_{Load}$ = 15 $\Omega$                |      | 0.69  |      | Vrms |

|                                    |                    |                                         |      | -3.19 |      | dBV  |

| DC Offset                          |                    | DC servo enabled, calibration complete. | -1.5 |       | +1.5 | mV   |

| Signal to Noise Ratio              | SNR                | A-weighted                              | 90   | 96    |      | dB   |

| Total Harmonic Distortion + Noise  | THD+N              | R <sub>L</sub> =30Ω; P₀=2mW             |      | -91   |      |      |

|                                    |                    | R <sub>L</sub> =30Ω; P₀=20mW            |      | -84   |      |      |

|                                    |                    | R <sub>L</sub> =15Ω; P₀=2mW             |      | -87   | -80  | dB   |

|                                    |                    | R <sub>L</sub> =15Ω; P₀=20mW            |      | -85   |      |      |

| Channel Separation                 |                    | 1kHz signal, 0dBFS                      |      | 100   |      | 15   |

|                                    |                    | 10kHz signal, 0dBFS                     |      | 90    |      | dB   |

| Channel Level Matching             |                    | 1kHz signal, 0dBFS                      |      | +/-1  |      | dB   |

| Power Supply Rejection Ratio       | PSRR               | 217Hz, 100mVpk-pk                       |      | 75    |      | JD   |

|                                    |                    | 1kHz, 100mV pk-pk                       |      | 70    |      | dB   |

| Stereo Playback to Line-out - DAC input to | LINEOUTL+LIN              | NEOUTR pins with 10k $\Omega$ / 50 | 0pF load |      |      |        |

|--------------------------------------------|---------------------------|------------------------------------|----------|------|------|--------|

| Test conditions: LINEOUTL_VOL = LINEO      | UTR_VOL = 11 <sup>2</sup> | 1001b (0dB)                        |          |      |      |        |

| PARAMETER                                  | SYMBOL                    | TEST CONDITIONS                    | MIN      | TYP  | MAX  | UNIT   |

| Full Scale Output Signal Level             |                           | DAC 0dBFS output at                |          | 1.0  |      | Vrms   |

|                                            |                           | 0dB volume                         |          | 0    |      | dBV    |

|                                            |                           |                                    |          | 2.83 |      | Vpk-pk |

| DC offset                                  |                           | DC servo enabled.                  | -1.5     |      | +1.5 | mV     |

|                                            |                           | Calibration complete.              |          |      |      |        |

| Signal to Noise Ratio                      | SNR                       | A-weighted                         | 90       | 96   |      | dB     |

| Total Harmonic Distortion + Noise          | THD+N                     | 10kΩ load                          |          | -85  | -70  | dB     |

| Channel Separation                         |                           | 1kHz signal, 0dBFS                 |          | 100  |      |        |

|                                            |                           | 10kHz signal, 0dBFS                |          | 90   |      | dB     |

| Channel Level Matching                     |                           | 1kHz signal, 0dBFS                 |          | +/-1 |      | dB     |

| Power Supply Rejection Ratio               | PSRR                      | 217Hz, 100mVpk-pk                  |          | 62   |      | dD     |

|                                            |                           | 1kHz, 100mV pk-pk                  |          | 62   |      | dB     |

| Output PGAs (HP, LINE)   |                 |      |     |      |      |

|--------------------------|-----------------|------|-----|------|------|

| PARAMETER                | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

| Minimum PGA gain setting |                 |      | -57 |      | dB   |

| Maximum PGA gain setting |                 |      | 6   |      | dB   |

| PGA Gain Step Size       |                 |      | 1   |      | dB   |

| PGA gain accuracy        | +6dB to -40dB   | -1.5 |     | +1.5 | dB   |

| PGA gain accuracy        | -40dB to -57dB  | -1   |     | +1   | dB   |

| Mute attenuation         | HPOUTL/R        |      | 85  |      | dB   |

|                          | LINEOUTL/R      |      | 85  |      | dB   |

# CHARGE PUMP

| PARAMETER                                   | TEST CONDITIONS   | MIN | ТҮР      | MAX | UNIT |

|---------------------------------------------|-------------------|-----|----------|-----|------|

| Start-up Time                               |                   |     | 260      |     | μS   |

| CPCA                                        | Normal mode       |     | CPVDD    |     | V    |

|                                             | Low power mode    |     | CPVDD/2  |     | V    |

| СРСВ                                        | Normal mode       |     | -CPVDD   |     | V    |

|                                             | Low power mode    |     | -CPVDD/2 |     | V    |

| External component requirements             |                   |     |          |     |      |

| To achieve specified headphone output power | r and performance |     |          |     |      |

| Flyback Capacitor                           | at 2V             | 1   | 2.2      |     | μF   |

| (between CPCA and CPCB)                     |                   |     |          |     |      |

| CPVOUTN Capacitor                           | at 2V             | 2   | 2.2      |     | μF   |

| CPVOUTP Capacitor                           | at 2V             | 2   | 2.2      |     | μF   |

## FLL

| PARAMETER                            | SYMBOL           | TEST CONDITIONS                 | MIN   | TYP   | MAX  | UNIT |

|--------------------------------------|------------------|---------------------------------|-------|-------|------|------|

| Input Frequency                      | F <sub>REF</sub> | FLL_CLK_REF_DIV = 00            | 0.032 |       | 13.5 | MHz  |

|                                      |                  | FLL_CLK_REF_DIV = 01            | 0.064 |       | 27   | MHz  |

| Lock time                            |                  |                                 |       | 2     |      | ms   |

| Free-running mode start-up time      |                  | VMID enabled                    |       | 100   |      | μS   |

| Free-running mode frequency accuracy |                  | Reference supplied<br>initially |       | +/-10 |      | %    |

|                                      |                  | No reference provided           |       | +/-30 |      | %    |

# **OTHER PARAMETERS**

| VMID Reference                                                |                             |     |        |     |      |

|---------------------------------------------------------------|-----------------------------|-----|--------|-----|------|

| PARAMETER                                                     | TEST CONDITIONS             | MIN | ТҮР    | MAX | UNIT |

| Midrail Reference Voltage (VMID pin)                          |                             | -3% | AVDD/2 | +3% | V    |

| Charge up time (from fully discharged to +5% or -10% of VMID) | External capacitor<br>4.7µF |     | 890    |     | μS   |

| Digital Inputs / Outputs |                 |                        |           |     |           |      |

|--------------------------|-----------------|------------------------|-----------|-----|-----------|------|

| PARAMETER                | SYMBOL          | TEST CONDITIONS        | MIN       | ТҮР | MAX       | UNIT |

| Input HIGH Level         | V <sub>IH</sub> |                        | 0.7×DBVDD |     |           | V    |

| Input LOW Level          | VIL             |                        |           |     | 0.3×DBVDD | V    |

| Output HIGH Level        | V <sub>OH</sub> | I <sub>он</sub> = +1mA | 0.9×DBVDD |     |           | V    |

| Output LOW Level         | V <sub>OL</sub> | I <sub>OL</sub> = -1mA |           |     | 0.1×DBVDD | V    |

## POWER CONSUMPTION

The WM8912 power consumption is dependent on many parameters. Most significantly, it depends on supply voltages, sample rates, mode of operation, and output loading.

The power consumption on each supply rail varies approximately with the square of the voltage. Power consumption is greater at fast sample rates than at slower ones. When the digital audio interface is operating in Master mode, the DBVDD current is significantly greater than in Slave mode. (Note also that power savings can be made by using MCLK as the BCLK source in Slave mode.) The output load conditions (impedance, capacitance and inductance) can also impact significantly on the device power consumption.

### **COMMON TEST CONDITIONS**

Unless otherwise stated, the following test conditions apply throughout the following sections:

- Ambient temperature = +25°C

- Audio signal = quiescent (zero amplitude)

- Sample rate = 48kHz

- MCLK = 12.288MHz

- Audio interface mode = Slave (LRCLK\_DIR=0, BCLK\_DIR=0)

- SYSCLK\_SRC = 0 (system clock comes direct from MCLK, not from FLL)

Additional, variant test conditions are quoted within the relevant sections below. Where applicable, power dissipated in the headphone or line loads is included.

## POWER CONSUMPTION MEASUREMENTS

| Stereo Playback to Headphones | - DAC input to HPOUTL+HPOUTR pins with 30Ω load. |

|-------------------------------|--------------------------------------------------|

|                               |                                                  |

#### Test conditions:

VMID\_RES = 01 (for normal operation)

CP DYN PWR = 1 (Class-W, Charge pump controlled by real-time audio level)

| Variant test conditions                                                               | AV   | 'DD  | DC   | VDD  | DB   | VDD  | CP   | VDD  | TOTAL |

|---------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|-------|

|                                                                                       | v    | mA   | v    | mA   | v    | mA   | v    | mA   | mW    |

| 48kHz sample rate                                                                     | 1.80 | 1.69 | 1.00 | 0.76 | 1.80 | 0.00 | 1.80 | 0.31 | 4.38  |

| 8kHz sample rate                                                                      | 1.80 | 1.69 | 1.00 | 0.18 | 1.80 | 0.00 | 1.80 | 0.31 | 3.80  |

| 48kHz, Po = 0.1mW/channel<br>1kHz sine wave 0dBFS<br>HPOUT_VOL= -25dB<br>DAC_VOL= 0dB | 1.80 | 1.71 | 1.00 | 0.77 | 1.80 | 0.00 | 1.80 | 1.99 | 7.45  |

| 48kHz, Po = 1mW/channel<br>1kHz sine wave 0dBFS<br>HPOUT_VOL= -15dB<br>DAC_VOL= 0dB   | 1.80 | 1.73 | 1.00 | 0.77 | 1.80 | 0.00 | 1.80 | 5.61 | 13.99 |

| 48kHz sample rate, Master mode,<br>FLL enabled, MCLK input frequency =<br>13MHz       | 1.80 | 1.82 | 1.00 | 1.05 | 1.80 | 0.73 | 1.80 | 0.30 | 6.18  |

| 48kHz sample rate, Master mode,<br>FLL enabled, MCLK input frequency =<br>32.768kHz   | 1.80 | 1.83 | 1.00 | 0.94 | 1.80 | 0.76 | 1.80 | 0.29 | 6.14  |

# Stereo Playback to Line-out - DAC input to LINEOUTL+LINEOUTR or HPOUTL+HPOUTR pins with $10k\Omega$ / 50pF load Test conditions :

VMID\_RES = 01 (for normal operation)

CP\_DYN\_PWR = 1 (Class-W, Charge pump controlled by real-time audio level)

| Variant test conditions          | AVDD |      | DCVDD |      | DBVDD |      | CPVDD |      | TOTAL |

|----------------------------------|------|------|-------|------|-------|------|-------|------|-------|

|                                  | v    | mA   | v     | mA   | v     | mA   | v     | mA   | mW    |

| 48kHz sample rate                | 1.8  | 1.67 | 1     | 0.76 | 1.8   | 0.00 | 1.8   | 0.36 | 4.43  |

| 8kHz sample rate                 | 1.8  | 1.67 | 1     | 0.18 | 1.8   | 0.00 | 1.8   | 0.36 | 3.86  |

| 48kHz, Po = 0dBFS 1kHz sine wave | 1.8  | 1.78 | 1     | 0.77 | 1.8   | 0.00 | 1.8   | 2.27 | 8.09  |

**Note:** DC servo calibration is retained in this state as long as DCVDD is supplied. This allows fast, pop suppressed start-up from the off state.

| Variant test conditions               | AVDD |      | DCVDD |      | DBVDD |      | CPVDD |      | TOTAL |

|---------------------------------------|------|------|-------|------|-------|------|-------|------|-------|

|                                       | v    | mA   | v     | mA   | v     | mA   | v     | mA   | mW    |

| Off (default settings)                | 1.8  | 0.01 | 1     | 0.00 | 1.8   | 0.00 | 1.8   | 0.01 | 0.04  |

| No Clocks applied                     |      |      |       |      |       |      |       |      |       |

| Off (default settings)                | 1.8  | 0.01 | 1     | 0.02 | 1.8   | 0.00 | 1.8   | 0.01 | 0.06  |

| DACDAT, MCLK, BCLK, and LRCLK applied |      |      |       |      |       |      |       |      |       |

# SIGNAL TIMING REQUIREMENTS

# **COMMON TEST CONDITIONS**

Unless otherwise stated, the following test conditions apply throughout the following sections:

- Ambient temperature = +25°C

- DCVDD = 1.0V

- DBVDD = AVDD = CPVDD = 1.8V

- DGND = AGND = CPGND = 0V

Additional, specific test conditions are given within the relevant sections below.

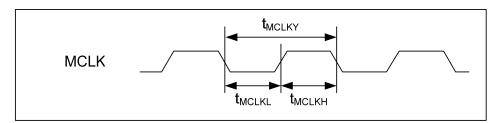

### MASTER CLOCK

Figure 1 Master Clock Timing

| Master Clock Timing |                     |                 |       |     |       |      |

|---------------------|---------------------|-----------------|-------|-----|-------|------|

| PARAMETER           | SYMBOL              | TEST CONDITIONS | MIN   | TYP | MAX   | UNIT |

| MCLK cycle time     | T <sub>MCLKY</sub>  | MCLK_DIV=1      | 40    |     |       | ns   |

|                     |                     | MCLK_DIV=0      | 80    |     |       | ns   |

| MCLK duty cycle     | T <sub>MCLKDS</sub> |                 | 60:40 |     | 40:60 |      |

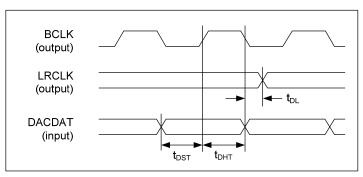

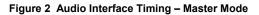

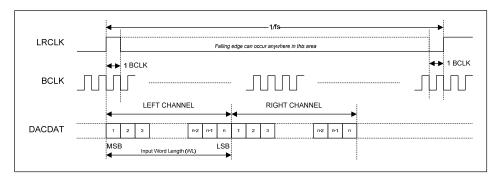

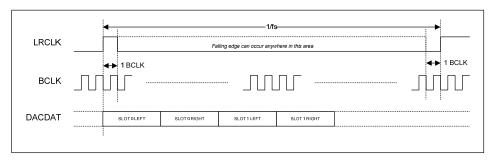

### AUDIO INTERFACE TIMING

### **Test Conditions**

DCVDD = 1.0V, AVDD = DBVDD = CPVDD = 1.8V, DGND=AGND=CPGND =0V,  $T_A$  = +25°C, Master Mode, fs=48kHz, MCLK=256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                      | SYMBOL           | MIN | TYP | MAX | UNIT |

|------------------------------------------------|------------------|-----|-----|-----|------|

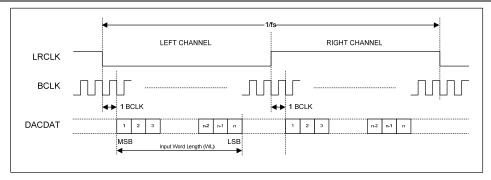

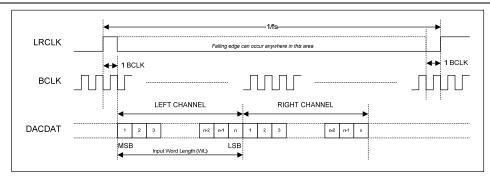

| Audio Interface Timing - Master Mode           |                  |     |     |     |      |

| LRCLK propagation delay from BCLK falling edge | t <sub>DL</sub>  |     |     | 20  | ns   |

| DACDAT setup time to BCLK rising edge          | t <sub>DST</sub> | 20  |     |     | ns   |

| DACDAT hold time from BCLK rising edge         | t <sub>DHT</sub> | 10  |     |     | ns   |

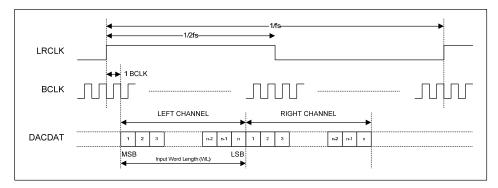

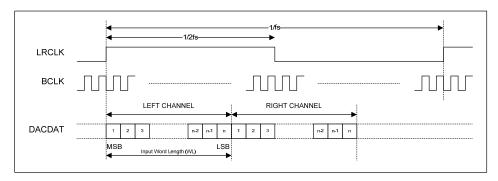

### SLAVE MODE

Figure 3 Audio Interface Timing – Slave Mode

### **Test Conditions**

DCVDD = 1.0V, AVDD = DBVDD = CPVDD = 1.8V, DGND=AGND=CPGND =0V,  $T_A$  = +25°C, Slave Mode, fs=48kHz, MCLK=256fs, 24-bit data, unless otherwise stated.

| PARAMETER                              | SYMBOL            | MIN | TYP | MAX | UNIT |

|----------------------------------------|-------------------|-----|-----|-----|------|

| Audio Interface Timing - Slave Mode    |                   |     |     |     |      |

| BCLK cycle time                        | t <sub>BCY</sub>  | 50  |     |     | ns   |

| BCLK pulse width high                  | t <sub>BCH</sub>  | 20  |     |     | ns   |

| BCLK pulse width low                   | t <sub>BCL</sub>  | 20  |     |     | ns   |

| LRCLK set-up time to BCLK rising edge  | t <sub>LRSU</sub> | 20  |     |     | ns   |

| LRCLK hold time from BCLK rising edge  | t <sub>LRH</sub>  | 10  |     |     | ns   |

| DACDAT hold time from BCLK rising edge | t <sub>DH</sub>   | 10  |     |     | ns   |

| DACDAT set-up time to BCLK rising edge | t <sub>DS</sub>   | 20  |     |     | ns   |

Note: BCLK period must always be greater than or equal to MCLK period.

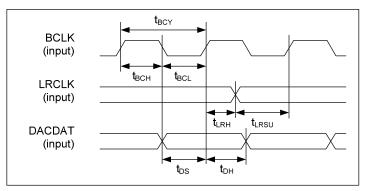

### CONTROL INTERFACE TIMING

### Figure 4 Control Interface Timing

#### **Test Conditions**

DCVDD = 1.0V, AVDD = DBVDD = CPVDD = 1.8V, DGND=AGND=CPGND =0V,  $T_A$ =+25°C, Slave Mode, fs=48kHz, MCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                     | SYMBOL          | MIN  | TYP | MAX | UNIT |

|-----------------------------------------------|-----------------|------|-----|-----|------|

| SCLK Frequency                                |                 |      |     | 400 | kHz  |

| SCLK Low Pulse-Width                          | t <sub>1</sub>  | 1300 |     |     | ns   |

| SCLK High Pulse-Width                         | t <sub>2</sub>  | 600  |     |     | ns   |

| Hold Time (Start Condition)                   | t <sub>3</sub>  | 600  |     |     | ns   |

| Setup Time (Start Condition)                  | t <sub>4</sub>  | 600  |     |     | ns   |

| Data Setup Time                               | t <sub>5</sub>  | 100  |     |     | ns   |

| SDA, SCLK Rise Time                           | t <sub>6</sub>  |      |     | 300 | ns   |

| SDA, SCLK Fall Time                           | t <sub>7</sub>  |      |     | 300 | ns   |

| Setup Time (Stop Condition)                   | t <sub>8</sub>  | 600  |     |     | ns   |

| Data Hold Time                                | t <sub>9</sub>  |      |     | 900 | ns   |

| Pulse width of spikes that will be suppressed | t <sub>ps</sub> | 0    |     | 5   | ns   |

# DIGITAL FILTER CHARACTERISTICS

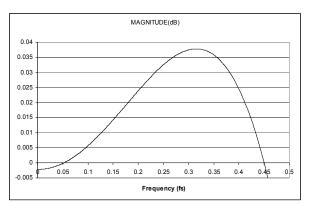

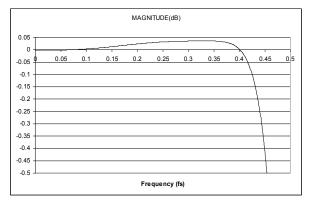

| PARAMETER                   | TEST CONDITIONS | MIN      | TYP    | MAX      | UNIT |

|-----------------------------|-----------------|----------|--------|----------|------|

| DAC Normal Filter           |                 |          |        |          |      |

| Passband                    | +/- 0.05dB      | 0        |        | 0.454 fs |      |

|                             | -6dB            |          | 0.5 fs |          |      |

| Passband Ripple             | 0.454 fs        |          |        | +/- 0.03 | dB   |

| Stopband                    |                 | 0.546 fs |        |          |      |

| Stopband Attenuation        | F > 0.546 fs    | -50      |        |          | dB   |

| DAC Sloping Stopband Filter |                 |          |        |          |      |

| Passband                    | +/- 0.03dB      | 0        |        | 0.25 fs  |      |

|                             | +/- 1dB         | 0.25 fs  |        | 0.454 fs |      |

|                             | -6dB            |          | 0.5 fs |          |      |

| Passband Ripple             | 0.25 fs         |          |        | +/- 0.03 | dB   |

| Stopband 1                  |                 | 0.546 fs |        | 0.7 fs   |      |

| Stopband 1 Attenuation      | f > 0.546 fs    | -60      |        |          | dB   |

| Stopband 2                  |                 | 0.7 fs   |        | 1.4 fs   |      |

| Stopband 2 Attenuation      | f > 0.7 fs      | -85      |        |          | dB   |

| Stopband 3                  |                 | 1.4 fs   |        |          |      |

| Stopband 3 Attenuation      | F > 1.4 fs      | -55      |        |          | dB   |

| DAC FILTERS      |             |  |  |  |

|------------------|-------------|--|--|--|

| Mode             | Group Delay |  |  |  |

| Normal           | 16.5 / fs   |  |  |  |

| Sloping Stopband | 18 / fs     |  |  |  |

# TERMINOLOGY

- 1. Stop Band Attenuation (dB) the degree to which the frequency spectrum is attenuated (outside audio band)

- 2. Pass-band Ripple any variation of the frequency response in the pass-band region

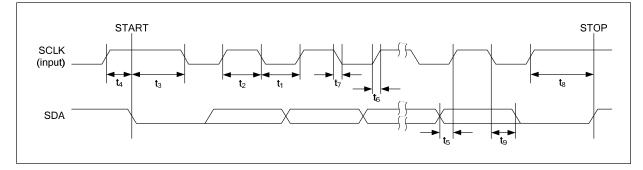

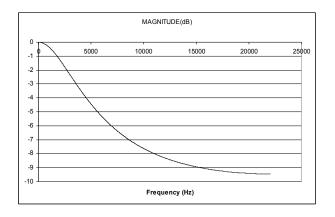

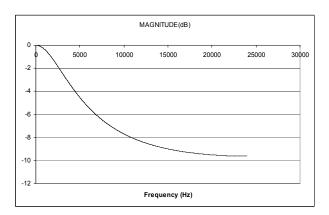

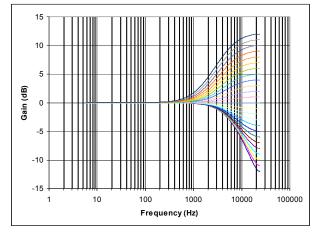

### DAC FILTER RESPONSES

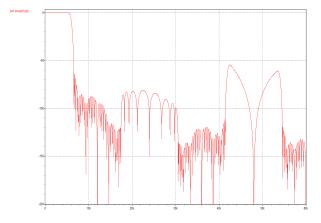

Figure 5 DAC Digital Filter Frequency Response; (Normal Mode); Sample Rate > 24kHz

Figure 7 DAC Digital Filter Frequency Response; (Sloping Stopband Mode); Sample Rate <= 24kHz

Figure 6 DAC Digital Filter Ripple (Normal Mode)

Figure 8 DAC Digital Filter Ripple (Sloping Stopband Mode)

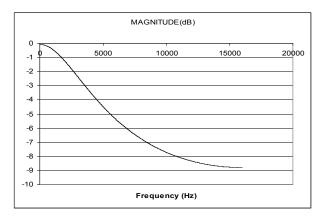

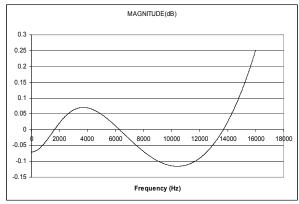

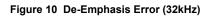

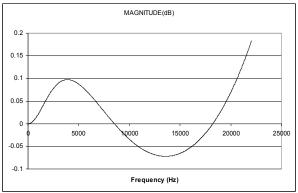

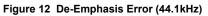

## **DE-EMPHASIS FILTER RESPONSES**

Figure 9 De-Emphasis Digital Filter Response (32kHz)

Figure 11 De-Emphasis Digital Filter Response (44.1kHz)

Figure 13 De-Emphasis Digital Filter Response (48kHz)

## **DEVICE DESCRIPTION**

### INTRODUCTION

The WM8912 is a high performance ultra-low power stereo DAC optimised for portable audio applications. Powerful digital signal processing (DSP) makes it ideal for small portable devices.

Two stereo pairs of ground-referenced Class-W outputs are provided, suitable for driving a stereo headphone and stereo line load simultaneously. The ground-referenced outputs are powered from an integrated Charge Pump, enabling high quality, power efficient outputs without requirement for DC blocking capacitors. A DC Servo circuit is available for DC offset correction, thereby suppressing pops and further reducing power consumption. Ground loop feedback is provided on the headphone outputs and on the line outputs, providing rejection of noise on the ground connections. All outputs use Wolfson SilentSwitch<sup>™</sup> technology for pop and click suppression.

The stereo DACs are of hi-fi quality, using a 24-bit low-order oversampling architecture to deliver optimum performance. A flexible clocking arrangement supports all commonly used DAC sample rates, either directly from an external MCLK or with the use of the integrated Frequency Locked Loop (FLL) for additional flexibility. DAC soft mute and un-mute is available for pop-free music playback.

The integrated Dynamic Range Controller (DRC) and ReTune<sup>™</sup> Mobile 5-band parametric equaliser (EQ) provide further processing capability of the digital audio paths. The DRC provides compression and signal level control to improve the handling of unpredictable signal levels. 'Anti-clip' and 'quick release' algorithms improve intelligibility in the presence of transients and impulsive noises. The EQ provides the capability to tailor the audio path according to the frequency characteristics of an earpiece or loudspeaker, and/or according to user preferences.

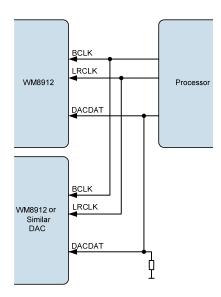

The WM8912 has a highly flexible digital audio interface, supporting a number of protocols, including I<sup>2</sup>S, DSP, MSB-first left/right justified, and can operate in master or slave modes. PCM operation is supported in the DSP mode. A-law and  $\mu$ -law companding are also supported. Time division multiplexing (TDM) is available to allow multiple devices to stream data simultaneously on the same bus, saving space and power.

The system clock (SYSCLK) provides clocking for the DACs, DSP core, digital audio interface and other circuits. SYSCLK can be derived directly from the MCLK pin or via the integrated FLL, providing flexibility to support a wide range of clocking schemes. Typical portable system MCLK frequencies and commonly used sample rates from 8kHz to 48kHz are all supported. The clocking circuits are configured automatically from the sample rate and from the MCLK / SYSCLK ratio.

The integrated FLL can be used to generate SYSCLK from a wide variety of different reference sources and frequencies. The FLL can accept a wide range of reference frequencies, which may be high frequency (e.g. 13MHz) or low frequency (eg. 32.768kHz). The FLL is tolerant of jitter and may be used to generate a stable SYSCLK from a less stable input signal. The integrated FLL can be used as a free-running oscillator, enabling autonomous clocking of the Headphone Charge Pump and DC Servo if required.

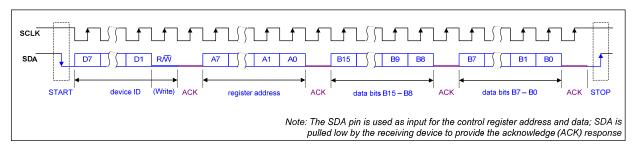

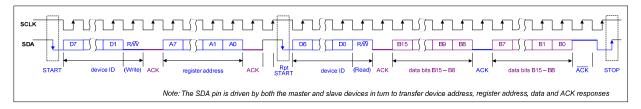

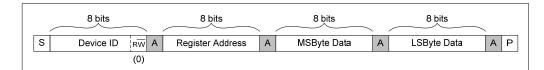

The WM8912 uses a standard 2-wire control interface, providing full software control of all features, together with device register readback. An integrated Control Write Sequencer enables automatic scheduling of control sequences; commonly-used signal configurations may be selected using ready-programmed sequences, including time-optimised control of the WM8912 pop suppression features. It is an ideal partner for a wide range of industry standard microprocessors, controllers and DSPs. Unused circuitry can be disabled under software control, in order to save power; low leakage currents enable extended standby/off time in portable battery-powered applications.

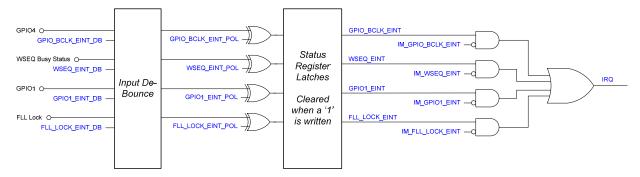

Two GPIO pins may be configured for miscellaneous input/output functions such as button/accessory detect inputs, or for clock, system status, or programmable logic level output for control of additional external circuitry. Interrupt logic, status readback and de-bouncing options are supported within this functionality.

### DYNAMIC RANGE CONTROL (DRC)

The dynamic range controller (DRC) is a circuit which can be enabled in the digital DAC playback path. The function of the DRC is to adjust the signal gain in conditions where the input amplitude is unknown or varies over a wide range, e.g. when recording from microphones built into a handheld system. The DRC can apply Compression and Automatic Level Control to the signal path. It incorporates 'anti-clip' and 'quick release' features for handling transients in order to improve intelligibility in the presence of loud impulsive noises.

The DRC is enabled in the digital DAC playback path by setting DRC\_ENA and DRC\_DAC\_PATH, as shown in Table 1. Both bits must be set for DRC operation.

| REGISTER<br>ADDRESS | BIT | LABEL       | DEFAULT | DESCRIPTION     |

|---------------------|-----|-------------|---------|-----------------|

| R40 (28h)           | 15  | DRC_ENA     | 0       | DRC enable      |

| DRC Control 0       |     |             |         | 0 = disabled    |

|                     |     |             |         | 1 = enabled     |

|                     | 14  | DRC_DAC_PAT | 0       | DRC path select |

|                     |     | Н           |         | 0 = Reserved    |

|                     |     |             |         | 1 = DAC path    |

Table 1 DRC Enable

#### **COMPRESSION/LIMITING CAPABILITIES**

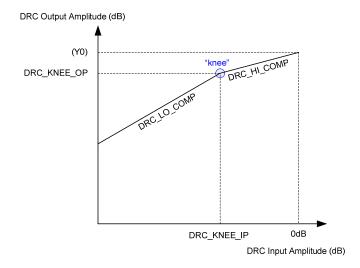

The DRC supports two different compression regions, separated by a "knee" at input amplitude T. For signals above the knee, the compression slope DRC\_HI\_COMP applies; for signals below the knee, the compression slope DRC\_LO\_COMP applies.

The overall DRC compression characteristic in "steady state" (i.e. where the input amplitude is nearconstant) is illustrated in Figure 15.

The slope of the DRC response is determined by register fields DRC\_HI\_COMP and DRC\_LO\_COMP respectively. A slope of 1 indicates constant gain in this region. A slope less than 1 represents compression (i.e. a change in input amplitude produces only a smaller change in output amplitude). A slope of 0 indicates that the target output amplitude is the same across a range of input amplitudes; this is infinite compression.

The "knee" in Figure 15 is determined by register fields DRC\_KNEE\_IP and DRC\_KNEE\_OP.

Parameter Y0, the output level for a 0dB input, is not specified directly, but can be calculated from the other parameters, using the equation.

Y0 = DRC\_KNEE\_OP - (DRC\_KNEE\_IP \* DRC\_HI\_COMP)

The DRC Compression parameters are defined in Table 2.

| REGISTER<br>ADDRESS        | BIT  | LABEL                | DEFAULT | DESCRIPTION                                |

|----------------------------|------|----------------------|---------|--------------------------------------------|

| R43 (2Bh)<br>DRC Control 3 | 10:5 | DRC_KNEE_IP<br>[5:0] | 00_0000 | Input signal at the Compressor<br>'knee'.  |

| Dito control o             |      |                      |         | 000000 = 0dB                               |

|                            |      |                      |         | 000001 = -0.75dB                           |

|                            |      |                      |         | 000010 = -1.5dB                            |

|                            |      |                      |         | (-0.75dB steps)                            |

|                            |      |                      |         | 111100 = -45dB                             |

|                            |      |                      |         | 111101 to 111111 = Reserved                |

|                            | 4:0  | DRC_KNEE_OP<br>[4:0] | 0_0000  | Output signal at the Compressor<br>'knee'. |

|                            |      |                      |         | 00000 = 0dB                                |

|                            |      |                      |         | 00001 = -0.75dB                            |

|                            |      |                      |         | 00010 = -1.5dB                             |

|                            |      |                      |         | (-0.75dB steps)                            |

|                            |      |                      |         | 11110 = -22.5dB                            |

|                            |      |                      |         | 11111 = Reserved                           |

| R42 (2Ah)                  | 5:3  | DRC_HI_COMP          | 000     | Compressor slope (upper region)            |

| DRC Control 2              |      | [2:0]                |         | 000 = 1 (no compression)                   |

|                            |      |                      |         | 001 = 1/2                                  |

|                            |      |                      |         | 010 = 1/4                                  |

|                            |      |                      |         | 011 = 1/8                                  |

|                            |      |                      |         | 100 = 1/16                                 |

|                            |      |                      |         | 101 = 0                                    |

|                            |      |                      |         | 110 to 111 = Reserved                      |

|                            | 2:0  | DRC_LO_COMP          | 000     | Compressor slope (lower region)            |

|                            |      | [2:0]                |         | 000 = 1 (no compression)                   |

|                            |      |                      |         | 001 = 1/2                                  |

|                            |      |                      |         | 010 = 1/4                                  |

|                            |      |                      |         | 011 = 1/8                                  |

|                            |      |                      |         | 100 = 0                                    |

|                            |      |                      |         | 101 to 111 = Reserved                      |

Table 2 DRC Compression Control

### GAIN LIMITS

The minimum and maximum gain applied by the DRC is set by register fields DRC\_MINGAIN and DRC\_MAXGAIN. These limits can be used to alter the DRC response from that illustrated in Figure 15. If the range between maximum and minimum gain is reduced, then the extent of the dynamic range control is reduced. The maximum gain prevents quiet signals (or silence) from being excessively amplified.

| REGISTER<br>ADDRESS        | BIT | LABEL                | DEFAULT | DESCRIPTION                                                                                                               |

|----------------------------|-----|----------------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| R41 (29h)<br>DRC Control 1 | 3:2 | DRC_MINGAIN [1:0]    | 10      | Minimum gain the DRC can use<br>to attenuate audio signals<br>00 = 0dB (default)<br>01 = -6dB<br>10 = -12dB<br>11 = -18dB |

|                            | 1:0 | DRC_MAXGAIN<br>[1:0] | 00      | Maximum gain the DRC can use<br>to boost audio signals<br>00 = 12dB<br>01 = 18dB (default)<br>10 = 24dB<br>11 = 36dB      |

Table 3 DRC Gain Limits

### DYNAMIC CHARACTERISTICS

The dynamic behaviour determines how quickly the DRC responds to changing signal levels. Note that the DRC responds to the average (RMS) signal amplitude over a period of time.

DRC\_ATK determines how quickly the DRC gain decreases when the signal amplitude is high. DRC\_DCY determines how quickly the DRC gain increases when the signal amplitude is low.

These register fields are described in Table 4. Note that the register defaults are suitable for general purpose microphone use.

| REGISTER<br>ADDRESS | BIT   | LABEL         | DEFAULT | DESCRIPTION                    |

|---------------------|-------|---------------|---------|--------------------------------|

| R41 (29h)           | 15:12 | DRC_ATK [3:0] | 0011    | Gain attack rate (seconds/6dB) |

| DRC Control 1       |       |               |         | 0000 = Reserved                |

|                     |       |               |         | 0001 = 182µs                   |

|                     |       |               |         | 0010 = 363µs                   |

|                     |       |               |         | 0011 = 726µs (default)         |

|                     |       |               |         | 0100 = 1.45ms                  |

|                     |       |               |         | 0101 = 2.9ms                   |

|                     |       |               |         | 0110 = 5.8ms                   |

|                     |       |               |         | 0111 = 11.6ms                  |

|                     |       |               |         | 1000 = 23.2ms                  |

|                     |       |               |         | 1001 = 46.4ms                  |

|                     |       |               |         | 1010 = 92.8ms                  |

|                     |       |               |         | 1011-1111 = Reserved           |

### WM8912

| REGISTER<br>ADDRESS | BIT  | LABEL         | DEFAULT | DESCRIPTION                   |

|---------------------|------|---------------|---------|-------------------------------|

|                     | 11:8 | DRC_DCY [3:0] | 0010    | Gain decay rate (seconds/6dB) |

|                     |      |               |         | 0000 = 186ms                  |

|                     |      |               |         | 0001 = 372ms                  |

|                     |      |               |         | 0010 = 743ms (default)        |

|                     |      |               |         | 0011 = 1.49s                  |

|                     |      |               |         | 0100 = 2.97s                  |

|                     |      |               |         | 0101 = 5.94s                  |

|                     |      |               |         | 0110 = 11.89s                 |

|                     |      |               |         | 0111 = 23.78s                 |

|                     |      |               |         | 1000 = 47.56s                 |

|                     |      |               |         | 1001-1111 = Reserved          |

Table 4 DRC Attack and Decay Rates

#### Note:

For detailed information about DRC attack and decay rates, please see Wolfson application note WAN0247.

### ANTI-CLIP CONTROL

The DRC includes an Anti-Clip feature to avoid signal clipping when the input amplitude rises very quickly. This feature uses a feed-forward technique for early detection of a rising signal level. Signal clipping is avoided by dynamically increasing the gain attack rate when required. The Anti-Clip feature is enabled using the DRC\_ANTICLIP bit.

Note that the feed-forward processing increases the latency in the input signal path. For low-latency applications (e.g. telephony), it may be desirable to reduce the delay, although this will also reduce the effectiveness of the anti-clip feature. The latency is determined by the DRC\_FF\_DELAY bit. If necessary, the latency can be minimised by disabling the anti-clip feature altogether.

| The DRC Anti-Clip | control bits are | described in Table 5. |

|-------------------|------------------|-----------------------|

|                   |                  |                       |

| REGISTER<br>ADDRESS        | BIT | LABEL        | DEFAULT | DESCRIPTION                                                                                                                                                               |

|----------------------------|-----|--------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R40 (28h)<br>DRC Control 0 | 5   | DRC_FF_DELAY | 1       | Feed-forward delay for anti-clip<br>feature<br>0 = 5 samples<br>1 = 9 samples<br>Time delay can be calculated as $5/f_s$<br>or 9/ $f_s$ , where $f_s$ is the sample rate. |

|                            | 1   | DRC_ANTICLIP | 1       | Anti-clip enable<br>0 = disabled<br>1 = enabled                                                                                                                           |

Table 5 DRC Anti-Clip Control

Note that the Anti-Clip feature operates entirely in the digital domain. It cannot be used to prevent signal clipping in the analogue domain nor in the source signal. Analogue clipping can only be prevented by reducing the analogue signal gain or by adjusting the source signal.

### QUICK RELEASE CONTROL

The DRC includes a Quick-Release feature to handle short transient peaks that are not related to the intended source signal. For example, in handheld microphone recording, transient signal peaks sometimes occur due to user handling, key presses or accidental tapping against the microphone. The Quick Release feature ensures that these transients do not cause the intended signal to be masked by the longer time constants of DRC\_DCY.

The Quick-Release feature is enabled by setting the DRC\_QR bit. When this bit is enabled, the DRC measures the crest factor (peak to RMS ratio) of the input signal. A high crest factor is indicative of a transient peak that may not be related to the intended source signal. If the crest factor exceeds the level set by DRC\_QR\_THR, then the normal decay rate (DRC\_DCY) is ignored and a faster decay rate (DRC\_QR\_DCY) is used instead.

| REGISTER<br>ADDRESS | BIT | LABEL               | DEFAULT | DESCRIPTION                               |

|---------------------|-----|---------------------|---------|-------------------------------------------|

| R40 (28h)           | 2   | DRC_QR              | 1       | Quick release enable                      |

| DRC Control 0       |     |                     |         | 0 = disabled                              |

|                     |     |                     |         | 1 = enabled                               |

| R41 (29h)           | 7:6 | DRC_QR_THR          | 01      | Quick release crest factor threshold      |

| DRC Control 1       |     | [1:0]               |         | 00 = 12dB                                 |

|                     |     |                     |         | 01 = 18dB (default)                       |

|                     |     |                     |         | 10 = 24dB                                 |

|                     |     |                     |         | 11 = 30dB                                 |

|                     | 5:4 | DRC_QR_DCY<br>[1:0] | 00      | Quick release decay rate<br>(seconds/6dB) |

|                     |     |                     |         | 00 = 0.725ms (default)                    |

|                     |     |                     |         | 01 = 1.45ms                               |

|                     |     |                     |         | 10 = 5.8ms                                |

|                     |     |                     |         | 11 = Reserved                             |

The DRC Quick-Release control bits are described in Table 6.

Table 6 DRC Quick-Release Control

#### **GAIN SMOOTHING**

The DRC includes a gain smoothing filter in order to prevent gain ripples. A programmable level of hysteresis is also used to control the DRC gain. This improves the handling of very low frequency input signals whose period is close to the DRC attack/decay time. DRC Gain Smoothing is enabled by default and it is recommended to use the default register settings.

The extent of the gain smoothing filter may be adjusted or disabled using the control fields described in Table 7.

| REGISTER<br>ADDRESS        | BIT   | LABEL                     | DEFAULT | DESCRIPTION                                                                                                   |

|----------------------------|-------|---------------------------|---------|---------------------------------------------------------------------------------------------------------------|

| R40 (28h)<br>DRC Control 0 | 12:11 | DRC_GS_HYST<br>_LVL [1:0] | 00      | Gain smoothing hysteresis<br>threshold<br>00 = Low<br>01 = Medium (recommended)<br>10 = High<br>11 = Reserved |

|                            | 3     | DRC_GS_ENA                | 1       | Gain smoothing enable<br>0 = disabled<br>1 = enabled                                                          |

|                            | 0     | DRC_GS_HYST               | 1       | Gain smoothing hysteresis enable<br>0 = disabled<br>1 = enabled                                               |

Table 7 DRC Gain Smoothing

### INITIALISATION

When the DRC is initialised, the gain is set to the level determined by the DRC\_STARTUP\_GAIN register field. The default setting is 0dB, but values from -3dB to +6dB are available, as described in Table 8.

| REGISTER<br>ADDRESS | BIT  | LABEL        | DEFAULT | DESCRIPTION                  |

|---------------------|------|--------------|---------|------------------------------|

| R40 (28h)           | 10:6 | DRC_STARTUP_ | 00110   | Initial gain at DRC start-up |

| DRC Control 0       |      | GAIN [4:0]   |         | 00000 = -3dB                 |

|                     |      |              |         | 00001 = -2.5dB               |

|                     |      |              |         | 00010 = -2dB                 |

|                     |      |              |         | 00011 = -1.5dB               |

|                     |      |              |         | 00100 = -1dB                 |

|                     |      |              |         | 00101 = -0.5dB               |

|                     |      |              |         | 00110 = 0dB (default)        |

|                     |      |              |         | 00111 = 0.5dB                |

|                     |      |              |         | 01000 = 1dB                  |

|                     |      |              |         | 01001 = 1.5dB                |

|                     |      |              |         | 01010 = 2dB                  |

|                     |      |              |         | 01011 = 2.5dB                |

|                     |      |              |         | 01100 = 3dB                  |

|                     |      |              |         | 01101 = 3.5dB                |

|                     |      |              |         | 01110 = 4dB                  |

|                     |      |              |         | 01111 = 4.5dB                |

|                     |      |              |         | 10000 = 5dB                  |

|                     |      |              |         | 10001 = 5.5dB                |

|                     |      |              |         | 10010 = 6dB                  |

|                     |      |              |         | 10011 to 11111 = Reserved    |

Table 8 DRC Initialisation

# **RETUNE<sup>™</sup> MOBILE PARAMETRIC EQUALIZER (EQ)**

The ReTune<sup>TM</sup> Mobile Parametric Equaliser is a circuit that can be enabled in the DAC path. The function of the EQ is to adjust the frequency characteristic of the output to compensate for unwanted frequency characteristics in the loudspeaker (or other output transducer). It can also be used to tailor the response according to user preferences, for example to accentuate or attenuate specific frequency bands to emulate different sound profiles or environments such as concert hall, rock etc. The EQ is enabled using the EQ\_ENA bit as shown in Table 9.

| REGISTER<br>ADDRESS | BIT | LABEL  | DEFAULT | DESCRIPTION     |

|---------------------|-----|--------|---------|-----------------|

| R134 (86h)          | 0   | EQ_ENA | 0       | EQ enable       |

| EQ1                 |     |        |         | 0 = EQ disabled |

|                     |     |        |         | 1 = EQ enabled  |

Table 9 ReTune<sup>™</sup> Mobile Parametric EQ Enable

The EQ can be configured to operate in two modes - "Default" mode or "ReTune<sup>™</sup> Mobile" mode.

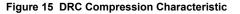

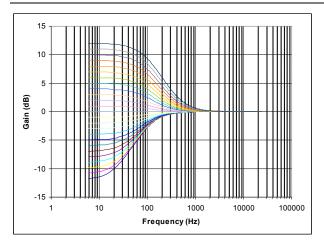

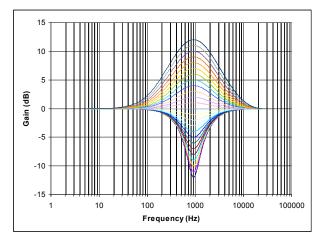

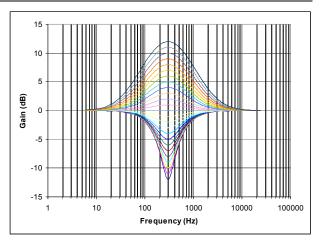

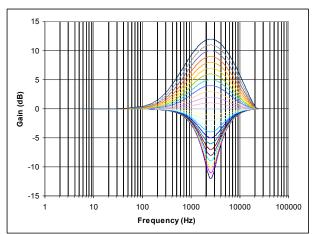

### **DEFAULT MODE (5-BAND PARAMETRIC EQ)**

In default mode, the cut-off / centre frequencies are fixed as per Table 10. The filter bandwidths are also fixed in default mode. The gain of the individual bands (-12dB to +12dB) can be controlled as described in Table 11.

Note that the cut-off / centre frequencies noted in Table 10 are applicable to a DAC Sample Rate of 48kHz. When using other sample rates, these frequencies will be scaled in proportion to the selected sample rate.

| EQ BAND | CUT-OFF/CENTRE<br>FREQUENCY |

|---------|-----------------------------|

| 1       | 100 Hz                      |

| 2       | 300 Hz                      |

| 3       | 875 Hz                      |

| 4       | 2400 Hz                     |

| 5       | 6900 Hz                     |

Table 10 EQ Band Cut-off / Centre Frequencies

| REGISTER<br>ADDRESS | BIT | LABEL            | DEFAULT | DESCRIPTION                   |

|---------------------|-----|------------------|---------|-------------------------------|

| R135 (87h)          | 4:0 | EQ_B1_GAIN [4:0] | 01100b  | EQ Band 1 Gain                |

| EQ2                 |     |                  | (0dB)   | (see Table 12 for gain range) |

| R136 (88h)          | 4:0 | EQ_B2_GAIN [4:0] | 01100b  | EQ Band 2 Gain                |

| EQ3                 |     |                  | (0dB)   | (see Table 12 for gain range) |

| R137 (89h)          | 4:0 | EQ_B3_GAIN [4:0] | 01100b  | EQ Band 3 Gain                |

| EQ4                 |     |                  | (0dB)   | (see Table 12 for gain range) |

| R138 (8Ah)          | 4:0 | EQ_B4_GAIN [4:0] | 01100b  | EQ Band 4 Gain                |

| EQ5                 |     |                  | (0dB)   | (see Table 12 for gain range) |

| R139 (8Bh)          | 4:0 | EQ_B5_GAIN [4:0] | 01100b  | EQ Band 5 Gain                |

| EQ6                 |     |                  | (0dB)   | (see Table 12 for gain range) |

Table 11 EQ Band Gain Control

| EQ GAIN SETTING | GAIN (DB) |

|-----------------|-----------|

| 00000           | -12       |

| 00001           | -11       |

| 00010           | -10       |

| 00011           | -9        |

| 00100           | -8        |

| 00101           | -7        |

| 00110           | -6        |

| 00111           | -5        |

| 01000           | -4        |

| 01001           | -3        |

| 01010           | -2        |

| 01011           | -1        |

| 01100           | 0         |

| 01101           | +1        |

| 01110           | +2        |

| 01111           | +3        |

| 10000           | +4        |

| 10001           | +5        |

| 10010           | +6        |

| 10011           | +7        |

| 10100           | +8        |

| 10101           | +9        |

| 10110           | +10       |

| 10111           | +11       |

| 11000           | +12       |

| 11001 to 11111  | Reserved  |

Table 12 EQ Gain Control

## RETUNE<sup>™</sup> MOBILE MODE

ReTune<sup>TM</sup> Mobile mode provides a comprehensive facility for the user to define the cut-off/centre frequencies and filter bandwidth for each EQ band, in addition to the gain controls already described. This enables the EQ to be accurately customised for a specific transducer characteristic or desired sound profile.

The EQ enable and EQ gain controls are the same as defined for the default mode. The additional coefficients used in ReTune<sup>™</sup> Mobile mode are held in registers R140 to R157. These coefficients are derived using tools provided in Wolfson's WISCE<sup>™</sup> evaluation board control software.

Please contact your local Wolfson representative for more details.

#### EQ FILTER CHARACTERISTICS

The filter characteristics for each frequency band are shown in Figure 16 to Figure 20. These figures show the frequency response for all available gain settings, using default cut-off/centre frequencies and bandwidth.

Figure 16 EQ Band 1 – Low Freq Shelf Filter Response

Figure 18 EQ Band 3 – Peak Filter Response

Figure 20 EQ Band 5 – High Freq Shelf Filter Response

Figure 17 EQ Band 2 – Peak Filter Response

Figure 19 EQ Band 4 – Peak Filter Response

### **DIGITAL MIXING**

The digital DAC data can be controlled in various ways to support a range of different usage modes.

Data from either of the digital audio interface channels can be routed to either the left or the right DAC. The DACs can be configured as a mono mix of the two audio channels. See "Digital Audio Interface Control" for more information on the audio interface.

The WM8912 provides a Dynamic Range Control (DRC) feature, which can apply compression and gain adjustment in the digital domain to the DAC signal path. This is effective in controlling signal levels under conditions where input amplitude is unknown or varies over a wide range. See "Dynamic Range Control (DRC)" for further details.

The W8912 also incorporates the ReTune<sup>™</sup> Mobile 5-band parametric equaliser with fully programmable coefficients for optimization of speaker characteristics or for tailoring the response according to user preferences. See "ReTune<sup>™</sup> Mobile Parametric Equalizer (EQ)" for further details.

#### DAC INTERFACE ROUTING AND CONTROL

The input data source for each DAC can be changed under software control using register bits AIFDACL\_SRC and AIFDACR\_SRC. The polarity of each DAC input may also be modified using register bits DACL\_DATINV and DACR\_DATINV. These register bits are described in Table 13.

| REGISTER<br>ADDRESS | BIT | LABEL       | DEFAULT | DESCRIPTION                               |

|---------------------|-----|-------------|---------|-------------------------------------------|

| R24 (18h)           | 12  | DACL_DATINV | 0       | Left DAC Invert                           |

| Audio               |     |             |         | 0 = Left DAC output not inverted          |

| Interface 0         |     |             |         | 1 = Left DAC output inverted              |

|                     | 11  | DACR_DATINV | 0       | Right DAC Invert                          |

|                     |     |             |         | 0 = Right DAC output not inverted         |

|                     |     |             |         | 1 = Right DAC output inverted             |

|                     | 5   | AIFDACL_SRC | 0       | Left DAC Data Source Select               |

|                     |     |             |         | 0 = Left DAC outputs left interface data  |

|                     |     |             |         | 1 = Left DAC outputs right interface data |

|                     | 4   | AIFDACR_SRC | 1       | Right DAC Data Source Select              |

|                     |     |             |         | 0 = Right DAC outputs left interface data |

|                     |     |             |         | 1 = Right DAC outputs right interface     |

|                     |     |             |         | data                                      |

Table 13 DAC Routing and Control

#### DAC INTERFACE VOLUME BOOST

A digital gain function is available at the audio interface to boost the DAC volume when a small signal is received on DACDAT. This is controlled using register bits DAC\_BOOST [1:0]. To prevent clipping at the DAC input, this function should not be used when the boosted DAC data is expected to be greater than 0dBFS.

The digital interface volume is controlled as shown in Table 14.

| REGISTER<br>ADDRESS | BIT  | LABEL              | DEFAULT | DESCRIPTION                                        |

|---------------------|------|--------------------|---------|----------------------------------------------------|

| R24 (18h)<br>Audio  | 10:9 | DAC_BOOST<br>[1:0] | 00      | DAC Input Volume Boost<br>00 = 0dB                 |

| Interface 0         |      |                    |         | 01 = +6dB (Input data must not<br>exceed -6dBFS)   |

|                     |      |                    |         | 10 = +12dB (Input data must not<br>exceed -12dBFS) |

|                     |      |                    |         | 11 = +18dB (Input data must not<br>exceed -18dBFS) |

Table 14 DAC Interface Volume Boost

PD, Rev 4.1, February 2013

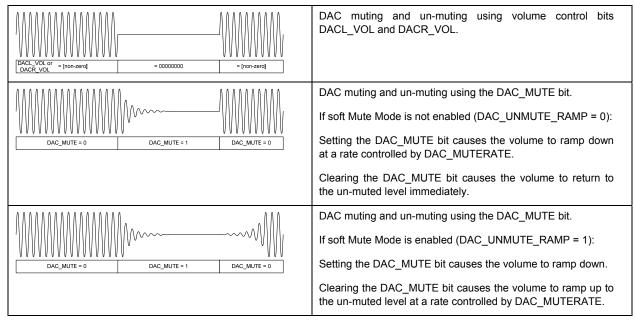

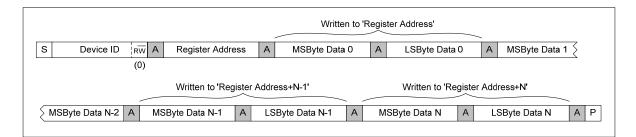

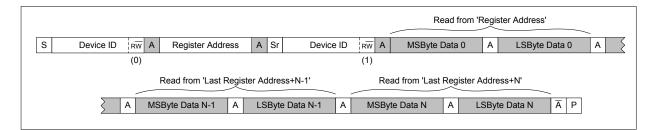

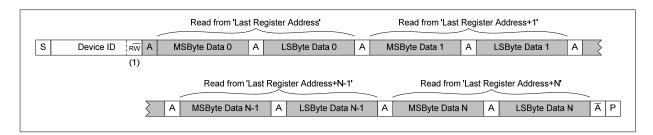

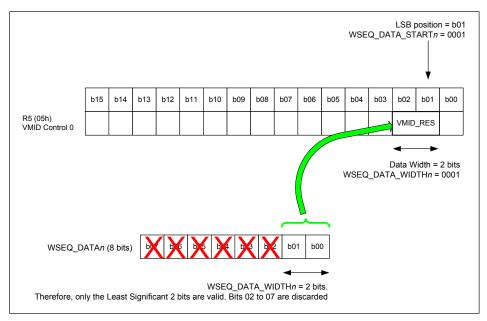

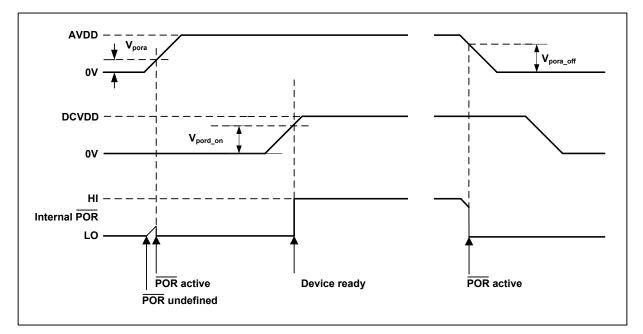

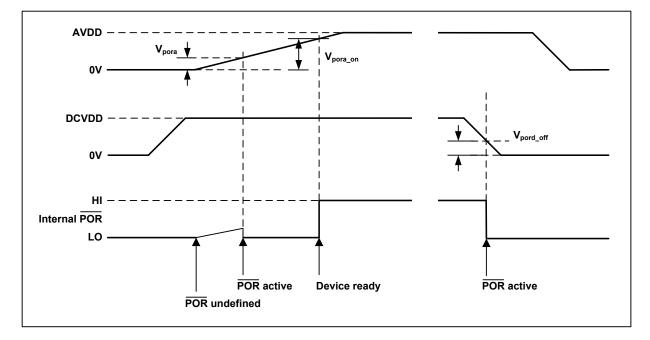

### DIGITAL-TO-ANALOGUE CONVERTER (DAC)