LTC1264

High Speed, Quad Universal Filter Building Block

### FEATURES

- High Speed, Up to 250kHz Center Frequency

- Four Identical Filters in a 0.3" Wide Package

- Clock-to-Center Frequency Ratio of 20:1

- Double-Sampling, Improved Aliasing

- Operates from ±2.37V to ±8V Power Supplies

- Customized Version with Internal Resistors Available

- Low Noise

- Low Harmonic Distortion

- Available in 24-Pin DIP and SO Wide Packages

### **APPLICATIONS**

- Digital Communications

- Spread Spectrum Communications

- Spectral Analysis

- Loran Receivers

- Instrumentation

T, LTC and LT are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

### DESCRIPTION

The LTC<sup>®</sup>1264 consists of four identical, high speed 2nd order switched-capacitor filter building blocks designed for center frequencies up to 250kHz. Each building block, together with three to five resistors, can provide 2nd order functions like lowpass, highpass, bandpass and notch. The center frequency of each 2nd order section is tuned via an external clock. The clock-to-center frequency ratio is internally set to 20:1, but it can be modified via external resistors.

The aliasing performance of the LTC1264 is improved by double-sampling each 2nd order section. Input signal frequencies can reach up to twice the clock frequency before any alias products will be detectable.

For  $Q \le 5$  and for  $T_A < 85^{\circ}C$ , the maximum center frequency is 160kHz. For  $Q \le 2$ , the maximum center frequency is 250kHz. Up to 8th order filters can be realized by cascading all four 2nd order sections.

A customized monolithic version of the LTC1264 including internal thin film resistors can be obtained.

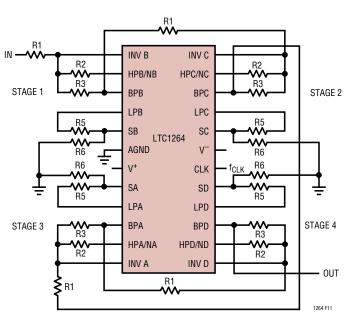

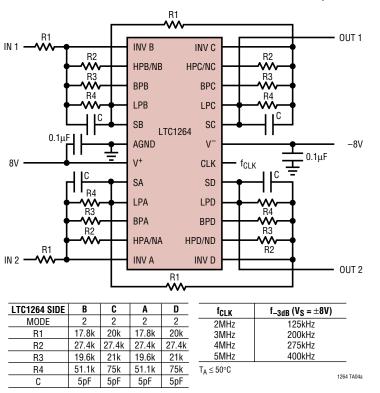

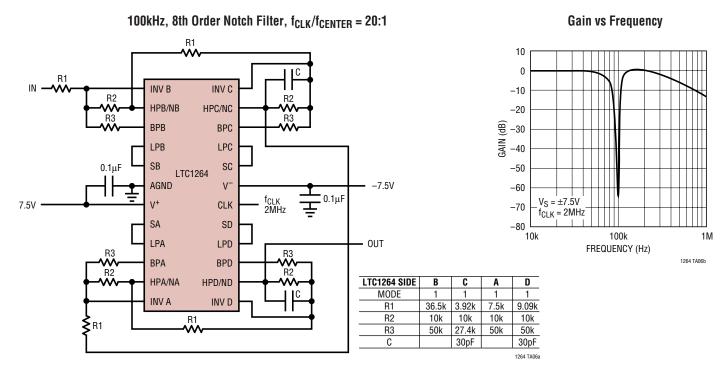

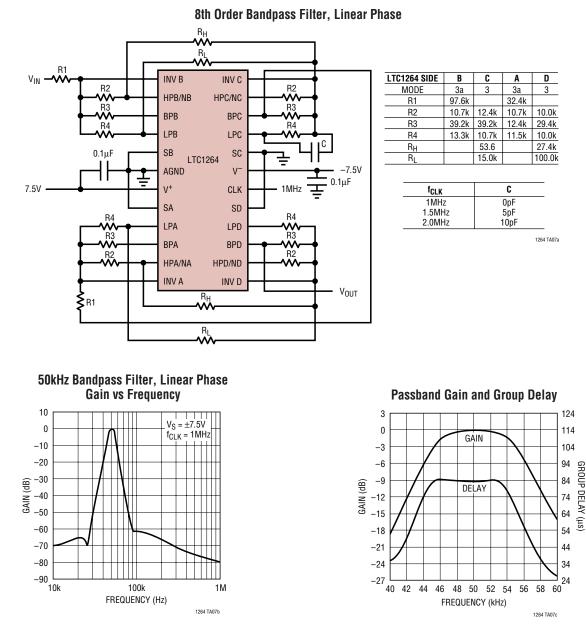

### TYPICAL APPLICATION

Clock-Tunable 8th Order Bandpass Filter, f<sub>CENTER</sub> = f<sub>CLK</sub>/20 50k 50k INV B INV C 10k 10k Ś HPB/NB HPC/NC 50k BPB BPC Ŵ MAXIMUM POWER LPB LPC SUPPLY **f**CENTER SB SC 160kHz ±7.5V LTC1264 120kHz +5V AGND V-Single 5V 60kHz 0.1µF V+ CLK 1μF SA SD LPA LPD OUT 50 BPA BPD ~~~ 104 HPA/NA 10k w HPD/ND INV A INV D **Š** 50k  $\sim$

50k

Gain vs Frequency 100kHz Bandpass,  $f_{-3dB}$  Bandwidth =  $f_{CENTER}/10$ 10 0 -10 -20 g -30 GAIN -40 -50 -60 -70 -80 10k 100k 1M FREQUENCY (Hz) 1264 TA02

#### **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Total Supply Voltage (V <sup>+</sup> to V <sup>-</sup> ) 1 | 6V  |

|------------------------------------------------------------|-----|

| Input Voltage (Note 2) $(V^+ + 0.3V)$ to $(V^ 0.3V)$       | SV) |

| Output Short-Circuit Duration Indefin                      | ite |

| Power Dissipation 400m                                     | ۱W  |

| Burn-In Voltage 1                                          | 6V  |

| Operating Temperature Range40°C to 85                      | °C  |

| Storage Temperature Range –65°C to 150                     | °C  |

| Lead Temperature (Soldering, 10 sec) 300                   | °C  |

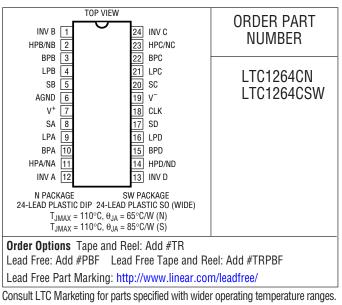

### PACKAGE/ORDER INFORMATION

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . (Internal Op Amps)  $T_A = 25^{\circ}C$ , unless otherwise noted.

| PARAMETER                                  | CONDITIONS                                 |   | MIN    | ТҮР  | MAX | UNITS |

|--------------------------------------------|--------------------------------------------|---|--------|------|-----|-------|

| Operating Supply Range                     |                                            |   | ±2.375 |      | ±8  | V     |

| Voltage Swings                             | $V_{\rm S} = \pm 2.375 V, R_{\rm L} = 5 k$ |   |        | ±1.5 |     | V     |

|                                            | $V_{\rm S} = \pm 5 V, R_{\rm L} = 5 k$     |   | ±3.2   | ±3.7 |     | V     |

|                                            |                                            | • | ±3.1   |      |     | V     |

|                                            | $V_{\rm S} = \pm 7.5, R_{\rm L} = 5k$      |   |        | ±6   |     | V     |

| Output Short-Circuit Current (Source/Sink) |                                            |   |        | 3    |     | mA    |

| DC Open-Loop Gain                          |                                            |   |        | 80   |     | dB    |

| GBW Product                                |                                            |   |        | 7    |     | MHz   |

| Slew Rate                                  |                                            |   |        | 10   |     | V/µs  |

(Complete Filter)  $V_S = \pm 5V$ ,  $f_{CLK} = 1$ MHz, all sides mode 1,  $f_0 = 50$ kHz, Q = 5,  $T_A = 25^{\circ}$ C, unless otherwise noted.

| PARAMETER                                                         | CONDITIONS                                                                                     |   | MIN | ТҮР                    | MAX          | UNITS        |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---|-----|------------------------|--------------|--------------|

| Center Frequency Range, f <sub>0</sub> (Note 2)                   | $V_{S} = \pm 7.5V, T_{A} < 85^{\circ}C, Q < 2$<br>$V_{S} = \pm 5V, T_{A} < 85^{\circ}C, Q < 2$ |   |     | 0.1 - 250<br>0.1 - 200 |              | kHz<br>kHz   |

|                                                                   | $V_{S} = \pm 2.5 V$ , $T_{A} < 85^{\circ}C$ , $Q < 2$                                          |   |     | 0.1 - 100              |              | kHz          |

| Clock-to-Center Frequency Ratio, f <sub>CLK</sub> /f <sub>0</sub> |                                                                                                |   |     | 20:1                   |              |              |

| Center Frequency Error (Note 4)                                   | $V_{S} = \pm 7.5 V$                                                                            |   |     | ±0.1                   | ±0.7<br>±0.8 | %            |

|                                                                   | $V_S = \pm 5V$                                                                                 |   |     | ±0.2                   | ±0.8<br>±1.0 | //<br>%<br>% |

|                                                                   | V <sub>S</sub> = ±2.375V                                                                       |   |     | -1.6                   | 1.0          | %            |

| Clock-to-Center Frequency Ratio,<br>Side-to-Side Matching         | $V_{S} \ge \pm 5V$                                                                             | • |     | 0.4                    | 0.8<br>1.0   | %            |

| Q Accuracy                                                        | $V_S = \pm 5V$                                                                                 |   |     | -2.7                   | 7.0          | %            |

| f <sub>0</sub> Temperature Coefficient                            | f <sub>CLK</sub> < 2MHz                                                                        |   |     | ±1                     |              | ppm/°C       |

| Q Temperature Coefficient                                         | f <sub>CLK</sub> < 2MHz                                                                        |   |     | 5                      |              | ppm/°C       |

|                                                                   |                                                                                                |   |     |                        |              | 1264fb       |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Complete Filter) V<sub>S</sub> = ±5V, f<sub>CLK</sub> = 1MHz, all sides mode 1, f<sub>0</sub> = 50kHz,

Q = 5, unless otherwise noted.

| PARAMETER                  | CONDITIONS                                               | MIN | ТҮР | MAX | UNITS             |

|----------------------------|----------------------------------------------------------|-----|-----|-----|-------------------|

| DC Offset Voltage (Note 3) | V <sub>OS1</sub> (DC Offset of Input Inverter)           |     |     | ±20 | mV                |

|                            | V <sub>OS2</sub> (DC Offset of First Integrator)         |     |     | ±45 | mV                |

|                            | V <sub>OS3</sub> (DC Offset of Second Integrator)        |     |     | ±45 | mV                |

| Clock Feedthrough          | $V_{S} = \pm 7.5V$ (f <sub>CLK</sub> is a Square Wave)   |     | 160 |     | μV <sub>RMS</sub> |

|                            | $V_{S} = \pm 5V$ (f <sub>CLK</sub> is a Square Wave)     |     | 120 |     | μV <sub>RMS</sub> |

|                            | $V_{S} = \pm 2.375V$ (f <sub>CLK</sub> is a Square Wave) |     | 90  |     | μV <sub>RMS</sub> |

| Maximum Clock Frequency    | $V_{S} = \pm 7.5 V, T_{A} = 25^{\circ} C$                |     | 6   |     | MHz               |

| Power Supply Current       | $V_{S} = \pm 5V$                                         | 9   | 14  | 23  | mA                |

|                            |                                                          |     |     | 26  | mA                |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

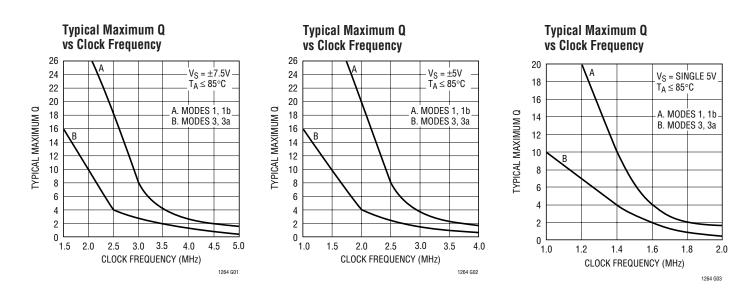

**Note 2:** Please refer to Typical Maximum Q vs Clock Frequency graphs. Note 3: Calculations of output DC offsets of one 2nd order section. Also see Block Diagram.

**Note 4:** The center frequency f<sub>0</sub>, error is calculated as:

$\frac{f_0(\text{measured}) - f_0(\text{ideal})}{f_0 \text{ (ideal)}} \bullet 100$

| MODE | V <sub>OSN</sub><br>PINS 2, 11, 14, 23                                                                                                                            | V <sub>osbp</sub><br>Pins 3, 10, 15, 22 | V <sub>OSLP</sub><br>PINS 4, 9, 16, 21                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------|

| 1    | $V_{OS1}[(1Q) + 1   H_{OLP}  ] - V_{OS3}/Q$                                                                                                                       | V <sub>OS3</sub>                        | $V_{OSN} - V_{OS2}$                                                                                   |

| 1b   | V <sub>0S1</sub> [(1/Q) + 1 + R2/R1] - V <sub>0S3</sub> /Q                                                                                                        | V <sub>OS3</sub>                        | ≈(V <sub>OSN</sub> – V <sub>OS2</sub> )(1 + R5/R6)                                                    |

| 2    | $ \begin{bmatrix} V_{0S1}(1 + R2/R1 + R2/R3 + R2/R4) - V_{0S3}(R2/R3) \end{bmatrix} $<br>• $ \begin{bmatrix} R4/(R2 + R4) \end{bmatrix} + V_{0S2}[R2/(R2 + R4)] $ | V <sub>OS3</sub>                        | V <sub>OSN</sub> – V <sub>OS2</sub>                                                                   |

| 3    | V <sub>0S2</sub>                                                                                                                                                  | V <sub>OS3</sub>                        | V <sub>0S1</sub> [1 + R4/R1 + R4/R2 + R4/R3] – V <sub>0S2</sub> (R4/R2)<br>– V <sub>0S3</sub> (R4/R3) |

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### TYPICAL PERFORMANCE CHARACTERISTICS

### PIN FUNCTIONS

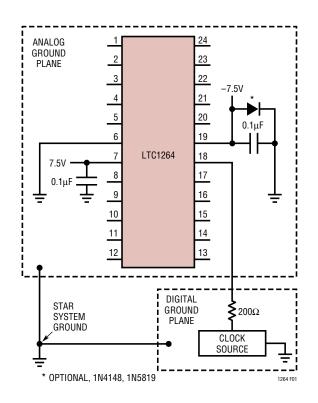

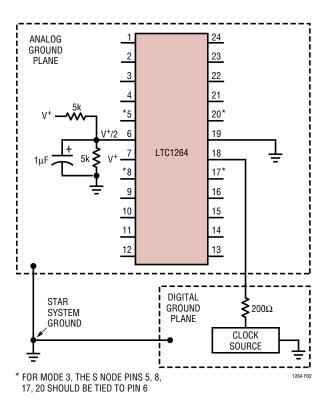

**V<sup>+</sup>**, **V<sup>-</sup>**(**Pins 7, 19**): Power Supply Pins. The V<sup>+</sup> (Pin 7) and the V<sup>-</sup> (Pin 19) should each be bypassed with a  $0.1\mu$ F capacitor to an adequate analog ground. The filter's power supplies should be isolated from other digital or high voltage analog supplies. A low noise linear supply is recommended. Using a switching power supply will lower the signal-to-noise ratio of the filter. The supply during power-up should have a slew rate less than 1V/µs. When V<sup>+</sup> is applied before V<sup>-</sup> and V<sup>-</sup> is allowed to go above ground, a diode should clamp V<sup>-</sup> to prevent latch-up. Figures 1 and 2 show typical connections for dual and single supply operation. **AGND (Pin 6):** Analog Ground Pin. The filter performance depends on the quality of the analog signal ground. For either dual or single supply operation, an analog ground plane surrounding the package is recommended. The analog ground plane should be connected to any digital ground at a single point. For dual supply operation, Pin 6 should be connected to the analog ground plane. For single supply operation, Pin 6 should be biased at 1/2 supply and should be bypassed to the analog ground plane with at least a 1 $\mu$ F capacitor (Figure 2). For single 5V operation and f<sub>CLK</sub> greater than 1MHz, pin 6 should be biased at 2V. This minimizes passband gain and phase variations.

Figure 1. Dual Supply Ground Plane Connections

Figure 2. Single Supply Ground Plane Connections

### **PIN FUNCTIONS**

**CLK (Pin 18):** Clock Input Pin. Any TTL or CMOS clock source with a square wave output and 50% duty cycle  $(\pm 10\%)$  is an adequate clock source for the device. The power supply for the clock source should not be the filter's power supply. The analog ground for the filter should be connected to clock's ground at a single point only. Table 1 shows the clock's low and high level threshold values for a dual or single supply operation.

| POWER SUPPLY             | HIGH LEVEL | LOW LEVEL    |

|--------------------------|------------|--------------|

| Dual Supply = $\pm 7.5V$ | ≥ 2.18V    | ≤ 0.5V       |

| Dual Supply = $\pm 5V$   | ≥ 1.45V    | $\leq 0.5V$  |

| Dual Supply = $\pm 2.5V$ | ≥ 0.73V    | $\leq -2.0V$ |

| Single Supply = 12V      | ≥ 7.80V    | $\leq 6.5V$  |

| Single Supply = 5V       | ≥ 1.45V    | $\leq 0.5 V$ |

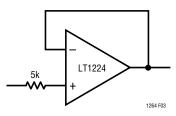

A pulse generator can be used as a clock source provided the high level on-time is greater than 0.2µs. Sine waves are not recommended for clock input frequencies less than 100kHz, since excessively slow clock rise or fall times generate internal clock jitter (maximum clock rise or fall time  $\leq 1\mu$ s). The clock signal should be routed from the right side of the IC package and perpendicular to it to avoid coupling to any input or output analog signal path. A 200 $\Omega$ resistor between clock source and Pin 11 will slow down the rise and fall times of the clock to further reduce charge coupling (Figures 1 and 2). HPB/NB, BPB, LPB, LPA, BPA, HPA, HPD, BPD, LPD, LPC, BPC, HPC/NC (Pins 2, 3, 4, 9, 10, 11, 14, 15, 16, 21, 22, 23): Output Pins. Each 2nd order section of the LTC1264 has three outputs which typically source 3mA and sink 1mA. Driving coaxial cables or resistive loads less than 20k will degrade the total harmonic distortion performance of any filter design. When evaluating the distortion or noise performance of a particular filter design implemented with an LTC1264, the final output of the filter should be buffered with a wideband noninverting high slew rate amplifier (Figure 3).

Figure 3. Wideband Buffer

**INV B, INV A, INV D, INV C (Pins 1, 12, 13, 24):** Inverting Input Pins. These pins are the high impedance inverting inputs of internal op amps and they are susceptible to stray capacitive connections to low impedance signal outputs and power supply lines.

**SB, SA, SD, SC (Pins 5, 8, 17, 20):** Summing Input Pins. The summing pins connections determine the circuit topology (mode) of each 2nd order section. Please refer to Modes of Operation.

# **MODES OF OPERATION**

For the definition of filter functions please refer to the LTC1060 data sheet.

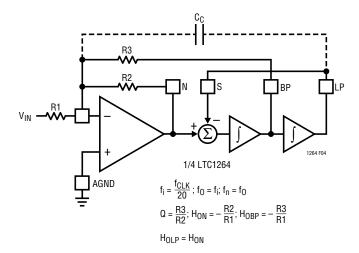

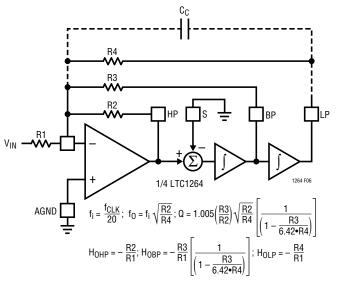

### Mode 1

In Mode 1, the ratio of the external clock frequency to the center frequency of each 2nd order section is internally fixed at 20:1. Figure 4 illustrates Mode 1 providing 2nd order notch, lowpass, and bandpass outputs. Mode 1 can be used to make high order Butterworth lowpass filters; it can also be used to make low Q notches and for cascading 2nd order bandpass functions tuned at the same center frequency. Mode 1 is faster than Mode 3.

Please refer to the Maximum Frequency of Operation paragraph under Applications Information for a guide to the use of capacitor  $C_{\rm C}.$

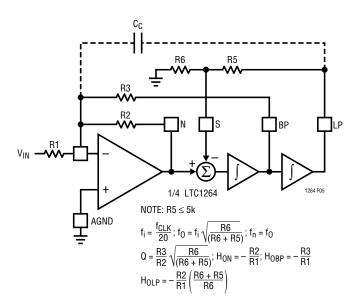

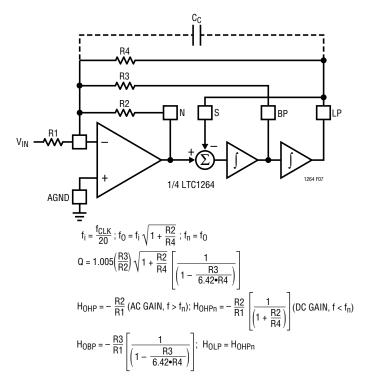

### Mode 1b

Mode 1b is derived from Mode 1. In Mode 1b (Figure 5) two additional resistors R5 and R6 are added to alternate the amount of voltage fed back from the lowpass output into the input of the SA (SB, SC or SD) switched-capacitor summer. This allows the filter's clock-to-center frequency ratio to be adjusted beyond 20:1. Mode 1b maintains the speed advantages of Mode 1 and should be considered an 1264fb

### **MODES OF OPERATION**

optimum mode for high Q designs with  $f_{CLK}$  to  $f_{CUTOFF}$  (or  $f_{CENTER}$ ) ratios greater than 20:1.

Please refer to the Maximum Frequency of Operation paragraph under Applications Information for a guide to the use of capacitor  $C_{\rm C}$ .

Figure 4. Mode 1, 2nd Order Filter Providing Notch, Bandpass and Lowpass Outputs

Figure 5. Mode 1b, 2nd Order Filter Providing Notch, Bandpass and Lowpass Outputs

#### Mode 3

In Mode 3, the ratio of the external clock frequency to the center frequency of each 2nd order section can be adjusted above or below 20:1. Figure 6 illustrates Mode 3, the classical state variable configuration, providing highpass, bandpass, and lowpass 2nd order filter functions. Mode 3 is slower than Mode 1. Mode 3 can be used to make high order all-pole bandpass, lowpass, and highpass filters.

Please refer to the Maximum Frequency of Operation paragraph under Applications Information for a guide to the use of capacitor  $C_{\rm C}$ .

#### Mode 2

Mode 2 is a combination of Mode 1 and Mode 3, shown in Figure 7. With Mode 2, the clock-to-center frequency ratio,  $f_{CLK}/f_0$ , is always less than 20:1. The advantage of Mode 2 is that it provides less sensitivity to resistor tolerances than does Mode 3. As in Mode 1, Mode 2 has a notch output which depends on the clock frequency, and the notch frequency is therefore less than the center frequency,  $f_0$ .

Please refer to the Maximum Frequency of Operation paragraph under Applications Information for a guide to the use of capacitor  $C_{\rm C}$ .

Figure 6. Mode 3, 2nd Order Section Providing Highpass, Bandpass and Lowpass Outputs

Figure 7. Mode 2, 2nd Order Filter Providing Highpass Notch, Bandpass and Lowpass Outputs

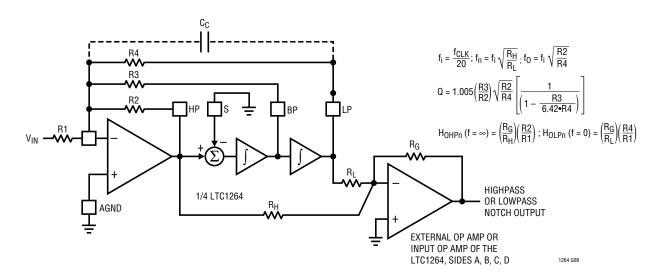

#### Mode 3a

This is an extension of Mode 3 where the highpass and lowpass output are summed through two external resis-

tors  $R_H$  and  $R_L$  to create a notch. This is shown in Figure 8. Mode 3a is more versatile than Mode 2 because the notch frequency can be higher or lower than the center frequency of the 2nd order section. The external op amp of Figure 8 is not always required. When cascading the sections of the LTC1264, the highpass and lowpass outputs can be summed directly into the inverting input of the next section.

Please refer to the Maximum Frequency of Operation paragraph under Applications Information for a guide to the use of capacitor  $C_{C}$ .

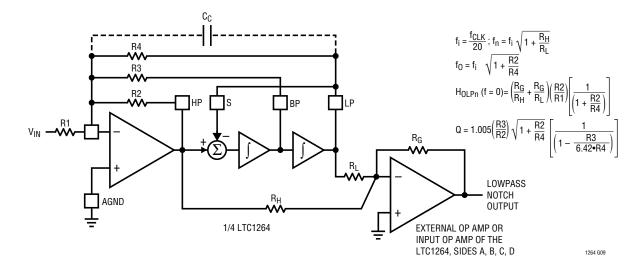

#### Mode 2n

This mode extends the circuit topology of Mode 3a to Mode 2 (Figure 9) where the highpass notch and lowpass outputs are summed through two external resistors  $R_H$  and  $R_L$  to create a lowpass output with a notch higher in frequency than the notch in Mode 2. This mode, shown in Figure 8, is most useful in lowpass elliptic designs. When cascading the sections of the LTC1264, the highpass notch and lowpass outputs can be summed directly into the inverting input of the next section.

Please refer to the Maximum Frequency of Operation paragraph under Applications Information for a guide to the use of capacitor  $C_{C}$ .

Figure 8. Mode 3a, 2nd Order Filter Providing a Highpass Notch or Lowpass Notch Output

### **MODES OF OPERATION**

Figure 9. Mode 2n, 2nd Order Filter Providing a Lowpass Notch Output

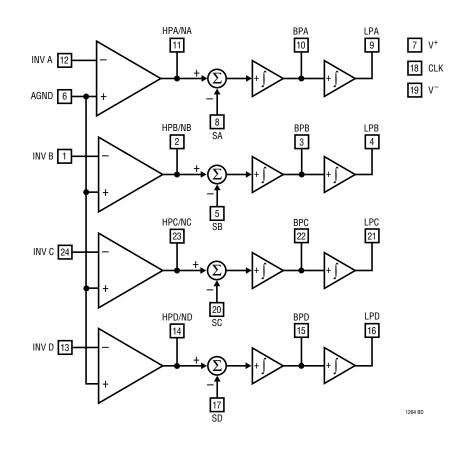

### **BLOCK DIAGRAM**

9

## APPLICATIONS INFORMATION

#### **Operating Limits**

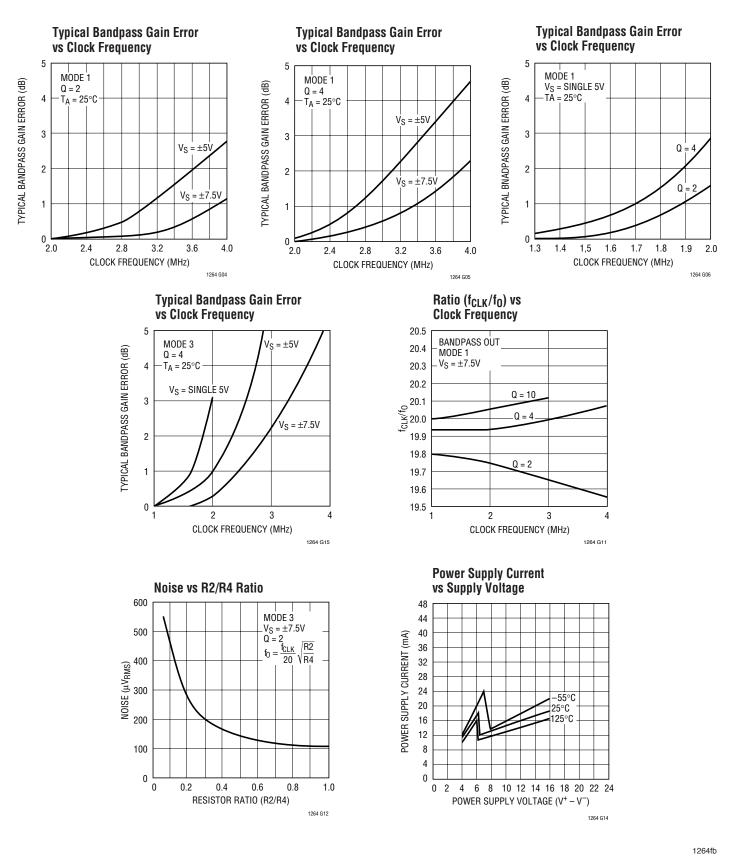

The Typical Maximum Q vs Clock Frequency and Bandpass Gain Error graphs, under Typical Performance Characteristics, define an upper limit of operating Q for each LTC1264 2nd order section. These graphs indicate the power supply,  $f_{CLK}$  and Q value conditions under which a filter implemented with an LTC1264 will remain stable when operated at temperatures of 85°C or less. For a 2nd order section, a bandpass gain error of 3dB or less is arbitrarily defined as a condition for stability.

When the passband gain error begins to exceed 1dB, the use of capacitor  $C_C$  will reduce the gain error (capacitor  $C_C$  is connected from the lowpass node to the inverting node of a 2nd order section). Please refer to Figures 4 through 9. The value of  $C_C$  can be best determined experimentally, and as a guide it should be about 5pF for each 1dB of gain error and not to exceed 15pF. When operating LTC1264 very near the limits defined by the Typical Performance Characteristics graphs, passband gain variations of 2dB or more should be expected.

### **Speed Limitations**

To avoid op amp slew rate limiting, the signal amplitude should be kept below a specified level as shown in Table 2.

| Vs        | MAXIMUM CLOCK | MAXIMUM V <sub>IN</sub>                      |

|-----------|---------------|----------------------------------------------|

| ±7.5V     | 4MHz to 5MHz  | 0.5V <sub>RMS</sub> f <sub>IN</sub> ≥ 400kHz |

| ±5V       | 3MHz to 4MHz  | $0.5V_{RMS} f_{IN} \ge 250 kHz$              |

| Single 5V | 1MHz to 2MHz  | $0.35V_{RMS} f_{IN} \ge 160 kHz$             |

Table 2. Maximum  $V_{\rm IN}$  vs  $V_{\rm S}$  and Clock

### **Clock Feedthrough**

Clock feedthrough is defined as the RMS value of the clock frequency and its harmonics that are present at the filter's output pins. The clock feedthrough is tested with the filter's input grounded and it depends on PC board layout and on the value of the power supplies. With proper layout techniques, the typical values of clock feedthrough are listed under Electrical Characteristics.

Any parasitic switching transients during the rise and fall edges of the incoming clock are not part of the clock feedthrough specifications. Switching transients have frequency contents much higher than the applied clock; their amplitude strongly depends on scope probing techniques as well as grounding and power supply bypassing. The clock feedthrough, if bothersome, can be greatly reduced by adding a simple RC lowpass network at the final filter output. This RC will completely eliminate any switching transients.

#### Wideband Noise

The wideband noise of the filter is the total RMS value of the device's noise spectral density and it is used to determine the operating signal-to-noise ratio. Most of its frequency contents lie within the filter passband and it cannot be reduced with post filtering.

The total wideband noise ( $\mu V_{RMS}$ ) is nearly independent of the value of the clock. The clock feedthrough specifications are not part of the wideband noise.

For a specific filter design, the total noise depends on the Q of each section and the cascade sequence. Table 3 shows typical 2nd order section noise (gain = 1) for Q values and supplies operating at  $25^{\circ}$ C. Noise increases by 20% at the highest operating temperatures.

| Table 3. 2nd Order Section Noise ( $\mu V_{RMS}$ ) for Modes 1, 1b, |  |

|---------------------------------------------------------------------|--|

| 2 or 3 (R2 = R4)                                                    |  |

| Q | $V_S = \pm 2.5V$    | $V_S = \pm 5V$ | $V_S = \pm 7.5 V$ |

|---|---------------------|----------------|-------------------|

| 1 | 40μV <sub>RMS</sub> | 50             | 60                |

| 2 | 50μV <sub>RMS</sub> | 60             | 75                |

| 3 | 60μV <sub>RMS</sub> | 75             | 95                |

| 4 | 75μV <sub>RMS</sub> | 90             | 115               |

| 5 | 90μV <sub>RMS</sub> | 110            | 135               |

### Aliasing

Aliasing is an inherent phenomenon of switched-capacitor filters and it occurs when the frequency of input signals approaches the sampling frequency. The input signals that produce the strongest aliased components have a frequency,  $f_{IN}$ , such as  $(f_{SAMPLING} - f_{IN})$  falls into the filter's passband. For the LTC1264 the sampling frequency is twice  $f_{CLK}$ . If the input signal spectrum is not band-limited, aliasing may occur.

### APPLICATIONS INFORMATION

For example, for an LTC1264 bandpass filter with  $f_{CENTER}$  = 100kHz and  $f_{CLK}$  = 2MHz, a 3.9MHz, 10mV input will produce a 100kHz, 10mV output. A 1st or 2nd order prefilter will reduce aliasing to acceptable levels in most cases.

#### A GUIDE TO BANDPASS DESIGN

Filter design tools like FCAD require design specification inputs such as passband ripple, attenuation, passband width and stopband width in order to calculate filter parameters  $f_0$ , Q,  $f_n$  or poles and zeroes. The results of these filter approximations most often require Q values which make excessive demands on the gain-bandwidth products of active filter realizations. The active filter designer should define a gain response so that the filter's mathematical approximation has practical requirements. Table 4 is a guide to practical design specifications for realizing bandpass filters with LTC1264 (please also refer to the Typical Maximum Q vs Clock Frequency and Bandpass Gain Error graphs under Typical Performance Characteristics).

#### A Bandpass Design Example

| Filter Type:      | Bandpass                     |

|-------------------|------------------------------|

| Filter Response:  | Butterworth                  |

| Passband Ripple:  | 3dB                          |

| Attenuation:      | 60dB                         |

| Center Frequency: | 40kHz (f <sub>CENTER</sub> ) |

| Passband Width:   | 10kHz                        |

| Stopband Width:   | 60kHz                        |

#### Implementing the Bandpass Design

With the LTC1264 in Mode 1b, Butterworth and Chebyshev bandpass designs with  $f_{CLK}$  to  $f_{CENTER}$  ratios greater than 20:1 are possible.

First choose the clock frequency which in Mode 1b must be greater than 20 times the bandpass center frequency of 40kHz. For this example, let's choose  $f_{CLK}$  to be 1MHz. Table 6 lists the resistors for for the bandpass design example and Figure 11 shows the complete circuit.

# Table 4. Bandpass Design Specifications ( $f_{CENTER}$ is center frequency of passband.)

| PASSBAND<br>RIPPLE<br>(dB) | PASSBAND<br>WIDTH<br>(Hz) | STOPBAND<br>WIDTH<br>(Hz)  | ATTENU-<br>Ation<br>(db) |

|----------------------------|---------------------------|----------------------------|--------------------------|

| $\leq$ 3dB for Butterworth | $\geq f_{CENTER}/20$      | $\geq$ 5 × Passband        | -40 to -60               |

| $\leq$ 0.1 for Chebyshev   | $\geq f_{CENTER}/20$      | $\geq$ 5 $\times$ Passband | -40 to -60               |

Note: Reducing passband ripple or attenuation will decrease Q values. The filter order may also increase.

#### Table 5. Calculated Filter Parameters

| STAGE | fo         | Q       |  |

|-------|------------|---------|--|

| 1     | 38.1201kHz | 4.3346  |  |

| 2     | 41.9726kHz | 4.3346  |  |

| 3     | 35.6418kHz | 10.5221 |  |

| 4     | 44.8911kHz | 10.5221 |  |

Table 6. Calculated Mode 1b Resistors to Nearest 1% Value

Using Table 5 Filter Parameters and Figure 10 Equations

| STAGE | R1    | R2  | R3    | R5 | R6    |

|-------|-------|-----|-------|----|-------|

| 1     | 52.3k | 10k | 56.2k | 5k | 6.98k |

| 2     | 47.5k | 10k | 51.1k | 5k | 11.8k |

| 3     | 56.2k | 10k | 147k  | 5k | 5.11k |

| 4     | 44.2k | 10k | 118k  | 5k | 20.5k |

$$\begin{aligned} & \text{R2} = 10k \\ & \text{R5} = 5k \\ & f_i = \frac{f_{\text{CLK}}}{20} \\ & \text{R1} = \frac{R3}{H_{\text{OBP}}} \text{ (FOR BANDPASS)} \\ & \text{R6} = \frac{R5 \bullet f_0^2}{\left(f_i^2 - f_0^2\right)} \\ & \text{H}_{\text{OBP}} = \sqrt{Q^2 \left[ \left(\frac{f_0}{f_{\text{CENTER}}}\right) - \left(\frac{f_{\text{CENTER}}}{f_0}\right) \right]^2 + 1} \\ & \text{R3} = \frac{R2 \bullet Q}{\sqrt{\frac{R6}{(R6 + 5)}}} \end{aligned}$$

#### Figure 10. Equations for Resistors in Mode 1b Operation

**APPLICATIONS INFORMATION**

Figure 11. Mode 1b Bandpass Filter

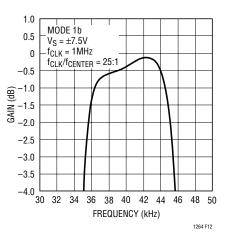

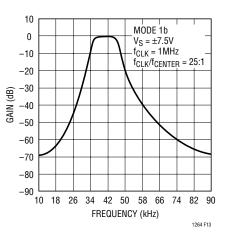

Figures 12 and 13 show the gain response graphs of the 40kHz Butterworth bandpass design described above. The passband gain response graph (Figure 12) shows a 40kHz gain of -0.4dB and a tilted passband from 37kHz to 43kHz. These errors are due to the 1% resistors used and the side-to-side matching of the LTC1264 f<sub>CLK</sub>-to-f<sub>CENTER</sub> ratio which typically is 0.4%. To adjust for 0dB gain at 40kHz, reduce the value of R1 in the first stage by 5%. To adjust for a flat passband, adjust by  $\pm$ 1% the value of R6 in stages 3 and 4. Adjusting R6 compensates for the side-to-side matching errors. Please refer to Figure 5 equations defining f<sub>0</sub> and Q as a function of R6.

The sequence of 2nd order stages and the bandpass gain  $H_{OBP}$  of each stage will determine the gain peaks at the filter's intermediate outputs. A given internal output can have several dB more gain than the final filter output. Gain peaks occur around the corners of the passband. The gain peaks can be reduced by increasing the R1 resistor of the

first stage and decreasing the R1 resistor of the last stage by the same amount (multiplying the R1 resistor of the first stage and dividing the R1 resistor of the last stage by 2 for narrowband filter, and by 5 for wideband filter is a good rule of thumb). This adjustment may, however, increase the filter's passband noise.

Figure 12. Passband Gain vs Frequency 40kHz Butterworth Bandpass

Figure 13. Gain vs Frequency 40kHz Butterworth Bandpass

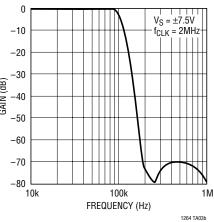

### **TYPICAL APPLICATIONS**

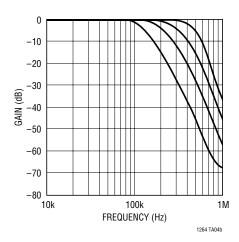

Linear Phase Clock-Tunable to 400kHz, Dual 4th Order Lowpass Filter

#### Gain vs Frequency

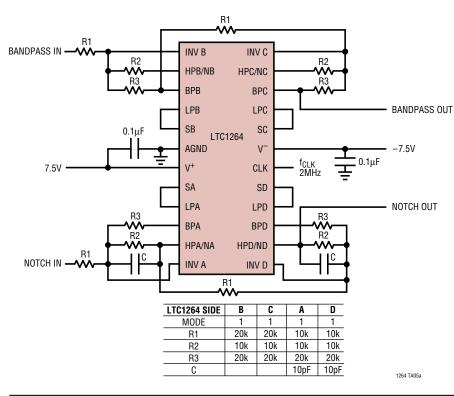

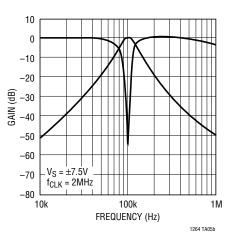

Clock-Tunable, f<sub>CENTER</sub> = f<sub>CLK</sub>/20, 100kHz, 4th Order Bandpass and Notch Filters

**Gain vs Frequency**

LINEAR TECHNOLOGY 13

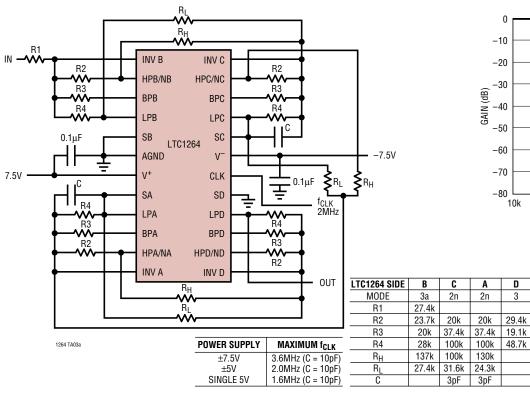

### TYPICAL APPLICATIONS

Clock-Tunable, 8th Order Elliptic Lowpass Filter,  $f_{CLK}/f_{CUTOFF} = 20:1$

**Gain vs Frequency**

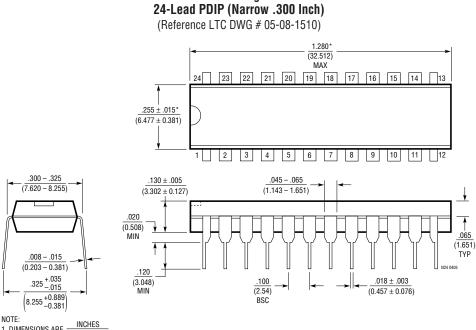

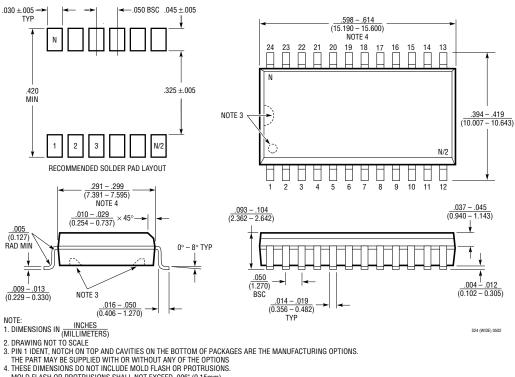

### PACKAGE DESCRIPTION

N Package

1. DIMENSIONS ARE MILLIMETERS \*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

> SW Package 24-Lead Plastic Small Outline (Wide .300 Inch) (Reference LTC DWG # 05-08-1620)

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

### TYPICAL APPLICATION

### **RELATED PARTS**

| PART NUMBER                                                                    | DESCRIPTION                                                        | COMMENTS                                                                                                                                                        |  |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LTC1068 Very Low Noise, High Accuracy, Quad Universal Filter<br>Building Block |                                                                    | Four 2nd Order Filter Sections in 28-Pin SSOP, 56kHz Max Center Frequency, $\leq 40 \mu V_{RMS}$ Noise per 2nd Order Section, Operation 3.3V to $\pm 5 V_{RMS}$ |  |

| LTC1068-25                                                                     | High Speed, High Accuracy, Quad Universal<br>Filter Building Block | Four 2nd Order Filter Sections in 28-Pin SSOP, 200kHz Max Center Frequency, Operation 3.3V to $\pm 5V$                                                          |  |

| LTC1068-50                                                                     | Low Power, High Accuracy, Quad Universal<br>Filter Building Block  | Four 2nd Order Filter Sections in 28-Pin SSOP, 40kHz Max Center<br>Frequency, 3.5mA at Single 5V, Operation 3.3V to ±5V                                         |  |

| LTC1562                                                                        | Very Low Noise, Low Distortion, Active RC Quad<br>Universal Filter | Four 2nd Order Filter Sections, No Clock Required, 150kHz Max Center Frequency, SSOP                                                                            |  |

1264fb LT/LT 0805 REV B • PRINTED IN USA TECHNOLOGY © LINEAR TECHNOLOGY CORPORATION 1993

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.